**ABSTRACT**

Title of dissertation: MODEL-BASED HARDWARE DESIGN FOR IMAGE

PROCESSING SYSTEMS

Mainak Sen, Doctor of Philosophy, 2006

Dissertation directed by: Professor Shuvra S. Bhattacharyya

Department of Electrical and Computer Engineering, and

Institute for Advanced Computer Studies

Model-based design has been touted as the most viable design methodology of the future for the design of embedded hardware/software systems. Due to the large complexity of modern embedded systems, it is more and more error-prone to design systems without having a formal model to support and verify the application at design time. Also, formal models generally capture broad classes of applications, and thus any innovation on a modeling technique has the potential to enhance every individual application in the associated class. Often, a formal model captures the high-level abstraction of an application, which is lost in the final implementation, and thus modeling gives an effective platform to perform high-level design optimizations. Dataflow graphs have been widely used as formal models in the signal processing domain for a long time, and various commercial tools have adopted dataflow semantics for model-based design methodology.

In this thesis, we develop a new dataflow meta-modeling technique, called *homoge-neous parameterized dataflow* (*HPDF*). HPDF is a meta-modeling technique in that it can be applied to a variety of underlying dataflow models of computation to enhance their expressive power, while maintaining much of the useful structure of the underlying models. HPDF addresses an important range of applications, especially in the image processing domain. We present various properties and capabilities of HPDF, including the notions of repetitions vector, valid schedule, derivation of looped schedules, single-rate equivalent graphs, and HPDF graph transformation methods. We also give three in-depth examples of complex systems that we have studied to demonstrate the capabilities of HPDF — a gesture recognition application, an image registration application, and a gait-DNA application. For hardware implementation, we target our applications onto Xilinx and Altera field programmable gate arrays (FPGAs), and we present results from the hardware mapping of the gesture recognition and the image registration application.

To build a foundation for further broadening the impact of HPDF modeling, we present initial work on applying cyclo-static dataflow as an intermediate representation for mapping MATLAB programs into hardware implementations. Because of the compatibility between cyclo-static dataflow and the HPDF meta-modeling approach, which we demonstrate in Chapter 3 of this thesis, this is an important first step to exploiting HPDF techniques in the context of MATLAB-to-hardware synthesis. In particular, we focus on relating cyclo-static dataflow to Compaan process networks, which is a variant of the Kahn process network model of computation that has been shown to be useful in representing concurrency in MATLAB programs.

In summary, this thesis develops a useful new meta-modeling approach for implementing an important class of image processing applications, and develops and extensively demonstrates a methodology for efficient hardware implementation from representations in the proposed new meta-model.

# MODEL-BASED HARDWARE DESIGN FOR IMAGE PROCESSING SYSTEMS

by

Mainak Sen

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2006

#### **Advisory Committee**

Professor Shuvra S. Bhattacharyya, Chair/Advisor Professor Rama Chellappa Professor Gang Qu Professor Raj Shekhar Professor Amitabh Varshney, Dean's Representative © Copyright by

Mainak Sen

2006

## **DEDICATION**

to my Mother, Father, Brother and Amrita

#### **ACKNOWLEDGMENTS**

I want to take this opportunity to thank my advisor, Professor Shuvra Bhattacharyya for all his support and encouragement throughout the course of my graduate studies. Looking back, I feel extremely lucky to have had him straight out of undergraduate from Jadavpur University as I was lost coming to a new country, and getting into unfamiliar surroundings. From that point on, whenever I have tried to set foot into something new, he has always given me the extra time for the learning curve. Without his support, I could not have taken some time out to have my own music band or lead the Electrical and Computer Engineering Graduate Student Association (ECEGSA).

I also want to thank Prof. Rama Chellappa for his support and ideas that has helped me in my Ph.D at various times. Prof. Wayne Wolf at Princeton University has provided us with applications to build our model on and has always obliged to all my requests. Prof. Raj Shekhar has been very supportive and also helped me with applications to test my model on. Prof. Ed Deprettere from Leiden University, The Netherlands has been very helpful with development of a strong collaboration between his research group and our DSPCAD group at UMD and it was a very rewarding experience to work with such an experienced professor in our field. Prof. Gang Qu, Prof. Andre Tits, Prof. Ankur Srivastava, and Prof. Richard La has lent me a patient ear specially towards the end of my Ph.D when time seems to be the flying faster than ever. Prof. Amitabh Varshney has been very kind by agreeing to be the Dean's representative for my committee.

It has been a pleasure to interact with many students in the DSPCAD group and the Embedded Systems Research Lab, including Ming-Yung, Vida, Dong-Ik, Nitin, Neal,

Shahrooz, Sumit, Fuat, Sadagopan, Lin, Chung-Ching, Chia-Jui, Sankalita, Sebastian, Celine, and Ruirui.

Ivan and Fiorella needs special mention for working with me. It was a great experience working late nights and sharing our thoughts. The modeling and FPGA implementation of gesture recognition algorithm was the result of joint effort from the three of us. Modeling of image registration algorithm was a joint work with Yashwant and this work would not have been possible in such a short time without his efforts. I would also like to thank Todor Stefanov from Leiden University for our joint work on CPN and dataflow. I want to thank Dr. William Plishker for reviewing some of my papers and part of my thesis. My collaborations and discussions with all of them have strengthened this thesis and enriched my experience here.

I would also like to thank some of my friends here at UMD, many of whom I met for a relatively small period of time but they left a large footprint on my heart. Suvarcha has been a very good friend of mine for a long time and Ankush is one of the best people I have met in my life.

Finally and most importantly, I would like to thank my family for their love, support, and patience during these years while I focused on studies. Thanks to my mom, dad and brother for helping me aim high and provide support in every way possible. My late grandparents who loved me more than anyone else in the whole world. My nieces and nephews have been my source of fun and joy always. Last but certainly not the least, I would also like to thank Amrita for filling my life with laughter and joy and I look forward to spending the rest of my life with her.

# Table of Contents

| Chapter 1. | Intro | duction                                                   | 1      |

|------------|-------|-----------------------------------------------------------|--------|

|            | 1.1.  | Overview                                                  | 1      |

|            | 1.2.  | Contributions of this Thesis                              | 3      |

|            | 1.3.  | Outline of this thesis                                    | 7      |

| Chapter 2. | Back  | ground and Related Work                                   | 9      |

|            | 2.1.  | Dataflow Graphs                                           | 9      |

|            | 2.2.  | Related Work                                              | 18     |

| Chapter 3. | Hom   | ogeneous Parameterized Dataflow Graph (HPDF)              | 25     |

|            | 3.1.  | Model Definition                                          | 26     |

|            | 3.2.  | An Extended Model Definition                              | 27     |

|            | 3.3.  | Comparison of HPDF and PSDF                               | 31     |

|            | 3.4.  | Scheduling of HPDF Graphs                                 | 32     |

|            | 3.5.  | Modeling using HPDF                                       | 42     |

| Chapter 4. | Tran  | sformations for HPDF Graphs                               | 46     |

|            | 4.1.  | Motivation                                                | 46     |

|            | 4.2.  | Node Unfolding                                            | 49     |

|            | 4.3.  | Node Unfolding on HPDF                                    | 50     |

|            | 4.4.  | High-level Synthesis Problem Statement and Systematic Noc | le Un- |

|            |       | folding Algorithm                                         | 51     |

|            | 4.5.  | Automatic Verilog Code generation                         | 55     |

|            | 4.6.  | Results                                                    | 58   |

|------------|-------|------------------------------------------------------------|------|

|            | 4.7.  | Conclusion                                                 | 60   |

| Chapter 5. | HPD   | F-based Analysis Case Study: Gesture Recognition           | 62   |

|            | 5.1.  | Description of the algorithm                               | 63   |

|            | 5.2.  | Modeling the Single-Camera Gesture Recognition Algorithm . | 66   |

|            | 5.3.  | Modeling the Distributed Gesture Recognition Algorithm     | 71   |

|            | 5.4.  | From the Model to Hardware                                 | 75   |

|            | 5.5.  | Experimental Setup                                         | 77   |

|            | 5.6.  | Design Trade-offs and Optimizations                        | 79   |

|            | 5.7.  | Results                                                    | 86   |

|            | 5.8.  | Conclusion                                                 | 88   |

| Chapter 6. | HPD   | F-based Hardware Mapping Case Study: Image Registr         | ra-  |

|            | tion. |                                                            | 90   |

|            | 6.1.  | Introduction                                               | 90   |

|            | 6.2.  | FPGA technology                                            | 92   |

|            | 6.3.  | Application Description                                    | 93   |

|            | 6.4.  | Modeling using HPDF-CSDF                                   | 99   |

|            | 6.5.  | Actor Implementation                                       | 105  |

|            | 6.6.  | Experimental Setup                                         | 106  |

|            | 6.7.  | Results                                                    | 107  |

|            | 6.8.  | Dynamic Reconfiguration                                    | 111  |

|            | 6.9.  | Conclusion                                                 | 113  |

| Chapter 7. | Inter | mediate Representations for MATLAB Synthesis               | .114 |

|             | 7.1.  | Introduction to Compaan       | 115 |

|-------------|-------|-------------------------------|-----|

|             | 7.2.  | Relation between SBF and CSDF | 118 |

|             | 7.3.  | CSDF to SBF                   | 122 |

|             | 7.4.  | Introduction to DIF           | 124 |

|             | 7.5.  | Proposed extensions to DIF    | 126 |

|             | 7.6.  | Binary CSDF                   | 129 |

| Chapter 8.  | Conc  | clusions and Future Work      | 130 |

|             | 8.1.  | Conclusion                    | 130 |

|             | 8.2.  | Future Work                   | 133 |

| Appendix    | ••••• |                               | 136 |

| Bibliograph | ıy    |                               | 144 |

# List of Figures

| Figure 1.1 | Example working of Simulink HDL coder. Figure taken from the Math        | -    |

|------------|--------------------------------------------------------------------------|------|

|            | works website.                                                           | 3    |

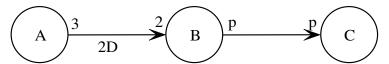

| Figure 2.1 | A simple SDF graph.                                                      | 10   |

| Figure 2.2 | A simple CSDF graph.                                                     | 11   |

| Figure 2.3 | PSDF specification of a decimate actor that decimates by a different fac | ctor |

|            | at each run (figure from [3]).                                           | 16   |

| Figure 2.4 | A 16 processing element (PE) MESH architecture where end-around co       | n-   |

|            | nections are not shown.                                                  | 22   |

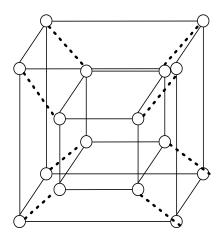

| Figure 2.5 | processor hypercube architecture                                         | 23   |

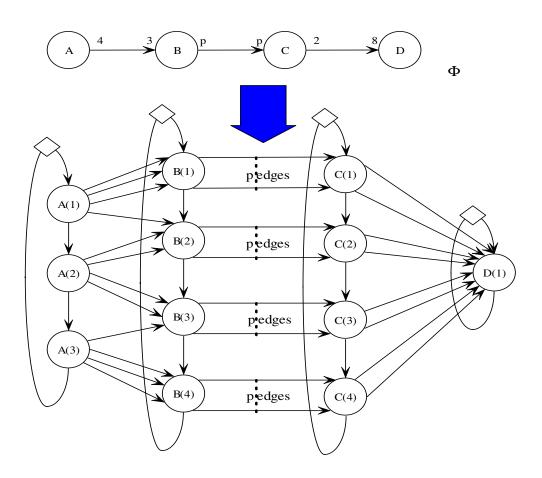

| Figure 3.1 | An example of an HPDF graph                                              | 28   |

| Figure 3.2 | Converting to its SDF reduction by replacing parameters and with the     | val- |

|            | ue                                                                       | 34   |

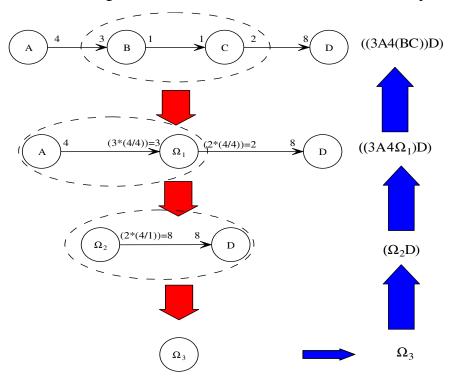

| Figure 3.3 | Example of working of APGAN and the resultant schedule                   | 38   |

| Figure 3.4 | APGAN on an HPDF graph                                                   | 39   |

| Figure 3.5 | HSDF equivalent of an HPDF graph                                         | 41   |

| Figure 3.6 | HPDF-SDF model of the Gait-DNA algorithm for load carrying event of      | de-  |

|            | tection                                                                  | 43   |

| Figure 3.7 | HPDF-CSDF model of the Gait DNA application for load carrying event      | de-  |

|            | tection                                                                  | 44   |

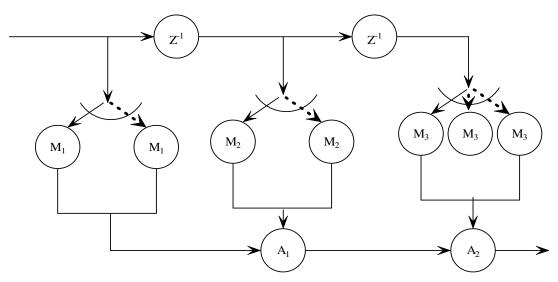

| Figure 4.1 | An SDF graph representation of a 3-tap FIR filter with production and o  | con- |

|            | sumption rates uniformly equal to one.                                   | 47   |

| Figure 4.2 | The 3-tap FIR filter shown in Figure 4.1 with different node unfolding   | fac- |

|            | tors for the multipliers. Switches are also shown as a means of implementa-  |

|------------|------------------------------------------------------------------------------|

|            | tion of node unfolding48                                                     |

| Figure 4.3 | Algorithm for unfolding a node, times                                        |

| Figure 4.4 | Illustration of the Node unfolding algorithm where A is unfolded twice50     |

| Figure 4.5 | Example showing node unfolding being used on HPDF51                          |

| Figure 4.6 | The algorithm used to get the data parallel factors for each module53        |

| Figure 4.7 | Generated synthesizable Verilog code for the 3-tap FIR filter described in   |

|            | Figure 1                                                                     |

| Figure 4.8 | The example Verilog code of a simple switch58                                |

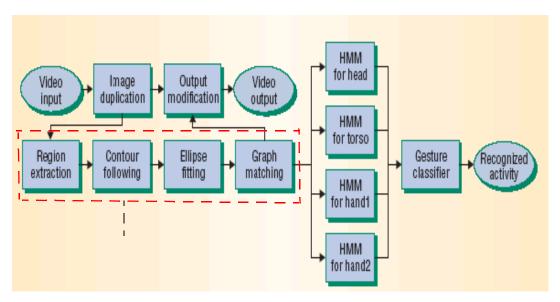

| Figure 5.1 | Block level representation of the smart camera algorithm [55]64              |

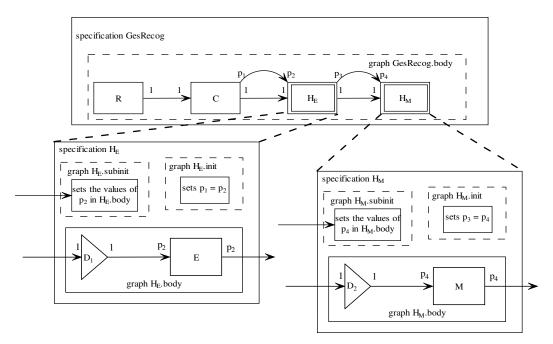

| Figure 5.2 | PSDF modeling of the Gesture Recognition application67                       |

| Figure 5.3 | HPDF model of the application with parameterized token production and        |

|            | consumption rates, where R is Region, C is Contour, E is Ellipse, and M is   |

|            | Match                                                                        |

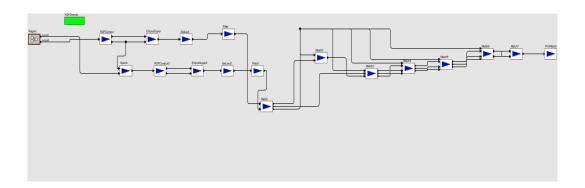

| Figure 5.4 | The HPDF graph of the application as shown in Figure 5.3 with flattened hi-  |

|            | erarchy for C, E, and M in Ptolemy II69                                      |

| Figure 5.5 | Model of the static part of the system69                                     |

| Figure 5.6 | Region is shown to be broken into a four stage pipeline process71            |

| Figure 5.7 | Contour is shown to have conditional edges and serial execution. This struc- |

|            | ture is implemented as a four-stage, self-timed process71                    |

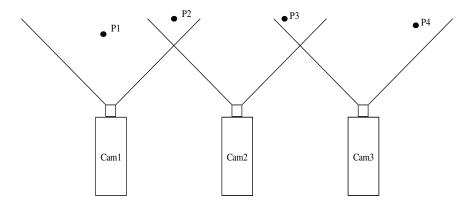

| Figure 5.8 | The geometry of the smart cameras in the multiple camera system72            |

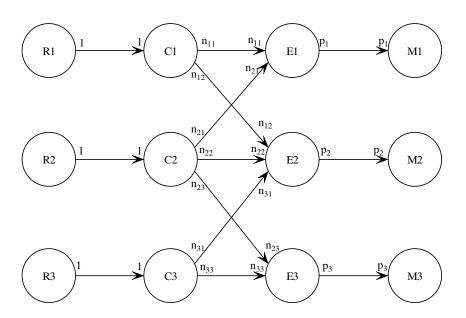

| Figure 5.9 | HPDF model of the distributed gesture recognition algorithm for the net-     |

|            | work in Figure 5.8, assuming contour is transmitted across cameras 73        |

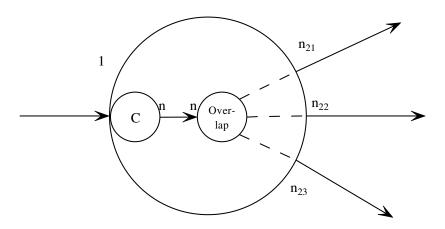

| Figure 5.10 | A closer look at the modified Contour actor in the distributed gesture recog- |

|-------------|-------------------------------------------------------------------------------|

|             | nition algorithm74                                                            |

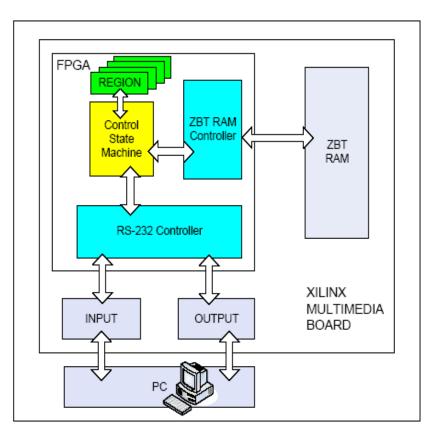

| Figure 5.11 | The overall setup showing interactions among various modules of our de-       |

|             | sign and components of the multimedia board                                   |

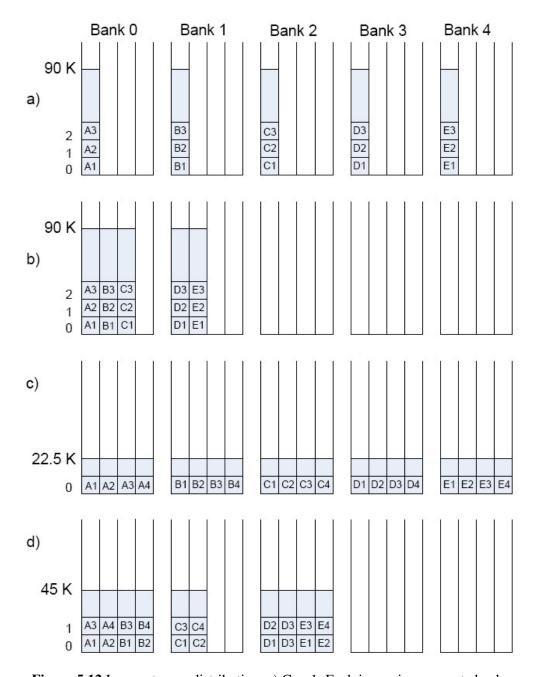

| Figure 5.12 | Image storage distribution. a) Case1: Each image in a separate bank using     |

|             | only the first byte of the first 90K words of the memory. b) Case2: Three im- |

|             | ages in bank 0 and two in bank. c) Case3: Each image in a separate bank but   |

|             | all four bytes used in each word, using 22.5K words. d) Case4: Images         |

|             | stored in three banks, each using 2 bytes of the first 45K words81            |

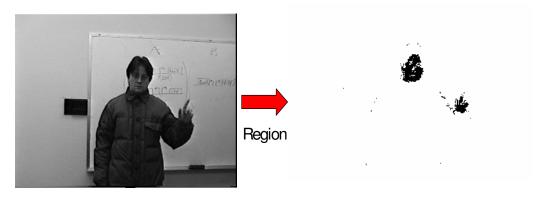

| Figure 5.13 | Our HDL representation of Region transforms the image on the left to the      |

|             | output on the right86                                                         |

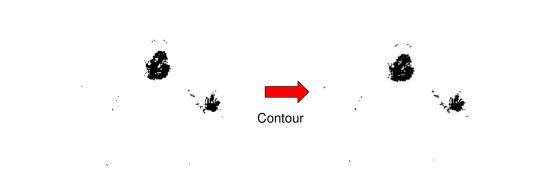

| Figure 5.14 | Actual transformation to the image done by HDL representation of Contour      |

|             | 86                                                                            |

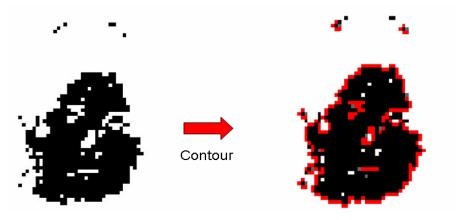

| Figure 5.15 | Part of Figure 5.14 zoomed-in and colored to show the effect of Contour       |

|             | 87                                                                            |

| Figure 5.16 | Comparison of percentage RMS error for different-length floating point rep-   |

|             | resentations, normalized to a 64-bit floating point representation87          |

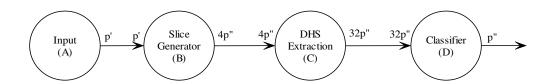

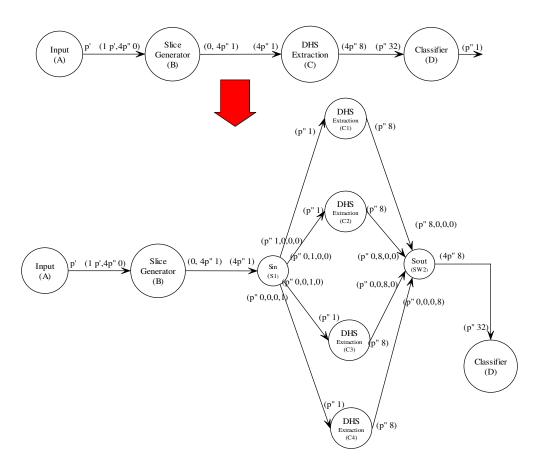

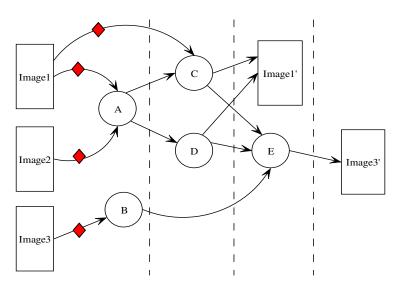

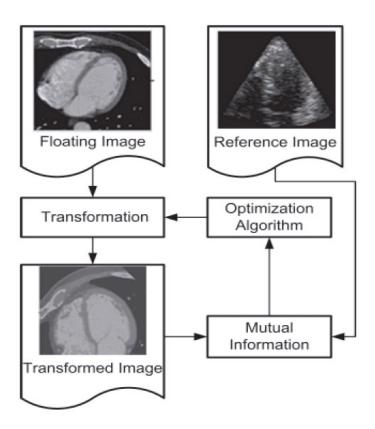

| Figure 6.1  | Mutual Information based Image Registration94                                 |

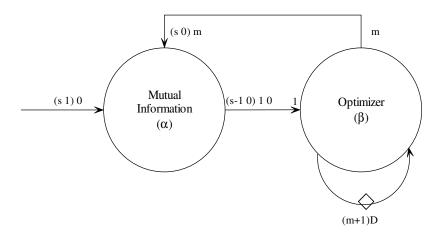

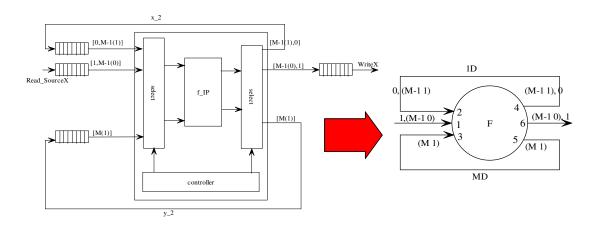

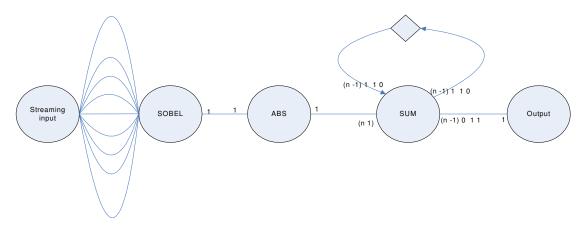

| Figure 6.2  | Top level model of image registration application                             |

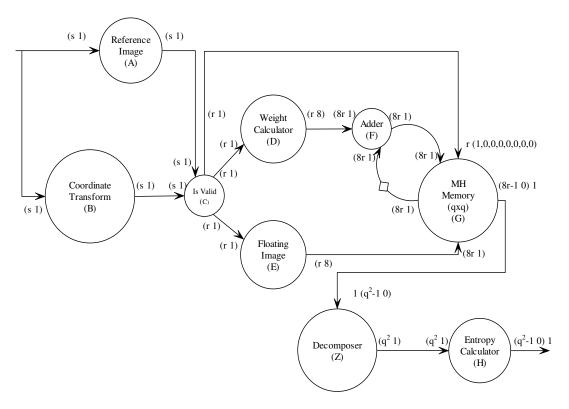

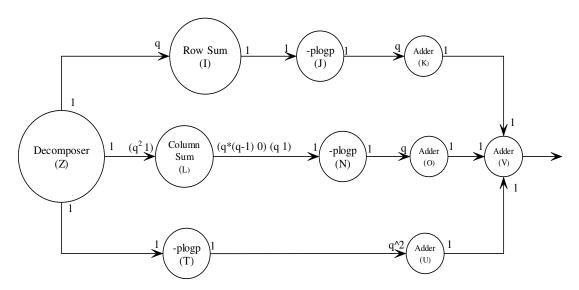

| Figure 6.3  | Dataflow model of Mutual Information subsystem100                             |

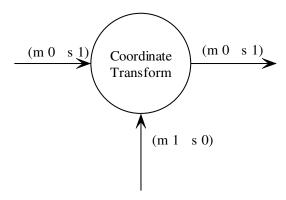

| Figure 6.4  | Initial and steady-state modeling of Coordinate Transform                     |

| Figure 6.5  | Parameterized "Entropy Calculator" where depends on the number of bits        |

|             | used to represent each pixel in the input image, is for bit images102         |

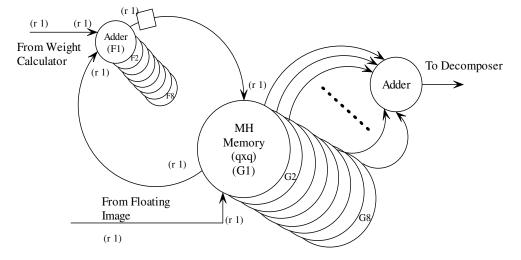

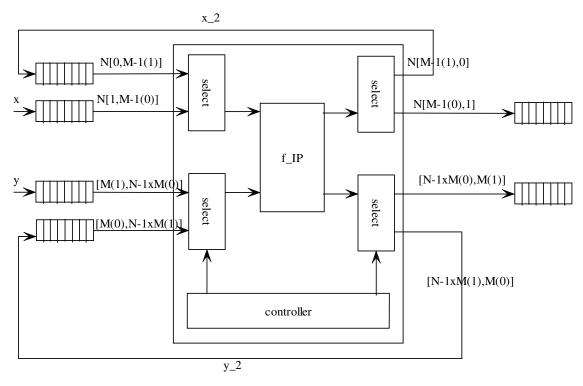

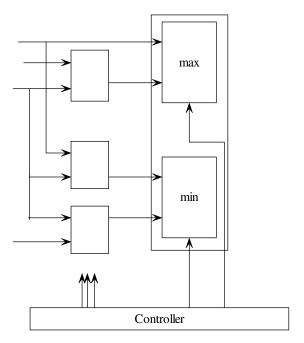

| Figure 6.6  | Parallel architecture for MH update103                                          |

|-------------|---------------------------------------------------------------------------------|

| Figure 6.7  | Example code (partial) of the Adder from Figure 6.3                             |

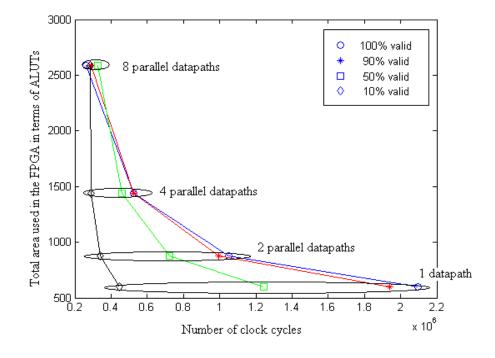

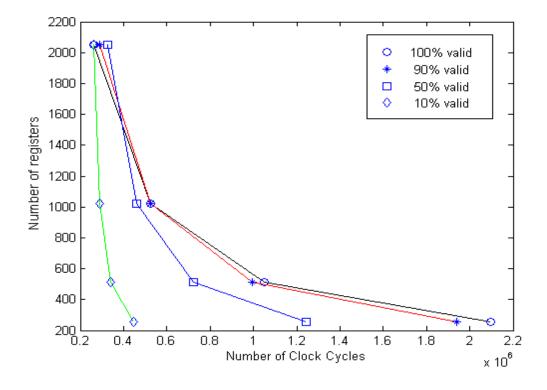

| Figure 6.8  | Area v/s clock cycles for different PVV for different number of datapaths       |

|             | 110                                                                             |

| Figure 6.9  | Whole system memory requirements in bytes including external memory             |

|             | 111                                                                             |

| Figure 7.1  | An affine-nested loop program                                                   |

| Figure 7.2  | The Single Assignment Program version of the Affine Nested Loop Pro-            |

|             | gram in Figure 7.1                                                              |

| Figure 7.3  | The PRDG corresponding to the SAP in Figure 7.2117                              |

| Figure 7.4  | Example of the generated code for a Node. This node used here is ND_3 in        |

|             | Figure 7.3                                                                      |

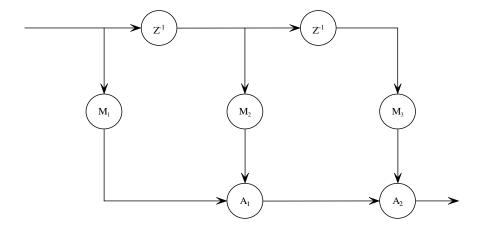

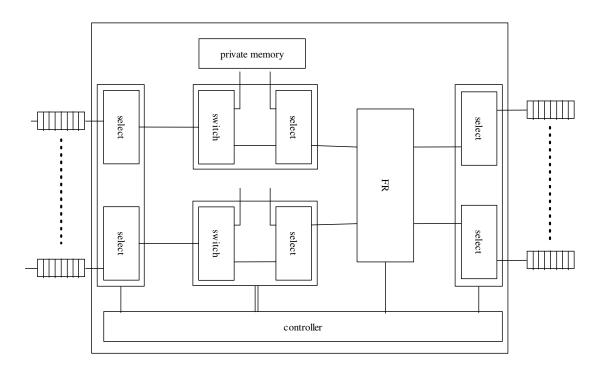

| Figure 7.5  | Strucure of a SBF Virtual Processor                                             |

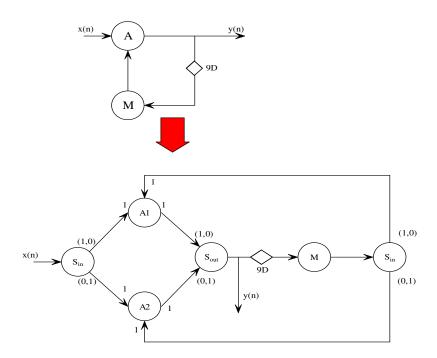

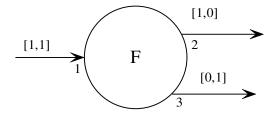

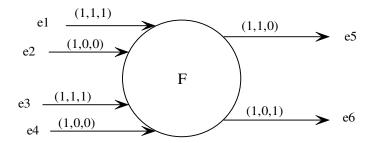

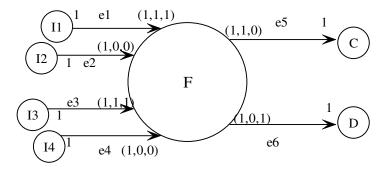

| Figure 7.6  | An example CSDF actor                                                           |

| Figure 7.7  | SBF virtual f() processor for the prgram in Figure 7.1 with explicit mention    |

|             | of read and write sequences.                                                    |

| Figure 7.8  | The steady-state equivalent virtual f() processor of Figure 7.7 on the left and |

|             | its corresponding CSDF actor on the right                                       |

| Figure 7.9  | Construction of SBF VP back from Table 7. 1                                     |

| Figure 7.10 | An example binary CSDF                                                          |

| Figure 7.11 | Computational behavior of actor F in Figure 7.10                                |

| Figure 7.12 | SBF VP for the actor in Figure 7.10                                             |

| Figure 7.13 | CSDF graph made from Figure 7.10 for the purpose of explaining the DIF          |

|             | generated from it                                                           |

|-------------|-----------------------------------------------------------------------------|

| Figure 7.14 | DIF representation of the CSDF graph in Figure 7.13128                      |

| Figure 7.15 | C addition to the DIF representation of Figure 7.14 to represent the CSDF   |

|             | graph of Figure 7.13                                                        |

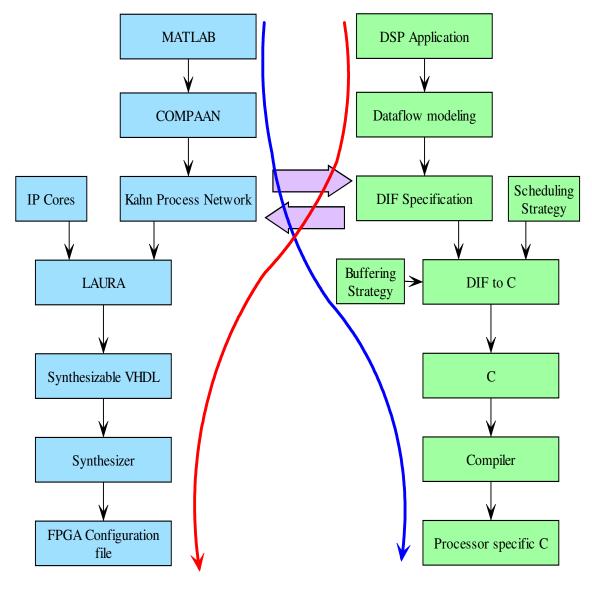

| Figure 8.1  | The two existing flows can be merged using our proposed intermediate rep-   |

|             | resentation as shown by the two curved lines                                |

| Figure A.1  | The flowchart of the application                                            |

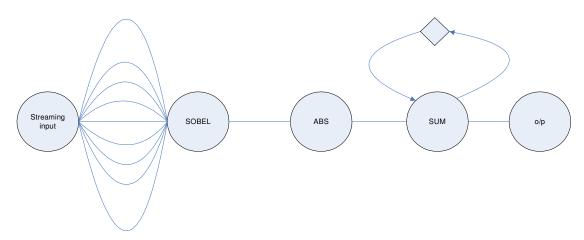

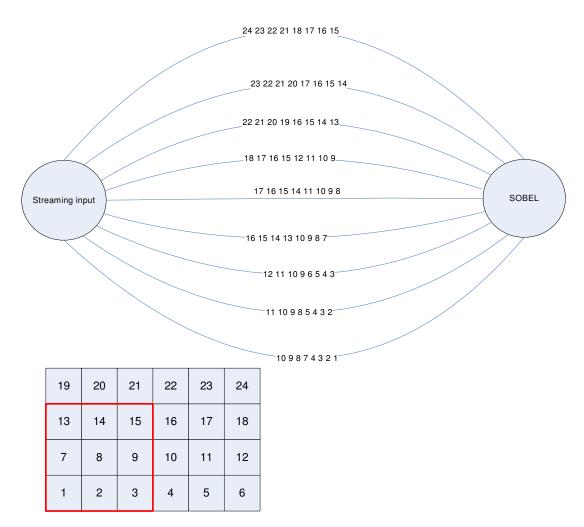

| Figure A.2  | An example showing the pixels to be stored on different edges where $m = 6$ |

|             | and n = 4                                                                   |

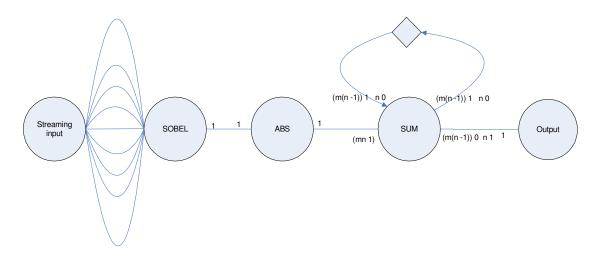

| Figure A.3  | CSDF modeling of the model of the application with horizontal scanning      |

|             |                                                                             |

| Figure A.4  | CSDF modeling of the application for vertical scanning. The buffer is ini-  |

|             | tialized to zero for each iteration of the graph140                         |

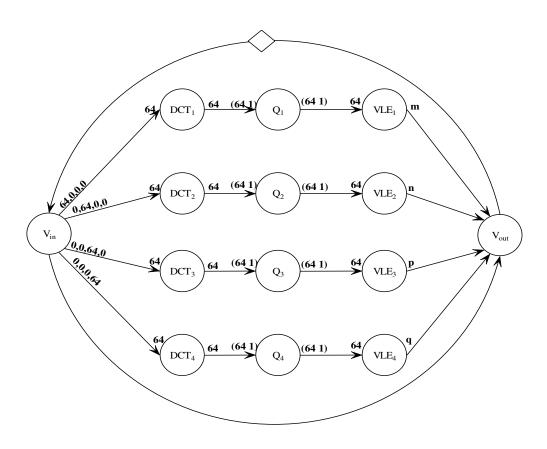

| Figure A.5  | A simplied version of MJPEG algorithm in dataflow representation142         |

| Figure A.6  | way image partioning for MJPEG where each numbered block is143              |

| Figure A.7  | CSDF representation of the MJPEG considering a partition as shown in Fig.   |

|             | A.6143                                                                      |

# List of Tables

| Table 4.1.  | Results of adder multiplier circuit from Synopsys                        | 59    |

|-------------|--------------------------------------------------------------------------|-------|

| Table 4.2.  | Results of a 3-tap FIR filter from Synopsys                              | 59    |

| Table 4.3.  | Results of a second order IIR filter from Synopsys                       | 60    |

| Table 5 1.  | Comparison of different memory layout strategies.                        | 82    |

| Table 5 2.  | Synthesis results.                                                       | 85    |

| Table 6.1.  | Synthesis results for the whole system for different configurations of t | he    |

|             | MH Update actor.                                                         | 108   |

| Table 6.2.  | Comparison of power consumption of circuit in different datapath con     | figu- |

|             | rations                                                                  | 109   |

| Table 6.3.  | Comparison of intra- versus inter-pixel parallelism modes for different  | PVV   |

|             | values                                                                   | 112   |

| Table 7. 1. | Table represnting the function                                           | 122   |

| Table 7. 2. | Table representing the BCSDF actor in Figure 7.10                        | 123   |

## **Chapter 1. Introduction**

#### 1.1. Overview

Model-based design is rapidly becoming a popular approach in design environments for embedded systems due to high level of complexity in these systems. In model-based design, design representations in terms of formal models of computation (MoC) are used to capture, analyze, simulate, and in some cases, optimize and implement the targeted applications. Detailed simulation of the whole system can cut down on costly changes late in the design phase, which are otherwise not visible at a component level. To overcome this fundamental problem, engineers are moving toward model-based design environments that encompass and support all the major phases of system development: design, simulation, code generation, verification, and implementation, as outlined above.

There are many model-based design tools available, both commercially and from academic sources, for embedded systems design — e.g., LabVIEW from National Instruments, Simulink<sup>®</sup> from Mathworks, and Ptolemy II from U.C. Berkeley [17], to name a few. However, designing a hardware system through systematic use of a formal model has only recently been emerging as an area of interest not only to the academic world, but also to commercial vendors.

We cite some of the industry efforts made towards model-based hardware code generation, however this list is not comprehensive. We also present some related work done in academia in Section 2.2. First, Synplicity — a leading provider in electronic design automation (EDA) tools, has a model-based hardware design tool named Synplify<sup>®</sup> DSP, which is built for digital signal processing (DSP) system designers who target field pro-

grammable gate arrays (FPGAs) and application specific integrated circuits (ASICs) for implementation of high-performance DSP designs. Synplify<sup>®</sup> DSP provides an environment for specifying a design at the algorithm level in MATLAB<sup>®</sup>/Simulink<sup>®</sup>, and mapping the algorithm representation into an RTL design without the need for multiple iterations between the DSP algorithm architect and the RTL hardware designer as in a traditional design cycle.

LabVIEW FPGA by National Instruments provides a graphical programming environment to define the logic in FPGA chips that are embedded across the family of National Instruments reconfigurable I/O hardware targets. Due to the high level of abstraction used in this tool, designer can design and implement FPGA-based designs without the knowledge of low-level hardware description languages.

Xilinx — a leading provider of FPGAs and related software tools, introduced System Generator<sup>™</sup> for DSP, which is another effort to build a high-level tool for designing high-performance DSP systems using FPGAs. The tool provides abstractions that enable the development of parallel systems with advanced FPGAs, providing system modeling and automatic code generation from Simulink<sup>®</sup> and MATLAB<sup>®</sup>.

Altera, another leading maker of high-performance FPGAs, has a similar graphical tool for high performance DSP design for FPGAs. This tool, called Altera DSP Builder, is a block-based tool that interfaces between Quartus<sup>®</sup> II — which is the synthesis tool for Altera FPGAs — and MATLAB<sup>®</sup>/Simulink<sup>®</sup> tools.

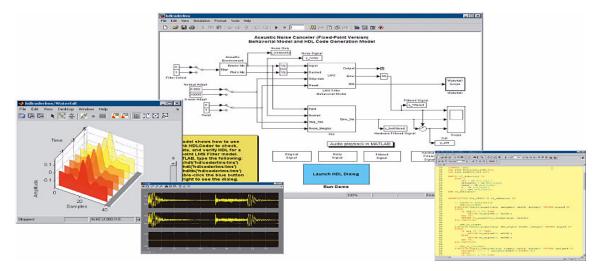

Recently (September 2006), The Mathworks has introduced a new tool called the Simulink<sup>®</sup> HDL Coder. It is for system and hardware engineers, letting them adopt model-based design in their development processes for both hardware and software. The tool

automatically generates synthesizable hardware description language (HDL) code from its own Simulink<sup>®</sup> and Stateflow<sup>®</sup> software. Simulink HDL Coder can produce target-independent Verilog and VHDL code and test benches for implementing and verifying ASICs and FPGAs and later synthesize for their target platforms. Figure 1.1 shows a snapshot of the working of HDL coder with a block-based design window in the middle, simulation results in software on the left, and generated HDL code on the right of the figure.

#### 1.2. Contributions of this Thesis

Our work is similar in spirit to the recent industry trends described in the previous section. This similarity is in the sense that we have a similar motivation of proposing a methodology for generating FPGA implementations from high-level, block- and model-based design environments. However, our work is different in certain respects towards obtaining that goal. First, we employ dataflow models of computation, which are widely used in the DSP community, as the general formal modeling approach to capture high-level abstractions of applications, and we develop a framework through which various

**Figure 1.1** Example working of Simulink HDL coder. Figure taken from the Mathworks website.

dataflow graph transformations can be made with high-performance, hardware synthesis in view. Second, we develop a specific dataflow modeling approach that targets a restricted but important class of image processing applications, and using our modeling approach, we develop methods for systematically exploiting properties in the targeted applications to streamline the analysis, synthesis, and optimization of hardware implementations. Thus, this thesis represents a novel convergence of methods involving dataflow modeling, image processing, and hardware implementation.

In the following sections, we elaborate further on the main contributions of this thesis.

#### **1.2.1.** Homogeneous Parameterized Dataflow (HPDF)

Static dataflow graphs, such as those based on synchronous dataflow (SDF) [31] or cyclo-static dataflow (CSDF) [6] principles, have been relatively well-studied in the literature. However, many modern signal processing applications are dynamic or data-dependent in nature to some extent, and cannot be fully modeled using static dataflow graphs. We have proposed a new dataflow modeling approach, called homogeneous parameterized dataflow (*HPDF*), that captures a subset of applications with a restricted form of dynamic data production and consumption behavior.

HPDF is a meta-model in that it can be applied to a variety of different underlying dataflow models of computation, such as synchronous dataflow or cyclo-static dataflow. When HPDF is applied to an underlying dataflow model, we refer to the underlying model as the *base model* to which HPDF is applied, and we say that HPDF is being applied "over" the base model (e.g., "HPDF over SDF" or "HPDF over CSDF"). The integration of the HPDF meta model with a base model generally results in a more powerful (more

expressive) version of the base model that retains much of the intuitive structure and much of the useful analysis and optimization potential of the base model.

HPDF is intuitive and well-suited to many image processing applications. HPDF is similar to SDF in that it imposes significant restrictions on application structure, and has an inherent simplicity in its core semantics, but captures an important class of applications despite this simple and restrictive nature. to the These characteristics have contributed significantly to the intuitive appeal, general popularity, and utility of SDF, and it is therefore promising that HPDF exhibits this similarity.

In this thesis, we motivate and develop in detail the HPDF meta-modeling technique. We then define and explore useful properties of HPDF. To demonstrate the applicability and capabilities of HPDF, we have develop three in-depth case studies of important image processing applications. These applications include a gait-DNA application for load carrying event detection [42], a gesture recognition application [55], and a 3-D image registration application. For all the three applications, we first employ HPDF over SDF, and then refine our model using HPDF over CSDF so that the meta-modeling aspect of HPDF can be concretely demonstrated.

#### 1.2.2. Graph Transformation - Node Unfolding

In this thesis, we propose a new dataflow graph transformation — *node unfolding*. Node unfolding can be used effectively to explore the design space starting with a dataflow graph representation of an application when the final implementation is targeted towards hardware, especially hardware in which area constraints are relevant. Node unfolding systematically replicates selected nodes in the dataflow graph.

We propose an algorithm to transform an input dataflow graph by repeated application of node unfolding for high-throughput implementation in hardware. The algorithm requires initial estimates of execution time and area for each node in the graph, and it applies maximum cycle mean (MCM) analysis for performance estimation. We also present a preliminary version of a Verilog code generator for dataflow graphs that can be used after we arrive at a suitably-transformed graph to generate HDL code.

#### 1.2.3. HPDF to FPGA implementation

In this thesis, we present extensive demonstrations of FPGA implementations that are derived from HPDF-based representations. Such demonstrations are developed for two applications. First, we demonstrate the mapping of a gesture recognition application onto the Xilinx Multimedia and Microblaze board. This board features a Virtex II FPGA that supports 2 million gates. For the gesture recognition application, we also present an effective method for exploring trade-offs between different memory layout schemes, and we present a thorough floating point optimization study for the application. Next we present an HPDF-based mapping of a 3-D image registration algorithm onto an Altera StratixII FPGA. In the process, we present a study of performance and area trade-offs across a multitude of design points that correspond to various parallel implementations. These parallel implementations can be mapped naturally onto an FPGA from the high-level HPDF specification. We also present a dynamically reconfigurable architecture for the image registration algorithm, and we present a novel parameterization of such an architecture in terms of a metric that is based on the percentage of valid voxels (PVV) that are being considered at a given algorithm iteration. This metric and its utility are developed in detail in Chapter 6.

#### 1.2.4. Dataflow as an Intermediate Representation for MATLAB Synthesis

Sequential, static affine nested loop programs can be automatically converted to input-output equivalent Kahn process network (KPN) specifications [28]. The correspondence between these classes of specifications have derived and exploited in depth by the Compaan project [28]. Such specialized KPNs are also called Compaan process networks (CPNs). Our studies, which have been developed in collaboration with the Compaan project team at Leiden University, have shown that CPNs form a special case of the cyclostatic dataflow graph (CSDF) model [6], but with additional non-dataflow properties that need to be associated to derive a comprehensive correspondence [14].

The dataflow interchange format (DIF) is a standard language for specifying mixed-grain dataflow models for DSP systems [25]. In this thesis, we extend DIF to capture the form of cyclo-static dataflow that emerges from CPNs. Both CPN and CSDF are relatively mature formal models and our preliminary study on their correspondence establishes the potential to exchange information between the two domains to improve the synthesis of hardware and software implementations from MATLAB programs. In particular, the correspondence that we developed provides a bridge between the path from MATLAB to CPNs, that has been developed in the Compaan project [28], with the paths from dataflow representations to hardware that are developed in efforts such as this thesis.

#### 1.3. Outline of this thesis

The rest of this thesis is structured as follows — Chapter 2 gives background information on dataflow, and describes previous related work. Chapter 3 introduces the HPDF meta-model, proves formal properties in relation to this model, and provides a concrete

example by modeling a gait-DNA application using the proposed techniques. Chapter 4 introduces a new graph transformation technique named "node unfolding", its application to HPDF, use of this technique for design space exploration in high-level synthesis techniques for hardware synthesis from dataflow, and preliminary work developed towards designing a Verilog code generator for dataflow graphs. Chapter 5 describes a gesture recognition algorithm, and HPDF modeling and hardware implementation targeting a Xilinx Virtex II FPGA. Chapter 6 describes an image registration algorithm, its HPDF model, dataflow graph transformation based on the applied modeling, and FPGA implementation and comparison of various implementation points for the algorithm. Chapter 7 describes initial efforts towards integrating the Compaan intermediate representation framework with dataflow modeling, and develops extensions to the dataflow interchange format (DIF) [25] that achieve this integration. Chapter 8 gives concluding remarks, summarizes this thesis, and suggests useful directions for future work.

## Chapter 2. Background and Related Work

In this chapter, we present some background to understand this thesis and also present some previous work and show their relation to this thesis.

#### 2.1. Dataflow Graphs

In this section, we review background on synchronous dataflow, cyclo-static dataflow, and parameterized dataflow modeling, and describe various basic definitions related to signal-processing-oriented dataflow modeling. The concepts reviewed in this section will be applied later in the thesis in our formal development of HPDF.

#### 2.1.1. Synchronous Dataflow

Synchronous dataflow (SDF) is a restricted form of dataflow in which data production and consumption rates of actor ports (inputs and outputs) are restricted to be constant values that are known at compile time [31]. This restriction enables static scheduling from SDF representations, and offers strong compile-time predictability properties, and powerful optimization techniques, such as joint minimization of program and data memory requirements [5]. These features come at the expense of limited expressive power, since SDF cannot model data production rates that vary dynamically or are otherwise unknown at compile time.

SDF is employed in a variety of widely-used commercial design tools, such as CoWare SPW, Agilent ADS, and National Instruments LabVIEW.

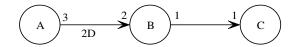

An example of a simple SDF graph is in shown in Figure 2.1. Here, each edge is annotated with the numbers of tokens that are produced by the source and sink actors of the edge. For example, actor A produces 3 tokens on edge (A, B) every time it is invoked, and each invocation of C results in 1 token being consumed from the edge (B, C). The description of 2D is given in Section 2.1.3.

SDF graphs — and signal-processing-oriented dataflow graphs in general — typically represent computations that are iterated infinitely or for indefinite time (e.g., due to the absence of apriori bounds on the durations of the input streams). Thus, each actor generally corresponds to an infinite number of invocations in an execution of the graph.

#### 2.1.2. Cyclo-static dataflow

Cyclo-static dataflow (CSDF) is an extension of SDF where production and consumption rates of actors can vary as long as the variations take the form of periodic sequences that are known at compile time. Given a CSDF actor A, a finite sequence is associated with the production rate of each output edge, and with the consumption rate of each input edge. These sequences associated with inputs and outputs of A all have the same length, and correspond to a single period of the interface (data transfer) behavior of A. The ith element of each sequence corresponds to a distinct phase of execution for A.

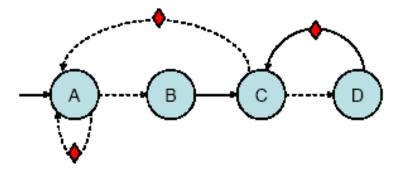

Figure 2.1 A simple SDF graph.

A simple example of a CSDF graph is presented in Figure 2.2. Each actor input/out-put is annotated with the associated sequence of production/consumption rates. For example, actor A has only one phase, and produces 3 tokens on edge (A, B) every time it executes. Actor B has two phases, and the amounts of tokens consumed and produced by successive invocations of B form the periodic patterns (1, 1, 1, 1, ...), and (1, 0, 1, 0, ...), respectively.

#### 2.1.3. Scheduling Concepts

In this section, we review some basic SDF- and CSDF-related scheduling concepts and notations that are used throughout the rest of the thesis.

Dataflow notation. Given an edge e in a dataflow graph, the source and sink actors of e are denoted by src(e) and snk(e), respectively. Given an SDF edge e, the number of tokens produced on e by each invocation of src(e) is denoted by p(e), and the number of tokens consumed from e by each invocation of snk(e) is denoted by c(e). Given a CSDF actor e, the number of phases associated with e is denoted by e0. Given a CSDF edge e, the number of tokens produced by e1 onto e2 in the e3 th phase of e3 is denoted by e4. Given a consumed by e5 is denoted by e6, in the e6 in the e7 in the e8 in the e9 is defined by e9. Clearly, e9 is defined for e9 in the e9 is defined for e9 in the e9 is defined for e9. Clearly, e9. Clearly, e9 is defined for e9 in the e9 is defined for e9. Clearly, e9.

Delays and buffer state. In dataflow models for signal processing, edges can have non-unity delays associated with them. One unit of delay is analogous to the  $z^{-1}$  operator

**Figure 2.2** A simple CSDF graph.

in signal processing, and can be implemented by placing an initial token on the associated edge. The *buffer state* of an SDF graph at a given point in time t is an integer-vector b that is indexed by the graph edges such that b(e) gives the number of tokens that reside on e at t. Since delays can be implemented as initial tokens, we define the initial buffer state of a graph to be b(e) = delay(e), where delay(e) denotes the delay on edge e.

Topology Matrix — The topology matrix (denoted by  $\Gamma$ ) is used to represent the dataflow characteristics of an SDF graph G [31]. The rows of  $\Gamma$  are indexed by the edges in G, and the columns are indexed by the actors in G. The entries of  $\Gamma$  are defined by

$$\Gamma(e,A) = \begin{cases} p(e); & \text{if } A = src(e) \\ -c(e); & \text{if } A = snk(e) \\ 0; & \text{otherwise} \end{cases}$$

(2.1)

For example, the topology matrix for the SDF graph in Figure 2.1 can be written as

$$\Gamma = \begin{bmatrix} 3 & -2 & 0 \\ 0 & 1 & -1 \end{bmatrix},\tag{2.2}$$

where the rows correspond to the edges (A, B) and (B, C), respectively, and the columns correspond to the actors A, B, and C, respectively.

The topology matrix for a CSDF graph is defined effectively by replacing p(e) and c(e) in (2.1) with the sums of P(e,i) and C(e,i), respectively, across all relevant phases. More precisely, the entries of the topology matrix  $\Gamma_{CSDF}$  for a CSDF graph can be expressed as

$$\Gamma_{CSDF}(e, A) = \begin{pmatrix} \phi(A) \\ \sum_{i=1}^{n} P(e, i) \end{pmatrix} if A = src(e)$$

$$-\begin{pmatrix} \phi(A) \\ \sum_{i=1}^{n} C(e, i) \end{pmatrix} if A = snk(e)$$

$$0 \text{ otherwise}$$

$$(2.3)$$

Hence, the topology matrix for the CSDF graph in Figure 2.2 is the same as the topology matrix for the SDF graph in Figure 2.1.

Repetitions vector and valid schedules — The repetitions vector (usually denoted by q) for an SDF graph is a vector of co-prime positive integers that denotes the number of times that each actor in the graph is executed in a minimal valid schedule for the graph. A valid schedule S in turn is a finite sequence of actor invocations that fires each actor atleast once, does not deadlock (i.e., does not attempt to consume data from an empty buffer), and produces no net change in the buffer state of the graph (i.e., execution of S returns the graph to its initial buffer state). The repetitions vector, when it exists, can be determined by solving for the  $n_a \times I$  column vector x in the system of balance equations defined by

$$\Gamma x = 0. (2.4)$$

In particular, the repetitions vector is defined to be the minimum positive integer solution to (2.4). It can be shown that such a unique minimum positive integer solution exists whenever (2.4) has a nontrivial solution [31].

For example, the repetitions vector for the SDF graph in Figure 2.1 is given by q(A) = 2, and q(B) = q(C) = 3.

An example of a valid schedule for this graph is given by (BABABCCC).

The main practical significance of a valid schedule is that it can be iterated indefinitely to achieve unbounded-duration execution of the given graph with bounded buffer memory requirements.

For CSDF graph, the concept of a valid schedule is the same as that for an SDF graph; however, the process of computing the numbers of actor invocations involved in a valid schedule is slightly more involved. The system of balance equations for a CSDF graph is given by

$$\Gamma_{CSDF} x = 0, (2.5)$$

where x again represents an  $n_a \times 1$  column vector.

A solution to the CSDF balance equations, when it exists, gives the number of "actor periods" for each actor that is involved in an iteration of a valid schedule. Here, an actor period for actor A corresponds to execution of  $\phi(A)$  successive invocations (phases) of A. The CSDF repetitions vector — which gives the number of actor invocations for each actor in a valid schedule — is thus obtained from

$$q_{CSDF}(A) = \tau(A)\phi(A) \text{ for all } A,$$

(2.6)

where  $\tau$  is the minimum positive integer solution to (2.5).

For example, for the CSDF graph in Figure 2.2, we have  $\tau(A) = 2$ ,  $\tau(B) = \tau(C) = 3$ ,  $q_{CSDF}(A) = 2$ ,  $q_{CSDF}(B) = 6$ , and  $q_{CSDF}(C) = 3$ . Furthermore, the schedule (BBABBABBCCC) is a valid schedule for this CSDF graph.

Consistent graph — An SDF graph or CSDF graph is said to be consistent if it has a valid schedule. Intuitively, consistency in this context means that the balance equations ((2.4) or (2.5)) have a nontrivial solution, and all directed cycles in the graph have enough delays (initial tokens) to allow for deadlock-free execution [31].

The graphs in Figure 2.1 and Figure 2.2 are both consistent.

#### 2.1.4. Parameterized Dataflow

Parameterized dataflow [3] is a meta-modeling technique that can be used in conjunction with any dataflow model of computation that has a well-defined notion of a graph *iteration*. For example, in SDF and CSDF graphs, a graph iteration usually corresponds to execution of a valid schedule. When parameterized dataflow is applied to a dataflow model of computation D, the model D is called the *base* model, and the resulting integrated model can be viewed as a dynamically reconfigurable augmentation of D. Thus, parameterized dataflow provides for increased expressive power by allowing for run-time reconfigurability of actor and edge parameters in a certain structured way.

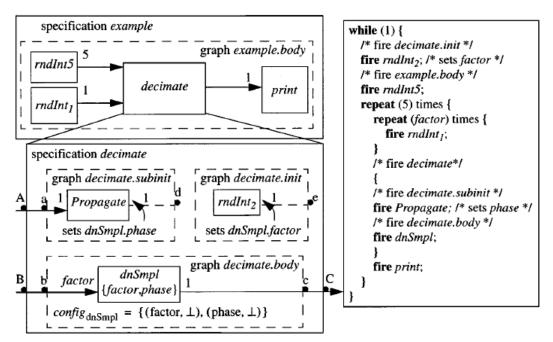

When parameterized dataflow is applied to SDF as the base model, the resulting model of computation is called parameterized synchronous dataflow (*PSDF*). An actor *A* in PSDF is characterized by a set of parameters (*params*(*A*)) that control the actor's functionality, including possibly its dataflow behavior. Each parameter is either assigned a value from a set of permissible values or left unspecified. These unspecified parameters are assigned values at run-time through a disciplined run-time reconfiguration mechanism. Techniques have been developed to execute PSDF graphs efficiently through carefully constructed quasi-static schedules [3].

Parameterized dataflow specifications are built up in a modular way in terms of hierarchical subsystems. Every subsystem is in general composed of three subgraphs, called the *init*, *subinit* and *body* graphs. New parameter values used during run-time reconfiguration are generally computed in the init and subinit graphs, and the values are propagated to the body graph, which represents the computational core of the associated

parameterized dataflow subsystem. The init graph for a subsystem H is invoked at the beginning of each invocation of the (hierarchical) parent graph of H. In contrast, the subinit graph is invoked at the beginning of each invocation of H itself, prior to execution of the body graph. Intuitively, reconfiguration of a body graph by the corresponding init graph occurs less frequently but is more flexible compared to reconfiguration by the subinit graph [3].

#### 2.1.5. Generic Model for Hierarchical Reconfiguration of Dataflow Graphs

Parameterization is a widely-used method to implement dynamic behavior of a dataflow graph. But a parameterized actor might also have a predetermined production and consumption rate. For example, an FIR filter might have its number of taps as a parameter, which does not affect the production consumption rate. In this thesis, we discuss parameters in the context of actors whose token production and consumption rates are a function

**Figure 2.3** PSDF specification of a decimate actor that decimates by a different factor at each run (figure from [3]).

of these parameters. In [38], the authors develop a mathematical model to represent the reconfiguration of various types of dynamic dataflow graphs. The model allows reconfiguration at all levels of hierarchy. A hierarchical reconfiguration model is represented by a *containment tree*, which has a finite set of actors in it. Non-leaf nodes are composite actors and leaf elements are atomic actors. The behavior of a composite actor is given by the actors that are its direct children. Every actor has its own set of parameters which define its behavior and there is a one-to-one relation between the parameters and actors. Dependencies among parameters are expressed explicitly through a domain function and its value is constrained by a *constraint function*. A dependent parameter must at all times satisfy the constraint function to become *consistent*. An independent parameter has null in its domain function.

The authors introduce specific points in their model called *quiescent points*, which are constrained points in the execution model where change of parameter values are permitted. These points occur between firings and an actor cannot communicate or perform computation at these points. A *precedence relation* is set that performs partial ordering of quiescent points of all the actors. At each quiescent point, a set of independent parameters Q is chosen for reconfiguration and all the parameters dependent on Q are also reconfigured based on their initial and reconfigured values. Parameters that cannot be reconfigured or can be changed only at certain quiescent points are declared as *constant parameters*. A constant parameter can be forced to remain constant either during one particular execution of the model or over firings of the associated actor. To statically analyze the reconfiguration of a model, two methodologies have been suggested. Firstly, all the executions of the model are checked along with all possible reconfigurations and any invalid reconfigura-

tion predicts invalidity of the model. Secondly, the authors suggest a least change context for every parameter p which is a conservative estimate of the actors affected by p. This helps in easy semantic constraint checking.

#### 2.2. Related Work

#### 2.2.1. Hardware from Formal Models

A number of studies have been undertaken in recent years on the design and implementation of multimedia applications on FPGAs using other formal or systematic approaches.

Streams-C [19] developed at the Los Alamos National Laboratory, USA provides compiler technology that maps high-level, *parallel C* language descriptions into circuit-level netlists targeted to FPGAs. To use Streams-C effectively, the programmer needs to have some application-specific hardware mapping expertise as well as expertise in parallel programming under the CSP (communicating sequential processes) model of computation [22]. Streams-C consists of a small number of libraries and intrinsic functions added to a subset of C that the user must use to derive synthesizable HDL code.

Handel-C [11] developed at the Oxford University, UK represents another important effort towards developing a hardware oriented C language. Handel-C is based on a subset of the ANSI C standard along with extensions that support a synchronous parallel mode of operation. It supports specification of width of variables, and consequently has strong bit manipulation capabilities. This language also conforms to the CSP model. A canny edge detector was designed in hardware in [37] using the Celoxica DK2 IDE tool — which is the development tool for Handel-C.

Match [1] or AccelFPGA as it is called now, generates VHDL or Verilog from an algorithm coded in MATLAB, a programming language that is widely used for prototyping image and video processing algorithms. AccelFPGA has various compiler directives that the designer can use to explore the design space for optimized hardware implementation. Loop unrolling, pipelining, and user-defined memory mapping are examples of implementation aspects that can be coordinated through AccelFPGA directives.

Compaan [28] is a another design tool for translating MATLAB programs into HDL for FPGA implementation. Compaan performs its translation through an intermediate representation that is based on the Kahn process network model of computation [27]. Compaan can either generate an embedded software code to run on the softcores (for example PowerPC on Virtex II Pro) or it can generate output in the form of executable Kahn Process Networks for another tool named Laura [56]. Laura accepts this specification and transforms the specification into design implementations described in synthesizable VHDL.

Rather than adapting a sequential programming language for hardware design, as the above-mentioned approaches do, our approach is based on concurrency exposed by the designer in representing the algorithm as a dataflow model. This is a useful approach for signal processing because the structure of signal processing applications in terms of its coarse-grain components (e.g., FIR filters, IIR filters, and FFT computations) often translates intuitively into concurrent specifications based on dataflow principles.

#### 2.2.2. Hardware from SDF

A SDF based digital hardware design for embedded signal processing was addressed in [54]. Two techniques were presented for architecture generation — one is a

general resource sharing technique for flexibility, and the other is a mapping of sequenced groups for compact communication and interconnect. The problem addressed was to find the minimum-cost hardware to meet the deadline for the time to execute all firings in the SDF dataflow (for this work, a firing precedence graph was constructed from the schedule of the SDF on which the hardware mapping was done). After the schedule of the SDF was generated, each individual firing (execution) of a node j in the graph was associated with a hardware cost  $C_i$  and execution time  $T_i$  which were estimates from the RTL (register transfer level) synthesis results of any standard synthesizer. Hence the goal was to minimize  $\sum C_i$  for the schedule when  $\sum T_i < T_{deadline}$ . The two heuristics mentioned in the work, approach the same problem from the two opposite directions. In one approach, the authors start with maximum hardware — which is a separate hardware unit for every firing in the firing precedence graph and then try to cluster firings into shared hardware units until no more clustering can be done without violating the deadline. Clustering (which means shared resource allocation) was done based on the following criteria — two actors having the same firing (identical computation of the same SDF actor without any constraints on sequential firings) can be merged to execute on the same hardware; two actors having similar firings (similar computations, so that much of the execution unit can be the same hardware and no constraints on sequential firing) can be merged; actors differing only by a parameter can be merged too. If the inputs of the merged actors are from different actors, then a multiplexer is needed and controller logic needs to be added for correct execution. In the other approach, the whole graph is mapped onto a single hardware unit, which is capable of performing all the required functionalities — this would result in lowest area implementation as the standard hardware synthesizers are able to optimize the circuit the best. However, this would act like a uniprocessor with every node firing sequentially, thus not taking advantage of any parallelism that might be present in the application. However, there are various design point in between the two extreme implementations that can be explored using clustering or declustering techniques.

Our approach is different from the approach in [54], in respect that due to inherent simplicity of HPDF, we try to explore the architecture from the dataflow graph instead of the firing precedence graph and our approach can handle limited dynamicity in the application which the SDF based approach cannot. Also the clustering techniques are orthogonal to our approach and hence can be used to enhance our method of hardware development.

# 2.2.3. Image Processing in Hardware

Computer vision algorithms can be divided into three categories depending on the level of granularity at which they are specified — low level, intermediate level and high level algorithms. In the late 1980s and early 90s, a lot of work was done on image processing on hardware. Some of it was on homogeneous/heterogeneous architectures specially suited for image processing, and some of it was on specialized algorithms suited for hardware implementations. The general observation was that single instruction multiple data (SIMD) machines were good for exploiting fine-grained parallelism and multiple instruction multiple data (MIMD) machines were suitable for coarse-grained parallelism. In this section, we mention a few instances of the work done in the hardware architecture for computer vision domain. A more detailed description of all the architectures and some others not mentioned here can be found in [16], [40].

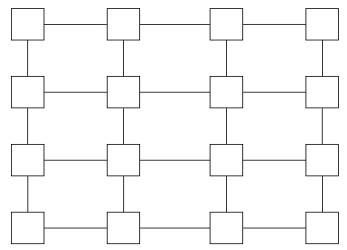

# 2.2.3.1. MESH Architecture

MESH is a SIMD 2D array architecture (array of processors) for computer vision. This architecture is suited to perform low and intermediate level vision algorithms. One major problem with such a major system is fault in final architecture due to fabrication variabilities. MESH has a fault-tolerant strategy to enhance yield and improve reliability. MESH has a hardware reconfiguration strategy to eliminate defective processors in combination with data reconfiguration to redistribute the problem over the working processors. We give an example of a *16* processing element MESH architecture in Figure 2.4.

# 2.2.3.2. Hypercube Architecture

A hypercube also describes a SIMD connection. It differs from a MESH connection in the way connections are made between different processing elements (PEs). A p-dimensional hypercube network connects  $2^p$  processing elements. A hypercube network connects pairs of processing elements whose indices differ in exactly one bit when expressed in the binary representation. We represent the hypercube network in Figure 2.5.

**Figure 2.4** A 16 processing element (PE) MESH architecture where end-around connections are not shown.

#### 2.2.3.3. NETRA

NETRA is a highly configureable architecture for image understanding. The topology of NETRA is recursive and hence easily scalable. It has a tree-type hierarchical architecture with leaf nodes consisting of small but powerful processor clusters connected by crossbar switches — the tree has distributing and scheduling processors that perform the task distribution. Each processor cluster has 16 to 64 processing elements with both shared and distributed memory. Each of the clusters can operate in SIMD mode, MIMD mode or systolic mode, and each processing element is a general purpose processor with high-speed floating point capabilities.

#### **2.2.3.4.** IUA (Image Understanding Architecture)

IUA is a 3-tier architecture with a dedicated architecture for each level of abstraction (low level, intermediate level and high level vision algorithms). Main processor languages were added with extensions to provide several levels of parallelism, each requiring a unique level of overhead.

**Figure 2.5** *16* processor hypercube architecture.

#### 2.2.3.5. Warp

Warp was a medium grain systolic array machine built at Carnegie Melon University (CMU). There are a few versions of this machine — WWWarp consists of a linear array of 10 cells, each giving 10 MFLOPS with a total of 100 MFLOPS; PCWarp is an extension to WWWarp with capabilities of 160 MFLOPS and with larger cell data and program memory; iWarp (integrated Warp) which was a joint venture between CMU and Intel had capabilities of 16 MFLOPS per cell as a result of faster clock with a linear array of 72 cells, giving a total 1.152 GFLOPS.

# Chapter 3. Homogeneous Parameterized Dataflow Graph (HPDF)

Real-time multimedia applications are an integral part of embedded systems technology. Modeling such applications using dataflow graphs can lead to useful formal properties, such as bounded memory requirements, and efficient synthesis solutions (e.g, see [4]). The synchronous dataflow (SDF) model for example has particularly strong compile time predictability properties [31]. However, this model is highly restrictive and cannot handle data-dependent execution of dataflow graph vertices (actors). There have been previous studies on extensions of SDF to provide for more flexible actor execution, including handling of such dynamic execution capabilities. For example, a cyclo-static dataflow (CSDF) [6] graph can accommodate multiphase actors with different consumption and production rates at the input and output, respectively, at different phases of iteration. This provides for more flexibility but does not permit data dependent production or consumption patterns. Another extension known as the token flow model [7] was proposed in which we can have dynamic actors where the number of data values (tokens) transferred across a graph edge may depend on the run-time value of a token that is received at a "control port" of an incident actor. A meta-modeling technique called parameterized dataflow [3] (PSDF) was proposed later in which dynamic dataflow capability was formulated in terms of run-time reconfiguration of actor and edge parameters. In this chapter, we present another model HPDF which can model certain restricted forms of dynamic dataflow very effectively and is more constrained compared to PSDF.

#### 3.1. Model Definition

In this section, we first provide a more constrained definition of HPDF that was presented at some of our initial work. We present the characteristics of the actors, edges, and delay buffers in an HPDF graph.

An HPDF subsystem is homogeneous in two ways. First, unlike general SDF graphs and other multirate models, the top level actors in an HPDF subsystem execute at the same rate. Second, unlike the hierarchically-oriented parameterized dataflow semantics, reconfiguration across subsystems can be achieved without introducing hierarchy (i.e., reconfiguration across actors that are at the same level of the modeling hierarchy). Some dynamic applications are naturally non-hierarchical, and this kind of behavior can be modeled using HPDF without imposing "artificial" hierarchical structures that a parameterized dataflow representation would entail. At the same time, hierarchy can be used within the HPDF framework when it is desired.

HPDF is a meta modeling technique. Composite actors in an HPDF model can be refined using any dataflow modeling semantics that provide a well-defined notion of subsystem iteration. For example, the composite HPDF actor might have SDF, CSDF, PSDF or multi-dimensional SDF [32] actors as its constituent actors.

As with other many other dataflow models, such as SDF and CSDF, an HPDF edge e can have a non-negative integer delay  $\delta(e)$  on it. This delay gives the number of initial data samples (tokens) on the edge. The stream of tokens that is passed across an edge needs markers of some kind to indicate the "packets" that correspond to each iteration of the producing and consuming actors. An end-of-packet marker is used for this purpose in our implementation.

Interface actors in HPDF can produce and consume arbitrary amounts of data, while the internal connections must, for fixed parameter values, obey the constraints imposed by the base model. An HPDF source actor in general has access to a variable number of tokens at its inputs, but it obeys the semantics of the associated base model on its output. Similarly, an HPDF sink actor obeys the semantics of its base model at the input but can produce a variable number of tokens on its output. HPDF source and sink actors can be used at subsystem interfaces to connect hierarchically to other forms of dataflow.

#### 3.2. An Extended Model Definition

In this section, we present, a generalized form of our proposed homogeneous parameterized dataflow (HPDF) model of computation [44][46][20], which is an extension to the definition presented in Section 3.1. and we build on SDF scheduling fundamentals to present, a precise formalization static scheduling concepts for HPDF.

Like parameterized dataflow, HPDF is a meta-modeling technique that can be applied to different dataflow models, including SDF and CSDF. In our generalized form of HPDF, we restrict the homogeneity constraint so that it is required only for edges whose production or consumption rates involve parameter values that can vary dynamically (e.g., parameterized scalar rates in the case of HPDF-SDF or parameterized vector-rates in the case of HPDF-CSDF).

Henceforth in this thesis, by *HPDF* we mean the generalized form of HPDF that we develop in this section, as opposed to the original, more restricted, form introduced in Section 3.1. [44][46].

#### 3.2.1. Definition of HPDF

An HPDF subsystem is homogeneous in the sense that parameterized edges (in particular, edges that are associated with dynamically variable parameter values) have identical rates of production and consumption for any given iteration of the underlying base model. Thus, the production rate associated with any given edge can change from one base model iteration to the next provided the consumption rate of that edge changes in exactly the same way.

For example, let e be an edge in an HPDF-SDF graph G — that is, a dataflow graph in which HPDF is applied to SDF as the base model. Furthermore, in a given execution of the G, let  $p_{HPDF}(e,i)$  denote the (constant) production rate associated with e during the ith iteration of G, and similarly, let  $c_{HPDF}(e,i)$  denote the consumption rate associated with e during the i iteration of G. Then the HPDF meta-model imposes the restriction that either 1)  $p_{HPDF}(e,i)$  and  $c_{HPDF}(e,i)$  remain constant for all i (although the constant value for  $p_{HPDF}(e,i)$  may differ from the constant value for  $c_{HPDF}(e,i)$ , or 2)  $p_{HPDF}(e,i) = c_{HPDF}(e,i)$  for all i. Here, condition 1 simply means that  $p_{HPDF}(e,i)$  and  $c_{HPDF}(e,i)$  are both independent of i. An edge that satisfies condition 2 but does not satisfy condition 1 is called a  $dynamic\ edge$  of the enclosing HPDF graph.

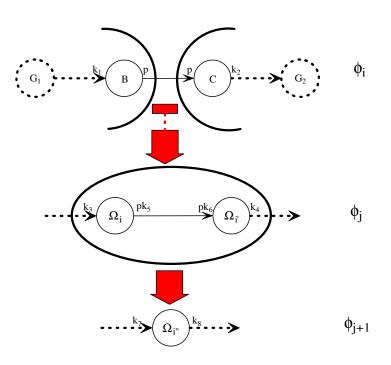

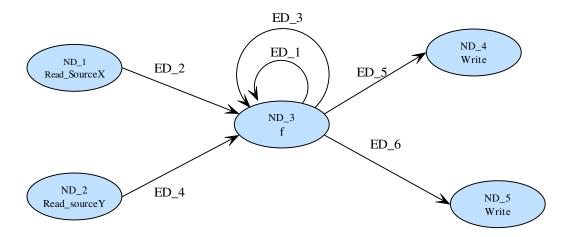

An example of an HPDF graph is shown in Figure 3.1. Here, the base model is SDF, and p is a symbolic placeholder for a parameter value that is not statically known and that

Figure 3.1 An example of an HPDF graph.

can vary dynamically from one base model iteration to the next. Thus,  $p_{HPDF}((A,B),i)=3$  for all i;  $c_{HPDF}((A,B),i)=2$  for all i; and

$$p_{HPDF}(e, i) = c_{HPDF}(e, i) = p_i \text{ for all } i,$$

where  $p_i$  represents the value of the parameterized expression p throughout the ith base model iteration and e represents the edge between B and C.

Interface actors in HPDF can produce and consume arbitrary amounts of data from interface edges — the constraints imposed by the HPDF meta-model in conjunction with the given base model need only be satisfied for the internal connections of an HPDF graph. Here, by an *interface actor* of an HPDF graph G, we mean an actor that is connected to one or more components that are outside of G, and by an *interface edge*, we mean an input or output edge of an interface actor that provides such an external connection. An HPDF source actor is an interface actor that has one or more input edges that are interface edges, but conforms to HPDF semantics on its output edges. Similarly, an HPDF sink actor conforms to HPDF on its input edges, and has one or more output edges that are interface outputs.

#### 3.2.2. HPDF with CSDF as the Base Model

We now demonstrate the integration of CSDF base model semantics into the HPDF meta-modeling framework. This integration provides simultaneous application of the bounded memory, dynamic parameterization of HPDF and the finer granularity, phased decomposition of actor execution in CSDF.

As mentioned in Section 3.2.1., the homogeneity requirement in HPDF is in the sense that data transfer across a parameterized edge (production and consumption) must be equal (but not necessarily constant or statically-known) across corresponding invoca-

tions of the source and sink actors. In CSDF, a complete invocation of an actor involves execution of all of the phases in a fundamental period of the actor [6]. Integration of CSDF with HPDF allows the number of phases in a fundamental period to vary dynamically, and also allows the number of tokens produced or consumed in a given phase to vary dynamically. Such dynamic variation must adhere to the general HPDF constraint, however, that the total number of tokens produced by a source actor of a given parameterized edge in a given invocation (which, in the case of phased actors, means a given fundamental period) must equal the total number of tokens consumed by the sink in its corresponding invocation. Thus, for all positive n, the number of tokens produced by the nth complete invocation of a source actor must equal the number of tokens consumed by the nth complete invocation of the associated sink actor when they are connected by a parameterized edge.

For fundamental periods that involve dynamic token transfer, this can be accommodated by employing a special token that delimits the end of a fundamental period of a source actor. The source actor produces this special end-of-invocation (*EOI*) delimiter just after the end of each complete invocation. The HPDF restriction then requires the following.

Suppose that the sink actor of a dynamically parameterized HPDF edge e consumes the last token in its ith invocation (fundamental period of phases) at time  $z_i(t)$ . Then just after completing  $\delta(e)$  more consumption operations after time  $z_i(t)$ , the sink actor will consume an EOI token, and it will not consume any EOI tokens before that. This pattern must hold for all positive integers i (i.e., all invocation indices); that is, after each complete sink invocation, the next EOI token is consumed after exactly  $\delta(e)$  consumption

operations. Furthermore no EOI token should be consumed during the first invocation (i = 1) of the sink actor.

The above formulation is useful for precisely specifying how HPDF applies to dynamic parameterization of CSDF actors. The formulation can also be used to generate code for quasi-static schedules, and to verify consistency of HPDF specifications at runtime (i.e., to detect violations of HPDF behavior as soon as they occur).

## 3.3. Comparison of HPDF and PSDF

While HPDF employs parameterized actors and subsystems like PSDF, there are several distinguishing features of HPDF in relation to PSDF. For example, unlike PSDF, HPDF always executes in bounded memory whenever the component models execute in bounded memory. In contrast, some PSDF systems do not execute in bounded memory, and in general, a combination of static and run-time checks is need to ensure bounded memory operation for PSDF [5].

Also, as described in Section 3.2.1, we do not have to introduce hierarchy in HPDF to account for dynamic behavior of actors. For example, suppose that a dynamic source actor A produces n tokens that are consumed by the dynamic sink actor B. In PSDF, we need to have A and B in different subsystems; the body of A would set the parameter n, which will be a known quantity at that time, in the subinit of B (see Section 5.2.1 for a more detailed example). This hierarchy can be avoided in HPDF as we assume that data is produced and consumed in same-sized blocks. As we will describe further in Chapter 5, this simple form of dynamicity has many applications in image processing algorithms. It therefore deserves explicit, efficient support as provided by HPDF.

Also, unlike parameterized dataflow, the stream of tokens that is passed across a dynamic HPDF edge requires markers of some kind to delimit the "packets" that correspond to successive invocations of the producing/consuming actors. An end-of-packet marker is used for this purpose in our implementation.

In summary, compared to PSDF, HPDF provides for simpler (non-hierarchical) parameter reconfiguration, and for more powerful static analysis. In exchange for these features, HPDF is significantly more narrow in the scope of applications that it is suitable for. Intuitively, a parameterized multirate application cannot be modeled using HPDF. However, as we motivate in this thesis, HPDF is suitable for an important class of computer vision applications, and therefore it is a useful modeling approach to consider when developing embedded hardware and software for computer visions systems.

# 3.4. Scheduling of HPDF Graphs

# **3.4.1.** Repetitions Vectors and Valid Schedules

When HPDF is applied to SDF or CSDF, the *topology matrix*  $\Gamma_{HPDF}$  for an HPDF graph can be defined in manner analogous to the definition of the topology matrix for its base model, with symbolic placeholders used to represent production rate values and consumption rate values that are not statically known. For HPDF-SDF, such a symbolic placeholder represents an unknown scalar value. For HPDF-CSDF, such a placeholder corresponds to symmetric production/consumption-rate tuples that are equal, but in general have variable lengths (numbers of phases), and variable values across CSDF iterations.

For example, the topology matrix for the HPDF graph in Figure 3.1 can be written as

$$\Gamma_{HPDF} = \begin{bmatrix} 3 & -2 & 0 \\ 0 & p & -p \end{bmatrix}.$$

Valid schedules and repetitions vectors can be defined for HPDF graphs in a manner similar to the corresponding concepts that are reviewed in Section 2.1.3. The *repetitions* vector denoted by  $q_{HPDF}$ , for an HPDF graph is a vector of co-prime integers that denotes the numbers of times the actors in the HPDF graph should be executed in a minimal base model iteration so that there is no resultant change in buffer state. For example, the repetitions vector for the HPDF graph in Figure 3.1 can be expressed as

$$q_{HPDF}(A) = 2$$

,  $q_{HPDF}(B) = q_{HPDF}(C) = 3$ .

As in Chapter 2, we can derive a valid schedule from the repetitions vector for an HPDF graph. A valid schedule for Figure 3.1 is given by (*BABABCCC*).

In Sections 3.4.2 and 3.4.3, we apply HPDF with SDF as the base model and show how existing methods for static scheduling that are based on SDF can be extended systematically to HPDF.

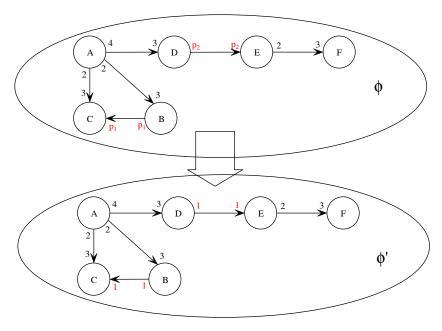

# **3.4.2.** SDF Reductions of HPDF Graphs

Based on the concept of symbolic placeholders described in Sections 3.2.1 and 3.4.1, an HPDF graph contains a set of dynamic-parameter edges  $e_1, e_2, ..., e_n$  such that the for each  $e_i$ , the production and consumption rate values of  $e_i$  are equal in any given base model iteration, and this common value of dynamically-varying production/consumption rate is represented by a symbolic placeholder  $p_i$ .

Given an HPDF-SDF graph G, the SDF reduction of G is an SDF graph G' that is derived by replacing each  $p_i$  associated with G by the constant production and consumption rate value of I for the associated edge. That is,

$$p(e_i) = c(e_i) = 1$$

for  $i = 1, 2, ..., n$ .

For example, the SDF reduction of the HPDF graph of Figure 3.1 is the SDF graph in Figure 2.1.

SDF reductions are useful because important scheduling-related operations on HPDF-SDF graphs can be reduced to scheduling operations on the corresponding SDF reductions.

For example, the repetitions vector for HPDF-SDF graphs is well defined and has a similar interpretations as with SDF graphs — each element of the HPDF-SDF repetitions vector gives the number of times to execute the corresponding actor in a minimal valid schedule. Given an HPDF-SDF graph G, its repetitions vector can be derived simply by

**Figure 3.2** Converting  $\phi$  to its SDF reduction  $\phi'$  by replacing parameters  $p_1$  and  $p_2$  with the value I.