**ABSTRACT**

Title of Thesis: TESTING AND CHARACTERIZATION OF

SILICON DEVICES AT CRYOGENIC

**TEMPERATURES**

Jeffrey Foster Allnutt Master of Science, 2007

Directed By: Professor Martin Peckerar

Department of Electrical Engineering

Satellite and space exploration applications require electronics which are capable of operation at extremely low temperatures (T<40K). Low temperature device models are essential for the design of circuits operating in these extreme environments. To address these needs, a helium Dewar test setup has been constructed and used to

evaluate several MOSFET devices, a bipolar device, and a tunneling structure. The

temperature dependent performance of each has been characterized down to 20K and,

in some cases, as low as 4K. Complete voltage and temperature dependent MOSFET

characteristics have led to the development of a simulator which predicts device

performance at cryogenic temperatures. A tunneling structure has demonstrated

comparable low temperature voltage reference performance to that of a silicon

germanium voltage reference circuit.

# TESTING AND CHARACTERIZATION OF SILICON DEVICES AT CRYOGENIC TEMPERATURES

By

Jeffrey Foster Allnutt

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science 2007

Advisory Committee: Professor Martin Peckerar, Chair Professor Neil Goldsman Assistant Professor Pamela Abshire © Copyright by Jeffrey Foster Allnutt 2007

## Acknowledgements

First, I would like to that my advisor, Dr. Martin Peckerar, for his continued guidance and support throughout my undergraduate and graduate education. Dr. Peckerar made my graduate education a reality and it has been a pleasure both working for him and having him as a personal friend.

I would also extend special thanks to the members of my committee, Dr. Neil Goldsman and Dr. Pamela Abshire, as both have assisted greatly in my education and research endeavors.

I would like to thank Akin Akturk for sharing much of his device knowledge with me and for his excellent modeling work in conjunction with my research. I would also like to thank Zenyep Dilli for providing me with several devices as well as a ring oscillator circuit. Thanks to Nicole Nelson and Marc Dandin for their help obtaining and using test equipment. I would like to thank Jimmy Wienke for taking this plunge with me and supporting me throughout, and thanks to all my lab-mates who have been there to answer questions and discuss ideas.

I would like to thank Shahid Aslam, Mike Johnson, Umesh Patel, and other members of the NASA Goddard Space flight center who have supported this research.

Finally, I would like to thank my family and friends. I am grateful to my parents for instilling in me the value of education and putting me in a position to succeed. I would also like to thank my friends who kept the local establishments busy without me, and Cameron for his vicarious support.

## **Table of Contents**

| Acknowledgements                             |     |

|----------------------------------------------|-----|

| Table of Contents                            | iii |

| List of Figures                              | v   |

| CHAPTER 1: Introduction                      | 1   |

| 1.1 Background                               |     |

| 1.1.1 Semiconductor Device Physics           | 3   |

| 1.1.2 Low Temperature Phenomena              | 5   |

| 1.1.3 Low Temperature Testing Considerations | 9   |

| 1.2 Research Objectives                      |     |

| 1.2.1 Research Goals                         | 14  |

| 1.2.2 Scope of Research                      |     |

| CHAPTER 2: Test Setup                        |     |

| 2.1 Cryogenic Test Dewar                     |     |

| 2.1.1 Dewar Design                           |     |

| 2.1.2 Internal Board Design                  |     |

| 2.1.3 Thermal Considerations                 |     |

| 2.2 Cooling Procedure                        |     |

| 2.2.1 High-Vacuum Pump                       |     |

| 2.2.2 Liquid Nitrogen Transfer               |     |

| 2.2.3 Liquid Helium Transfer                 |     |

| CHAPTER 3: Transistor Characterization       |     |

| 3.1 MOSFET Characterization                  |     |

| 3.1.1 Low Temperature Functionality          | 31  |

| 3.1.2 Low Temperature I-V Characteristics    |     |

| 3.2 BJT Characterization                     |     |

| 3.2.1 Motivation and Test Procedure          | 48  |

| 3.2.2 BJT Test Results                       | 49  |

| 3.3 MOSFET NOISE Analysis                    | 51  |

| 3.3.1 Motivation                             |     |

| 3.3.2 Test Setup and Measurement Process     | 52  |

| 3.3.3 Results                                |     |

| CHAPTER 4: Cryogenic Integrated Circuits     | 58  |

| 4.1 Zener Diode Voltage Reference            | 58  |

| 4.1.1 Operation                              | 58  |

| 4.1.2 Test Setup.                            |     |

| 4.1.3 Results                                |     |

| 4.2 Ring Oscillator                          | 67  |

| 4.2.1 Operation                              |     |

| 4.2.2 Test Setup.                            |     |

| 4.2.3 Results                                |     |

| CHAPTER 5: Conclusions and Future Work       |     |

| 5.1 Contributions                            | 72  |

| 5.1.1 MOSFET Low Temperature Functionality        | 73 |

|---------------------------------------------------|----|

| 5.1.2 MOSFET I-V Characteristics                  |    |

| 5.1.3 Zener Diode Voltage Reference               | 75 |

| 5.1.4 Cryogenic Testing Guide                     | 76 |

| 5.2 Recommendations for Future Work               | 76 |

| 5.2.1 Full Process Characterization               | 76 |

| 5.2.2 Silicon MOSFET Voltage Reference            | 77 |

| Appendix A: MOSFET Modeling and Simulation        |    |

| A.1 Modeling                                      | 78 |

| A.1.1 Semiconductor Device Equations              |    |

| A.1.2 Incomplete Ionization and Mobility Modeling |    |

| A.2 Simulation                                    |    |

| A.2.1 Current versus Temperature                  | 86 |

| A.2.2 I-V Characteristic Simulation               |    |

| References                                        |    |

## **List of Figures**

| Figure 1: Energy Band Diagram of Silicon                                                        | 3  |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2: Lattice Structure of (a) Intrinsic and (b) n-type Silicon                             | 7  |

| Figure 3: Storage Dewars: (a) Thermos beverage container and (b) Liquid helium                  |    |

| Dewar                                                                                           | 10 |

| Figure 4: Infrared Laboratories test Dewar cross section [38]                                   | 11 |

|                                                                                                 | 19 |

|                                                                                                 | 20 |

| Figure 7: Inside of test Dewar with proper wire heat-sinking to minimize heat                   |    |

| injection                                                                                       | 24 |

| Figure 8: Alcatel pump and controller (left) and Balzers pressure gauge (right)                 | 25 |

|                                                                                                 | 26 |

| Figure 10: (a) LN <sub>2</sub> storage Dewar with fill tube and (b) Top view of test Dewar      | 27 |

| Figure 11: Helium transfer from storage Dewar to test Dewar                                     |    |

| Figure 12: Keithley 2700 (top) and Lakeshore 340 (bottom)                                       |    |

| Figure 13: Schematic of MOSFET functionality test setup                                         |    |

| Figure 14: Saturation Current versus Temperature (Device A)                                     |    |

| Figure 15: Hewlett Packard 4156B Semiconductor Parameter Analyzer                               |    |

| Figure 16: Hewlett Packard 16058 Personality Board                                              |    |

| Figure 17: Schematic of MOSFET I-V characteristic test setup                                    |    |

| Figure 18: I <sub>D</sub> versus V <sub>DS</sub> family of curves at 37K (Device B)             |    |

| Figure 19: I <sub>D</sub> versus V <sub>DS</sub> family of curves at 293K (Device B)            |    |

| Figure 20: $I_D$ versus $V_{DS}$ Curves for Several Temperatures at $V_G = 5V$ (Device B)       |    |

| Figure 21: I <sub>D</sub> versus T Curves for linear and saturation regions (Device B). Current |    |

| normalized to 1 at room temperature to show rate of increase.                                   |    |

| Figure 22: $I_D$ versus $V_{DS}$ curves for several temperatures at $V_G = 3V$ (Device C)       |    |

| Figure 23: I <sub>D</sub> versus T curves for linear and saturation Regions (Device C). Current |    |

|                                                                                                 | 44 |

| Figure 24: Decrease in current after device saturation (Current Dip) as a function of           |    |

|                                                                                                 | 45 |

| Figure 25: Saturation I <sub>D</sub> versus T curves for several MOSFET devices. Current is     |    |

| normalized to 1 at T=120K to emphasize the rate of change at higher and lower                   |    |

| temperatures.                                                                                   | 47 |

| Figure 26: $I_C$ versus $V_{CE}$ Curves for several temperatures at $I_B = 50\mu A$ (BJT)       |    |

| Figure 27: I <sub>C</sub> versus T in the forward active region of operation (BJT)              |    |

| Figure 28: HP4396B Spectrum Analyzer                                                            |    |

| Figure 29: Stanford Research Systems SR570 Low-Noise Current Preamplifier                       | 53 |

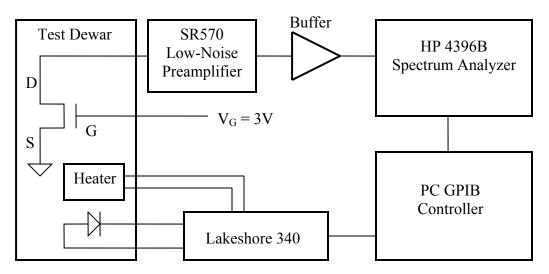

| Figure 30: Schematic of MOSFET noise test setup                                                 |    |

| Figure 31: Resistive heater mounted on test board (bottom-middle)                               |    |

| Figure 32: MOSFET Noise versus Frequency at room temperature and 20K                            |    |

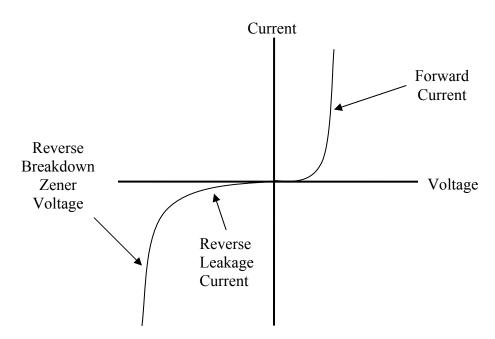

| Figure 33: Zener diode I-V characteristic                                                       |    |

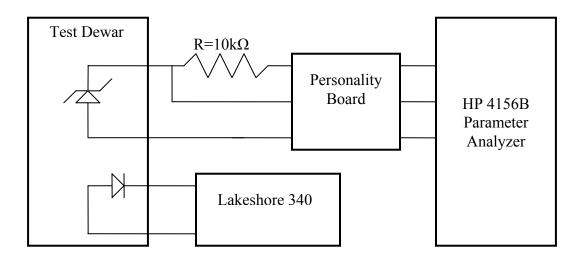

| Figure 34: Zener diode voltage reference test setup                                             |    |

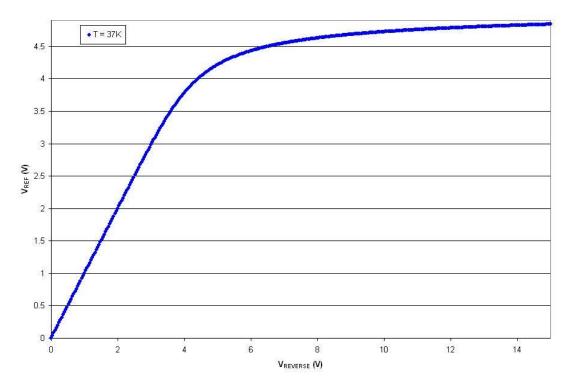

| Figure 35: Zener diode voltage reference voltage versus input voltage at T=37K                  |    |

|                                                                                                 |    |

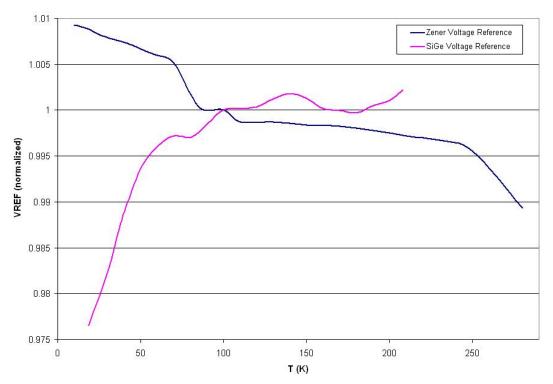

| Figure 36: Reference Voltage versus Temperature for zener diode and SiGe voltage      | •  |

|---------------------------------------------------------------------------------------|----|

| references (normalized to one at T=100K)                                              | 62 |

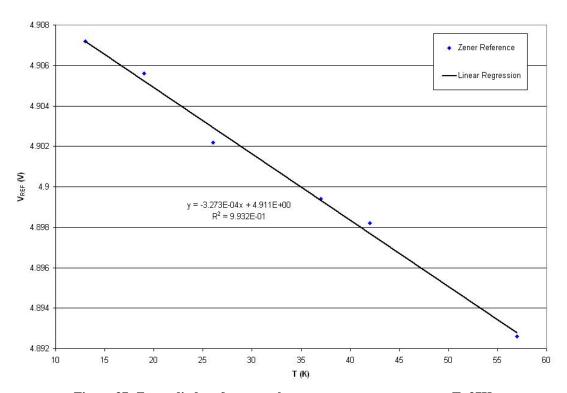

| Figure 37: Zener diode reference voltage versus temperature near T=37K                | 63 |

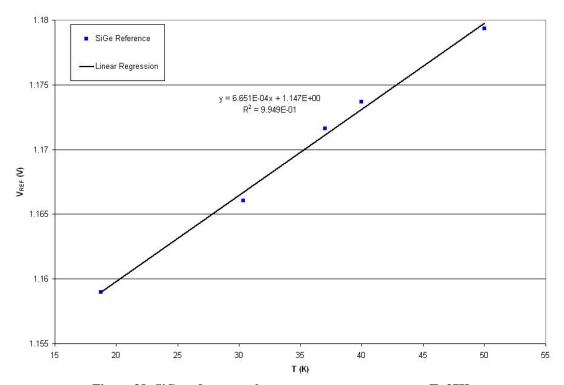

| Figure 38: SiGe reference voltage versus temperature near T=37K                       | 64 |

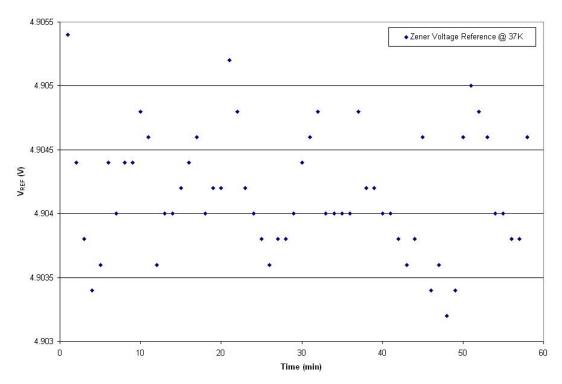

| Figure 39: Zener diode voltage reference stability at T=37K                           | 65 |

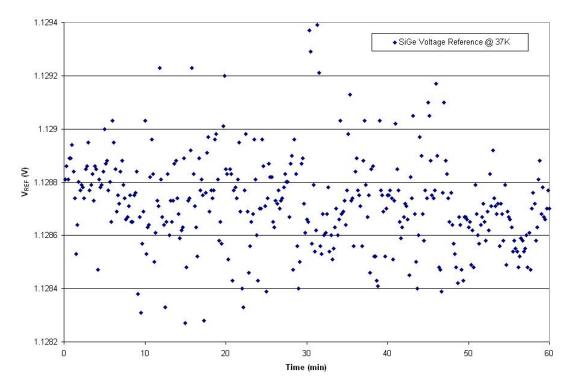

| Figure 40: SiGe voltage reference stability at T=37K                                  | 66 |

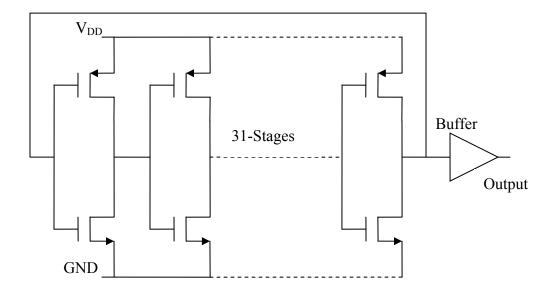

| Figure 41: Schematic of Ring Oscillator Circuit                                       | 68 |

| Figure 42: Tektronix TDS 744A Oscilloscope                                            | 69 |

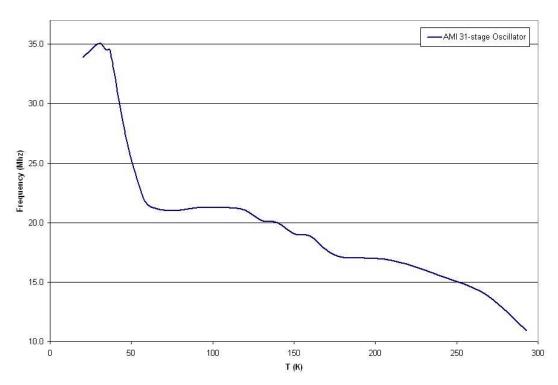

| Figure 43: Frequency versus Temperature (Oscillator B)                                | 70 |

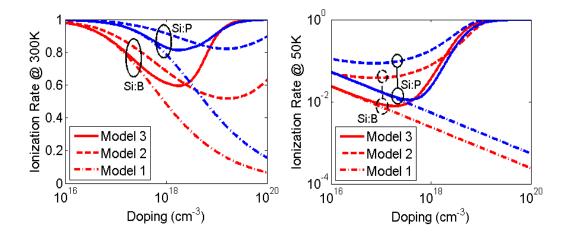

| Figure 44: Calculated ionization rates of phosphorus and Boron in Silicon at room     |    |

| temperature (left) and 50K (right) as a function of dopant concentration, using three | ;  |

| different models                                                                      | 85 |

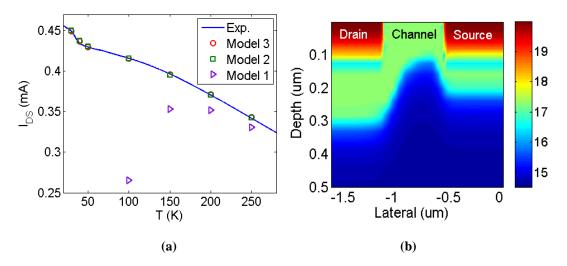

| Figure 45: (a) Calculated and measured current versus temperature characteristic fo   | r  |

| device A, and (b) calculated doping profile at T=50K using Model 3. Colorbar show     | VS |

| concentration in cm <sup>-3</sup> (V <sub>GS</sub> =4V, V <sub>DD</sub> =5V)          | 87 |

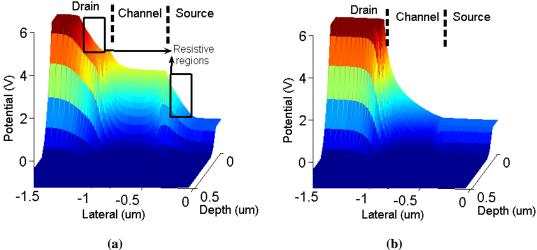

| Figure 46: Calculated MOSFET potential profiles at 40K, using (a) Model 1, and (b     | )  |

| Model 3 (V <sub>GS</sub> =4V, V <sub>DD</sub> =5V)                                    | 89 |

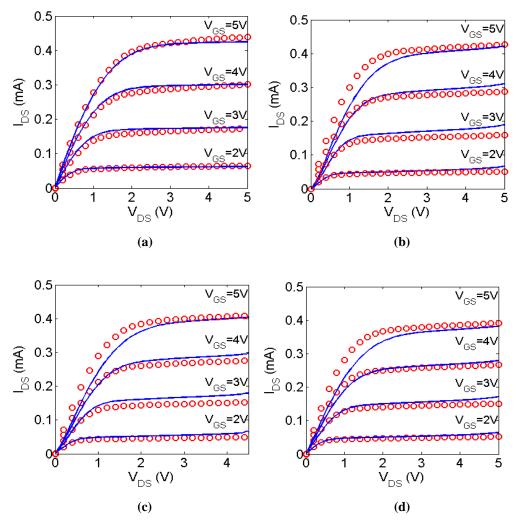

| Figure 47: Calculated (circles) and measured (lines) I-V families of curves for (a)   |    |

| device A at 293K and device B at (b) 37K, (c) 60K, and (d) 120K, using Model 3        | 90 |

## **CHAPTER 1: Introduction**

## 1.1 Background

As space exploration, satellite communications, and other extraterrestrial activities become increasingly common, so too has the need for electronics that function at extremely low temperatures. The operational temperature of space assets can vary anywhere from a few Kelvin, in the cold of deep space, all the way up to 100-200K for satellites in near earth orbit exposed to the extremes of solar radiation [1]. While electronics do exist that operate at these temperatures, their development is severely limited by inefficient design tools and prohibitive costs. Two main reasons exist for these limitations. First, there is a lack of simulation and modeling capabilities in the low temperature electronics community. Standard semiconductor simulation models, such as the industry standard Berkeley Simulator (BSIM), only support temperatures down to approximately -55°C. These models do not take into account the physical changes that occur below this temperature and thus provide inaccurate simulation results for space applications. The second reason is due to a perceived need for exotic technologies such as silicon germanium based devices [2]. While these technologies are not without merit, they are more expensive and less widely available than standard silicon and are not absolutely necessary for every low temperature application. These technologies also suffer from the lack of a sound modeling basis for designs at low temperature.

The lack of modeling capabilities described above forces the designer to choose one of two approaches. One can either use rule-of-thumb estimates in which a device is fabricated and then tested at low temperature in the hope that it works, or

the device can be contained in a temperature controlled environment. The guess and check approach is extremely inefficient and has no guarantee of producing the desired results. The second approach has a much greater chance of success, but changing the environment instead of the device itself has many drawbacks, including increased power consumption, weight, and size, all of which are at a premium on a spacecraft. Furthermore, this option is not always available. Clearly, neither of these design approaches is desirable from an economic or feasibility standpoint.

The ideal environment for low temperature design would include the ability to accurately model and simulate circuits and low temperature, and the option to use standard silicon CMOS processes. By demonstrating and characterizing the functionality of standard silicon transistors over the range from room temperature to cryogenic space temperatures, the development of a physics based model that will accurately predict device operation over this range becomes possible. Such a model would allow for a systematic design process, no different then that used for standard circuit design at room temperature. The "guess and check" aspect of low temperature design would be eliminated, providing substantial time and cost savings. In addition, designers would have the ability to use relatively inexpensive, well-developed silicon CMOS processes for low temperature circuits.

This section will provide a brief background in semiconductor device physics and discuss low temperature phenomena that affect device performance. Specifically, the formation of impurity bands, as well as impurity dependent changes in activation energy will be discussed, as this is central to device operation at low temperature. In addition, this section will also provide background information on cryogenics and

mechanisms of heat transfer. It should be noted that the temperature of 37K appears several times throughout this work. This is due to the fact that much of this research was aimed at a NASA specification at this temperature. The body of work presented, however, is relevant over a large range, not just a single temperature.

### 1.1.1 Semiconductor Device Physics

This subsection will offer a brief background in semiconductor device physics. Discussion is limited to background information relevant to the understanding of low temperature effects.

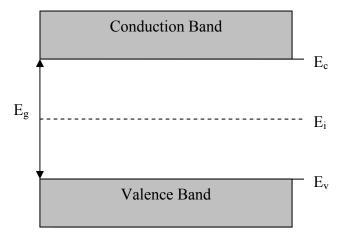

The basis of any silicon semiconductor is an intrinsic silicon wafer that is nearly pure. Silicon is a column IV element, meaning that it has four valence electrons which form covalent bonds with four neighboring atoms. It follows from the application of quantum mechanics that the allowed energy levels of electrons in a solid can be grouped into bands [3]. These energy bands are separated by forbidden regions of energy that cannot be possessed by electrons in the material. These are so called bandgaps. The energy-band diagram of silicon is shown below in Figure 1.

Figure 1: Energy Band Diagram of Silicon

In Figure 1,  $E_c$  and  $E_v$  represent the conduction and valence band energies, respectively.  $E_g$  is the energy difference between the conduction band and valence band, also known as the bandgap energy.  $E_i$  is the intrinsic Fermi level, the energy at which the probability of occupation of an energy state by an electron is one-half. At absolute zero temperature, the valence band is completely full of electrons and there are no mobile carriers in the conduction band, thus current conduction is impossible. As the temperature increases, electrons are promoted via thermal energy into the conduction band, leaving behind holes in the valence band. This ionization creates a free carrier concentration and allows for conduction to take place [4].

What differentiates a semiconductor from a metal is that metals have electrons in the conduction band even at absolute zero temperature, allowing for conduction at any temperature. Insulators, on the other hand, have a much larger bandgap energy that does not allow for the excitation of electrons into the conduction band at room temperature. In practice, the relatively large silicon bandgap energy of 1.1eV [5] leads to a low mobile carrier concentration and makes it a poor conductor even at room temperature. To obtain more desirable electrical properties, impurity atoms (dopants) are added to the intrinsic silicon.

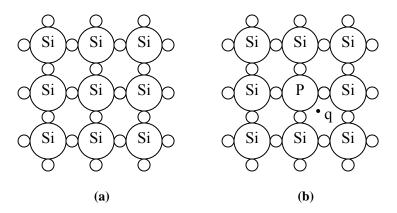

Silicon dopants come from either column III (boron) or column V (arsenic or phosphorus) of the periodic table. A column V atom has five valence electrons, meaning that it will form four covalent bonds in the silicon lattice and have a loosely bonded extra electron. The addition of column V dopants creates impurity energy states in the forbidden region between the valence and conduction bands. Located close to the conduction band, these energy states reduce ionization energies and

increase the number of mobile carriers, making the doped silicon a much better conductor. Silicon doped in this fashion is known as n-type, and its electrical conductivity is dominated by electrons in the conduction band. Column III dopants work in the opposite fashion. Since they only have three valence electrons, they can be ionized by accepting an electron from the valence band, thus leaving behind a mobile hole. This type of doping produces p-type silicon, in which electrical conduction is dominated by holes in the valence band.

Over an intermediate range of temperatures in doped silicon, including room temperature, there is enough thermal energy to fully ionize all mobile carriers. This is due to the small energy gap between the impurity energy states and conduction band (or valence band for p-type). The mobile carrier concentration over this range is generally assumed to be the same as the doping concentration [4]. As temperature decreases below this range, however, there may no longer be enough thermal energy to ionize all the impurity atoms. This condition is known as incomplete ionization, or freeze-out [6]. As will be explained in the following subsection, doping and incomplete ionization are key to the understanding and modeling of low temperature device operation.

## 1.1.2 Low Temperature Phenomena

As temperature decreases, there are two physical phenomena that dominate device operation, increased mobility and incomplete ionization. High mobility is generally good for component performance as long as it can be modeled. Freeze-out is bad as it increases parasitic resistances and decreases a transistor's current drive capability.

Mobility is determined by two main scattering mechanisms, electron-phonon scattering and impurity scattering. Electron-phonon scattering is due to scattering in the silicon lattice, while impurity scattering is due to ionized impurities. At higher temperatures (near room temperature) scattering by ionized impurities is less effective since the faster moving carriers interact less effectively with stationary impurities [26]. Initially, as temperature decreases, mobility increases due to a decrease in the electron-phonon scattering rate [27-30]. This increase continues until the impurity scattering effect begins to dominate over the lattice vibrations, causing the mobility to reach a maximum value and then roll off. The location of the roll-off point is a function of doping. Temperature models have been developed which include these mobility effects as well as the decrease in current at lower temperatures due to the increase in built in potential [15, 27-28]. These models show an increase in MOSFET current for decreasing temperature in the region where electron-phonon scattering is dominant, followed by a sharp decrease in current in the region where impurity scattering begins to dominate. An accurate low temperature model, however, must also include the effects of impurity concentration as it pertains to incomplete ionization [31].

If one were to simply extract the mobile carrier occupancy of a band assuming an "activation energy" model then the promotion energy from the dopant level to the band-edge is fixed, significant freeze-out effects would be observed at temperatures below 77K. This, though, does not occur in modern, deeply scaled (10<sup>18</sup>/cm<sup>3</sup>) VLSI. This is due to the more heavily doped source/drain regions encountered in scaled structures. Heavy doping leads to impurity band formation. Impurity band formation

and charge conduction through this band has been studied ever since the introduction of solid-state devices [12-14]. To understand the formation of impurity bands it is important to understand how the semiconductor doping process works. Figure 2 below shows the lattice bond structures of intrinsic silicon and phosphorus doped n-type silicon.

Figure 2: Lattice Structure of (a) Intrinsic and (b) n-type Silicon

The process of doping silicon creates impurity energy states in the forbidden gap between the conduction and valence bands. Increasing the impurity concentration causes increased interaction between the impurity states. Eventually, when doping exceeds 10<sup>16</sup>/cm<sup>3</sup>, the impurity states themselves form a band. To clarify this, realize that most impurity atoms are situated far apart in the lattice and thus their bound electrons do not interact with one another [7]. As doping levels increase, however, the impurity atoms become situated closer together. When the distance between two such atoms shrinks to less than two Bohr radii, quantum mechanical mixing occurs due to Coulomb interaction [8]. Further increases in doping cause additional impurity atoms to interact with one another, leading to the formation of impurity clusters. At doping densities greater than 10<sup>18</sup> cm<sup>-1</sup>, clusters of three or more impurity atoms outnumber

isolated impurities [8-11]. This increase reduces activation energies in two ways. First, the clusters interact to broaden the impurity band and the density of states (DOS) associated with these bands [8]. Second, the dopant energy level approaches the conduction band since the excess electrons are less strongly bound to their column VI impurity cores [9].

Over the years, a number of theories have been proposed to explain how both doping concentration and temperature affect incomplete ionization, as well as the implications of these effects on device performance [15-25]. There have also been approaches developed to include incomplete ionization models in device simulators. Despite this work, there remains a level of ambiguity about the effects of incomplete ionization on device performance and inclusion of incomplete ionization models in device simulators. There have been several works that suggest that ionization rates decrease for higher dopant concentrations, with no full ionization observed at very high concentrations [20-25,32,33]. Recent works by Altermatt et al., however, suggest otherwise [16-18]. These papers predict a decrease in ionization rate beginning at doping densities of approximately 10<sup>18</sup> cm<sup>-1</sup> and then a return to full ionization near 10<sup>19</sup> cm<sup>-1</sup> due to Mott metal-insulator transition [34]. If this, in fact, what happens, then heavily doped devices may not suffer from incomplete ionization effects at low temperature as previously thought.

It is apparent from a review of the literature that a complete device data set that provides current-voltage characteristics from cryogenic temperatures up to room temperature is needed for heavily doped structures. This data would provide a reference point from which different incomplete ionization models could be verified or disproved. This would subsequently allow for the development of a low temperature model which incorporates doping dependent incomplete ionization, impurity band conduction, and temperature dependent mobility effects to accurately predict low temperature operation. These data are provided in this thesis. They are, in fact, the major contribution of this work to the scientific literature.

## 1.1.3 Low Temperature Testing Considerations

Cryogenic testing presents many inherent challenges. Cooling a device to extremely low temperatures in an environment which permits electronic testing requires highly specialized equipment, as well as knowledge of the heat transfer processes which govern the temperature of the system. This section will serve as an introduction to the low temperature testing process and provide a general background on the mechanisms of heat transfer.

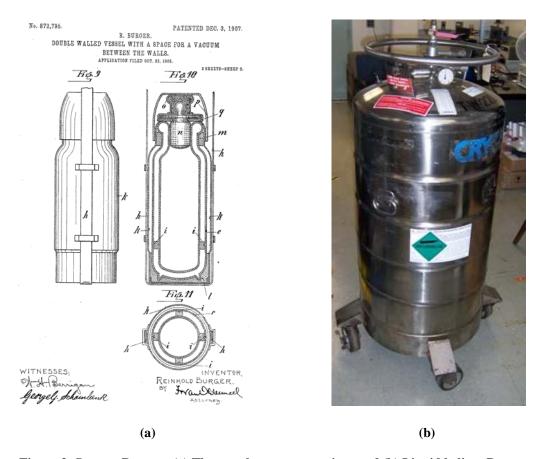

Cryogenic testing is performed inside a device called a Dewar (named after its inventor, James Dewar [35]), which is a container designed to keep its contents hotter or cooler than the ambient environment. In its simplest form, a Dewar is double-walled container with an evacuated region between its inner and outer walls. Two such containers are shown below. Figure 3a is a drawing from the patent application for the first commercial Dewar, also known as the Thermos beverage container [36]. Figure 3b shows a standard liquid helium Dewar. The vacuum region does not permit heat transfer via conduction or convection, and thus maintains the temperature of the contents for an extended period of time.

Figure 3: Storage Dewars: (a) Thermos beverage container and (b) Liquid helium Dewar

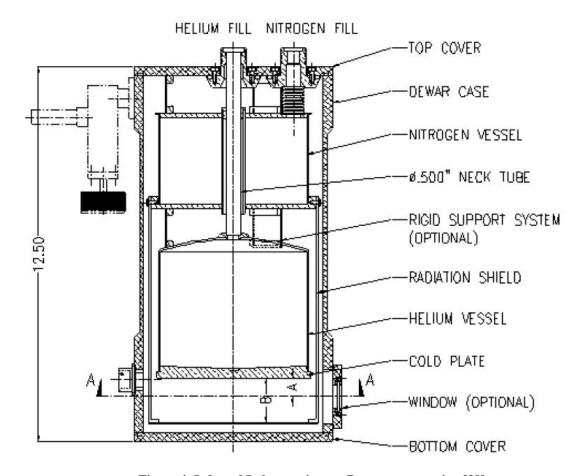

The Thermos and liquid helium Dewar shown above are only useful for storing liquids. To perform actual low temperature testing, a more complicated type of Dewar is needed. The cross section of a test Dewar is shown below in Figure 4. Much like the containers shown above, this Dewar contains vacuum shielded vessels for liquid nitrogen and liquid helium. In addition, however, there is a radiation shielded vacuum chamber in which the device under test (DUT) is located. This Dewar minimizes convection and radiation (as well as unwanted conduction through air), and uses conduction from the helium vessel through the cold plate to the DUT as the only means of heat transfer. The following paragraphs will explain the three

mechanisms of heat transfer and chapter two will discuss the operation and use of the test Dewar in greater detail.

Figure 4: Infrared Laboratories test Dewar cross section [38]

Conduction, convection, and radiation are the three mechanisms of heat transfer. Of the three, radiation is the only one which can transfer energy through a vacuum. When designing a low temperature test setup, it is essential to understand how each of these processes works to achieve the desired cooling effects as efficiently as possible.

Conduction is the process by which thermal energy is transferred from a region of higher temperature to a region of lower temperature. It can occur within a single medium or across two mediums which are in physical contact with each other.

On an atomic scale, this transfer represents the exchange of kinetic energy between electrons in a material, either due to vibration of electrons in the lattice or the motion of free electrons [37]. Metals are good thermal conductors due to their high concentration of free electrons, whereas insulators have the opposite effect. Gases are very poor thermal conductors because of their large separation distance between particles [37]. The amount of energy transferred Q during time interval  $\Delta t$  due to conduction is given by the following formula:

$$\frac{Q}{\Delta t} = kA \frac{dT}{dx} \tag{1}$$

In the equation above, A is the cross-sectional area, T is the temperature difference over a length x or temperature gradient, and k is the thermal conductivity proportionality constant. Since the dominant heat transfer mechanism in a cryogenic test setup is conduction, this equation is very important. It determines how quickly thermal energy will be transferred out of the DUT through the cold plate, and hence, how fast the device will cool. Copper is generally used for the cold plate since it has very high thermal conductivity and thus achieves maximum energy transfer between the helium vessel and the DUT.

Convection is the transfer of thermal energy via circulation of warmer particles to cooler areas. For convection to occur, a heat source must be surrounded by a fluid medium. The source transfers heat to the fluid, which in turn causes it to become less dense and rise. The rising fluid is then replaced by the surrounding cooler fluid. This process continues until the heat source and the surrounding medium reach equilibrium [37]. This process can be accelerated by using a fan to increase the speed of circulation between hot and cold fluids.

If the DUT was not contained in a vacuum chamber, convection would occur in the opposite manner as that described above. The device under test would receive heat from the surrounding air, causing the air to descend and be replaced by warmer air. This process would continue until the device was at equilibrium with the surrounding air. This process would make cryogenic testing extremely inefficient, if not impossible. The test Dewar is thus pumped down to a very low vacuum pressure to minimize convection.

The third means of heat transfer is radiation. All objects radiate energy continuously in the form of electromagnetic waves produced by thermal vibrations of atoms [37]. The rate at which an object radiates energy is governed by Stefan's Law, which states that radiation rate is proportional to the fourth power of absolute temperature. This relationship is given below in (2), where P is the power radiated by the object,  $\sigma$  is a constant, A is the surface area, e is the emissivity constant, and T is the surface temperature. The emissivity constant is the ratio of energy radiated by the object to that radiated by a perfect black body.

$$P = \sigma A e T^4 \tag{2}$$

Since radiation is capable of propagating through a vacuum, the DUT inside the Dewar is susceptible to heating via radiation. This heating is obviously undesirable and would lead to temperature gradients across the device. To minimize this effect, the test chamber inside the Dewar is surrounded by a liquid nitrogen cooled, aluminum radiation shield. Thus, instead of seeing 300K radiation from the outer casing of the Dewar, the DUT sees the 77K, radiation shield, which minimizes

heating due to radiation and allows conduction to dominate the temperature of the device.

## 1.2 Research Objectives

#### 1.2.1 Research Goals

The primary objective of this research is to advance the understanding of silicon device operation at cryogenic temperatures. Several different transistors will be tested and characterized at low temperature. A heavy focus is placed on MOSFETs since these devices have the potential for low temperature operation due to their higher doping concentrations. The goals of this testing and characterization process are to demonstrate MOSFET functionality at cryogenic temperatures and provide complete families of I-V curves at temperatures ranging from room temperature down below the NASA specification of 37K. In doing so, this research will provide the basis for the development and verification of a physics-based model that predicts device performance at any temperature. Such a model would enable the cost effective use of standard silicon MOSFETs in space and other low temperature applications.

In addition to testing and characterizing transistors, this research will explore an alternative to the use of expensive silicon-germanium (SiGe) based structures for the design of a low temperature voltage reference circuit. A zener diode reference with a temperature compensating resistor will be tested as a solution to meeting the specification of a 37K voltage reference. The goal of this study is not to discount the merits of SiGe technology, but rather to illuminate a more cost effective alternative for the specific application.

The third goal main goal of this research is to examine how changes in MOSFET device performance at low temperature affect circuit performance. A ring oscillator will be tested since it is a relatively simple circuit and its oscillation frequency is directly related to device current. Thus, changes in current with temperature should be reflected by an increasing or decreasing frequency of oscillation.

To meet these challenges, a helium Dewar based cryogenic test setup has been constructed and used to test several different devices. These include various MOSFET transistors, a bipolar junction transistor (BJT), a zener diode voltage reference, and two ring oscillator circuits. The following subsection will outline the scope of the research and the contributions made to the low temperature electronics community.

## 1.2.2 Scope of Research

This research investigates the operation of various semiconductor devices and circuits at low temperature. Chapter 2 focuses on the design and operation of a cryogenic test setup which facilitates testing of electronic components at low temperatures. The design of a specialized helium test Dewar is explained, and a description of the internal test board is also provided. This is followed by an explanation of the many thermal considerations that must be taken into account when designing a low temperature test setup. Several factors, including vacuum levels, outgassing, cleaning, and heat transfer are discussed. Finally, the complete, step-by-step cool down process is described in detail, providing pictures and descriptions of everything from pump down to helium transfer. This chapter aims to serve as a basic

reference which will minimize the steep learning curve associated with cryogenic testing.

Chapter 3 details the preedures and results of the transistor characterization process. First, a MOSFET device is tested for functionality at cryogenic temperatures. A small transistor is used to reduce current and subsequently minimize self heating. Once transistor functionality is established, the I-V characteristics of several devices are measured over the entire temperature range of interest to provide the basis for a simulation model. One of the devices tested in this fashion is a large transistor. The results of this test provide insight into self heating effects. The I-V curve families of a bipolar junction transistor (BJT) are also measured to verify the theory of BJT freezeout due to a lower doping concentration in the base. At the end of this chapter, a noise test is also conducted to measure the reduction in 1/f noise due to low temperature operation.

In chapter 4, two different types of circuits are tested at low temperature. The first of the two is a zener diode based voltage reference. A zener is chosen as a suitable alternative to a SiGe based voltage reference because it operates as a tunneling structure under reverse bias. These structures are extremely heavily doped (>10<sup>19</sup>/cm³) and should not be susceptible to incomplete ionization. The zener is tested in two configurations, with the series resistor outside the test Dewar to determine the zener temperature dependence and with the resistor inside the Dewar to provide temperature compensation. The results of these tests are compared against a SiGe voltage reference circuit which is also tested at low temperature. The second type of circuit tested in chapter four is an integrated ring oscillator. This test is

conducted to determine if increases in current due to decreasing temperature will correspond to increasing oscillation frequency.

## **CHAPTER 2: Test Setup**

The first major challenge of this research was to design an environment suitable for testing electronic devices at cryogenic temperatures. To meet this challenge, a liquid helium based cryogenic test setup has been constructed with internal electrical connections for transistors and integrated circuits in various packages. This section will describe the test setup assembly process and discuss the many thermal considerations that must be taken into account when designing for low temperature. It will also describe the steps necessary to actually cool the Dewar and perform low temperature testing. The test setup and cool down procedures described in this chapter will form the basis for the low temperature measurements described in chapters three and four.

## 2.1 Cryogenic Test Dewar

### 2.1.1 Dewar Design

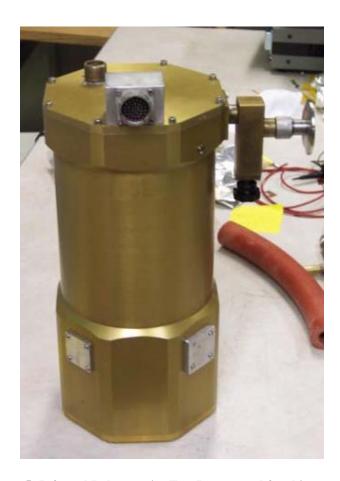

As was stated in chapter one, a highly specialized Dewar is required for low temperature testing. It must be able to not only store liquid like the Thermos-style Dewar shown in Figure 3a, but also provide a cold, dry, electronics testing compartment with connections to the outside world. The cross section of the test Dewar used for this research was shown in chapter one (Figure 4) and the actual Dewar is shown below in Figure 5.

Figure 5: Infrared Laboratories Test Dewar used for this research

The test Dewar consists of three main compartments, these include the liquid nitrogen (LN<sub>2</sub>) tank, liquid helium (LHe) tank, and the device testing area below the helium tank. As was explained in chapter one, the DUT is heat sunk to the LHe chamber via a copper cold plate. Vacuum seals are located at the bottom plate, the top plate, and the pump connector. It is important to note that the sealed inner parts of the Dewar are kept under vacuum during testing to maintain insulation for the cryogenic holding tanks. A radiation shield which is heat sunk to 77K extends down from the liquid nitrogen tank to surround both the liquid helium tank and the test chamber. This increases the lifetime of the LHe and thus the hold time of the system as well.

## 2.1.2 Internal Board Design

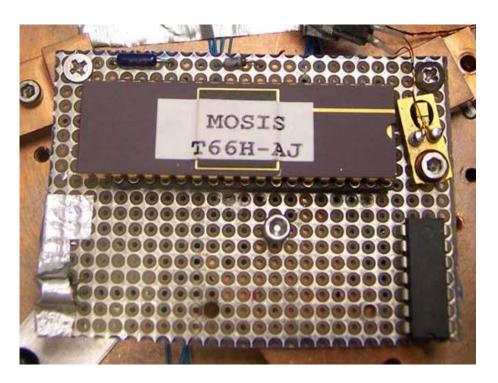

To facilitate the testing of various transistor devices and other integrated circuits, a board has been mounted inside the Dewar on the cold plate. The board consists of a socket to accommodate both 40 and 28 pin dual-inline packages (DIP40, DIP28), a temperature sensor, and free space which can be populated with a heater or other various components as desired. The test board is shown below in Figure 6.

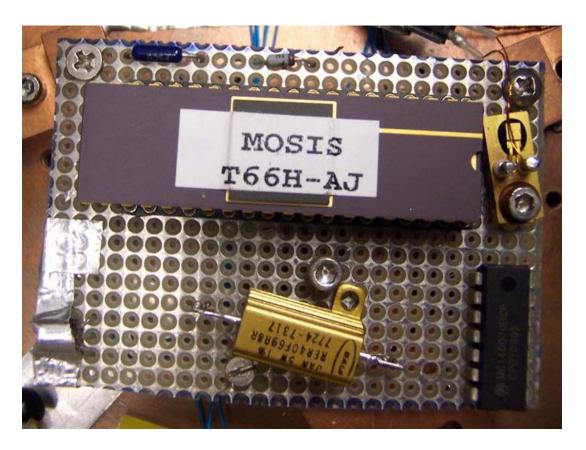

Figure 6: Internal test board

As shown in the photo above, the test board contains the following components: resistor (top left), zener diode voltage reference (top middle), transistor housed in a DIP40 package (middle), thermal diode sensor (top right), commercial MOSFET (bottom right), commercial BJT (bottom left beneath aluminum tape). Here, the board is shown with copper standoffs. This is one of several board configurations that have been used for this research. The board components, as well

as the thermal connections from the board to the cold plate, have been varied based on what is being tested and the desired cooling rate. Thermal considerations and cooling rate will be discussed in the next subsection.

#### 2.1.3 Thermal Considerations

When performing cryogenic testing, thermal effects are of utmost importance. Improper design may result in a system exhibiting unacceptable temperature fluctuation, or worse, is impossible to cool down to the desired testing temperature. To ensure that this does not occur, many thermal considerations must be taken into account.

The first key to low temperature testing is a very high vacuum. If a sufficiently low pressure is not reached within the system, several adverse effects occur. First, particles left in the Dewar permit heat transfer via conduction and convection as described in chapter one, which prevents the cryogens from establishing equilibrium with the inner wall of their containers. This leads to rapid boil-off and make the system very difficult to cool. Second, a poor vacuum environment contains water vapor molecules. If the DUT is cooled within such a medium, then water vapor will condense on the cold surfaces, which can lead to failure for sensitive electronic components. The test Dewar should be pumped down to a pressure of at least 2\*10<sup>-5</sup>Torr before cooling begins. This ensures that nearly all of the nitrogen, oxygen, and water vapor have been pumped out of the system, and only inert gases remain [46].

To achieve the desired low pressure, high vacuum grease is applied to each of the o-ring seals within the Dewar and a turbocharged vacuum pump is used. To minimize pump-down time, outgassing materials such as electrical tape are avoided. Outgassing is the release of gas particles that have been trapped or absorbed inside a material [39]. At atmospheric pressure, the rate at which most materials outgas is relatively insignificant. In space applications, however, pressures are generally on the order of 10<sup>-6</sup>Torr or lower; outgassing presents a challenge to maintaining such high-vacuum environments. NASA maintains a database which provides outgassing data for selecting spacecraft materials [40]. In addition to proper material selection, the inside of the Dewar is thoroughly cleaned with isopropyl alcohol before each test to remove outgassing impurities.

As was explained in chapter one, nearly all heat transfer within the evacuated test Dewar system occurs via conduction. To minimize temperature gradients across the test board and maintain consistent temperatures, standoffs are placed around the edges as well as in the middle of the board. This configuration ensures that the temperature measured by the thermal diode is as close as possible to that of the test components, since each is heat sunk via copper or aluminum to the board. In Figure 6, the board is shown with copper standoffs. These copper thermal connections are typically used, but brass standoffs are also used depending on the desired cooling rate. The thermal conductivity of brass is approximately 1/3 that of copper [41], so the rate of cooling can be increased or decreased accordingly. In any cryogenic test setup, there is an inherent tradeoff between cool down time and hold time, or the amount of time the system can remain cold. Increased thermal conduction between the cold plate and the DUT means that the device will cool faster, but also warm faster once the cryogens boil off. Thermal isolation between the cold plate and the

DUT has the opposite effect. The device will not cool as quickly, but it will remain cold for a longer period of time.

In addition to using different standoff materials, the rate of cooling is also affected by the addition (or subtraction) of mass from the system, which occurs in the form of different test components. This is due to the specific heat of the added material, which is a measure of the amount of energy required to raise the temperature of that material by 1K. Or, from a cooling standpoint, it is the amount of energy that must be removed to decrease the temperature by 1K. The heat capacity of a substance, which is a function of specific heat and mass, is given below:

$$Q = mc\Delta T \tag{3}$$

In (3), Q is energy, m is mass, and c is the specific heat of the material. It follows that as mass increases, the amount of energy required to change the temperature of the substance increases as well. When several components are being tested during the same cool down, the thermal conductivity between the board and the cold plate is increased to account for this increase in mass.

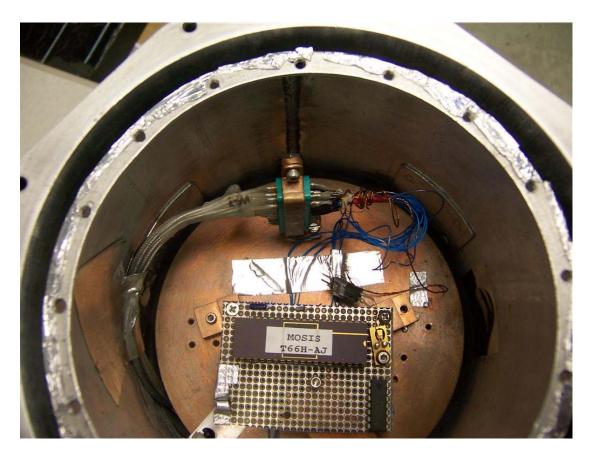

The last thermal consideration, which can be easily overlooked, is the internal Dewar wiring. Wires link the DUT to the outside world, and hence, provide a thermal link to a 300K environment. Two steps are taken to minimize heat injection from the wires. First, very thin gauge wires are used to minimize cross-sectional area and hence thermal conduction. Second, the wires are heat sunk to the 4.2K LHe cold plate, and then to the 77K radiation shield on their way out of the Dewar. If these steps are not taken, then the cooling power of the system will be severely compromised. In Figure 7 below, the inside of the test Dewar is shown after having

been prepared for cooling. This photo shows the outer casing of the Dewar, the radiation shield, and the board mounted to the cold plate. Note that the wires have been heat sunk to both the cold plate and the radiation shield using thermally conductive aluminum tape.

Figure 7: Inside of test Dewar with proper wire heat-sinking to minimize heat injection

## 2.2 Cooling Procedure

The process of cooling the test Dewar from room temperature down to temperatures below 37K requires several steps. The goal when cooling the system is to minimize the use of liquid helium, since it is considerably more expensive than its  $LN_2$  counterpart. Steps are taken to use LHe as efficiently as possible. Since the cool

down process is the same regardless of which device is being tested, it is prudent to explain this procedure in a detailed, step-by-step fashion.

## 2.2.1 High-Vacuum Pump

The first step in the cool down process is to establish a high-vacuum environment. This is done using an Alcatel 2008A turbo pump connected to a CVF-100 controller and a Balzers pressure gauge. The pump and pressure gauge are shown below in Figure 8.

Figure 8: Alcatel pump and controller (left) and Balzers pressure gauge (right)

Initially, the pump itself and tube fixture must be evacuated. Since the pump has been evacuated many times and is designed minimize outgassing, this is usually

very quick process. After being on for a minute or two, the turbo spins up to speed and the pressure drops down to the order of 10<sup>-6</sup>Torr. At this point, the pump is connected to the Dewar as shown in Figure 9 and the valves on both the Dewar and the pump are opened to allow evacuation of the Dewar.

Figure 9: Dewar connected to vacuum pump

The amount of time required to pump down the test Dewar depends on volume and outgassing materials. If the system has been pumped down before and thus the components inside have already been outgassed, then pumping time is significantly reduced. This particular test Dewar has a relatively small volume and takes only a matter of minutes to pump down to a suitable fill pressure of 2\*10<sup>-5</sup>Torr.

By contrast, large Dewars may take several hours to pump down to a reasonable fill pressure.

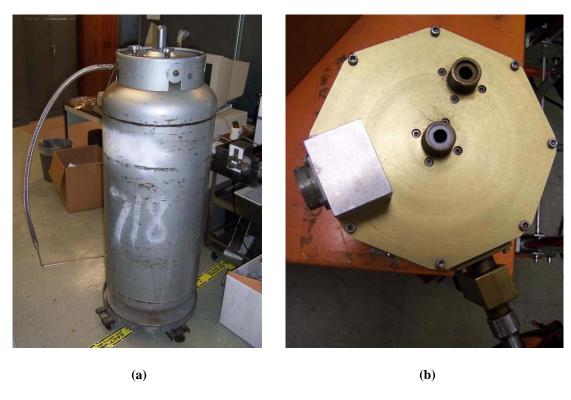

## 2.2.2 Liquid Nitrogen Transfer

Once the Dewar has reached a suitable vacuum, it remains attached to the pump while it is filled with  $LN_2$ . Liquid nitrogen filling is done using the direct injection fill tube connected to the storage Dewar as shown in Figure 10a. The fill tube connects to an internal tube which extends to the bottom of the tank. Since the  $LN_2$  is stored under pressure, opening the release valve causes liquid to flow out of the storage tank. Figure 10b shows the top of the Dewar with openings for the LHe (middle) and  $LN_2$  chambers.

Figure 10: (a) LN<sub>2</sub> storage Dewar with fill tube and (b) Top view of test Dewar

Initially, both the inner LHe and outer LN<sub>2</sub> tanks are filled with liquid nitrogen. This is done to cool the entire system as much as possible while saving LHe. If liquid helium was filled into a room temperature container, excessive amounts of the expensive cryogen would boil off. After approximately 1-2 hours, depending on the exact internal configuration, the nitrogen fill cools the system down to the LN<sub>2</sub> temperature of 77K. Once again, it should be noted that this cool down time is heavily dependent on the internal DUT configuration, which can range anywhere from a minutes to days. Once the temperature reaches 77K, or is within a few Kelvin, the Dewar is ready for the next step.

When the Dewar reaches equilibrium with the LN<sub>2</sub>, the air valve is closed and pump is disconnected. At this stage, the cold inner surfaces of the test Dewar act like a pump. The inert gas molecules adsorb on to the 77K inner surfaces and do not permit conduction through the vacuum insulation [46]. If the pump is disconnected prematurely, the test Dewar will feel cold to the touch and condensation will appear on the outside surface, this is a telltale sign that internal equilibrium has not yet been reached. If this occurs, the pump should be reconnected to stop the condensation and give the inner surfaces of the test Dewar additional time to equilibrate with the 77K LN<sub>2</sub>. After the pump is disconnected, the LN<sub>2</sub> is carefully dumped out of both chambers to make room for LHe in the inner tank. The outer chamber is then quickly refilled before the system begins to warm up. The test Dewar is now ready for liquid helium filling.

## 2.2.3 Liquid Helium Transfer

Liquid helium is stored in the Dewar shown above in Figure 3b. This Dewar is similar to one that stores  $LN_2$ , but has a special fitting on top with pressure release valves and an opening for a liquid helium transfer tube. The LHe transfer tube has an inner and outer chamber and utilizes the same vacuum insulation principle as the Dewar. It is also fitted with an o-ring seal to prevent pressure loss during fills. Without a vacuum tube, it would be impossible to transport a liquid with a boiling point of 4.2K through a room temperature medium. To initiate a fill, the pressure-release safety valves are closed and the transfer tube is slowly inserted into the top of the tank. As the warm tube contacts the cryogenic liquid, pressure builds up inside the storage tank and forces the LHe up through the tube and into the Dewar. When fill is complete, the safety valve is opened to release excess pressure and the tube is removed from the tank. Figure 11 shows a helium transfer in progress. In this picture a larger test Dewar is being filled than the one used in this research, but the transfer process is exactly the same.

Figure 11: Helium transfer from storage Dewar to test Dewar

Depending on the amount of LHe transferred to the test Dewar and the thermal considerations discussed earlier in this chapter, the system may reach the LHe temperature of 4.2K. In practice, the experiments conducted in this research were generally run over a temperature range from approximately 20K to room temperature. A minimum temperature of 20K is well below the NASA specification of 37K and is suitable for most space applications. If desired, the test Dewar could be reconfigured to cool much faster for 4.2K testing.

## **CHAPTER 3: Transistor Characterization**

## 3.1 MOSFET Characterization

Low Temperature device operation is the central focus of this research. For reasons outlined in the introduction, modern silicon MOSFET devices with heavily doped source drain regions have the potential to function at cryogenic temperatures. These devices are the building blocks of integrated circuits, and are an attractive solution for low temperature applications due to the availability of advanced design tools and relatively low design and fabrication costs. This section provides detailed results and analysis of MOSFET operation at low temperature. A MOSFET device is first tested for basic functionality at cryogenic temperatures. After this has been established, a detailed characterization of multiple devices takes place over the entire temperature range. Ultimately, this characterization process has led to the development of a simulator which predicts I-V characteristics at any temperature for a specific device. The explanation of the model is given in Appendix A. In addition to I-V analysis, noise and self-heating effects are also explored in this chapter.

## 3.1.1 Low Temperature Functionality

The first test conducted was a MOSFET functionality experiment. The measurement equipment used for this test consisted of a Keithley 2700 multimeter and a Lakeshore 340 temperature controller. These instruments are shown below in Figure 12.

Figure 12: Keithley 2700 (top) and Lakeshore 340 (bottom)

The device used was an NMOSFET fabricated by MOSIS [42] in the AMI 0.6µm process (device A). This transistor had a minimum gate length of 0.6µm and a width/length ratio of 3/1. The goal of this test was to determine if the device was capable of operation at low temperature due to theorized decreases in activation energy brought about by the heavy doping levels of the modern MOSFET. Self-heating was minimized due to the very small size of the device, detailed discussion of self-heating effects given later on in this section.

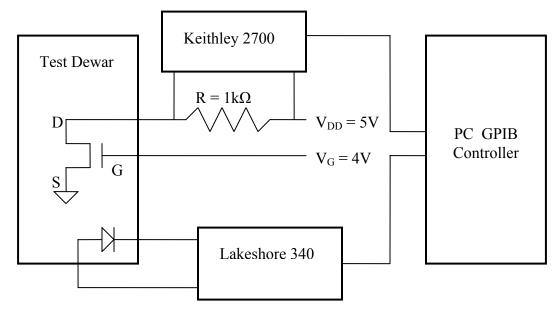

The transistor was placed in the DIP40 socket, and the source, gate, and drain terminals were wired out of the test Dewar. The device was biased in saturation with the gate terminal connected to 4V, source terminal connected to ground, and drain current connected to 5V via a  $1k\Omega$  resistor. The resistor was located outside the Dewar to avoid any changes in current due to the temperature dependence of the resistor. Both the 5V source ( $V_{DD}$ ) and drain voltage ( $V_{D}$ ) were connected to the multimeter. The thermal diode, as always, was connected to the temperature

controller. Both instruments were connected to a LabVIEW equipped PC via the GPIB interface. A schematic of the setup is presented in Figure 13.

Figure 13: Schematic of MOSFET functionality test setup

Once the configuration shown above had been setup, the test Dewar was cooled to 20K using the procedure outlined in Section 2.3. The system was then allowed to slowly warm up to room temperature over a period of approximately three hours. As the DUT warmed, both the temperature and voltage across the resistor were recorded at 30 second time intervals. The voltage across the resistor was used to calculate drain current. It should be noted that this test was conducted using two different methods to explore possible self heating effects. First,  $V_{\rm DD}$  was left on throughout the entire test as data was recorded. The second time around,  $V_{\rm DD}$  was switched on immediately before each measurement and switched off immediately after. These two methods produced the same results, and thus it was concluded that

self heating was not affecting the test. The results of this measurement are shown below.

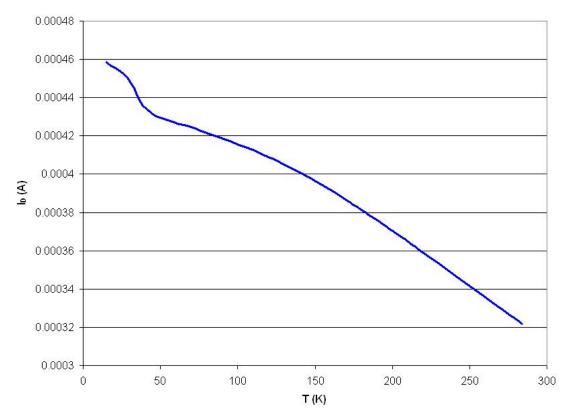

Figure 14: Saturation Current versus Temperature (Device A)

Figure 14 shows that as temperature decreases, current increases over the entire range of the measurement. The sharp roll off that would be expected for a device which is suffering from incomplete ionization was not observed. The plot can be explained in the following manner. Starting at room temperature, the initial increase in current is due to a reduction in the electron-phonon scattering rate. As the temperature continues to decrease, however, the rate of increase in current begins to level off. This is associated with the increase in impurity scattering, which begins to cancel out the electron-phonon scattering effect at lower temperatures. Below 50K,

impurity scattering gives way to a rise in conduction in the impurity band, which leads to a sharp increase in current. This test confirmed that the silicon MOSFET was a viable device at low temperature and allowed for progression to the next device test, described below.

## 3.1.2 Low Temperature I-V Characteristics

The results of the previous section established MOSFET functionality at cryogenic temperatures and provided insight into the physical processes which dictate MOSFET performance at low temperature. The next step was to further the understanding of these processes and enable the development of a low temperature model. To accomplish this, complete current-voltage characteristics, as opposed to single data points, were needed over the entire temperature the range of interest. This data was obtained by running a series of tests using the HP4156B semiconductor parameter analyzer, shown below in Figure 15.

Figure 15: Hewlett Packard 4156B Semiconductor Parameter Analyzer

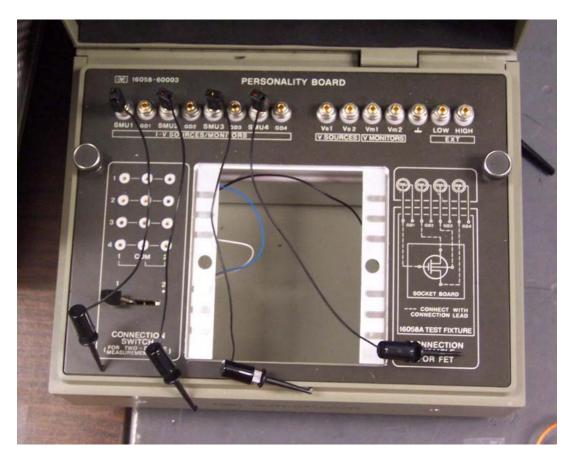

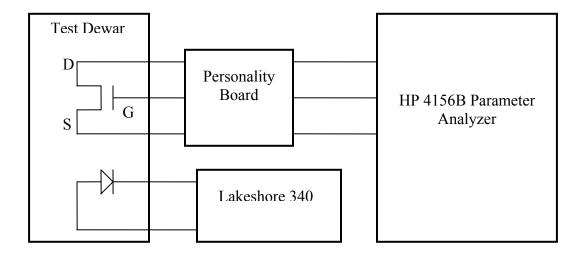

The parameter analyzer is a very robust instrument which can be configured to test a variety of different devices. It consists of four triaxial source-measurement units (SMUs) which are capable of sourcing voltage and measuring current simultaneously. It also has two coaxial voltage source units (VSU) and voltage measurement units (VMU). The SMUs interface with the transistor terminals via the HP16058 Personality Board shown in Figure 16. The schematic of this test setup is shown in Figure 17.

Figure 16: Hewlett Packard 16058 Personality Board

Figure 17: Schematic of MOSFET I-V characteristic test setup

Several MOSFETs were tested in this configuration. The first of which was a second small AMI 0.6µm transistor (device B) fabricated on the same run as device A. Device A was not used for this test because it began to malfunction after being cooled several times for the previous test. This was attributed to the thermal stresses on the package caused by repeatedly cooling the device from 300K down to approximately 20K as well as mechanical stresses associated with picking up the test Dewar to dump out the liquid nitrogen as described in Section 2.3.

Device B (DIP40 package) was mounted in the test Dewar in the same fashion as in Figure 7 and wired out to the personality board as shown in the schematic above. The following measurement settings were used on the 4156B: The source was grounded; the drain voltage was swept from 0-5V at gate voltages of 2, 3, 4, and 5V; the drain SMU was set to measure current. Drain current was then plotted as a function of the drain-source voltage (V<sub>DS</sub>) for each gate voltage. The test Dewar was then slowly cooled to 20K over a period of approximately three hours. As the device cooled, the parameter analyzer sweep was run at various temperature intervals, producing a complete set of I-V curves at each temperature. The slow cool down rate of the system, combined with a sweep time of just a few seconds for the 4156B, ensured that the entire set of curves was measured within 0.5K of the desired measurement temperature. At colder temperatures, however, where rate of cooling was significantly slower, the temperature accuracy of these measurements increased to 0.1K or better. The results from this test are provided below (Figures 18-21).

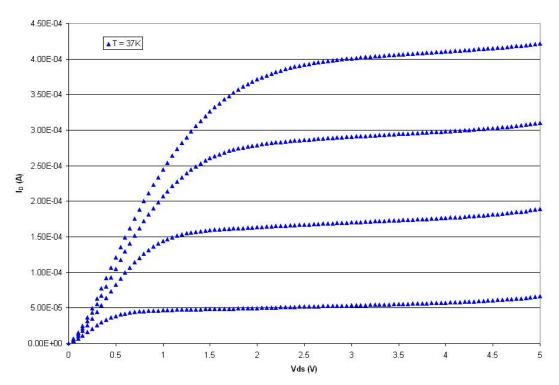

Figure 18:  $I_D$  versus  $V_{DS}$  family of curves at 37K (Device B)

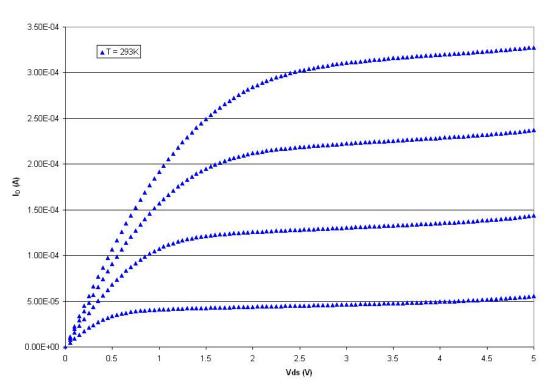

Figure 19:  $I_D$  versus  $V_{DS}$  family of curves at 293K (Device B)

Figure 18 and Figure 19 show the  $I_D$  versus  $V_{DS}$  families of curves for 37K and room temperature (293K), respectively. The current shows a similar increase as in the previous functionality test. In addition, Figure 18 shows that the MOSFET is functioning properly and producing a standard family of curves at 37K. Similar curves were obtained at other temperatures throughout the range of interest. For the sake of comparison, several of these curves are plotted together in Figure 20.

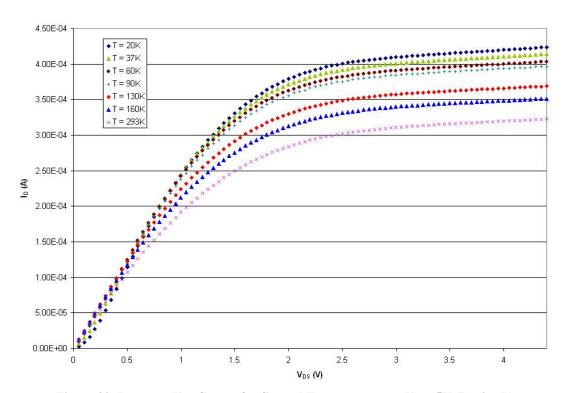

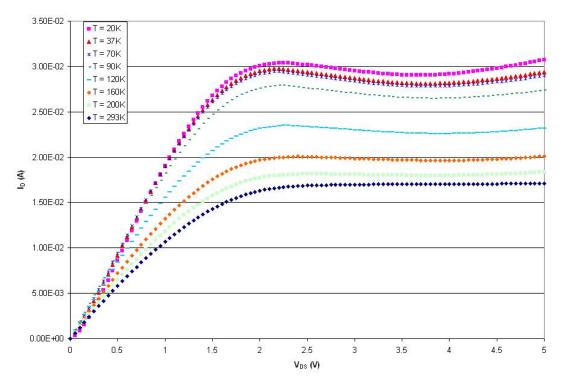

Figure 20:  $I_D$  versus  $V_{DS}$  Curves for Several Temperatures at  $V_G$  = 5V (Device B)

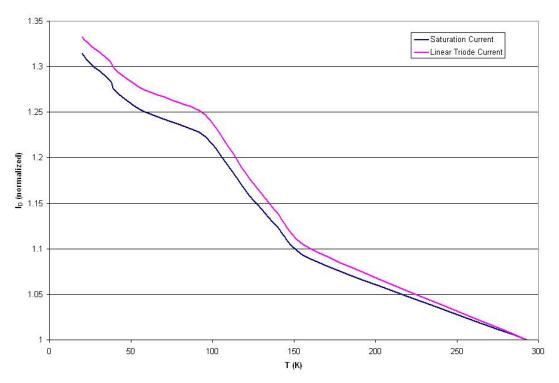

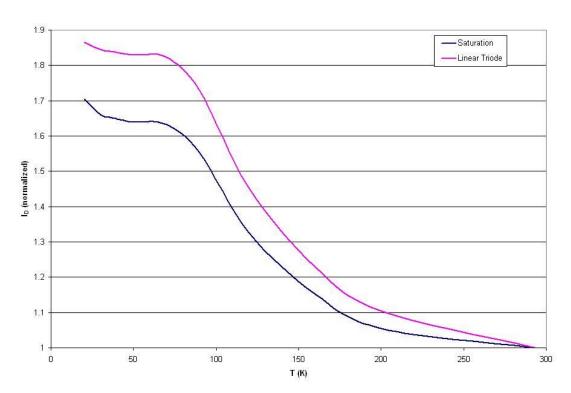

Figure 21:  $I_D$  versus T Curves for linear and saturation regions (Device B). Current is normalized to 1 at room temperature to show rate of increase.

Figure 20 shows of  $I_D$  versus  $V_{DS}$  curves at  $V_{GS}$ =5V for several different temperatures (some temperature measurements are omitted for clarity in this figure, but all are incorporated into Figure 21). This plot demonstrates that proper device behavior is occurring over the entire temperature range. The data from Figure 20, as well as the measurements taken at all other temperatures, is used to compare current versus temperature in the saturation ( $V_{DS}$ =4.5V,  $V_{G}$ =5V) and linear triode ( $V_{DS}$ =2V,  $V_{G}$ =5V) regions of operation (Figure 21). In this figure, the current has been normalized to 1 at 293K by dividing all measured currents by the current value at room temperature (for the same region of operation). This plot shows the percent increase in current from room temperature provides a convenient basis for comparison. It is apparent from Figure 21 that current in the linear region has a very

similar temperature dependence to that in the saturation region, indicating that channel pinch-off does not significantly affect  $dI_D/dT$ . This data set was key to this research, and as was discussed in the objectives section of chapter one, it did provide the basis for the development of a low temperature, physics based simulator. The development of the simulator was a collaboration of the characterization work performed here and the modeling efforts of Dr. Akin Akturk (University of Maryland). The development of the model and resulting simulations will be explained in detail in Appendix A.

The second MOSFET tested in this fashion (device C) was fabricated using the same process as devices A and B, but had a width of 200µm and a length of 6µm, making it much larger than the two previous devices. The large width of this transistor caused it to source much larger amounts of current, resulting in significant self-heating. Device C was tested in the same manner as device B to see how a larger device would perform at low temperature. The results of this test, which provided valuable insight into self heating effects, are shown below.

Figure 22:  $I_D$  versus  $V_{DS}$  curves for several temperatures at  $V_G = 3V$  (Device C)

Figure 22 shows the  $I_D$  versus  $V_{DS}$  family of curves for device C (the large "power" device) at several temperatures. At first glance, it appears as if the device is malfunctioning due to the decrease in current as the transistor enters saturation. Upon closer inspection, however, it becomes apparent this current "dip" is very pronounced at lower temperatures, but gradually disappears as temperature increases up to room temperature. This decrease in current after the device saturates is associated with self heating effects, which can be explained in the following manner. First, it is clear from Figure 14, Figure 21, and Figure 23 (below) that MOSFET current decreases with increasing temperature. In the linear region of operation, there is less current flowing through the device and therefore a smaller amount of heat is generated. In addition, the rate of change  $dI_D/dV_{DS}$  is much larger in this region than in saturation. Thus, as  $V_{DS}$  is swept through the linear region, the increase in current due to increasing

voltage dominates over any potential decreases in current due to self heating. When the transistor reaches saturation, however, there is a greater current flowing through it, and hence a greater amount of heat is produced. Also,  $dI_D/dV_{DS}$  in this region is significantly reduced. As a result,  $dI_D/dV_{DS}$  no longer dominates over  $dI_D/dT$  (selfheating), and the transient self heating effects shown in Figure 22 are observed. Eventually, device temperature stabilizes and current begins to increase.

Figure 23:  $I_D$  versus T curves for linear and saturation Regions (Device C). Current is normalized to 1 at room temperature to show rate of increase.

Figure 23 shows the current versus temperature curves for device C in the saturation ( $V_{DS} = 4V$ ,  $V_G = 3V$ ) and linear triode ( $V_{DS} = 1.5V$ ,  $V_G = 3V$ ) regions of operation. Once again, the current has been normalized by dividing all measured currents for a given region of operation by the current value at room temperature for

that region. As with the smaller device, the two curves are very similar, but there is a larger discrepancy between current in the linear triode and saturation regions. The greater increase in linear triode current is attributed to self heating effects, which counteract the increase in saturation current at lower temperatures.

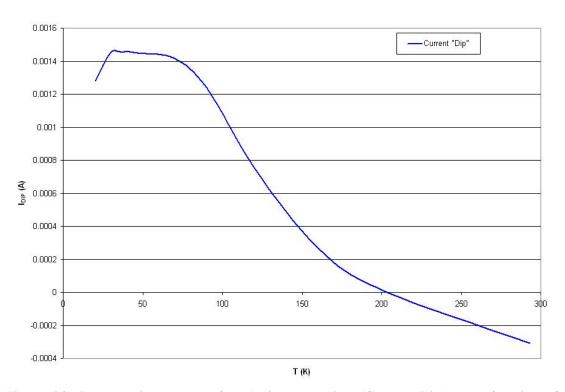

As a final method of analyzing this data, the transient self heating effects shown in Figure 24 were quantified by examining the reduction in voltage after the transistor reached saturation. For each measured temperature, the minimum current in the saturation region was subtracted from the current value at the edge of saturation. The result of this calculation is the "current dip" due to self heating effects. Current reduction as a function of measurement temperature is shown below in Figure 24.

Figure 24: Decrease in current after device saturation (Current Dip) as a function of temperature (Device C)

At temperatures near 300K, the current dip is negative, indicating (as one would expect) that there was no decrease in current due to self heating at these temperatures. As temperature decreases, the current dip becomes positive and increases as well, indicating a rise in self heating. At the lowest measured temperatures (near 20K), the current dip levels off and slightly decreases. This may seem counterintuitive, but it is most likely a reflection of the MOSFET current versus temperature curve. At very low temperatures, self heating moves the curve across the region where increased impurity scatterings have caused the current to level off. Increasing the temperature of the device through this region results in a smaller decrease in current than would occur if the device were heated into the region where current decreases at a faster rate. Thus, although self heating may be greater at lower temperatures, this does not directly translate into greater decreases in current. It is apparent from this analysis that while large transistors can be used at low temperature, self heating effects must be considered to accurately model device performance.

As an additional step in the transistor characterization efforts of this research, the current versus temperature characteristics of devices fabricated in different processes were measured examine temperature dependent current effects in processes other than AMI 0.5µm. Two additional MOSFETs were tested, including a small IBM 0.13µm device with a width/length ratio of 2/1 (device D), and a commercial device fabricated by On Semiconductor (part number MC14007UB, device E). Size information was not available for the commercial device, but it sourced a greater amount of current than device B by a factor of approximately 10 and less current than

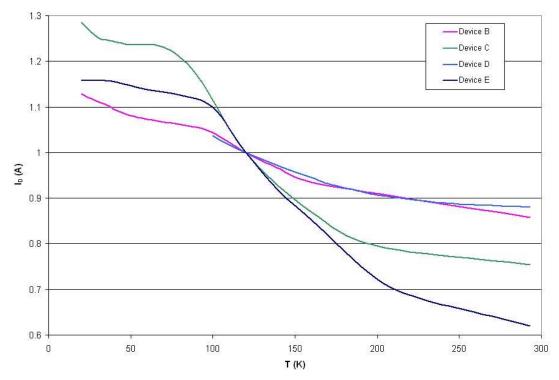

device C by a factor of approximately five. Thus, it was reasonable to assume that device E had an intermediate width/length ratio in between that of the very small and very large AMI devices. The results of testing these additional devices, as well as the earlier results from the AMI devices are shown below in Figure 25.

Figure 25: Saturation  $I_D$  versus T curves for several MOSFET devices. Current is normalized to 1 at T=120K to emphasize the rate of change at higher and lower temperatures.

In Figure 25, it is clear that the current through each MOSFET device increases with temperature and each curve seems to follow the same general trend, although rates of increase are different. It should be noted that the IBM device suffered ESD failure as a result of necessary disconnections and reconnections during the cool down process (the device was fabricated without any form of ESD protection), leading to the incomplete data set shown. The currents in this plot have

been normalized around 120K to emphasize the rate of change at higher and lower temperatures. Below 120K, the rate of increase in current appears to be positively correlated with transistor size, as evidenced by the curves for devices B, C, and E. At higher temperatures, this trend continues for the AMI devices, and is supported by the data for the small IBM transistor, which closely matches that of the minimum size AMI device. The commercial MOSFET, however, sees a faster drop off in current with increasing temperature than even the large AMI device, indicating that this device is more susceptible to electron-phonon scattering. It can be concluded from this discussion that the rate of change in device current as a function of temperature is both size and process dependent, and thus, different processes must be individually modeled at low temperature. Furthermore, successful designs must also include a detailed thermal model of device performance.

#### 3.2 BJT Characterization

### 3.2.1 Motivation and Test Procedure

The doping dependent incomplete ionization models discussed in chapter one suggest that high levels of doping decrease activation energies and allow for impurity band conduction, thus improving device performance at low temperature. Silicon bipolar junction transistors are dependent on a relatively lightly doped base region to provide current drive, making them highly susceptible to incomplete ionization effects. This effect reduces the number of available mobile carriers at low temperature, making the BJT a poor choice for cryogenic applications. As a control experiment, a commercial BJT was tested at low temperature. The device used was a commercial silicon NPN transistor, part number P2N2222A. The goal of this

experiment was to characterize silicon BJT performance at low temperature and determine if the lower doping inherent to this device would indeed cause it to freeze-out when cooled, thus supporting the theory of impurity dependent activation energies.

The bipolar junction transistor was tested using a similar procedure as that used for the MOSFET devices. First, the device was soldered to the board inside the test Dewar and the package was affixed to the board using aluminum tape to maximize thermal conduction as shown in Figure 7. The base, emitter, and collector terminals were wired out and connected to the source measurement units of the 4156B via the personality board shown in Figure 16. The parameter analyzer was set to produce a family of  $I_C$  versus  $V_{CE}$  curves by sweeping  $V_{CE}$  from 0-1V at base currents of 10, 20, 30, 40, and 50 $\mu$ A. The test Dewar was then slowly cooled and I-V measurements were recorded in the same manner as with the MOSFET devices.

#### 3.2.2 BJT Test Results

The results of the low temperature BJT test are shown on the following page:

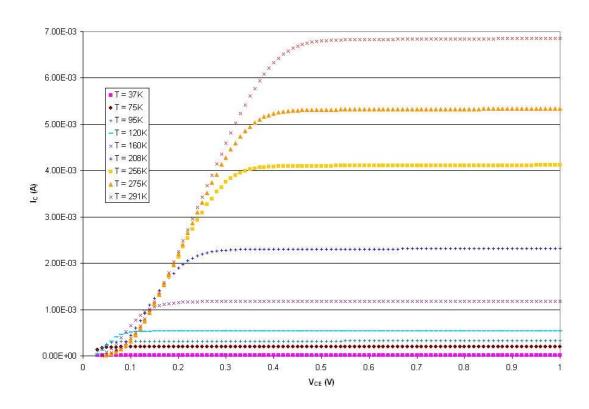

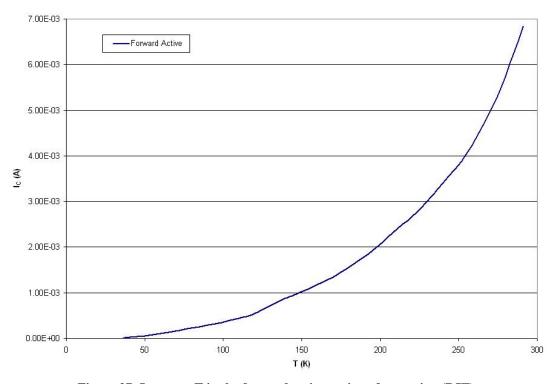

Figure 26:  $I_{C}$  versus  $V_{CE}$  Curves for several temperatures at  $I_{B}$  = 50 $\mu A$  (BJT)

Figure 27:  $I_{\text{\scriptsize C}}$  versus T in the forward active region of operation (BJT)

Figure 26 shows  $I_C$  versus  $V_{CE}$  curves at several different temperatures with base drive current set at 50 $\mu$ A. The I-V curves for this device follow an opposite trend as those for the MOSFET devices. This is accentuated by Figure 27, which plots collector current versus temperature in the forward active region of operation ( $I_B$  = 50 $\mu$ A,  $V_{CE}$  = 1V). As is clear from both of the figures above, the BJT exhibited very poor low temperature performance. At room temperature, the device has a current gain ( $\beta$ ) of approximately 140. A relatively small reduction in temperature to 240K reduced  $\beta$  by a factor of two. At the NASA target temperature of 37K,  $\beta$  was approximately 0.1, rendering the device essentially useless. This test confirmed the theory that standard silicon bipolar junction transistors are not suitable for use at cryogenic temperatures.

It should be pointed out that the component studied, while an industry standard, has been in process for almost 20 years. Base doping is relatively low  $(<10^{18})$  and freeze-out is clearly a possibility.

# 3.3 MOSFET NOISE Analysis

### 3.3.1 Motivation

Although not the primary focus of this research, it was important to explore noise performance in order to make the claim that overall MOSFET device performance is better at low temperature. If increases in current were accompanied by increases in noise at low temperature, then MOSFETs might not be a viable low temperature solution. Thus, a spectrum analysis was conducted to determine noise performance

# 3.3.2 Test Setup and Measurement Process

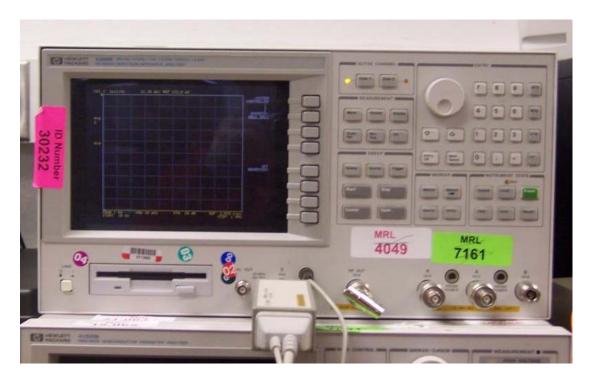

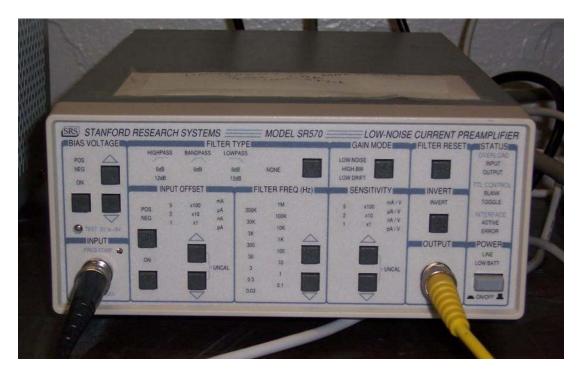

To test transistor noise, a spectrum analyzer was employed along with a low-noise current preamplifier. The spectrum analyzer was used to measure transistor noise as a function of frequency. The current preamplifier was used to source a low-noise drain current through the MOSFET device. These devices are shown below in Figure 28 and Figure 29.

Figure 28: HP4396B Spectrum Analyzer

Figure 29: Stanford Research Systems SR570 Low-Noise Current Preamplifier

The spectrum analyzer was connected to the preamplifier using an Agilent 41800A active probe, shown connected to the spectrum analyzer in Figure 28. A buffer was placed in between the two instruments to protect sensitive equipment. The preamplifier was set to source a small amount of current through the drain of device C, and the gate and source terminals were connected to 3V and ground, respectively. The schematic for this test setup is shown below.

Figure 30: Schematic of MOSFET noise test setup

Since the noise test had a running time of approximately two hours, the Dewar was modified to increase hold time and maintain temperature stability. Small brass standoffs were used instead of copper standoffs as described in chapter two and a heater was mounted on the test board. The heater used was a 5W,  $40\Omega$ , wire wound resistor, housed in aluminum casing with a flat base to maximize heat transfer. The two terminals of the resistor were connected to the temperature controller as shown in Figure 30. In Figure 31, the heater is the gold-colored item mounted to the bottom-middle section of the board. Note that this picture is just to show how the heater was mounted to the board; the two terminals of the resistor had not yet been wired out of the test Dewar, nor had the brass standoffs been installed.

Figure 31: Resistive heater mounted on test board (bottom-middle)

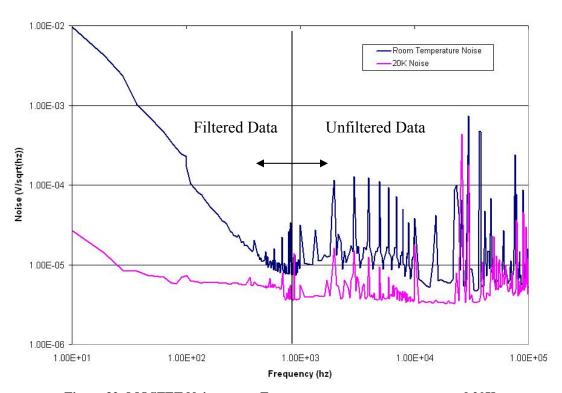

Once all components were properly installed, the test Dewar was cooled to using the technique described in chapter two. Using the GPIB controller, the Lakeshore 340 was programmed with the heater resistance and power rating, as well as the desired system temperature. This information, along with the temperature read by the thermal diode, was used by the instrument to program a proportional-integral-derivative (PID) feedback control, which stabilizes the DUT at the desired temperature. When the temperature reached 20K, the heater switched on and stabilized the system. The drain current and gate bias were then turned on and a frequency sweep from 10Hz to 100kHz was conducted using the spectrum analyzer. As a basis for comparison, the same test was also run at room temperature. Since a low noise environment was unavailable for this test, the results were fed through a

software filter to remove 60Hz harmonics. The software filter functioned by first dividing all measured frequencies by 60 and then filtering out the data point closest to each integer value. Due to the relatively few number of data points taken per decade, this filter could only be applied to frequencies less than 1kHz. Application at higher frequencies would have resulted in the filtering of arbitrary data points. This is evidenced by the results shown in Figure 32, where the data is much cleaner at low frequency.

#### 3.3.3 Results

The results of the noise test are shown below. At low frequencies, where the 60Hz harmonics have been filtered out, it is clear that flicker (1/f) noise is significantly reduced at low temperature. Specifically, at 10Hz, the noise figure decreases by a factor of 200. At higher frequencies, for reasons explained above, the data is contaminated by outside noise sources and cannot be filtered. Nonetheless, it appears that the noise floor at high frequencies is lower at for the 20K measurement than for the room temperature measurement. Despite the non-ideal conditions for this experiment, it can be concluded from the data that low frequency (1/f) noise performance is significantly better at 20K than at room temperature. At higher frequencies, noise performance at low temperature seems to improve, and at the very least is no worse than room temperature noise.