**ABSTRACT**

Title of Document: ANALOG VLSI CIRCUITS FOR

BIOSENSORS, NEURAL SIGNAL PROCESSING AND PROSTHETICS.

Alfred M. Haas

Doctor of Philosophy, 2009

Directed By: Professor Martin Peckerar,

Department of Electrical and Computer

Engineering

Stroke, spinal cord injury and neurodegenerative diseases such as ALS and Parkinson's debilitate their victims by suffocating, cleaving communication between, and/or poisoning entire populations of geographically correlated neurons. Although the damage associated with such injury or disease is typically irreversible, recent advances in implantable neural prosthetic devices offer hope for the restoration of lost sensory, cognitive and motor functions by remapping those functions onto healthy cortical regions. The research presented in this thesis is directed toward developing enabling technology for totally implantable neural prosthetics that could one day restore lost sensory, cognitive and motor function to the victims of debilitating neural injury or disease.

There are three principal components to this work. First, novel integrated biosensors have been designed and implemented to transduce weak extra-cellular

electrical potentials and optical signals from cells cultured directly on the surface of the sensor chips, as well as to manipulate cells on the surface of these chips. Second, a method of detecting and identifying stereotyped neural signals, or action potentials, has been mapped into silicon circuits which operate at very low power levels suitable for implantation. Third, as one step towards the development of cognitive neural implants, a learning silicon synapse has been implemented and a neural network application demonstrated.

The original contributions of this dissertation include:

- A contact image sensor that adapts to background light intensity and can asynchronously detect statistically significant optical events in real-time;

- Programmable electrode arrays for enhanced electrophysiological recording,

for directing cellular growth, for site-specific *in situ* bio-functionalization, and

for analyte and particulate collection;

- Ultra-low power, programmable floating gate template matching circuits for the detection and classification of neural action potentials;

- A two transistor synapse that exhibits spike timing dependent plasticity and can implement adaptive pattern classification and silicon learning.

# ANALOG VLSI CIRCUITS FOR BIOSENSORS, NEURAL SIGNAL PROCESSING AND PROSTHETICS

By

#### Alfred M. Haas

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2009

Advisory Committee: Professor Martin Peckerar, Chair Joel Cohen Nicholas DeClaris Neil Goldsman Robert Newcomb © Copyright by Alfred M. Haas 2009

### Dedication

I dedicate this thesis to my family, to whom I owe everything.

## Acknowledgements

To everyone who has supported me, I thank you all.

### Table of Contents

| Dedication.                                            | ii  |

|--------------------------------------------------------|-----|

| Acknowledgements                                       | iii |

| Table of Contents                                      | iv  |

| List of Figures                                        | vi  |

| Chapter 1: Introduction                                | 1   |

| 1.1 Overview.                                          | 1   |

| 1.2 Research Contributions                             | 2   |

| Chapter 2: Contact Imaging                             | 5   |

| 2.1 Integrated Image Sensors                           | 5   |

| 2.1.1 Active Pixel Sensors.                            | 6   |

| 2.1.2 Contact Imaging.                                 | 13  |

| 2.2 Biosensing.                                        | 18  |

| 2.2.1 Sensing Cells                                    | 19  |

| 2.2.2 Sensing Biological Activity                      | 25  |

| Chapter 3: Neural Recording.                           | 36  |

| 3.1 Neural Signals                                     | 36  |

| 3.1.1 Neurophysiology                                  | 38  |

| 3.1.2 Modeling Neural Action Potentials                | 41  |

| 3.1.3 Conventional Neural Recording                    | 43  |

| 3.2 Integrated Electrode Arrays                        | 49  |

| 3.2.1 Neurite Outgrowth                                | 51  |

| 3.2.2 Programmable Electrode Arrays                    | 56  |

| A. Programmable High Density CMOS Microelectrode Array | 57  |

| B. Galvanotropism                                      | 62  |

| C. Other Applications.                                 | 67  |

| <u>3.3 EMG</u>                                         | 68  |

| Chapter 4: Spike Sorting                               | 70  |

| 4.1 Mixed Signal Stochastic Computation                | 73  |

| 4.1.1 Analog VLSI                                      | 74  |

| 4.1.2 Low Power Design.                          | 74  |

|--------------------------------------------------|-----|

| 4.1.3 Floating Gate Basics.                      | 76  |

| A. Floating Gate Adaptation                      | 76  |

| B. Multiple Input Translinear Elements ("MITEs") | 78  |

| 4.2 Spike Sorting Literature Review.             | 81  |

| 4.2.1. Spike Sorting Methods and Algorithms      | 81  |

| A. Summaries and Reviews                         | 81  |

| B. Template Matching.                            | 85  |

| C. Wavelet and Multiresolution Analysis          | 86  |

| D. Neural Network Classifiers.                   | 88  |

| E. Automated and Unsupervised.                   | 89  |

| F. Neural Prosthetics.                           | 91  |

| 4.2.2 Spike Sorting Circuits                     | 92  |

| 4.3 Floating Gate Template Matching              | 105 |

| 4.3.1 Detecting Neural Action Potentials         | 107 |

| 4.3.2 Sorting Neural Spikes.                     | 112 |

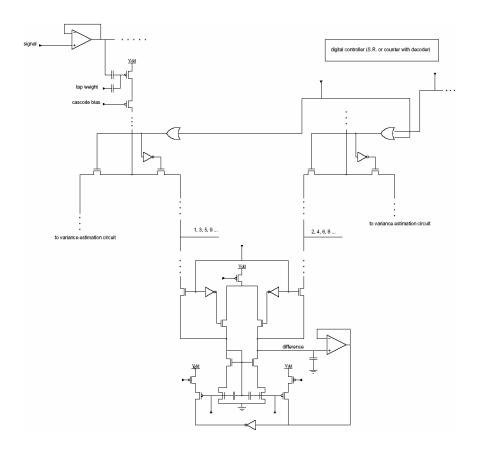

| A. Floating Gate Template Matching Filter Bank   | 112 |

| B. Variance Estimation Circuit.                  | 124 |

| C. Classification Block                          | 132 |

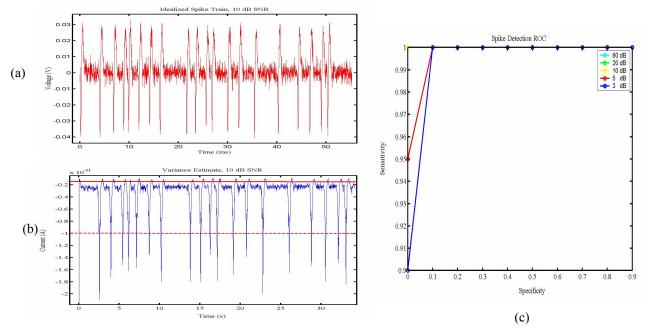

| 4.3.3 System Performance.                        | 132 |

| Chapter 5: 2TS                                   | 135 |

| 5.1 Two Transistor Synapse with STDP             | 135 |

| 5.2 Neural Network Implementation                | 145 |

| Chapter 6: Conclusions                           | 150 |

| Bibliography                                     | 152 |

# List of Figures

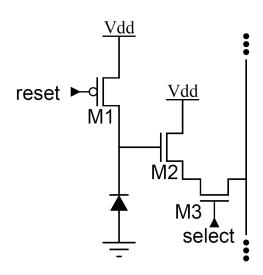

| 2.1  | Schematic of typical 3-transistor ("3T") active pixel sensor ("APS")                                                                                                      | 7    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

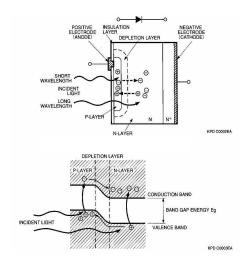

| 2.2  | Photodiode physical cross-section (top) and energy band diagram (bottom). [25]                                                                                            | 9    |

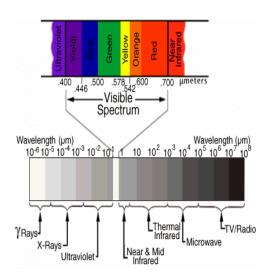

| 2.3  | Electromagnetic spectrum. [26]                                                                                                                                            | 9    |

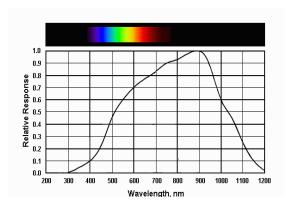

| 2.4  | Typical silicon photodiode spectral responsivity. [28]                                                                                                                    | . 11 |

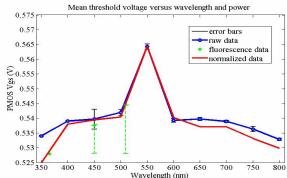

| 2.5  | Measured spectral responsivity for the n-APS sensor. Blue curve represents raw data; bottom represents measured intensity. Each data point is the mean of 50 trials. [11] | . 11 |

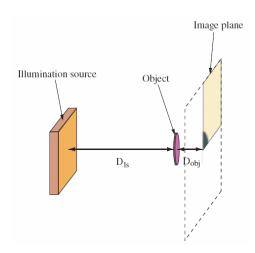

| 2.6  | Schematic of theoretically modeled contact imaging system. [8]                                                                                                            | . 14 |

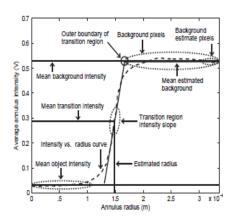

| 2.7  | Plot of average annulus intensity as a function of radius, illustrating the computation of contrast parameters. [8]                                                       | 14   |

| 2.8  | Simulated contact images of a quarter disk formed on image planes at: (a) 1 $\mu$ m, (b) 240 $\mu$ m, and (c) 500 $\mu$ m away from the disk [8].                         | 16   |

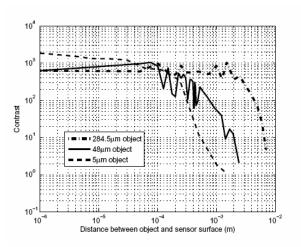

| 2.8  | Simulated image contrast as a function of distance between the object disk and sensor surface. [8]                                                                        | 16   |

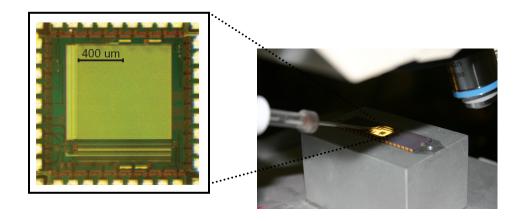

| 2.10 | Photomicrograph of fabricated image sensor, [8], alongside a photograph of experimental contact imaging setup with micropipette, light source and chip shown.             | . 16 |

| 2.11 | Measured images of a 284.5 um bead formed on image planes at (a) 1 μm, (b) 1950 μm, and (c) 3950 μm away from imager surface. [8]                                         | 17   |

| 2.12 | Image contrast as a function of increasing D from simulation (5μm) and experimental results (48 and 284.5 μm). [8]                                                        | 17   |

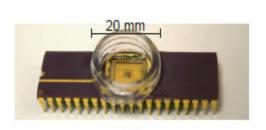

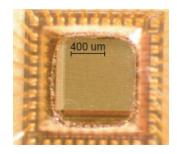

| 2.13 | Photographs of (a) test fixture ready for cell plating, and (b) a close-up view of packaged contact imager. [8]                                                           | 20   |

| 2.14 | Pictures of live cells coupled to chip surface are taken using (a) a camera and (b) the contact imager. The overlapped view is shown in (c). [8], [9]                     | 20   |

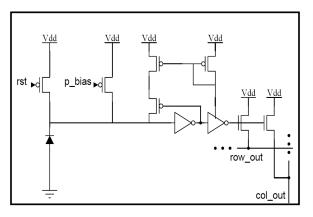

| 2.15 | principle of operation. Incident light generates a photocurrent that discharges the photodiode junction capacitance, while an opposing, user-tuned, current source supplements the thermal (dark) current and charges the node. [10]                                                                                                                                                                   | 22 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.16 | (a) Non-adaptive APS ("n-APS") source follower output in response to slow changes in ambient light intensity (30s total time scale); (b) n-APS digital output in response to slow changes in ambient light intensity. Plateaus represent periods of static ambient light intensity, while high voltages represent dark or occluded signals, and low voltages represent the incident light. [10], [11]. | 24 |

| 2.17 | Jablonski diagram, [34]                                                                                                                                                                                                                                                                                                                                                                                | 26 |

| 2.18 | Stokes shift and principles of fluorescence detection                                                                                                                                                                                                                                                                                                                                                  | 26 |

| 2.19 | Photomicrograph of n-APS sensor array, shaded with a drawn blue filter.                                                                                                                                                                                                                                                                                                                                | 26 |

| 2.20 | Principle of adaptive thresholding. [11]                                                                                                                                                                                                                                                                                                                                                               | 30 |

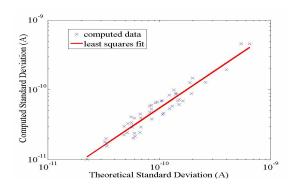

| 2.21 | Computed standard deviation from measured variance estimation circuit data. [11]                                                                                                                                                                                                                                                                                                                       | 30 |

| 2.22 | a-APS sensor. [11]                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

| 2.23 | Simulated single a-APS spike. [11]                                                                                                                                                                                                                                                                                                                                                                     | 31 |

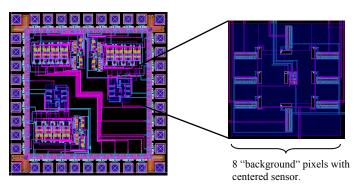

| 2.24 | Layout of two a-APS sensors and one standard deviation circuit, [12]                                                                                                                                                                                                                                                                                                                                   | 32 |

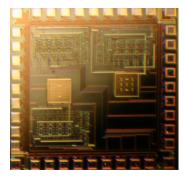

| 2.25 | Photomicrograph of fabricated image sensor, [12]                                                                                                                                                                                                                                                                                                                                                       | 32 |

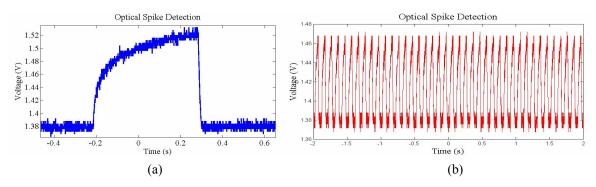

| 2.26 | Measured data from the a-APS when uniformly illuminated with a pulsed blue LED. (a) single spike measured at 1 Hz; (b) spike train measured at 10 Hz, [11]                                                                                                                                                                                                                                             | 32 |

| 2.27 | Laser experimental setup, including 633 nm class II laser, chopper wheel, prototype board and sensor                                                                                                                                                                                                                                                                                                   | 33 |

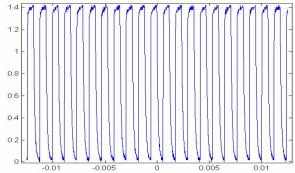

| 2.28 | Measured data from the a-APS when red laser light (633 nm) is focused directly onto the sense pixel and chopped at 1 kHz                                                                                                                                                                                                                                                                               | 33 |

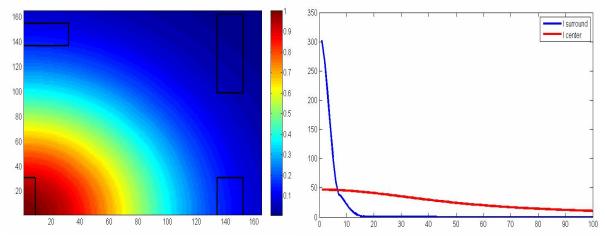

| 2.29 | function of position in the upper right quadrant of the image plane. Black boxes mark the locations of the pixels, the pseudo-color gradient reflects the relative intensity, with red normalized to one and blue approaching zero | .34  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.30 | Simulated center versus surround current intensities as a function of the spread or focus of the laser light. Units on the x-axis represent signal spread; the y-axis is proportional to the photocurrent.                         | 34   |

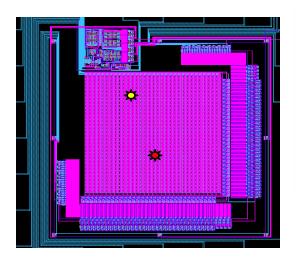

| 2.31 | Layout of 32 x 32 a-APS imager array with adaptive thresholding and arbitrated AER readout. Yellow and red suns indicate optical events                                                                                            | .35  |

| 2.32 | Simulated AER readout from four optical events. Event timing is represented by the shaded color-coded columns                                                                                                                      | 35   |

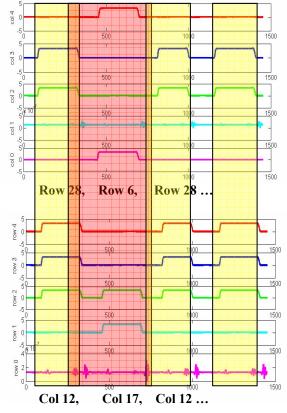

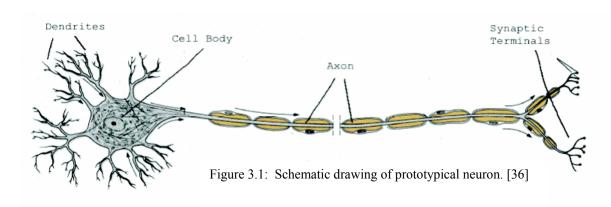

| 3.1  | Schematic drawing of prototypical neuron. [36]                                                                                                                                                                                     | . 38 |

| 3.2  | First published AP recording, 1939. [36]                                                                                                                                                                                           | 39   |

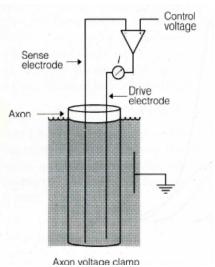

| 3.3  | Voltage clamp apparatus drawing. [45]                                                                                                                                                                                              | 39   |

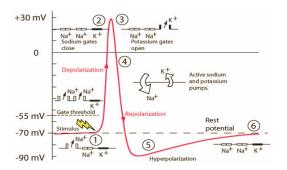

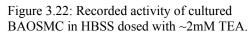

| 3.4  | Action potential as a function of ion channel activity. [46]                                                                                                                                                                       | 4    |

| 3.5  | Action potential as a function of Na <sup>+</sup> and K <sup>+</sup> channel conductances. [36]                                                                                                                                    | 4    |

| 3.6  | Hodgkin-Huxley cell membrane model. [47]                                                                                                                                                                                           | 42   |

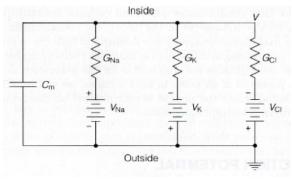

| 3.7  | (a) Real action potentials versus silicon neuron APs [12];<br>(b) PSPICE simulations                                                                                                                                               | 43   |

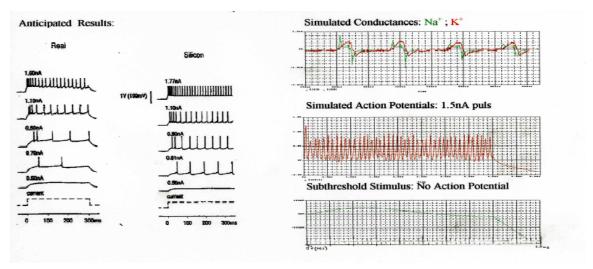

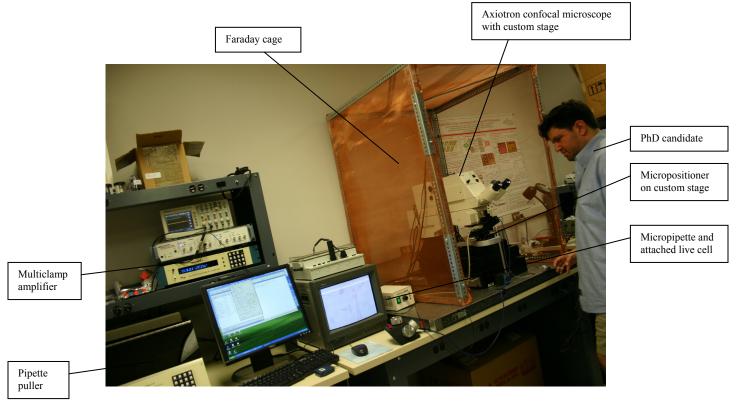

| 3.8  | Author performing a whole-cell patch-clamp experiment using the custom-built rig                                                                                                                                                   | 45   |

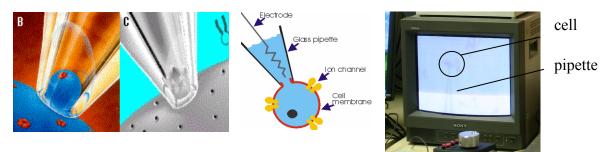

| 3.9  | Cartoons of the whole-cell patch clamping procedure. [62][63]                                                                                                                                                                      | 46   |

| 3.10 | Video capture of whole-cell patch-clamp experiment                                                                                                                                                                                 | 46   |

| 3.11 | Seal test on BAOSM cell.                                                                                                                                                                                                           | 46   |

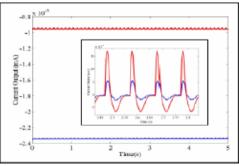

| 3.12 | Whole cell patch-clamp recording from cultured BAOSM cells                                                                                                                                                                         | 4    |

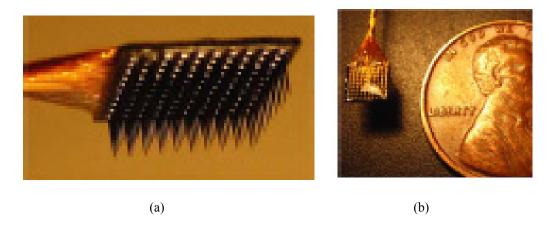

| 3.13 | (a) "Utah" microelectrode array; (b) Utah array next to penny for comparison. [56]                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

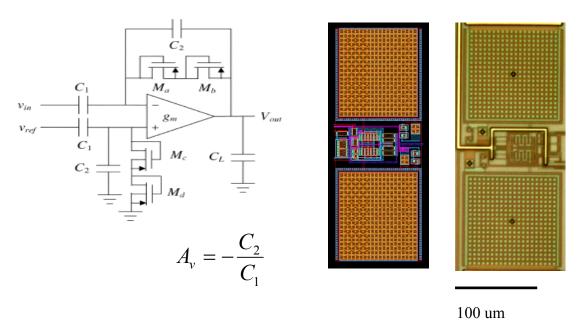

| 3.14 | Harrison bioamplifier schematic. [57]                                                                                                                                                            |

| 3.15 | Haas scaled version layout and photomicrograph                                                                                                                                                   |

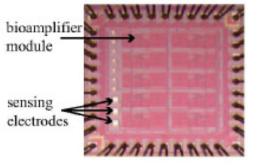

| 3.16 | Array of first generation scaled bioamplifiers, [12]51                                                                                                                                           |

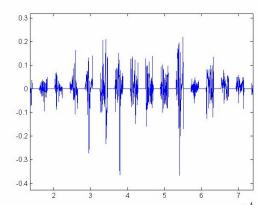

| 3.17 | Recorded signals from cultured BAOSMC, on one channel, and across all eight channels. [12]                                                                                                       |

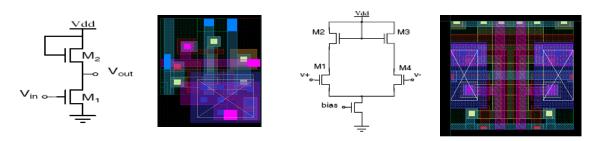

| 3.18 | (a) single-ended common-source pre-amplifier schematic and layout; (b) differential common-source preamplifier schematic and layout                                                              |

| 3.19 | Bench-testing apparatus for probing microelectrodes using signal generator                                                                                                                       |

| 3.20 | Data from single-ended pre-amplifier, fed by arbitrary waveform generator and buffered by bioamplifier from [12]53                                                                               |

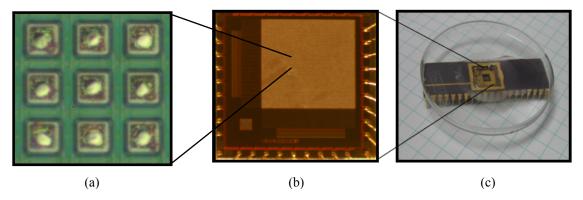

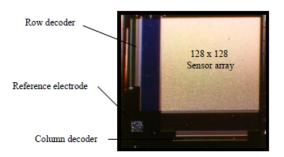

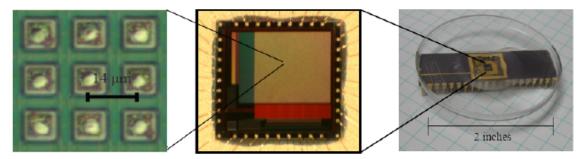

| 3.21 | Left, photograph of electrolessly plated planar commercially cut electrodes; center, photomicrograph of fabricated 128x128 differential sensor array; right, packaged electrode array            |

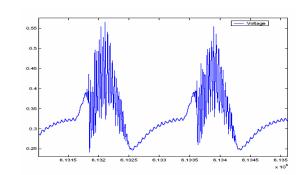

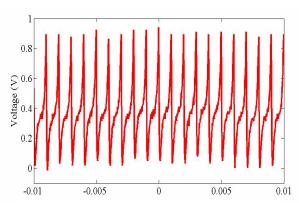

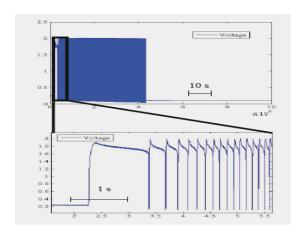

| 3.22 | Recorded activity of cultured BAOSMC in HBSS dosed with ~2mM TEA                                                                                                                                 |

| 3.23 | Stereotyped cardiac action potential. [61]                                                                                                                                                       |

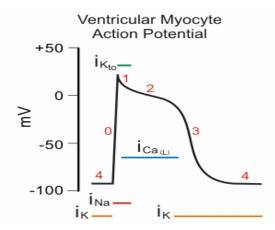

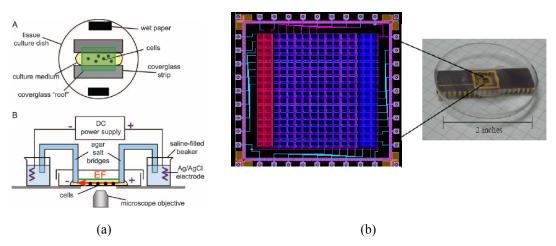

| 3.24 | Schematic, layout and fabricated 128 x 128 array of programmable electrodes                                                                                                                      |

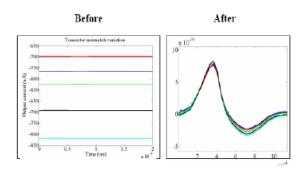

| 3.25 | Before: simulated swamp the signal; After: the offsets are mathematically removed                                                                                                                |

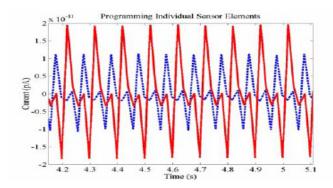

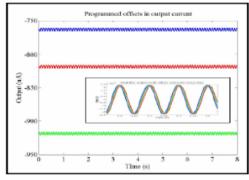

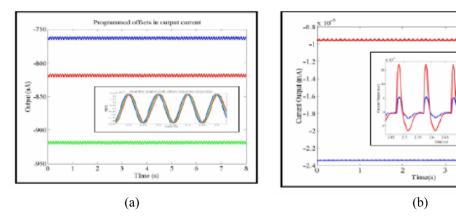

| 3.26 | Programming arbitrary offsets onto floating gates in order to shift I-V curves and tune gain. Within each box, input signals are identical. Inlays show signals with DC offsets subtracted. [13] |

| 3.27 | Sensor array element before and after programming the floating node by injection. Both gain and offset are affected. [13]61                                                                      |

| 3.28 | pitch and die size to the fabricated sensors, plated and packaged                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.29 | (a) Typical set-up for two electrode galvanotropism, [72]; (b) layout of fabricated 16 x 16 array for performing arbitrary field pattern galvanotropism, and photograph of typical bio-packaging                     |

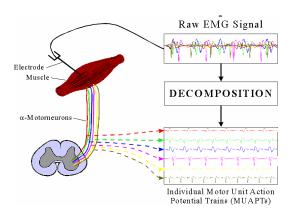

| 3.30 | Basic principles of EMG acquisition and signal decomposition. [76] 69                                                                                                                                                |

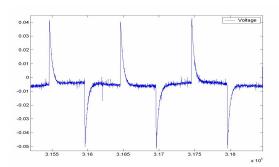

| 3.31 | Surface-EMG recording from calf-muscle                                                                                                                                                                               |

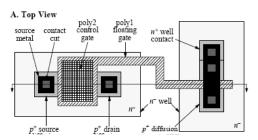

| 4.1  | Floating gate layout with control, injection and tunneling nodes. [19]77                                                                                                                                             |

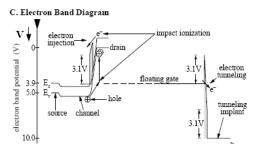

| 4.2  | Schematic of injection and tunneling mechanisms. [19]                                                                                                                                                                |

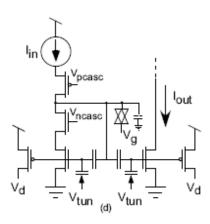

| 4.3  | Floating gate schematic with differential injection and tunneling nodes. [149]                                                                                                                                       |

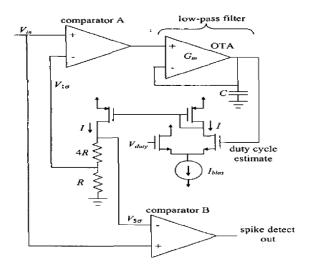

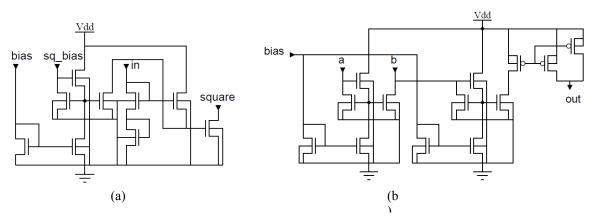

| 4.4  | Multiple input translinear element ("MITE") current squaring circuit. [158]                                                                                                                                          |

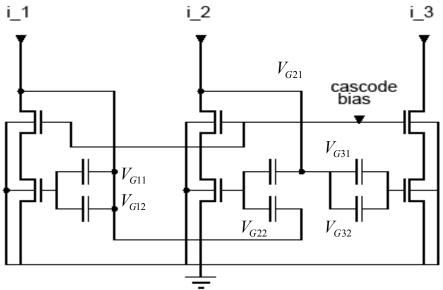

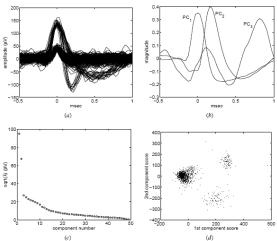

| 4.5  | Lewicki's PCA analysis [106]: (a) shows raw data; (b) illustrates the first three principal components; (c) provides the standard deviation of the scores for each component; and (d) clusters the component scores. |

| 4.6  | Gaussian clustering by Lewicki [106]; (a) shows the Bayesian decision boundaries for the four clusters; (b) shows the same data with nine clusters                                                                   |

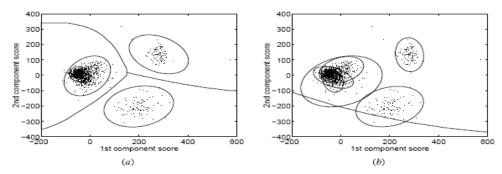

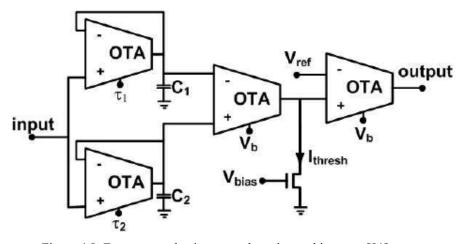

| 4.7  | Harrison's adaptive threshold detection circuit. [102]                                                                                                                                                               |

| 4.8  | Frequency selective onset detection architecture. [91]                                                                                                                                                               |

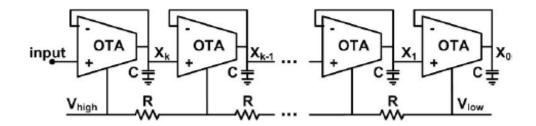

| 4.9  | Gm-C filter bank for implementing analog wavelet transform. [152]99                                                                                                                                                  |

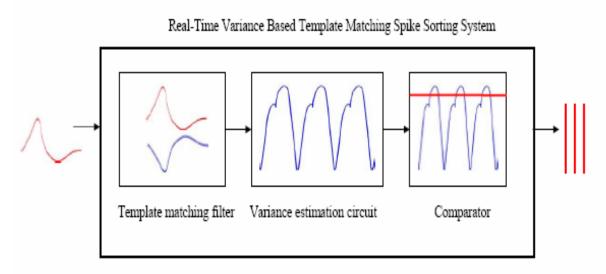

| 4.10 | System-level diagram of the floating gate template matching spike sorting system                                                                                                                                     |

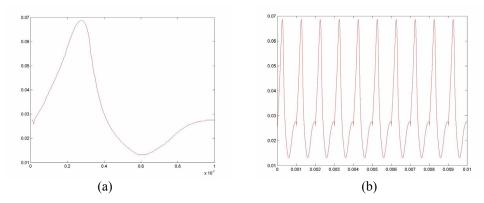

| 4.11 | (a) left: Schematic drawing of neural action potential; (b) right: spike train consisting of cascade of simulated action potentials                                                                                  |

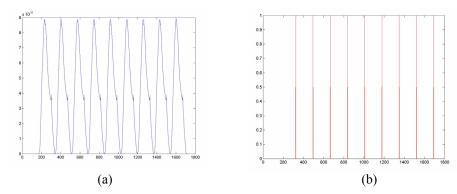

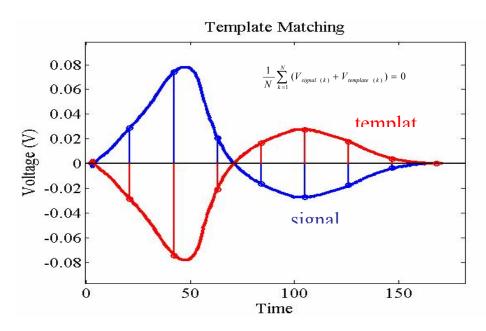

| 4.12 | (a) left: MATLAB simulated output of the floating                                                                                                                                                                    |

| _    | emplate matching variance estimator; (b) right: pulse-train e each event corresponds with a template match                                                                                     | 107 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

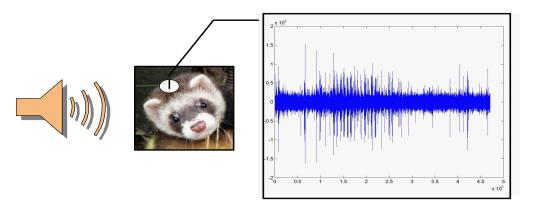

| 4.13 | Neural signals obtained from the NSL and schematic representation of recording apparatus.                                                                                                      | 108 |

| 4.14 | (a) simulated spike train with 10 dB SNR; (b) variance circuit estimate with user defined thresholds; (c) spike detection ROC using template matching threshold                                | 110 |

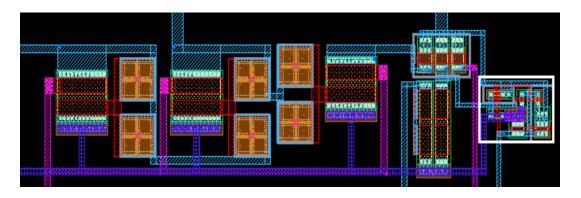

| 4.15 | First generation spike detector layout                                                                                                                                                         | 111 |

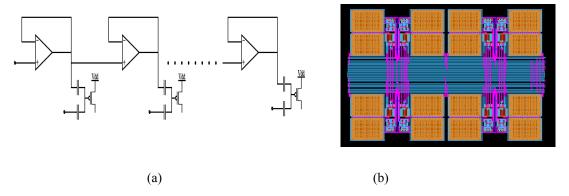

| 4.16 | Schematic of the N (=8) point template matching method                                                                                                                                         | 113 |

| 4.17 | (a) schematic of floating gate filter bank for neural signal decomposition; (b) layout of filter                                                                                               | 114 |

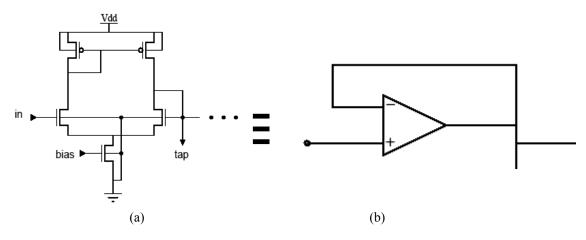

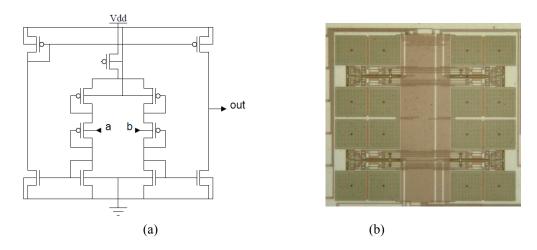

| 4.18 | (a) schematic of conventional OTA in unity gain configuration; (b) symbolic view.                                                                                                              | 115 |

| 4.19 | <ul><li>(a) schematic of wide-linear range OTA with low g<sub>m</sub> [159];</li><li>(b) fabricated filter bank incorporating filters</li></ul>                                                | 115 |

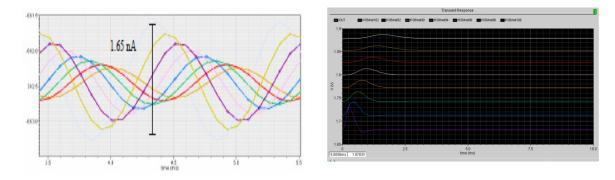

| 4.20 | (a) simulated transient data for 1 kHz sinusoidal input asserted onto the first generation filter bank; (b) reflects the propagation of a transient spike across the taps of the WLR OTA       | 116 |

| 4.21 | (a) Direct measurement of voltage signals from floating gate taps; (b) current amplitude response of single slowly varying tap. In both cases, inferred current outputs are on the order of nA | 117 |

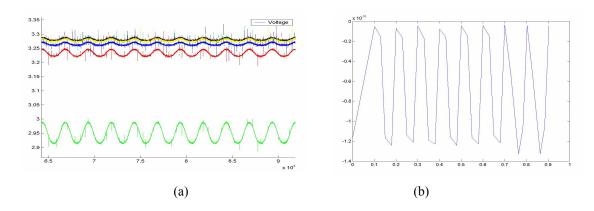

| 4.22 | Modulating the current output of a fabricated filter bank tap by adjusting the capacitively coupled DC control bias                                                                            | 118 |

| 4.23 | Schematic illustrating proposed method of mismatch correction                                                                                                                                  | 119 |

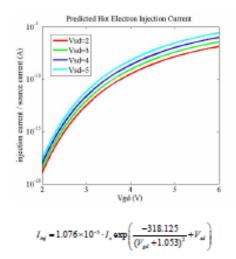

| 4.24 | Theoretical hot electron injection currents based on Rahimi model and with experimentally fitted parameters                                                                                    | 121 |

| 4.25 | High-level schematic of programming mechanism. Comparison between desired and measured current drives injection or tunneling.                                                                  | 121 |

| 4.26 | Programming arbitrary offsets onto floating gates in order to shift I-V curves and tune gain. Within each box, input signals are identical. Inlays show signals with DC offsets subtracted | 121 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

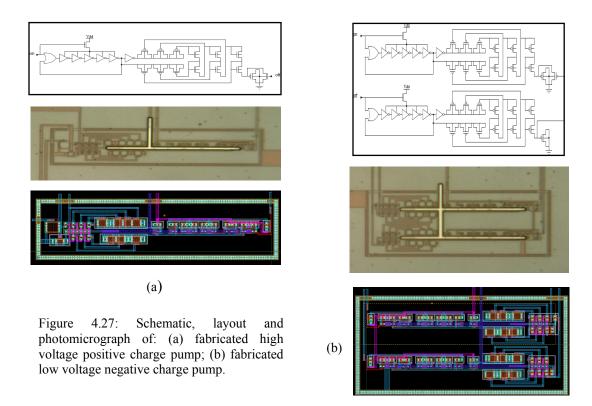

| 4.27 | Schematic, layout and photomicrograph of: (a) fabricated high voltage positive charge pump; (b) fabricated low voltage negative charge pump.                                               | 122 |

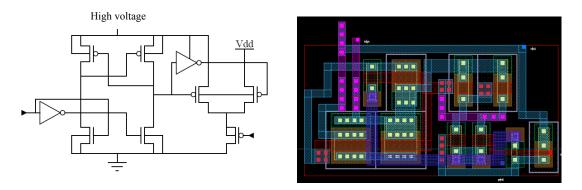

| 4.28 | Schematic and layout for a fabricated set of high voltage switches                                                                                                                         | 123 |

| 4.29 | Schematic and layout for a fabricated Traff current comparator, [160].                                                                                                                     | 123 |

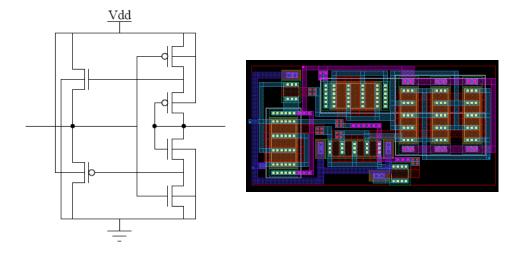

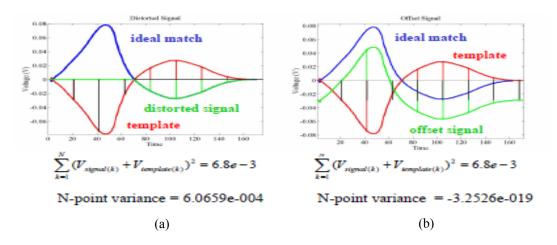

| 4.30 | Computed variance estimates for the distance between  (a) a distorted signal and the stored template; and  (b) an offset signal and the stored template.                                   | 125 |

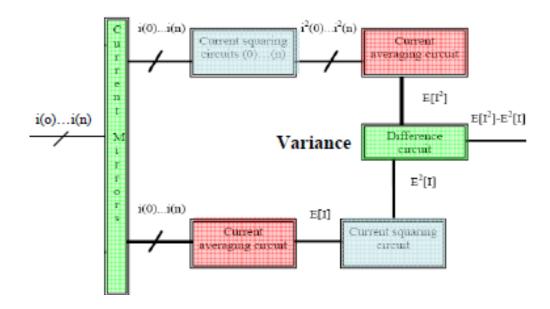

| 4.31 | Block diagram of variance estimation circuit                                                                                                                                               | 125 |

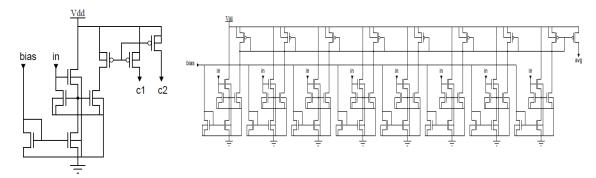

| 4.32 | Ultra-low-current current mirror                                                                                                                                                           | 127 |

| 4.33 | Second generation current averaging circuit                                                                                                                                                | 127 |

| 4.34 | <ul><li>(a) second generation subthreshold squaring circuit;</li><li>(b) second generation current subtraction circuit.</li></ul>                                                          | 128 |

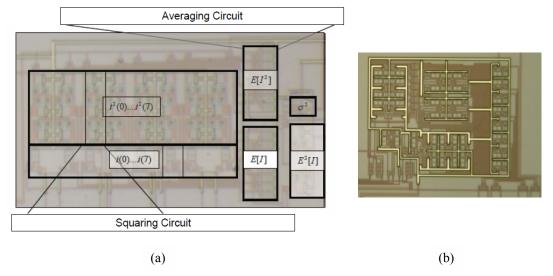

| 4.35 | (a) Labeled photomicrograph of first generation variance estimation circuit; (b) bare photomicrograph of fabricated second generation circuit.                                             | 128 |

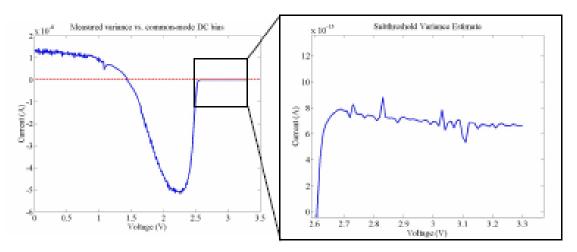

| 4.36 | DC response of first generation variance estimation circuit                                                                                                                                | 129 |

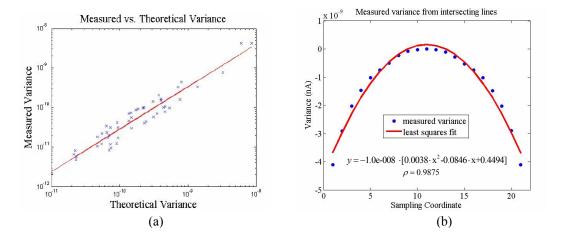

| 4.37 | Measured versus theoretically computed variance estimates. In (a) inputs are random; $p=0.96$ ; in (b) inputs are converging (intersecting) linear currents, red line is fit               | 130 |

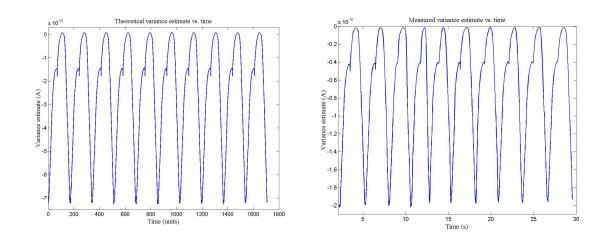

| 4.38 | Theoretical and measured response of variance estimation circuit to MATLAB simulated output of floating gate filter bank to artificial neural spike train.                                 | 131 |

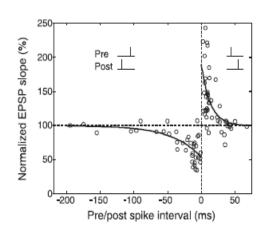

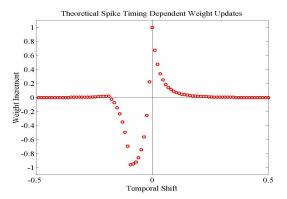

| 5.1  | Biological spike timing dependent plasticity. [162], [163]                                                                                                                                 | 135 |

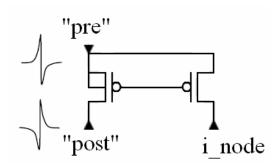

| 5.2  | Schematic of the two-transistor synapse with illustrative "pre" and "post" waveforms                                                                                                       | 137 |

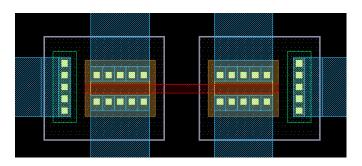

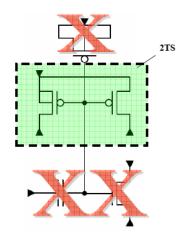

| 5.3  | Physical layout of a 2TS in a commercial 0.5 μm process                                                                                                                                                                      | 139 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Ideal discrete PRE and POST synaptic spike waveforms                                                                                                                                                                         | 142 |

| 5.5  | Simulated STDP as a function of biphasic mirror-image input waveforms. Computed weight update is shown in red                                                                                                                | 142 |

| 5.6  | Equivalent, but differently-sized, 2TS test structure                                                                                                                                                                        | 143 |

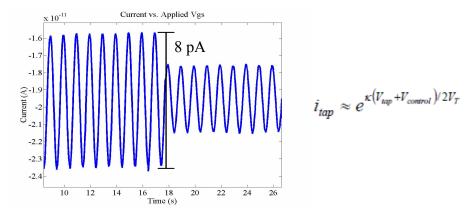

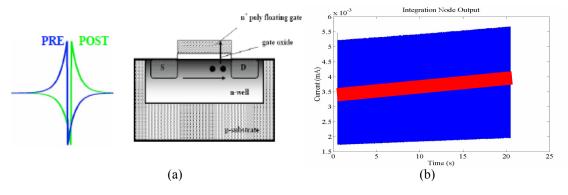

| 5.7  | (a) Cartoon of "pre"-"post" overlap for potentiation and hot electron injection weight update; (b) Measured output of circuit integration node as a function of successive positive weight updates. Trend line shown in red. | 143 |

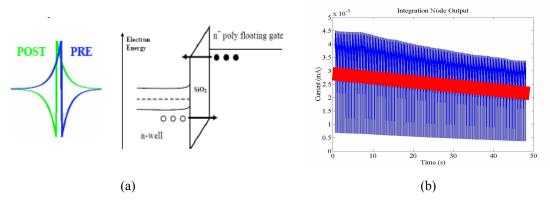

| 5.8  | (a) Cartoon of "pre"-"post" overlap for depression and FN tunneling weight update; (b) Measured output of circuit integration node as a function of successive negative weight updates. Trend line shown in red              | 144 |

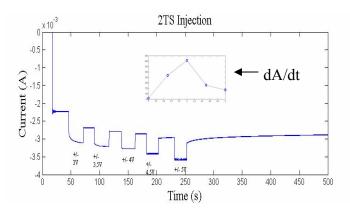

| 5.9  | 2TS current increases owing to successive hot electron injection weight updates. Inlay shows dA/dt for each pulsed drain voltage asserted.                                                                                   | 145 |

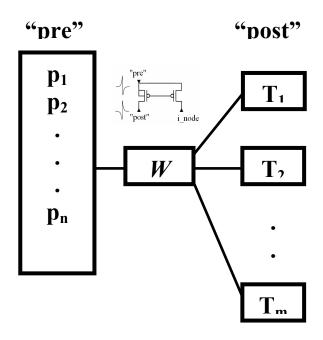

| 5.10 | Block diagram of Hebbian learning system based on 2TS as synapse                                                                                                                                                             | 146 |

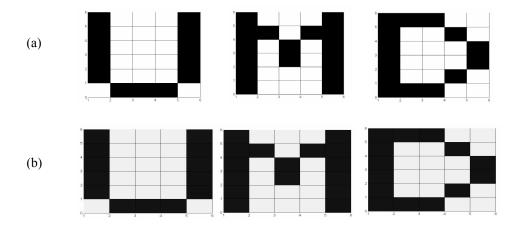

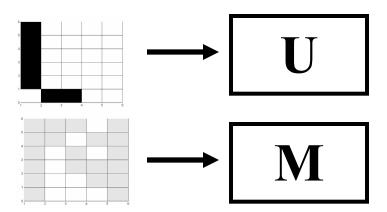

| 5.11 | (a) graphical plot of ideal template; (b) plot of noisy programmed template                                                                                                                                                  | 148 |

| 5.12 | Two examples of pattern recognition using the trained In the first, a partial letter is correctly identified. In the second, a noisy and attenuated letter is also correctly identified by the trained network.              | 148 |

#### Chapter 1: Introduction

#### 1.1 Overview

Stroke, spinal cord injury and neurodegenerative diseases such as ALS and Parkinson's debilitate their victims by suffocating [1], cleaving communication between [2], and/or poisoning [3], entire populations of geographically correlated neurons. Although the damage associated with such injury or disease is typically irreversible, recent advances in implantable neural prosthetic devices offer hope for the restoration of lost sensory, cognitive and motor functions by remapping those functions onto healthy cortical regions [4]. These prosthetics are remarkable devices, yet for most of these state of the art systems, neural event detection and classification systems remain external; and most implants still consume too much power and occupy too much space to reliably resolve neural events across multiple channels simultaneously [5], [6]. To truly restore lost sensory, cognitive and motor function to victims of debilitating neural injury or disease, a totally implantable neural prosthetic is required [7]. The principal aim of my research, therefore, has been to develop enabling technology for such prosthetics and the rehabilitation of lost sensory, cognitive and motor function.

In order to meet this ambitious aim, I have taken a multi-tiered approach. In one aspect of this research, I studied existing technology and developed novel integrated biosensors for electrophysiological recording and optical sensing of neural activity. In another, I designed, fabricated and characterized ultra-low-power circuits for detecting, extracting the salient features from, and identifying the source of neural action potentials. Finally, in an attempt to build technology for closed-loop

unsupervised control, I implemented a new silicon synapse capable of correlating signals for Hebbian learning. In developing these circuits and systems, I have addressed some of the key limitations of previous generations of biosensor and implantable signal processing architectures – power consumption and reliable encoding of neural data – and I offer some novel approaches for next generation implantable prosthetic devices.

#### 1.2 Research Contributions

This thesis is divided into four technical Chapters, 2-5, which detail the original contributions of this work and provide the context to appreciate the significance of these contributions to the field.

Chapter 2, entitled Contact Imaging, introduces integrated active pixel sensors ("APS") for imaging biological activity, such as neural action potentials. In this chapter, we introduce and lay the theoretical foundations for a deeper understanding of the advantages and limitations of integrated contact imaging [8], and show the simulated and experimentally verified performance of fabricated contact image sensors [8], [9], [10], [11]. The original contributions of this thesis described in this chapter include the design, fabrication and characterization of a contact image sensor that adapts to background light intensity and can asynchronously detect statistically significant optical events in real-time. The architecture of this adaptive sensor ("a-APS") is presented along with experimental data [11], and we disclose an array of a-APS sensors with arbitrated AER readout for asynchronous (and unsupervised) neural spike detection that has also been designed, simulated and submitted for fabrication.

Chapter 3, entitled Neural Recording, details the historical evolution of neural recording techniques and demonstrates the experimental performance of several state-of-the-art integrated microelectrode arrays designed to interface with, manipulate and record from living biological cells and systems [12], [13]. The original contributions of this thesis described in this chapter include the design, fabrication and characterization of programmable electrode arrays for enhanced electrophysiological recording, for directing cellular growth, for site-specific *in situ* bio-functionalization, and for analyte and particulate collection. Fabricated programmable arrays for compensating electrode and amplifier mismatch, process variation and local environmental inhomogeneities have been characterized [13]. When properly packaged, these arrays are suitable for *in vitro* neural recording and also for integration with implantable recording and signal processing devices. Moreover, a variant of these arrays can be used to pattern arbitrary potentials across the sensor surface for directing the growth of developing and possibly damaged nerve cells.

Chapter 4, entitled Spike Sorting, is divided into three parts. First, we provide a concise primer on the relevant aspects of mixed-signal VLSI design. Second, we perform an in-depth review of state-of-the-art spike sorting algorithms and circuits. Finally, we detail the architecture and performance of the ultra-low-power floating gate template matching circuits I designed for the detection and classification of neural action potentials [14]. The original contributions of this thesis described in this chapter include: (a) the overall floating gate template matching architecture; (b) application of floating gate adaptation and template matching to solve the detection and classification problem under competing constraints of low-power dissipation and

high computational precision; (c) novel on-chip variance estimation circuitry; (d) novel asynchronous current-mode weight-update circuits; (e) unique silicon neuron template generation mechanism; and (f) a VLSI implementation of a theoretical non-linear energy operator ("NEO") to threshold incoming signals for unsupervised template generation. Together, these contributions represent a significant step down the path toward next generation neural prosthetics.

Finally, in Chapter 5, entitled The Two Transistor Synapse, we consider biological Hebbian learning, explore a new analog circuit architecture for implementing biologically realistic learning (the two transistor synapse, "2TS"), and conclude with an illustrative pattern recognition application. The original contributions of this thesis described in this chapter include the development and implementation of a novel two transistor synapse that exhibits spike timing dependent plasticity and can implement adaptive pattern classification and silicon learning. This silicon synapse [15], provides the foundation for unsupervised silicon learning which could one day be used for the closed-loop control of implantable neural prosthetics.

### Chapter 2: Contact Imaging

In this Chapter, we introduce, lay the theoretical foundations for and demonstrate the experimental performance of integrated contact image sensors for biosensing applications. Original contributions of this thesis to the field include the design, fabrication and characterization of a contact image sensor that adapts to background light intensity and can asynchronously detect statistically significant optical events in real-time.

#### 2.1 Integrated Image Sensors

Since the late 16<sup>th</sup> century we have been using microscopes as a window into a world that remains hidden to the naked eye [16]. Powerful optical lenses and submicrometer precision stages provide an unparalleled view of the molecules, structures and biological organisms that populate that world – microscopes enable us to elucidate surface chemistries [17], to characterize deadly pathogens [18], and to visualize the very mechanisms of conscious thought [19]. However, for all the marvels that modern microscopes can conjure, ownership and operation of these instruments is costly in more ways than one. Conventional "light" microscopes are heavy and take up large volumes of space, e.g. [20]. While this is an overhead that is fine for research, it is a price that first responders in the field and prosthetics engineers cannot tolerate. In the modern era, diagnostic, therapeutic and rehabilitative applications that have historically been anchored to the instruments must be untethered and allowed to follow the need.

Necessity breeds innovation, and forty years after Smith, Boyle and Thompsett first shaped silicon sands into a charge-coupled array for storing patterns of light and dark projected onto the focal plane [21], today's engineers have developed the technology to integrate tens of millions of tiny photosensors onto a silicon chip the size of a fingernail, e.g. [22]. As a result, state-of-the art telecommunications devices can transduce full frame images into a bitstream of millions of 1's and 0's in a fraction of a second [23]. Removing the lenses from such systems and coupling microscopic particles or biological cells directly to the integrated sensor surface, it is possible to leverage the myriad advantages of integrated circuit technology – low cost and power consumption, high speed, and advanced focal plane processing – with the superior efficiency and reduced footprint of imaging systems that do not require the overhead of intervening optics. What follows is an introduction to integrated contact image sensors, and the theoretical and experimentally established performance of such sensors.

#### 2.1.1 Active Pixel Sensors

Although there are many different means of transducing light into electrical signals, we shall focus on the active pixel sensor ("APS"), which is broadly defined as an integrated photodetector and amplifier. Arrays of APS's fabricated in today's standard complementary metal oxide semiconductor ("CMOS") technology can be read out orders of magnitude faster and more efficiently than the charge-coupled devices ("CCD") first fabricated in the early 1970's, compare e.g. the sensors reported in [24] with the technology in [21]. CMOS offers the additional advantages of reliable, low cost manufacturing and the ability to integrate photosensors with

advanced image plane processing on the same chip. The prototypical APS constitutes a reverse biased, or "pinned", photodiode and source-follower readout transistor. A schematic of a typical 3-transistor ("3T") CMOS APS is shown in Fig. 2.1 below.

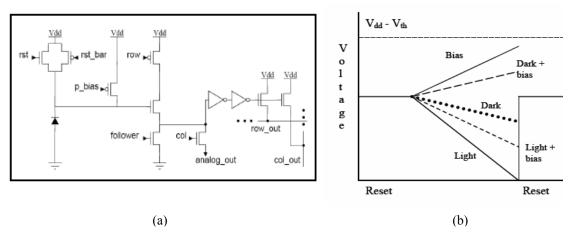

In this particular configuration, PMOS transistor M1 is operated as a switch that resets the voltage at the gate of the source-follower, M2, to Vdd when the rst signal is asserted. Incident light (photon flux) generates charge carriers (electron-hole pairs) in the depletion region of the reverse-biased photodiode, and the carriers that do not recombine internally are swept across the

Figure 2.1: Schematic of typical 3-transistor ("3T") active pixel sensor ("APS").

photodiode junctions, resulting in a photocurrent that tends to discharge the photodiode junction capacitance to ground. Transistor M2 is a source-follower single transistor amplifier whose output voltage is proportional to the voltage at its gate, which is equivalently the voltage across the photodiode junction capacitance. M3 is a simple switch that permits the voltage at the source of M2 to be read out on a common bus.

Under ideal conditions, assuming a perfectly linear photodiode junction capacitance and uniform illumination, we would expect both the photocurrent, I, and the photodiode junction capacitance, C, to remain relatively constant, so that according to the characteristic equation:  $I = C \frac{dV}{dt}$ , we would observe the change in voltage over time to be roughly linear. This holds true to first order approximation

even though the photodiode junction capacitance is not truly linear. Instead it is a function of photodiode junction width, which is proportional to the square root of the difference between the built-in potential and the voltage across the diode, as is shown in Equations 2.1 & 2.2, below:

$$C_{diode\_junction} \approx \frac{\varepsilon_{silicon} \cdot A_{diode}}{X_{diode\_depletion}}$$

(2.1)

$$X_{diode\_depletion} \approx \sqrt{\frac{2\varepsilon}{q} \left(\frac{N_A + N_D}{N_A N_D}\right) (V_{reverse\_bias} - \Phi_0)}$$

(2.2)

In these equations,  $C_{diode\_junction}$  represents the photodiode junction capacitance,  $\varepsilon_{silicon}$  is the permittivity of silicon,  $A_{diode}$  is the exposed area of the photodiode,  $X_{diode\_depletion}$  is the diode depletion region depth, q is the charge on a single electron,  $1.6 \times 10^{-19} \, \text{A}$ ,  $N_A$  and  $N_D$  respectively represent the acceptor and donor concentrations of the p- and n- type silicon regions of our photodiodes,  $V_{reverse\_bias}$  is the external voltage drop across the photodiode, and  $\Phi_0$  represents the built-in-potential. The voltage drop across the photodiode, in turn, depends on both the reset bias voltage and illumination conditions which give rise to photocurrents that tend to discharge the photodiode junction capacitance. However, for nearly all illumination conditions, dV is so small during the integration period (the time between reset and readout) that the dependency may be relegated to a second-order effect.

Figure 2.2 shows a schematic of a photodiode in a standard, single-well CMOS process. The p-type substrate ("p-sub") is silicon that has been doped with a

group-III acceptor such as Boron, while the n-well has been doped with an electron rich group-V donor such as Arsenic or Phosphorous. As with a typical diode junction, in the absence of any applied electric field across the diode, electrons from the donor atoms on the n-type side will tend to migrate across the junction to fill the vacancies in the group-III acceptors on p-type side. This results in unmasked positive atomic cores on the n-type side and filled valence shells on the p-type side that form the depletion region.

Figure 2.2: Photodiode physical cross-section (top) and energy band diagram (bottom). [25]

Figure 2.3: Electromagnetic spectrum. [26]

Free charge carriers do not reside in the depletion region, as the built-in potential reflected in the potential energy diagram shown in Fig. 2.2, sweeps them away. The depletion region as bounded by the charged atomic cores acts as a parasitic capacitor in parallel with the photodiode. It is this parasitic capacitance which is charged and discharged by the photocurrent, and thus gives rise to a proportional voltage change across the photodiode. Under reverse bias, the depletion

region is extended and free carriers tend to get swept across the junction if they do not first recombine with each other.

Photocurrents occur when incident photons impart sufficient energy to the doped silicon to generate electron-hole pairs – i.e., when photons impart sufficient energy to valence electrons to jump the 1.12eV bandgap to the conduction band. Since the wavelength and energy, or frequency, of electromagnetic radiation are inversely proportional ( $c=\lambda v$ ), UV, visible and near-IR all possess such energy, see Fig. 2.3, but electromagnetic radiation with a wavelength greater than about 1100 nm, such as microwaves and radio frequencies, do not and therefore cannot generate photocurrents in Si. The reason for this is described simply by Planck's law:  $E = hf = \frac{hc}{\lambda} = \frac{1240_{nm}}{\lambda_{nm}} eV$ , where h is Planck's constant, 6.626 x  $10^{-34} kgm^2/s$ , c is the speed of light,  $3 \times 10^8$  m/s, and 1 eV is  $1.6 \times 10^{-19}$  J. Given the 1.12 eV indirect bandgap of silicon, individual photons of light with  $\lambda > (1240/1.12)$ , or approximately 1100 nm (IR), do not possess the requisite energy to, by themselves, excite electrons to the conduction band. If the incident light intensity is high - e.g. with a laser excitation source, it is possible for two higher wavelength, lower energy photons to impact the same atom at the same time to generate electron-hole pairs, and a corresponding photocurrent, but absent high intensity collimated laser light, this occurrence is a rarity.

However, using longer wavelength, lower frequency laser radiation, scientists can probe deeper into tissues with less damage – 2-photon microscopy is a very useful technique [27]. Finally, with respect to the spectral responsivity of silicon – light with a wavelength below about 300 nm does not penetrate the photodiode as

deeply and tends to recombine before it reaches the depletion region to be turned into photocurrent; likewise some much higher frequency (lower wavelength) radiation, such as x-rays, can pass through silicon without being substantially detected at all.

The ratio of electrons collected to incident photons at a given wavelength is referred to as the detective quantum efficiency ("DQE")<sup>1</sup>. Theoretically DQE can approach unity, but for a standard CMOS APS fabricated in a commercial 0.5um process, owing to material imperfections that give rise to local recombination, thermal carrier generation that can become conflated with small photocurrents, and electrical noise, the observed DQE over the visible wavelengths is on the order of 0.33. The spectral responsivity ("SR") reflects the relative DQE of a photosensor at different wavelengths, normalized for optical power. A characteristic silicon photodiode SR curve is shown in Fig. 2.4, alongside measured data from a fabricated APS, shown in Fig. 2.5. Note that the shape of the experimentally observed data on the right, shown in blue, closely parallels the optical power curve, shown in red. Thus when normalized, the experimentally characterized APS SR is relatively flat.

Figure 2.4: Typical silicon photodiode spectral responsivity. [28]

Figure 2.5: Measured spectral responsivity for the n-APS sensor. Blue curve represents raw data; bottom represents measured intensity. Each data point is the mean of 50 trials. [11]

<sup>&</sup>lt;sup>1</sup> As contrasted with quantum efficiency ("QE") which we use to refer to the number of electron-hole pairs generated by a single incident photon.

The disparity between the characteristic and experimentally observed data is in part a function of the sensitivity of the fabricated photodiode with respect to the dark current noise floor - note that the minimum mean threshold voltage recorded is approximately 527 mV (for the filtered fluorescent light), separated from the highest peak by less than 10% or 38 mV; it is in part proportional to the accuracy and precision of the readout and data acquisition hardware – measured mean threshold voltages are proportional to the photocurrent, but do not represent a direct current measurement – instead they are the bias voltages at which, over a fixed integration time, the generated bias current overwhelmed the photocurrent (more on this later) and invoked a digital trigger – the imprecision in the readout circuitry is further compounded by the data acquisition system which is capable of controlling the bias voltage with approximately 1-2 mV accuracy; finally, and to a lesser extent, the observed SR is in part due to the precision of the optical test apparatus, including such factors as ambient light leakage, and also the limited precision and reliability of the monochromator light source and optical power meter.

In sum, device physics and circuit design both play an important role in defining the capabilities of integrated CMOS. Physical properties of the photodiode set both the DQE and SR and define the noise floor – i.e., the minimum detectable signal beneath which it is not possible to differentiate between the photocurrent and the current resulting from thermally generated carriers. However, numerous circuit techniques have been reported to reduce dark current and to extend the dynamic range of silicon photodiodes, e.g. [29]; device physics alone does not determine the characteristics of the APS. As seen above, much of the difficulty in designing ultra-

sensitive APS image sensors is in crafting the readout circuitry that will preserve the dynamic range of the signal against circuit imprecision – due to mismatch and process variations – and against noise inherent in analog and mixed-signal designs. We will discuss APS design considerations in greater detail later in this chapter. First, in evaluating the fundamental limits of CMOS APS imagers, we consider the resolution limits of these image sensors independent of any intervening optics – coupling the object or cell to be detected directly to the sensor surface.

#### 2.1.2 Contact Imaging

APS imagers are ubiquitous. They are embedded in every cell phone, PDA and laptop computer on the market, they have replaced CCD's in even high-end digital cameras, and they have supplanted film as the medium of choice for most medical and diagnostic applications. However, these imagers typically employ discrete optical lenses to focus images onto the sensor surface, which adds to the cost, size and complexity of these instruments and makes them unsuitable for applications such as implantable neural imaging [30]. In order to establish the fundamental performance limitations of APS technology, we have investigated and characterized contact imagers capable of visualizing microscopic objects simply by coupling them directly to the sensor surface. These sensors leverage the enhanced collection efficiency that proximity to the sensor provides, and are able to perform functional microscopy without the overhead of intervening optics. In this section, we describe the results of simulations and measurement of CMOS APS imaging response, as published in [8].

In assessing the quality of captured images, we used the contrast of an imaged object – defined in terms of the mean object intensity,  $m_{object}$ , the mean background intensity,  $m_{background}$ , and the background variance,  $\sigma^2 - \text{as } C = \frac{(m_{object} - m_{background})^2}{\sigma^2}$ .

Contrast represents the squared, or power, SNR of the imager and was both simulated and experimentally verified.

Simulations were performed using the commercial software simulator LightTools<sup>TM</sup>, by fixing a 2 mm x 2mm Lambertian light source a uniform distance from a virtual opaque circular disk with diameter of 5 um and thickness of 1 um. The simulated image plane constituted one quarter of a 60 μm x 60 μm 2D array of 4900 square bins, each bin corresponding with a pixel of an image sensor. Fig. 2.6 illustrates the simulated system. Since the simulated image plane captured every photon incident upon it, the stochastic nature of the simulation is a function of the random photon generation of the Lambertian light source.

Figure 2.6: Schematic of theoretically modeled contact imaging system. [8]

Figure 2.7: Plot of average annulus intensity as a function of radius, illustrating the computation of contrast parameters. [8]

In order to quantitatively assess contrast, we needed to specify the regions corresponding to the captured image of the object and the background. We defined the object as comprising all pixels of the simulated image plane within a specified radius of the fixed object center. To ensure that we could reliably segregate background from object, we defined a transition region between the two whose midpoint was determined iteratively by identifying the smallest radius at which the mean value of an annulus two pixels wide was greater than the calculated mean intensity of the transition region. We determined the outer boundary of the transition region by finding the intersection between the line approximating the intensity in the transition region and the estimated background intensity. All pixels outside the transition region are background pixels. The method is illustrated in Fig. 2.7.

Fig. 2.8 represents simulated data for the virtual quarter image plane as a function of increasing object distance from the surface. Notably, even at relatively large distances it is possible to resolve the object with the human eye, a feat that would prove exceedingly difficult for an integrated image processor. Fig. 2.9 illustrates the simulated data across all measured distances; the solid line is the LMS fit between the function  $f(D_{obj}) = \frac{a}{(1 + (\frac{D_{obj}}{d})^n)}$  and the logarithmically weighted

contrast data. For the simulation data shown in Fig. 2.8, a = 1341, the characteristic distance, d = 0.1305 mm, and shape parameter, n = 3.076.

10<sup>3</sup>

Figure 2.8: Simulated contact images of a quarter disk formed on image planes at: (a) 1  $\mu$ m, (b) 240  $\mu$ m, and (c) 500  $\mu$ m away from the disk. [8]

Figure 2.9: Simulated image contrast as a function of distance between the object disk and sensor surface. [8]

In order to measure imager contrast and confirm the theoretical results shown above, we performed two sets of experiments on a 96 x 96 APS, 8.4 µm pitch imager fabricated in a commercial 0.5 µm process.<sup>2</sup> The test setup I devised is shown in Fig. 2.10, alongside the fabricated contact imager.

Figure 2.10: Photomicrograph of fabricated image sensor, [8], alongside a photograph of experimental contact imaging setup with micropipette, light source and chip shown.

<sup>2</sup> This imager array was designed and submitted for fabrication by Mr. Honghao Ji while he was a student at the University of Maryland Department of Electrical and Computer Engineering.

16

For the first experiment that I formulated, we represented the Lambertian surface between the light source and the focal plane using a 48 µm polystyrene microbead; for the second, we employed a 284.5 µm stainless steel microball. In both instances, the microparticles were attached to the tip of a pulled (using a Flaming Brown P-97 micropipette puller) borosilicate pipette with a clear UV-curable polymer, Loctite<sup>TM</sup> 3340. The bead-pipette fixture was then affixed to a Sutter MP-285 micropositioner (at an angle of 29 degrees from the horizontal) and the imager chip and board were then positioned onto a custom stage for an Axiotron microscope. Using the micropositioner, we first aligned the anchored bead to a position near the center of the imager and then raised and lowered the beads to take images at varying distances from the focal plane The sample and imager were illuminated using halogen light provided by the built-in light source of an Axiotron microscope, projected through an empty socket in the nosepiece which was approximately 45 mm above the sensor surface.

Figure 2.11: Measured images of a 284.5 um bead formed on image planes at (a) 1  $\mu$ m, (b) 1950  $\mu$ m, and (c) 3950  $\mu$ m away from imager surface. [8]

Figure 2.12: Image contrast as a function of increasing D from simulation  $(5\mu m)$  and experimental results (48 and 284.5  $\mu m$ ). [8]

The images were analyzed using the algorithm described above, except that the location of the object center was determined by inspection, and we: (a) attempted to reduce fixed pattern noise by subtracting a reference frame containing no bead from the captured data; and (b) cropped four pixels on each edge of the frame to eliminate edge effects. Once these tasks were completed, we computed the contrast ratios for each frame according to the formula provided above. Captured images for the stainless steel microball, as well as compiled data for all experiments and simulations are presented in Figs. 2.11 & 2.12.

For the polystyrene bead (not shown), the fit has amplitude, a=643.1, characteristic distance, d=0.2679 mm, and shape parameter, n=2.150; the metal microbead shown above has a=603.6, d=3.283, and n=5.8087. The characteristic distance at which the contrast begins to degrade increases as the size of the object increases. The higher noise content of the measured images, including the pipette tip and real-world illumination conditions, resulted in an expected but nonetheless significant increase in variance versus theoretical results, accounting in part for the observed discrepancy in contrast values between the three sets of data. Nonetheless, experimentally observed data qualitatively match the theoretical predictions, and proves the paradigm for assessing contact image quality.

#### 2.2 Biosensing

Having explored the device physics, integrated circuit realization and performance of integrated contact image sensors, we next consider contact imagers as biosensors. In particular, we focus on two principal applications: (1) localizing cells and other microscopic particles coupled to the sensor surface for handheld cytometry,

cell sorting and other diagnostic and integrated feedback applications; and (2) detecting optical transients, or spikes, that correspond with, e.g., localized metabolic or neural activity, for identifying pathogens or visualizing cellular neural activity.

#### 2.2.1 Sensing cells

An APS contact imager can detect microscopic particles or biological cells coupled to the sensor surface, provided that the pixel size is on the scale of the particles or cells to be visualized. Numerous integrated APS sensors for biological sensing have been reported, e.g. [8], [9], [11], [30]. A common problem is that cells, being semi-transparent, are difficult to detect without some means of enhancing contrast. Typically, this is accomplished by staining the cells with a dye such as neutral red, which can be introduced into live cells without significantly impacting their health. As an example that we presented in [8], taking a maximum safe dye concentration of 0.1 M, we can use the extinction coefficient for neutral red of 39000 cm-1 M-1 to compute the transmission rate through a 2 µm thick monolayer of stained cells as  $T = 10^{-E_C \cdot conc \cdot l} \approx 0.17$  so that approximately 83% of incident light will be blocked by the cells. Therefore, to register the location of individual cells on the sensor surface, it is simply necessary to identify the dark, or occluded pixels – this forms the foundation of the spike detecting imager that we shall discuss in the next section. The dynamic range of a typical n-well, p-sub APS imager in a commercial 0.5 µm process, is about 54 dB (500:1), [8] allowing us to register 83% occlusion easily.

To demonstrate proof of principle cell localization, it is first necessary to insulate the exposed electrical areas of the packaged chip (bond wires and pads), and

also to keep the biological cells from coming into contact with any electrical connections or toxins. To accomplish both aims, we encapsulate the bondwires with a biocompatible UV-patternable polymer, Loctite 3108 in this case, and affix a custom media well using silicon glue, as is shown in Fig. 2.13 [8].

Figure 2.13: Photographs of (a) test fixture ready for cell plating, and (b) a close-up view of packaged contact imager. [8]

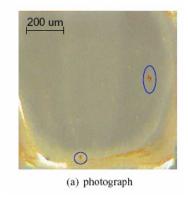

The surface of the chip is washed with deionized water and culture media to remove any harmful residues, and for the experiment whose results are shown in Fig. 2.14, bovine aortic smooth muscle cells ("BAOSMC") that had been stained with neutral red dye were plated onto the surface of the chip. A digital photograph of the sensor surface was taken through a microscope lens, and images were captured using the contact imager. Fig. 2.14 (a) is an enhanced photograph, Fig. 2.14 (b), is the image acquired by the APS sensor array, and Fig. 2.14 (c) is the overlay of (a) on top of (b). The stained cells are clearly seen in all three images [8], [9].

Figure 2.14: Pictures of live cells coupled to chip surface are taken using (a) a camera and (b) the contact imager. The overlapped view is shown in (c). [8],[9]

It is possible therefore, to image cells coupled directly to the sensor surface. However, in order to identify the location of the cells using a standard CMOS APS imager, an entire imaging frame must be read out first so that a user or computer program can segregate object(s) from background. To enable unsupervised detection of dynamic cellular behavior, it would be desirable for the imager itself to be able to identify and report the location of sparse distributions of cells without the necessity and computational cost of full frame readout. That is precisely the problem that the dark address event imager seeks to address.

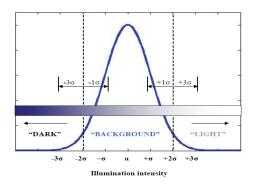

Specifically, we designed a hybrid dark-active address-event representation ("AER") image sensor whose active pixel elements operated in both: (1) a conventional imaging mode; and (2) a "dark AER" mode wherein the individual pixels asynchronously generate voltage pulses, or spikes, when the incident light on a pixel falls below a user defined threshold [10]. Thus, in the dark AER mode, individual pixels sense whether they are occluded ("dark"), or not, by integrating the difference between the photocurrent and a tunable bias current onto the photodiode junction capacitance. Charge accumulates on an occluded photodiode because the photocurrent is smaller than the bias current. The capacitor voltage is then buffered by a source follower and, for a dark photodiode, increases until it crosses the threshold of a CMOS inverter, whereupon it is converted into a logic "high" event. For a full frame image sensor, "dark" digital events can be queued using a standard arbiter structure as outlined in [31], or may priority encoded in real-time and then multiplexed together for serial readout.

Fig. 2.15 (a) illustrates the fundamental sensing unit of the dark AER imager – it is a standard APS cell, with two essential modifications: (a) an in-pixel current source controlled by the voltage **p\_bias**; and (b) the digital **inverter buffers** which convert the analog follower voltage to a digital signal. As laid out in a commercial 0.5 μm, 3-metal 2-poly process, the pixel is approximately 32 μm x 30 μm in size, and achieves a fill factor of 19%. The operation of the circuit can be seen in Fig. 2.15 (b), which represents the voltage across the photodiode junction capacitance as a function of time, under different bias conditions.

Figure 2.15: (a) Non-adaptive APS ("n-APS") schematic; (b) n-APS principle of operation. Incident light generates a photocurrent that discharges the photodiode junction capacitance, while an opposing, user-tuned, current source supplements the thermal (dark) current and charges the node. [10]

During the reset period, the voltage is fixed at a DC level. When the **rst** switch is turned off, then the incident light generates a photocurrent that tends to discharge the pixel. However, the opposing bias current tends to charge the photodiode, resulting in a competition between the two. In the dark, the bias current is stronger than the photocurrent and so the pixel will charge and the voltage rises.

By contrast, in bright light, the photocurrent is more powerful than the user-fixed bias current, and so it tends to discharge the pixel, thereby reducing the voltage across the photodiode. Note that owing to the characteristic relationship between voltage and current described above, the  $\frac{dV}{dt}$  for a given illumination intensity is essentially linear. In asynchronous mode, when the voltage rises above or falls below a certain threshold, the competition between light and dark is concluded; the voltage triggers the inverter buffers which convert the analog output into a binary decision – logic high or logic low, and thereby signal an optical occlusion or spike event. Thus, instead of reading out an entire image frame and performing costly post-processing on the data, the image sensors themselves flag the location of migrating objects or cells that occlude light from the sensor surface. Furthermore, since the spatial location of each APS is fixed in an array, the address of each flag can be deduced and transmitted by integrated readout circuitry. For sparse distributions of cells, this address-event representation is an efficient and compact alternative to conventional techniques.

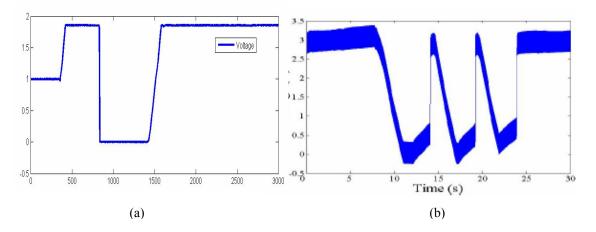

Several experiments were performed to validate the operation of the dark AER APS. Results from two of these experiments which illustrate analog and digital transitions between light and dark for a pixel of the fabricated image sensor are shown in Figs 2.16 (a) & 2.16 (b), respectively. Voltage peaks correspond with the dark, whereas troughs represent bright incident light. Note that the digital transitions are rail-to-rail, whereas the analog transitions do not rise above 2 V. Likewise, it is important to observe that while the analog transitions are crisp, the digital readout

suffers from considerable jitter, owing in part to parasitic capacitances and leakage through the analog readout architecture.

Figure 2.16: (a) Non-adaptive APS ("n-APS") source follower output in response to slow changes in ambient light intensity (30s total time scale); (b) n-APS digital output in response to slow changes in ambient light intensity. Plateaus represent periods of static ambient light intensity, while high voltages represent dark or occluded signals, and low voltages represent the incident light. [10], [11]

In addition, owing to the very small photo- and bias- currents (a fraction of a pF), and the size of the photodiode junction and parasitic capacitances (100's of fF), the full-swing transition time is on the order of hundreds of ms to seconds. Their slow speed, while useful for detecting the natural migration of cells that occurs over minutes, hours and days, does not permit rapid physiological measurement of optical activity. Furthermore, the thresholds for these transitions are fixed, user defined and subject to circuit mismatch and process variation; although each pixel can distinguish light from dark, none can adapt to changes in ambient illumination. As a result, in order to: (a) enable reliable unsupervised optical event detection under different ambient lighting conditions; and (b) enhance the discrimination speed of the detector, we developed a new adaptive image sensor for optical spike detection.

# 2.2.2 Sensing biological activity

With sufficient spatial, optical and temporal resolution, it is possible to measure not only static information about a cell, such as the location to which it may have migrated, but additionally to observe some aspects of a cell's dynamic behavior and physiology as well. There are several reported integrated architectures that perform just such measurements [30]. Photodiodes fabricated on the scale of biological cells possess the requisite sensitivity<sup>3</sup>, integrated fluorescence filters permit us to employ optical dyes and coated fluorescent microbeads to illuminate chemical potential spikes [32], and detector speed is enhanced so that sensing dynamic biological activity with integrated contact imagers is rapidly becoming the new paradigm.

As our first step down that path, we note that the ambitious objective of observing salient biological activity using a contact imager is predicated on the notion that we can visualize such activity — i.e. that physiology can be mapped to fluctuations in optical intensity that can be captured by the image sensor. Inasmuch as most biological processes do not exhibit optical signals naturally, this is no mean feat. The most common conventional manner in which to visualize such processes fluorescence microscopy — this process requires a microscope fitted at a minimum with both an excitation filter and source [33]. Several important biological compounds, principally NADH, will fluoresce when excited, and emit light at a

<sup>&</sup>lt;sup>3</sup> Many promising new technologies with superior sensitivity are being developed – avalanche photodiodes in standard CMOS still suffer a high noise floor, but offer much promise in this area. Likewise, techniques for enhancing the signal quality, such as surface plasmon resonance and optical waveguides suggest that the future of this field is indeed bright.

different wavelength; other biological compounds, metabolic processes and potential shifts can trigger fluorescent dyes or probes.

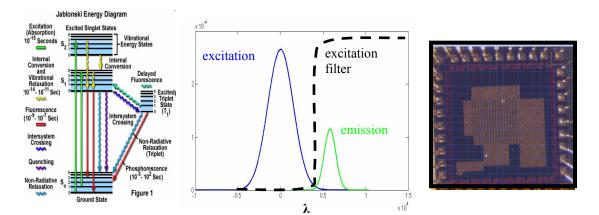

Figure 2.17: Jablonski diagram, [34].

Figure 2.18: Stokes shift and principles of fluorescence detection.

Figure 2.19: Photomicrograph of n-APS sensor array, shaded with a drawn blue filter.

Fig. 2.17 is a schematic Jablonski diagram illustrating the fundamental physics underlying fluorescence, and Fig. 2.18 displays an idealized representation of excitation and emission spectra, along with the concept behind an excitation filter. Although there are many commercial ways to implement these filters, none of these fall within the province of this dissertation. For the fluorescence experiments conducted here, the integrated fluorescence filters were prepared by adding a UV chromophore, benzotriazole, to poly-dimethyl-siloxane ("PDMS") in order to form a patternable absorption filter that absorbs over 99 percent of light below 400 nm, while passing nearly all of the light above that wavelength [35].<sup>4</sup> Fig. 2.19 displays a photomicrograph of the n-APS shaded with a drawn blue filter.

<sup>&</sup>lt;sup>4</sup> The filters were prepared by Mr. Marc Dandin of the University of Maryland Department of Bioengineering.

To the extent that there exist several well-known reported techniques for monitoring biological activity by fluorescence imaging, we have not attempted to substantially modify or add to these methods. Although we address two such means for neural signal detection – the methods in and of themselves do not represent a contribution of the present work. Instead, we establish basic theoretical performance characteristics of a contact imaging system for the fluorescence detection of neural signals, and report a novel adaptive contact image sensor with enhanced detection speed suitable for measuring optical spikes that correspond with biological metabolic and/or neural activity.