**ABSTRACT**

Title of Document: EFFECT OF INTERMETALLIC GROWTH ON

DURABILITY OF HIGH TEMPERATURE SOLDERS (SNAG, SAC305, SAC+MN, SNAG+CU NANO) IN THERMAL AND

VIBRATION ENVIRONMENTS

Michael Adam Crandall, Master of Science, 2011

Directed By: Associate Professor F. Patrick McCluskey

Department of Mechanical Engineering

The RoHS ban of lead from electronics has pushed the industry to find lead free alternatives. In high temperature environments, high lead solders have typically been used. A suitable lead free replacement alloy is required. In this study quad flat packages (QFP) and 2512 chip resistors soldered with commercially available Sn3.5Ag and SAC305, and experimental SAC+Mn and SnAg+Cu Nano alloys on ENIG finished copper were subjected to three tests. Isothermal aging at 185°C for up to 1000 hours and at 200°C for up to 500 hours were performed to measure the interfacial intermetallic thickness, assess intermetallic compounds, and view the microstructure. A durability assessment was performed featuring thermal cycling ranges of -40 to 185°C and -40 to 200°C intermixed with 50G vibration cycling to determine the most durable solder alloy. Failure analysis was performed to understand the durability results. Finally, shear testing was performed to determine a correlation between shear strength and durability. The results show SAC305 is the most reliable solder under these conditions.

# EFFECT OF INTERMETALLIC GROWTH ON DURABILITY OF HIGH TEMPERATURE SOLDERS (SNAG, SAC305, SAC+MN, SNAG+CU NANO) IN THERMAL AND VIBRATION ENVIRONMENTS

By

Michael Adam Crandall

Thesis submitted to the Faculty of Graduate School of the University of Maryland, College Park in partial fulfillment Of requirements for the degree of Master of Science

2011

**Advisory Committee:**

Professor F. Patrick McCluskey, Advisor & Chair Professor Michael Pecht Dr. Michael Osterman © Copyright by Michael Adam Crandall 2011

# **Dedication**

To my parents, Beth, Jon, and Jess.

#### Acknowledgements

I would first like to thank Dr. McCluskey for the opportunity to do this research as well as the time and guidance provided. I often felt you had more faith in me than I did and your confidence drove me towards greater success. Additionally, I would like to thank the members of the advisory committee, Dr. Pecht and Dr. Osterman for all their input and help improving this work.

I would also like to thank the members of Dr. McCluskey's research group for their advice, and friendship. Special thanks to Chandra, Hannes, Rayhoo, Doug, and Lauren. An even bigger thanks to Kyle for providing a daily sounding board.

Additionally, I need to thank CALCE for the use of equipment and facilities, especially to Anshul, Bhanu, and Swapnesh for the help and guidance provided during my work in the laboratories.

Thank you to the Schlumberger team including Francis, Glen, and Mark. I owe a great deal of understanding to your insight of deep energy exploration as well as all of your help assessing the results of this study.

Finally, I would like to thank my parents, brother, and sister for the love and support, as well as always lending a listening ear. Last but not least I would like to thank Jess for always being there for me during this journey, taking care of me, and reminding me to eat dinner when I so often forgot.

# **Table of Contents**

| Dedicati | ion   |                                                   | ii    |

|----------|-------|---------------------------------------------------|-------|

| Acknow   | ledg  | gements                                           | iii   |

| Table of | f Co  | ntents                                            | iv    |

| Table of | f Fig | ures                                              | . vii |

| Table of | f Tal | oles                                              | viii  |

| Chapter  | 1:    | Introduction                                      | 1     |

| 1.1      | Ha    | rsh Environments                                  | 1     |

| 1.2      | Su    | rface Mount Soldering                             | 2     |

| 1.3      | Ide   | entification of High Temperature Solders          | 3     |

| 1.4      | Re    | search Motivation                                 | 5     |

| Chapter  | 2:    | Literature Review                                 | 6     |

| 2.1      | Hig   | gh Temperature Reliability                        | 6     |

| 2.2      | Inte  | erfacial Intermetallic Layer                      | 9     |

| 2.3      | Sol   | lder Alloy Intermetallic Layer Reduction          | . 12  |

| 2.3      | 3.1   | Trace Element Dopant                              | . 12  |

| 2.3      | 3.2   | Reactive Nano Particles Additions                 | . 13  |

| 2.4      | Su    | rface Finish                                      | . 14  |

| 2.4      | .1    | Review of Lead Free Surface Finishes              | . 14  |

| 2.4      | 2     | Comparison of Finish Results                      | . 15  |

| 2.5      | Ex    | perimental Selections                             | . 16  |

| Chapter  | 3:    | Solder Preparation and Test Materials Procurement | . 17  |

| 3.1      | Sol   | lder Preparation                                  | . 17  |

| 3.2      | Co    | mponent Selection                                 | . 19  |

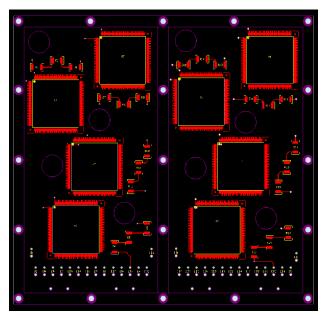

| 3.3      | Tes   | st Board Design                                   | . 19  |

| 3.4      | Tes   | st Equipment                                      | . 21  |

| 3.5      | Mo    | onitoring Systems                                 | . 23  |

| Chapter  | 4:    | Design of Experiment                              | . 25  |

| 4.1      | Ag    | ing Test                                          | . 25  |

| 4.1      | .1    | Homologous Temperature Calculations               | . 26  |

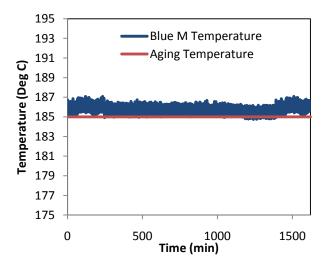

| 4.1      | .2    | Aging Chamber Characterization                    | . 26  |

| 4 1      | 3     | Cross Sectioning Parameters                       | 27    |

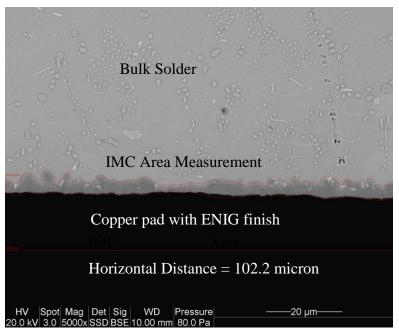

| 2    | 4.1.4   | IMC Thickness Measurement Method                                 | 28         |

|------|---------|------------------------------------------------------------------|------------|

| 4.2  | Rel     | iability Test                                                    | 30         |

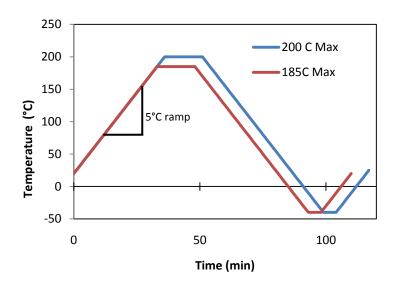

| 4    | 4.2.1   | Thermal Cycling Chamber Characterization                         | 31         |

| 4    | 4.2.2   | Board / Frame Modifications                                      | 34         |

| 4.3  | She She | ear Strength Test                                                | 36         |

| Chap | ter 5:  | Aging Test Interfacial Intermetallic Layer Results               | 38         |

| 5.1  | 185     | 5°C Aging Results QFP Samples                                    | 38         |

| 4    | 5.1.1   | Intermetallic Evolution as a result of Isothermal Aging at 185°C | 39         |

| 5.2  | 2 200   | 0°C Aging Results QFP Samples                                    | 43         |

| 4    | 5.2.1   | Intermetallic Evolution as a result of Isothermal Aging at 200°C | 45         |

| 5.3  | 3 200   | O°C Aging Results 2512 Chip Resistor Samples                     | 48         |

| 5.4  | For     | ır Layer Intermetallic Layer Evolution                           | 49         |

| 5.5  | 5 Dis   | cussion of Isothermal Aging Study                                | 52         |

| Chap | ter 6:  | Thermal/Vibration Cycling Durability Test                        | 53         |

| 6.1  | Tes     | st One Durability Results                                        | 53         |

| (    | 6.1.1   | -40°C to 185°C Thermal/Vibration Cycling                         | 53         |

| (    | 6.1.2   | QFP Intermetallic Layer Thickness Comparison                     | 57         |

| 6.2  | 2 Tes   | st Two Durability Results                                        | 59         |

| (    | 6.2.1   | -40°C to 200°C Thermal/Vibration Cycling                         | 59         |

| (    | QFP In  | termetallic Layer Thickness Comparison                           | 61         |

| (    | 6.2.2   | 2512 Chip Resister Intermetallic Layer Thickness Comparison      | 62         |

| 6.3  | 8 Fai   | lure Analysis                                                    | 64         |

| (    | 6.3.1   | Failure Locations and Pathway                                    | 64         |

| (    | 6.3.2   | QFP and Chip Resistor Lead Intermetallic Measurements            | 66         |

| (    | 6.3.3   | Solder Joint Quality Assessment                                  | 71         |

| 6.4  | Dis     | scussion of Durability Testing Results                           | 73         |

| Chap | ter 7:  | Shear Strength Test and Correlation to Reliability               | <b>7</b> 4 |

| 7.1  | 185     | 5°C Shear Testing Results                                        | 74         |

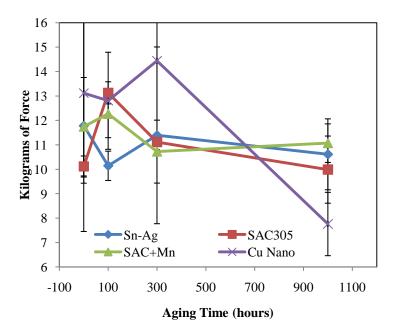

| •    | 7.1.1   | Shear Strength vs. Aging Time at 185°C                           | 74         |

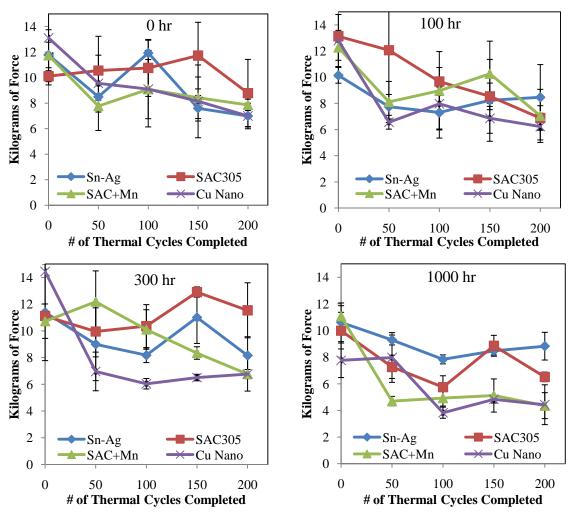

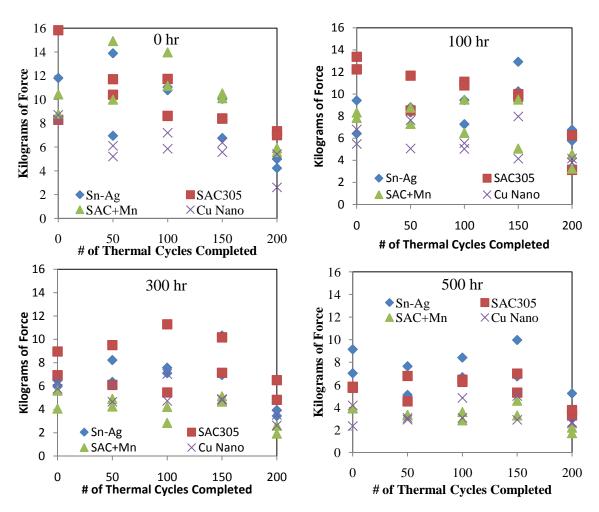

| -    | 7.1.2   | Shear Strength versus Thermal/Vibration Cycling                  | 75         |

| 7.2  | 2 200   | O°C Shear Testing Results                                        | 77         |

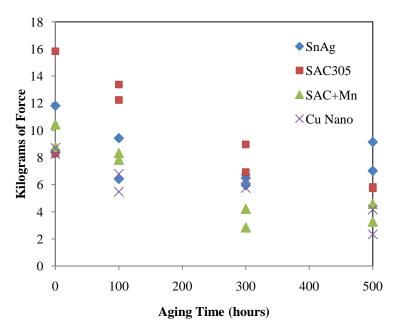

| -    | 7.2.1   | Shear Strength vs. Aging Time at 200°C                           | 77         |

| -    | 7.2.2   | Shear Strength versus Thermal/Vibration Cycling                  | 78         |

| 7.3     | Fractography Analysis                         | 79 |

|---------|-----------------------------------------------|----|

| 7.3     | 3.1 Fracture Location                         | 80 |

| 7.3     | 3.2 Voiding Discussion                        | 81 |

| 7.4     | Discussion of Shear Strength Results          | 82 |

| Chapte  | er 8: Conclusions and Contributions           | 83 |

| 8.1     | Summary of Results                            | 83 |

| 8.2     | Conclusions                                   | 85 |

| 8.3     | Contributions                                 | 86 |

| Append  | dix A: EC-12 Sun Electronics Chamber Programs | 87 |

| Append  | dix B: Raw Failure Data                       | 88 |

| Referer | nces                                          | 90 |

# **Table of Figures**

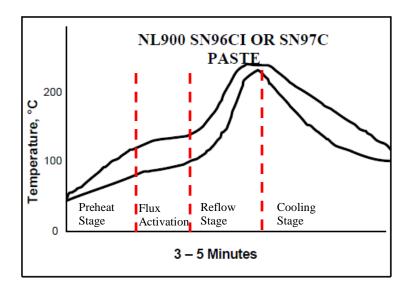

| Figure 1: SAC305 recommended by FCT Assembly data sheet [2]                                                | 3   |

|------------------------------------------------------------------------------------------------------------|-----|

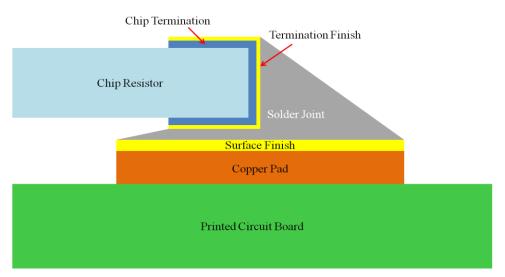

| Figure 2: Example chip resistor solder joint showing surface finish                                        |     |

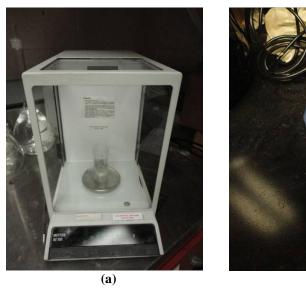

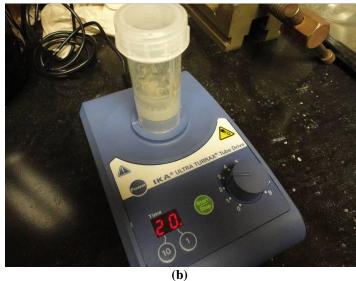

| Figure 3: Equipment used to create solder paste, (a) Mettler AE100 scale, (b) IKA tube mixer during use    |     |

| with 20 minutes remaining                                                                                  | 18  |

| Figure 4: Test Board Layout                                                                                |     |

| Figure 5: One of two test racks built                                                                      |     |

| Figure 6: Dage 2400 with shear cartridge.                                                                  |     |

| Figure 7: Blue M Chamber Characterization                                                                  |     |

| Figure 8: Sn-Ag Ohr aging, 2512 chip capacitor, interfacial IMC thickness measurement (courtesy CALCE,     |     |

| Figure 9: Ideal Thermal Cycle Profiles                                                                     | -   |

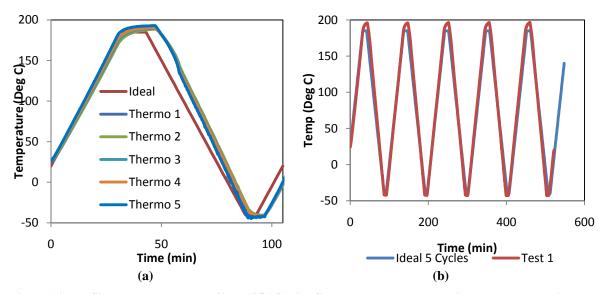

| Figure 10: (a) Single thermal cycle -40 to 185 °C with five thermocouples tracking chamber gradient, (b)   |     |

| Five thermal cycles, -40 to 185 °C, to ensure repeatable cycles using centered thermocouple                |     |

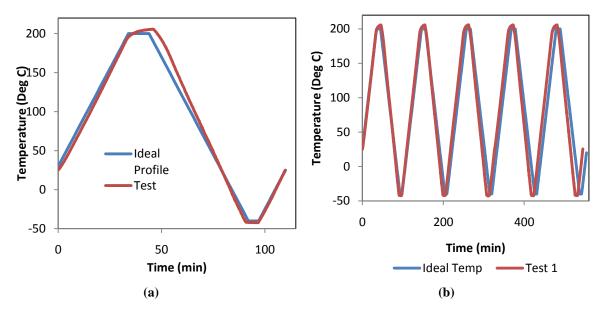

| Figure 11: (a) Single thermal cycle -40 to 200 °C, (b) Five thermal cycles, -40 to 200 °C                  |     |

| Figure 12: Uniaxial Shaker with Boards mounted                                                             |     |

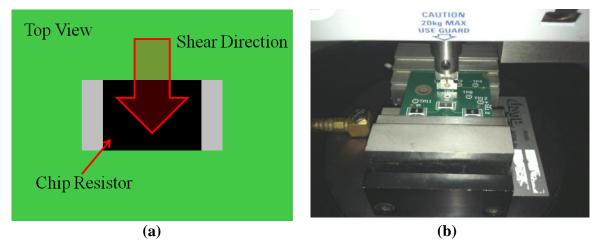

| Figure 13: Shear set up, (a) shear direction diagram, (b) shear specimen in holder                         |     |

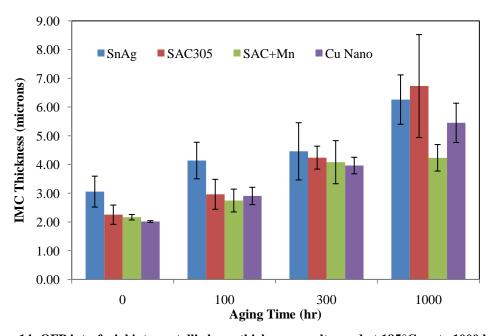

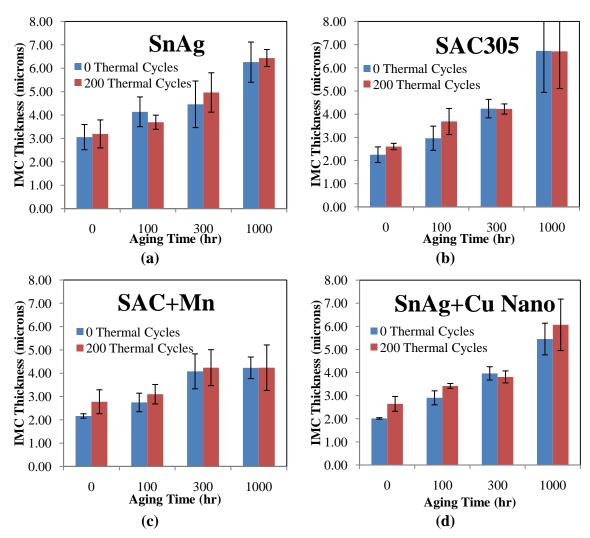

| Figure 14: QFP interfacial intermetallic layer thickness results aged at 185°C up to 1000 hours            |     |

|                                                                                                            |     |

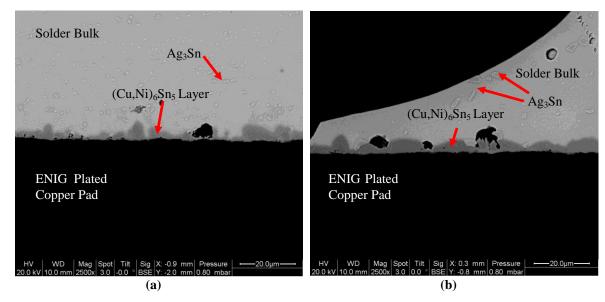

| Figure 15: SnAg QFP solder joints, (a) after reflow, (b) after 1000 hours of aging at 185°C (courtesy CALC |     |

| Figure 16: SAC20E OFF colder joints (a) after reflew (b) after 1000 hours of aging at 195°C (sourtes)      | 40  |

| Figure 16: SAC305 QFP solder joints, (a) after reflow, (b) after 1000 hours of aging at 185°C (courtesy    | 11  |

| CALCE).                                                                                                    | 41  |

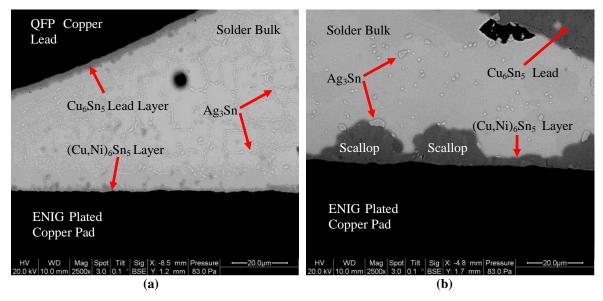

| Figure 17: SAC+Mn QFP solder joints, (a) after reflow, (b) after 1000 hours of aging at 185°C (courtesy    | 42  |

| CALCE).                                                                                                    | 42  |

| Figure 18: SnAg+Cu Nano QFP solder joints, (a) after reflow, (b) after 1000 hours of aging at 185°C        | 40  |

| (courtesy CALCE)                                                                                           |     |

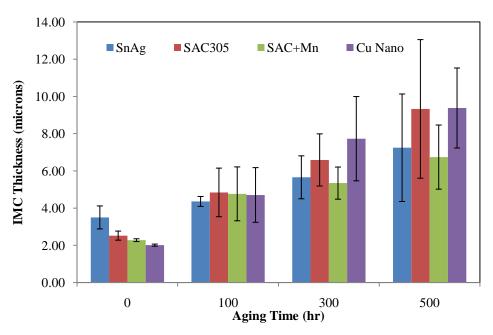

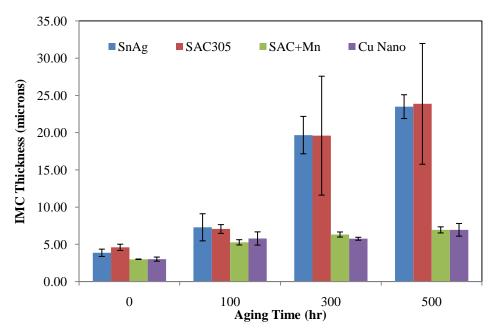

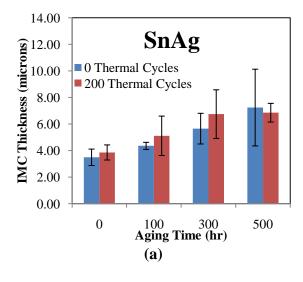

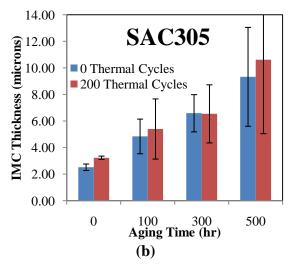

| Figure 19: QFP interfacial intermetallic layer thickness results aged at 200°C up to 500 hours             |     |

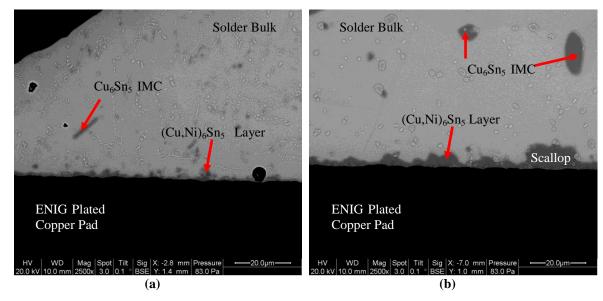

| Figure 20: SnAg QFP solder joints, (a) after reflow, (b) after 500 hours of aging at 200°C (courtesy CALCI |     |

| 5in - 24 CACCOS OSD - Idazisint (-) often offer (b) often 500 beauty of animal 2009C (-)                   | 45  |

| Figure 21: SAC305 QFP solder joints, (a) after reflow, (b) after 500 hours of aging at 200°C (courtesy     |     |

| CALCE)                                                                                                     | 46  |

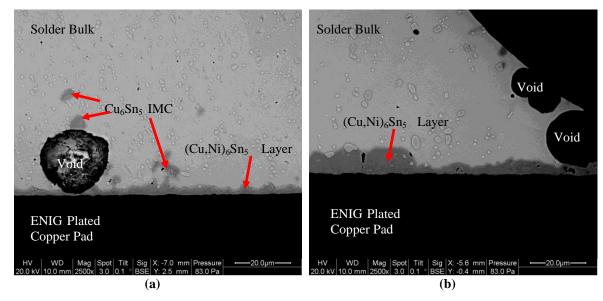

| Figure 22: SAC+Mn QFP solder joints, (a) after reflow, (b) after 500 hours of aging at 200°C (courtesy     | 4-  |

| CALCE).                                                                                                    |     |

| Figure 23: SnAg+Cu Nano QFP solder joints, (a) after reflow, (b) after 500 hours of aging at 200°C (court  |     |

| CALCE).                                                                                                    |     |

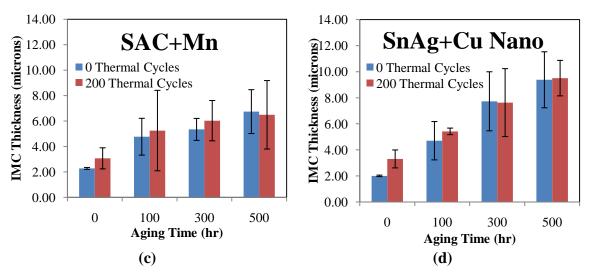

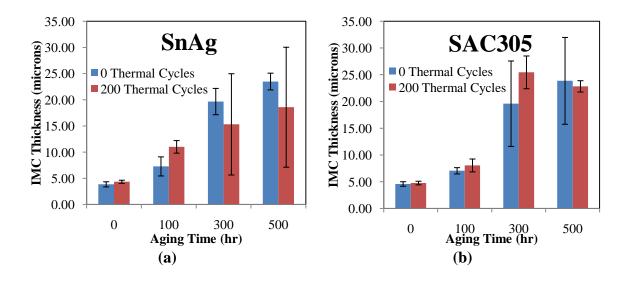

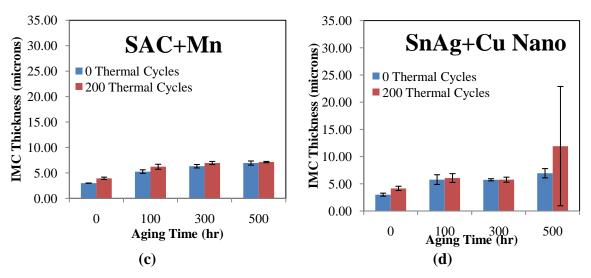

| Figure 24: 2512 Chip resistors interfacial intermetallic layer thickness results aged at 200°C for a maxim |     |

| of 500 hours                                                                                               |     |

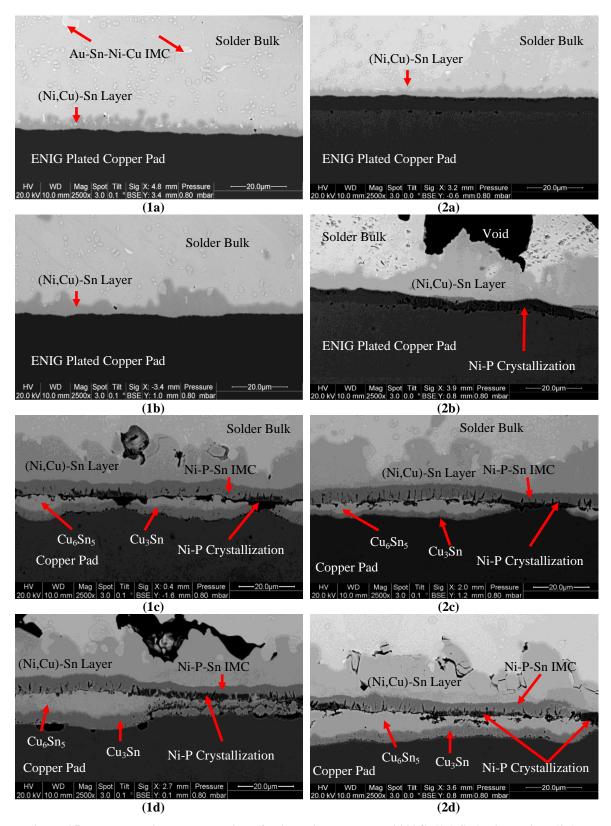

| Figure 25: Intermetallic layer evolution of chip resistors aged at 200°C, (1a) SnAg Ohr aging, (2a) SAC30  | 5   |

| Ohr aging, (1b) SnAg 100hr aging, (2b) SAC305 100hr aging, (1c) SnAg 300hr aging, (2c) SAC305 300hr        |     |

| aging, (1d) SnAg 500hr aging, (2d) SAC305 500hr aging (courtesy CALCE)                                     |     |

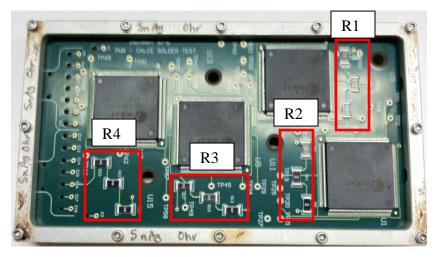

| Figure 26: Test board chip resistor chain number scheme                                                    |     |

| Figure 27: Comparison of QFP interfacial intermetallic layer thickness before and after thermal/vibration  |     |

| cycling for each solder and isothermal aging condition at a maximum of 185°C                               |     |

| Figure 28: Comparison of QFP interfacial intermetallic layer thickness before and after thermal/vibration  | n   |

| cycling for each solder and isothermal aging condition at a maximum of 200°C                               | 62  |

| Figure 29: Comparison of 2512 chip resistor interfacial intermetallic layer thickness before and after     |     |

| thermal/vibration cycling for each solder and isothermal aging condition at a maximum of 200°C             | 63  |

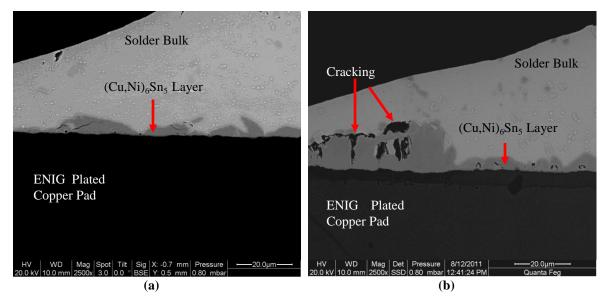

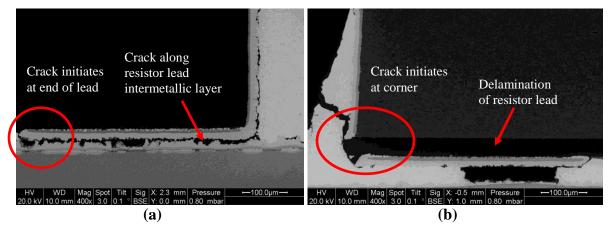

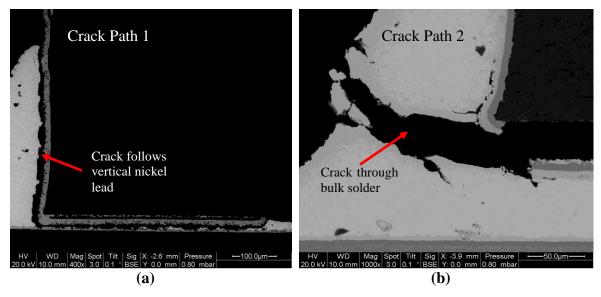

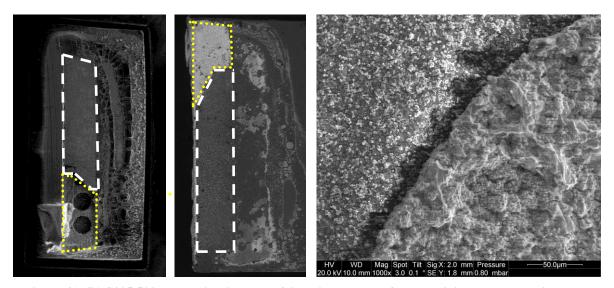

| Figure 30: Failure site initiation and layer, (a) SAC305 aged 300hr at 200°C and full set of thermal/      |     |

| vibration cycling, (b) SnAg aged 300hr at 200°C and full set of thermal/vibration cycling (courtesy CALCE  | E). |

|                                                                                                            |     |

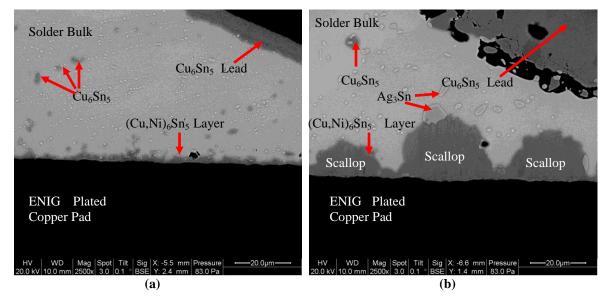

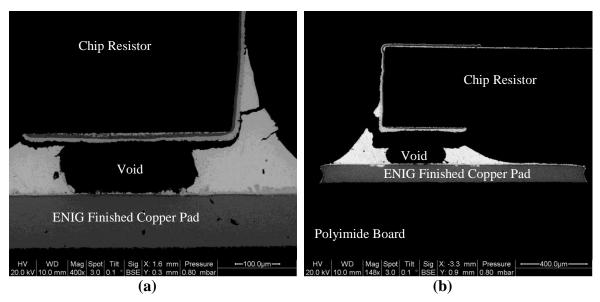

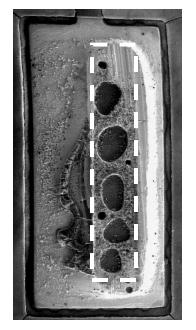

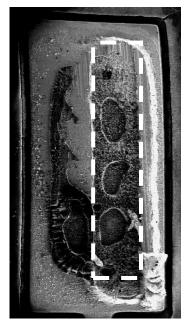

| Figure 31: 2512 chip resistor failure pathway, (a) SAC+Mn aged 100hr at 200°C and full set of cycling, (b) | ))  |

| SnAg Cu Nano good 100hr at 200°C and full set of custing (sourtess CALCE)                                  | 66  |

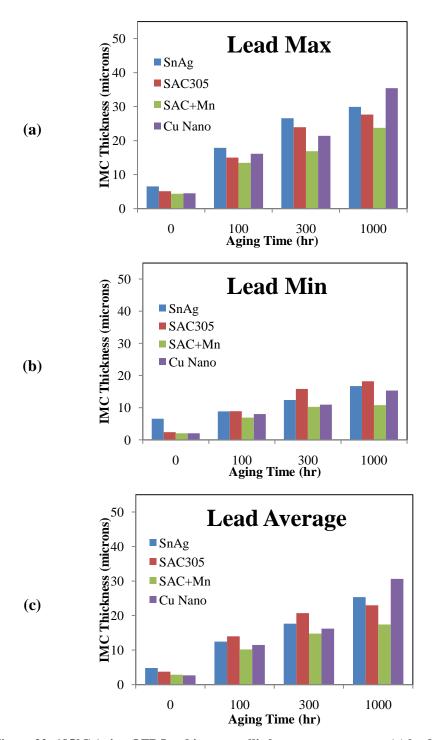

| Figure 32: 185°C Aging QFP Lead intermetallic layer measurements, (a) lead maximum thickness, (b) lead maximum thickness, (b) lead maximum thickness, (c) lead maximum thickness, (d) lead maximum thickness, (e) lead maximum thi | ead |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| minimum thickness, (c) lead average thickness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

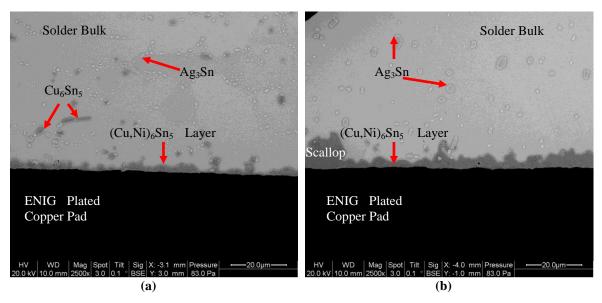

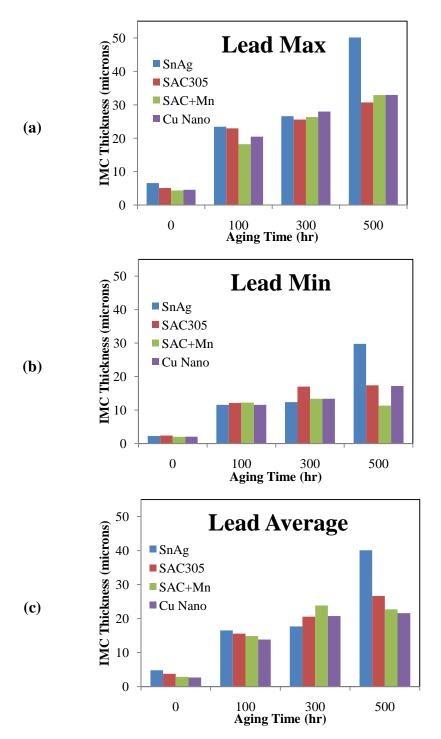

| Figure 33: 200°C Aging QFP Lead intermetallic layer measurements, (a) lead maximum thickness, (b) lead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| minimum thickness, (c) lead average thickness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68  |

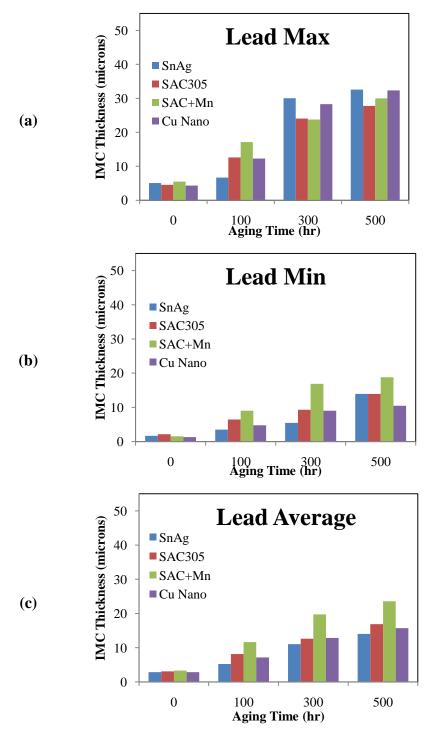

| Figure 34: 200°C Aging 2512 chip resistor termination intermetallic layer measurements, (a) lead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| maximum thickness, (b) lead minimum thickness, (c) lead average thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70  |

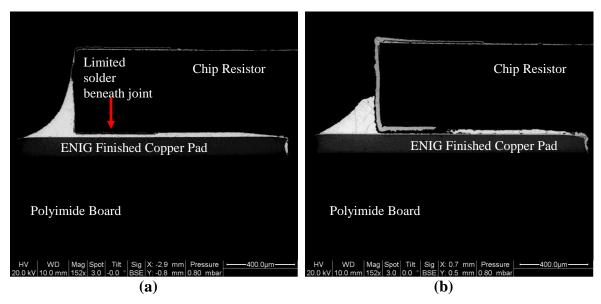

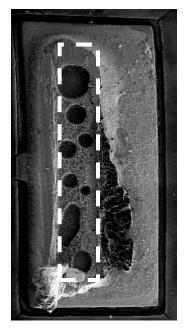

| Figure 35: Examples of poor manufacturing of SAC+Mn chip resistor joints, (a) as reflowed (b) 500hr a at 200°C (courtesy CALCE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

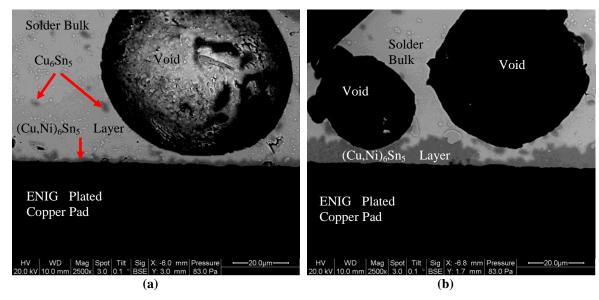

| Figure 36: Examples of SnAg+Cu Nano chip resistor joint voiding observed during failure analysis, (a) 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| aging at 200°C, (d) 500hr aging at 200°C (courtesy CALCE).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| Figure 37: Shear Strength versus aging time at 185°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Figure 38: Shear Results by aging time 185°C, comparing shear strength versus thermal/vibration cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| completed, at each interval of 50 thermal cycles vibration cycling was performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Figure 39: Shear Strength versus aging time at 200°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Figure 40: Shear Results by aging time at 200°C, comparing shear strength versus thermal/vibration c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| completed, at each interval of 50 thermal cycles vibration cycling was performed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Figure 41: SAC305 500 hour aging 0 thermal/vibration cycles, left, solder joint on board, middle,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| corresponding chip lead flipped across horizontal axis, right, zoomed in fracture surface on chip lead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| (courtesy CALCE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80  |

| Figure 42: SnAg+Cu Nano solder joints aged 500 hours at 200°C, three shear fracture surface example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25  |

| located in the remaining solder joint on the board level (courtesy CALCE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Table of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Table 1: Classification of Electronics Operating Environment [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   |

| Table 2: Isothermal aging time for each temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Table 3: Polishing Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Table 4: QFP failure results -40°C to 185°C thermal cycling and vibration cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Table 5: 2512 chip resistors failure results -40°C to 185°C thermal cycling and vibration cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Table 6: Test 1 chip resistor failure occurrence by testing method and solder type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |