**ABSTRACT**

Title of Document: SYSTEM SYNTHESIS FOR IMAGE PROCESSING

APPLICATIONS

Dong-Ik Ko, Doctor of Philosophy, 2006

Directed By: Professor Shuvra S.Bhattacharyya

Department of Electrical and Computer Engineering

Over the past few decades, embedded systems have been widely infiltrated into our daily lives. Prominent examples are cellular phones, personal digital assistants, digital television set-top boxes, web-pads, and mp3 players. New kinds of embedded devices are being introduced continually for various purposes.

Embedded systems have different combinations and prioritizations of objectives and constraints for their proper design. With the increasing complexity in application functionality, implementation constraints, and optimization objectives, more effective techniques for modeling embedded applications, and for systematically synthesizing implementations become more and more desirable on one hand, and more and more challenging on the other.

In this thesis, we focus on the efficient design, implementation, and synthesis of signal processing applications, which form a broad and important class of embedded systems. We place special emphasis in the thesis on the signal processing domain on image processing, a sector that has seen rapidly increasing demand in recent years, but for which present techniques for signal processing design are often lacking in modeling and optimization capability.

In this thesis, we propose novel models and algorithms for streamlining scheduling, memory management, and interprocessor communication in embedded multiprocessor implementations of signal processing applications, with the aforementioned emphasis on the image processing domain.

For application modeling, we propose two novel modeling techniques called blocked dataflow (BLDF) and dynamic graph topology (DGT). These modeling approaches capture within their respective formal frameworks the structure of blockbased image processing operations and reconfigurable, multi-mode dataflow behaviors, respectively.

For scheduling, we develop a novel intermediate representation called the pipeline decomposition tree (PDT). The PDT provides efficient representation and analysis of alternative multiprocessing configurations for signal processing applications. We also develop an algorithm, called pipeline decomposition tree scheduling (PDT scheduling), which applies the PDT to systematically derive optimized multiprocessor schedules that employ coarse-grained (task-level) pipelining, which is an especially useful form of parallelism for signal processing. To optimize interprocessor communication, we develop two novel post-optimization techniques for hardware resource mapping and software synthesis.

The suite of techniques presented in this thesis address image processing system

optimization at key phases in the design process and lead to significant improvements in performance, cost, and predictability of implementations that are derived from them.

#### SYSTEM SYNTHESIS FOR IMAGE PROCESSING APPLICATIONS

By

Dong-Ik Ko

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2006

## Advisory Committee:

Professor Shuvra S. Bhattacharyya, Chairman/Advisor Professor Rama Chellappa Professor Gang Qu Professor Manoj Franklin Professor Chau-Wen Tseng

© Copyright by

Dong-Ik Ko

2006

# Dedication

To my parents, and to Gye-sun, Yu-jin, and Yu-min

# Acknowledgements

| Thank the Lord! He led me to the completion of this thesis.                      |

|----------------------------------------------------------------------------------|

| It was a wonderful blessing to study under Prof. Shuvra Bhattacharyya.           |

| His encouragement and kindness has kept me focusing on my research with great    |

| passion.                                                                         |

|                                                                                  |

| I also thank my friends, Ming-Yung, Vida, Mainak, Chung-Ching, Sankalita, Jerry, |

| Sebastian, Ivan, Celine, Lin, Sadagopan and many other friends!                  |

|                                                                                  |

| I also thank brothers and sisters in my church for their prayers and loves.      |

|                                                                                  |

| My lovely wife; Gye-Sun and two daughters; Yu-Jin and Yu-Min! I am sorry for not |

| having so much time with you.                                                    |

|                                                                                  |

| Praise the Lord !!!                                                              |

|                                                                                  |

|                                                                                  |

# **Table of Contents**

| Dedication                               | ii   |

|------------------------------------------|------|

| Acknowledgements                         | iii  |

| Table of Contents                        | iv   |

| List of Tables                           | vii  |

| List of Figures                          | viii |

| Chapter 1: Introduction                  | 1    |

| 1.1 Background                           | 2    |

| 1.1.1 Modeling                           | 2    |

| 1.1.2 Scheduling[94,95,96,97]            | 10   |

| 1.1.3 Communication optimization         |      |

| 1.2 Overview of the suggested techniques | 16   |

| 1.2.1 Modeling                           |      |

| 1.2.2 Scheduling                         | 22   |

| 1.2.3 Communication cost                 | 26   |

| 1.3 Contributions of this thesis         | 29   |

| 1.3.1 Modeling                           | 29   |

| 1.3.2 Scheduling                         | 34   |

| 1.3.3 Communication optimization         | 36   |

| 1.4 Outline of thesis                    | 37   |

| Chapter 2: Modeling of DSP applications  | 39   |

| 2.1 Introduction                         | 39   |

| 2.2 Blocked Dataflow Graph (BLDF)        | 39   |

| 2.2.1 Abstract                           | 39   |

| 2.2.2 Related work                       | 40   |

| 2.2.3           | Blocked dataflow                                              | 42  |

|-----------------|---------------------------------------------------------------|-----|

| 2.2.4           | Application example                                           | 46  |

| 2.2.5           | Experiments                                                   | 50  |

| 2.2.6           | Conclusions of BLDF                                           | 58  |

| 2.3 <b>D</b> yn | namically configured graph topology (DGT)                     | 59  |

| 2.3.1           | Abstract                                                      | 59  |

| 2.3.2           | Related Work                                                  | 60  |

| 2.3.3           | Dynamic Graph Topology                                        | 62  |

| 2.3.4           | Experimental results                                          | 70  |

| 2.3.5           | Conclusions of DGT                                            | 75  |

| Chapter 3:      | Scheduling of DSP applications onto multiprocessors           | 77  |

| 3.1 Intro       | oduction                                                      | 77  |

| 3.2 Pipe        | eline Decomposition Tree scheduling                           | 78  |

| 3.2.1           | Abstract                                                      | 78  |

| 3.2.2           | Introduction                                                  | 78  |

| 3.2.3           | PDT(Pipeline Decomposition Tree) based scheduling             | 82  |

| 3.2.4           | Scheduling                                                    | 94  |

| 3.2.5           | Application examples                                          | 126 |

| 3.2.6           | Experimental results                                          | 129 |

| 3.2.7           | Conclusion                                                    | 134 |

| Chapter 4:      | Communication optimization of DSP applications implementation | 137 |

| 4.1 Intro       | oduction                                                      | 137 |

| 4.2 Mod         | deling and optimization of buffering trade-off                | 138 |

| 4.2.1           | Abstract                                                      | 138 |

| 4.2.2          | Related Work                                                           | 139 |

|----------------|------------------------------------------------------------------------|-----|

| 4.2.3          | FIFO hardware mapping for dataflow graphs                              | 140 |

| 4.2.4          | Experimental results                                                   | 150 |

| 4.2.5          | Conclusions and future work                                            | 152 |

|                | rgy-driven partitioning of signal processing algorithms ensor networks | 153 |

| 4.3.1          | Abstract                                                               | 153 |

| 4.3.2          | Introduction and Related work                                          | 154 |

| 4.3.3          | Energy consumption optimization by distribution of an application      | 156 |

| 4.3.4          | Experimental results                                                   | 165 |

| 4.3.5          | Summary                                                                | 168 |

| Chapter 5:     | Conclusion and Future work                                             | 170 |

| 5.1 <b>Mod</b> | deling                                                                 | 171 |

| 5.1.1          | Blocked DataFlow (BLDF)                                                | 171 |

| 5.1.2          | Dynamically configured graph topology                                  | 171 |

| 5.1.3          | Future work                                                            | 172 |

| 5.2 Sch        | eduling                                                                | 176 |

| 5.2.1          | Future work                                                            | 177 |

| 5.3 Con        | nmunication optimization                                               | 179 |

| 5.3.1          | Hardware communication optimization                                    | 179 |

| 5.3.2          | Software communication optimization                                    | 179 |

| 5.3.3          | Future work                                                            | 180 |

# **List of Tables**

| Table 1. | and "Token delivery"                                                                                                                                                                  | 8 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Table 2. | Memory usage comparison(MPEG2 encoder)                                                                                                                                                | 3 |

| Table 3. | Memory usage comparison (Multi resolution Spline Pyramid)                                                                                                                             | 4 |

| Table 4. | Memory usage comparison (Laplacian Pyramid)                                                                                                                                           | 4 |

| Table 5. | Memory usage comparison (Pyramid Complex)                                                                                                                                             | 5 |

| Table 6. | Memory usage comparison (Image Complex)                                                                                                                                               | 5 |

| Table 7. | Memory usage comparison                                                                                                                                                               | 6 |

| Table 8. | An example of comparison of buffer memory usages depending on task duplication and a memory architecture both under general data parallelism and under heterogeneous data parallelism | n |

| Table 9. | Function description of each block of figure 44 128                                                                                                                                   | 8 |

| Table 10 | ). Function description of each block of figure 45                                                                                                                                    | 9 |

| Table 11 | . Comparison of FIFO mapping results                                                                                                                                                  | 8 |

| Table 12 | 2. Latency comparison for different values of order                                                                                                                                   | 8 |

| Table 13 | 3. A comparison of runtime manipulation methods of multiple dataflow graphs174                                                                                                        | 4 |

# **List of Figures**

| Figure 1.  | Example of SDF graph                                                                                         | 4  |

|------------|--------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Comparison of a down-sampler actor by factor 4 each under SDF and under CSDF                                 | 5  |

| Figure 3.  | Comparison of FIFO queues under SDF and MDSDF model                                                          | 7  |

| Figure 4.  | Control flow decision under BDF                                                                              | 8  |

| Figure 5.  | Example of PSDF model                                                                                        | 10 |

| Figure 6.  | Fully static schedule                                                                                        | 13 |

| Figure 7.  | PSDF and BLDF.                                                                                               | 44 |

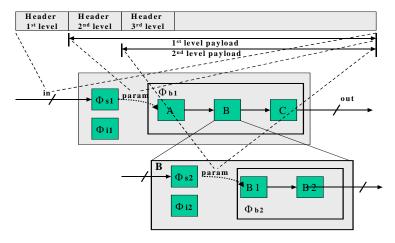

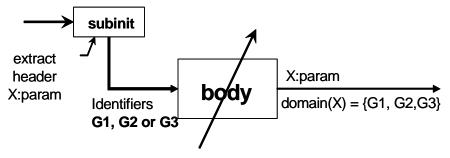

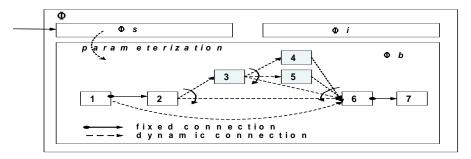

| Figure 8.  | BLDF and SDF: param(): parameterization; Φs: subinit graph, Φb: body graph; "a", "b": tokens being delivered | 46 |

| Figure 9.  | Data tokens with nested headers                                                                              | 47 |

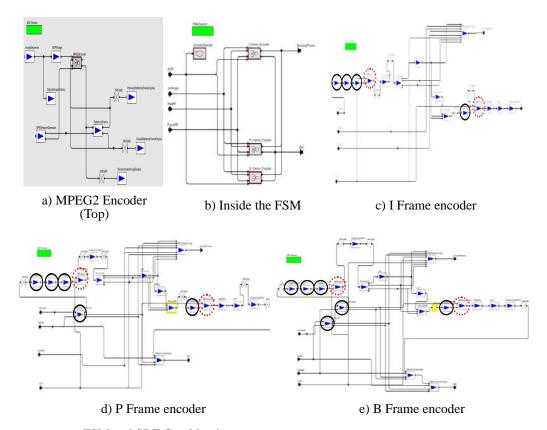

| Figure 10. | FSM and SDF Combination                                                                                      | 52 |

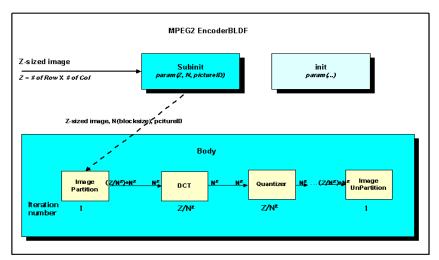

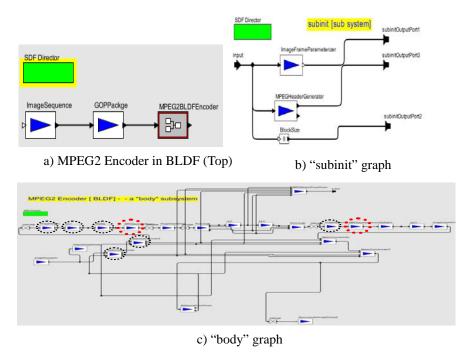

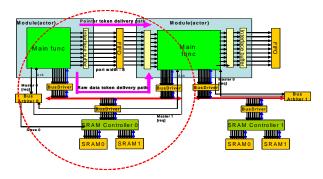

| Figure 11. | Blocked data delivery in BLDF                                                                                | 55 |

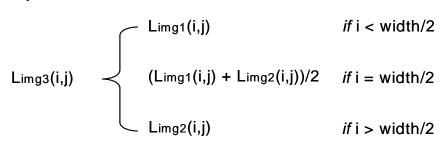

| Figure 12. | MPEG2 Encoder under BLDF                                                                                     | 56 |

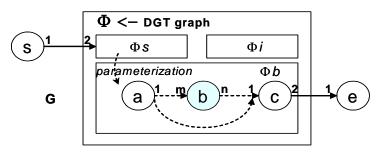

| Figure 13. | DGT (Dynamic Graph Topology)                                                                                 | 63 |

| Figure 14. | An example of a graph under DGT                                                                              | 64 |

| Figure 15. | DGT graph under SDF                                                                                          | 66 |

| Figure 16. | Part of an MPEG2 video encoder                                                                               | 68 |

| Figure 17. | Operational semantics of DGT operating with any type of dataflow model                                       |    |

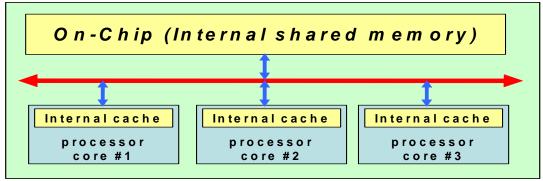

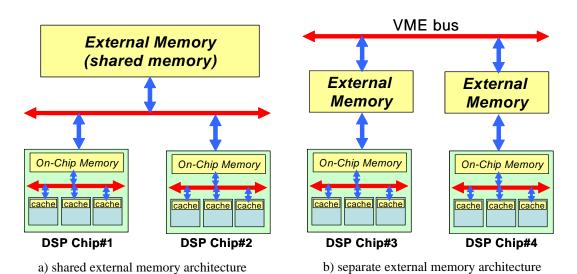

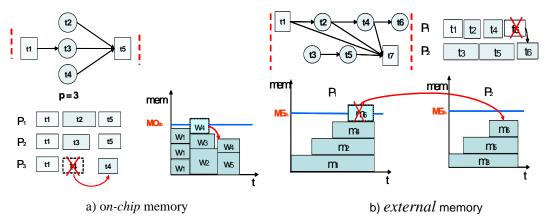

| Figure 18. | An "on-chip" memory and an internal cache of DSP chip                                                        | 84 |

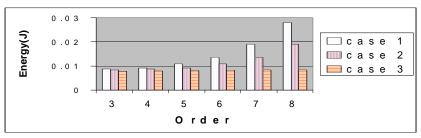

| Figure 19. | Comparison of a shared external memory architecture and a separate external memory architecture              |    |

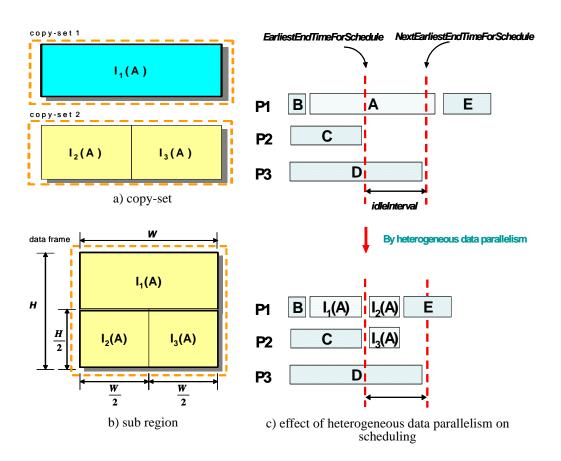

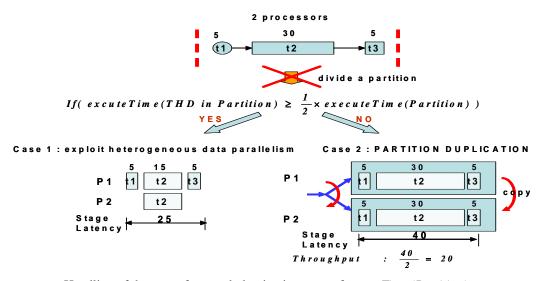

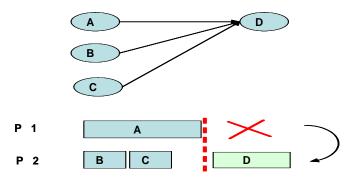

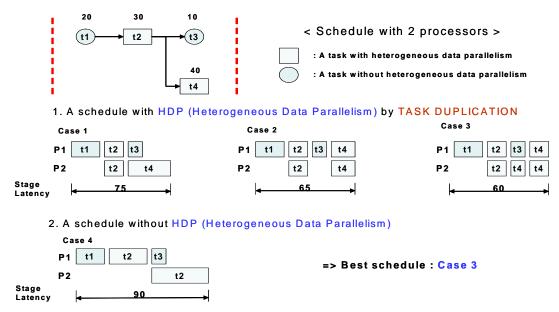

| Figure 20. | Heterogeneous data parallelism.                                                                              | 87 |

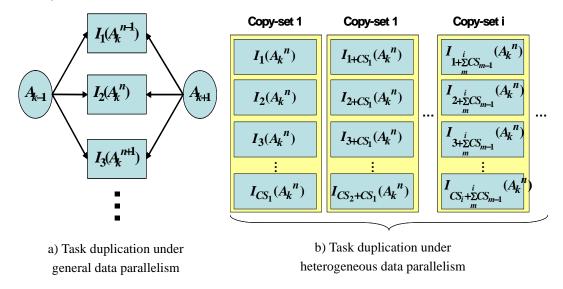

| Figure 21  | Task duplication under general data parallelism and under heteroge-                                          |    |

|            | neous data parallelism                                                                                                                         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|

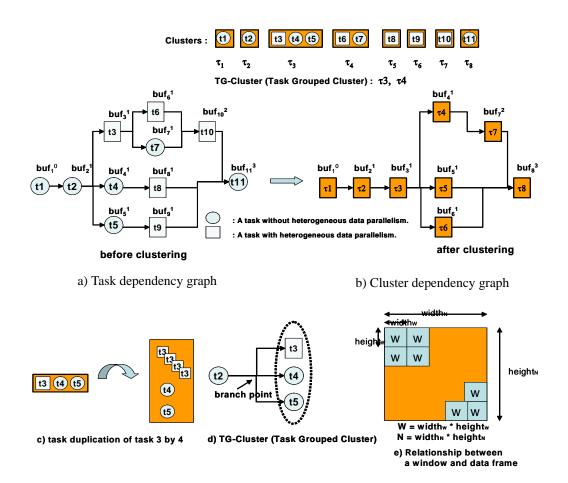

| Figure 22. | Examples of tasks, clusters, clustering and window                                                                                             |

| Figure 23. | FindSchedule() algorithm                                                                                                                       |

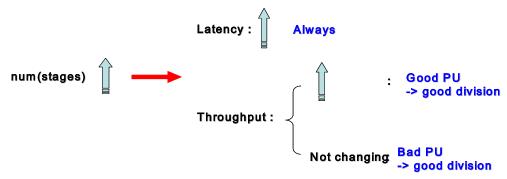

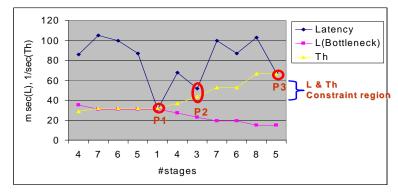

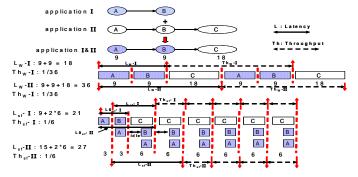

| Figure 24. | Relationship between Latency, Throughput and Number of stages 99                                                                               |

| Figure 25. | CPAP algorithm                                                                                                                                 |

| Figure 26. | PDT() algorithm                                                                                                                                |

| Figure 27. | A variation of the size of partitions depending on the cutflag 104                                                                             |

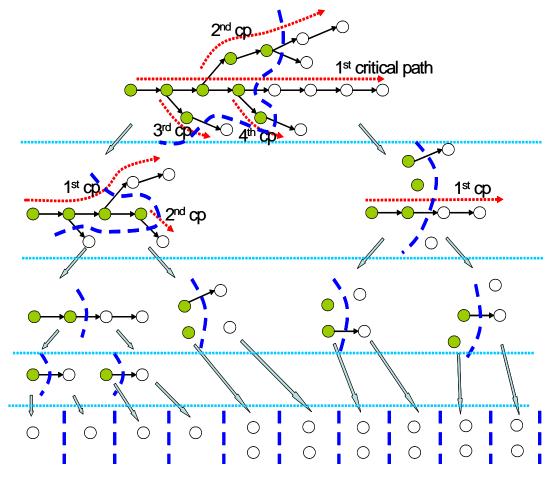

| Figure 28. | An example of usage of CPAP in PDT                                                                                                             |

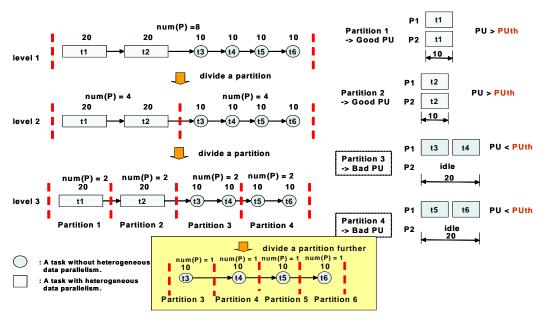

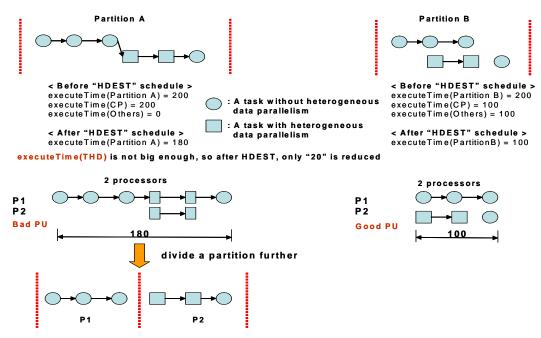

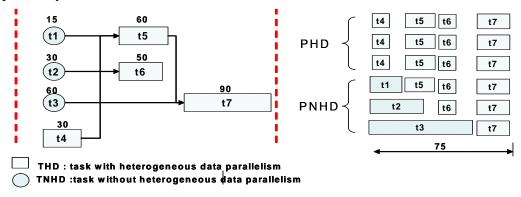

| Figure 29. | Effect of THDs and TNHDs in scheduling                                                                                                         |

| Figure 30. | Effect of executeTime(Tasks in the longest critical path) and executeTime(Other tasks not included in the longest critical path) in scheduling |

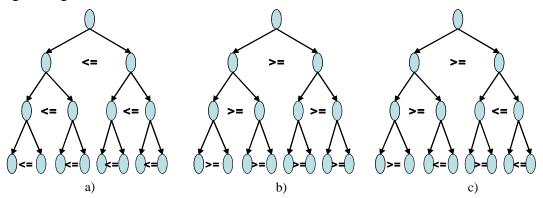

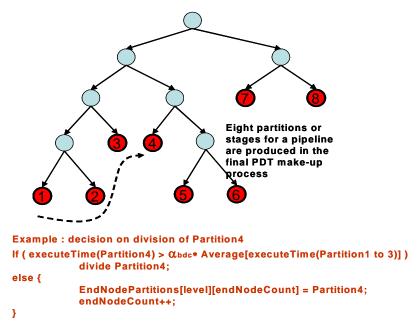

| Figure 31. | PDT(Pipeline Decomposition Tree) and division by basic division criterion                                                                      |

| Figure 32. | Examples with a large difference in executeTime(Partition)s between two sub partitions                                                         |

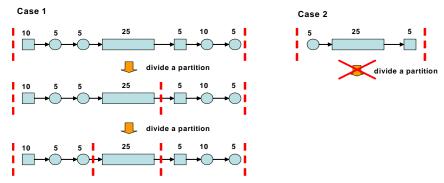

| Figure 33. | Handling of the case of one task dominating most of excuteTime (Partition)                                                                     |

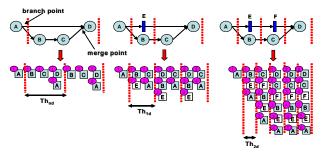

| Figure 34. | An example of making up pipelines with different trade-offs between latency and throughput from PDT                                            |

| Figure 35. | An example of a schedule by HDEST116                                                                                                           |

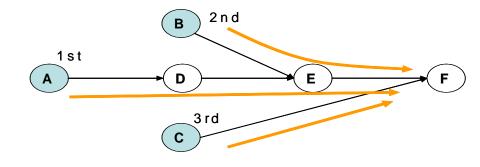

| Figure 37. | Priority setting of tasks in RL (Ready List) based on a critical path of succeeding tasks                                                      |

| Figure 36. | HDEST algorithm118                                                                                                                             |

| Figure 38. | Example of consideration communication cost of HDEST in scheduling                                                                             |

| Figure 39. | An example of how THDs reduce the execution time of a given stage . $121$                                                                      |

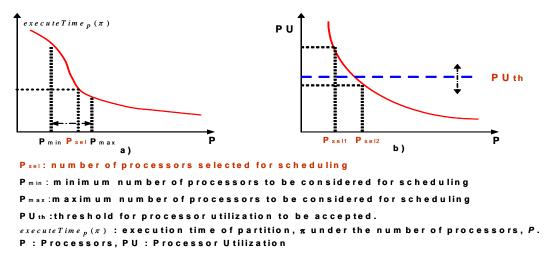

| Figure 40. | Relationship among execution time of partition, p, the number of processors, p and processor utilization, PU                                   |

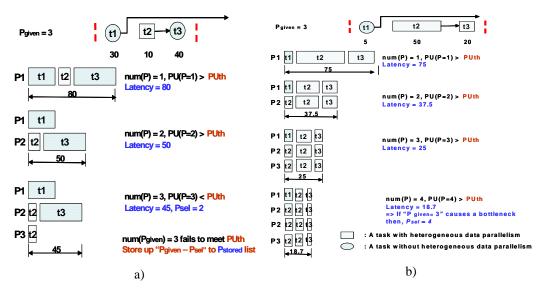

| Figure 41. | Examples of verification of Pgiven                                                             | 123 |

|------------|------------------------------------------------------------------------------------------------|-----|

| Figure 42. | Usage of on-chip and external memory                                                           | 125 |

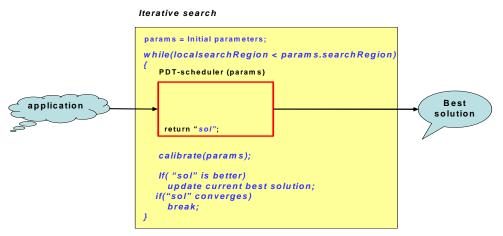

| Figure 43. | Adaptation of PDT scheduling algorithm with varying parameters to iterative search approach    |     |

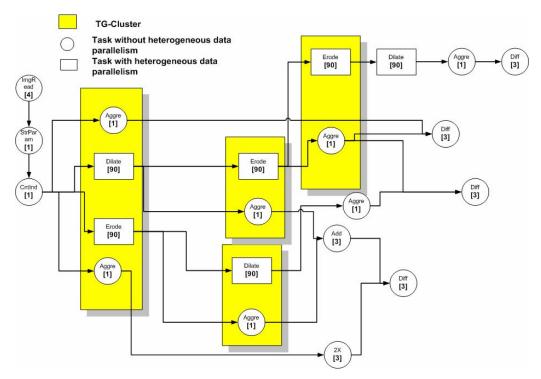

| Figure 44. | A graph of a complex module of morphological operations                                        | 127 |

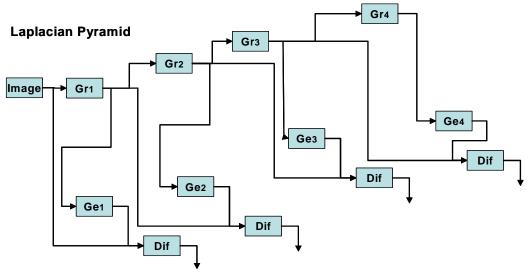

| Figure 45. | Laplacian Pyramid as an application example.                                                   | 127 |

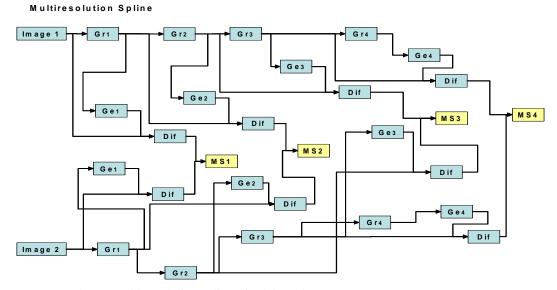

| Figure 46. | Multi resolution Spine as an application example                                               | 128 |

| Figure 47. | MPEG2 Encoder                                                                                  | 130 |

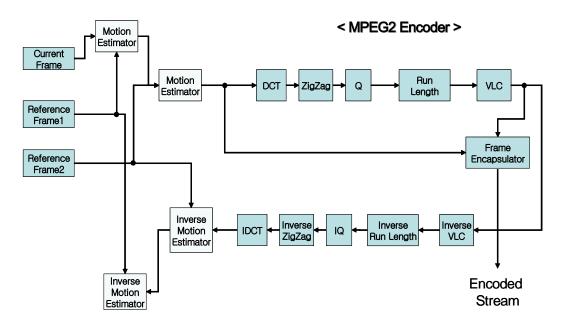

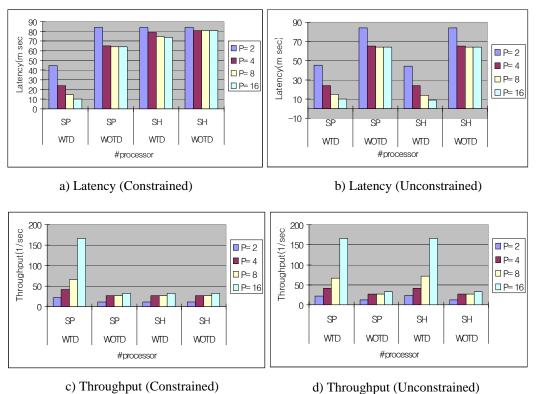

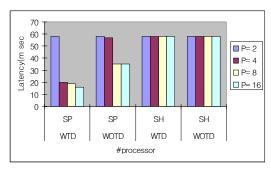

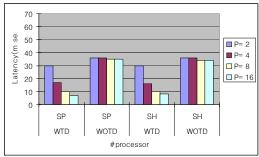

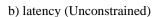

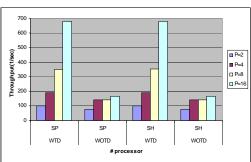

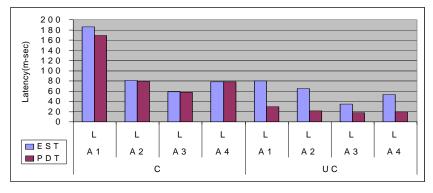

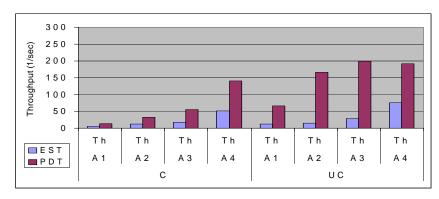

| Figure 48. | Latency and throughput comparison (Multi-Spline)                                               | 131 |

| Figure 49. | Latency and throughput comparison (Laplacian)                                                  | 132 |

| Figure 50. | Latency and throughput comparison (Image Complex)                                              | 133 |

| Figure 51. | Latency and throughput comparison(MPEG2 Encoder)                                               | 133 |

| Figure 53. | Latency vs Throughput trade-off (Multi-resolution Spline, P=16, Unconstrained, Shared memory)  | 134 |

| Figure 52. | EST vs PDT comparison                                                                          | 135 |

| Figure 54. | Comparison of FIFO architectures                                                               | 142 |

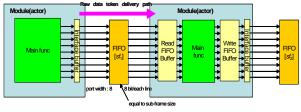

| Figure 55. | Effect of sub-frame division on latency and throughput.                                        | 143 |

| Figure 56. | Effect of data dependency on performance.                                                      | 146 |

| Figure 57. | Comparison of FIFO mapping                                                                     | 148 |

| Figure 58. | FIFO mapping algorithm-PartA.                                                                  | 150 |

| Figure 59. | FIFO mapping algorithm-PartB                                                                   | 151 |

| Figure 60. | Complex, composite morphological image processing application (TopHat, Gradient and Smoothing) | 152 |

| Figure 61. | An illustration of partitioning (cutting line) trade-offs                                      | 159 |

| Figure 62. | Application mapping over sensor nodes                                                          | 165 |

| Figure 63. | MSP430-based sensor node platforms                                                             | 166 |

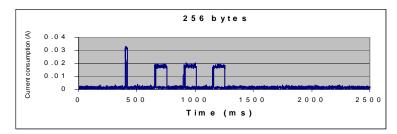

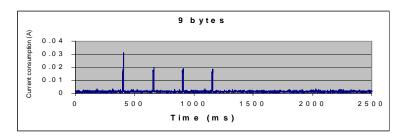

| Figure 64. | Current consumption comparison of three application mappings 168                          |

|------------|-------------------------------------------------------------------------------------------|

| Figure 65. | Energy consumption comparison for different order values 168                              |

| Figure 66. | An example of simultaneous running of multiple dataflow graphs 174                        |

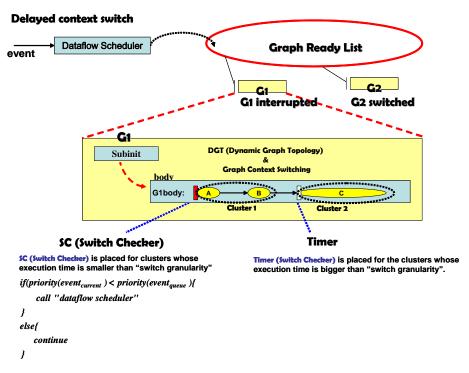

| Figure 67. | Delayed context switch model of dataflow graphs                                           |

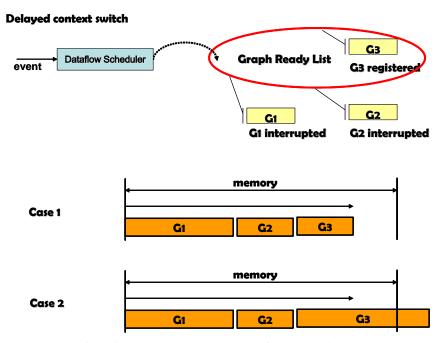

| Figure 68. | Relationship between memory usage of graphs and the graph context switch                  |

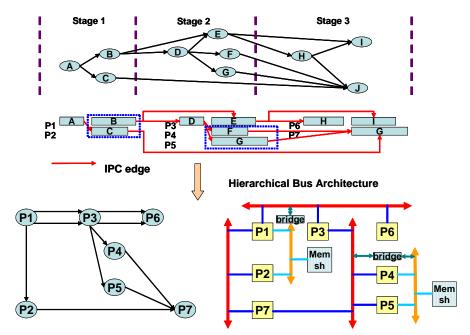

| Figure 69. | Hierarchical bus architecture synthesis based on data dependency of actors within a graph |

# Chapter 1: Introduction

As the complexity of functionality in modern embedded systems increases along with the rising demand for multimedia processing capabilities, embedded systems are increasingly incorporating image processing capabilities in various forms. Many image processing applications impose critical performance constraints, require high volumes of data processing, and also require tight resource usage due to cost considerations. System design factors such minimizing the amount of on-chip memory needed and the efficient configuration and utilization of digital signal processor cores become especially important and challenging under these considerations.

The decision on an appropriate system architecture is difficult due to conflicting requirements, such as the need for a cost- and power-efficient integrated circuit foot-print, and the simultaneous need for extensive data management, high throughput, and low latency. As technology advances for integrating multiple cores on a single integrated circuit, embedded multiprocessor platforms become attractive for addressing these challenges of image processing system implementation.

For such embedded multiprocessor platforms, image processing tasks must be scheduled effectively onto the available processors in a manner that effectively exploits the various forms of available parallelism, and the memory architecture must be organized and utilized to support high volume data buffering and efficient interprocessor communication. Useful to both of these steps is the application of appropriate design representations based on image-processing-oriented models of computation. Such representations expose high level application structure that designer and design

tools can use to explore the design space more efficiently, and derive more optimized and more predictable implementations.

This thesis addresses key problems in the design and implementation of multiprocessor image processing systems. In this thesis, we divide the embedded multiprocessor implementation process into the three inter-related phases of application modeling, task scheduling, and communication optimization, and we provide a comprehensive, integrated approach to these phases.

In the remainder of this chapter, we provide an overview of relevant background concepts and technology considerations, along with brief, motivational overviews of the methods that are developed in the thesis.

## 1.1 Background

### 1.1.1 Modeling

Modeling semantics based on dataflow graphs are used widely in design tools for digital signal processing (DSP). Dataflow is a directed graph called dataflow graph where vertices within the graph called actors represent computation and edges correspond to buffers between actors. These buffers hold data tokens which are delivered from the output port of one actor to the input port of another. An actor is ready for execution when all input ports of the actor have at least the minimum number of data tokens each input port requires for activation in the associated buffers. An actor consumes a certain number of tokens from its input ports and produces a certain number of tokens to its output ports when it is fired (executed).

Various kinds of dataflow models have been introduced for diverse purposes. Each dataflow model has different features and advantages in terms of expressivity and static (compile time) predictability of models. A common goal is to increase the flexibility of modeling an application in terms of expressivity while taking advantage of compile time predictability to reduce runtime overhead. Compile-time obtained information may include the estimation of a runtime memory usage and verification of valid schedule which guarantees the total number of data tokens produced within a dataflow graph is same as the total consumed number of data tokens within the same graph in one iteration.

#### 1.1.1.1 Synchronous DataFlow (SDF)

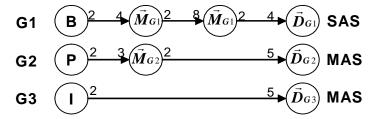

Lee and Messerschmitt[63] have proposed the synchronous dataflow (SDF) model. SDF assumes that the number of tokens produced/consumed by each actor within a dataflow model is known at compile time. SDF enables us to predict bounded memory usage including code and data size statically and generate valid schedules at compile time. An optimal static schedule depends on the size of code and the size of data. Various valid schedules can be obtained based on the number of data tokens produced/consumed and the repetition vector. The repetition vector represents the number of firings of each actor. The repetition vector can be obtained through matrix computation with data tokens produced/consumed by each actor. Figure 1 shows an example of SDF graph. e0 represents the edge between actor A and actor B. e1 is the edge between actor A and actor B. A topology matrix of Eq 1 for a connected SDF graph can be built based on the number of tokens produced/consumed between actors within a SDF graph. The positive sign is set for the number of tokens produced and a minus

sign is set for the number of tokens consumed. A balance equation is built with a topology matrix as shown Eq2. In a balance equation matrix Eq3 of figure 1, columns of a topology matrix correspond to actors. Rows of a topology matrix correspond to edges. Finally, repetition vector q in eq 4 is obtained by solving eq3.

$$\begin{array}{c|c}

A & 3 & 2 \\

\hline

& e0 \\

\end{array}$$

B  $\begin{array}{c|c}

1 & 1 \\

\hline

& e1 \\

\end{array}$

C

**SAS: 2A3B3C, 2A3(BC)**

MAS: ABABBCCC, ABABCCBC, ABCABCBC

b) valid schedules of a)

Figure 1. Example of SDF graph

$$T(e, v) = \begin{bmatrix} prd(e) & \text{if } v = src(e) \\ -cns(e) & \text{if } v = src(e) \\ 0 & \text{otherwise} \end{bmatrix}$$

(1)

$$T \bullet q = 0 \tag{2}$$

$$\begin{bmatrix} 3, -2, 0 \\ 0, 1, -1 \end{bmatrix} \bullet \begin{bmatrix} q_1 \\ q_2 \\ q_3 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

(3)

$$q = [2, 3, 3] \tag{4}$$

Figure 1 b) shows that figure 1 a) could have various valid schedules. For example, *SAS* in figure 1 b) represents a single appearance schedule where each actor appears only once in a schedule by exploiting looped schedule. SAS is good for reducing a code size. *MAS* in figure 1 b) is a multiple appearance schedule where each actor could appear multiple times to reduce buffer size between actors. For example, *SAS* schedule 2A3B3C requires 6 tokens between actor A and actor B. *MAS* schedule ABABBCCC requires only 4 tokens between actor A and actor B. Thus, *MAS* is likely to be a better choice due to the advantage of further buffer size reduction at the expense of some code size increase when a buffer size dominates a total memory area

used. Despite the benefits of a static scheduling and a memory manage of SDF, as the need for the flexible expressivity for dataflow graphs increases, many other dataflow models are introduced.

#### 1.1.1.2 Cyclo-Static DataFlow (CSDF)

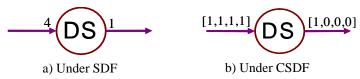

As an extension of SDF. Cyclo-Static DataFlow (CSDF)[25] allows for modeling a dataflow graph whose actors can support a cyclic change of the number of data produced/consumed. Thus, over each iteration of a dataflow graph, actors under CSDF semantics can have different production and consumption rates in a cyclic and periodic pattern. Cyclo-Static DataFlow is more flexible than SDF in terms of the expressivity while maintaining a static predictability of a bounded buffer memory of SDF. For example[77], for the case of down-sampler actor by factor 4, in SDF semantics, the actor should wait for firing until the input port of the down-sampler actor holds at least 4 tokens. In CSDF semantics, the behavior of the down-sampler can be described in four different phases. The actor takes one token at the input port and produces one token through its output port for the first phase. And then the actor can take one token from its input port and produces zero token to the output port for the following three phases. Figure 2 shows the comparison of modeling of a down-sampler actor each under SDF and under CSDF semantic.

DS:Down sampler actor

**Figure 2.** Comparison of a down-sampler actor by factor 4 each under SDF and under CSDF

CSDF, as a generalization of SDF, increases the expressivity of dataflow model

but inevitably causes the complicated scheduling problem. As well, operational patterns of actors of dataflow under CSDF semantic are confined to be periodic. However, many image processing applications have the feature of unpredictable changes of the number of tokens produced/consumed in a non periodic manner. CSDF has the limitation to fully adopt the diverse needs of various complicated image processing applications.

#### 1.1.1.3 MultiDimensional Synchronous DataFlow (MDSDF)

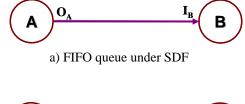

SDF and other dataflow models takes only one-dimensional signal processing channel FIFO buffers and the associated one dimensional algorithms. As the demand for the multi-dimensional data processing increases, the efficient way of modeling two dimensional or higher dimensional data is necessary. As a generalized extension of SDF, multidimensional synchronous dataflow (MDSDF) is introduced. MDSDF extended the one dimensional FIFO queues used in SDF to array types of FIFO queues. Figure 3[70] shows the comparison of FIFO queues between a SDF model and a MDSDF model. In MDSDF, FIFO queue holds two dimensional data tokens. A balance equation for figure 3 a) is shown Eq 5. A balance equation of figure 3 b) under MDSDF can be extended to two balance equations for each dimension as shown in Eq 6. r represents repetition vector. O is the number of tokens produced. I is the number of tokens consumed.

$$r_A \cdot O_A = r_B \cdot I_B \tag{5}$$

$$\begin{array}{l} r_{A,\,1} \cdot O_{A,\,1} = r_{B,\,1} \cdot I_{B,\,1} \\ r_{A,\,2} \cdot O_{A,\,2} = r_{B,\,2} \cdot I_{B,\,2} \end{array} \tag{6}$$

b) FIFO queue under MDSDF

**Figure 3.** Comparison of FIFO queues under SDF and MDSDF model

MDSDF increases flexibility and expressivity while maintaining static schedulability of SDF model. However, as the data dimension and the complexity of an application graph under MDSDF increase, there is a high chance that unexpected errors can be smeared in the modeling process by a designer due to its dimensional complexity. As well, multidimensional distinction of data tokens leads to complicated scheduling problems even though MDSDF preserves data parallelism and functional parallelism through dimensional distinction of data tokens.

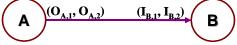

#### 1.1.1.4 Boolean DataFlow (BDF)

Boolean dataflow (BDF) model by Buck[18] allows for each port to hold either a constant or a two-valued function for controlling a dataflow. This function is placed on a control port of an actor. A control token delivered through a control port of an actor controls the number of tokens transferred by a conditional data port. BDF extends the scheduling method for SDF graphs to process BDF actors with conditional ports, by associating symbolic expressions with conditional ports. By adding two simple control actors with a control port such as switch and select, conditional constructs like if-then-

else and do-while loops can be built under BDF.

Figure 4. Control flow decision under BDF

Figure 4 shows how the switch actor and the selector actor under BDF semantic determine the number of tokens for an output port and an input port depending on a control token. In figure 4, the switch actor and the selector actor are BDF actors that take one token from the control input port and determine either a *True* route or *False* route depending on whether the value of the control token on *enable* in figure 4 is true or false.

A conditionally transferred data token allows for the runtime flow of a control to be determined based on the values of tokens on control ports. At compile-time, a scheduler analyzes the change of control flows based on values of control tokens. This enables us to build an annotated schedule which is a compile-time schedule where each firing of a BDF actor is linked with the runtime firing conditions.

BDF allows runtime change of a data flow while exploiting the benefit of compile time scheduling technique. However, BDF leads to the addition of redundant ports and paths for control token delivery. The change of token values of a BDF actor is limited to two cases. Building various conditional paths with multiple token values leads to a complicated graph topology with many switches and selectors.

#### 1.1.1.5 Parameterized Synchronous DataFlow (PSDF)

A parameterized dataflow modeling emphasizes a hierarchical modeling of a dataflow and relates the underlying hierarchical dataflow to a subsystem. A parameter-

ized dataflow modeling framework allows a subsystem's behavior to be controlled by a set of parameters. These parameters can change at runtime by allowing the subsystem behavior to vary dynamically. Parameters can control the functional behaviors of subsystems as well as the token flow behavior of a dataflow graph. In parameterized dataflow model, the model can have different parameter configurations at each iteration of a graph. But, after parameters are configured, parameters are held during the corresponding iteration of a graph. Parameterized dataflow modeling is a meta-modeling technique which allows schedules of a graph to be expressed with meta variables of parameters enabling the use of quasi-static scheduling.

In quasi-static scheduling, the number of firings of actors could be annotated with meta-variable coefficients related to the values of parameters and those meta variable coefficients could be determined at runtime whereas firing orders of actors are determined at compile time. Thus, parameterized models allows dynamic reconfiguration of parameters.

Parameterized dataflow could be applied to any types of underlying dataflow graphs. As an extension of SDF semantic with parameterization, a parameterized synchronous dataflow (PSDF) is suggested.

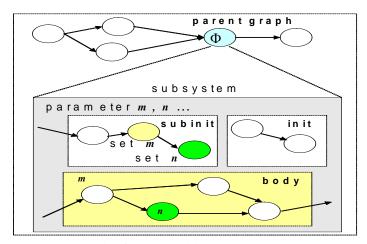

PSDF adopts a hierarchical modeling of parametrization. A hierarchy represents an abstraction of subsystem. Parameters are used to control the functional behavior of hierarchical subsystems. PSDF specification consists of three distinct graphs: the init graph, the subinit graph and the body graph. Intuitively, the body graph models the main functional behavior of the subsystem, whereas the init and subinit graphs control the behavior of the body graph by appropriately configuring the body graph parame-

ters. The init graph is invoked prior to each invocation of the associated (hierarchical) parent subsystem while the subinit graph is invoked prior to each invocation of the associated body subsystem, thus allowing for two distinct reconfiguration of controls. Figure 5 shows an example of PSDF graph. Parent Φ has three sub graphs. Subinit graph sets parameters of the body graph before the associated body graph is fired. PSDF increases the expressivity by adopting parameterized modeling, and exploits a quasi-static schedule. PSDF model allows runtime reconfiguration of a dataflow model.

Figure 5. Example of PSDF model

# 1.1.2 Scheduling[94,95,96,97]

Mapping an application graph onto a multiprocessor architecture needs three major steps; **processor assignment**, **actor ordering** and **actor invocation**. The process assignment step corresponds to assignment of actors to processors. The actor ordering step is ordering the execution of tasks assigned to the same processor. The actor invocation step determines the time at which each actor starts execution. Actors are assumed to be non-preemptive. Once an actor is invoked on a processor, the pro-

cessor is allocated to the actor until the invocation completes. This is because preemption leads to a significant runtime context switch overhead and is of limited use in time-critical DSP embedded applications. These three steps can be performed at runtime (dynamic) or at compile time (static) depending on scheduling strategies.

Lee and Ha [64] suggested a scheduling taxonomy depending on scheduling strategies from a fully dynamic approach to a fully static approach. Performing as many of the three scheduling tasks as possible at compile reduces run time overhead specially for the applications with hard real-time constraints. Performing processor assignment and actor ordering at compile time is useful for a time-critical DSP applications. In general, runtime assignment and ordering allows a more flexible run time variations in terms of managing available hardware resources.

Depending on scheduling strategies, scheduling methods can be divided into four categories; fully static, self-timed, static assignment and fully dynamic scheduling.

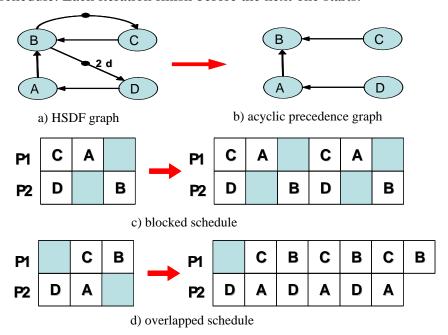

In scheduling an application over multiprocessors, homogeneous SDF graph (HSDFG) is useful. In HSDF, every actor consumes and produces only one token from each of its inputs and outputs. A multirate SDF graph can be converted into an HSDF graph [61]. This conversion may lead to significantly increased number of actors in HSDF graph. However, this conversion process simplifies scheduling an application modeled by dataflow graph over multiprocessors. For algorithmic simplicity, HSDF graph can be converted into Acyclic Precedence Graph (APG) by removing edges with delays and replacing multiple edges between the same two actors in the same direction with a single edge. APG removes multiple edges leading to the identical precedence.

As a performance evaluation metric of schedules, the average iteration period (or makespan) is widely used. The average iteration period (or makespan) is time taken to execute all the actors in the graph once.

#### 1.1.2.1 Fully static schedule.

In a fully-static strategy, assignment, ordering, and invocation are all performed at compile-time. The exact firing time of each actor is also determined at compile time. This technique is applied to scheduling VLIW processors [59] and synthesizing VLSI systems with guaranteed worst-case execution times[57].

Fully-static schedule can be expressed as a Gantt chart. In a Gantt chart the processors are arranged along the vertical axis. Elapsed times are marked along the horizontal axis. The actors are displayed as rectangles whose horizontal lengths correspond to the execution time of the actor. The left side of each rectangle in the Gantt chart corresponds to a starting time of the associated actor. Scheduling can be displayed by filling a Gantt chart with actors based on scheduling technique while minimizing the total schedule length and idle time slots.

Fully static schedules can be divided into two categories (blocked schedule and overlapped schedule) depending on the way of placing successive iterations of the HSDFG onto a Gantt chart.

#### 1.1.2.1.1 Blocked schedule

In a blocked schedule, each iteration of the HSDFG is scheduled separately. Namely, executions of all actors in the previous iteration complete before the next iteration begins. Thus, dependencies between iterations are not considered. The schedule is

assumed to be repeated in a infinite periodic manner. Under a blocked schedule, the length of the critical path of the graph becomes a makespan.

#### 1.1.2.1.2 Overlapped schedule

In an overlapped schedule, operations within a successive iteration of a graph can be overlapped with a previous iteration. To exploit an overlapped schedule, unfolding and retiming techniques are widely used. Unfolding schedules N iterations together where N is a blocking factor to improve a blocked schedule. However, unfolding leads to the increase of program size and complexity. Retiming manipulates delays in the HSDF graph to reduce the critical path in the graph[32,61].

Figure 6 [94] shows an example of a fully static schedule. Figure 6 c) shows a blocked schedule. Each iteration finish before the next one starts.

Figure 6. Fully static schedule

Figure 6 d) displays an overlapped schedule. Successive iterations in the HSDFG overlap. An overlapped schedule improves a makespan of a HSDF graph. The

makespan of the blocked schedule of Figure 6 c) occupies 3 time slots whereas the makespan of Figure 6 d) occupies 2 slots.

#### 1.1.2.2 Self-timed schedule[60,61]

The fully-static strategy requires a precise estimation of actor execution times for processor communication synchronization and doesn't allow for the variations of execution times of actors. Self-timed schedule loosens this tight requirement by allowing the variations of execution times of actors. After the fully-static schedule, only the processor assignment and the firing orders of actors on each processor are retained while removing timing information among actors. Each processor holds a firing order of actors allocated to the process. Communication synchronization is performed at runtime by the associated processors. Runtime synchronization increases IPC cost and leads to a runtime bus arbitration. To reduce runtime communication cost, ordered transaction is introduced. Ordered transaction holds three scheduling information; the processors assignment, actor ordering and communication order at compile time. By making processors accesses to shared communication hardwares in an compile time obtained order, runtime arbitrations overhead can be alleviated.

#### 1.1.2.3 Static assignment and dynamic scheduling

In a static assignment, only assignment of actors on processors is performed at compile-time but ordering and invocation of actors are performed at runtime. In fully dynamic scheduling, assignment, ordering, and invocation are all performed at runtime which is based on greedy approach and only guarantees locally optimal decisions. Dynamic scheduling also leads to resource contention problems at runtime. A static

scheduling approach may often lead to a better result.

This thesis provides an elaborate scheduling technique by applying a self-timed scheduling strategy to a pipelined processor manner while considering various constraints requirements.

#### 1.1.3 Communication optimization

The communication optimization stage includes post optimization processes such as resource mapping or software communication optimization depending on application specific requirements and limitations. For example, after scheduling, a trade-off between resource costs and performance or between low power and high performance can be further exploited depending on priorities of an application's requirements. Applying the appropriate hardware or software communication optimization techniques can lead to reduced system cost or improved energy saving without sacrificing performance loss. This thesis studies two cases of an application specific post optimization technique each in terms of an efficient hardware mapping for resource cost reduction and a dataflow cutting technique for low power consumption.

In a hardware resource mapping study, this thesis contributes toward reducing hardware costs of FIFO buffers within a dataflow graph by analyzing data dependency of a dataflow graph without sacrificing performance loss. In a dataflow cutting technique, this thesis performed the case study of a sensor network application optimization in terms of power consumption minimization combined with the overall system performance improvement in conjunction with effects of communication traffic change on a sensor network.

### 1.2 Overview of the suggested techniques

In this section, brief descriptions of novel algorithms suggested in this thesis will be given in each category of system synthesis; modeling, scheduling and communication optimization. In modeling category, this thesis suggests two novel modeling techniques; Blocked DataFlow (BLDF) and Dynamically configured graph topology(DGT). In scheduling category, this thesis suggests a new multiprocessor based scheduling technique named Pipeline Decomposition Tree (PDT) scheduling. For communication optimization, this thesis suggests two new algorithms for communication optimization for a hardware and software mapping of a dataflow graph.

#### 1.2.1 Modeling

#### 1.2.1.1 Blocked DataFlow (BLDF)

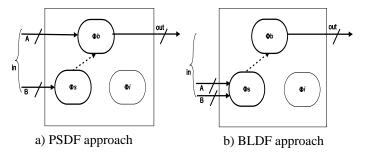

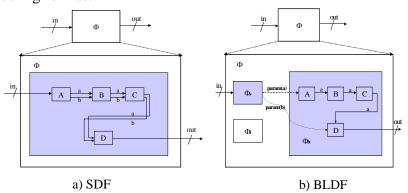

In the digital signal processing (DSP) domain, rapid prototyping tools based on coarse-grain dataflow semantics are widely used [10]. One important requirement in these tools is support for block-based processing, such as that involved in image and video applications. A number of efforts have examined block processing at the level of individual actors. The scalable synchronous dataflow (SSDF) [53] model formalized this concept in the context of multirate dataflow graphs, and algorithms have been developed to extract the maximum vectorization potential from an SSDF graph [83]. More recently, retiming techniques have been explored for manipulating homogeneous dataflow graphs (graphs in which the production and consumption parameters are all equal to one) to improve vectorizability [58]. The objective in such vectorization is to improve throughput and reduce context-switching overhead by executing

actors many times in succession. BLDF(Blocked Dataflow) suggested in this thesis differs from these approaches in its applicability beyond the level of individual actors, and into arbitrary subsystems at any level of the modeling hierarchy. BLDF also differs in its close integration with parameterized dataflow semantics [9], which allows for powerful dynamic reconfiguration capabilities.

Modeling semantics based on dataflow graphs are used widely in design tools for digital signal processing (DSP). This thesis develops efficient techniques for representing and manipulating block-based operations in dataflow-based DSP design tools. In this context, a block refers to a finite-length sequence of data items, such as a sequence of speech samples, an image, or a group of video frames, as part of an enclosing data stream. We develop in this thesis a meta-modeling technique called blocked dataflow (BLDF) for augmenting DSP design tools with more effective blocked data support in an efficient and general manner. We compare BLDF against alternative modeling approaches through a detailed case study of an MPEG 2 video encoder system.

As dataflow modeling alternatives emerge further it is highly desirable to identify new modeling features that can be achieved through novel applications of existing models rather than defining a totally new dataflow variant for each new extension. This promotes reuse and integration rather than reinvention of the growing body of knowledge on established dataflow styles. BLDF adheres to this approach by defining general mechanisms that can be used to augment existing dataflow models with systematic data grouping capabilities. It is in this sense that we refer to BLDF as a metamodel. BLDF can be used with the well-known decidable dataflow models, SDF,

CSDF, MDSDF, and SSDF, as described above. Its use with other, more dynamic models such as boolean dataflow [17] and SBF [46] may be possible, although efficient application to such models requires further investigation.

Blocked data token delivery of BLDF enables us to reduce dimensions of MDSDF [70] by processing multi dimensional data tokens dimension by dimension with blocked data processing of nested BLDF subsystems. At the same time, BLDF can be used in conjunction with MDSDF, with BLDF parameter control used to define the boundaries of processing to be performed using MDSDF semantics.

We develop in this thesis a blocked dataflow (BLDF) modeling approach for efficient handling of block-based data in dataflow-based DSP design tools. BLDF combines meta-modeling, block-based processing, multidimensional representation, and dynamic parameter reconfiguration in a single, unified framework that leads to more efficient dataflow graphs for scheduling and software synthesis.

Blocked dataflow builds on parameterized dataflow semantics[9]. BLDF inherits most features of parameterized dataflow [9]. Thus, a BLDF specification (or subsystem)  $\Phi$  also consists of three distinct graphs: 1) the *init* graph  $\Phi$ i; 2) the *subinit* graph  $\Phi$ s; and 3) the *body* graph  $\Phi$ b. Intuitively, the body graph models the main functional behavior of the subsystem, whereas the init and subinit graphs control the behavior of the body graph by appropriately configuring the body graph parameters. The init graph is invoked prior to each invocation of the associated (hierarchical) parent subsystem, parent  $(\Phi)$ , while the subinit graph is invoked prior to each invocation of the associated body subsystem  $\Phi$ b, thus allowing for two distinct "frequency levels" of reconfiguration control [9]. In a blocked dataflow subsystem, blocks of input

data are treated as subsystem parameters, and the initialization graphs (the subinit or init graphs, as described below) are used in-between processing of successive blocks to change the value of the associated block-parameter. Thus successive blocks of data are translated into successive reconfigurations of block-parameter values.

For example, consider an image processing system that performs a given filtering operation on a stream of input images. A blocked dataflow representation might define the processing of a single image using a dataflow graph  $G_c$ . The graph  $G_c$  operates on input from a special *image source* actor that is parameterized with an image I. The image source actor simply transfers its image parameter to its output according to the desired protocol. The transfer protocol involves both rasterization aspects, and may also involve sub-blocking (e.g., outputting the image as a sequence of row blocks). Such sub-blocking can be used to defined nested BLDF subsystems.

## 1.2.1.2 Dynamically configured graph topology(DGT)

Dataflow is widely used for designing DSP applications. Despite its intrinsic advantages, one weak point is its difficulty in flexible expression of applications with data dependent change in execution structure. To handle data driven changes in execution structure, several dataflow models such as CDDF [109], BDF [18], and BDDF [75], have been proposed. CDDF uses control tokens to determine the token transfer at an actor port. However, determination by a control token is applied to the actor in the next phase of execution, therefore, control tokens are not present at the moment that the actual phase is determined. BDDF introduces dynamic ports and an upper bound is provided for the data rate so that each dynamic port can keep the model bounded. However, control flow depends on FSMs. Using FSMs for minor changes of control

flow with dataflow graphs can make application models unnecessarily complicated and result in limited flexibility. BDF provides "SWITCH" and "SELECT" actors to determine control flow. For satisfying bounded memory and consistency, a symbolic function of probability is introduced. This function increases the complexity of solving the balance equations (for verifying sample rate consistency), and results in the possibility of "weak consistency," which is less desirable in an implementation. This thesis suggests an approach to providing dynamically configured dataflow graph topologies using a new modeling and synthesis technique called DGT (Dynamic Graph Topology). DGT builds on PSDF semantics [84]. All possible graph topologies for a given graph are obtained at compile time and the corresponding graph based on parameters and data is dynamically set up in an efficient manner at runtime before the invocation of the associated graph.

To provide for more powerful and efficient data dependent execution related to application mode changes, where entire graphs or subsystem are replaced or reconfigured at run time, this thesis tackles dynamic set-up of dataflow graph topologies before the graphs are invoked. All configurations of possible graph topologies are pre-computed at compile time and stored for usage at run time. At runtime, the initialization step of DGT generates an appropriate graph topology based on parameters extracted from data being delivered and picks up a pre-computed schedule to fit the current parameter configuration.

However, not all configurations are valid or can be obtained at compile time. Some configurations may cause deadlock or inconsistency or may not be predictable at compile time. Reconfiguration of dataflow graphs is carefully considered in [73].

[73] analyzes the reconfiguration of a model based on behavioral types and extracts the *least change context* to check approximate semantic constraints. This thesis statically checks the validity of each configuration like [73] and keeps the scheduling results for use at run time.

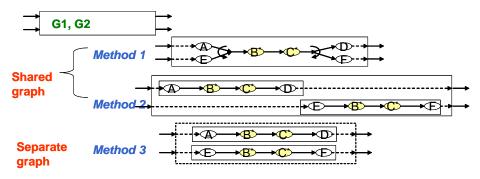

The main distinguishing feature of DGT is that it efficiently supports multi-function applications by configuring graph topologies dynamically. There are two kinds of multi-function applications. The first, which we call type-I applications, are exclusive-or applications, where only one graph topology is selected from multiple sets of possible graph topologies for a given application. The other, which we call type-II applications, are concurrent applications where two or more applications with different graph topologies are running at the same time. This thesis focuses on type-I (exclusive-or) application for experimentation of DGT. For synthesis of type-I applications, [40] extracted *commonality measures* of each actor and used these values to determine a hardware bias of each actor by hardware oriented partitioning. This thesis focuses on software implementation, and applies novel scheduling techniques based on graph characteristics to reduce code and buffer size, which is critical for DSP software.

Systematic methods for reducing code and buffer size are applied based on characteristics of each configured graph. We have compared DGT against conventional modeling approaches through a detailed case study of an MPEG 2 video encoder system, and our experiments demonstrate the efficiency of the DGT approach. The DGT approach provides efficiency and flexibility in modeling applications with data driven change of graph topology from runtime parameter changes by using pre-computed information (information related to graph topology, scheduling, code/buffer size,

bounded memory, etc.).

### 1.2.2 Scheduling

### 1.2.2.1 Pipeline Decomposition Tree (PDT) scheduling

Scheduling an application under multiprocessors environment is a NP hard problem due to its complexity. Many heuristics or evolutionary[2][19][23][28][115] efforts have been proposed. Evolutionary algorithm can be used in case a deterministic algorithm cannot be easily applied. Under evolutionary approach, the manipulation of the effect of external constraints on the scheduling results is difficult due to its non deterministic optimization process. Besides an evolutionary approach, many heuristic algorithms have been exploited. Banerjee. [7] presented two-step approach by separating partitioning and process allocation under heterogeneous architecture. Hoang. [32] suggested a heuristic algorithm by providing detailed IPC cost model. Konstantinides. [53] tackled detailed issues in modeling I/O by subdividing I/O parts into sequential I/ O parts and parallel I/O parts. However, these approaches overlooked the benefit of potential data parallelism that most DSP applications commonly have. Exploiting data parallelism contributes toward speed-up. Subhlok. [99] tackled data parallelism along with task parallelism for scheduling. However, this approach mainly focuses on a linearly chained dataflow. Applying data parallelism and task parallelism to an application with non-linearly connected dataflow paths causes more complicated and various difficult problems.

Modern embedded systems for digital signal processing (DSP) integrate more and more complicated functions in one system. As the complexity of functionality increases, considering multiple processing units in one system is inevitable. The demand for the real-time response also grows along with various functionalities. Integration of multiple functions under tightly environmental constraints causes many complicated problems. Many made for schedulefforts have been ing[29][37][69][78][93]and integrating an application over multiple processing units[10][11][12][13][14][29][71][85]. Researches mainly tend to focus on partial interactions of the overall problems environmental constraints may cause [3][65][68][74].

An application can be expressed as a dataflow graph of tasks. Many efforts tack-ling task dependencies of a graph have been widely taken to distribute the workloads of tasks over multiple processing units[85][86][93][97]. However, the internal operational features of each task was not widely exploited. Internal operations of a single task can be copied to multiple tasks and copied tasks can run in parallel over multiple processors. Finally a response time of the application can be reduced.

PDT scheduling (Pipeline Decomposition Tree) by exploiting both heterogeneous data parallelism and task parallelism. In general, data parallelism allows multiple copies of a single task to run on multiple processing units. Operation of each task is independent of each other. Each copied task handles different sequences of data frames. Thus, a general data parallelism increase the overall buffer size since separate memory regions are required for holding different sequential data frames.

PDT scheduling suggests heterogeneous data parallelism model. Heterogeneous data parallelism is an extension of data parallelism. A single data frame can be divided

into smaller sub areas named copy-set. A sets of copied tasks can handle different copy-sets within a single data frame whose size can vary depending on available processors. Each copy-set can also be divided into sub regions. Thus, a single data frame consists of several copy-set-regions. Each copy set consists of sub regions. The size of a sub region is obtained by dividing the copy-set-region by the number of copied tasks allocated to the corresponding copy-set. Thus, all sub regions within a single copy-set are of the same size. But, the sizes of copy-set-regions may or may not be the same depending on available idle processors. The copy-set-region is an array of data tokens in a multi dimensional data stream frame, especially, two dimensional data tokens for most 2-D based image processing applications. Copied tasks can be allocated to different copy-sets whose sizes can vary. But, copied tasks allocated to the same copy-set handle the same size of sub regions within the corresponding copy-set-region. The number of tasks in a copy-set may vary from 1 to N depending on available idle processors. Ultimately, heterogeneous data parallelism allows for dynamic change of the size of sub regions and handles a single data frame by multiple processors without increasing the buffer size while exploiting the parallelism. The suggested technique tackles task parallelism by exploiting a pipelined architecture for the high throughput. The suggest scheduling technique provides constraints satisfactory solution by taking into consideration IPC communication cost model of a separate memory architecture[21][56][106][112] and a bus contention model of a shared memory architecture. Constraints could be the limitation of on/off chip memory size[100][108][113], latency, or throughput etc.

Most embedded systems for digital signal processing (DSP) integrate an image

processing application. The common feature of image processing applications is parallelism. The completion of the whole operations of a single task is based on an unit operation and each unit operation requires only a subset of neighboring data and each unit operation is independent of each other. This neighboring data can be a block or a window. The unit operation is called a **window based operation** in this thesis. The window based operation enables us to exploit potential parallelism by running a single task over multiple processors by task duplication[1][22][47][80]. This potential parallelism by a window based operation is called a **data parallelism** [55][81]. Data parallelism hasn't been deeply exploited for a multi-processors based scheduling compared to **task parallelism**. Task parallelism exploits pipelined scheduling for improving throughput[4][16][20][26][36]. This thesis tackles heterogeneous data parallelism and task parallelism together for improving latency and throughput at the same time.

A lot of tasks in DSP applications have the feature of heterogeneous data parallelism due to their window based operation patterns. The representative application examples with a window based operation are image processing applications. We selected a complex image processing module consisting of multiple morphological operations like opening, closing, gradient, Laplacian, smoothing and top-hat simultaneously, Laplacian pyramid, Multi-resolution spline pyramid and MPEG2 encoder for experimentations.

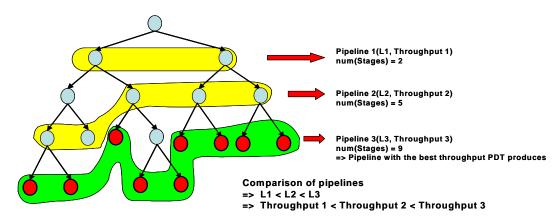

Our scheduling algorithm basically chooses a pipelined architecture. Each stage of the pipeline can be mapped to multiple processing cores, which may or may not span over multiple DSP chips depending on the synthesis constraints. To determine the number of stages in a pipeline, this thesis suggests a new algorithm called **PDT**(Pipe-

line **D**ecomposition **T**ree) exploration process, which builds pipelines by a depth first search tree. By **PDT**, tasks are partitioned into stages of the pipeline[44][101]. Depending on a task dependency and relationship between neighboring tasks, different memory architectures and bus architectures are considered by **PDT scheduling**. The suggested scheduling technique contributes toward finding a constraints satisfactory solution in consideration of memory architectures along with the studies of the associated communication models such as IPC model from a separate memory architecture or a bus contention model of a shared memory architecture.

### 1.2.3 Communication cost

### 1.2.3.1 Hardware communication optimization

Various efforts on dataflow graph mapping onto hardware implementations have been undertaken. For example, the approach of [30] exploits loop parallelism to map nested loop kernels onto a coarse-grained reconfigurable architecture. The approach of [33,34] uses direct mapping of each dataflow graph component (actor) onto the corresponding hardware resource. The approach of [38] uses shared resources and looped schedules. The approach of [40] analyzes a given set of applications to extract commonalities across nodes in different applications and uses them to bias the mapping of nodes in the partitioning process. For FPGA implementation, the approach of [92] provides a rapid system prototyping method through a component architecture and an associated set of software tools. The approach of [103] provides a pipelined asynchronous circuit mapping method. For pointer synthesis, the approach of [87] encodes pointer values and generates circuits that can dynamically access different locations

with each pointer reference. The approach of [105] points out that pointers can reference indices to RAM, registers or even wires in a hardware mapping. The approach of [8] applies an external memory for mapping FIFO buffers and implements real-time image convolution on an FPGA. The approach of [72] implements image processing applications on FPGAs and points out that such implementations lead to a large on-chip FIFO buffers that prevent flexible usage of FPGAs for image processing applications. The approach of [104] presents an elaborate technique for mapping global, static arrays to distributed communication structures while classifying four types of interprocess communication patterns. The approach of [110] studies memory optimization for embedded software, particularly the performance of cache-based systems. The approach of [107] presents a novel technique for background memory allocation in multi-dimensional signal processing applications based on dataflow analysis.

The efforts described above make useful contributions toward mapping application representations at various levels of abstraction into hardware implementations. However, the simultaneous analysis of both performance and cost implications when mapping image processing applications, which involve especially large volumes of data token delivery, has not been thoroughly investigated in previous work.

This thesis helps to bridge this gap by studying, in the context of mapping dataflow graphs into hardware, the relationship between token delivery methods (indirect, pointer-based token delivery vs. direct-reference, raw token delivery) and FIFO architecture. This thesis exploits pointer-based token delivery to reduce on-chip FIFO sizes, and also provides a range of efficient trade-offs between performance (latency and throughput) and FPGA resource cost through a novel FIFO mapping algorithm. This thesis also shows how overall performance and cost vary in relation to the selected sub-frame size at which block processing is carried out. Finally, this thesis provides a new mapping algorithm for dataflow representations of image processing applications to reduce overall FPGA resource costs without significant performance loss.

### 1.2.3.2 Software communication optimization

This thesis studies a software communication optimization technique under the sensor network application domain in terms of power consumption minimization of a sensor network system and provides a dataflow graph cutting technique for mapping the divided graphs over multiple sensor nodes for minimizing communication traffics. In a sensor network, energy consumption of a sensor node is related to a network lifetime. To increase the network lifetime, low power friendly design of a sensor network is necessary. Many efficient approaches are suggested to reduce an energy consumption of a sensor network. [89] distributed FFT function over a master node and slave nodes to reduce energy consumption without consideration of data traffic change by moving FFT function from a cluster head node to slave nodes. [54] provides a tradeoff of an energy and a latency by considering different computational capabilities for a master node and a slave node. However, [54] didn't consider the potential possibility of using a low computational micro controller by balancing functional workloads over sensor nodes. [66,91] suggested a hierarchical and physical layer driven sensor network design to reduce data traffic and energy consumption of a sensor node in connection with each physical function. However, the node optimization should be optimized in conjunction with a underlying protocol characteristics and change of data transmission method depending on specific characteristics of network related devices. This

thesis suggests an overall minimization of an energy consumption of a sensor network in connection with a trade-off of latency and network lifetime by balancing workload of each sensor node. This thesis exploits internal token flows of an application dataflow graph and divides the application over a master node and slave nodes by applying dataflow modeling technique. A sensor network application can be efficiently modeled under a dataflow semantics. By analyzing dataflow graph modeling an application[11,18,40], energy consumption and operational complexity of an application can be effectively estimated in a coarse grain level. Especially, parameterized dataflow semantic[9] is intrinsically friendly to reconfigurable demands of most sensor network applications. Parameterized dataflow allows for dynamic change of meta variables which can be mapped to internal parameters of an application. This thesis selects DGT[48] (Dynamic Graph Topology) method for modeling an application. DGT inherits from a parameterized dataflow and provides more efficiency by allowing for dynamic change of graph topologies based on runtime request. In DGT semantics, connection between nodes and the number of tokens produced/consumed by each node can be changed at runtime and be expressed along with reconfigurable parameters. This feature enables a master cluster to control slave nodes efficiently and allows each sensor node to support various graph topologies.

# 1.3 Contributions of this thesis

# 1.3.1 Modeling

In this thesis, we challenge new modeling techniques for image processing appli-

cations under a dataflow semantic while exploiting blocked processing and dynamic reconfigurability. This thesis suggests two new dataflow based modeling techniques named Blocked DataFlow (BLDF) and Dynamically reconfigurable Graph Topology (DGT), respectively.

### 1.3.1.1 Blocked DataFlow (BLDF)

This thesis suggests a new modeling technique named Blocked DataFlow (BLDF). Unlike other dataflow models, BLDF exploits a blocked processing feature of data tokens in a dataflow graph, which makes it possible to model most image processing applications. In BLDF, a blocked processing feature of multi dimensional data streams can be allowed in an automated manner. BLDF model enables the firing numbers of each actor within a dataflow graph to be expressed in meta variables. Meta variables are obtained through parameterization of blocked data tokens. Parameterized firing numbers allow for quasi-static schedule which can be reconfigured at runtime by the subinit sub system during the parameterization process of blocked data frames.

#### 1.3.1.1.1 Iteration control

The major enhancement in BLDF is the delivery method of data tokens into body graphs. In BLDF, blocked data tokens such as sequential MPEG2 video streams are delivered via the parameter value updating process of init or subinit graphs so that an init or a subinit graph can extract information concerned for the associated body graph from raw data tokens delivered, and then convert raw data tokens as well as the information extracted into sets of new parameter values for the body graph. Thus, raw data

tokens are delivered to the associated body graph as parameters along with other parameters extracted from them before the body graph starts running.

Blocked tokens are transferred to the subinit graph and then converted into a block of parameters, which are set as parameters of each relevant actor in the associated body graph. Here, BLDF provides Dynamic configuration of parameters for the associated body graph such as image resolution and block size as basic processing units along with other provisional parameters at the stage of the subinit graph, which directs detailed operation of the associated body graph before that body graph starts an invocation of itself.

At the same time, iterations of each actor within a body graph can be obtained along with other parameters. Suppose, for example, that an init or a subinit graph takes a Z pixel frame from its input port. An init or a subinit graph can obtain  $Z/N^2$  iterations of the associated body graph actor by setting the *block size* parameter for the body graph as N by which image frames are divided into sub-image frames. Each actor within the body graph then operates on the basis of sub-image frames for high throughput and more parallelism. Iteration numbers may be used further as factors in a quasi-static looped schedule by a BLDF scheduler. Obtaining parameters relevant to the scheduling of the associated body graph before it runs and reconfiguring those parameters dynamically based on concerned payloads of tokens delivered at a runtime gives an application developer enhanced flexibility and efficiency in the design phase.

### 1.3.1.1.2 Token delivery

One of the advantages of BLDF is its efficiency in token delivery. First, in token delivery, BLDF enables us to reduce buffers required for delivering tokens among actors.

This is because tokens can be delivered from parent graphs to nested body graphs by parameterization. This parameterization process enables us to remove redundant connections and buffers between actors in BLDF.

#### 1.3.1.1.3 Data tokens with nested headers

Most multimedia data tokens consist of a *header* part and a *payload* part. The header part has the information for handling the payload. However, the payload also may have sub-header and sub-payload components. Therefore, each level of composite actors implemented hierarchically or heterogeneously may process a different area of a packetized multimedia data token. BLDF provides an efficient way for delivering data tokens to composite actors of lower hierarchical levels by parameterization. Only the relevant part needs to be decoded for configuration and the remaining parts can be encapsulated as parameters for composite actors of lower hierarchical levels in the dataflow specification. Decoding headers sequentially according to the need for the associated header information allows us to implement each module within an application consistently, which is easy to understand for future code reuse. This approach also reduces the number of connections and buffers required between actors by parameterization.

### 1.3.1.2 Dynamically reconfigurable Graph Topology (DGT)

### 1.3.1.2.1 Modeling of separate dataflow graphs in a single dataflow semantic.

This thesis suggests a new modeling technique named Dynamically reconfigurable Graph Topology (DGT). Unlike other approaches challenging the change of data/control flow within dataflow models, DGT allows separate individual dataflow graphs to be integrated in a single dataflow semantic. Under DGT semantic, vertices and edges within a dataflow graph can be categorized into two groups; fixed or varying. In DGT domain, Any vertex/edge whose topological behaviors are commonly constant among individual dataflow graphs can be marked fixed edge/vertex. Any vertex/edge not marked as fixed graphic components belongs to varying vertex/edge.

In DGT, the topological behaviors of varying edges/vertices can be dynamically changed based on the change of parameters or tokens being delivered while allowing for dynamic change of graph topologies and a single dataflow integration of separate individual dataflow graphs.

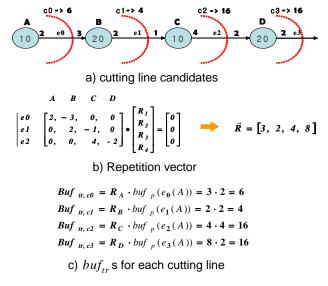

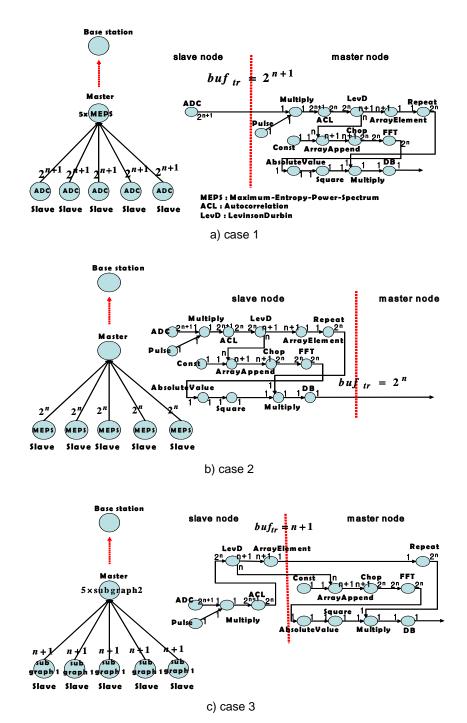

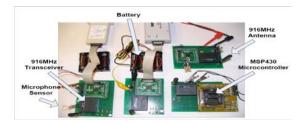

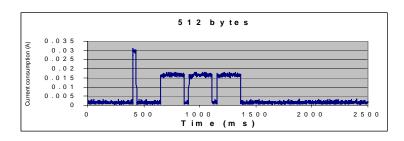

### 1.3.1.2.2 Minimization of resource usage among separate dataflow graphs