**ABSTRACT**

Title of dissertation:

ELECTROMAGNETIC BANDGAP

STRUCTURES FOR BROADBAND

SWITCHING NOISE MITIGATION IN

**HIGH-SPEED PACKAGES**

Shahrooz Shahparnia, Doctor of Philosophy, 2005

Dissertation directed by:

Professor Omar M. Ramahi

Mechanical Engineering Department,

Electrical and Computer Engineering Department

For the past two decades, silicon-based complementary metal-oxide semiconductor

(CMOS) technology and circuits have been advancing along an exponential path of

shrinking device dimensions, increasing density, increasing speed, and decreasing cost.

Electronic design complexity is in constant acceleration and new designs have to

incorporate new features, which inevitably will require faster processing time. In recent

years this acceleration rate has drastically decreased because of various constraints, such as

static power dissipation due to leakage current, the effect of wires and interconnects and the

decreased immunity of modern devices to noise, interference and voltage fluctuations on

their Power Distribution Network (PDN).

Lowering the power supply voltages and hence the power consumption of a single transistor, has been possible due to the fact that these new technologies are able to provide smaller and faster transistors with lower threshold levels. The benefits associated with lowering the threshold levels of the transistors used in a given device comes at a high-price, specifically the decrease of immunity of such device to noise and fluctuations of the power supply voltage.

The research work carried out in this dissertation, addresses the concept of embedding Electromagnetic Bandgap (EBG) structures in conventional power distribution networks in order to increase the immunity of the circuits that feed from such networks to noise and voltage fluctuations. Underlying theories of Embedded EBG (EEBG) structures and design methodologies are presented. Various design concepts, based on simulations, measurements and different modeling techniques developed during this research work are presented. The accuracy of these methods is analyzed by comparing results of these techniques with experimental results.

Also, this work shows that EEBG structures are not only very effective in the suppression of switching noise in high-speed circuit but also they suppress Electromagnetic Interference (EMI) caused by such switching and they provide increased immunity for their PDN to external sources of noise.

Finally new EEBG configurations, topologies and miniaturized structures are introduced that overcome the limitations of current switching noise mitigation techniques, including initial EEBG designs to provide immunity against high-bandwidth noise, voltage fluctuations and radiation, new EEBG configurations, topologies and miniaturized structures are introduced and their efficacy is demonstrated. The novel designs developed

during this research provide noise mitigation over a wide range of frequencies, and also extends the suppression frequency range into the sub-gigahertz region, only using a single EBG design with smaller patches than those used in previous works.

#### ELECTROMAGNETIC BANDGAP STRUCTURES FOR BROADBAND SWITCHING NOISE MITIGATION IN HIGH-SPEED PACKAGES

Shahrooz Shahparnia

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2005

#### Advisory Committee:

Professor Omar Ramahi, Chair Professor Amr Baz Professor Neil Goldsman Professor Victor Granatstein Professor Agis Iliadis © Copyright by

Shahrooz Shahparnia

2005

## **DEDICATION**

To my family, especially my grandmother Sedighe, my uncle Shahpour, my aunt Shahin, and my lovely wife Raha.

#### ACKNOWLEDGEMENTS

First and foremost I would like to thank my research advisor, Prof. Omar M. Ramahi. This research work would not have been possible without his invaluable guidance, support, encouragement and expert advice.

I would like to thank all current and former graduate students that I have met here during our time together in the electromagnetic compatibility and propagation lab. Specifically, I would like to thank Baharak Mohajer-Iravani, Mohammad H. Kermani, Lin Li and Xin Wu for the various technical discussions and Telesphor Kamgaing for his invaluable guidance in early stages of this research.

I would also like to thank Professor Granatstein, Professor Agis Iliadis, Professor Goldsman, and Professor Baz for their availability to serve on my dissertation committee.

I would like to acknowledge Maria Hoo, Cliff Russel and To Anh Chung on the staff of the ECE department at the University of Maryland for their constant support and help.

During my time at the University of Maryland I developed a large group of friends that now constitute a large family that I am proud to be part of. My special thanks to Nicola Pasquino, Antonio Cardone, Farshad Bahari, Alireza Modafe, Tullio Grassi, Marco Morresi, and. Erika Monnati.

I would like to thank my old friends Raha Zandifar, Babak Soroush, Shahriar Zand, Maziar Naseri, Maziar Khatir, Lila Torabi and Aram Pakravan for being there for me during the time that I was most in need.

I gratefully acknowledge the financial support of the ECE department, Institute for Research in Electronics and Applied Physics (IREAP), CALCE Electronic Products and Systems Center and the Electromagnetic Compatibility and Propagation Lab (EMCP).

At the end, it is hard to acknowledge all of you, friends, relatives, who have shaped my life in one way or the other individually, but be sure that I am very grateful for all you have done for me.

## TABLE OF CONTENTS

| Chapter  | 1. Intro  | oduction, Background and Objective of the Dissertation                                 | 1   |

|----------|-----------|----------------------------------------------------------------------------------------|-----|

| 1.1      | In        | troduction                                                                             | 1   |

| 1.2      | A         | natomy of Switching Noise in Electronic Power Distribution Systems                     | 4   |

|          | 1.2.1     | Electromagnetic Wave Propagation and Resonance in an Infinite Parallel-plate Structure | 6   |

| 1.3      | R         | esearch Objectives and Thesis Structure                                                | 10  |

| Chapter  | 2. Pow    | er Planes with Embedded Electromagnetic Bandgap (EEBG) Structure                       | s12 |

| 2.1      | E         | EBG Structures and the Switching Noise Suppression Concept                             | 12  |

| 2.2      | D         | esign Methodologies, Parameters and Issues                                             | 15  |

|          | 2.2.1     | Direct Experimentation                                                                 | 16  |

|          | 2.2.2     | Full-wave Analysis of a Complete Structure                                             |     |

|          | 2.2.3     | Dispersion Diagram Extraction                                                          |     |

|          | 2.2.4     | Double-symmetric Model                                                                 | 26  |

|          | 2.2.5     | Lumped Element Circuit Modeling                                                        |     |

|          | 2.2.6     | Periodically Loaded Transmission Line Modeling                                         | 37  |

| 2.3      | In        | nplementation of EEBG Structures, Experiments and Results                              | 46  |

|          | 2.3.1     | Plain Structures.                                                                      | 46  |

|          | 2.3.2     | Exotic Structures                                                                      | 50  |

|          | 2.3.3     | Design Considerations                                                                  | 53  |

| Chapter  | 3. Ultra  | a-wideband Noise Mitigation Using Cascaded EEBG Structures                             | 60  |

| 3.1      | D         | esign Concept                                                                          | 60  |

| 3.2      |           | nplementation, Measurements and Results                                                |     |

| Chapter  | 4. Elec   | tromagnetic Interference (EMI) Suppression using EEBG Structures                       | 70  |

| 4.1      | D         | esign Concept                                                                          | 70  |

| 4.2      |           | nplementation, Measurements and Results                                                |     |

| 4.3      | U         | ltra Wide-Band EMI Reduction                                                           | 75  |

|          |           | ndband Noise Mitigation Using Miniaturized EEBG Structures on High<br>terial           |     |

| Permitti | v11y 1V10 | WITHI                                                                                  |     |

| 5.1      | D         | esign Concept                                                                          | 85  |

| 5.2          | Simulation Results                                               | 89        |

|--------------|------------------------------------------------------------------|-----------|

| 5.3          | Implementation, Experiments and Results                          | 98        |

| Chapter 6. C | onclusions and Future Work                                       | 103       |

| 6.1          | Conclusions                                                      | 103       |

| 6.2          | Future works                                                     | 104       |

| Appendix A.  | Design of a monopole antenna over a ground plane using numerical | codes 106 |

| A.1          | Theoretical Designs                                              | 107       |

| A.2          | Design by Simulation                                             | 108       |

| A.3          | Practical Considerations and Measurements                        | 110       |

## LIST OF TABLES

| Table 2-1          | Comparison of periodically loaded transmission line model and Finite                                 |

|--------------------|------------------------------------------------------------------------------------------------------|

| Element (FE        | ) simulations: For all table entries $\varepsilon_{r2}$ is equal to 4.1. $Vd$ is the diameter of the |

| vias of the E      | EBG cells. In both FE simulations and in the model four cascaded single cells                        |

| have been co       | nsidered44                                                                                           |

| Table 2-2          | Results from experiments on sample EEBG structures shown in Figure 2-18.                             |

|                    | mm patches the attenuation of FR4 at the higher edge is more than 20 dB,                             |

|                    | gap never reaches the -20 dB line                                                                    |

|                    |                                                                                                      |

| Table 5-1          | Band-stop frequency range of various EBG structures derived by eigenmode                             |

| simulation us      | sing a finite element full-wave solver. (th = thickness, $f_l$ = lower frequency of                  |

| the gap, $f_h = 1$ | nigher frequency of the gap)94                                                                       |

|                    |                                                                                                      |

|                    |                                                                                                      |

| Table A-1          | Monopole antenna characteristics from simulations                                                    |

| Table A-2          | Input impedance of the monopole antennas at resonance from simulations 109                           |

| Table A-3          | Simulation results comparing ideal 2.45 GHz monopole vs. non-Ideal110                                |

| Table A-4          | Monopole antenna characteristics from measurements                                                   |

## LIST OF FIGURES

| Figure 1-1      | Switching noise generation mechanism in a PDN of a multilayer printed                  |

|-----------------|----------------------------------------------------------------------------------------|

| circuit board   | 6                                                                                      |

| Figure 1-2      | Diagram for an ideal parallel plate waveguide as a model for the power                 |

| planes of a P   | CB                                                                                     |

| _               | EBG structures embedded in PCBs: Switching noise generation, radiation and mechanisms. |

|                 |                                                                                        |

| Figure 2-2      | Efficacy range of different switching noise reduction methods                          |

| Figure 2-3      | Test setup for EEBG structures with patches of 20 mm x 20 mm. A separate               |

| one layer boa   | ard is mounted on top of this one as a second power plane                              |

| Figure 2-4      | Measurement setup using a Vector Network Analyzer (VNA). S21 is a                      |

| representativ   | e for transfer impedance between port 1 and port 2                                     |

| Figure 2-5      | Sample measurement for the setup depicted in Figure 2-3                                |

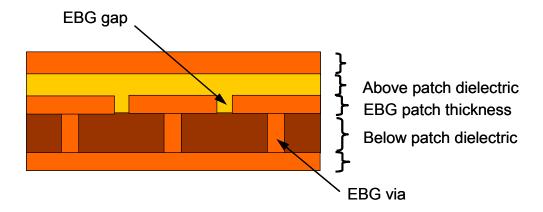

| Figure 2-6      | Lateral view of the PCB under test                                                     |

| Figure 2-7      | Diagram representing the simulation model used to extract the bandgap of an            |

| EEBG struct     | ture using dispersion diagrams. The computational domain includes a single             |

| cell. Periodic  | (Master/Slave) boundary conditions are placed in the x-z and y-z planes. The           |

| top and bott    | om planes of the cell are perfect electric conductors (PEC). The Brillouin             |

| triangle is she | own above the top plane24                                                              |

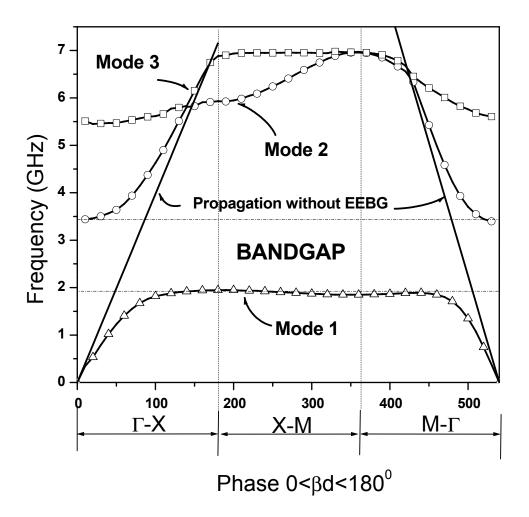

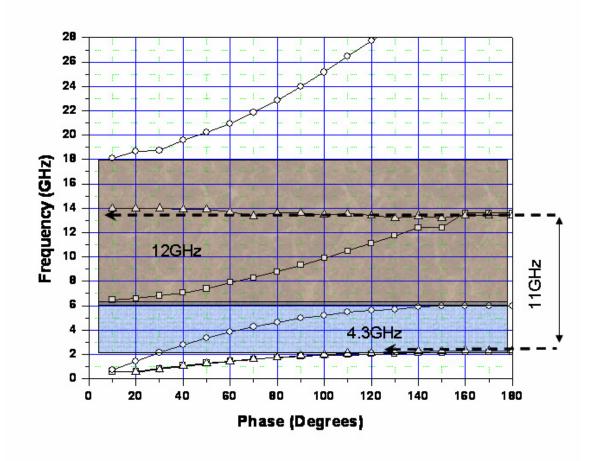

| Figure 2-8      | Dispersion diagram derived for an EEBG structure with dielectric material of           |

| dielectric cor  | nstant of 4.1, via diameter of 0.8 mm, gap size of 0.4 mm and board thickness          |

| of 3.08 mm.     | Patches are located at equal distances from the power planes between them              |

| and their size  | e is 12 mm x 12 mm                                                                     |

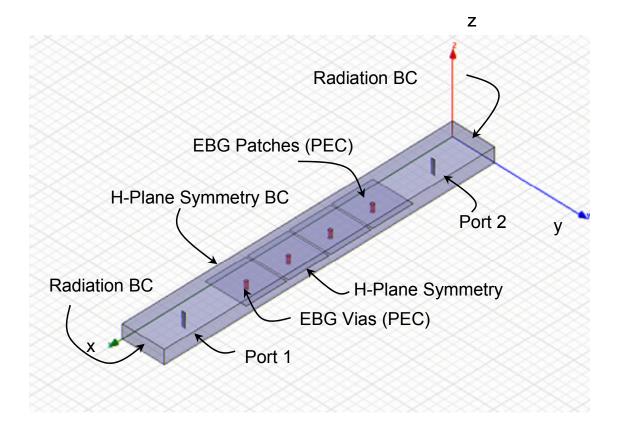

| Figure 2-9     | Diagram representing the simulation model used to derive the bandgap of an                                                                      |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| EEBG struct    | ure by extracting S-parameter. The computational domain includes a single                                                                       |

| cell. H-plane  | symmetry Boundary Conditions (BC) are placed in the x-z plane on the two                                                                        |

| sides of the s | tructure to resemble an infinite structure in the y direction. The top and bottom                                                               |

| planes of the  | cell are perfect electric conductors (PEC)                                                                                                      |

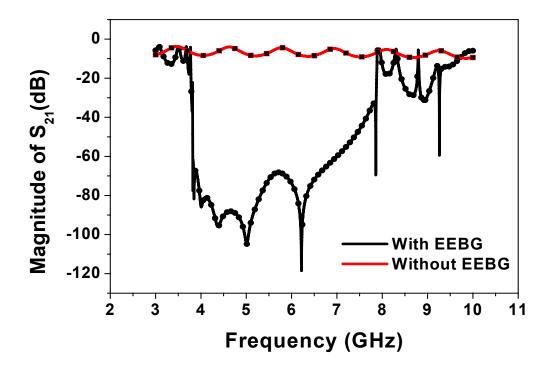

| Figure 2-10    | Typical result of double-symmetric simulations of the model in Figure 2-9                                                                       |

|                | 28                                                                                                                                              |

| Figure 2-11    | Model developed in previous studies for normal incident waves29                                                                                 |

| Figure 2-12    | Proposed model developed for waves propagating in a plane parallel to the                                                                       |

| power bus an   | d containing the patches of the EEBG structure31                                                                                                |

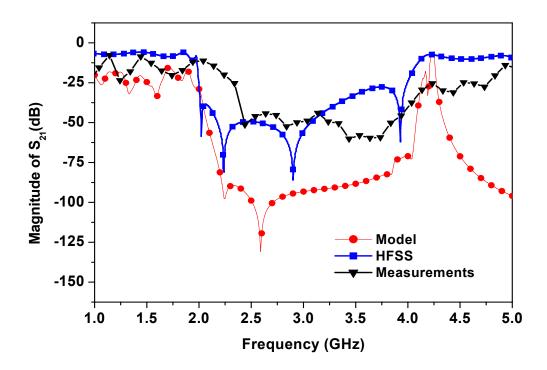

| Figure 2-13    | EEBG unit cell model merged with a conventional low frequency power bus                                                                         |

| circuit model  | . A 2D array of these cells represents the whole power bus                                                                                      |

| Figure 2-14    | Comparison of the model shown in Figure 2-13, simulations using HFSS and                                                                        |

| experimental   | measurements                                                                                                                                    |

| Figure 2-15    | Lateral view of an EEBG structure. Each unit cell consists of a transmission                                                                    |

| line of length | d with shunt admittance across the midpoint of the line. The admittance is a                                                                    |

| lumped elem    | ent equivalent for the patch-via structure assuming square-patched EEBG                                                                         |

| structures.    | 42                                                                                                                                              |

| Figure 2-16    | Scattering parameters for entry 5 of Table 2-1. The magnitude of $S_{21}$ and $S_{11}$                                                          |

| characterize t | the amount of power that propagates through the structure and the power that                                                                    |

| reflects back  | into the source respectively46                                                                                                                  |

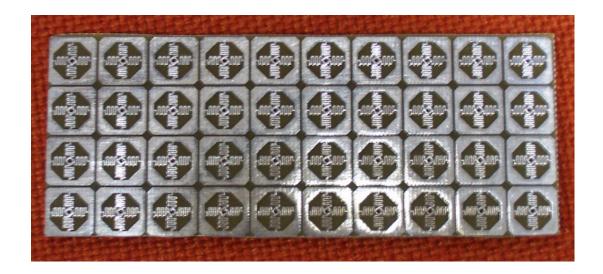

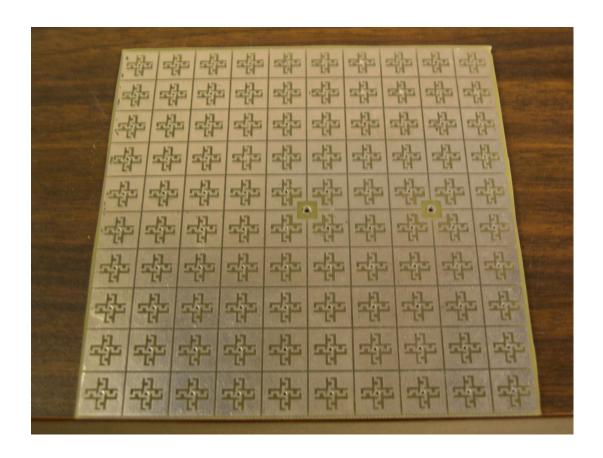

| Figure 2-17    | Mid-layer of a fully populated structure. Board size is 10 cm x 10 cm, patch                                                                    |

| size is 10 mm  | $a \times 10 \text{ mm}$ $Vd = 0.8 \text{ mm}$ $h_1 = h_2 = 1.54 \text{ mm}$ $\sigma = 0.4 \text{ mm}$ $\epsilon_{rd} = \epsilon_{rd} = 4.1$ 47 |

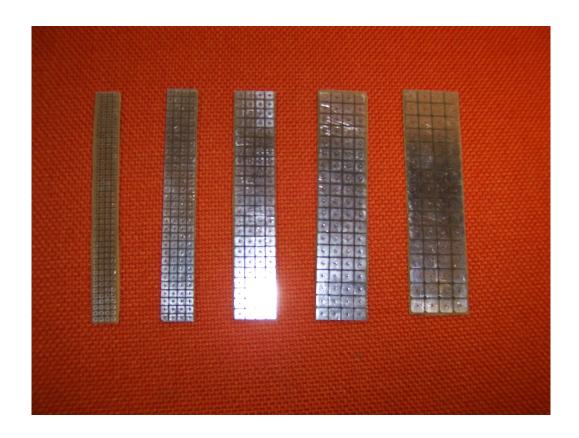

| Figure 2-18       | Implementation of EEBG structures with patch sizes of (from left to right) 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mm x 2 mm,        | 3 mm x 3 mm, 5 mm x 5 mm, 6 mm x 6 mm and 10 mm x 10 mm. $Vd = 0.8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| mm, $h_1 = h_2 =$ | = 1.54 mm, $g = 0.4$ mm, $\varepsilon_{r1} = \varepsilon_{r2} = 4.1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

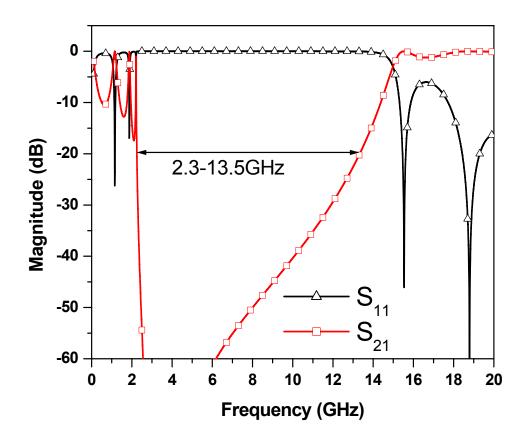

| Figure 2-19 2-17. | S-parameter measurement of a fully populated structure as shown in Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 2-20       | A sample design used to increase the inductance of a single cell of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| structure by s    | sacrificing some capacitance to study the overall effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | Another sample design used to increase the inductance of a single cell of the sacrificing some capacitance to study the overall effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

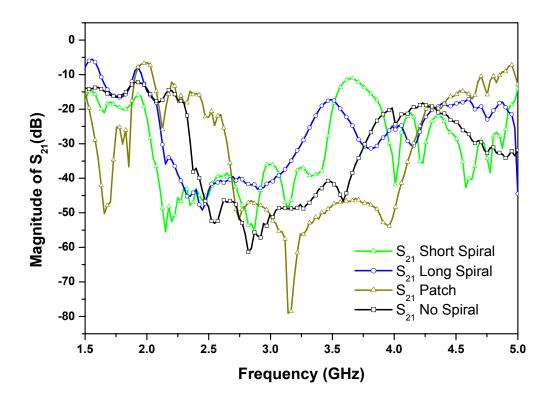

| Figure 2-22       | Results from experiments using exotic structures53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

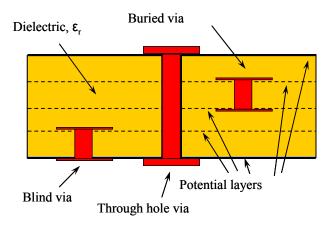

| _                 | Diagram of the cross section through a 5-layer multilayer PCB produced by mination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

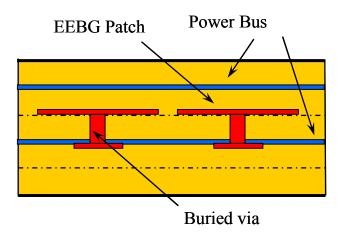

| •                 | Lateral view of a multilayer PCB that uses an EEBG structure in between its showing buried vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

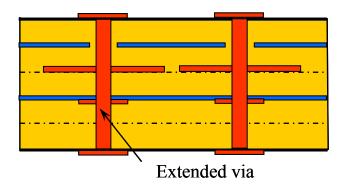

| _                 | Lateral view of a multilayer PCB that uses an EEBG structure in between its showing extended vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

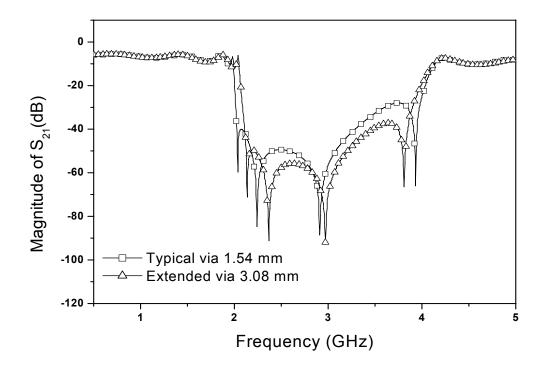

|                   | Effect of via height, $h_2$ , on the gap of an EEBG structure. The simulated $a = 10$ mm, $g = 0.4$ mm, $Vd = 0.8$ mm, and $h_1 + h_2 = 3.08$ mm57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

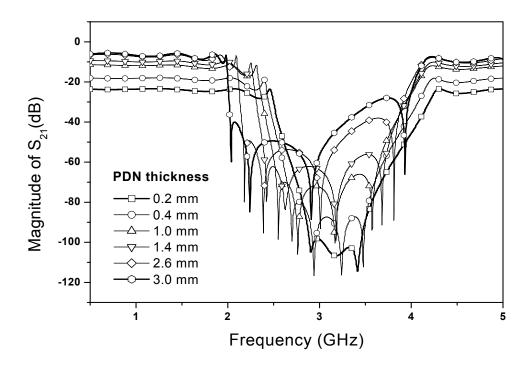

| _                 | Effect of board thickness, $h_1 + h_2$ , on the band-gap of an EEBG structure.<br>d structure has $a = 10$ mm, $g = 0.4$ mm, $h_2 = (h_1 + h_2)/2$ , and $Vd = 0.8$ mm58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

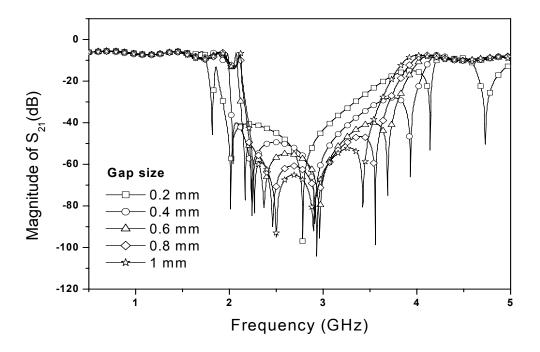

|                   | Effect of the size of the gap between patches, $g$ , on the band-gap of an EEBG e simulated structure has a = 10 mm, Vd = 0.8 mm, $h_1 + h_2 = 3.08$ mm, and $h_2 = 3.08$ mm, and $h_2 = 3.08$ mm, and $h_3 = 3.08$ mm, and $h_4 = 3.08$ mm, and $h_5 = 3.08$ mm, and $h_6 = 3.08$ mm, and |

| Figure 3-1      | Lateral view of a multi-layer PCB with two designs of EEBG structures                      |

|-----------------|--------------------------------------------------------------------------------------------|

| embedded in     | between a pair of power planes                                                             |

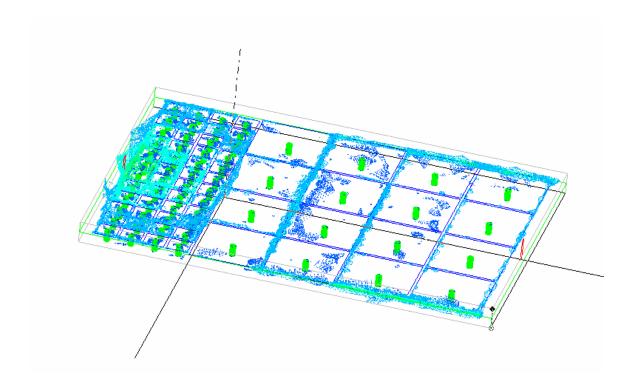

| Figure 3-2      | FE simulation of two cascaded structures. The excitation port is at the left of            |

| the structure   | and the frequency of excitation is in the stop-band of the structure on the right.         |

| The clouds r    | epresent the magnitude of the electric field and as expected it is strong in the           |

| first region (l | left)62                                                                                    |

|                 |                                                                                            |

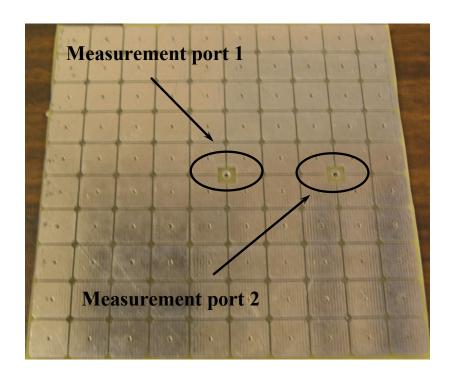

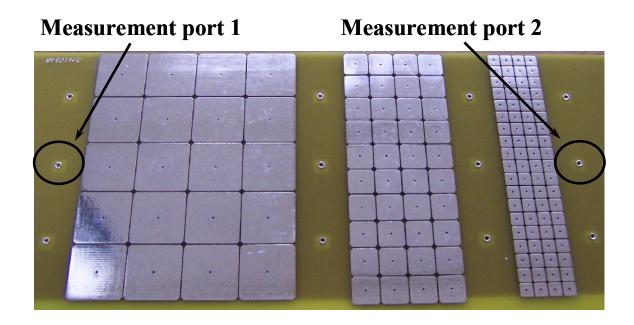

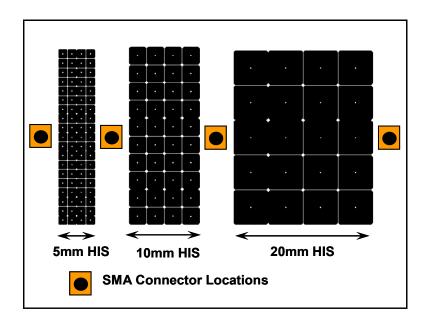

| Figure 3-3      | Proposed wideband/multiple band structure (gap size = 0.4, via diameter =                  |

| 0.8 mm, boar    | rd thickness = 1.54 mm and $\varepsilon_r$ = 4.1). Top view of the middle layer of the PCB |

| and measure     | ment points. Fabricated cascaded structures                                                |

| Figure 3-4      | Proposed wideband/multiple band structure (gap size = 0.4, via diameter =                  |

| 0.8 mm, boar    | rd thickness = 1.54 mm and $\varepsilon_r$ = 4.1). Top view of the middle layer of the PCB |

| and measure     | ment points. Schematic of the overall filter                                               |

|                 |                                                                                            |

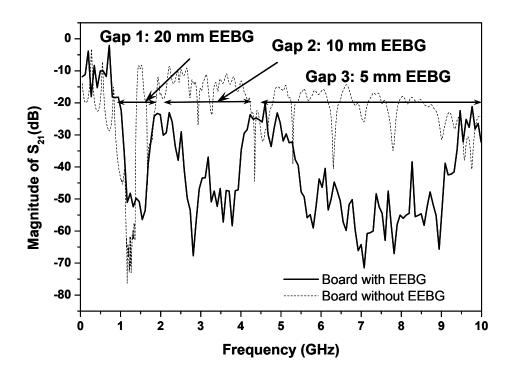

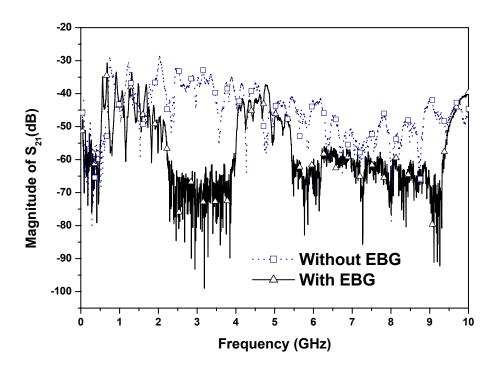

| Figure 3-5      | Measured $S_{21}$ of the fabricated PCB shown in Figure 3-3 employing the                  |

| cascaded EE     | BG structures. $S_{21}$ is measured between the farthest SMA connectors (port 1            |

| and port 2) a   | s shown in Figure 3-3 using a Vector Network Analyzer67                                    |

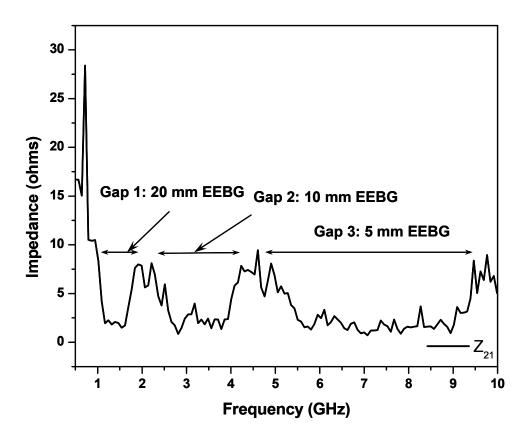

| Figure 3-6      | Plot of the impedance equivalent of the results of Figure 3-5 derived using                |

| equation 1-6.   | 68                                                                                         |

| _               |                                                                                            |

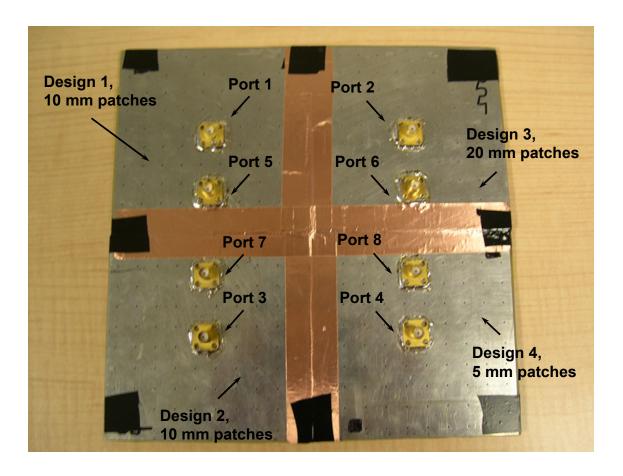

| Figure 3-7      | Test board used to test the sketch board design concept. Design 1 and design               |

| 2 are the sam   | ne                                                                                         |

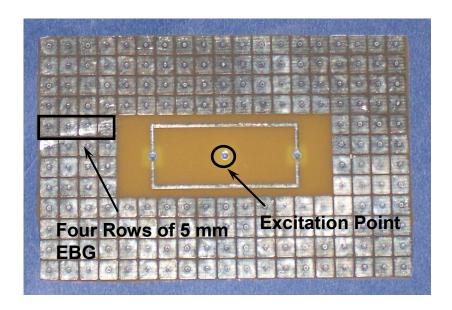

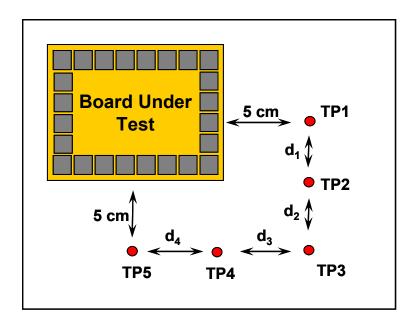

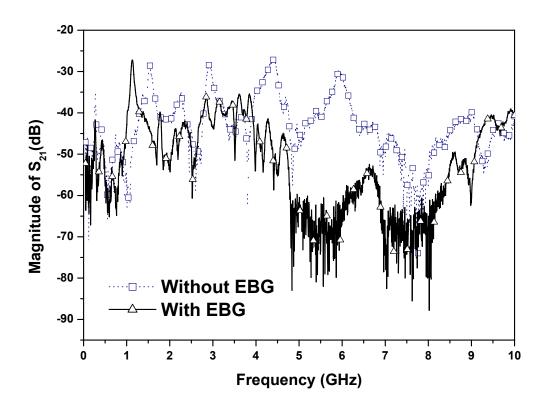

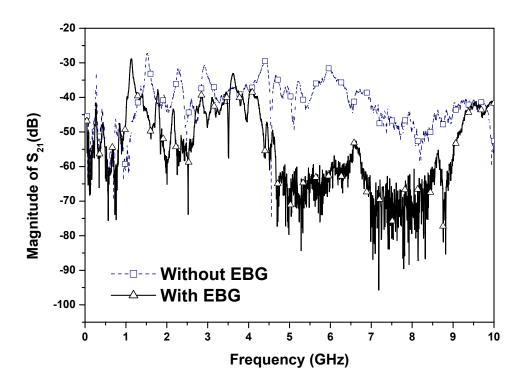

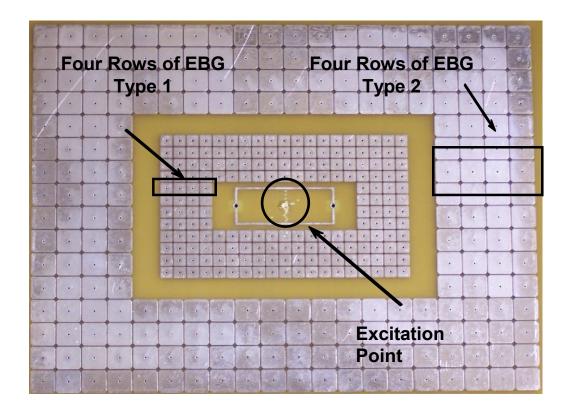

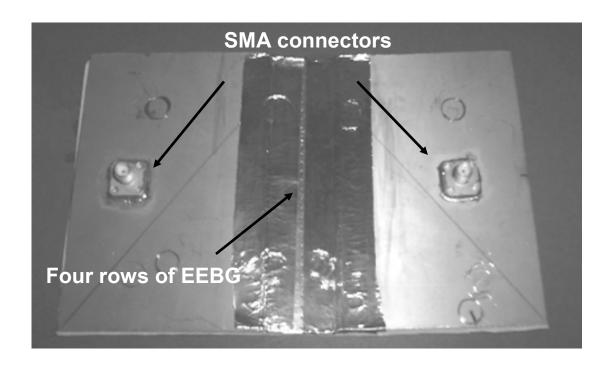

| Figure 4-1      | Test board (6.5 cm x 10 cm) fabricated on commercial FR4 in order to test                  |

| the EMI sup     | opression concept using EEBG structures. A ribbon of four rows of EEBG                     |

| structures wi   | th patch size of 5 mm x 5 mm, vd = 0.8 mm, $g = 0.4$ mm and $h_1 = h_2 = 1.54$             |

|                 | arce of noise (excitation point) is in the middle of the board74                           |

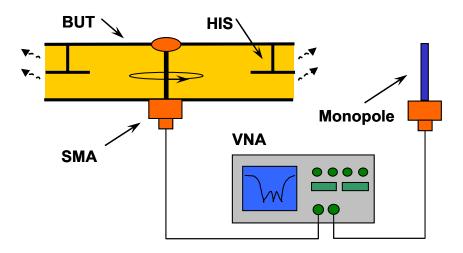

| Figure 4-2      | Experimental setup for $S_{21}$ measurements for boards under test (BUT). One              |

| Ü               | s connected to BUT and the other one to a monopole antenna                                 |

| - r             |                                                                                            |

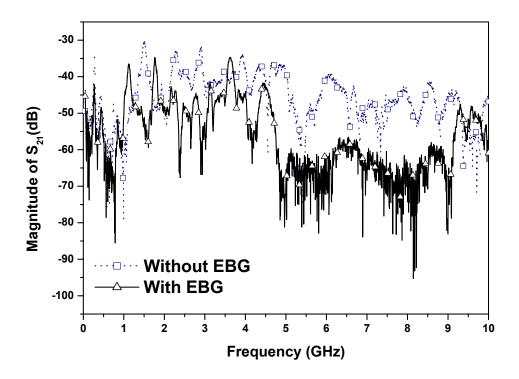

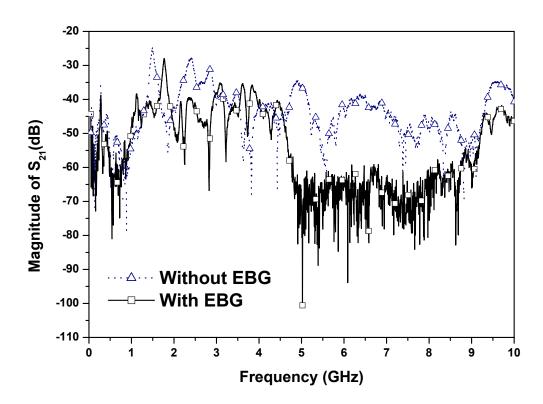

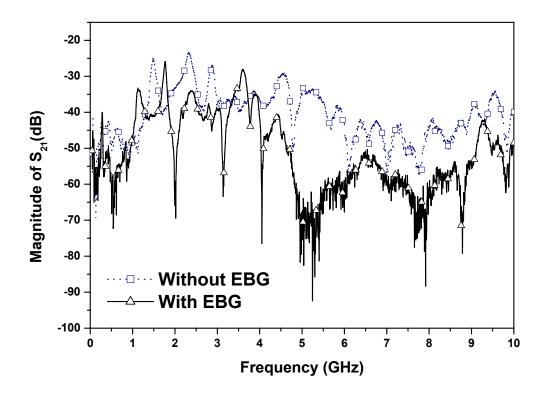

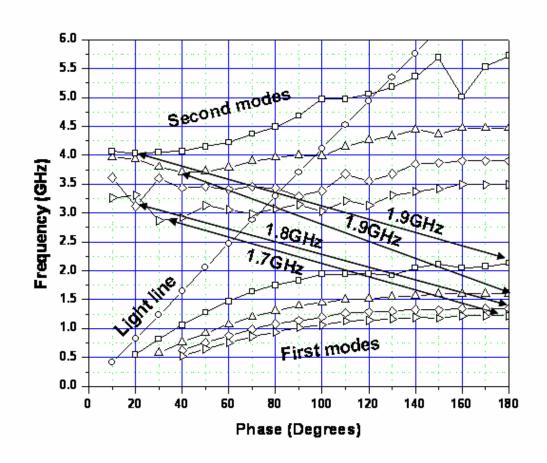

| distance bety  | veen the first mode and the second mode for each structure (no propagation) is                         |

|----------------|--------------------------------------------------------------------------------------------------------|

| the band-stop  | o region                                                                                               |

| Figure 5-4     | Dispersion diagram for entries 5, 7 and 8 in Table 5-1. Entry 5 can achieve                            |

| and ultra-wio  | de band gap (11 GHz) using high-dielectric material. Cascading entries 7 and 8                         |

| can also achi  | eve a wide-band region (16 GHz) but at a far lower cost                                                |

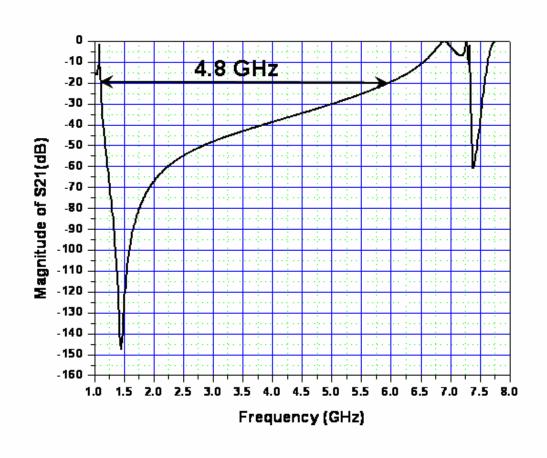

| Figure 5-5     | Simulation-derived (FE) attenuation for a power plane pair that employs EBG                            |

| structures (ei | ntry 9 of Table 5-1)93                                                                                 |

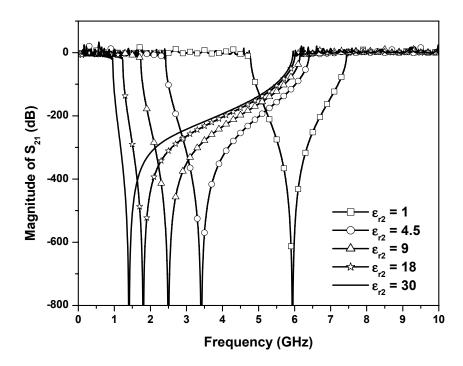

| Figure 5-6     | Magnitude of $S_{21}$ versus frequency for a structure with $d=5.4$ mm, $g=0.4$                        |

| mm, vd = 0.8   | 8 mm, $h_2 = 100 \mu m$ , $h_1 = 16 \mu m$ , $\varepsilon_{r2} = 4.5$ while $\varepsilon_{r1}$ changes |

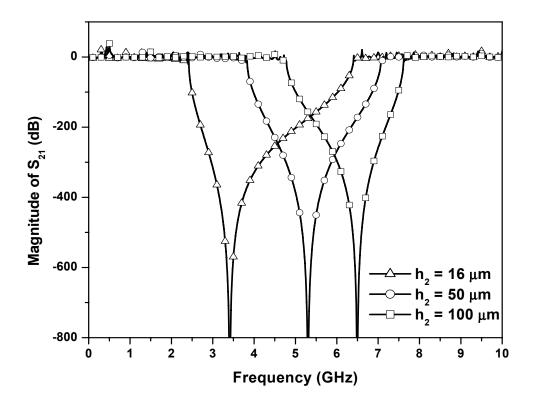

| Figure 5-7     | Magnitude of $S_{21}$ versus frequency for a structure with $d=5.4$ mm, $g=0.4$                        |

| mm, vd = 0.8   | 8mm, $h_2 = 100 \mu m$ , $\varepsilon_{r1} = 4.5$ , $\varepsilon_{r2} = 4.5$ , while $h_1$ changes     |

|                | Top view of the fabricated PCB. This experimental setup is used to test the                            |

| concept of b   | oadband switching noise suppression using high-dielectric constant material                            |

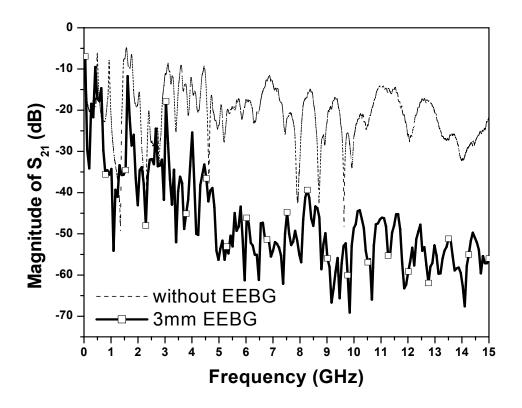

| Figure 5-9     | Measurement results for a structure with: $a = 3$ mm, $g = 0.4$ mm, $Vd = 0.8$                         |

| mm. Four ro    | ws of patches have been cascaded                                                                       |

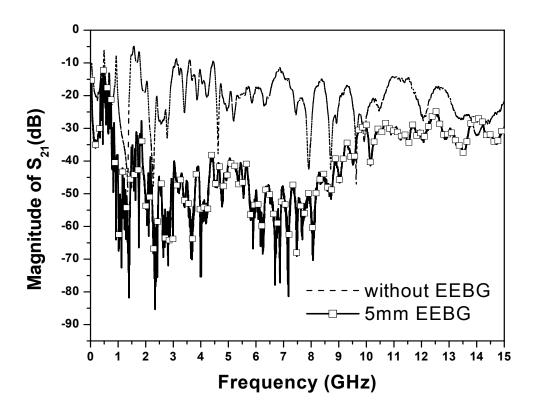

| Figure 5-10    | Measurement results for a structure with: EEBG period of 5.4 mm, a distance                            |

| of 0.4 mm 1    | between patches, via diameter of 0.8 mm. Four rows of patches have been                                |

| cascaded.      |                                                                                                        |

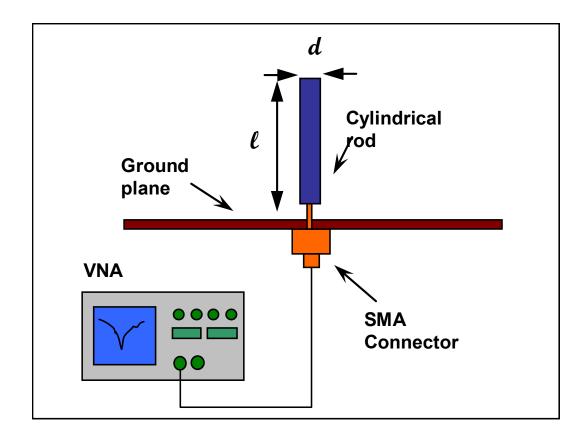

| Figure A-1     | Diagram of a monopole antenna over a ground plane (side view). 108                                     |

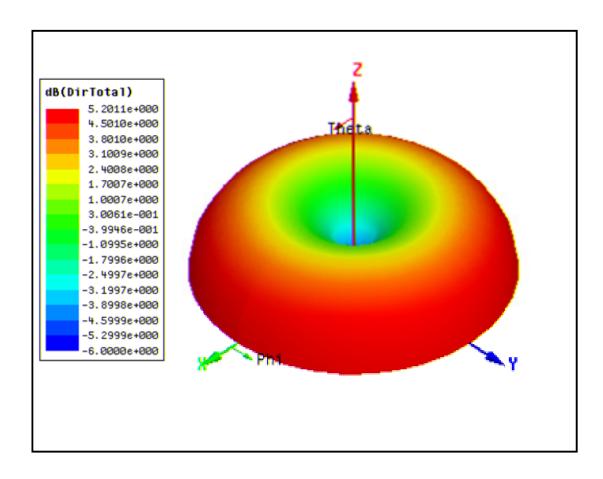

| Figure A-2     | Diagram of a 1 GHz monopole antenna pattern (3D view)111                                               |

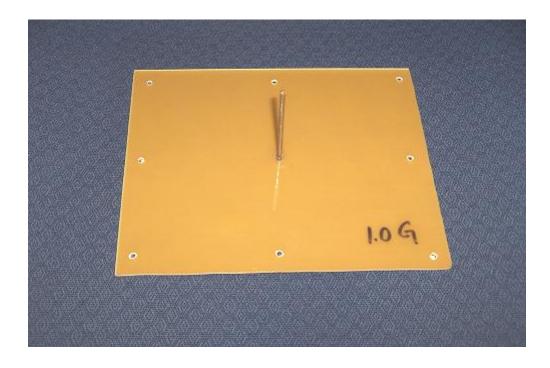

| Figure A-3     | Top view of the 1 GHz monopole                                                                         |

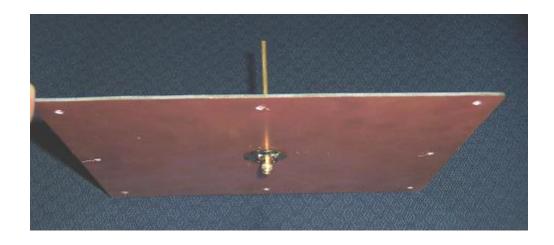

| Figure A-4     | Bottom view of the 1 GHz monopole showing the feed connection112                                       |

# Chapter

# Chapter 1. Introduction, Background and Objective of the Dissertation

#### 1.1 Introduction

For the past two decades, silicon-based complementary metal-oxide semiconductor (CMOS) technology and circuits have been advancing along an exponential path of shrinking device dimensions, increasing density, increasing speed, and decreasing cost. Electronic design complexity is in constant acceleration and new designs have to incorporate new features, which inevitably will require faster processing time. In recent years this acceleration rate has drastically decreased because of various constraints, such as static power dissipation due to leakage current, the effect of wires and interconnects and the decreased immunity of modern devices to noise, interference and voltage fluctuations on their Power Distribution Network (PDN) [1]-[3].

Switching noise is known to be the main source of noise and voltage fluctuations on the power planes of the printed circuit boards (PCB) and packages that contain modern CMOS-based devices [4]. The fundamental mechanism behind the generation of this type of noise is either high-speed time-varying current or the vias that pass through the parallel plate of a power distribution network, or a combination of both. The flow of high-speed time varying current through such vias, causes radiation. The radiated waves use the parallel plate wave guiding structure to propagate. At the edges of the PCB, a portion of these waves are reflected back and the rest is radiated. The radiated waves cause interference problems, and the reflected waves cause a resonance behavior in the cavitylike structure created by the parallel plates and the dielectric material between them [5]. The ratio of reflected waves to radiated waves is frequency dependent. Other vias that pass through the same parallel-plate structure act as receiving antennas. In this scenario, the devices connected to the receiving vias become victims of the radiating via. This scenario is worsened when multiple vias radiate at the same time. The type of noise caused in such scenario in known as simultaneous switching noise (SSN). The transient currents, drawn by the internal fast switching logic gates of an integrated circuit can be in the order of hundreds of milliampere and can give rise to significant unwanted voltage fluctuations on the PDN of a PCB.

SSN, if uncontrolled, can cause logic circuits to switch state falsely. This false switching, in turn, can cause serious malfunctions in the subject circuits with catastrophic consequences. As a result, one of the key challenges for designers of modern high-speed circuits is to design a PDN capable of delivering large amounts of current at low voltage. Therefore it is absolutely necessary to reduce the power bus impedance as much as possible

while suppressing the propagation of waves generated by the consumption of that current by the switching devices.

Methods introduced in past works, in order to confront switching noise, all try to

reduce the resonance effects of the cavity-like structure. The most widely used and effective of them include the use of decoupling capacitors [6],[7], embedded capacitances [8] and capacitors [9], the use of dissipative and lossy components along the PCB and at its edges [10][11], dividing power planes in power islands [12], and via stitching [13]. The use of decoupling capacitors is the most wide spread method and it consists of placing large capacitors around the sources of noise to disrupt high-frequency fluctuations on the power planes by creating a low-impedance path between the planes at these frequencies. This method, although very effective, is limited by the fact that capacitors have leads and connections to the PCB which at high-frequency become inductive, and therefore tend to create an open circuit rather than a short circuit. Other methods try to overcome this frequency limitation, in one way or another. Embedded capacitors and capacitances try to minimize the length of the problematic leads. Dissipative components and via stitching, try to damp down the radiated waves in order to avoid resonance (and radiation) effects. Their effectiveness requires materials which operate at high frequency. Power islanding is also widely used, but its applicability is limited to applications in which isolation is the goal such that the source of noise and the susceptible components are kept on different power islands.

In summary, all methods mentioned above have an effective range of at most few hundred megahertz and are expensive to implement, if not ineffective at high frequencies.

Recently the use of electromagnetic bandgap (EBG) structures has been introduced as an effective inexpensive method for SSN suppression in the GHz frequency band [14][15]. These earlier works, while introducing for the first time a realizable concept for SSN suppression in the GHz region, were somewhat less attractive to implement in the high-frequency PCBs used in the low-cost highly competitive consumer electronics industry. The first unattractive feature was the relatively narrow band of noise suppression. The second, the earlier introduced structures were relatively large in dimensions in comparison to the size of the PCB in which they are inserted.

This dissertation covers methods for design and analysis of EEBG structures. It describes the underlying theories of operation of EBG structures. In addition, advanced designs presented in this work eliminate the first critical drawback of early design by providing ultra-wide band suppression over a wide range of frequencies in which previous methods cannot be used or they provide only limited efficacy. Furthermore the miniaturization concepts and methodologies introduced in this work eliminate the second drawback transforming early designs into a viable and practical solution for broadband switching noise suppression in PCBs.

#### 1.2 Anatomy of Switching Noise in Electronic Power Distribution Systems

As explained in the previous section, switching noise is usually caused by the high-speed time-varying currents needed by high-performance digital circuits. The flow of these currents through vias between layers of a printed circuit boards, causes radiation. The radiated waves use the parallel plates created by the power planes to propagate. Simultaneous Switching Noise (SSN) is a noise created while many outputs of a digital

circuit switch at the same time. SSN cannot be quantified in precise measure because of its dependence on the geometry of the board and current paths. Various studies have concentrated on modeling this phenomenon [16] [17] [18].

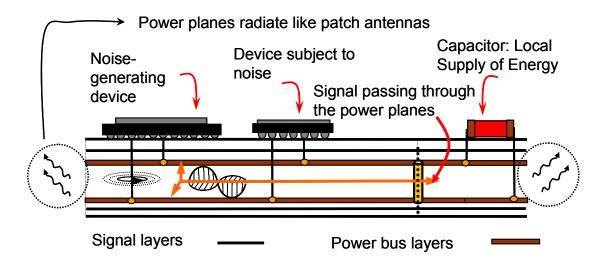

The continuous and rapid increase of clock frequency is another source for switching noise. In fact high-speed small currents have an equivalent impact on switching noise as switching of circuits that involve large amounts of current (simultaneous switching). Figure 1-1 shows a general schematic for generation of switching noise within a power bus of a PCB. A high-speed or high-power (or both) device that consumes power from two parallel power planes is the first type of noise. A via that passes through these plane and is not necessarily connected to any of them is another type of noise source. Electromagnetic waves generated by these sources of noise use the parallel plates to propagate and therefore induce noise on other signals passing through the power bus (vias), other devices that feed from the same power bus and eventually radiate from the edges of the board.

Figure 1-1 Switching noise generation mechanism in a PDN of a multilayer printed circuit board.

This section discusses the phenomenon of wave propagation and resonance in a parallel-plate structure and elaborates more on the theoretical fundamentals of such propagation and resonance.

# 1.2.1 Electromagnetic Wave Propagation and Resonance in an Infinite Parallel-plate Structure

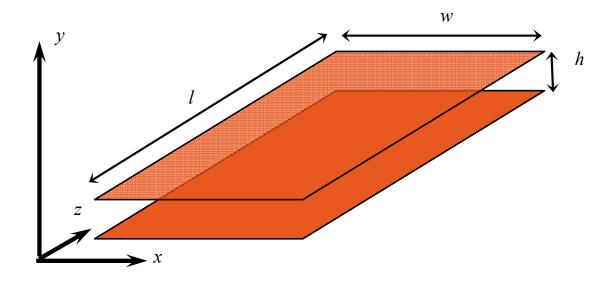

The ground and supply voltage planes of the power distribution network constitute a parallel-plate waveguide. This type of structures can therefore support TE, TM and TEM modes [19]. The TEM waves correspond to the situation, where there are no electric or magnetic fields in the direction of propagation. TE and TM modes correspond to situations in which the fields have no electric or magnetic field in the direction of propagation, respectively. In the idealization of the parallel-plate waveguide illustrated in Figure 1-2, the

dimensions in the x-direction is assumed to be much larger than the thickness h of the waveguide such that all fringing fields and any variation in the x-direction can be neglected. For this type of analysis the wave propagation is one-dimensional and in the z-direction.

Figure 1-2 Diagram for an ideal parallel plate waveguide as a model for the power planes of a PCB.

The TEM waves correspond to the situation, where there are no electric or magnetic fields in the direction of propagation. TE and TM modes correspond to situations in which the fields have no electric or magnetic field in the direction of propagation, respectively. For all types of propagating waves,

$$k_c = \frac{n\pi}{h}, \beta = \sqrt{k^2 - k_c^2}, f_c = \frac{n}{2h\sqrt{\mu\varepsilon}}$$

In which  $k_c$  is the wave number,  $\beta$  is the propagation constant and  $f_c$  is the cutoff frequency. The constant n is the number of the propagating mode for which  $k_c$ ,  $\beta$  and  $f_c$  are defined. k is the propagation constant of an equivalent wave in free space.

The first mode, which is a TEM mode is when *n* is equal to zero, hence:

$$\beta = k = \omega \sqrt{\mu \varepsilon} \quad f_c = 0$$

Typical power planes have a thickness of less than 2 mm. This implies that the parallel-plate  $TE_n$  and  $TM_n$  modes have cut-off frequencies in the order of tens or hundreds of GHz and are not a major concern for systems operating at 20 GHz and below. The only modes of concerns are the TEM modes and the resonance modes induced by the finiteness of the power planes. In fact, in the calculation of the parallel-plate waveguide modes [19], it was assumed that the plates have infinite length in the z-direction. In practical power planes, the width (w) and length (l) of the plates are finite. In this case, waves propagating to the edge of the waveguide are reflected back and forth. Therefore, in addition to the parallel-plate modes, rectangular cavity modes are also excited. Both  $TE_{mnp}$  and  $TM_{mnp}$  modes are excited. Their cut off frequency is given by the same equation,

$$f_{res}(m,n,p) = \frac{1}{2\pi\sqrt{\mu\varepsilon}}\sqrt{\left(\frac{m\pi}{w}\right)^2 + \left(\frac{n\pi}{l}\right)^2 + \left(\frac{p\pi}{h}\right)^2}$$

1-3

Since h is very small compared to l and w, only  $TE_{mn0}$  and  $TM_{mn0}$  modes have low enough resonance frequencies that fall into the frequency range of interest (below 20 GHz), hence:

$$f_{res}(m,n) = \frac{1}{2\pi\sqrt{\mu\varepsilon}}\sqrt{\left(\frac{m\pi}{w}\right)^2 + \left(\frac{n\pi}{l}\right)^2}$$

1-4

As an example a PCB with dimensions of 10 cm x 10 cm x 1.5 mm has resonance frequencies of 1.41 GHz, 2 GHz, 3.16 GHz, 4 GHz, 5.08 GHz, 6 GHz and so on.

More detail on the subject of power plane resonance the reader is referred to references [5] and [8].

Obviously, switching noise has its maximum impact if generated at the resonance frequencies of the PCB.

A very effective metric to characterize switching noise in PCBs is transfer impedance. Transfer impedance is defined as the ratio between the induced voltage at a victim location on the power bus and the injected current at a source location. The scattering parameter matrix [S] can be transformed into the impedance matrix using [20]:

$$[Z] = Z_0 \frac{[I] + [S]}{[I] - [S]}$$

1-5

Where [I] is the identity matrix and  $Z_0 = 50 \Omega$  is the characteristic impedance of the network analyzer. In [Z],  $Z_{21}$  represents the open circuit voltage at a victim location on the power bus generated by the current injected at a source location; hence it is the transfer impedance.

From equation 1-5 the magnitude of  $Z_{21}$  is related to  $S_{21}$  measurements as:

$$Z_{21} = \frac{2Z_0 S_{21}}{4 - S_{21}^2} \tag{1-6}$$

If  $|S_{21}|$ ,  $|S_{12}| \ll 1$  and  $S_{11}$ ,  $S_{22} \approx -1$  as it normally happens for power planes,

$$|Z_{21}|dB \approx |S_{21}|db + 28dB$$

1-7

As a result  $|S_{21}|$  measurements can and they will be used directly to study the transfer impedance  $|Z_{21}|$ . Furthermore, attenuation in the  $S_{21}$  parameter as a result of employing noise suppression techniques will be directly associated with a decrease in transfer impedance, hence noise coupling.

#### 1.3 Research Objectives and Thesis Structure

In summary, the objective of this research is to present a practical and very effective method for broadband switching noise suppression in high-speed CMOS based electronic packages.

Chapter 2 covers theoretical and empirical modeling techniques as well as simulation and experimental methods for the study of SSN suppression using EEBG structures and practical considerations for their fabrication.

Chapter 3 introduces the first ever design concept for wideband noise suppression of SSN, based on classical filter theory and the similarities of EEBG structures to bandstop filters.

Radiation from PCBs caused by switching noise is studied in chapter 4 and mitigation techniques based on EEBG structures are presented. Finally, chapter 5 introduces the concept of combining EEBG structures with commercial high dielectric

constant material for the purpose of achieving a very large suppression bandwidth that extends to sub-gigahertz frequencies but at the same time reduces geometrical sizes of EEBG structures in a drastic manner, therefore achieving the last milestone required to transform early EEBG design into practical, matured and effective mitigation technique for switching noise suppression in PCBs of high speed circuits.

Conclusions, future works and potential extension to this thesis will be covered in chapter 6.

# Chapter

# Chapter 2. Power Planes with Embedded Electromagnetic Bandgap (EEBG) Structures

#### 2.1 EEBG Structures and the Switching Noise Suppression Concept

Electromagnetic Band-Gap structures introduced as High-Impedance Surfaces (HIS) in early stages of research in this field [21], belong to a broad family of engineered materials called meta-materials, which have been initially employed for antenna applications because of their unique behavior. In fact, HIS structures can satisfy a Perfect Magnetic Conductor (PMC) condition over a certain frequency band and impose a 0° reflection phase to normal incident waves, making them suitable for applications such as coupling reduction between antennas and antenna directivity improvement. Although EBG (HIS) structures have been extensively studied, these studies have focused on open structures (not enclosed in environments like PCBs) and normal incident waves, such as antenna application, therefore derived theories and models are only applicable to such

cases. For more information on open EBG structures the reader is referred to reference [21] and also the references mentioned in these references.

The use of EBG structures in PCB environments was first reported in [14], to suppress simultaneous switching noise in printed circuit boards. A similar concept was also introduced in [15].

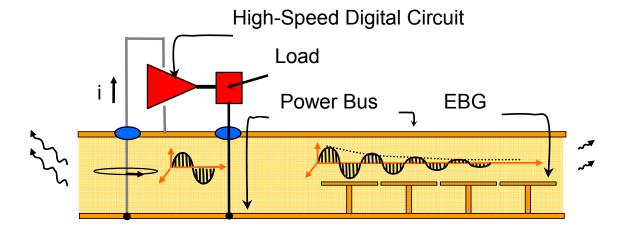

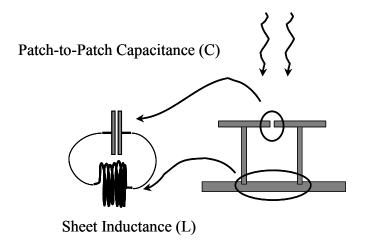

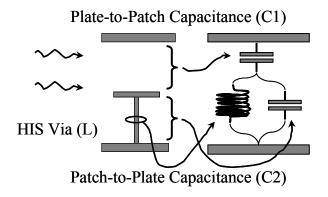

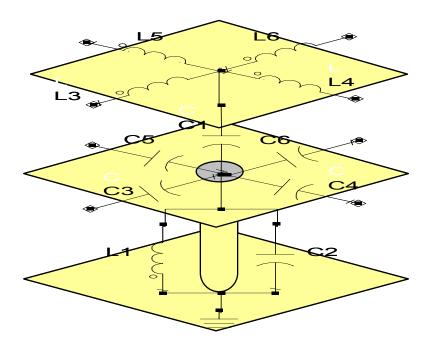

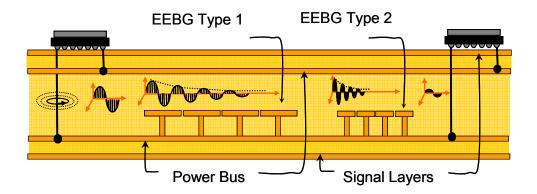

When inserting an EEBG structure in the parallel-plate waveguide-like structure of the PDN of a PCB, a resonant circuit composed of the top plate, a single patch, the corresponding via and the plane that connects the vias together is created. In fact this circuit provides a low-impedance path to high-frequency currents in the power-planes therefore shorting the planes (resonance) at the physical location of the patches within the band-stop frequency range, thus suppressing propagation. The diagram of Figure 2-1 illustrates the generation of switching noise, the propagation of waves in the PDN, their suppression using EEBG structures and their radiation from the sides of the PCB.

In summary, each row of EEBG introduces transfer zeros. At the resonance frequencies of these transfer zeros a low-impedance path is created between the plates of the power bus shorting all the signals propagating at that frequency. When other rows of EEBG ribbons are added to the PDN, they shift the resonance frequency of the single row ribbon, creating multiple transfer zeros, therefore a band-stop region. The overall effect of this design is therefore to shorten and shield the power bus of the PCB within a range of frequencies.

Figure 2-1 EBG structures embedded in PCBs: Switching noise generation, radiation and suppression mechanisms.

It is important to emphasize the fact that simple EEBG structures presented in this work are targeting the 0.5-20 GHz range, therefore pushing the limit of previous methodologies. Since simple EEBG structures have impractical geometrical sizes in the 500 MHz to 2 GHz frequency range, more complex EEBG structures need to be employed. In addition, in view of ongoing miniaturization of electronic systems the implementation of this method requires the availability of miniaturized EEBG structures with appropriate patch sizes, although the concept introduced in this paper can be generally applied regardless of the size of the EEBG structures. For wideband radiation reduction from hundreds of MHz to few GHz either a combination of different methods or use of advanced EEBG structures is the best solution. Such advanced EEBG structures are covered in chapter 3 and chapter 5.

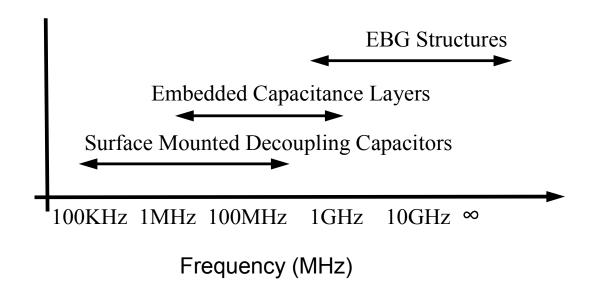

Figure 2-2 Efficacy range of different switching noise reduction methods.

Figure 2-2 shows the efficacy range of EEBG structures covered in this work in comparison to conventional switching noise suppression methodologies.

Early design for EEBG structures can also be applied to the same range of frequencies for which conventional methods are used (i.e. up to few hundred MHz). To provide noise suppression for the MHz range, the simple EEBG patches introduced earlier can be used, but the patch sizes will become possibly impractical. For practical purposes, to use the EEBG structures for noise suppression in the MHz range, more complex EEBG structures need to be considered. Alternatively, one can use a combination of the techniques introduced in this thesis with conventional methods.

#### 2.2 Design Methodologies, Parameters and Issues

In the last few years, different methods have been utilized for the design and test of EEBG structures. Goals for all these methods include but are not limited to describing the

behavior of EEBG structures [22], studying the effect of various design parameters (e.g. patch shape, patch size, via diameter, gap diameter, dielectric constant of the substrate, etc.) [23] and deriving new EEBG structures for more effective noise suppression (e.g. higher bandwidth) [24].

Methods used so far for design and analysis of EEBG structures can be separated in six main categories based on direct experimentation, numerical wave analysis (frequency domain and time domain), circuit modeling and transmission line modeling. This section describes and compares different methods for designing EEBG structures.

#### 2.2.1 Direct Experimentation

This method consists of fabricating PCBs with EEBG structures and performing S-parameter measurements in order to derive the band-stop region of the fabricated design. The major advantage of this method is the accuracy of the derived bandgap. The major drawback is when this method is used as a design method, a large design space needs to be explored. This can be costly and time consuming. For this scenario, approximate methods need to be developed to finalize the design by fabricating and testing a couple of possible configurations..

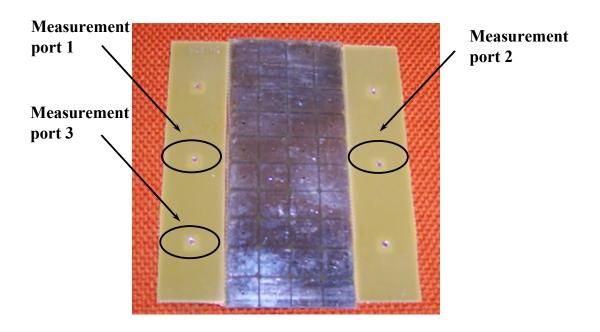

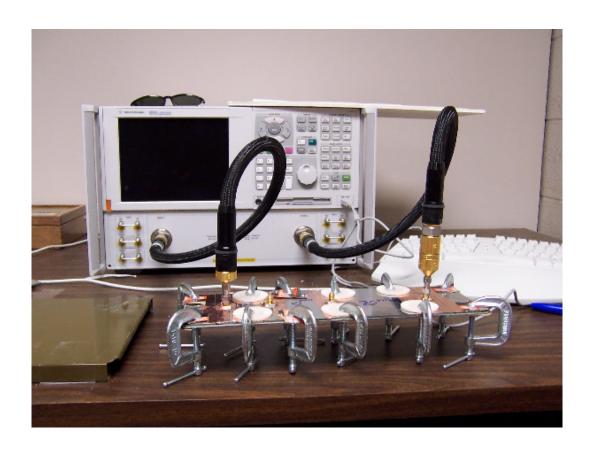

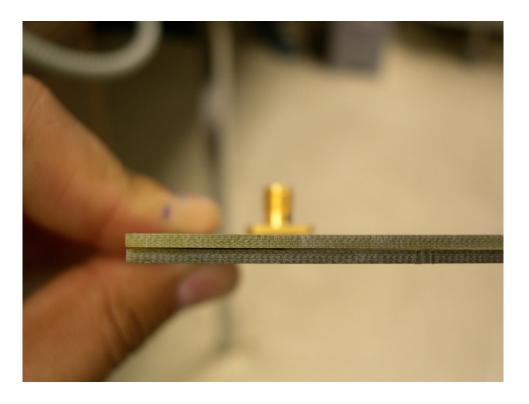

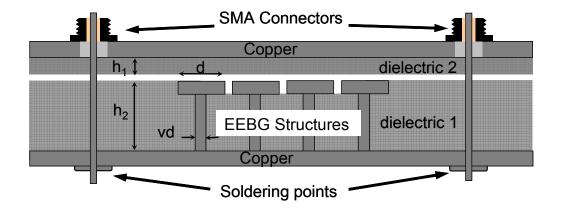

Figure 2-3 and Figure 2-4 show a typical experimental setup used for characterization of a sample EEBG structure. Figure 2-3 shows the patch layer of an EEBG structures placed in between two lateral pieces of PCB without any structure (i.e plain). A separate layer is mounted on top of this structure and pressed together as shown in Figure 2-4. For better clarity of the structure a lateral illustration of the final structure is shown in Figure 2-6. In this setup if port 1 is excited using a Vector Network Analyzer (VNA), waves can

propagate (and resonate) in the two lateral slabs of PCB (from port 1 to port 4) but propagation from port 1 to port 2 is suppressed by the presence of the EEBG structure. In this scenario a gap present in  $S_{21}$  represents the operating range of the EEBG structure under test. Figure 2-5 shows a typical  $S_{21}$  measurement using this technique.

Figure 2-3 Test setup for EEBG structures with patches of 20 mm x 20 mm. A separate one layer board is mounted on top of this one as a second power plane.

Figure 2-4 Measurement setup using a Vector Network Analyzer (VNA).  $S_{21}$  is a representative for transfer impedance between port 1 and port 2.

Figure 2-5 Sample measurement for the setup depicted in Figure 2-3

Figure 2-6 Lateral view of the PCB under test.

### 2.2.2 Full-wave Analysis of a Complete Structure

Full wave analysis of a complete EEBG structure consists of either analytically solve Maxwell's equations in the structure or simulation of the exact desired structure with all possible details using a numeric finite-element or finite-difference (time or frequency) method [25]. Analytical solutions of Maxwell's equations do not lead to a closed form equation.

On the other hand, simulations by numerical analysis can be achieved either by writing specific code for solving Maxwell's equations in EEBG structures or by using generic commercial tools. The performance (execution time and memory allocation) of this method is limited to the performance of those tools. Based on experience the real-size

models to be simulated become so large that even commercial tools take days to provide a fairly accurate result, assuming convergence happens.

### 2.2.3 Dispersion Diagram Extraction

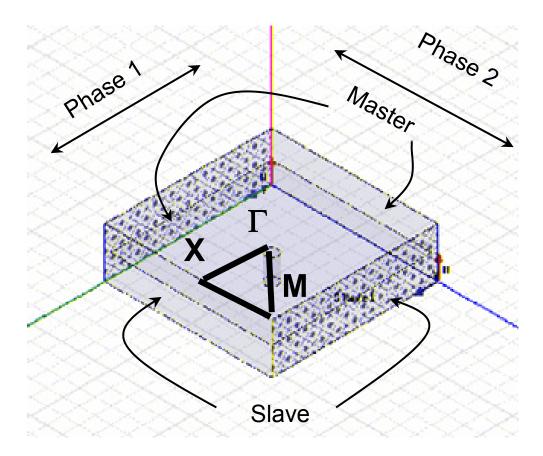

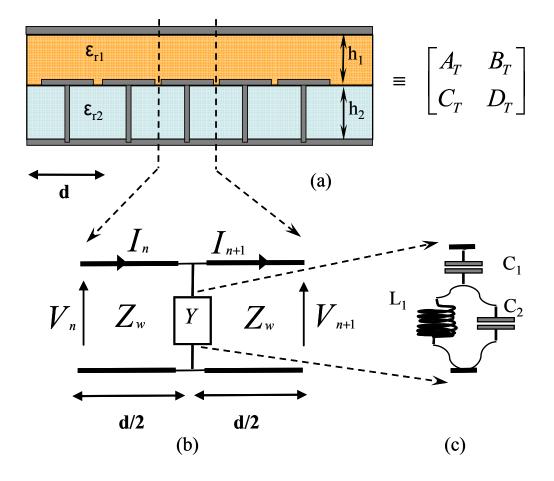

A numerical indirect procedure that has proven to be very effective and fast consists of extracting the dispersion diagram of the EEBG structure. Such diagram describes the propagation characteristics of an infinitely periodic structure composed of EBG patches. In this work the dispersion diagram is extracted using the commercial finite element full wave solver HFSS [26], by considering only one patch (or a unit cell) and applying a periodic boundary condition on the sides of the cell (to mimic the presence of the cell in a periodic structure extending to infinity), and Perfect Electric Conductor (PEC) boundary condition on the top and bottom of the cell for the power planes, as shown in Figure 2-7 [27].

Dispersion diagrams show the relationship between wave numbers and frequency. These diagrams present propagating modes and band gaps that can potentially exist between such modes (in a periodic structure at a given frequency of operation, many modes in different directions may be excited). Brillouin, in his theory of wave propagation in periodic structures [28], states that for any periodic structure there are certain vectors (i.e., directions) in the unit cell of the periodic structure that constitute a boundary region of propagation called irreducible Brillouin zone. According to this theory, deriving the propagating modes in the direction of these vectors suffices to cover all the possible direction of propagation within the lattice. Hence the problem of deriving the propagating modes excited at a certain frequency reduces to finding such modes only in the directions of the vectors of the irreducible Brillouin zone. For the type of structure considered in this