#### **ABSTRACT**

Title of Dissertation: A GALLIUM NITRIDE INTEGRATED

ONBOARD CHARGER

Shenli Zou, Doctor of Philosophy, 2020

Dissertation directed by: Professor, Alireza Khaligh, Department of

Electrical and Computer Engineering

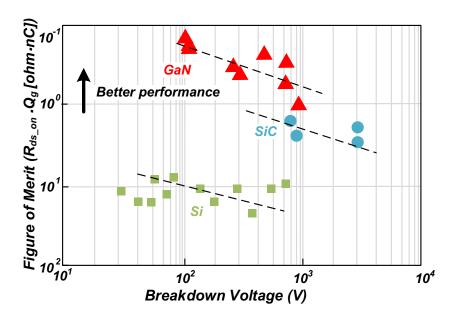

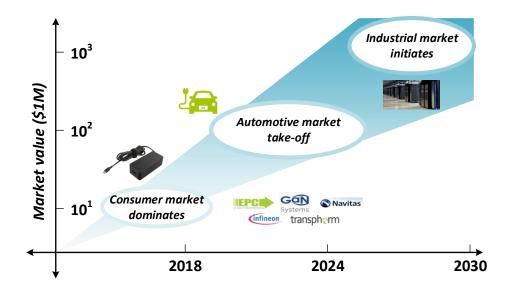

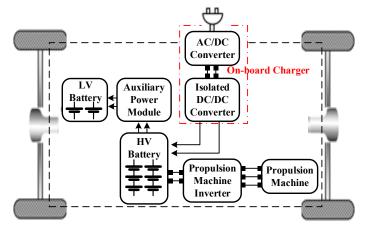

Compared to Silicon metal–oxide–semiconductor field-effect transistors (MOSFETs), Gallium Nitride (GaN) devices have a significant reduction in gate charge, output capacitance, and zero reverse recovery charge, enabling higher switching frequency operation and efficient power conversion. GaN devices are gaining momentum in power electronic systems such as electric vehicle (EV) charging system, due to their promises to significantly enhance the power density and efficiency. In this dissertation, a GaN-based integrated onboard charger (OBC) and auxiliary power module (APM) is proposed for EVs to ensure high efficiency, high frequency, high power density, and capability of bidirectional operation.

The high switching frequency operation enabled by the GaN devices and the integration of OBC and APM bring many unique challenges, which are addressed in this dissertation. An important challenge is the optimal design of high-frequency magnetics for a high-frequency GaN-based power electronic interface. Another challenge is to achieve power flow management among three active ports while minimizing the circulating power. Furthermore, the impact of circuit layout parasitics

could significantly deteriorate the system interface, due to the sensitivity of GaN device switching characteristics.

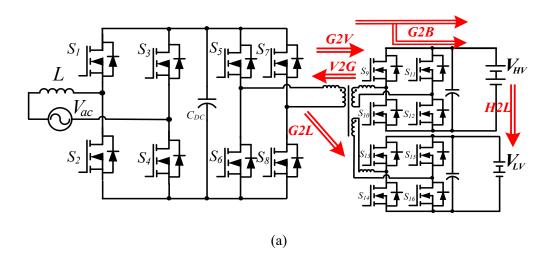

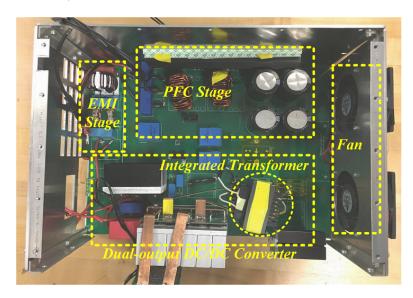

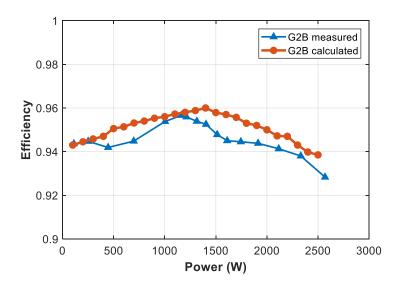

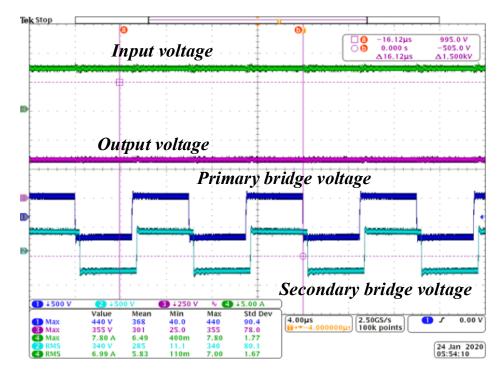

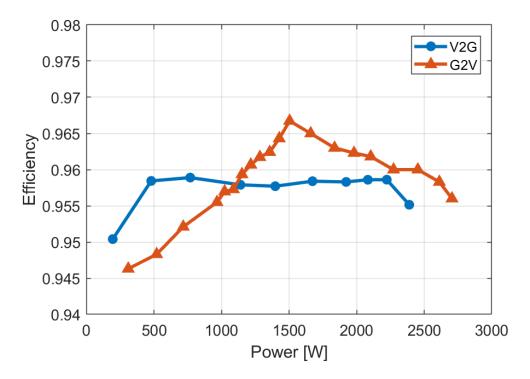

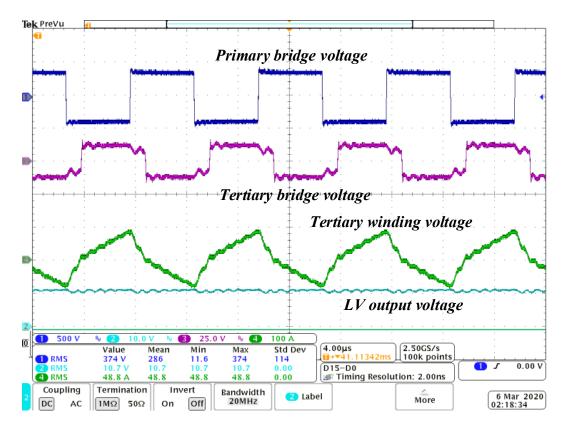

In this work, the aforementioned challenges have been addressed. First, a comprehensive analysis of the front-end AC-DC power factor correction stage is presented, covering a detailed magnetic modeling technique to address the high-frequency magnetics challenge. Second, the modeling and control of a three-port DC-DC converter, interfacing the AC-DC stage, high-voltage traction battery and low-voltage battery, are discussed to address the power flow challenge. Advanced control methodologies are developed to realize power flow management while maintaining minimum circulating power and soft switching. Furthermore, a new three-winding high-frequency transformer design with improved power density and efficiency is achieved using a genetic-algorithm-based optimization approach. Finally, a GaN-based integrated charger prototype is developed to validate the proposed theoretical hypothesis. The experimental results showed that the GaN-based charging system has the capability of achieving simultaneous charging (G2B) of both HV and LV batteries with a peak efficiency of 95%.

#### A GALLIUM NITRIDE INTEGRATED ONBOARD CHARGER

by

## Shenli Zou

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2020

Advisory Committee:

Professor Alireza Khaligh, Chair

Professor Agis Iliadis

Professor Neil Goldsman

Professor Kevin Daniels

Professor Patrick McCluskey

© Copyright by Shenli Zou 2020

# Acknowledgements

With sincere appreciation in my heart, I would like to thank my PhD advisor, Prof. Alireza Khaligh, for the guidance, support, encouragement during the past five years. He guided me to the most interesting research topics in the field of transportation electrification and power electronics. Under his insightful supervision, we worked closely to conduct high-quality research, which addresses one of the main challenges in electric vehicle charging. I appreciate all his contributions of time, ideas, and funding to make my PhD experience productive and stimulating. His rigorous research attitude, communication and prioritizing skills, and logistical thinking characteristic have been a great value for me.

In addition, I would like to thank Prof. Neil Goldsman, who gave me a lot of advice and support in my final PhD stage. I would also like to thank Prof. Agis Iliadis, Prof. Kevin Daniels, and Prof. Patrick McCluskey for the time and support serving as my dissertation committee. I am thankful to them for the comments from different technical perspectives.

The members of the Maryland Power Electronics Laboratory (MPEL) group have contributed immensely to my personal and professional time at UMD. I would like to show my appreciation for the help, support, and friendship I have been receiving from my previous and current lab mates (Dr. Junyi Shen, Dr. Chuan Shi, Mr. Weisheng Ding, Dr. Arun Sankar, Dr. Bin Wu, Dr. Ayan Mallik, Dr. Peiwen He, Dr. Jiangheng Lu, Dr. Zeyu Zhang, Mr. Michael D'Antonio, Mr. Akshay Singh, Mr. Yongwan Park, Mr. Chanaka Singhabahu, Dr. Jianfei Chen, and other lab members). Many thanks go to

Jiangheng and Ayan, who were one year senior than me, and gave me tons of technical help and support.

Thanks also go to the Power Electronics and Electric Machinery Group at Oak Ridge National Laboratory (ORNL), where I spent a wonderful eight-month internship. I would like to thank Dr. Omer Onar for his mentorship, support, and help at ORNL. It was fortunate to explore the high-power wireless charging, which is an important topic in transportation electrification. I would like to thank many staffs there (Dr. Burak Ozpineci, Dr. Madhu Chinthavali, Dr. Gui-Jia Su, Dr. Veda Galigekere, Dr. Sheng Zheng, Dr. Jack Wang, Dr. Tong Wu, Dr. Rong Zeng, and Mr. Cliff White).

My time at UMD was made enjoyable in large part due to the friends that became a part of my life. My thanks also go to all of them and it is precious memory to live and work with them in the past five years. I would also like to thank all the wonderful staffs in the department: Ms. Melanie Prange, Ms. Emily Erwin, Ms. Vivian Lu, Ms. Maria Hoo, Mr. Nolan Ballew, and ECE business office staffs.

Moreover, I would like to acknowledge that this dissertation work is sponsored by the National Science Foundation Grant Number 1602012 and the MII funding, which are gratefully acknowledged.

Lastly, I would like to thank my family, especially my parents, Weiqi Zou and Huaya Shen, for the love and encouragement, who raised me with a love of engineering and science, and supported me in all my pursuits. Special thanks to my wife Yiran Xiao for her love, company, encouragement, and patience throughout my ups and downs during my Ph.D.

# Table of Contents

| Acknowledgements                                                       | ii  |

|------------------------------------------------------------------------|-----|

| List of Tables                                                         | vi  |

| List of Figures                                                        | vii |

| Chapter 1: Introduction                                                | 1   |

| 1. 1 Background                                                        | 1   |

| 1. 1. 1 GaN devices                                                    | 1   |

| 1. 1. 2 EV Charging System                                             | 3   |

| 1. 1. 3 Challenges of GaN-Based System Design                          | 5   |

| 1. 2 Objectives and Research Problems                                  | 7   |

| 1. 3 Synopsis of the Dissertation                                      | 11  |

| Chapter 2 : Single-Phase Boost PFC Rectifier                           | 14  |

| 2. 1 Totem-Pole Bridgeless PFC Operation                               | 15  |

| 2. 2 Control of Totem-Pole Bridgeless PFC                              | 17  |

| 2. 2. 1 Current Loop                                                   | 17  |

| 2. 2. 2 Voltage Loop                                                   | 18  |

| 2. 2. 3 Zero-Crossing Distortion and Soft Transition                   | 20  |

| 2. 2. 4 Start-Up Inrush Control                                        | 21  |

| 2. 3 EMI Filters                                                       | 26  |

| 2. 3. 1 DM Filter Modeling                                             | 26  |

| 2. 3. 2 Simulation Verification                                        | 29  |

| 2. 4 Improved Dynamic Ripple-Based Inductor Design                     | 30  |

| 2. 4. 1 Current Ripple Analysis                                        | 31  |

| 2. 4. 2 Inductance Variation                                           | 33  |

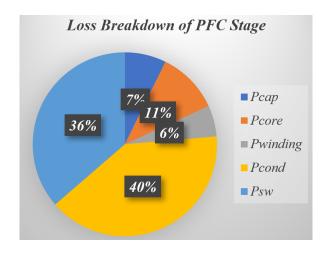

| 2. 4. 3 Loss Breakdown                                                 | 35  |

| 2. 4. 4 Simulation Verification                                        | 37  |

| 2. 5 Design Details                                                    | 38  |

| 2. 5. 1 DC Link Capacitor Loss                                         | 40  |

| 2. 5. 2 Semiconductor Loss                                             | 41  |

| 2. 5. 3 Robust Gate Driver                                             | 43  |

| 2. 6 Experimental Verification                                         | 44  |

| 2. 6. 1 Minimum Inrush Current                                         | 44  |

| 2. 6. 2 Zero-Crossing Current Spike Mitigation                         | 46  |

| 2. 6. 3 Steady-State Operation                                         | 47  |

| 2. 7 Summary                                                           |     |

| Chapter 3: Integrated Transformer Design and Optimization              |     |

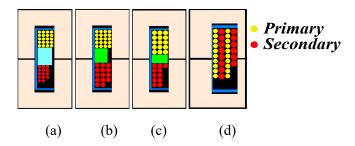

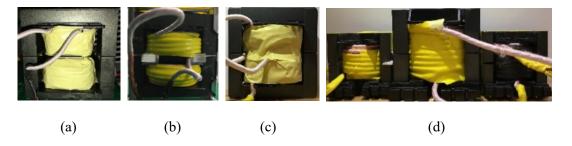

| 3. 1 The Proposed Litz-Wire Based Single-Phase Integrated Transformers | 53  |

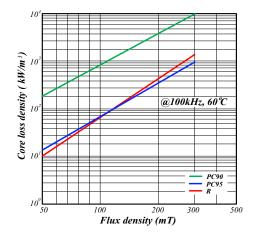

| 3. 1. 1 Transformer Core Loss Model                                    |     |

| 3. 1. 2 Litz Wire Winding Loss Analyses                                | 58  |

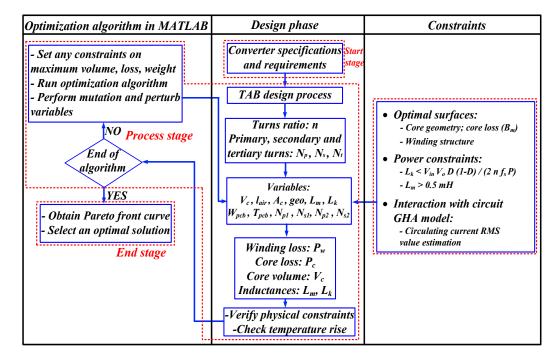

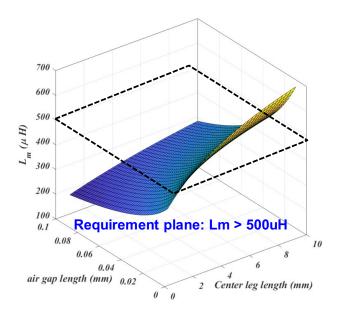

| 3. 1. 3 Optimal Design Process                                         |     |

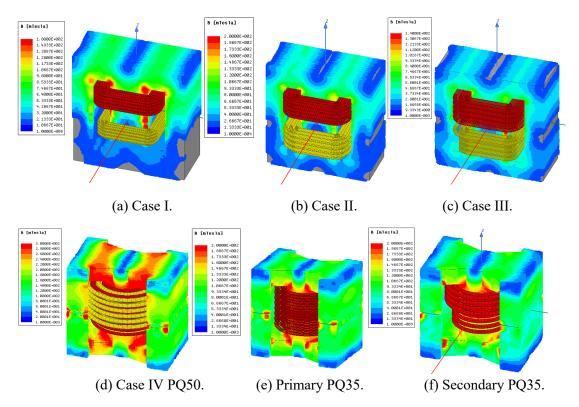

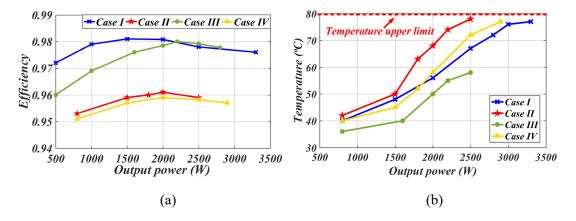

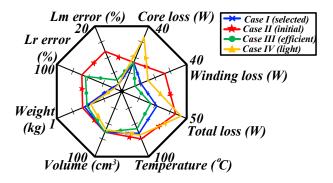

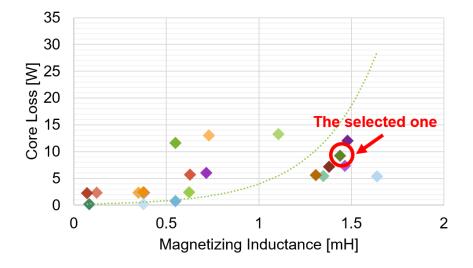

| 3. 1. 4 Comparison and Simulation Results                              |     |

| 3. 1. 5 Experimental Verifications                                     |     |

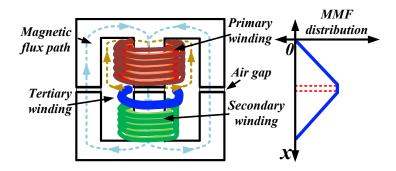

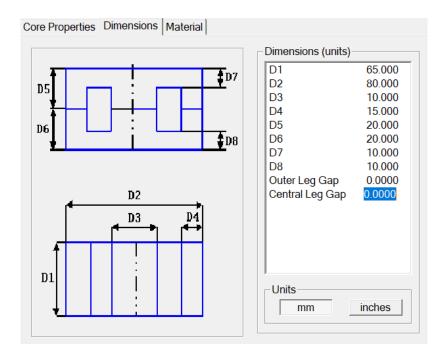

| 3. 2 The Proposed Integrated Planar Transformer                        |     |

| 3. 2. 1 The Planar Transformer Loss Model                    | 71  |

|--------------------------------------------------------------|-----|

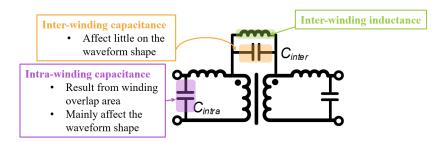

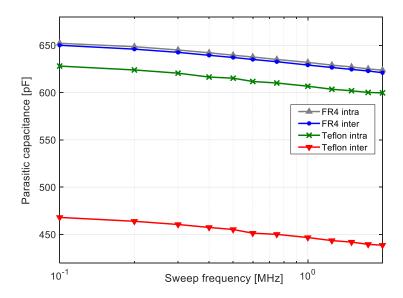

| 3. 2. 2 Parasitic Capacitance Study                          | 76  |

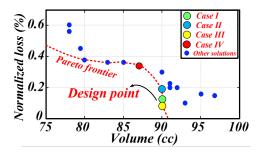

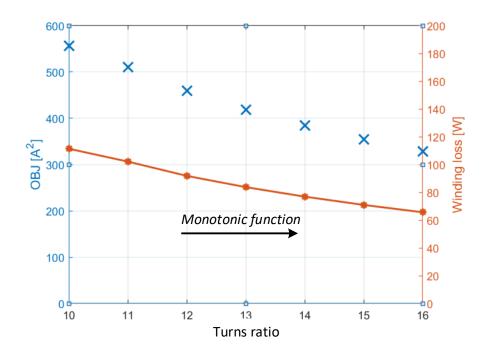

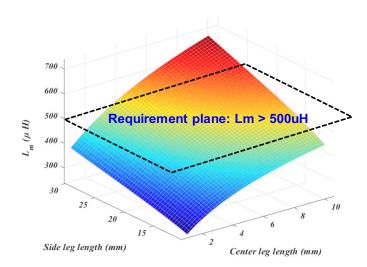

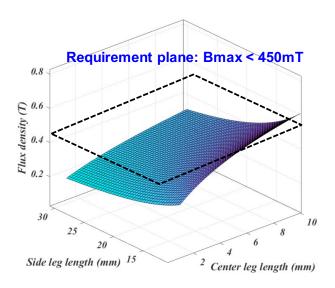

| 3. 2. 3 Multi-Objective Optimization                         | 83  |

| 3. 3 Verification                                            | 87  |

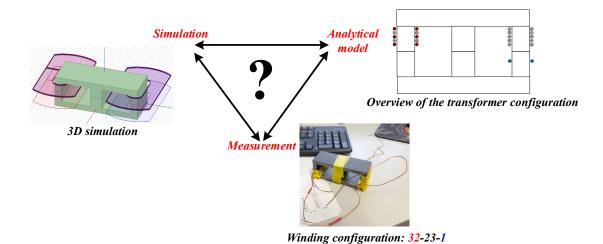

| 3. 3. 1 Scale-Down Transformer                               | 88  |

| 3. 3. 2 Validation of the Transformer Prototype              | 89  |

| 3. 4 Summary                                                 | 93  |

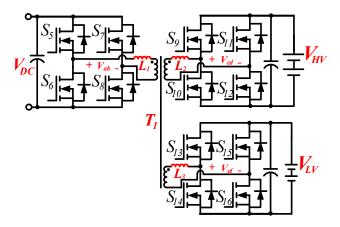

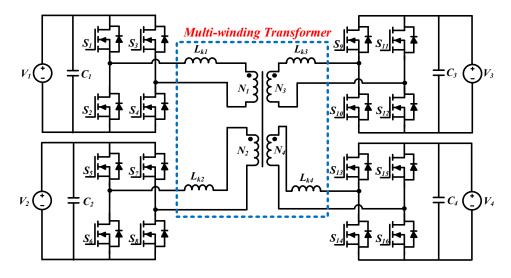

| Chapter 4: Triple-Active-Bridge GaN-Based DC-DC Converter    | 95  |

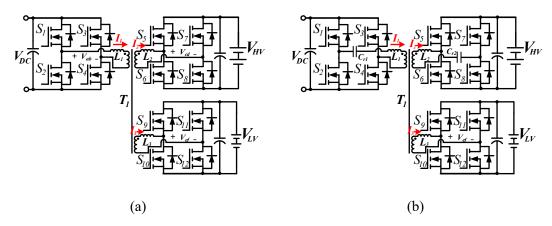

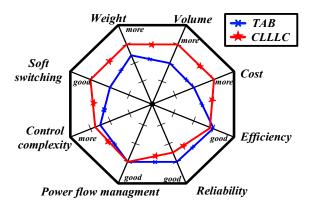

| 4. 1 Topology Study of the Three-Port DC-DC Converter        | 97  |

| 4. 1. 1 Topology Comparisons                                 | 97  |

| 4. 1. 2 Simultaneous Charging Architecture                   | 99  |

| 4. 2 TAB Converter Basic Operation and Design Considerations | 100 |

| 4. 2. 1 Operation Modes Analyses                             | 101 |

| 4. 2. 2 Design Consideration                                 | 102 |

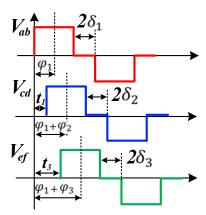

| 4. 3 Phase-Shift and Duty-Ratio Combined Control             | 103 |

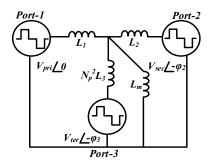

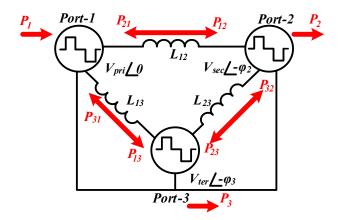

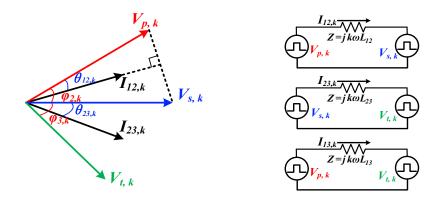

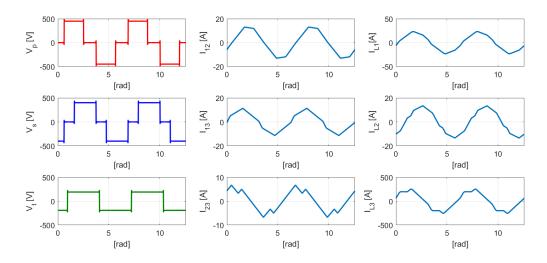

| 4. 3. 1 Decoupled Power Circuits                             | 104 |

| 4. 3. 2 Modeling of a TAB Converter                          | 106 |

| 4. 3. 3 Control Loop Design                                  | 112 |

| 4. 3. 4 ZVS Constraints                                      |     |

| 4. 3. 5 Extended Operation Range                             | 119 |

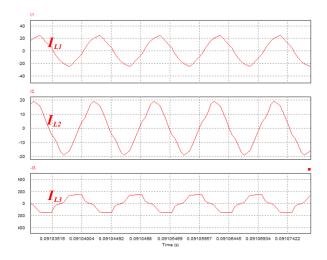

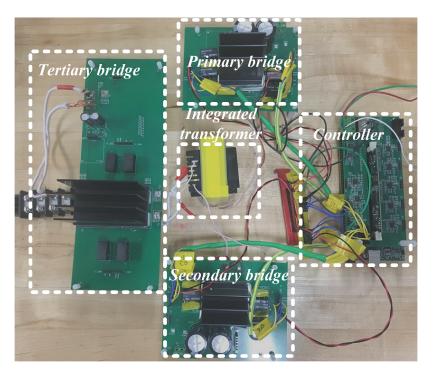

| 4. 4 Experimental Verification                               | 122 |

| 4. 4. 1 Simultaneous Charging of HV and LV Batteries         |     |

| 4. 4. 2 Other Operation Modes                                | 124 |

| 4. 5 Summary                                                 | 127 |

| Chapter 5 : Conclusions and Future Work                      |     |

| 5. 1 Conclusions                                             |     |

| 5. 2 Future Work                                             | 131 |

| Bibliography                                                 | 135 |

# List of Tables

| Table 1-1. Comparison of key properties of Silicon and WBG devices [8]                  | 1     |

|-----------------------------------------------------------------------------------------|-------|

| Table 2-1. The PFC stage design specifications.                                         | 38    |

| Table 2-2. Summary of the component selection in the PFC stage.                         | 39    |

| Table 2-3. DC link capacitor specification.                                             | 40    |

| Table 2-4. Detailed comparison between the film capacitors and the aluminum capacitors. | 41    |

| Table 3-1. The computed parameters from the optimization process.                       | 60    |

| Table 3-2. The detailed transformer specifications for different cases.                 | 62    |

| Table 3-3. The calculation results for different cases.                                 | 63    |

| Table 3-4. The quantified errors between simulation and proposed flux model             | 66    |

| Table 3-5. The measured parameters for different cases.                                 | 67    |

| Table 3-6. Errors between the conventional and proposed model (Case I).                 | 69    |

| Table 3-7. Lm comparison from different methods.                                        | 89    |

| Table 3-8. The measured parameters for the split and overlap winding boards             | 92    |

| Table 4-1. Simulated performance study between the CLLLC converter and the TAB conver   | rter. |

|                                                                                         | 99    |

| Table 4-2. The required number of PWM and ADC channels and their specifications         | 103   |

| Table 4-3. ZVS examination criteria.                                                    | 118   |

# List of Figures

| Fig. 1-1. The comparison of figure-of-merit over Si, SiC, and GaN devices [10]–[12]2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1-2. Long term GaN power market evolution [13]3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

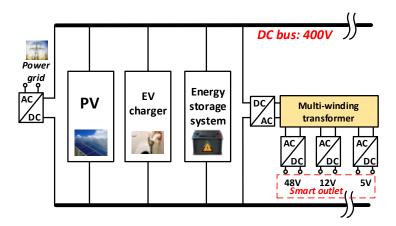

| Fig. 1-3. The typical EV power system, including OBC and APM interfaces4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

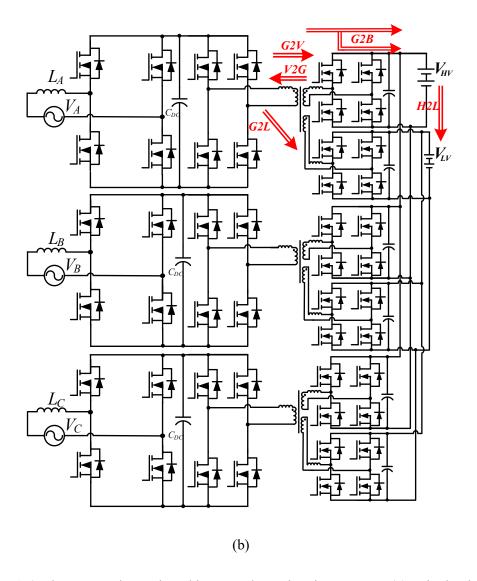

| Fig. 1-3. The proposed GaN-based integrated EV charging systems: (a) a single-phase module; (b) a three-phase system9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

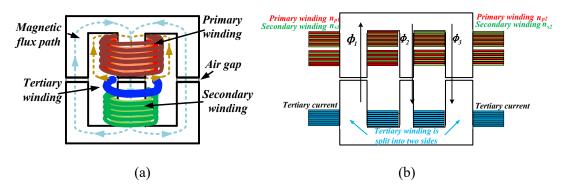

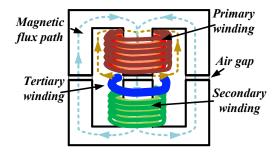

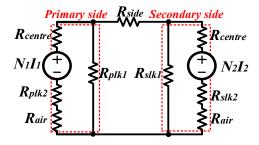

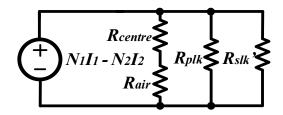

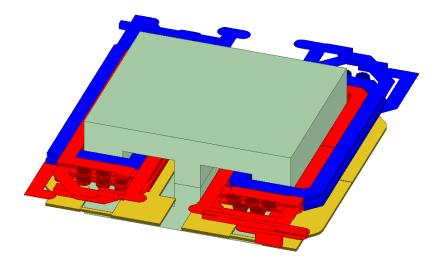

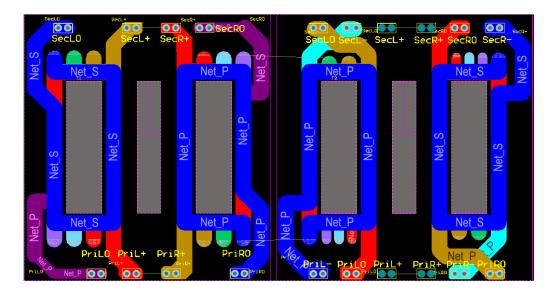

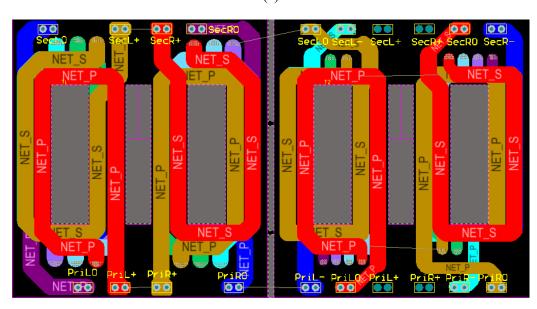

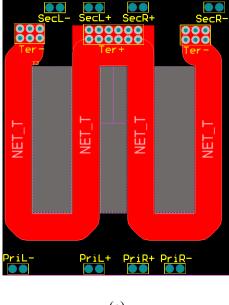

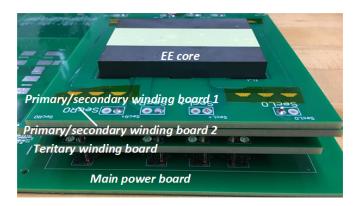

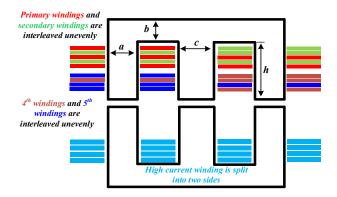

| Fig. 1-4. The integrated transformer configuration: (a) the Litz-wire based transformer; (b) the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| planar transformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

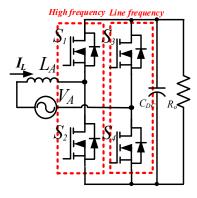

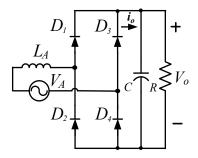

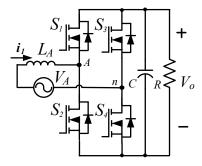

| Fig. 2-1. Topology of a single-phase totem pole PFC rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

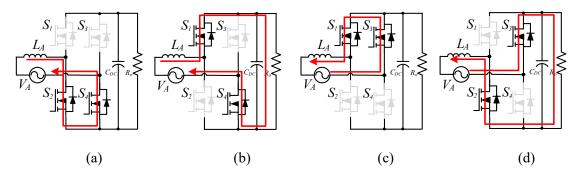

| Fig. 2-2. Operation modes: (a) Mode I: S2 is ON during positive half-cycle; (b) Mode II: S2 is OFF during positive half-cycle; (c) Mode III: S1 is ON during negative half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (d) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during positive half-cycle; (e) Mode IV. S1 is OFF during po |

| IV: S1 is OFF during negative half-cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

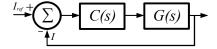

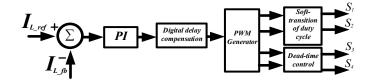

| Fig. 2-3. The current control loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

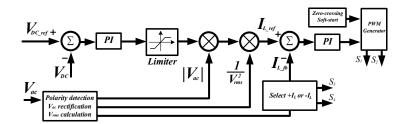

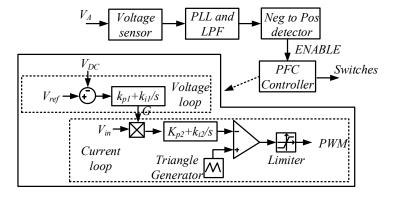

| Fig. 2-4. Overall control block of the totem-pole PFC rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

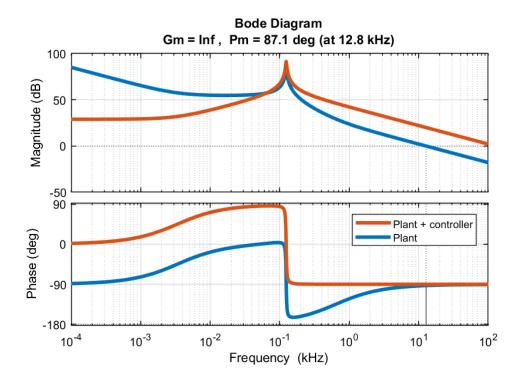

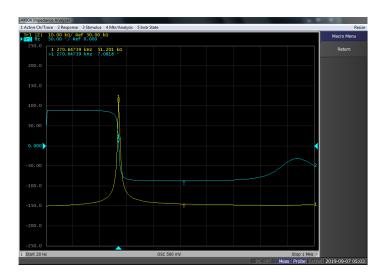

| Fig. 2-5. The Bode plot of the plant and the controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

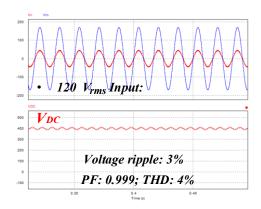

| Fig. 2-6. Simulation results for the PFC operation with 120V AC input voltage20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fig. 2-7. Control diagram for the zero-crossing transition in the totem-pole PFC rectifier21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Fig. 2-8. The equivalent circuit after relay-ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fig. 2-9. The equivalent circuit at steady-state PFC operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 2-10. Block diagram for the PFC minimal start-up inrush current control25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

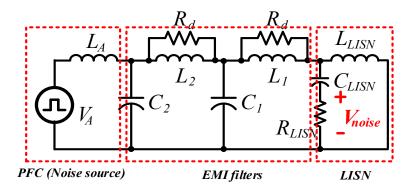

| Fig. 2-11. The equivalent circuit of the DM filters with the PFC rectifier and LISN27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

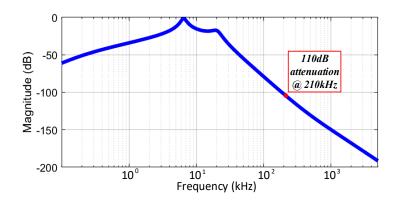

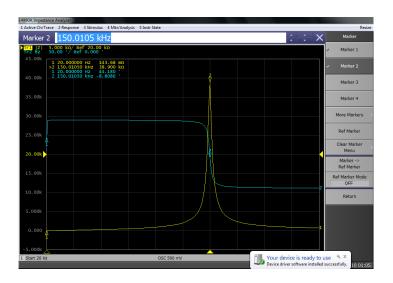

| Fig. 2-12. DM filters frequency response attenuation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

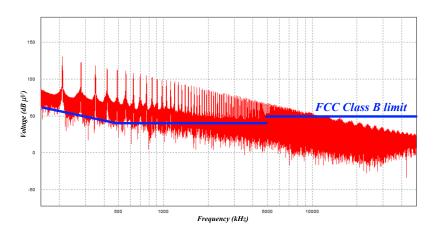

| Fig. 2-13. Simulated EMI spectrum at the LISN without any filters29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

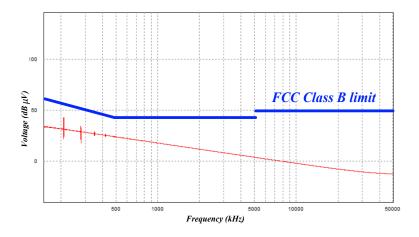

| Fig. 2-14. Simulated EMI spectrum at the LISN with DM filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

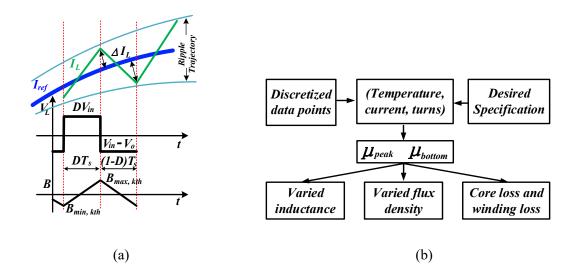

| Fig. 2-15. (a) Inductor ripple over one switching cycle; (b) Dynamic ripple-based estimation flowchart.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

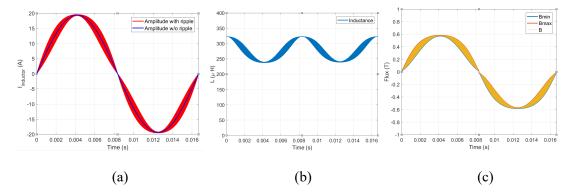

| Fig. 2-16. The computed variations over one line cycle from the proposed algorithm: (a) the inductor current waveform comparisons between with ripple and without ripple; (b) the inductance variation; (c) the high-frequency flux density <i>Bhigh</i> variation35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

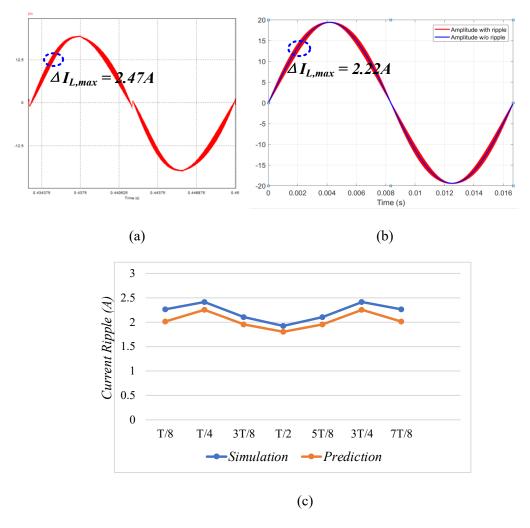

| Fig. 2-17. Comparison of the current waveforms in the PSIM simulation result and the prediction: (a) the simulated inductor waveform; (b) the predicted inductor waveform; (c) comparison of the current ripples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

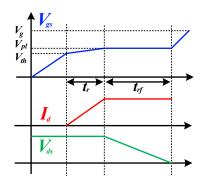

| Fig. 2-18. The relationship between <i>Vds</i> , <i>Vgs</i> and <i>Id</i> during the turn-on process42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Fig. 2-19. Loss breakdown for the PFC stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 2-20. The gate driver schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

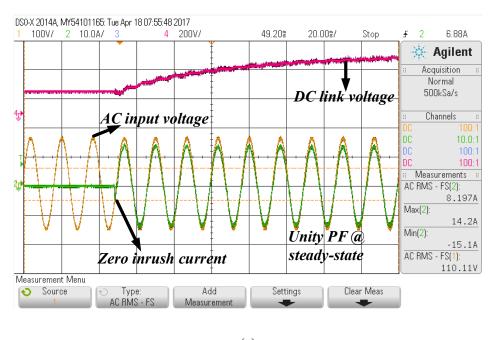

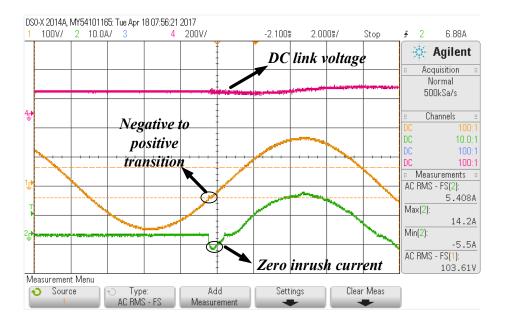

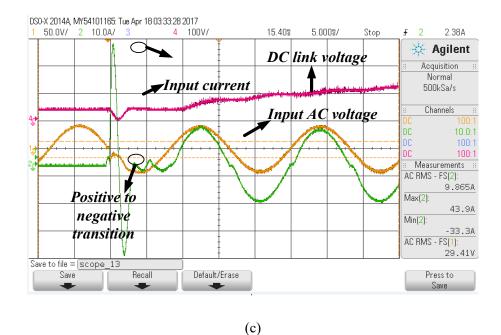

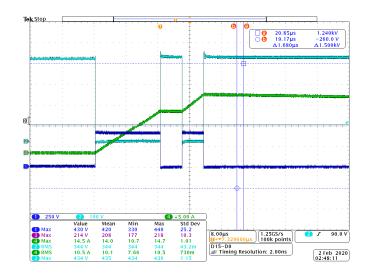

| Fig. 2-21. The experimental waveforms: (a) PFC start-up waveform at 1.5kW load, $V_{in}$ =120V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 60Hz AC RMS, V <sub>DC</sub> (ref)=400V; (b) the transition of the converter from uncontrolled to controlled PFC action during negative to positive zero crossing; (c) PFC start-up waveform while the PFC control is engaged during positive to negative zero crossing of input voltage; the inrush current goes as high as 40A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Infusii cuffeiii goes as fiigh as 40A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

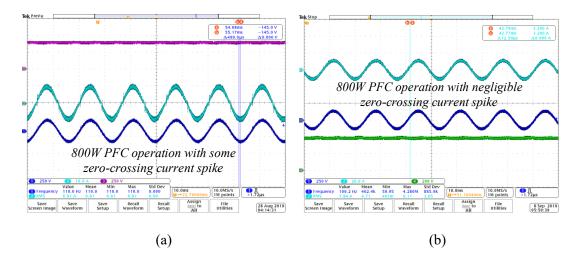

| Fig. 2-22. The experimental waveforms regarding the zero-crossing current distortion: (a PFC controller without soft transition algorithm; (b) the PFC controller with soft trans | -     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| algorithm.                                                                                                                                                                        |       |

| Fig. 2-23. The DPT waveforms for the PFC GaN switch.                                                                                                                              |       |

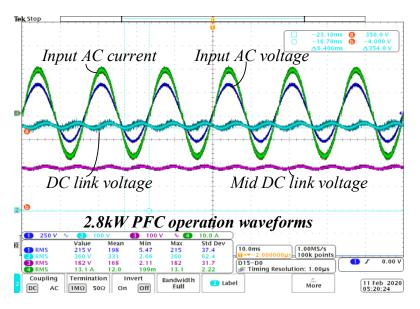

| Fig. 2-24. The steady-state PFC operation waveforms at 2.8kW output power in G2V m                                                                                                |       |

| The input voltage is 240V AC.                                                                                                                                                     | 48    |

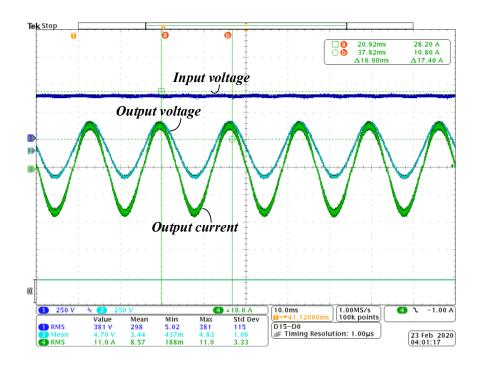

| Fig. 2-25. The steady-state PFC operation waveforms at 2kW output power in V2G mode                                                                                               | 49    |

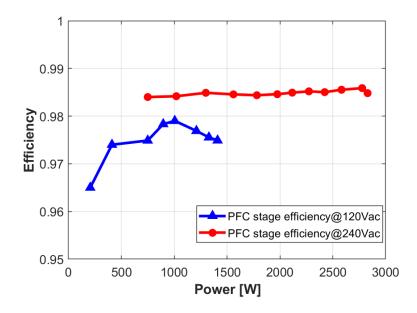

| Fig. 2-26. The measured efficiency curves for different line voltages.                                                                                                            | 50    |

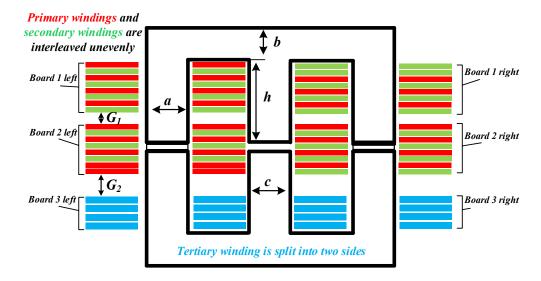

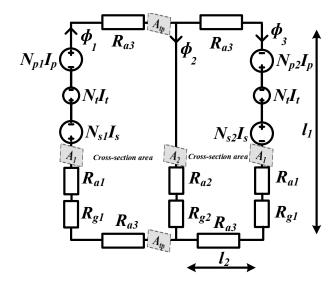

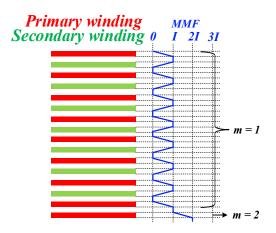

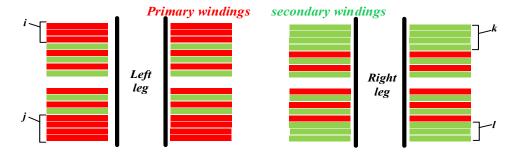

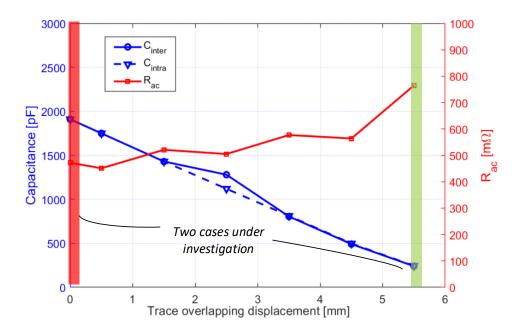

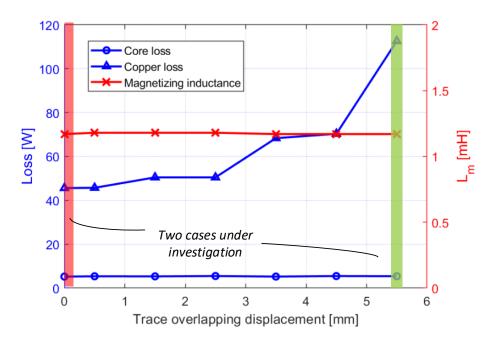

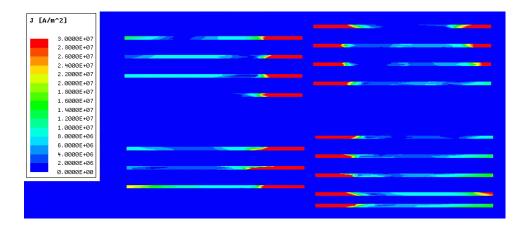

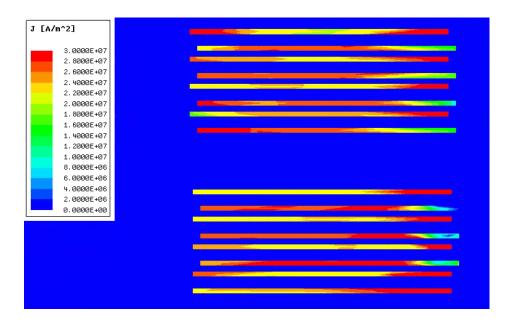

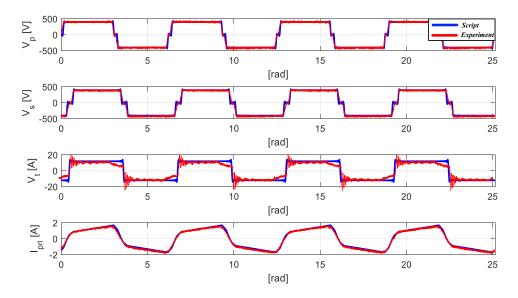

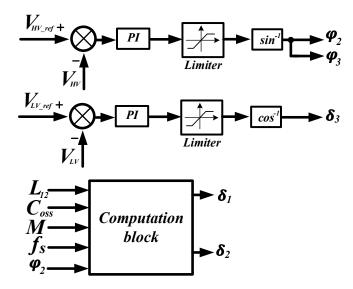

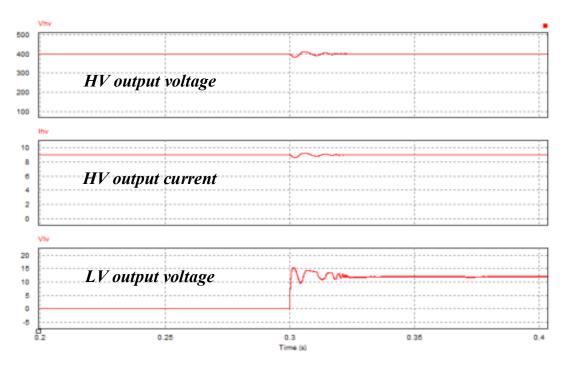

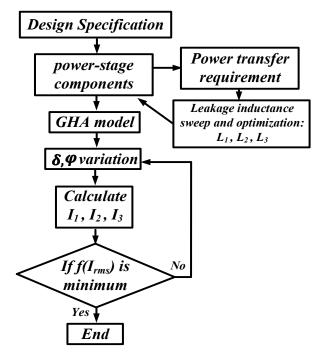

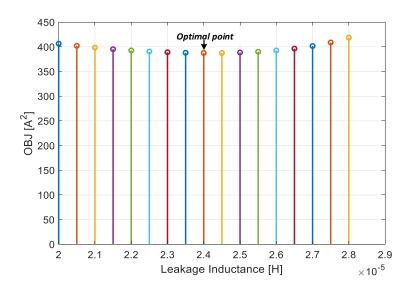

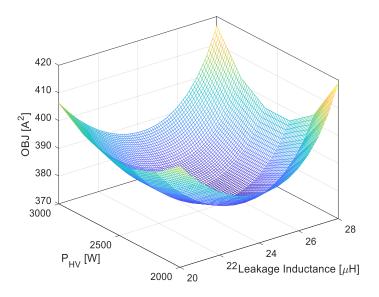

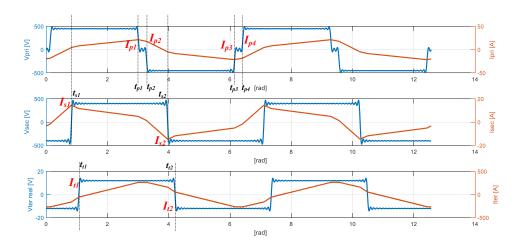

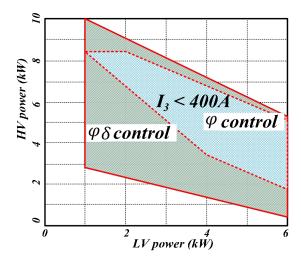

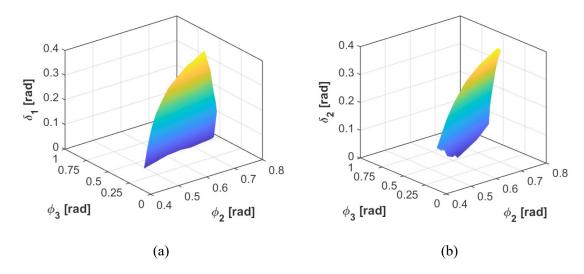

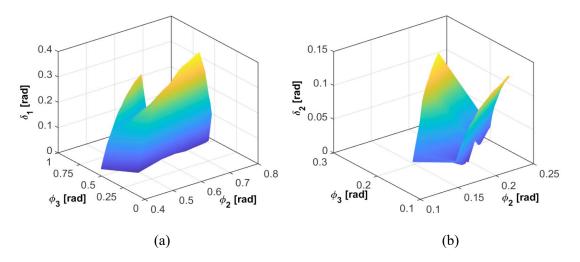

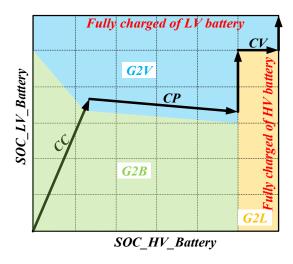

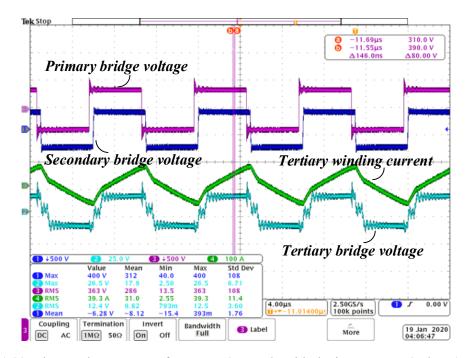

| Fig. 3-1. The diagram of a single-phase integrated transformer using EE-shape core                                                                                                | 54    |