**ABSTRACT**

Title: ELECTROSTATIC DISCHARGE AND

ELECTRICAL OVERSTRESS FAILURES OF

NON-SILICON DEVICES

Yu-Chul Hwang

Doctor of Philosophy, 2004

Directed By: Professor Michael G. Pecht

Department of Mechanical Engineering

Electrostatic discharge (ESD) causes a significant percentage of the failures in the electronics industry. The shrinking size of semiconductor circuits, thinner gate oxides, complex chips with multiple power supplies and mixed-signal blocks, larger chip capacitance and faster circuit operation, all contribute to increased ESD sensitivity of advanced semiconductor devices. Therefore, understanding and controlling ESD is indispensable for higher quality and reliability of advanced device technologies.

This thesis provides a comprehensive understanding of ESD and EOS failures in GaAs and SiGe devices. In the first part of this thesis, characteristics of internal damage caused by several ESD test models and EOS stress in non-silicon devices (GaAs and SiGe) are identified. Failure signatures are correlated with field failures using various failure analysis techniques.

The second part of this thesis discusses the effects of ESD latent damage in GaAs devices. Depending on the stress level, ESD voltage can causes latent failures if the device is repeatedly stressed under low ESD voltage conditions, and can cause premature

damage leading eventually to catastrophic failures. Electrical degradation due to ESD-induced latent damage in GaAs MESFETs after cumulative low-level ESD stress is studied. Using failure analysis, combined with electrical characterization, the failure modes and signatures of EOS stressed devices with and without prior low-level ESD stress are compared.

To predict the power-to-failure level of GaAs and silicon devices, an ESD failure model using a thermal RC network was developed. A correlation method of the real ESD stress and square wave pulse has been developed. The equivalent duration of the square pulse is calculated and proposed for the HBM ESD stress. The dependence of this value on the ESD stress level and material properties is presented as well.

# ELECTROSTATIC DISCHARGE AND ELECTRICAL OVERSTRESS FAILURES OF NON-SILICON DEVICES

## By

# Yu-Chul Hwang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland at College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

May 2005

# Advisory Committee:

Professor Michael Pecht, Advisor Professor Christopher Davis Associate Professor Peter Sandborn Associate Professor Patrick McCluskey Associate Professor Omar Ramahi © Copyright by Yu-Chul Hwang 2005

### **ACKNOWLEDGEMENTS**

This dissertation is the result of three and half years of work through which I have been accompanied and supported by many people around me. It is pleasant that I have now the opportunity to express my gratitude to all of them.

First, I am greatly grateful to my advisor, Dr. Michael G. Pecht, for his academic guidance and support throughout my Ph.D. studying, for his wisdom, open mind, and illuminations when I need most, for his energetic working style that gave me guidance to develop and complete my research and academic work.

Second, I would like to thank Dr. Christopher Davis, Dr. Patrick McCluskey, Dr. Sandborn and Dr. Omar Ramahi for kindly consenting to be on my thesis committee and their time, suggestions and comments. I also want to give my special thanks to Dr. Mikyoung Lee who has kept an eye on the progress of my research, who has been always available when I needed her advises. I would like to thank Dr. BongTae Han for his kind advice on my research, course work, serving as a Ph. D. qualifying exam committee and life in the U.S. for last three and half years. His strict and extensive comments and instructions had a direct impact on the quality of Ph. D. work and improvement of my research and presentation skills as well.

I am grateful to my many Korean friends in CALCE, Chang-Woon, Junpyo, Seungmin, Seunyeol, Yuri, Kyoungjun, and Dae-Whan.

Mr. Ho-Sung Jeon, Dong-Su Ryu, and Jin-Woo Kim for introducing me to the CALCE Center and their advices and help over the years in my six year working period at the Quality and Reliability Lab. of Daewoo Electronics Co. Ltd.. I am also grateful to Dr. Das for his instructions that helped me get started in the new environment, Keith Rogers for his friendship, his unselfish help in the laboratory as well as his encouragement, Ping Zhao who started Ph. D. work at the same time with me, Tong Fang, Sanjay Tiku, Yuki Fukuda, Sheng Zhen and other teammates who made the office a pleasant place for work and study, Dr. Azarian and Mr. Chris Wilkinson, for discussions during the last period of my thesis.

I would like to give thank to many of my friends in Korea (Bon-Young, Seoung-Hoon, Inseon, Heon-Gyu, Jae-Woo, Inchan, Si-Young, Sea-Jong, Hyun-Jung, Dong-Ju, Jae-Sang, Hyuk-Jae, Jin-Young, Hack-Soo, Jae-Goo, Min-Gyu, Hac-Ju, Chan-Hee, Dong-Kyung and many others). Even though we have not seen each other for a long time, our continuous communications over the phone and on the web have always reminded me of lovely memories of my homeland, Korea.

I would like to express heartfelt thanks to all colleagues and other people in the CALCE Electronic Products and Systems Center, Department of Mechanical Engineering, for their valuable help and friendship.

Last but certainly not least, I am especially indebted to my wife, Dami, my lovely daughter Emily, and parents in Korea for their encouragement, support, and love, as always.

# TABLE OF CONTENTS

| TABLE  | OF CONTENTS                                                | IV  |

|--------|------------------------------------------------------------|-----|

| LIST O | F TABLES                                                   | VI  |

| LIST O | F FIGURES                                                  | VII |

| LIST O | F FIGURES                                                  | VII |

| 1. IN  | FRODUCTION                                                 | 1   |

| 1.1    | Creating Electrostatic Charge                              | 3   |

| 1.2    | ESD/EOS Effects in Electronic Industries                   | 6   |

| 1.3    | ESD/EOS Protection Circuits                                | 10  |

| 2. ES  | D CHARACTERIZATION IN IC DEVICES                           | 14  |

| 2.1    | Basic Device Physics                                       | 15  |

| 2.2    | ESD/EOS Induced-Failure Mode and Mechanism                 | 17  |

| 2.3    | ESD Test Models                                            | 21  |

| 3. OB  | JECTIVES AND OUTLINE OF THIS THESIS                        | 33  |

| 4. FA  | ILURE ANALYSIS AND ESD EVALUATION OF S <b>IGE</b> OPAMPS   | 36  |

| 4.1    | SiGe devices and ESD                                       | 36  |

| 4.2    | Wideband Fixed-Gain Amplifiers                             | 40  |

| 4.3    | ESD test and electrical characterization                   | 42  |

| 4.4    | Failure analysis results                                   | 47  |

| 4.5    | Discussions and conclusions                                | 54  |

| 5. IN  | VESTIGATION OF FIELD FAILURES AND FAILURES CAUSED          | BY  |

| EOS AN | ND ESD IN GAAS MMIC                                        | 59  |

| 5.1    | GaAs devices and ESD                                       | 59  |

| 5.2    | Experimental approach                                      | 61  |

| 5.3    | ESD and EOS failure threshold test results                 | 64  |

| 5.4    | Failure analysis results                                   | 65  |

| 5.4    | .1. Failure mode identifications                           | 66  |

| 5.4    | .2. X-Ray observation                                      | 67  |

| 5.4    | .3. Decapsulation and optical microscopy/ESEM observations | 68  |

| 5.5    | Summary and conclusions                                    | 72  |

| 6. | ESI           | D-INDUCED LATENT FAILURES                             |                 |

|----|---------------|-------------------------------------------------------|-----------------|

|    | 6.1           | ESD Latent failure                                    | 76              |

|    | 6.2           | GaAs Devices and Latent Failure                       | 78              |

|    | 6.3           | Experimental procedure                                | 79              |

|    | 6.4           | Test Results                                          | 82              |

|    | 6.4.          | 1. ESD/EOS failure threshold test results             | 82              |

|    | 6.4.          | 2. ESD latent damage test result                      | 83              |

|    | 6.4.          | .3. EOS test after low level ESD stress               | 85              |

|    | 6.4.          | 4. The effect of thermal annealing                    | 87              |

|    | 6.5           | Failure Analysis Results                              | 88              |

|    | 6.5.          | 1. ESD stressed device                                | 88              |

|    | 6.5.          | 2. EOS stressed devices with no prior ESD stress      | 89              |

|    | 6.5.          | .3. EOS stressed devices with initial ESD stress      | 90              |

|    | 6.5.          | 4. Field failed devices                               | 93              |

|    | 6.6           | Conclusions                                           | 93              |

| 7. | ESI           | O FAILURE PREDICTION                                  | 95              |

|    | 7.1           | Background of ESD Failure Prediction and Power-to-Fai | lure Prediction |

|    | Model         | ls                                                    | 95              |

|    | 7.2           | Heat Flow Model Using Thermal RC Circuit              | 99              |

|    | 7.3           | Power-to-failure generation                           | 103             |

|    | 7.4           | Failure prediction for ESD pulse                      | 106             |

|    | 7.5           | Correlation of ESD and square pulse                   | 109             |

|    | 7.6           | Conclusions                                           | 112             |

| 8. | CO            | NTRIBUTIONS                                           | 114             |

| 9. | 9. REFERENCES |                                                       | 116             |

# LIST OF TABLES

| Table 1.1 Possible ESD phenomena in real life [6]                       | 4             |

|-------------------------------------------------------------------------|---------------|

| Table 1.2 Loses due to ESD in electronic industries [12]                | 7             |

| Table 2.1 ESD immunity classification                                   | 31            |

| Table 4.1 Properties of semiconductor materials [34]-[36]               | 37            |

| Table 4.2 Features, applications, and device data                       | 41            |

| Table 4.3 Absolute maximum ratings                                      | 41            |

| Table 4.4 Recommended operating conditions                              | 41            |

| Table 4.5 ESD failure threshold test results                            | 43            |

| Table 4.6 Measurements of electrical parameters (DC characteristics) of | of all the 20 |

| devices before being subjected to ESD stress                            | 46            |

| Table 4.7 Electrical parameters (DC characteristics) measured after ES  | D exposure    |

|                                                                         | 46            |

| Table 4.8 Characteristics of failure signatures                         | 54            |

| Table 5.1 ESD and EOS failure threshold test results                    | 64            |

| Table 5.2 Devices investigated for failure analysis                     | 65            |

| Table 5.3 Characteristics of failure signatures                         | 73            |

| Table 6.1 ESD and EOS failure threshold test result                     | 82            |

| Table 6.2 ESD/EOS threshold test results after multiple stresses        | 86            |

# LIST OF FIGURES

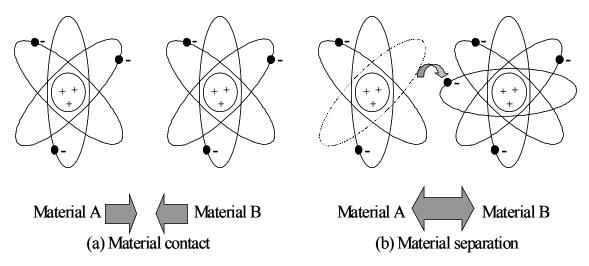

| Figure 1.1 The mechanism of triboelectric charge – contact and separation [3]   | 3      |

|---------------------------------------------------------------------------------|--------|

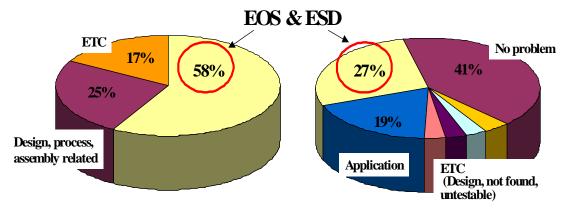

| Figure 1.2 Distribution of failure causes in IC devices [9], [10]               | 6      |

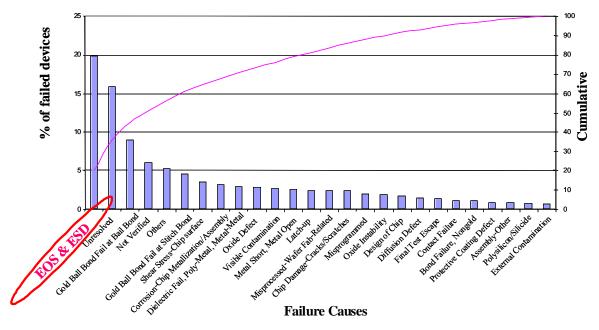

| Figure 1.3 Pareto chart of the failure causes of IC devices [11]                | 7      |

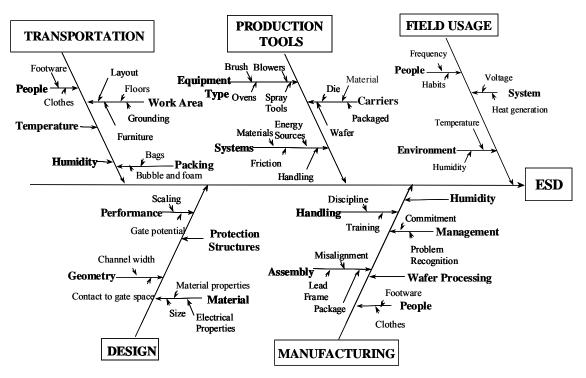

| Figure 1.4 Fishbone Diagram for Electrostatic discharge failures on IC devices  | [13]   |

|                                                                                 | 9      |

| Figure 1.5 Typical CMOS input protection scheme                                 | 11     |

| Figure 2.1 Decrease in thermal conductivity of silicon with increasing temperat | ture   |

| [25]                                                                            | 16     |

| Figure 2.2 A rapid decrease in resistivity of doped silicon with increasing     |        |

| temperature [25]                                                                | 16     |

| Figure 2.3 Cross sectional drawing of ESD damage in bipolar structures [25]     | 20     |

| Figure 2.4 Cross sectional drawing of ESD damage in MOS structures [25]         | 20     |

| Figure 2.5 HBM ESD waveform at 500 V, short circuit [26]                        | 22     |

| Figure 2.6 HBM test circuit [26]                                                | 22     |

| Figure 2.7 Machine model waveform at 500 V, short circuit [26]                  | 25     |

| Figure 2.8 MM ESD test circuit [28]                                             | 25     |

| Figure 2.9 CDM ESD test setup                                                   | 27     |

| Figure 2.10 Typical current waveform from CDM                                   | 27     |

| Figure 4.1 Advantages of SiGe devices                                           | 38     |

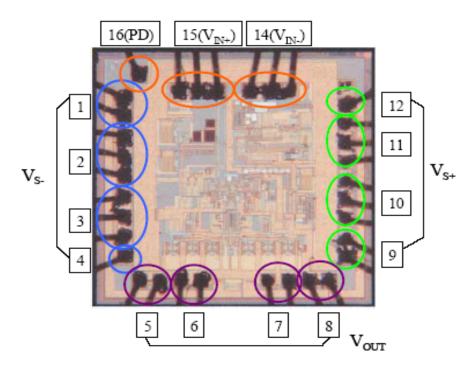

| Figure 4.2 Pin assignments and top view)                                        | 40     |

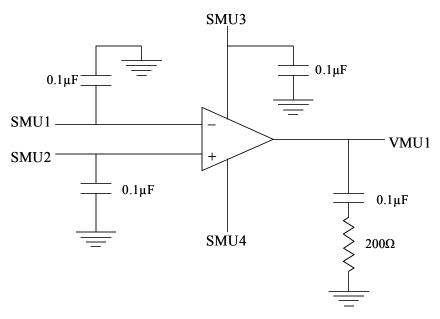

| Figure 4.3 Test setup used for DC characteristics measurements                  | 44     |

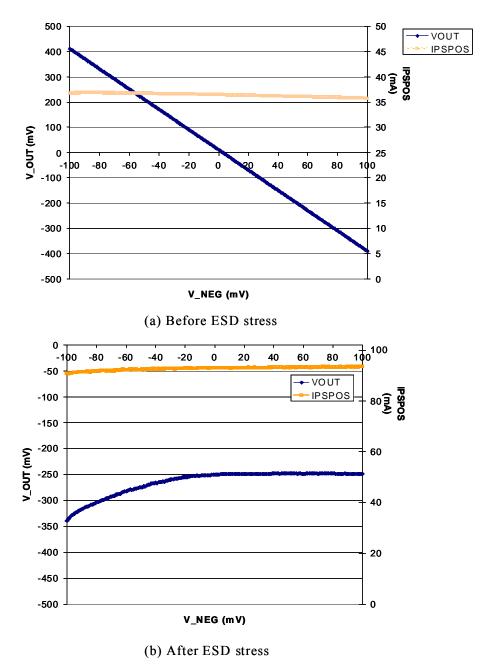

| Figure 4.4 Typical DC characteristics with Vs=±2.5V before and after ESD stre   | ess 45 |

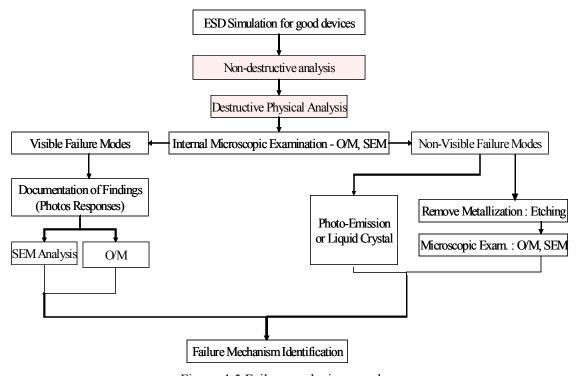

| Figure 4.5 Failure analysis procedure                                           | 47     |

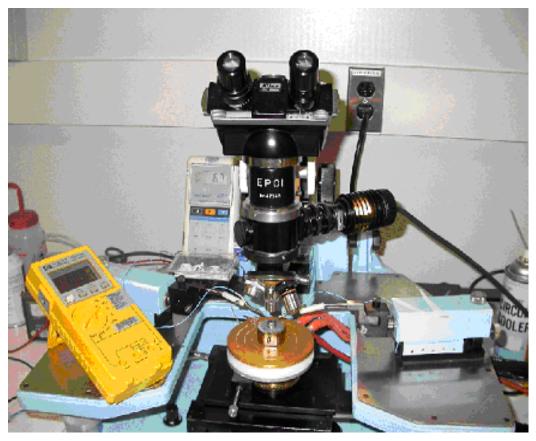

| Figure 4.6 Test set-up for liquid crystal thermal imaging analysis              | 49     |

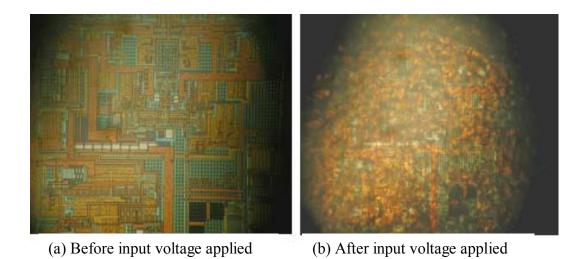

| Figure 4.7 Liquid crystal analysis result for a good device                     | 49     |

| Figure 4.8 Liquid crystal analysis result for failed devices                    | 50     |

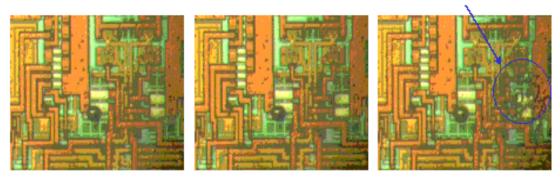

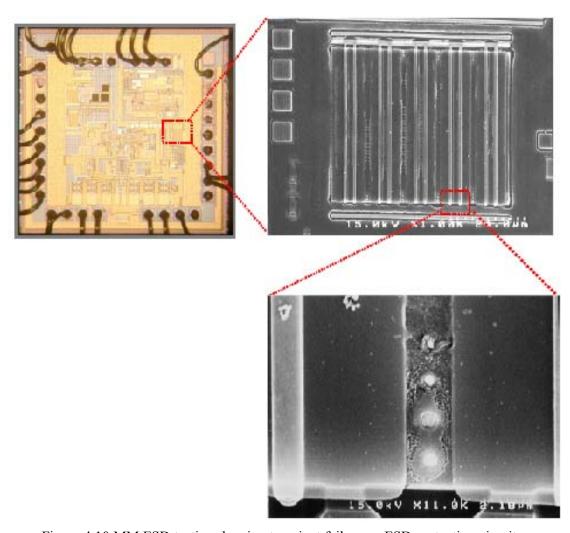

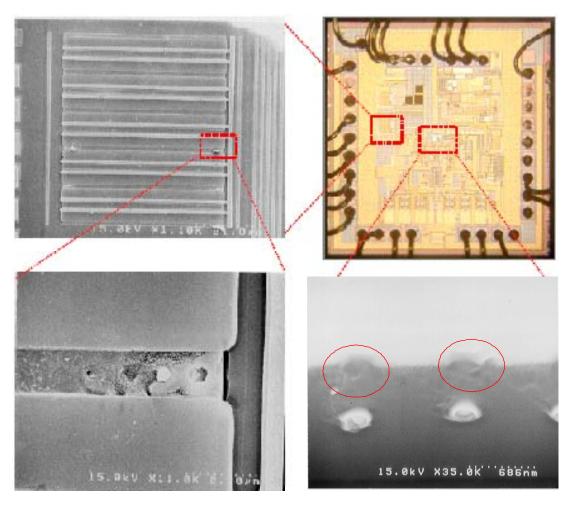

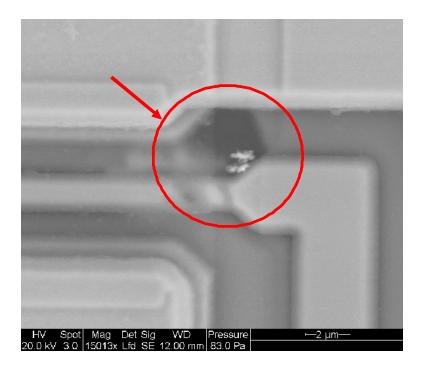

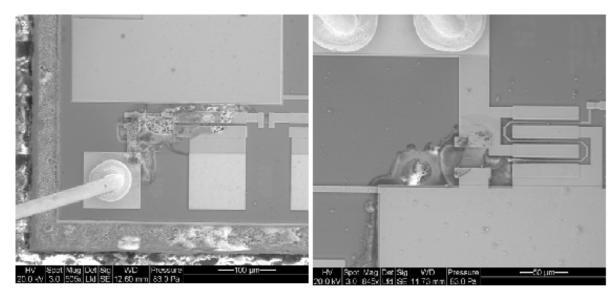

| Figure 4.9 HBM ESD testing showing transient failure on ESD protection circu    | uitry  |

|                                                                                 | 51     |

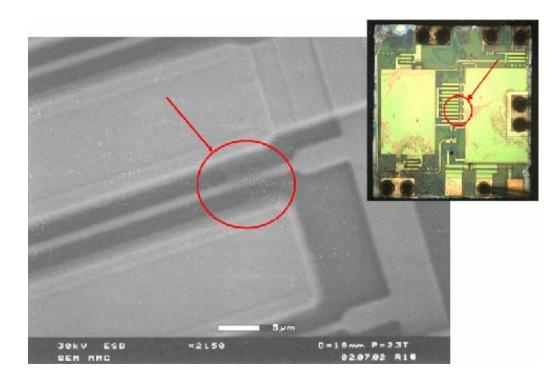

| Figure 4.10 MM ESD testing showing transient failure on ESD prote       | ection circuitry |

|-------------------------------------------------------------------------|------------------|

|                                                                         | 52               |

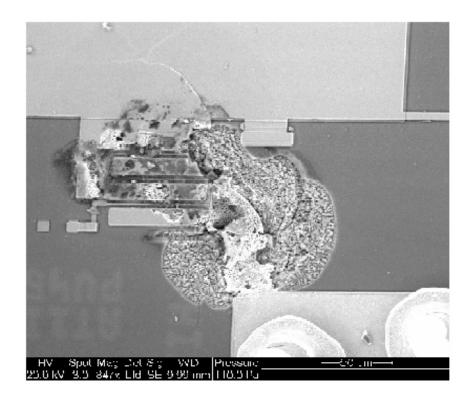

| Figure 4.11 CDM ESD testing showing transient failure on ESD pro-       | tection and      |

| internal circuitry of the gain stage                                    | 53               |

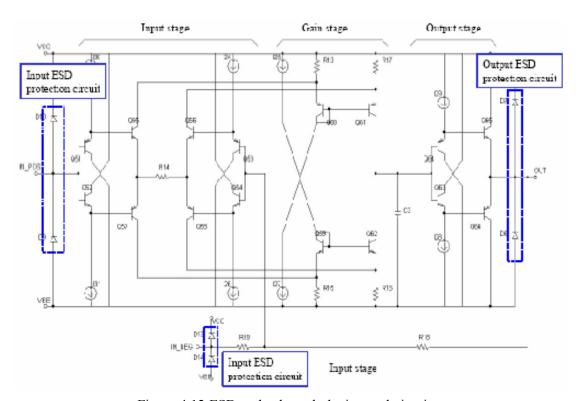

| Figure 4.12 ESD paths through the internal circuit                      | 56               |

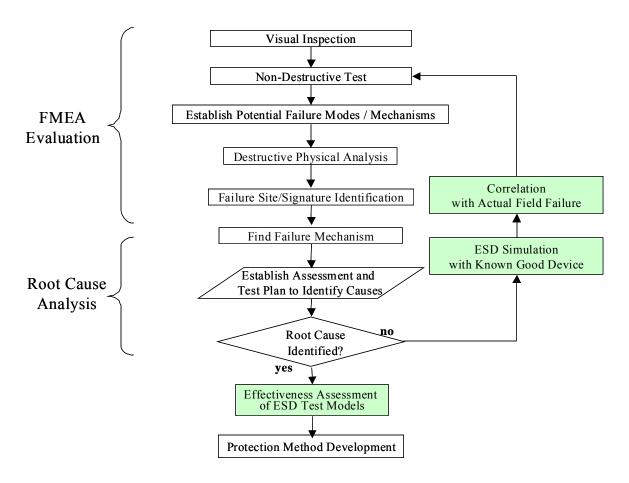

| Figure 5.1 Flowchart of failure analysis process                        | 61               |

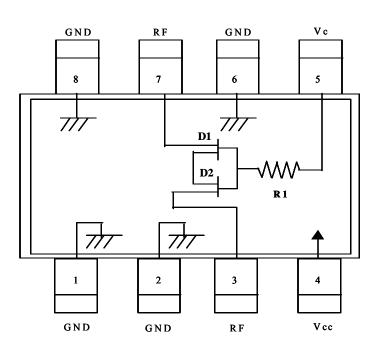

| Figure 5.2 Schematic circuit of the device                              | 62               |

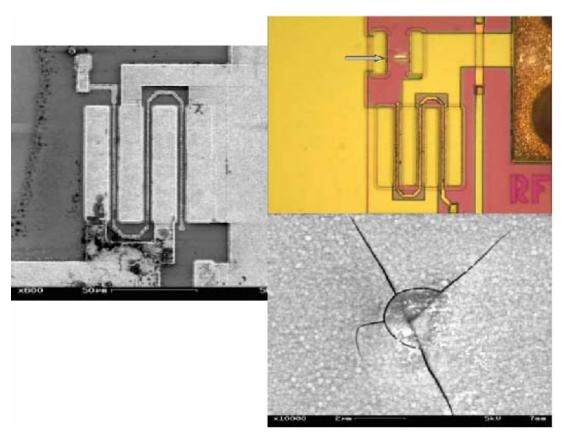

| Figure 5.3 Failure mode identifications                                 | 66               |

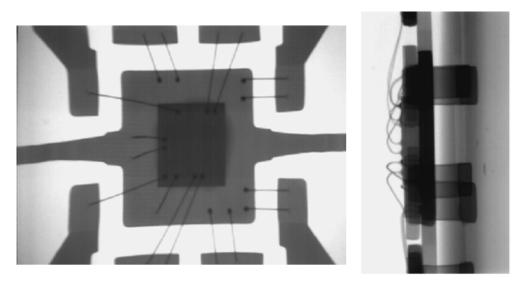

| Figure 5.4 X-Ray observations (top vie and side view)                   | 67               |

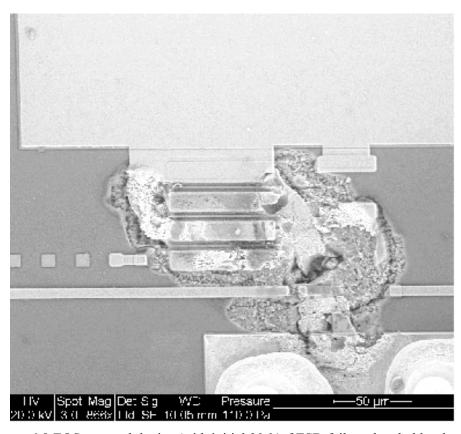

| Figure 5.5 HBM-stressed device                                          | 68               |

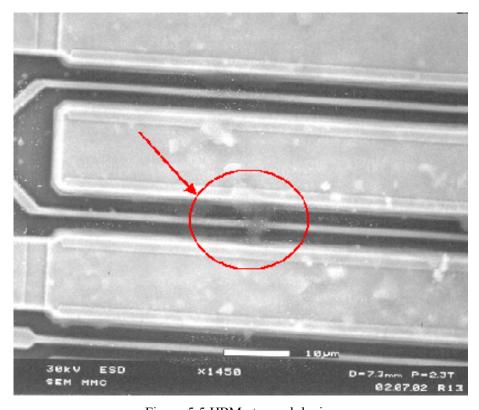

| Figure 5.6 HBM-stressed device                                          | 69               |

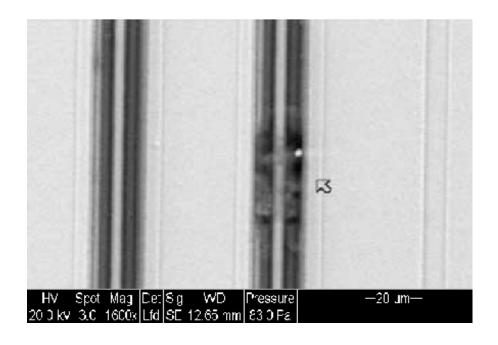

| Figure 5.7 MM-stressed device                                           | 69               |

| Figure 5.8 CDM-stressed device                                          | 70               |

| Figure 5.9 EOS stressed device                                          | 70               |

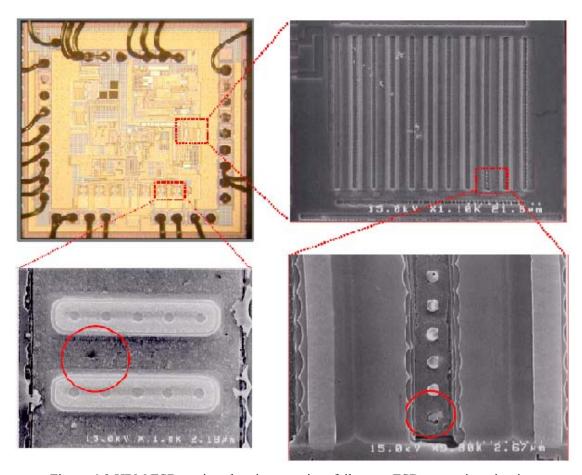

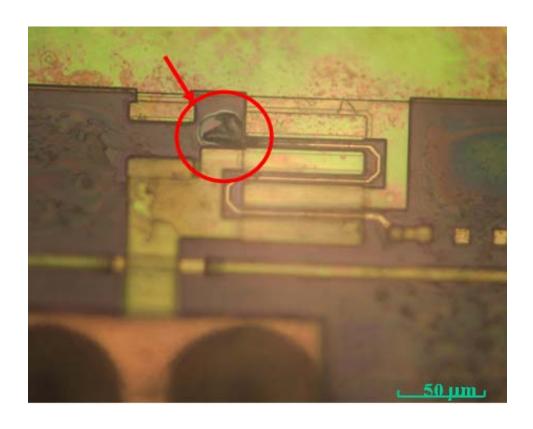

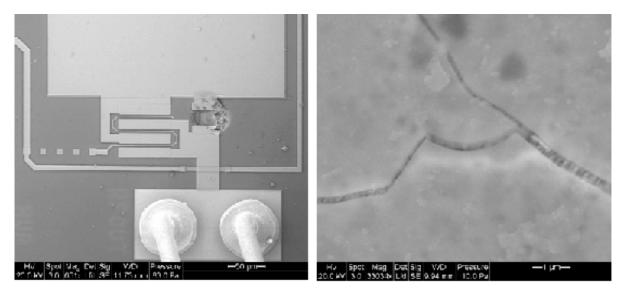

| Figure 5.10 Field failed device                                         | 71               |

| Figure 5.11 Field failed device showing the failure in the resistor are | a and a          |

| mechanical crack in the capacitor area                                  | 71               |

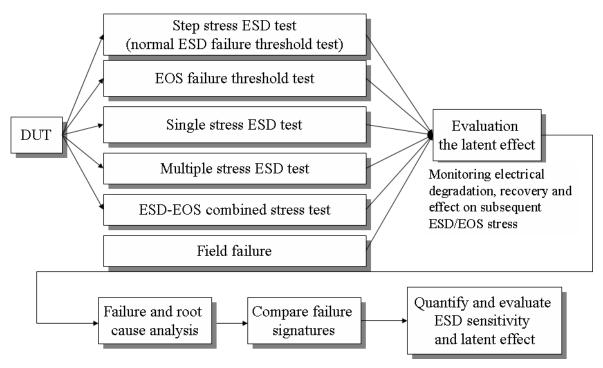

| Figure 6.1 Experimental procedure                                       | 79               |

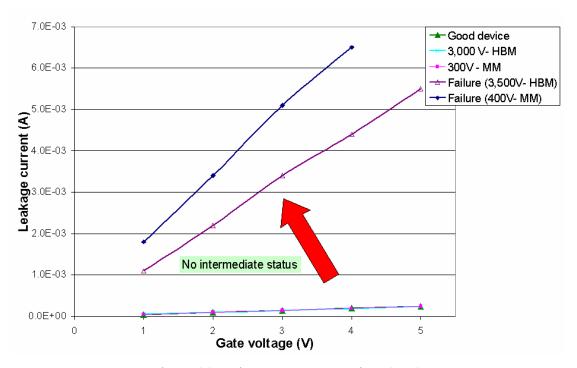

| Figure 6.2 Leakage current comparison (I <sub>GDO</sub> )               | 84               |

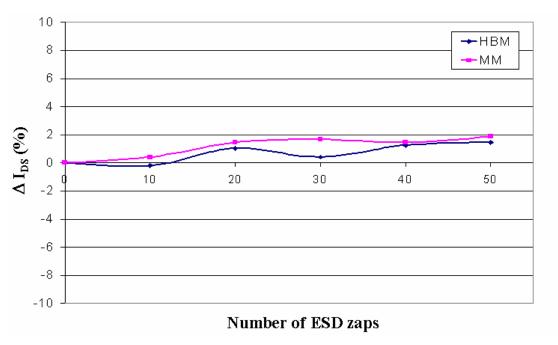

| Figure 6.3 Drain-source current (I <sub>DS</sub> , V <sub>GS</sub> =1V) | 85               |

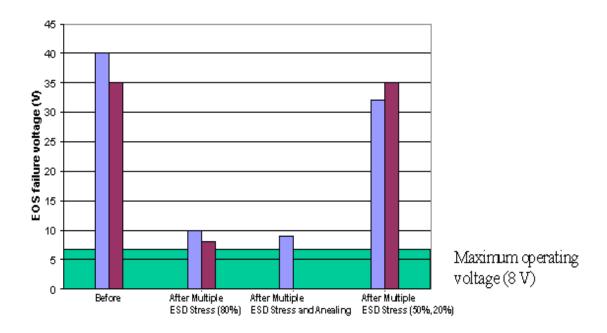

| Figure 6.4 EOS failure threshold comparison                             | 87               |

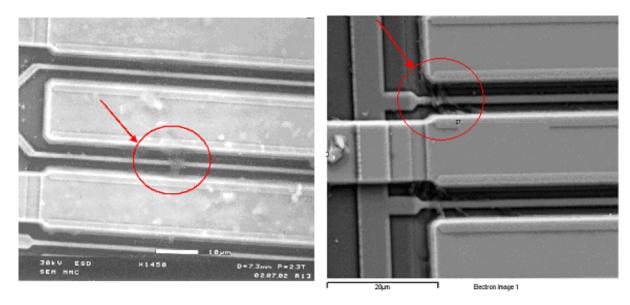

| Figure 6.5 ESD stressed device                                          | 89               |

| Figure 6.6 EOS-stressed device (with initial 80 %of ESD failure thre    | eshold voltage)  |

|                                                                         | 90               |

| Figure 6.7 EOS-stressed device (with initial 80 %of ESD failure thre    | eshold voltage)  |

|                                                                         | 91               |

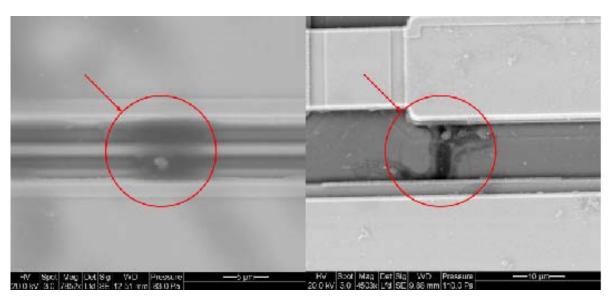

| Figure 6.8 EOS-stressed device (with initial 20 %of ESD failure thre    | eshold voltage)  |

|                                                                         | 91               |

| Figure 6.9 EOS-stressed device (with initial 50 % of ESD failure thre   | eshold voltage)  |

|                                                                         | 92               |

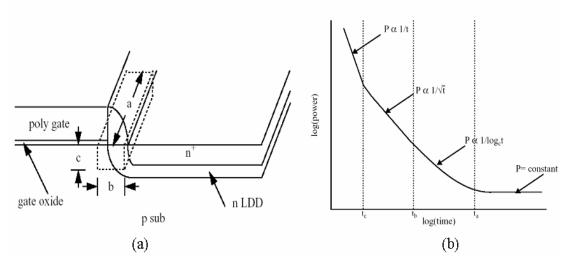

| Figure 7.1 (a) 3D thermal box region of heat dissipation for power-to-failur    | e        |

|---------------------------------------------------------------------------------|----------|

| prediction in an NMOS transistor, (b) Schematic of power-to-failure v           | s. width |

| of a square wave pulse                                                          | 98       |

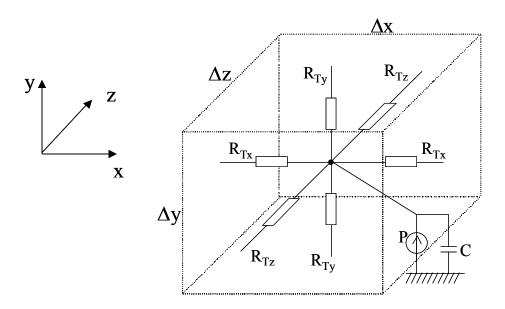

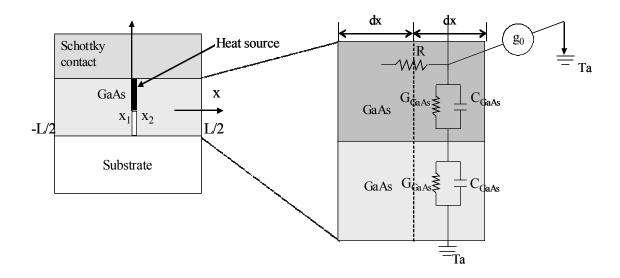

| Figure 7.2 Electrical-thermal equivalent schematic of a solid                   | 99       |

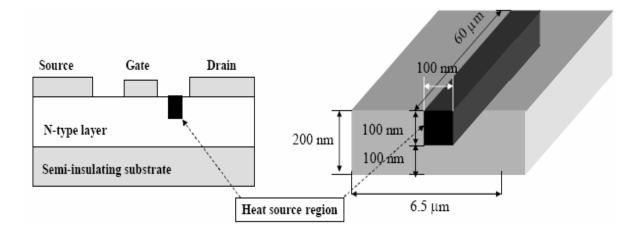

| Figure 7.3 Cross-sectional structure and heat source region                     | 100      |

| Figure 7.4 Electrical-thermal analogy modeling for heat source region           | 101      |

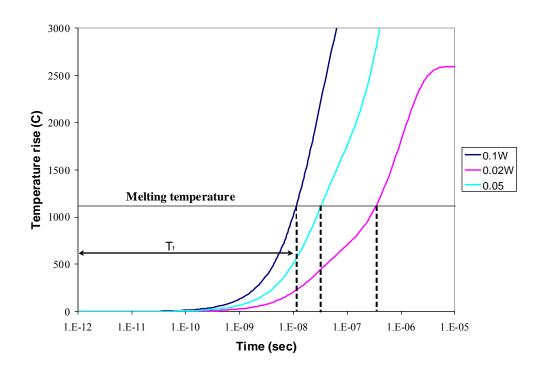

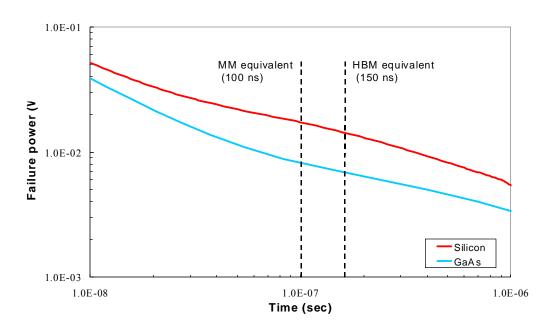

| Figure 7.5 Power-to-failure and Time-to-Failure (T <sub>f</sub> ) Determination | 104      |

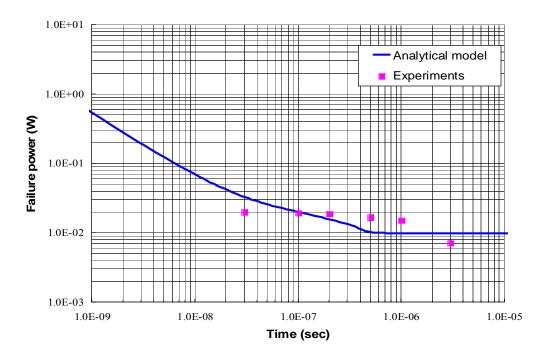

| Figure 7.6 Power-to-failure versus pulse duration, measurement versus pre       | diction  |

| for a silicon device                                                            | 104      |

| Figure 7.7 Comparison of predicted power-to-failure of silicon and GaAs d       | evices   |

|                                                                                 | 105      |

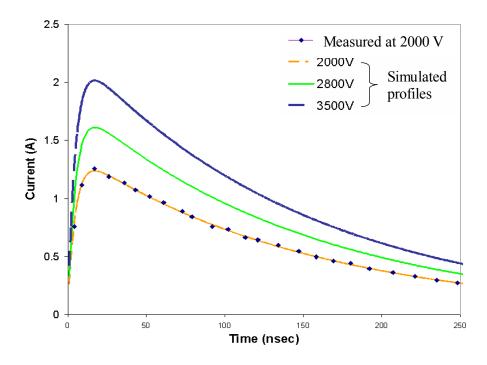

| Figure 7.8 HBM current waveform for failure prediction                          | 106      |

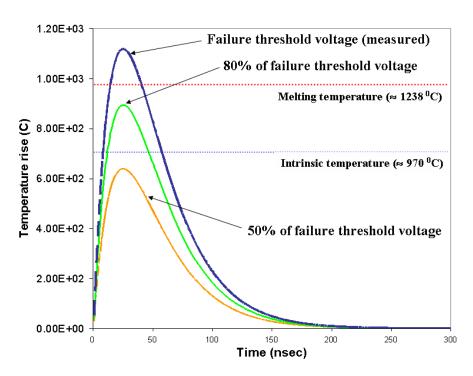

| Figure 7.9 Temperature rise profile from the HBM ESD pulses                     | 107      |

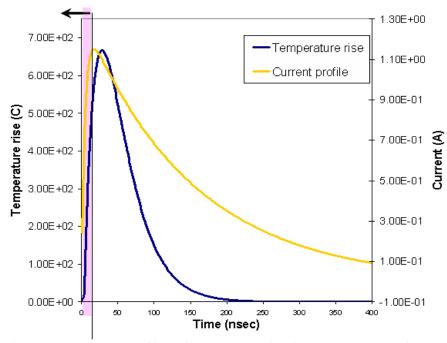

| Figure 7.10 Current profile and temperature rise from HBM ESD pulse             | 109      |

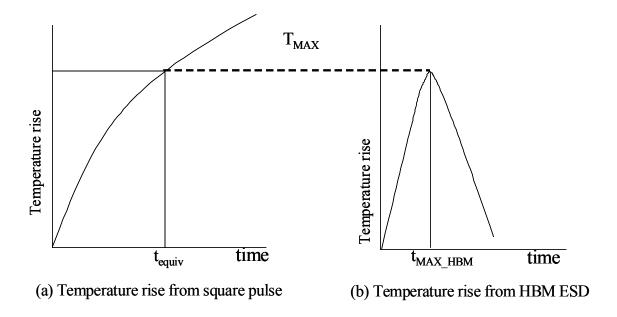

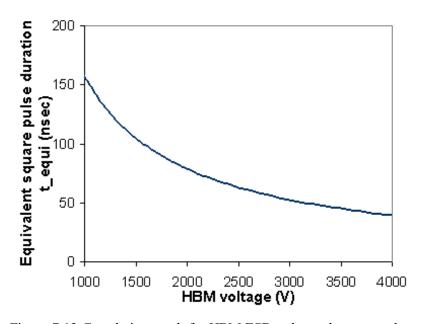

| Figure 7.11 Temperature rise from HBM ESD and square pulse                      | 110      |

| Figure 7.12 Correlation result for HBM ESD pulse and square pulse               | 111      |

## 1. INTRODUCTION

Electrostatic discharge (ESD) is one of the most important reliability problems in the integrated circuit industry. Typically, it is known that one-third to one-half of all field failures are due to ESD and other failures known as electrical overstress (EOS) [1], [2]. Therefore, to achieve higher quality and reliability standards for IC products and to reduce the IC product loss due to ESD and EOS related failures, ESD phenomenon should be well understood and controlled and proper corrective actions should be taken through all phases of IC device design, manufacturing, and use. As ESD damage has become more prevalent in newer technologies due to the higher susceptibility of smaller circuit components, there has been a corresponding increase in efforts to understand ESD failures through modeling and failure analysis. This has resulted in a greater industry-wide knowledge of ESD mechanisms and thus a greater ability to design robust ICs which sustain fewer field failures and in order to obtain higher ESD robustness of IC devices, significant progress has been made in understanding the implications of different types of ESD events on the design of protection circuits, and in implementing highly effective ESD protection circuits at each device technology.

However, despite these efforts, there are still ESD-related problems which are not well understood. The advent of new generation of device technology always leads to new challenges to higher ESD reliability and more efficient protection circuit. ESD is comparatively well known issues in silicon devices and seriously addressed during past years from the many researchers, but the ESD issue in non-

silicon devices such as GaAs and SiGe devices is only discussed in very few publications. Although significant progress has been made in understanding ESD and solving ESD related problems, there is still much room for improvement in the case of non-silicon devices.

Electronic system manufacturers and microelectronics device manufacturers claimed that they have trouble with microelectronics devices damaged after system level burn-in screening. Although the companies comprehended the possibility that the failure has occurred due to EOS or ESD, they have had difficulty in identifying failure causes and the process conditions that lead for damage. However, they need to define failure causes before the right protection can be implemented.

There have been efforts to find evidence of ESD and EOS failures in various process technologies for the last twenty years. But not nearly enough work has been done on classifying various ESD and EOS conditions such as the combination of ESD modes or continuous EOS in accordance with failure characteristics. Classification of failure characteristics will lead to a description of the quantitative causes of failure and this is an important process because manufacturers can understand why, where, and when these failures occur.

The focus of this thesis is on the characterization of ESD/EOS related IC failures, particularly for non-silicon devices using GaAs and SiGe. The objective of this study is to clarify ESD/EOS events experimentally and theoretically, and their effects on semiconductor devices due to the high voltage and current. In order to study ESD/EOS phenomenon, extensive experiments have been conducted, and an analytical model for failure of IC devices is described to explain failure

mechanisms. An outline of the thesis and a list of its objectives are presented in chapter 3.

## 1.1 Creating Electrostatic Charge

ESD is a subset of electrical overstress (EOS) and can be defined as "the transfer of charge between two bodies at different electrical potentials" [3] either through direct contact or through an induced electric field, so it is a charge driven physical mechanism resulting from a charge imbalance. There are three major charge-generation processes; triboelectric charging, induction, and conduction [4]. But usually, this imbalance of electrons on the surface of the material is caused by friction between different materials, which is called triboelectric charging. The potential induced by charges depends on the triboelectric properties of materials, contact area, pressure applied, and friction between the two materials [5]. For example, a person walking across the floor generates static electricity as shoe soles

Figure 1.1 The mechanism of triboelectric charge – contact and separation [3]

Table 1.1 Possible ESD phenomena in real life [6]

| Examples of electrostatic voltage    | Electrostatic voltage |              |  |

|--------------------------------------|-----------------------|--------------|--|

| Generating Source                    | 10 to 20% RH          | 65 to 90% RH |  |

| Person walking on a carpet           | 3500V                 | 1500V        |  |

| Person walking on a vinyl floor      | 1200V                 | 250V         |  |

| Vinyl cover                          | 7000V                 | 600V         |  |

| Polyethylene bag lifted from a bench | 20000V                | 1200V        |  |

| Chair packed with polyurethane foam  | 18000V                | 1500V        |  |

contact and then separate from the floor surface. An electronic device sliding into or out of a bag, magazine or tube generates an electrostatic charge as the device's housing and metal leads make multiple contacts and separations with the surface of the container. While the magnitude of electrostatic charge may be different in these examples, static electricity is indeed generated. Table 1.1 shows that huge electrostatic voltage can be generated even during normal daily life.

Triboelectric charging is generated by a contact and separation mechanism. In an electrically neutral condition, the atoms of materials have same number of positive protons and negative electrons. As shown in Figure 1.1(a), material "A" consists of atoms with equal numbers of protons and electrons. Material "B" also consists of atoms with equal (though perhaps different) numbers of protons and electrons. Once they are placed into contact and separated (Figure 1.1(b)), negatively charged electrons are transferred from the surface of one material to the surface of the other material. Which material loses electrons and which gains electrons is

totally dependent on the tribo-electrical properties of the two materials. In the example of Figure 1.1, the material "A" that loses electrons is charged positively and the material "B" that gains electrons is charged negatively.

This process of material contact, electron transfer and separation is really a more complex mechanism than described here. The amount of charge created by triboelectric generation is affected by the area of contact, the speed of separation, relative humidity, and other factors. Once the charge is created on a material, it becomes an electrostatic charge if it remains on the material. This charge may be transferred from the material, creating an electrostatic discharge, or ESD, event. Additional factors such as the resistance of the actual discharge circuit and the contact resistance at the interface between contacting surfaces also affect the actual charge that can cause damage. Even though triboelectric charging is the most common static charge generation mechanism, it can be generated by induction and conduction.

An electrostatic charge also may be created on a material in other ways such as by induction and conduction. Inductive charging is a two-step process. As a conductive object comes into close with a charged object, part of the field terminates on a conductive object, resulting in an internal separation of charge. When a charged object is removed from the area, a net charge exists on a conductive object but opposite in polarity from what existed on a charged object. The transient caused by induction is similar to a charged device model (CDM) event [7].

One more charging process, conductive charging involves the physical contact and balancing of voltage between two systems or objects at different

potentials. As a charged object is brought into physical contact with an isolated object of lower potential, charge is transferred to the lower biased object until the potential is balanced. When the objects are separated, the two objects have accumulated a charge of the same polarity.

### 1.2 ESD/EOS Effects in Electronic Industries

ESD may be able to change the electrical or physical properties of electronic devices, including semiconductor devices, degrading or destroying them (will be explained in Chapter 2). ESD combined with EOS is one of the most frequently occurring failures in the IC device industry and the potentially destructive nature of ESD in IC devices became more apparent as IC devices became smaller and more complex. As shown in Figure 1.2 (a), it is known that around 60 % of total IC failures are caused by ESD and ESD. A Pareto chart for both plastic and hermetic IC devices also shows that the number one failure mechanism is ESD/EOS (Figure 1.3). So there is no wonder that ESD/EOS is one of the most important failure

(a) Distribution of failure causes in Silicon ICs (b) Distribution of failure causes in GaAs ICs Figure 1.2 Distribution of failure causes in IC devices [9], [10]

Figure 1.3 Pareto chart of the failure causes of IC devices [11]

mechanisms in IC devices. Furthermore this ESD/EOS issue is expected to remain important for future IC technology and future IC device materials like GaAs and SiGe devices [8], [10]. (Figure 1.2 (b)) and this is also applicable to different types of device technologies such as CMOS, bipolar, and MESFETs. In both Figure 1.2

Table 1.2 Loses due to ESD in electronic industries [12]

| ESD losses reported         |              |              |                        |

|-----------------------------|--------------|--------------|------------------------|

| Description                 | Minimum loss | Maximum loss | Estimated average loss |

| Component and manufacturers | 4 %          | 97 %         | 16~22 %                |

| Subcontractors              | 3 %          | 70 %         | 9~15 %                 |

| Contractors                 | 2 %          | 35 %         | 8~14 %                 |

| User                        | 5 %          | 70 %         | 27~33 %                |

and Figure 1.2, EOS and ESD are categorized as a one single failure mechanism, "ESD and EOS". This is because of the similarities in EOS and ESD failure modes and failure signatures. So it is very difficult to distinguish between them. In many field failure analysis cases, both EOS and ESD are categorized as one group of failure causes.

Despite a great deal of effort during the past decade, ESD still affects production yields, manufacturing costs, product quality, product reliability, and profitability. Besides the loss directly associated with the damaged part, the loss from ESD may include;

- engineering time

- loss of reputation

- possible loss of future sales

- rework and test facility

- customer dissatisfaction

- shock to personnel

- damage to equipment

Industry experts have estimated average product losses due to ESD to range from 8-33% of total cost as shown in Table 1.2. Others estimate the actual cost of ESD damage to the electronics industry as running into the billions of dollars annually. The cost of damaged devices themselves ranges from only a few cents for a simple diode to several hundred dollars for complex hybrids. When associated costs of repair and rework, shipping, labor, and overhead are included, the total amount of ESD related loss is significantly increased.

Figure 1.4 Fishbone Diagram for Electrostatic discharge failures on IC devices [13]

Figure 1.4 is the fishbone diagram (cause and effect diagram) for ESD failures in IC devices. It shows that ESD events can happen everywhere, in areas including the manufacturing process, transportation, and even field usage. ESD occurs at all level of integration and from various sources including human beings, machines, electromagnetics, and harsh environments. Hence, in order to prevent ESD damage effectively in the IC industry, proper handling and grounding of personnel and equipment and shielding of ESD sensitive products during all the processes need to be along with incorporation of proper ESD protection circuits.

### 1.3 ESD/EOS Protection Circuits

As the size of IC devices is shrinking and newer technologies are being developed, ESD damage becomes a more and more critical issue in the IC industry. To prevent ESD damage, proper grounding/handling precautions are essential. But usually control over handling/grounding is limited, so incorporating proper protection circuitry is also required. The concept of protection circuitry is to connect the additional circuitry (on-chip or off-chip) to the pins of the IC packages which will divert high currents away from the internal core circuitry and clamp high voltages during an ESD stress. Additionally an ESD protection circuit should not be damaged during an incoming pulse such as ESD and EOS.

A great deal of effort to design and optimize ESD protection circuits has been made for many years. However, it is not always easy to select the appropriate protection device for a circuit, because there are almost too many choices available. It is important to understand the nature of each protection device element and to evaluate its characteristics properly against the requirements of the circuit to be protected.

For a successful on-chip ESD protection circuit design, it is essential to choose a proper type of protection circuitry and elements. A good protection circuit should absorb and be capable to handle various types of ESD and EOS events without being damaged. For example, ESD is a high-voltage transient with fast rise time and fast decay time. Several thousand volts of ESD with a high rise time (dv/dt) could break through the junction layer of protective devices easily and cause

damage. However, ESD surge energy is very small and it does not require much energy-handling capability from a protective device. One the other hand, EOS is a much slower phenomenon than ESD but much larger energy is involved. The following factors need be considered for designing an ideal protection device for EOS and ESD [14];

- Voltage-clamping devices should limit the surge voltage to a safe level for the circuit or component being protected.

- Voltage-clamping devices should withstand several thousand volts in a fast dv/dt impulse.

- Protective devices should be small enough to fit into a limited space on a printed circuit board (PCB). Most components that require ESD protection are small surface-mount devices (SMD).

- Current-limiting devices are sometimes not effective for ESD protection

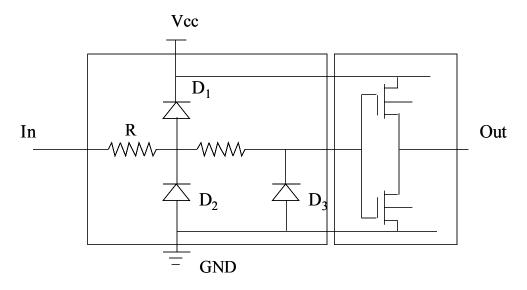

Figure 1.5 Typical CMOS input protection scheme

because ESD current is very small and does not induce much voltage across the device.

Limiting devices with high impedance are not effective for ESD protection. The stray capacitance in these devices could provide low reactance.

Relying upon on-chip protection to suppress ESD/EOS events may provide a false sense of security if not carefully evaluated. In the past, 2kV-4kV of on-chip ESD protection was thought to be adequate protection, but new standards such as IEC 61000-4-2 have raised the minimum protection level to as much as 15kV. As device geometries continue to shrink, it is becoming more difficult to add on-chip protection with a common manufacturing process. As a result, devices operating at low voltages may not be adequately protected.

Some integrated circuits feature built in protection by means of an internal SCR (silicon controlled rectifier) or resistor and diode network. The basic requirements of a protection network are that it provides a low impedance path for the discharge energy while limiting the current and voltage seen by the active circuit. This means that the transient energy is dissipated in the protection network itself. The basic input protection circuit usually consists of the following elements:

- A shunt device to discharge positive polarity transients

- A shunt device to discharge negative polarity transients

- A series element for current limiting

A typical CMOS input protection circuit is shown in Figure 1.5. When an ESD voltage is applied to the input structure, the on-chip diodes shunt the transient current to the power line  $(V_{cc})$  or ground. A positive transient voltage causes diode

$D_1$  to be forward biased when the input voltage exceeds Vcc. Likewise, for negative transients, diode  $D_2$  shunts the negative current. The polysilicon input resistors serve to limit the peak currents. Since polysilicon resistors are thermally insulated by a surrounding layer of  $SiO_2$  or glass, they are particularly susceptible to thermal damage resulting from joule heating by ESD induced currents. A typical CMOS input protection circuit can provide ESD immunity to approximately 4kV [15].

## 2. ESD CHARACTERIZATION IN IC DEVICES

In this chapter, a general overview of the characterization of ESD phenomena as preliminary information for this dissertation is presented. The ESD/EOS induced failure mode, basic device physics to explain ESD/EOS related failure mechanisms, and the overview of ESD test models are provided as well.

For mathematical models of ESD/EOS induced failures, modeling techniques have been proposed for failure mechanisms involved with semiconductor, oxide and metallization failures. Selected approaches are included in this chapter as well as the primary mechanisms associated with ESD and EOS.

In order to characterize the susceptibility of an IC to ESD damage, the IC must be tested using models which accurately simulate real ESD events. These models should be standardized so that testing is consistent and reliability can be defined quantitatively. Actual ESD stresses occur during wafer fabrication, packaging, testing, or any other time the circuit comes in contact with a person or machine. The majority of stresses occur between two pins of an IC package when the chip is not powered up, a fact reflected in the setup of ESD characterization tests [17]. Specific tests are designed to model specific events such as human handling, machine handling, and field induction.

The most common industrial tests used to measure ESD robustness are the human-body model (HBM), the machine model (MM), and the charged-device model (CDM) [18]-[20]. These most common models will be explained in detail in this chapter together with other models. Briefly, the human-body model consists of

charging a capacitor to a high voltage and then discharging the capacitor through a series resistor into the pins of a packaged IC with another pin grounded and all other pins floating. HBM testing is often the sole means of qualifying ESD reliability because the specifications of the test are standardized industry wide and because several commercial HBM testers are available.

Similarly to the HBM, in the machine model a capacitor is charged up to a high voltage and then discharged through the pins of an IC. Unlike the HBM, the MM discharges the capacitor through only a very small, parasitic series resistance, resulting in an oscillatory input pulse comparable to a pulse generated by a charged metal machine part contacting an IC pin.

The CDM test, which consists of charging a ground pin of a package using a voltage source, removing the voltage source, and then discharging the package by shorting a different pin, is meant to simulate the electrostatic charging of a package due to improper grounding and its subsequent discharging when a low-resistance path becomes available.

# **2.1 Basic Device Physics**

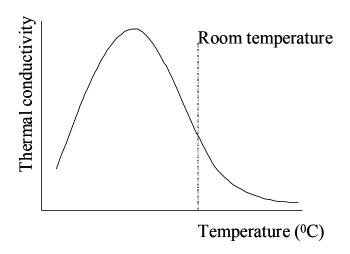

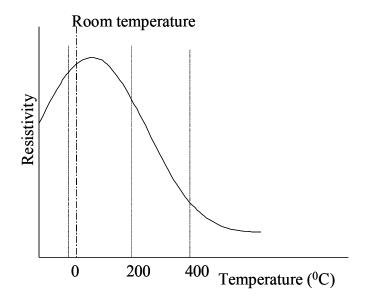

Before examining failure mechanisms caused by ESD, a brief overview of some device physics is useful to understand ESD failure phenomena. When silicon is heated, the carriers normally present in the device are supplemented by thermally generated carriers. This causes the resistivity of silicon to decrease sharply with an increase in temperature, as shown in Figure 2.1. This is known as Runyan's curve.

Additionally, Figure 2.2 shows that increasing the temperature of silicon causes its thermal conductivity to decrease.

Figure 2.1 Decrease in thermal conductivity of silicon with increasing temperature [25]

Figure 2.2 A rapid decrease in resistivity of doped silicon with increasing temperature [25]

Combining the effects shown in the two figures, some conclusions about the thermo-mechanical behavior of silicon may be reached. When energy is suddenly dumped into a silicon device in the form of an ESD impulse, the heating of the silicon is inherently uneven. A small area of the junction will absorb current and heat up, causing its resistivity to drop sharply. Once heating is taking place the small area becomes effectively thermally isolated from its surroundings because the thermal conductivity of the silicon decreases. This effect is a positive feedback mechanism resulting in damage to the device known variously as a punchthrough or a meltthrough.

#### 2.2 ESD/EOS Induced-Failure Mode and Mechanism

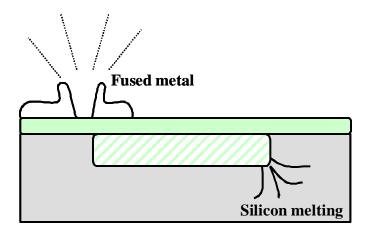

Electrical overstress (EOS) is defined as damage to a product caused by exceeding maximum ratings. EOS usually leads to catastrophic damages in integrated circuits resulting from high-energy events such as electrostatic discharge, electromagnetic pulses, lightning, or reversal of power and ground pins. EOS failure mechanisms fall into the two broad categories of thermally induced failures and high electric-field failures. The duration of an EOS event may be anywhere from less than one nanosecond to one millisecond and longer. Long EOS events can lead to damaged areas such as blown metal lines, cavities in the silicon, or discoloration of silicon due to local heating with a characteristic radius of 100um or greater. This damage leads to either a reduction in IC performance (e.g., increased leakage current on one or more pines) or total circuit failure [21].

The region of EOS/ESD phenomena with stress times of less than one nanosecond up to a few hundred nanoseconds is known as electrostatic discharge (although EOS covers a large range of phenomena including ESD, it is common to refer to the time range of 100ns and less as the ESD regime and the time range greater than 1us as the EOS regime, with a sort of transition region from ESD to EOS between 100ns and 1us.) ESD is a relatively rapid, high-current event resulting from the high voltage created when electrostatic charges are rapidly transferred between bodies at different potentials. ESD usually leads to relatively subtle, localized damage sites.

Two main failures can occur from ESD stress. The first one in CMOS technology is the danger of gate oxide dielectric breakdown due to the high voltage seen during ESD events. In a typical CMOS technology, the thin gates of an input buffer are tied directly to the input pin and thus are especially vulnerable to oxide breakdown. Dielectric breakdown is also of concern within the protection circuits since thin-gate MOS devices are commonly used. The other form of damage created by ESD stress is melting of material due to Joule heating which refers to the resistive heat generated by a current moving through an electric field.

If the high current of an ESD event is sufficiently localized in an area of high electric field, second breakdown will result [22], leading to either device failure, i.e., shorts and opens, or the more subtle damage of increased leakage. Secondary breakdown is a positive-feedback process and is a well-known phenomenon in power devices. Dielectric failure and thermal failure are generally considered to be catastrophic, i.e., the IC is no longer functional after the ESD

stress. However, as has been noted there is another type of ESD damage referred to as latent damage. Latent damage consists of increased leakage current or reduced oxide integrity, without loss of functionality. A latent ESD failure is defined as "malfunction that occurs in use conditions because of earlier exposure to ESD that did not result in an immediately detectable discrepancy" [23]. Latent damage is often bake-recoverable. Low-level leakage (an increase in leakage which remains below the failure threshold), also referred to as soft failure, may be due to injection of hot carriers into the gate oxide, which would cause a threshold voltage shift, or to damage in the silicon resulting from localized melting, or to both. A small damage site could act like a high-resistance filament across a diode junction, thereby increasing the leakage current to a significant but non-catastrophic level. Polgreen et al. [24] found this to be true for MOSFETs with pulse widths below a certain critical value. They postulated that a certain amount of total current is needed to cause widespread device damage. Extensive damage will not occur until the device is driven deeper into second breakdown by being stressed with a higher current.

During pulsed overstress, carriers are generated by avalanche multiplication. This thermally driven impact generation process occurs much faster than carrier generation during normal device operation. Thermal propagation is relatively slow compared to the avalanche breakdown mechanism, confining the heat generated to a small region of the device. Taken together, this results in current filamentation, shown in Figure 2.3. With repeated pulsing, a hot spot will develop because heat is being generated faster at the generation site than it can be dissipated.

Figure 2.3 Cross sectional drawing of ESD damage in bipolar structures [25]

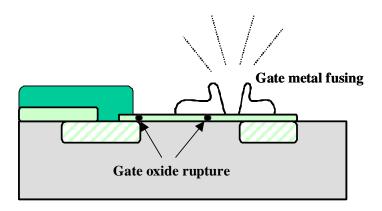

Figure 2.4 Cross sectional drawing of ESD damage in MOS structures [25]

In bipolar transistors, the base injection no longer controls the collector current, and the device is in thermal runaway. The mobility decreases with impurity concentration and decreases with increasing temperature. Depending on circuit conditions, the hot spot may also quickly develop temperatures at which the aluminum and silicon form an alloy, and the device is quickly shorted and destroyed.

Figure 2.3 and Figure 2.4 show simplified cross-sectional drawings of bipolar and MOS structures. Typical failure mechanisms are superimposed on these illustrations. Surface breakdown generally occurs when the rise time of the ESD pulse is short enough to break down the junction, usually just beneath the oxide, before thermal secondary breakdown can occur. Surface breakdown can also occur when the voltage is high enough to bridge a gap between two metal lines, on the device surface. This is gaseous arc breakdown.

#### 2.3 ESD Test Models

The electrostatic discharge problem has been elusive to investigators in more ways than just the subtle nature of the damage involved. Sometimes more puzzling are questions concerning the path of the transient and the original source of the energy or voltage involved. Initial realizations of the possibility of damage to susceptible parts from ESD were restricted to the human body as the source. Thus HBM model has been addressed longer than others.

Although present integrated circuit designs include ESD protection circuitry, the effectiveness of this protection must be determined in a manner which will ensure its effectiveness in the "real world" if the part is to meet the reliability requirements of the application. ESD has been studied for some time, and there is reasonable agreement on three models for this phenomenon: The human body model (HBM), machine model (MM), and charged device model (CDM).

# Human Body Model (HBM) [18]

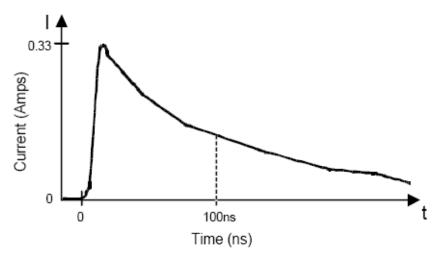

Figure 2.5 HBM ESD waveform at 500 V, short circuit [26]

Figure 2.6 HBM test circuit [26]

Under various conditions, the human body can be charged with electrical energy and transfer that charge to a semiconductor device through normal handling or assembly operations. To evaluate the effectiveness of the protection circuitry in

an integrated circuit, HBM ESD testing is performed. This HBM pulse is intended to simulate the human body type ESD conditions the part would experience during normal usage. The ESD testing is also used to determine the immunity or susceptibility level of a system or part to the HBM ESD event. Several different Human Body Model (HBM) ESD simulation circuits and pulse waveforms exist, including Military Standard MIL-STD 883C, International Electrotechnical Commission (IEC) 801-2, and JEDEC Standards.

When two objects come in contact with each other, the triboelectric action between them can generate an electrical energy charge that initiates an ESD event. The sudden release of generated charge in an object or person can produce extremely high voltages, currents, and electromagnetic fields that can result in malfunction, altering of device parameters, or even destruction of silicon junctions. In an ESD event, the human body can reportedly generate static charge levels as high as 15,000 volts by simply walking across a carpeted floor and 5,000 volts by walking across a linoleum floor. The potential difference between a charged human body and an object retaining an insignificant charge can range from a few hundred volts to as high as 30,000 volts. When a charged individual comes in contact with a device or system, a transfer of the stored energy occurs to the device or through the device to ground.

The typical ESD event has a fast, high current peak followed by a lower, more slowly decaying current pulse. The total energy in an ESD event can be tens of millijoules with time constants measured in picoseconds and several kilowatts of power. With this amount of energy available, it is quite evident how a single ESD

event can result in a device failure or possibly initiate a device weakness that can cause failure with continued use.

Recent research on human body ESD events shows that discharge pulses with fast rise times, on the order of 1 nanosecond or less, are the most disruptive to the normal operation of electronic equipment. Therefore, ESD test systems using a fast rise time pulse will more accurately simulate the human body discharge events frequently encountered. Measurement of these parameters has been difficult due primarily to the short time interval, large potential differences, and the measurement bandwidth required to capture both the amplitude and frequency characteristics of the ESD event. These limitations may cloud the issues of ESD susceptibility levels and environmental factors which may protect or damage electronic devices.

The simplest human body ESD model is the series RLC circuit shown in figure above in which the R corresponds to the body resistance, L is the corresponding body inductance, and C is the capacitance of the body with respect to its surroundings. The body inductance is often neglected, as in MIL-STD 883C, while a body capacitance of 100 to 250 pF and body resistance of 1000 to 2000 ohms is generally used.

#### Machine Model (MM) [19]

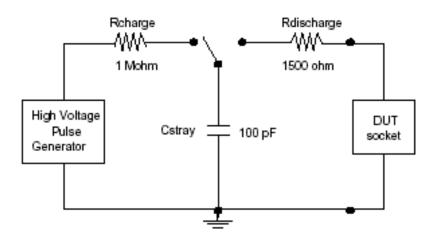

The Machine Model is designed to simulate a machine (test equipment, furniture, etc.) discharging accumulated static charge through a device to ground. It

comprises a series RC network of a 200-pF capacitor, a resistor of approximately 8.5 W, and an inductor of approximately 0.5 mH.

Figure 2.7 Machine model waveform at 500 V, short circuit [26]

Figure 2.8 MM ESD test circuit [28]

The equivalent circuit diagram and typical waveform of MM ESD event are shown in Figure 2.7 and Figure 2.8. This circuit is used to replicate machine ESD events in semiconductor devices. Usually, a commercial IC is requested to sustain at least 200 V MM ESD stress. A 200 V MM ESD event can generate an ESD current peak of up to 3.5A with a rise time up to 10ns. The ESD damage to an IC caused by MM ESD stress is similar to that caused by HBM ESD stress, but it occurs at a significantly lower voltage. Typically, the ratio between HBM ESD robustness and MM ESD robustness of the same IC product is about 8~12. But little research has been done to correlate both ESD test models.

The primary MM standards are known as JEDEC EIA/JESD22-A115-A and ESDA STM 5.2-1999. The JEDEC EIA/JESD22-A115-A was developed and released in 1994 for eliminating flaws in the EIAJ test method. The ESDA ESD STM 5.2 1999 was developed in early 90's. Recently, the ESDA MM device testing working group reviewed the results of additional round-robin testing using a reduced number of pulses per stress level (1 pulse instead of 5). The results obtained thus far reveal inconsistent failure thresholds. Further investigation into waveform parameters revealed large variations while meeting standard requirements.

# Charged Device Model (CDM) [20]

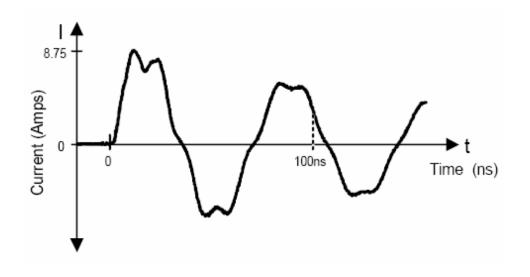

In 1974, Speakman [27] proposed the possibility of destroying an electronic part, such as an integrated circuit, by rapid discharge of accumulated static on a part's own body. This type of failure has since been called the charged device model (CDM) failure. The CDM ESD test is schematically drawn with the device in Figure 2.9 and a typical waveform is shown in Figure 2.10. In this CDM ESD event, the

ESD static charges are initially stored in the body of a floating IC. Most of the CDM charges are initially stored in the body of an IC device.

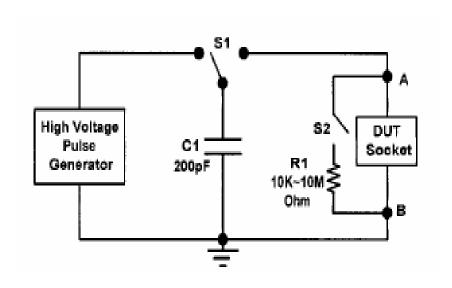

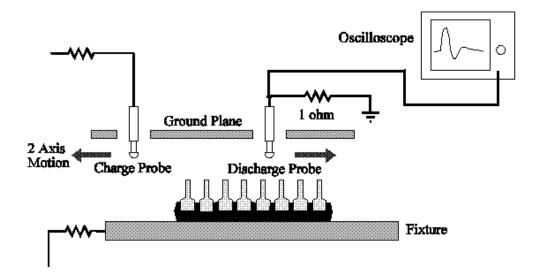

Figure 2.9 CDM ESD test setup

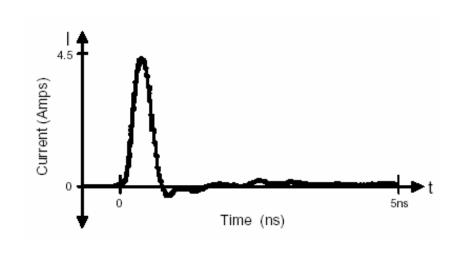

Figure 2.10 Typical current waveform from CDM

When some pin of this charged IC is touched by an external ground, the stored charged will be discharged from the inside of the IC to the outside ground. In the CDM ESD test setup (Figure 2.9), the IC is initially charged by the field-induced method without the socket, and then discharged through a grounded metal probe.

The IC is initially charged by the direct connection to the high voltage source through the IC socket, and then discharge through the switch and the socket of the tester to ground. Usually a commercial IC is requested to sustain at least 1 kV CDM ESD stress. The typical 1 kV CDM ESD event from a charged IC (with an equivalent 4pF capacitance to ground) can generate a current peak as high as 15A within a rise time of only around 200ps. With such a large ESD current and so fast a transition time, the I/O devices in CMOS IC's are totally destroyed by such ESD currents [28]. The primary CDM standards are ESDA STM 5.3.1-1999 and JESD22-C101A. The original CDM waveform and subsequent test system was designed by Bossard [29] in 1980. This architecture and waveform was the basis for the development of the JESD22-C101-A. Besides, the ESDA began development on its own method (ESD STM 5.3.1 & ESD STM 5.3.2).

# **Limitation of present ESD test methods**

A discrepancy appears to exist between reality, measured reality, and common practice as defined in some industry specifications. We feel a universally accepted specification defining the actual ESD waveform is not presently available due to various factors including:

- 1. The non-uniform conditions involved in the ESD environment.

- 2. The unpredictable circumstances of the ESD event.

- 3. The constant improvement in test equipment used to study the ESD event.

- 4. Supplier community resistance to adopting new standards that would indicate some currently used protection circuits are inadequate.

- 5. Lack of a standardized procedure for capturing the ESD event. Some procedures use measurement techniques that are not capable of capturing the high frequency content or fast rise time of the waveform.

Previous investigations into ESD testing have resulted in two conflicting philosophies. One philosophy states, "The test procedure must look like a human ESD spark...including all variability observed in natural ESD phenomena". The second testing philosophy is to choose a representative waveform from the range of likely ESD events and generate an instrumentation approach to ESD testing. This latter ESD testing philosophy employs test systems designed to produce a consistent and repeatable ESD waveform.

The difficulty with ESD test systems has been the inability to deliver the relatively fast risetime associated with the surface charge stored on the human body. Many test systems incorporate lumped time constant circuitry and are plagued by parasitic inductance, resistance, and capacitance of the various components. These parasitics can greatly affect the response of the ESD test system and therefore result in invalid ESD event rise times. The measured rise times are also limited by the capabilities of the measurement equipment used to capture the ESD event waveform. When the MIL-STD 883C testing procedure was released in 1989, the risetime stated as less than 10 ns may have been accurate for the type of equipment available for waveform verification. Measurement equipment presently available is

capable of detecting and capturing ESD waveforms with rise times as fast as a few hundred picoseconds [30].

#### Other models

The socketed CDM (SCDM) test method is basically similar to CDM. This model simulates a charged IC coming into contact with a low impedance conductive surface. The device under test is placed in a socket, charged from a high-voltage source, and then discharged. The SCDM test enhances the package parasitics by placing the device in a socket, mounted on a test fixture board, and connected via pogo pins to a relay switching matrix. Since the device itself is not in intimate contact with a ground plane, the stored energy is located on the tester components, associated with wiring, and to a much less degree, is located in the device socket [31].

The field induced charged device model (FCDM) is also known as indirect ESD. This type of ESD is not completely characterized, but it is generated by an electrostatic field, which is created by the discharge of an ESD pulse. It is similar to an EMI field which can induce a voltage and current on a data or power line. The transient that is induced on the line or PCB trace is conducted into the IC component. The level of ESD induced depends upon the length of the printed circuit board (PCB) traces. Induced ESD effects are more PCB dependent and need to be characterized by circuit/system design engineers [32].

## ESD sensitivity classification levels

A set of test procedures explained above is normally used to evaluate the ESD 'immunity' of a component, i.e., to evaluate the magnitude of an ESD discharge that a component can absorb without permanent damage.

Different IC device technologies and different applications have different levels of immunity to electrical stress such as ESD and EOS. So, there needs to be a convenient classification to differentiate ESD-sensitive devices from those which are not as vulnerable to ESD. Each of the ESD models used in ESD sensitivity testing has its own classification system for categorizing devices according to their ESD sensitivity. The ESD sensitivity of a device is usually specified in terms of the highest ESD test voltage that it passes and the lowest ESD test voltage that it fails per ESD model. Thus, ESD sensitivity is often expressed as a range of ESD voltage

Table 2.1 ESD immunity classification

| Class      | Voltage Range                           |

|------------|-----------------------------------------|

| 0          | < 250 volts                             |

| 1 <b>A</b> | 250 volts to < 500<br>volts             |

| 1B         | 500 volts to < 1,000 volts              |

| 1C         | 1000 volts to < 2,000 volts             |

| 2          | 2000 volts to < 4,000 volts             |

| 3A         | 4000 volts to < 8000 volts              |

| 3В         | > = 8000 volts                          |

| F 7 7      | D 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| Class | Voltage Range               |

|-------|-----------------------------|

| M1    | < 100 volts                 |

| M2    | 100 volts to < 200<br>volts |

| М3    | 200 volts to < 400 volts    |

| M4    | > or = 400 volts            |

| Class | Voltage Range                   |

|-------|---------------------------------|

| C1    | <125 volts                      |

| C2    | 125 volts to < 250<br>volts     |

| С3    | 250 volts to < 500<br>volts     |

| C4    | 500 volts to < 1,000 volts      |

| C5    | 1,000 volts to <<br>1,500 volts |

| C6    | 1,500 volts to < 2,000 volts    |

| C7    | =>2,000 volts                   |

[ Human Body Model ]

[ Machine Model ]

[ Charged Device Model ]

that a device can safely be subjected to for each of the ESD models. Table 2.1 presents the ESD sensitivity classification levels defined by the ESD Association for each ESD model. This type of device classification has several advantages. First, it can provide some information about the level of ESD protection that is required for the specific components and also it allows easy grouping and comparison of IC components based on their ESD sensitivity.

# 3. OBJECTIVES AND OUTLINE OF THIS THESIS

The objective of this study is to clarify ESD/EOS events experimentally and theoretically and their effects on non-silicon semiconductor devices (GaAs and SiGe devices) due to the high voltage and current. In order to study ESD/EOS phenomena, extensive experiments would have been conducted, and an analytical model for failure on IC devices will be developed. The specific experimental and modeling objectives of this dissertation are to research some key questions. The questions are listed below.

- 1. Can one differentiate ESD and EOS induced failures and develop a root cause analysis process to assess ESD/EOS induced field failures?

- 2. Are there differences in the failure signatures, based on the ESD models for non-silicon IC devices?

- 3. Can one reproduce field failures by EOS and several ESD test models?

- 4. What is the latent damage effect on GaAs MESFET devices?

- 5. Is there an acceptable model for failures caused by ESD conditions?

Chapter 1 and 2 presents a general overview of the characterization of the ESD and EOS phenomena as preliminary information for better understanding of this dissertation. The generation of ESD, the effect of ESD on electronics, type of ESD-induced failure mode and mechanisms are provided. A brief overview of ESD test models for replicating real ESD is presented as well.

Chapter 4 and chapter 5 addresses characterization and analysis for the failures caused by ESD/EOS and field returned devices. The detailed procedure for root cause analysis is documented with two case studies for SiGe and GaAs device. The failure site and signature resulting from different stress conditions are also documented and compared with those of field failures

In chapter 6, the effect of latent damage on GaAs devices is evaluated. Experimental procedures and electrical/physical characteristics after low-level ESD stress are presented. The difference of failure signatures resulting from different electrical stress levels through a detailed failure analysis is also documented. The effect of ESD stress below the threshold of hard failure to the susceptibility of the device to subsequent electrical overstress is also presented. The failure signatures from various types of ESD, EOS, and EOS-ESD combined stress are presented as well and a possible screening method is proposed.

An application and development of an ESD failure model using a thermal RC network to predict the power-to-failure level is presented in chapter 7, starting with a general discussion of the development procedure of the analytical model. A review of some previous prediction work and their comparison is also given. The effect of device parameters and power-to-failure comparison are also evaluated using a numerical model. Based on the analytical prediction model developed, the

correlation of HBM ESD stress and square wave pulse is presented and the issue of HBM equivalent square wave pulse duration is discussed.

# 4. FAILURE ANALYSIS AND ESD EVALUATION OF SiGe OPAMPS

In this chapter, Silicon-Germanium (SiGe) BiCMOS RF OpAmp devices have been investigated for electrostatic discharge (ESD) evaluation. ESD evaluation is particularly important in high-frequency RF wireless applications because the ESD immunity level in RF devices is comparatively lower than other devices. Also, application of ESD protection circuits or components for RF devices is not simple due to their unique characteristics.

During this evaluation, the human body model, machine model, and charged device model electrostatic discharge test models were applied to create ESD-induced failures. Failure mode and effect analysis, visual inspection, electrical tests, X-ray observation, liquid crystal application, focused ion beam examination, optical microscopy, and scanning electron microscopy inspection were performed on ESD-failed SiGe BiCMOS OpAmp RF devices. This study shows that the failure locations and damage shapes varied, depending upon how the failures are created. Results of failure analysis under different stress conditions are compared.

## 4.1 SiGe devices and ESD

Silicon-Germanium (SiGe) BiCMOS is a silicon technology that combines a high-performance heterojunction bipolar transistor (HBT) with advanced CMOS technology. Applications of SiGe technology are most important in microwave

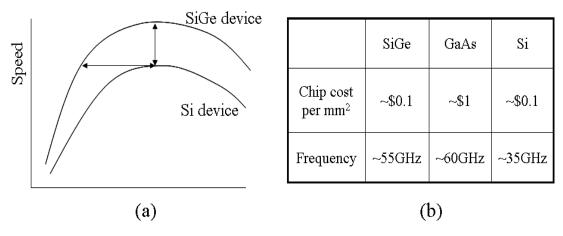

components, RF components, high-speed data converters, and mixed signal devices. With SiGe technology, it will soon become practical to replace more expensive Gallium-Arsenide (GaAs) RF circuits with SiGe circuits having comparable performance at the significantly lower cost that is normally associated with silicon manufacturing.

Silicon device technology is very highly developed, but still silicon does not offer the best mobility or saturation velocity, which are directly related to the device speed. In terms of material properties, Ge is one of the most promising materials for bipolar and CMOS devices because is offers high mobility for both electrons and holes (Table 4.1). But unfortunately, Ge devices will not operate over a wide temperature range and Ge also lacks a high-quality oxide which provides low manufacturability [34]. So in spite of its lower electron and hole mobility, Si has been more attractive. For high gain, high frequency application, GaAs or InAs devices are widely used as alternatives. These non-silicon devices offer the combination of high electron mobility- greater than Si devices.

In SiGe technology, to enhance the device performance, Ge is selectively

Table 4.1 Properties of semiconductor materials [34]-[36]

| Semiconductor<br>materials | Band gap (eV) | $\begin{array}{c} \text{Mobility} \\ \mu_n[\text{cm}^2/\text{Vsec}] \end{array}$ | Mobility<br>μ <sub>p</sub> [cm²/Vsec] |

|----------------------------|---------------|----------------------------------------------------------------------------------|---------------------------------------|

| Ge                         | 0.66          | 3900                                                                             | 1900                                  |

| Si                         | 1.12          | 1360                                                                             | 465                                   |

| GaAs                       | 1.42          | 8500                                                                             | 400                                   |

| InAs                       | 0.35          | 20000                                                                            | 100                                   |

| SiGe                       | 0.66~1.12     | 1360~3900                                                                        | 465~1900                              |

Figure 4.1 Advantages of SiGe devices

introduced into the base region of the transistor. The smaller base bandgap of SiGe compared to Si enhances electron injection, producing a higher current gain for the same base doping level compared to a Si device. As shown in Figure 4.1 (a), compared to a Si device, a SiGe device has better characteristics of high speed and low power consumption which means it is more suitable for high speed RF applications. For example, A SiGe transistor has up to 1.5 times higher peak frequency and up to 7 times lower power consumption for the same frequency as compared to a silicon based transistor [35]. One more advantage of a SiGe device is its cost. As shown Figure 4.1(b), the cost of a chip in SiGe is comparable to that of Si devices and performance of SiGe devices is comparable to GaAs devices which is essential in applications where a particular circuit function cannot be accomplished with silicon devices [36]. So SiGe devices are aimed at replacing silicon devices in RF and microwave components. A heterojunction bipolar transistor with SiGe technology was first demonstrated in 1988. The Si/SiGe system was developed using molecular beam epitaxy [37]-[39]. Molecular beam epitaxy

(MBE) is a controlled thermal evaporation process under ultrahigh vacuum conditions where a substrate is held in high vacuum while molecular or atomic beams of the constituents impinge on its surface.

Products utilizing SiGe technology undergo essentially the same product reliability stressing as products using bulk Si. Typical reliability test activities include high temperature operating life (HTOL) at 125 °C for 1000 hours, with DC and functional tests performed at 0 and 1000 hours. ESD testing is also included for both the human body model and charged device model; latch-up characterization is also completed [40].

With the increased volume and growth in the applications that use SiGe BiCMOS devices, the ESD sensitivity characterization of SiGe BiCMOS devices has become more important [41]. ESD evaluation is particularly important in high-frequency RF wireless applications. This is because damage from ESD/EOS is usually caused by localized overheating, which implies ESD robustness of devices is a strong function of the material melting temperature and thermal conductivity. Due to the low thermal conductivity and low melting temperature of SiGe, SiGe devices are more sensitive to ESD than Si devices. Furthermore, application of ESD protection circuit or components for RF devices is not simple due to its own unique characteristics. In this study, HBM, MM, and CDM testing for an epitaxial base SiGe device were carried out on all possible pin connections in order to duplicate ESD failures.

# 4.2 Wideband Fixed-Gain Amplifiers

The test devices used in this study are a set of wideband, fixed gain amplifiers that offer high bandwidth, high slew rate, low noise, and low distortion. This combination of specifications enables analog designers to overcome current performance limitations and process analog signals at much higher speeds than previously possible with closed loop, complementary amplifier designs. The devices are offered in a 16-pin leadless package as shown in Figure 4.2, and incorporate a power-down mode for quiescent power saving.

This device is fixed gain OpAmps manufactured by BiCMOS-III process, a SiGe based manufacturing process integrating bipolar, CMOS and passive components. The BiCMOS process integrates both npn and pnp type bipolar

Figure 4.2 Pin assignments and top view)

Table 4.2 Features, applications, and device data

| THS4302 Features                     | Applications for THS4302                         | Device Data                                                                                     |

|--------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Fixed Gain Closed Loop<br>Amplifiers | Wideband signal processing Wireless transceivers | Die Name: RTHS4302IM<br>Die Size: 53x53<br>Wafer Fab: TID                                       |

| Gain: +5 V/V (14dB)                  | IF amplifier ADC preamplifier                    | Assembly site: CAR Pins/Package: 16/RGT                                                         |

| Wide Bandwidth: 2.4GHz               | DAC Output buffers<br>Test, Measurement, and     | Mold compound: SUM EME-7730LF                                                                   |

| High Slew Rate: 5500V/μs             | instrumentation Medical and Industrial imaging   | Technology: BiCOM-III  1 <sup>st</sup> metal: TiN/AlCu0.5%  2 <sup>nd</sup> metal: TiN/AlCu0.5% |

| High Output Drive: ±180 mA           |                                                  | 3 <sup>rd</sup> metal: TiN/AlCu0.5%<br>L/F material: Copper<br>L/F finish: Solder Plate         |

| Power Supply Voltage: +3 V or +5 V   |                                                  | Die Mount: ABL 2600BT<br>Bond Wire: 1.0mil Au, TS                                               |

Table 4.3 Absolute maximum ratings

| Supply Voltage, V <sub>S</sub>                               | 6V             |

|--------------------------------------------------------------|----------------|

| Input voltage, V <sub>I</sub>                                | $\pm V_{ m S}$ |

| Output current, I <sub>O</sub>                               | 200MA          |

| Maximum junction temperature, T <sub>J</sub>                 | 150°C          |

| Operating free-air temperature range, T <sub>A</sub>         | -40°C to 85°C  |

| Storage temperature range, T <sub>stg</sub>                  | -65°C to 150°C |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds | 300°C          |

Table 4.4 Recommended operating conditions

|                                          |                    | Min                | Max  | Unit |  |

|------------------------------------------|--------------------|--------------------|------|------|--|

| Complementary (V. and V.)                | Dual Supply        | ±1.5               | ±2.5 | V    |  |

| Supply voltage ( $V_{S+}$ and $V_{S-}$ ) | Single Supply      | 3                  | 5    |      |  |

| Input common-mode vo                     | V <sub>S-</sub> +1 | V <sub>S+</sub> -1 |      |      |  |

transistors, achieving a three times speed increase and upto 50% noise reduction for OpAmps and other high-performance mixed signal products. This process allows analog components to operate at 100MHz with a distortion level of 100dB [42]. These parts are COTS (commercial-off-the-shelf) parts. Table 4.2 gives a summary of various features of OpAmps, applications and device data, and Table 4.3 and Table 4.4show absolute maximum ratings and recommended operating conditions for this device.

#### 4.3 ESD test and electrical characterization

The nine test devices were subjected to ESD exposure for the purpose of evaluation. Test models used for ESD testing were HBM, MM, and CDM. The ESD test involved "step stress test," whereby the zapping voltage level is increased by 500 V in HBM and CDM and by 50 V in MM until the components exhibit electrical malfunctions such as open, short, or parametric shift. In each voltage step, electrical characteristics are verified and compared with those of the good devices (test standards from MIL and JEDEC specify 1,000 V in HBM and CDM and 100 V in MM [18]-[20]).

The devices (sample numbers 11 to 19 were used for ESD testing) were split into three groups for the three models: three devices for HBM, three devices for MM, and three devices for CDM. All possible pin connections were used for test pin connections. The number of discharges was five in each voltage step. The discharge off interval was 1 second in HBM and MM and 0.5 second in CDM. The discharge

activity ended when the electrical malfunction appeared. All failure was noticed when discharging stress was applied between VS+ and VS-. Table 4.5 shows ESD test details.

Table 4.5 ESD failure threshold test results

| Test Condition |                              | Sample<br>Number | ESD Failure Threshold<br>Voltage (V) |

|----------------|------------------------------|------------------|--------------------------------------|

|                |                              | 18               | 4000                                 |

| HBM            | EIAJ/JESD22-<br>A114B, 100pF | 13               | 4500                                 |

|                | ттт ів, тоорт                | 12               | 4000                                 |

|                | EIAJ/JESD22-<br>A115A, 200pF | 15               | 300                                  |

| MM             |                              | 16               | 300                                  |

|                | , <sub>F</sub> -             | 17               | 250                                  |

|                |                              | 14               | 2000                                 |

| CDM            | EIAJ/JESD22-<br>C101-A       | 19               | 1500                                 |

|                |                              | 11               | 1500                                 |

An HP 4156A Semiconductor Parameter Analyzer and an Agilent Low-Leakage Switch Mainframe were used to obtain DC characteristics of these devices. Measurements were performed on 20 SiGe based OpAmps before and after the ESD stress, and the results of these electrical parameter measurements are shown in Table 4.6. Electrical parameters measured while obtaining DC characteristics of THS4302 were:

- Input offset current  $(I_{OSP})$

- Input offset voltage  $(V_{OS})$

- Open loop voltage gain (A<sub>OL</sub>)

- Supply current  $(I_{PS})$