### ABSTRACT

Title of Document: END-OF-LIFE AND CONSTANT RATE RE-

LIABILITY MODELING FOR SEMICON-

DUCTOR PACKAGES USING KNOWLEDGE-

**BASED TEST APPROACHES**

LIYU YANG, Doctor of Philosophy, 2009

Directed By: Professor Joseph B. Bernstein, Reliability Engi-

neering, Department of Mechanical Engineering,

University of Maryland at College Park.

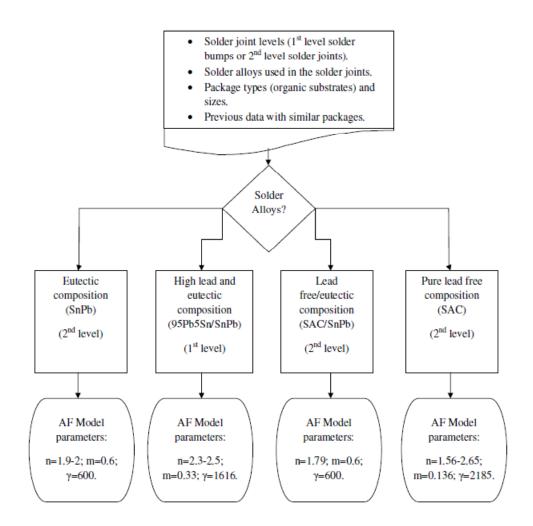

End-of-life and constant rate reliability modeling for semiconductor packages are the focuses of this dissertation. Knowledge-based testing approaches are applied and the test-to-failure approach is approved to be a reliable approach. First of all, the end-of-life AF models for solder joint reliability are studied. The research results show using one universal AF model for all packages is flawed approach. An assessment matrix is generated to guide the application of AF models. The AF models chosen should be either assessed based on available data or validated through accelerated stress tests. A common model can be applied if the packages have similar structures and materials. The studies show that different AF models will be required for SnPb solder joints and SAC lead-free solder joints. Second, solder bumps under power

cycling conditions are found to follow constant rate reliability models due to variations of the operating conditions. Case studies demonstrate that a constant rate reliability model is appropriate to describe non solder joint related semiconductor package failures as well. Third, the dissertation describes the rate models using Chi-square approach cannot correlate well with the expected failure mechanisms in field applications. The estimation of the upper bound using a Chi-square value from zero failure is flawed. The dissertation emphasizes that the failure data is required for the failure rate estimation. A simple but tighter approach is proposed and provides much tighter bounds in comparison of other approaches available. Last, the reliability of solder bumps in flip chip packages under power cycling conditions is studied. The bump materials and underfill materials will significantly influence the reliability of the solder bumps. A set of comparable bump materials and the underfill materials will dramatically improve the end-of-life solder bumps under power cycling loads, and bump materials are one of the most significant factors. Comparing to the field failure data obtained, the end-of-life model does not predict the failures in the field, which is more close to an approximately constant failure rate. In addition, the studies find an improper underfill material could change the failure location from solder bump cracking to ILD cracking or BGA solder joint failures.

## END-OF-LIFE AND CONSTANT RATE RELIABILITY MODELING FOR SEMI-CONDUCTOR PACKAGES USING KNOWLEDGE-BASED TEST APPROACHES

By

#### LIYU YANG

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2009

Advisory Committee:

Associate Professor Joseph B. Bernstein, Chair/Advisor

Associate Professor Hugh Bruck

Associate Professor Patrick F. McCluskey

Professor Peter Sandborn

Professor Peter Kofinas, Deans Representative

© Copyright by LIYU YANG 2009

# Dedication

To my parents, my wife, my brother, and my kids.

### Acknowledgements

I would like to express my sincere gratitude to my advisor Professor Joseph B. Bernstein for his valuable guidance and supports throughout my graduate studies. He has left a strong impression on my mind. He has been an excellent mentor which will forever inspire me towards good quality work. In particular his sense of honesty and genuine excitement in research is a source of inspiration. His easy personality, open mind and dedication to quality work will also inspire me. I am grateful to him for taking time from his busy schedule to explain concepts that beyond my knowledge. Last but not least I will also like to thank him for extricating me out of troubled times during my research.

I am also grateful to Professor Hugh Buck, Professor Patrick McCluskey, and Professor Peter Sandborn, for serving on my committee to evaluate my work and give valuable suggestion. I will like to thank Professor Peter Kofinas for serving on my committee as the Dean's representative and evaluating my work as well.

Thanks are also due to Professor Carol Smidts who has patiently answered questions regarding the topic of my research.

I will like to thank Professor Xuejun Fan (Lamar University, TX) who has been a friend of mine and often advise me during my research.

Needless to say that graduate study will not be completed without several good friends and colleagues in the companies I have worked for. Most of all, I specially thank my family for supporting me.

I will like to acknowledge the hardware and software, administrative and financial support by the companies during my graduate studies, including Intel Corp. and Freescale Inc.

Last, I want to thank professors and staff of Department of Mechanical Engineering who provide technical support and administrative helps.

## Table of Contents

| ABSTRACT                                                             | . ii |

|----------------------------------------------------------------------|------|

| Dedication                                                           | . ii |

| Acknowledgements                                                     | iii  |

| Table of Contents                                                    | . v  |

| List of Tables                                                       | хii  |

| List of Figuresx                                                     | vii  |

| List of Illustrations x                                              | ΧV   |

| 1. INTRODUCTION                                                      | . 1  |

| 1.1 Semiconductor packages and systems                               | . 1  |

| 1.1.2 Lead frames and substrates                                     | . 6  |

| 1.1.3 Low-k / Cu silicon technology                                  | . 6  |

| 1.1.4 Power dissipation and thermal profiles                         | . 7  |

| 1.1.5 Package reliability prediction and the failure rate estimation | . 7  |

| 1.2 Reliability considerations in semiconductor packages             | . 8  |

| 1.2.1 Reliability concepts                                           | . 8  |

| 1.2.2 Package failure categories                                     | . 8  |

| 1.2.3 Reliability assessment, prediction and failure rate modeling   | 11   |

| 1.3 Accelerated stress tests and acceleration factors (AF)           | 12   |

| 1.4 Failure rate modeling                                            | 17   |

|    | 1.5     | Objectives, motivation and scope                                  | 18 |

|----|---------|-------------------------------------------------------------------|----|

| 2. | REV     | VIEW OF FAILURE MECHANISMS IN SEMICONDUCTOR                       |    |

| P  | ACKA    | GES                                                               | 20 |

|    | 2.1     | Introduction                                                      | 20 |

|    | 2.2 Ke  | y failure mechanisms of semiconductor packages                    | 24 |

|    | 2.2.    | Wire bonding failures                                             | 24 |

|    | 2.2.2   | 2 Die cracking failures (e.g. passivation cracking, ILD cracking) | 28 |

|    | 2.2.    | 3 Package cracking failures                                       | 32 |

|    | 2.2.4   | 4 Interface delamination failures                                 | 35 |

|    | 2.2.    | 5 Solder interconnect failures                                    | 40 |

|    | 2.2.0   | 6 Electromigration failures                                       | 46 |

|    | 2.2.    | 7 Corrosion failures                                              | 50 |

|    | 2.3 Su  | mmary                                                             | 51 |

| 3. | FAI     | LURE/LIFE MODELS USED IN SEMICONDUCTOR PACKAGES                   | 52 |

|    | 3.1 Int | roduction                                                         | 53 |

|    | 3.1.    | I Inverse power law (IPL) model                                   | 53 |

|    | 3.1.2   | 2 Arrhenius models                                                | 54 |

|    | 3.2 De  | scription of reliability models                                   | 56 |

|    | 3.2.    | I Arrhenius-Weibull models                                        | 56 |

| 3.2.2 IPL-Weibull model                                                 | 57 |

|-------------------------------------------------------------------------|----|

| 3.2.3 Arrhenius-Exponential models                                      | 57 |

| 3.2.4 IPL-Exponential models                                            | 58 |

| 3.3 Acceleration factor (AF) models                                     | 59 |

| 3.4 Acceleration factors for multiple failure mechanisms                | 61 |

| 3.5 Package failure models                                              | 62 |

| 3.5.1 IMC diffusion model                                               | 62 |

| 3.5.2 Thermal-mechanical fatigue models                                 | 64 |

| 3.5.3 Fracture failure models                                           | 67 |

| 3.5.4 Electromigration models                                           | 69 |

| 3.5.5 Corrosion/temperature & humidity models                           | 69 |

| 3.6 Summary                                                             | 72 |

| 4. END-OF-LIFE AF MODELS FOR RELIABILITY PREDICTION OF                  |    |

| SOLDER JOINTS                                                           | 74 |

| 4.1 Introduction                                                        | 75 |

| 4.2 The acceleration factor models for solder interconnects reliability | 81 |

| 4.3 Assessment of AF models                                             | 85 |

| 4.3.1 Test vehicles and experiment descriptions                         | 85 |

| 4.3.2 Results and discussions                                           | 89 |

|    | 4.3.4 Discussions and conclusions                                          | . 109 |

|----|----------------------------------------------------------------------------|-------|

|    | 4.4 Summary                                                                | . 110 |

| 5. | FAILURE BOUND ESTIMATION AND FAILURE RATE MODELING                         | . 112 |

|    | 5. 1 Introduction                                                          | . 113 |

|    | 5.1.1 Failure trends                                                       | . 113 |

|    | 5.1.2 Failure rate modeling                                                | . 114 |

|    | 5.2 Theory                                                                 | . 116 |

|    | 5.2.1. Poisson distribution and the confidence bounds of its mean          | . 116 |

|    | 5.2.2 A proposal for confidence bounds for the number of failures observed | . 119 |

|    | 5.3 Acceleration factor and failure rate modeling                          | . 120 |

|    | 5. 3.1 The acceleration factor estimation                                  | . 120 |

|    | 5.3.2 AF modeling for multiple failure mechanisms                          | . 121 |

|    | 5.4 Case studies                                                           | . 123 |

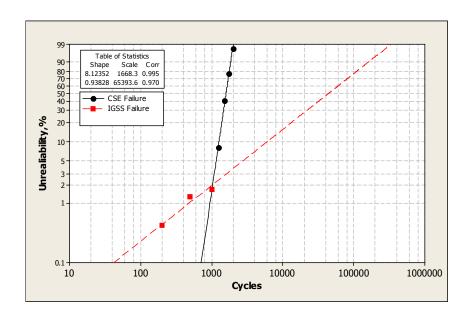

|    | 5.4.1 Reliability and failure rate estimation of RCPs                      | . 124 |

|    | 5.4.2 Reliability and failure rate analysis of FCMMAP modules              | . 130 |

|    | 5.4.3 Reliability testing on Power Quad Flat Non-lead (PQFN) packages      | . 135 |

|    | 5.4.4 Field failures of products (PLCC packages)                           | . 140 |

|    | 5.5 Discussions and summary                                                | 144   |

| 6. RELIABILITY ASSESSMENTS USING A KNOWLEDGE-BASED TI       | EST |

|-------------------------------------------------------------|-----|

| APPROACHES                                                  | 146 |

| 6.1 Introduction                                            | 146 |

| 6.2 Reliability assessment and prediction of TEBGA packages | 147 |

| 6.2.1 Introduction                                          | 147 |

| 6.2.2 Key failure mechanisms                                | 156 |

| 6.2.3 Materials and methods                                 | 158 |

| 6.2.4. Experimental results and discussions                 | 175 |

| 6.2.5 Discussions                                           | 191 |

| 6.3 Reliability assessment of RCPs                          | 192 |

| 6.3.1 Introduction                                          | 192 |

| 6.3.2 Key failure mechanisms                                | 194 |

| 6.3.3 Materials and methods                                 | 198 |

| 6.3.4 Experimental results discussions                      | 200 |

| 6.3.5 Discussions                                           | 210 |

| 6. 4 Summary                                                | 210 |

| 7. END-OF-LIFE RELIABILITY STUDIES OF FLIP CHIP BUMPS UNI   | DER |

| POWER CYCLING CONDITIONS                                    | 212 |

| 7.1 Introduction                                            | 212 |

| 7.2 Review of solder bump reliability                      | 215                         |

|------------------------------------------------------------|-----------------------------|

| 7.3 Test vehicles and experimental descriptions            | 217                         |

| 7.3.1 Packages under testing                               | 217                         |

| 7.3.2 Test set-up & descriptions                           | 218                         |

| 7.4 Data analysis and discussions                          | 222                         |

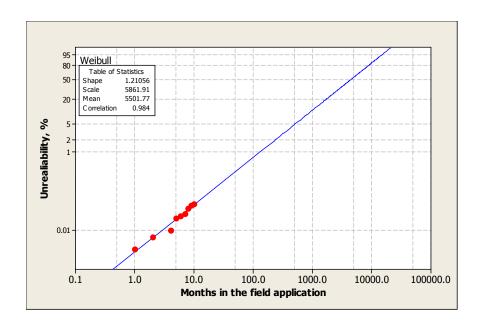

| 7.4.1 Field failure data assessment                        | 222                         |

| 7.4.2 Power cycling test results discussions               | 226                         |

| 7.4.3 Failure rate estimation                              | 243                         |

| 7.5 Summary and discussions                                | 247                         |

| 8. CONTRIBUTIONS AND FUTURE WORK                           | 250                         |

| 8.1 Contributions of the dissertation                      | 250                         |

| 8.1.1 End-of-life AF models for the prediction of sold     | er joint reliability 250    |

| 8.1.2 Constant failure rate modeling for semiconductor     | packages using              |

| knowledge-based test-tofailure approach                    | 252                         |

| 8.1.3 Reliability assessment for TEBGA and RCPs using      | ng knowledge-based test     |

| approaches                                                 | 253                         |

| 8.1.4 End-of-life and Constant failure rate estimation for | or solder bumps reliability |

| under power cycling conditions                             | 254                         |

| 8.2 Suggestions for future work                            | 255                         |

|      | 8.2.1 The correlation of constant failure rate estimation and the trends of field | 1   |

|------|-----------------------------------------------------------------------------------|-----|

|      | failures                                                                          | 255 |

|      | 8.2.2 End-of-life acceleration factor model development and verification          | 255 |

| App  | endices                                                                           | 256 |

| Bibl | liography                                                                         | 257 |

## List of Tables

| Table 1-1 Research data based on field-return failures from Company A between        |

|--------------------------------------------------------------------------------------|

| 2006 to 2007 (Yang et al., 2007)                                                     |

| Table 1-2 Package assembly related field-return failures [Yang et al., 2007] 11      |

| Table 1-3 Standard stress tests used in semiconductor package studies                |

| Table 1-4 Stress tests and associated failure mechanisms and models                  |

| Table 2-1 Categories of failure mechanisms observed in semiconductor packages 21     |

| Table 2-2 Failure mechanisms possible seen in BGA packages                           |

| Table 2-3 Critical properties for underfill materials                                |

| Table 3-1 Exponent parameters b used in IPL models                                   |

| Table 3-2 Activation energy (Ea) values [Blish et al., 1991, 1997, 2000] 55          |

| Table 3-3 Acceleration factor under various stress factors [JESD91A,                 |

| 2003][JEP122C, 2006]61                                                               |

| Table 4-1 the value of r [Norris and Landzberg, 1969]                                |

| Table 4-2 Test vehicles used in solder joint reliability study                       |

| Table 4-3 Thermal cycling conditions and cycle frequencies                           |

| Table 4-4 Cycles to failure of fcCSPs solder joints with various surface finishes 90 |

| Table 4-5 Cycles to failures at different cumulated failure percentages              |

| Table 4-6 Cycles of failures using SnPb and SAC405 pastes                           | 93  |

|-------------------------------------------------------------------------------------|-----|

| Table 4-7 Cycles to failure data observed for 225 BGA packages                      | 95  |

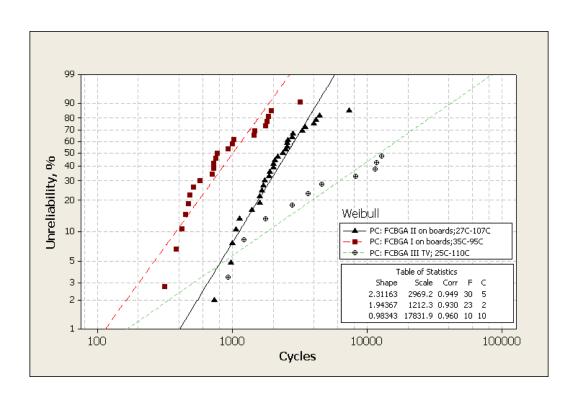

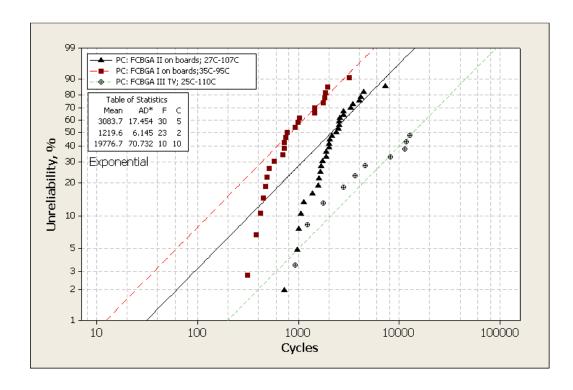

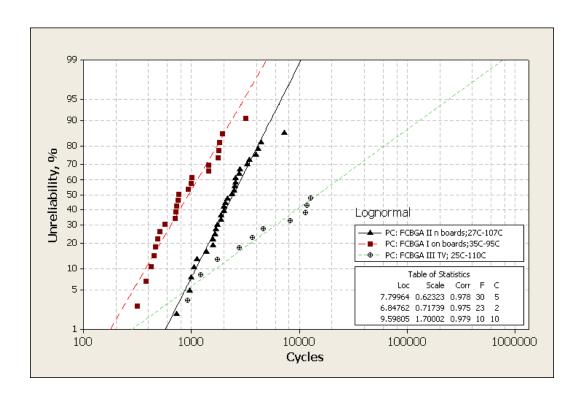

| Table 4-8 Weibull analysis for 360-ball FCBGAs                                      | 97  |

| Table 4-9 Weibull analysis data summary for 20 mm x 20 mm 431-ball CBGAs            | 97  |

| Table 4-10 Test conditions and test vehicles for the evaluation of cycle frequency. | 99  |

| Table 4-11 Estimation of <i>m</i> value                                             | 100 |

| Table 4-12 Cycles to failure and AF estimation                                      | 103 |

| Table 4-13 Cycles to failures and AF estimations                                    | 104 |

| Table 4-14 Cycles to failures and AF estimation                                     | 105 |

| Table 4-15 Thermal cycling conditions and characterization life $(\eta)$            | 106 |

| Table 4-16 The comparison of estimated AF value from various models                 | 107 |

| Table 5-1 Reliability testing results of RCPs                                       | 126 |

| Table 5-2 Failure rate estimation                                                   | 129 |

| Table 5-3 Confidence bounds estimation using various approaches                     | 130 |

| Table 5-4 Failure data for FCMMAP modules                                           | 132 |

| Table 5-5 Failure rate estimation                                                   | 134 |

| Table 5-6 Failure bound estimation for FCMMAPs                                      | 134 |

| Table 5-7 PQFN product qualification summary                                        | 135 |

| Table 5-8 Failure data for PQFN package (current sense failure)                     |

|-------------------------------------------------------------------------------------|

| Table 5-9 Weibull plot data summaries for the PQFNs                                 |

| Table 5-10 n value using various CFP percentage                                     |

| Table 5-11 Isothermal cycling results of PQFN parts                                 |

| Table 5-12 Field failure summaries for PLCC packages                                |

| Table 6-1 Comparison of various types of TEBGA packages                             |

| Table 6-2 Die/thin film cracking failures observed in pre-qual tests                |

| Table 6-3 Possible failure mechanisms expected from the TEBGA package reliability   |

| tests [Yang & Bernstein, 2008]                                                      |

| Table 6-4 Package and device attributes                                             |

| Table 6-5 A hypothesis summary for the die cracking and thin film cracking failures |

|                                                                                     |

| Table 6-6 Factors and parameters of the dual step wafer sawing processes            |

| Table 6-7 Package dimensions for the simulation study                               |

| Table 6-8 Test results of package qualification                                     |

| Table 6-9 Summaries of the dual step wafer sawing studies                           |

| Table 6-10 Low stress die attach and encapsulation material properties              |

| Table 6-11 Test packages, boards and conditions used in SJR study                   |

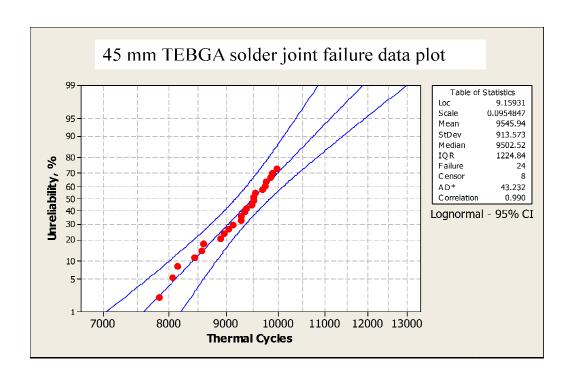

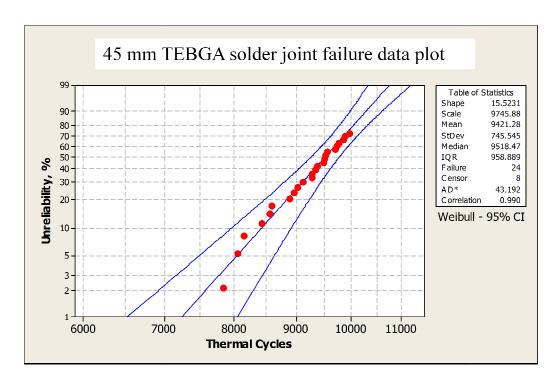

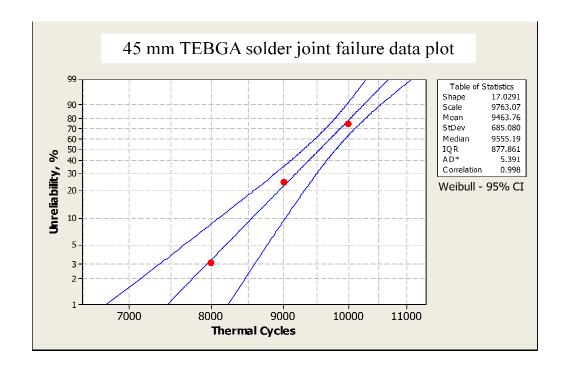

| Table 6-12 Solder joint failure data for TEBGA packages (45 mm x 45 mm) 188         |

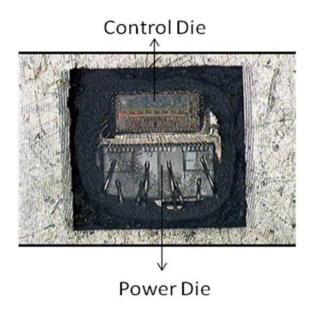

| Table 6-13 Failure rate estimation from TEBGA test results                              |

|-----------------------------------------------------------------------------------------|

| Table 6-14 Package attributes of RCPs                                                   |

| Table 6-15 Assembly information for the board level reliability study                   |

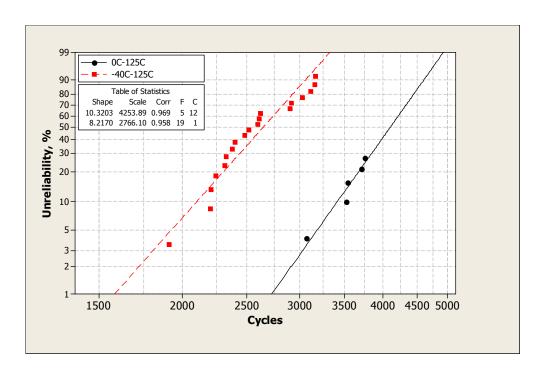

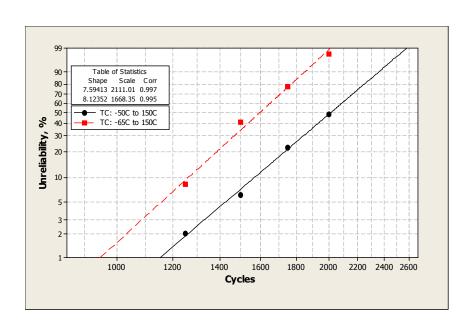

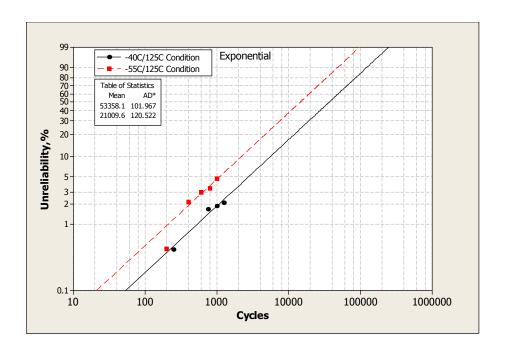

| Table 6-16 Failure data for 9 mm x 9 mm packages under -40 °C/125 °C condition201       |

| Table 6-17 Failure data for 9 mm x 9 mm package under -55 °C/125 °C condition 201       |

| Table 6-18 Failure data for 9 mm $\times$ 9 mm packages under thermal cycling tests 203 |

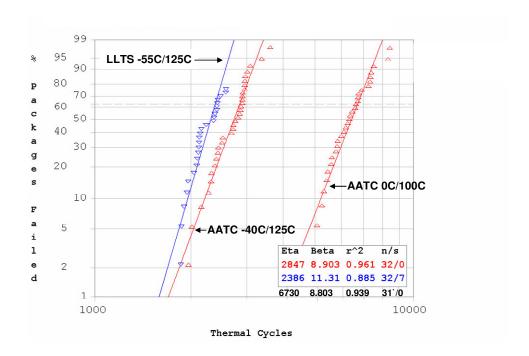

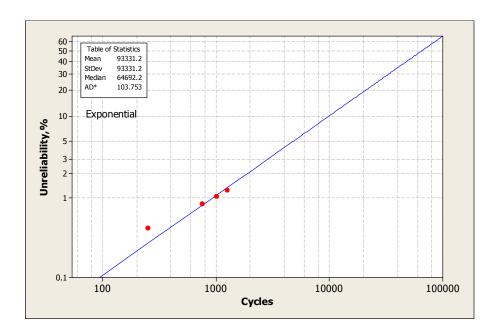

| Table 6-19 Failure data for FCMMAP packages under AATC condition 204                    |

| Table 6-20 Failure data observed from BLR study                                         |

| Table 6-21 17 mm x 17 mm WLCSPs with 7 mm x 9 mm die size                               |

| Table 6-22 SJR failures data on two pad surface finishes                                |

| Table 7-1 FCBGA package attributes                                                      |

| Table 7-2 Power cycling conditions                                                      |

| Table 7-3 Field failure summaries of Company B                                          |

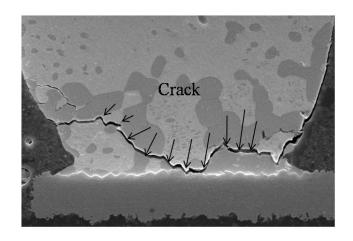

| Table 7-4 Weibull analysis summary for lots listed in Table 7-3                         |

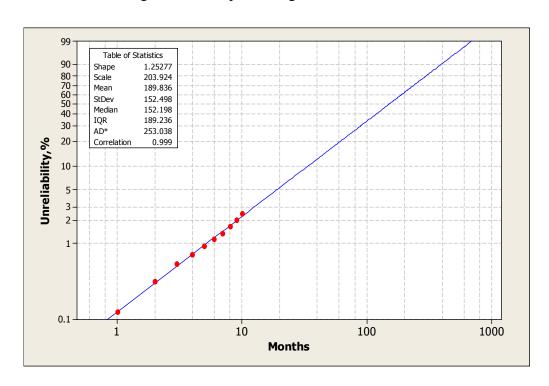

| Table 7-5 Cycles to failures (bump crack) for FCBGA I packages                          |

| Table 7-6 Failure distribution parameter summary                                        |

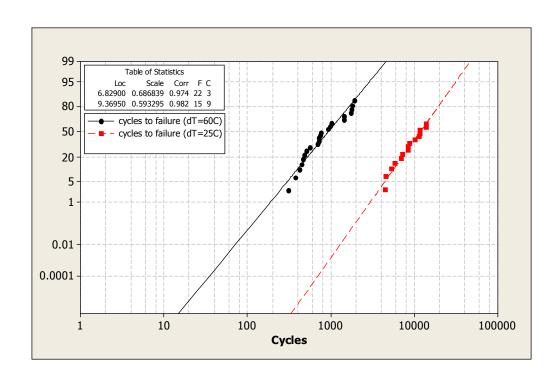

| Table 7-7 Break-down cycles to failures data using Log0normal distribution 228          |

| Table 7-8 Power exponent n estimation from N-L models                                   |

| Table 7-9 Cycles to failures data of FCBGA II packages                          | 231 |

|---------------------------------------------------------------------------------|-----|

| Table 7-10 Failure data analysis results                                        | 233 |

| Table 7-11 Comparison of field failure data and modeling results                | 233 |

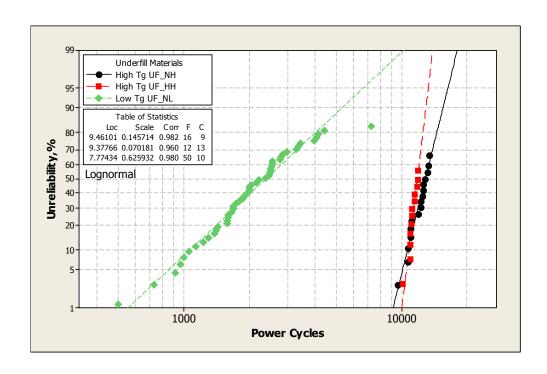

| Table 7-12 Low Tg and high Tg underfill material properties                     | 234 |

| Table 7-13 Cycles of failure data of FCBGAs using different underfill materials | 236 |

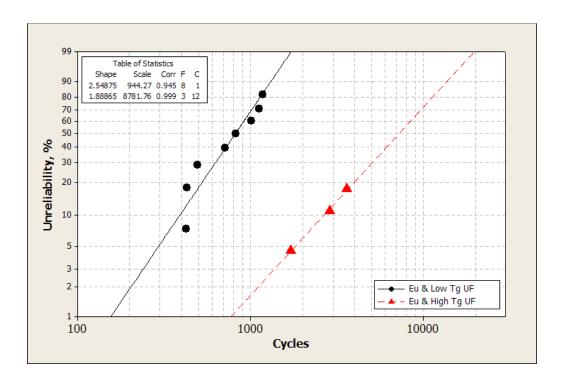

| Table 7-14 Cycles to failure data of FCBGA II packages using eutectic bumps     | 242 |

| Table 7-15 Cycles to failure data for 35 mm x 35 mm FCBGA III packages          | 244 |

# List of Figures

| Figure 1-1 Images of a FCBGA package [Prismark, 2007]2                               |

|--------------------------------------------------------------------------------------|

| Figure 1-2 A cross section view of the package [Prismark, 2007]                      |

| Figure 1-3 A cross section of a wire bond LGA package [Prismark, 2008]               |

| Figure 1-4 A cross section of a stacked BGA package [Prismark, 2008]                 |

| Figure 1-5 A CSAM image of the solder bumps                                          |

| Figure 1-6 A close-up view of bump/UBM interfaces                                    |

| Figure 1-7 Low-k dielectric cracking in silicon [Yang and Walls, 2007]               |

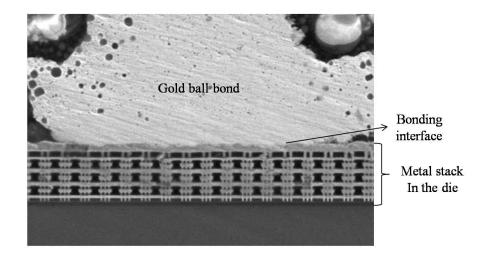

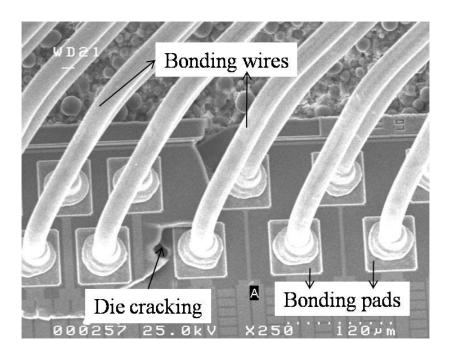

| Figure 2-1 An image of wire bond interconnects [Yang, 2007]                          |

| Figure 2-2 Ball bond in wire bonding [Yang, 2007]                                    |

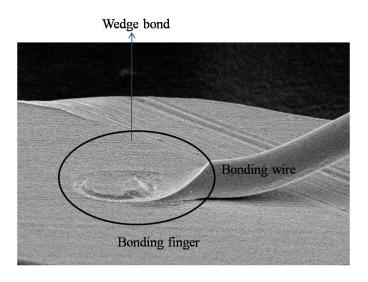

| Figure 2-3Wedge bond in wire bonding [Yang, 2007]                                    |

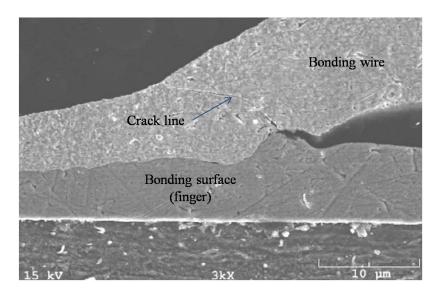

| Figure 2-4 Wedge bonding failure (fracture failure seen in the heel) [Yang, 2007] 27 |

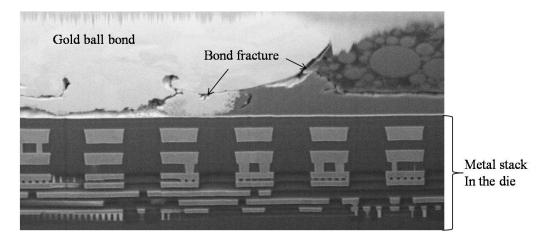

| Figure 2-5 Ball bond interface cracking (failure at TC 1000 cycles) [Yang, 2007] 27  |

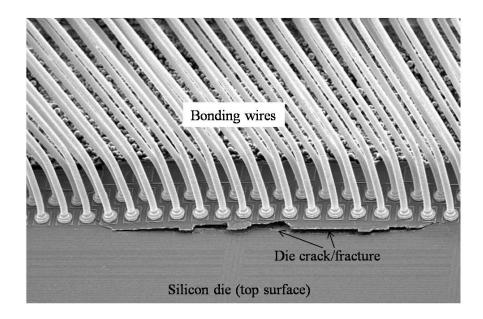

| Figure 2-6 die cracking failure seen at the die surface [Yang & Bernstein, 2008] 29  |

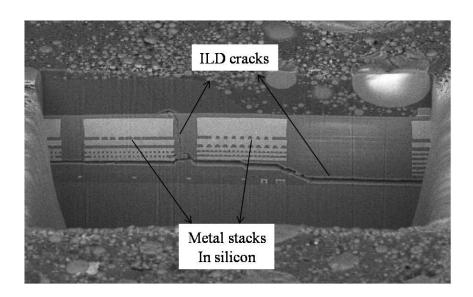

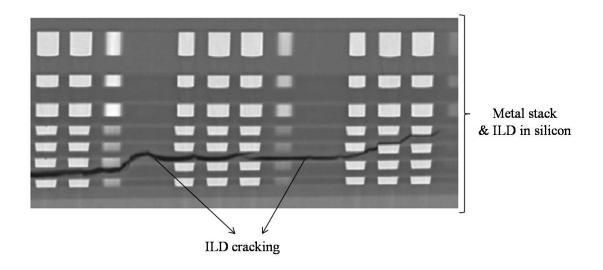

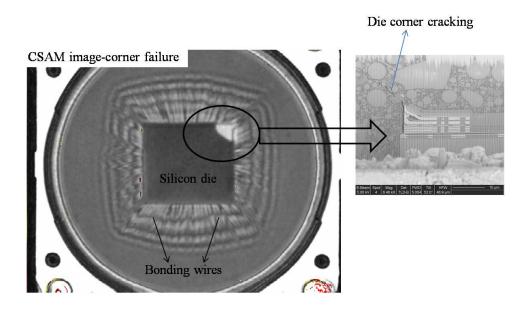

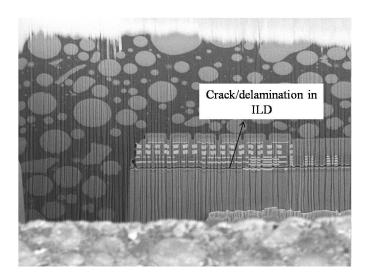

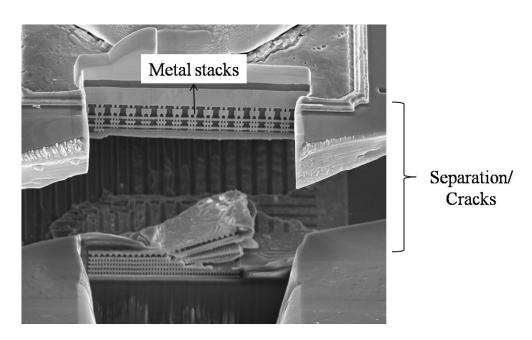

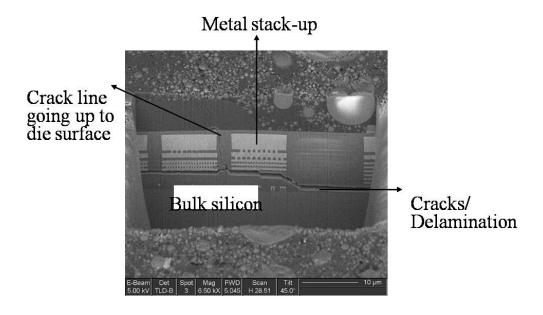

| Figure 2-7 Inner layer dielectric and thin film cracking failure [Yang & Bernstein,  |

| 2008]                                                                                |

| Figure 2-8A close-up view of low-k dielectric cracking [Yang, 2007]30                |

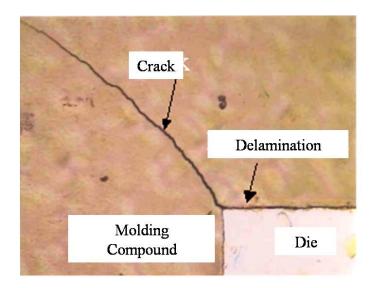

| Figure 2-9 Package cracking failure after TC 600 cycles (die corner delamination)   |

|-------------------------------------------------------------------------------------|

| [Yang, 2007]                                                                        |

| Figure 2-10 Package cracking (molding cound cracking) [Yang, 2007]34                |

| Figure 2-11 An example of a interface delamination failure seen in the package[Yang |

| 2007]                                                                               |

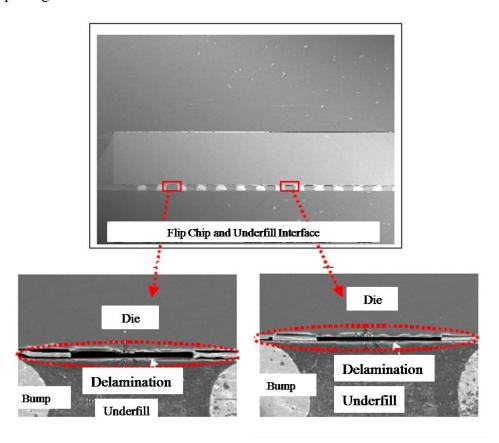

| Figure 2-12 Delamination at ILD after moisture sensitivity tests [Yang, 2007] 36    |

| Figure 2-13 Delamination between the underfill and the die after 100 hours HAST     |

| [Freescale, 2008]                                                                   |

| Figure 2-14 Solder interconnections in semiconductor packages [Prismark, 2007] 40   |

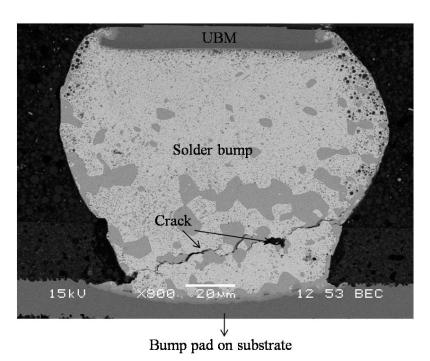

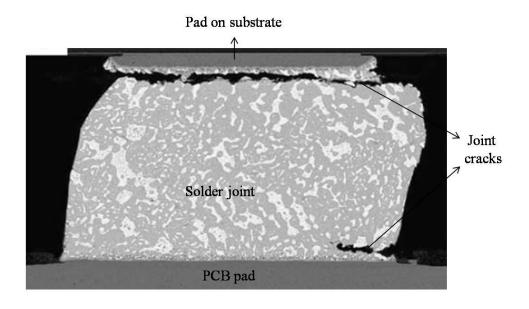

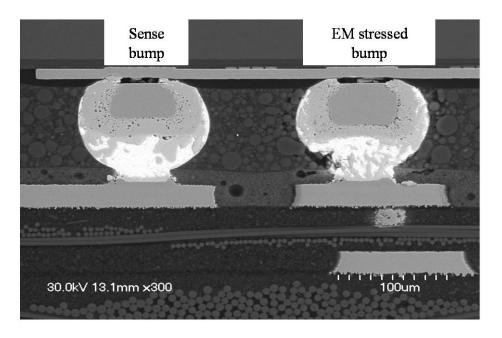

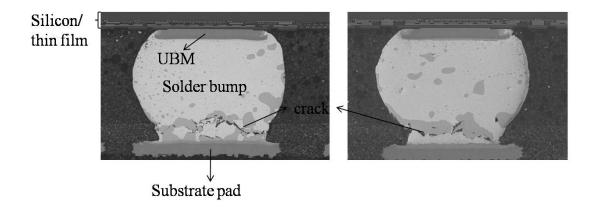

| Figure 2-15 A bump cracking failure                                                 |

| Figure 2-16 A second level solder joint failure [Freescale, 2004]                   |

| Figure 2-17 Bump structures under electromigration testing [Gajewski, 2006] 47      |

| Figure 2-18 Solder joint cracking due to electromigration [Su et al., 2005] 48      |

| Figure 4-1 Lead frame based packages and the solder joints                          |

| Figure 4-2 A close-up view of the solder joints in lead frame based packages 76     |

| Figure 4-3 A diagram of a flip chip BGA package and solder connects                 |

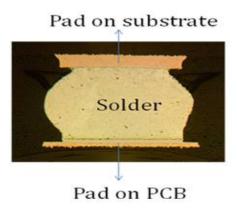

| Figure 4-4 Solder joint (2nd level) between the PCB and the substrate               |

| Figure 4-5 Solder joint between the substrates and the silicon die (bumps)          |

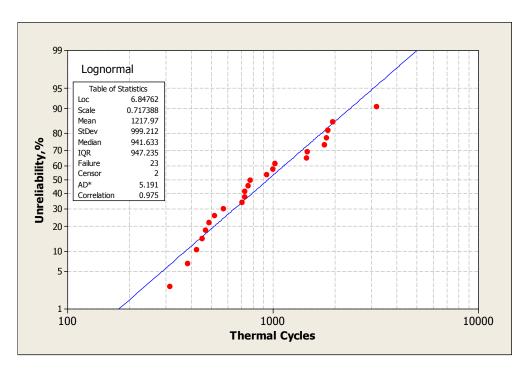

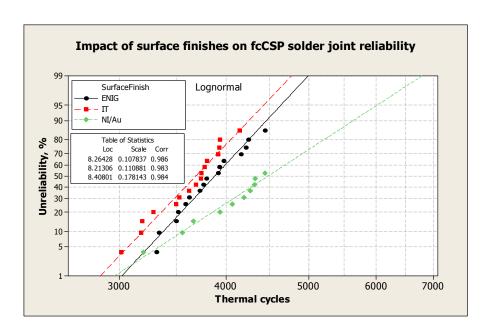

| Figure 4-6 An example of a Log-normal plot for solder joint failures                |

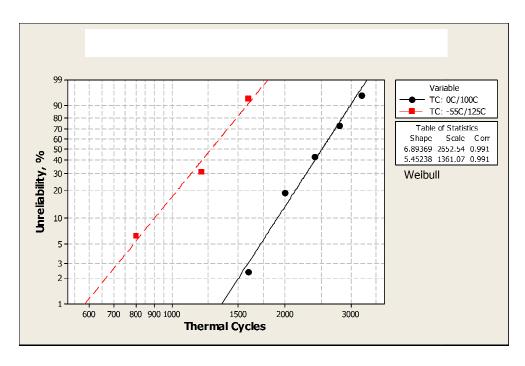

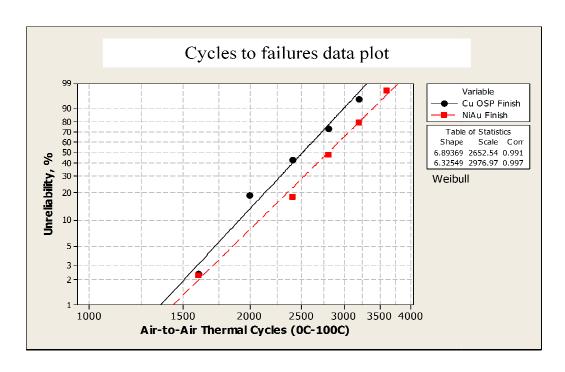

| Figure 4-7 Impact of surface finishes of PCB pads                                    |

|--------------------------------------------------------------------------------------|

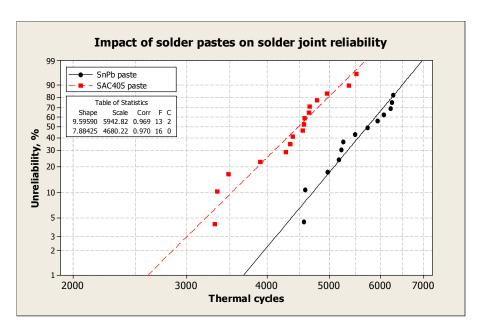

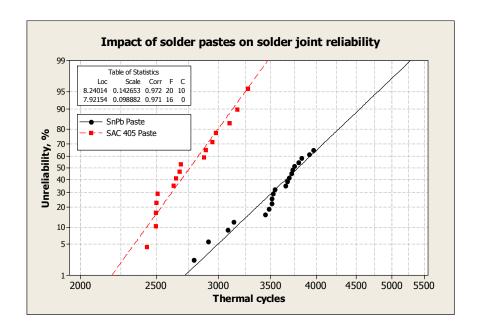

| Figure 4-8 Impact of solder pastes on solder joint reliability of 144-ball MAPBGAs94 |

| Figure 4-9 Impacts of solder pastes on solder joint reliability of 225 MAPBGAs 96    |

| Figure 4-10 Weibull plots of 33 mm FCBGA solder joint failures                       |

| Figure 4-11 Weibull plot of failure data of 209-ball MAPBGAs 108                     |

| Figure 5-1 Field return failure distribution of Company A in a year [Yang et al.,    |

| 2007]                                                                                |

| Figure 5-2 Schematic stack-up structure of RCPs                                      |

| Figure 5-3 Bottom view of the RCP package                                            |

| Figure 5-4 Cracking trace in the dielectric                                          |

| Figure 5-5 Cracks cutting into the die (Focus-ion-beam image)                        |

| Figure 5-6 Weibull distribution plot of the failure data observed in RCPs 127        |

| Figure 5-7 Exponential distribution plot of the failure data observed in RCPs 127    |

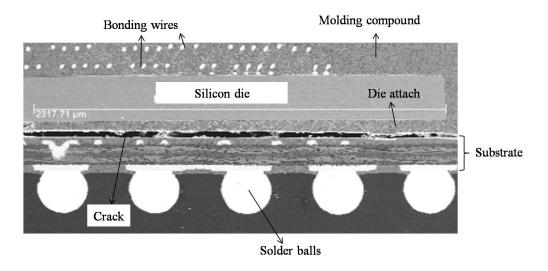

| Figure 5-8 FCMMAP module cross section                                               |

| Figure 5-9 Delamination failures seen in silicon                                     |

| Figure 5-10 Weibull plot of the failure data (FCMMAP)                                |

| Figure 5-11 Exponential plot of the failure data (FCMMAP)                            |

| Figure 5-12 PQFN cross section diagram                                               |

| Figure 5-13 Top view of PQFN packages                                          |

|--------------------------------------------------------------------------------|

| Figure 5-14 Weibull plot for the PQFN failures during thermal cycling test 137 |

| Figure 5-15 Failure data probability plot (two failure mechanisms)             |

| Figure 5-16 Weibull distribution of the failures of PLCC packages              |

| Figure 5-17 Exponential distribution of failures of PLCC packages              |

| Figure 6-1 Top and bottom view of TEBGA packages                               |

| Figure 6-2 A cross section image of a TEBGA package [Yang and Bernstein, 2008] |

|                                                                                |

| Figure 6-3 A cross section view of thin film cracking/delamination             |

| Figure 6-4 Die surface cracks after the thermal cycling tests                  |

| Figure 6-5 Die edge cracks and chipping                                        |

| Figure 6-6 FIB image showing the inner layer cracking/delamination             |

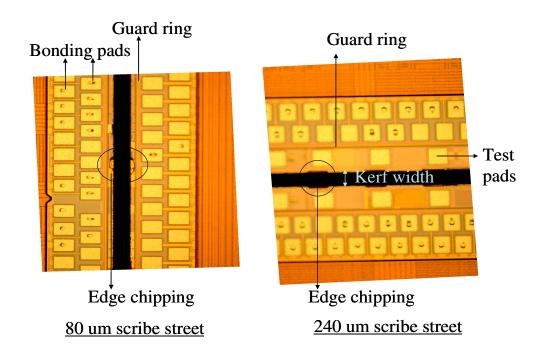

| Figure 6-7 Die cracks seen on the die surface                                  |

| Figure 6-8 A cross section view of thin film delamination at interfaces        |

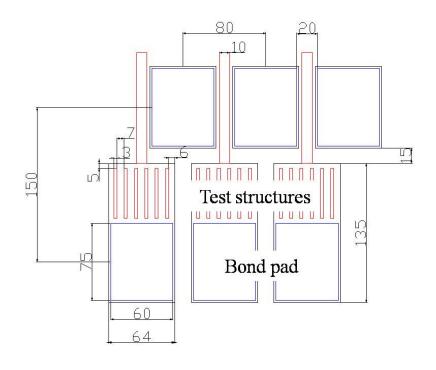

| Figure 6-9 Bond pad layout and pitch rules                                     |

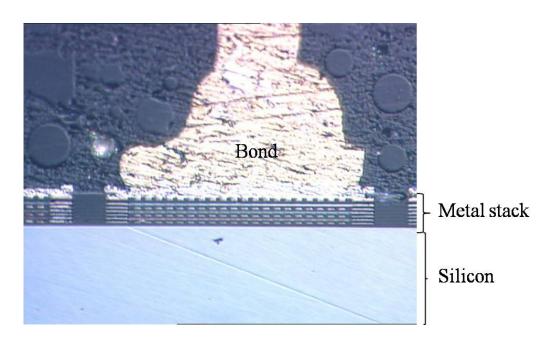

| Figure 6-10 Bond pad structure (Al cap above Cu stack-up)                      |

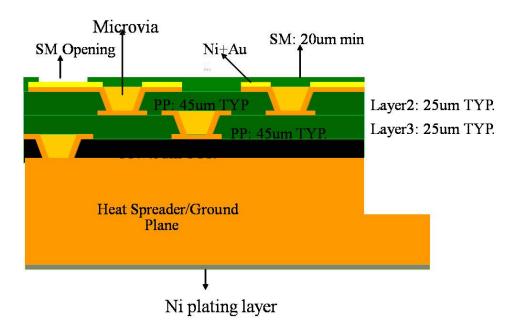

| Figure 6-11 The stack-up diagram of the substrate technology                   |

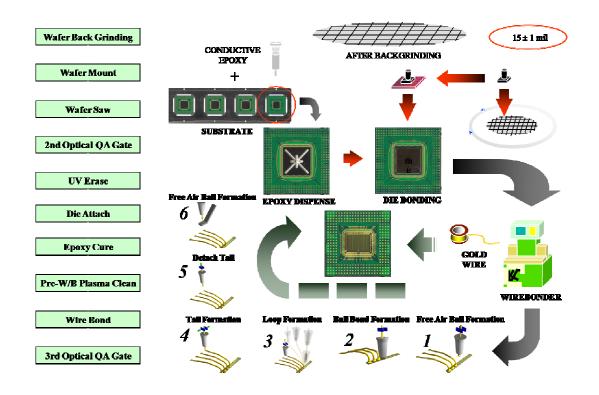

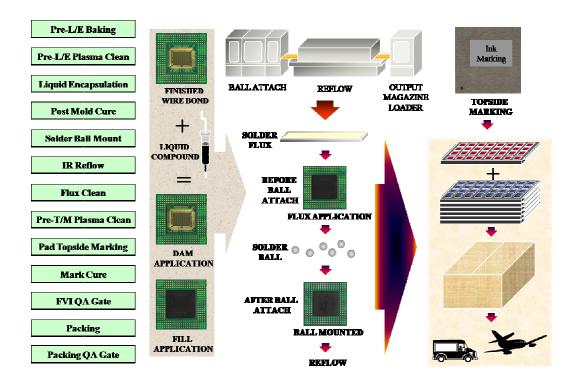

| Figure 6-12 TEBGA package assembly process flow-Part I [ASE, 2004] 162         |

| Figure 6-13 TEBGA package assembly process flow-Part II [ASE, 2004] 163                 |

|-----------------------------------------------------------------------------------------|

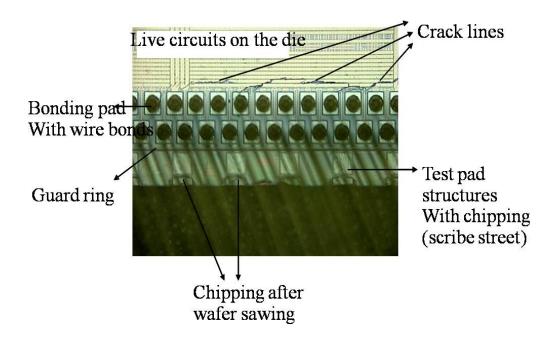

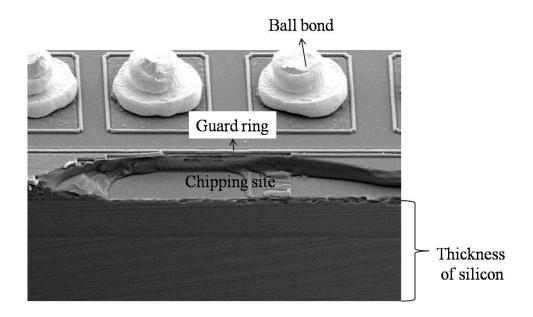

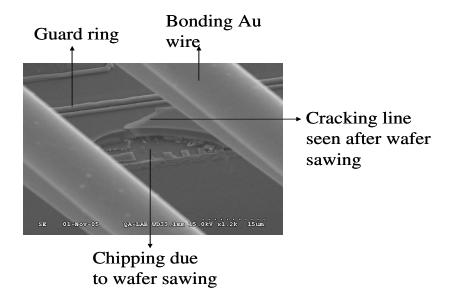

| Figure 6-14 Chipping touching the guard ring                                            |

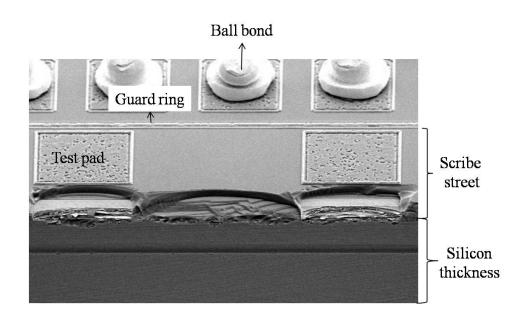

| Figure 6-15 Test pads and the chipping at the scribe street                             |

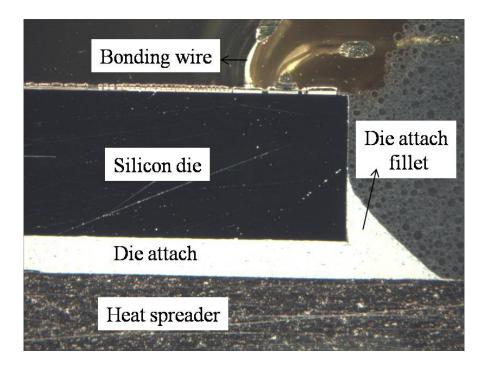

| Figure 6-16 Demonstration of die attach elements                                        |

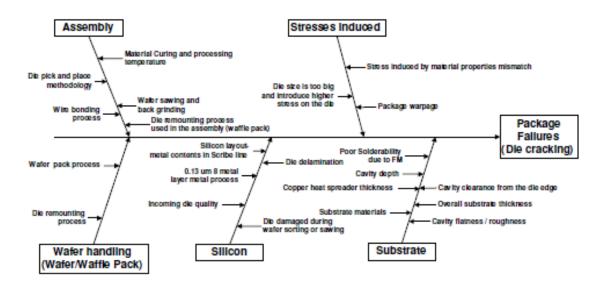

| Figure 6-17 Fishbone diagram for the root cause analysis of die cracking failures . 167 |

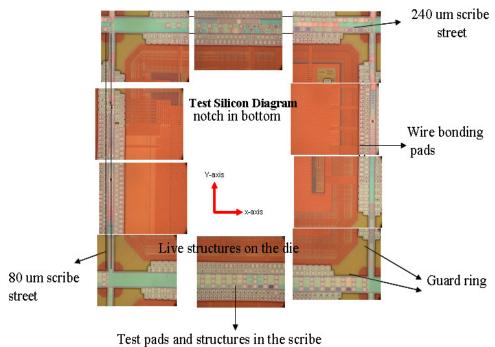

| Figure 6-18 Schematic diagram of the test chip showing the scribe street                |

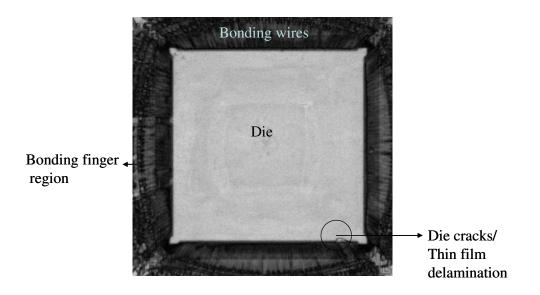

| Figure 6-19 A CSAM showing the die cracking/thin film delamination at the die edge      |

| (small)                                                                                 |

| Figure 6-20 A CSAM showing the die cracking/thin film delamination at the die 173       |

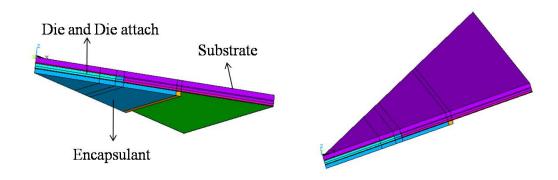

| Figure 6-21 A 1/8 FEA model of the package                                              |

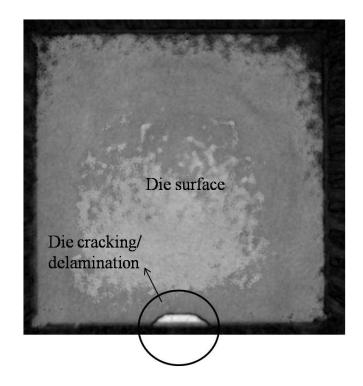

| Figure 6-22 Die edge cracking seen after decapping                                      |

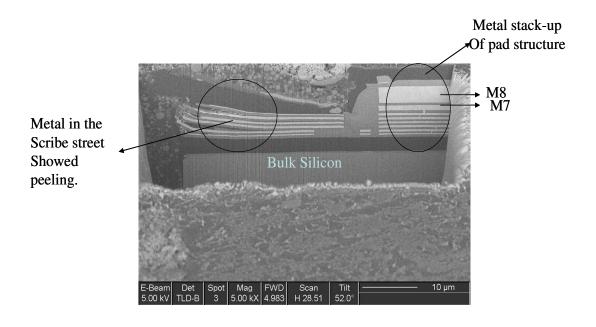

| Figure 6-23 Chipping and metal peeling at the die edge                                  |

| Figure 6-24 Visual images of the defects after the wafer sawing using resin blades 180  |

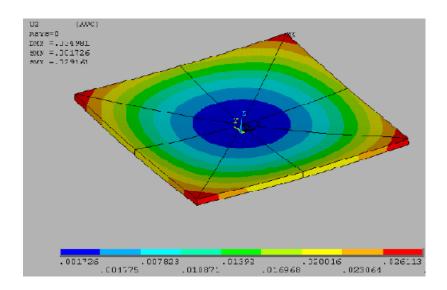

| Figure 6-25 Die placement contour under thermal cycling tests                           |

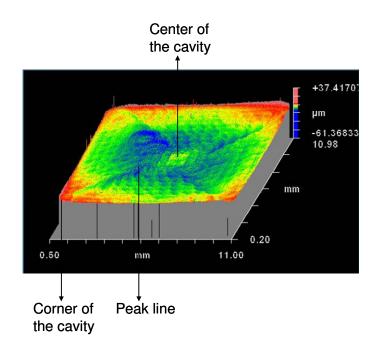

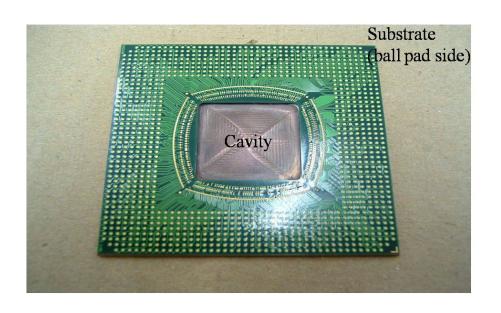

| Figure 6-26 A scanning contour showing the substrate cavity                             |

| Figure 6-27 Cavity surfaces of TEBGA substrates                                         |

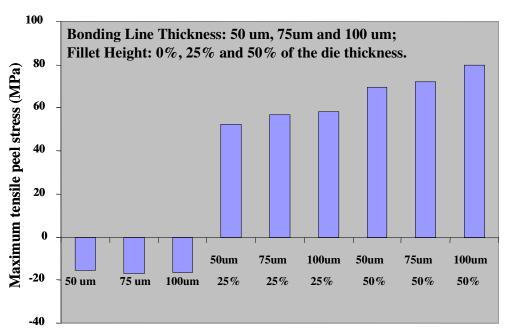

| Figure 6-28 Impact of the die fillet height on the die stress of TEBGAs                 |

| Figure 6-29 Log-normal plot of the solder joint failure data for TEBGAs                 |

| Figure 6-30 Weibull plot of the solder joint failure data for TEBGAs                | 189 |

|-------------------------------------------------------------------------------------|-----|

| Figure 6-31 Reliability analysis using periodic resistance data (every 1000 cycles) | 190 |

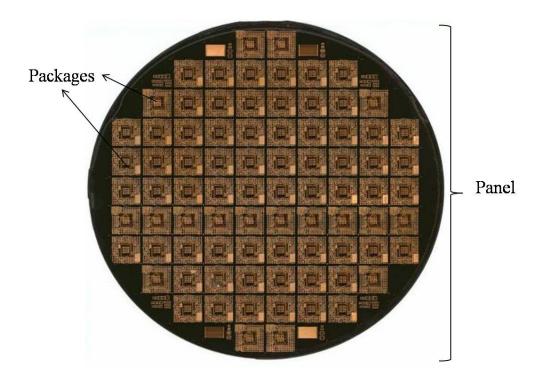

| Figure 6-32 A panel with CSP packages                                               | 193 |

| Figure 6-33 Stack-up view of the CSP package structure                              | 193 |

| Figure 6-34 Dielectric cracking on the surface                                      | 194 |

| Figure 6-35 Dielectric cracking near the ball pads                                  | 195 |

| Figure 6-36 Cu trace cracking in build-up layers                                    | 196 |

| Figure 6-37 Layout optimization of the Cu traces in the package                     | 196 |

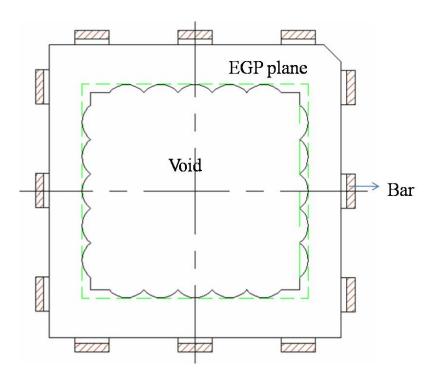

| Figure 6-38 An example of an EGP design                                             | 197 |

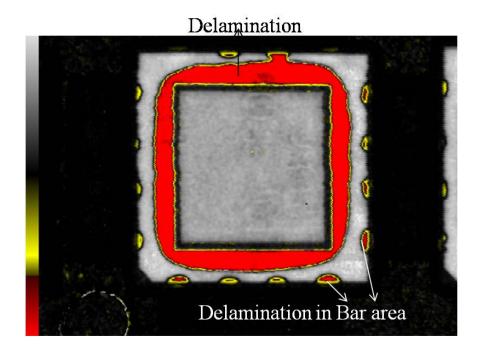

| Figure 6-39 EGP layer delamination failure (CSAM)                                   | 198 |

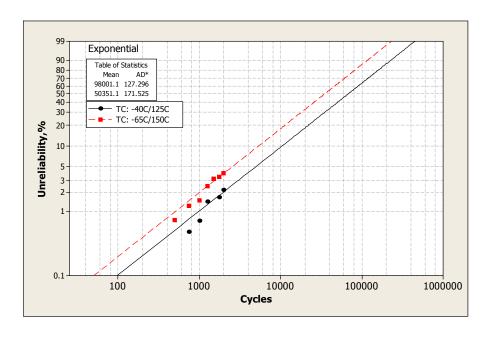

| Figure 6-40 Exponential plot of failure data under two TC conditions                | 202 |

| Figure 6-41Exponential plot for the failures under thermal cycling test             | 204 |

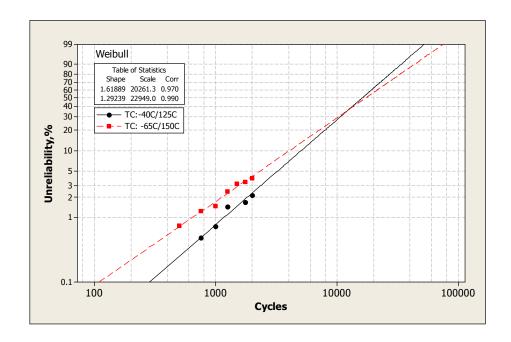

| Figure 6-42 Weibull plot of cycles to failures from 9 mm RCPs                       | 207 |

| Figure 6-43 Impact of surface finish on the solder joint reliability performance    | 209 |

| Figure 7-1 A diagram showing a flip chip package                                    | 212 |

| Figure 7-2 An example of bumping processes (plating processes)                      | 213 |

| Figure 7-3 An example of a solder joint between the die and the substrate           | 214 |

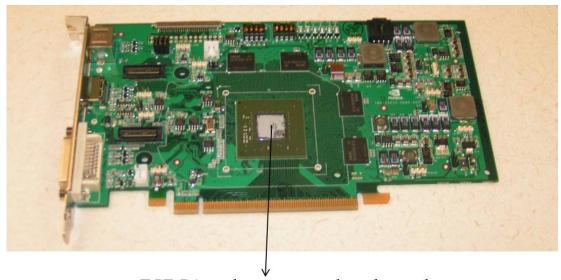

| Figure 7-4 An image of the application board used in power cycling tests            | 219 |

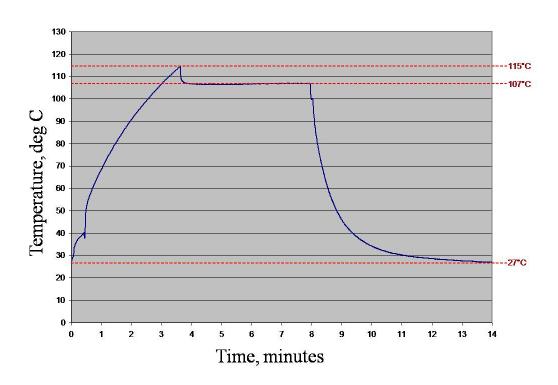

| Figure 7-5 An example of the power cycling profile                      | 219 |

|-------------------------------------------------------------------------|-----|

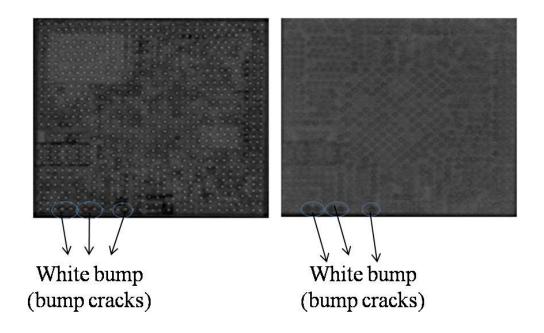

| Figure 7-6 Bump failure detection through CSAM                          | 221 |

| Figure 7-7 Bump cracking failures after 1650 cycles                     | 221 |

| Figure 7-8 Bump cracking seen infield failures                          | 224 |

| Figure 7-9 Weibull plot for field failures in 10 months                 | 224 |

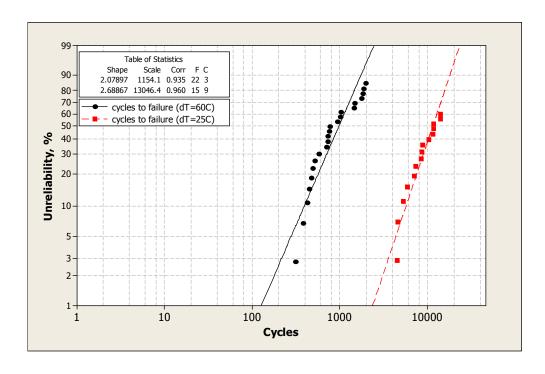

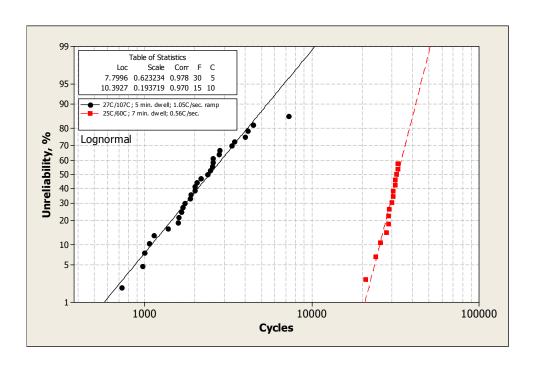

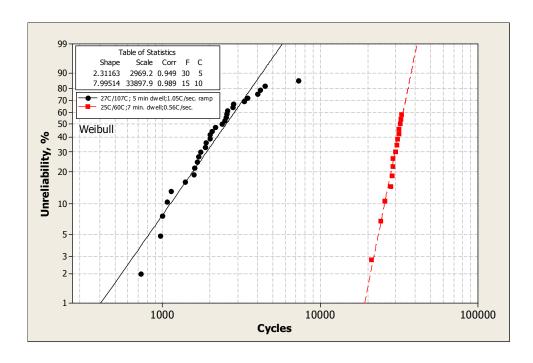

| Figure 7-10 Log-normal plot of power cycling failures                   | 229 |

| Figure 7-11 Weibull plot of power cycling failures                      | 229 |

| Figure 7-12 Log-normal plot of FCBGA II failures                        | 232 |

| Figure 7-13 Weibull plot of FCBGA II failures                           | 232 |

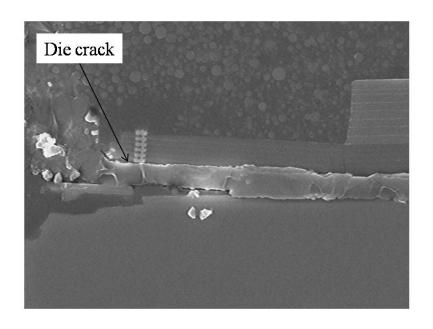

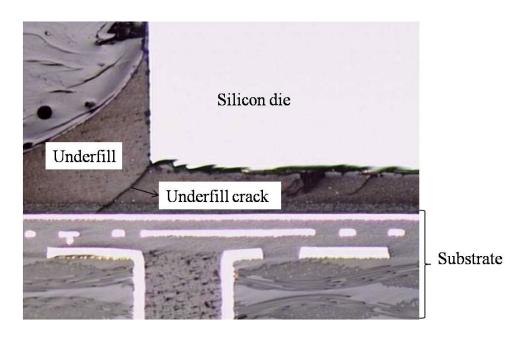

| Figure 7-14 Low-k dielectric / die cracking failures                    | 235 |

| Figure 7-15 Underfill cracking in flip chip packages                    | 235 |

| Figure 7-16 Distribution plot using low and high Tg underfill materials | 238 |

| Figure 7-17 Impact of underfill materials using eutectic solder bumps   | 238 |

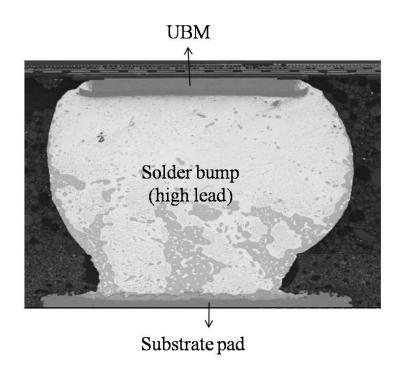

| Figure 7-18 High lead solder bump /joints                               | 240 |

| Figure 7-19 Eutectic solder bump joints                                 | 240 |

| Figure 7-20 High lead solder bump after 4500 cycles                     | 241 |

| Figure 7-21 Eutectic solder bump after 4500 cycles                      | 241 |

| Figure 7-22 Reliability of eutectic solder bumps in a large package/die | 243 |

| Figure 7-23Weibull distribution of FCBGA III power cycling failures      | 245 |

|--------------------------------------------------------------------------|-----|

| Figure 7-24 Exponential distribution of FCBGA III power cycling failures | 245 |

| Figure 7-25 Log-normal distribution of FCBGA III power cycling failures  | 246 |

| Figure 8-1 End-of-life AF model determination for semiconductor packages | 252 |

### List of Illustrations

| β                  | shape parameter in Weibull distribution                             |

|--------------------|---------------------------------------------------------------------|

| $oldsymbol{eta}_i$ | shape parameter in Weibull distribution for failure mechanism i     |

| η                  | characteristic life in Weibull distribution                         |

| α                  | the filament formation acceleration factor                          |

| p                  | the multilayer correction factor, from 1-3                          |

| μ                  | the geometry acceleration factor                                    |

| ω                  | the voltage acceleration factor                                     |

| $\theta$           | mean life in exponential distribution                               |

| $\sigma$           | normal stress                                                       |

| λ                  | failure rate                                                        |

| Ψ                  | constant                                                            |

| ξ                  | constant                                                            |

| $\eta(T)$          | characteristic life under temperature stress (Weibull distribution) |

| $\eta(V)$          | characteristic life under voltage stress (Weibull distribution)     |

| $\theta(T)$        | mean life under temperature stress (Exponential distribution)       |

| $\theta(V)$        | mean life under voltage stress (Exponential distribution)           |

| $\lambda(T)$             | failure rate as a function of temperature |

|--------------------------|-------------------------------------------|

| $\lambda(V)$             | failure rate as a function of voltage     |

| $\lambda_s$              | system failure rate                       |

| $\gamma_0$ , $\gamma_1$  | constant                                  |

| $oldsymbol{arepsilon}_f$ | the fatigue ductile coefficient in shear  |

| a                        | constant                                  |

| b                        | constant                                  |

| C                        | constant                                  |

| d                        | constant                                  |

| $dL_{c}/dN_{c}$          | crack growth rate                         |

| k                        | Boltzmann constant, 8.617343x10-5 eV/K    |

| t                        | time                                      |

| $t_a$                    | dwell time at use conditions              |

| $t_{t}$                  | the dwell time at test conditions         |

| $t_f$                    | time to failures                          |

| X                        | thickness of the diffusion layers         |

| $\Delta arepsilon$       | inelastic strain range                    |

|                          |                                           |

xxvi

plastic strain  $\Delta {\cal E}_p$  $\Phi(T_{\text{max}})$ function in N-L equation, related to the maximum temperature  $\Delta K$ intensity factor  $\Delta K_{eff}$ the effective stress intensity factor range  $\Delta T$ temperature interval or temperature range  $\Delta T_{use}$ temperature range/interval at use or field conditions  $\Delta T_{test}$ temperature range /interval at test conditions  $\Delta W$ viscoplastic strain energy density accumulated per cycle  $\Delta W_{avg}$ average viscoplastic strain energy density accumulated per cycle  $\boldsymbol{A}$ constant **AATC** air-to-air thermal cycling AFacceleration factor acceleration factor for failure mechanism I  $AF_1$  $AF_2$ acceleration factor for failure mechanism II  $AF_{\Delta T}$ acceleration factor due to temperature interval/range  $AF_{base}$ Acceleration factor value from N-L format

acceleration factor due to cycling frequency

$AF_f$

$AF_{RH}$  acceleration factor due to RH stress acceleration

$AF_s$  acceleration factor for the system

$AF_T$  acceleration factor due to temperature acceleration

$AF_{(T,RH)}$  acceleration factor due to temperature and relative humidity

$AF_{(T,V)}$  acceleration factor due to temperature and voltage acceleration

$AF_V$  acceleration factor due to voltage acceleration

B a value dependent on thermal profiles (average temperature of the

solder and the half dwell time

C constant

C4 controlled collapse chip connections

$Corr(\Delta T_{use})$  temperature excursion range dependent correction factor for use

$Corr(\Delta T_{test})$  temperature excursion range dependent correction factor for test

CSAM c-mode scanning acoustic microscopy

CTE coefficient of thermal expansion

$dL_c/dN_c$  crack propagation rate per thermal cycle

DNP distant neutral point

E<sub>a</sub> activation energy

EM electromigration

ENIG electroless Ni immersion Au

EOS electrical overstress

ESD electron static discharge

f cycle frequency

$f_{use}$  or  $f_a$  cycle frequency at use or field applications

$f_{test}$  or  $f_t$  cycle frequency at test conditions

F(t,T) cumulative distribution function related to time t and stress factor T

F(t,U) cumulative distribution function related to time t and stress factor U

FCBGA flip chip ball grid array

FIB focus ion beam

FP failure percentage

*FP*<sub>1</sub> failure percentage due to failure mechanism I

FP<sub>2</sub> failure percentage due to failure mechanism II

g the growth rate of the corrosion

G a function of geometry

H constant

$H_{use}$  stress factor of H at use conditions

$H_{test}$  stress factor of H at test conditions

HAST highly accelerated stress test

HDI high density interconnect

HTOL high temperature operating life

ILD inner layer dielectric

IMC intermetallic compound

IPL Inverse power law

J the current density

$K_0$  constant

$K_1$  constant

$K_2$  constant

$K_3$  constant

$K_4$  constant

$L_c$  crack length

$L_{\it eff}$  the effective length between conductors

LGA land grid array

M the percentage moisture contents

$M_t$  the percentage of the threshold moisture content

m constant for cycle frequency term in N-L model

MTTF mean- time- to- failure

$MTTF(T_{use})$  mean-time-to-failure at use condition temperature

$MTTF(T_{test})$  mean-time-to-failure at test condition temperature

*n* constant for temperature range term in N-L model

$n_i$  fractional sub-population for each failure mechanism i

*NF* number of failure mechanisms

$N_0$  initial number of cycles to crack initiation

$N_f$  number of cycles to failures

$N_{test}$  or  $N_t$  number of cycles at test conditions

$N_{\it use}~or~N_{\it a}$  number of cycles at use conditions

OLGA organic land grid array

OSP organic solderability preservatives

PBGA plastic ball grid array

PC power cycling

PCB printed circuit board

PCT pressure cooker test

PQFP plastic qual flat package

PTH plated through hole

QFP quad flat package

QFN quad flat no-lead

R(t) reliability at time t

RH relative humidity, %

$RH_{use}$  relative humidity at use or field conditions

*RH*<sub>test</sub> relative humidity at test conditions

s constant related to temperature

SAC Sn-Ag-Cu solder alloy

SAC105 Sn-1Ag-0.5Cu solder alloy

SAC205 Sn-2Ag-0.5Cu solder alloy

SAC305 Sn-3Ag-0.5Cu solder alloy

SAC405 Sn-4Ag-0.5Cu solder alloy

SOIC small outline integrated circuit

SnPb eutectic Sn and Pb solder

xxxii

t time

$t_d$  half dwell time

T temperature, K<sup>o</sup>

$T_{\text{max}}$  Max temperature of the thermal profiles

$T_s$  cycle temperature of solder

$T_{sj}$  the average temperature of the solder

$T_{use}$  temperature at use or field conditions

$T_{test}$  temperature at test conditions

$T_{use\_max}$  maximum temperature at use conditions

$T_{test\_max}$  maximum temperature at test conditions

TC thermal cycling or temperature cycling

TEBGA thermally enhanced ball grid array

TH temperature and humidity

$T_g \hspace{1cm} glass \hspace{1cm} transition \hspace{1cm} temperature$

TS thermal shock

U stress factor

UBM under bump metrology

V voltage stress, v

$V_{use}$  voltage at use or field conditions

$V_{test}$  voltage at test conditions

WB wire bond

$x_{tk}$  thickness of the diffusion layer

z constant related to temperature

# 1. INTRODUCTION

## 1.1 Semiconductor packages and systems

Semiconductor packages contain electrical circuits and interconnect which form desirable functional entities. In order to have reliable and robust package systems in the application, mechanical structures and enhancements / protections are required. In addition, the packages must provide adequate means for heat removal, since all circuits operate best at lower temperatures. Moreover, the packages must meet the required reliability performance under the specified conditions. The package design, assembly/ packaging processes, and packaging materials all contribute to the final reliability performance of the products.

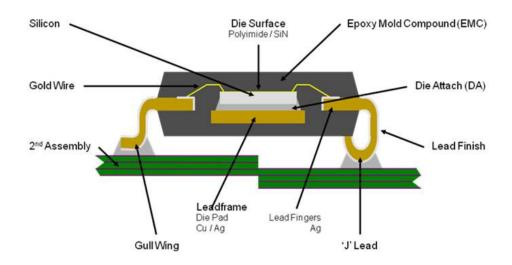

Semiconductor packages can be categorized into two types of platforms, lead-frame based or substrate based. Small Outline Integrated Circuits (SOIC), Quad Flat Package (QFP) and Quad Flat No-Lead (QFN) packages are all lead frame based packages. The substrate based packages include Plastic Ball Grid Array (PBGA) packages, Thermally Enhanced Ball Grid Array (TEBGA) packages and Flip Chip Ball Grid Array (FCBGA) packages. The multiple interfaces in the package present a great challenge to manufacturing processes and reliability performance.

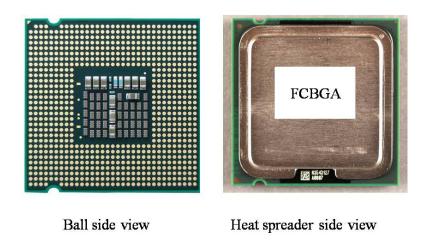

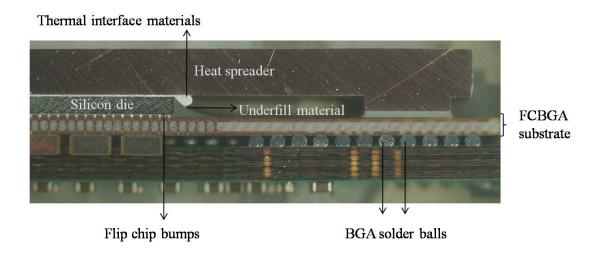

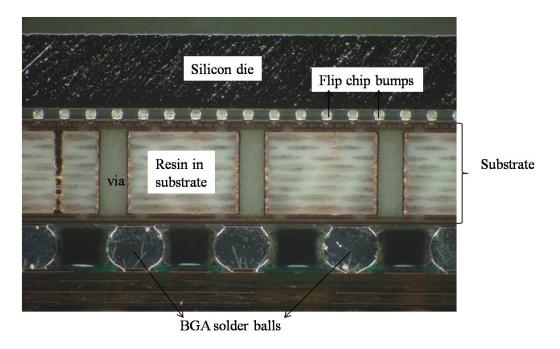

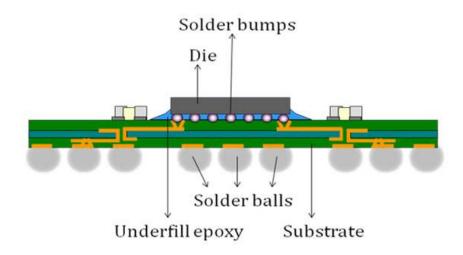

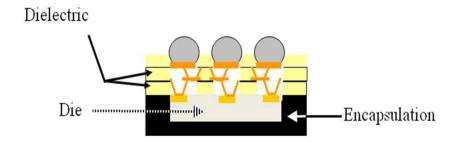

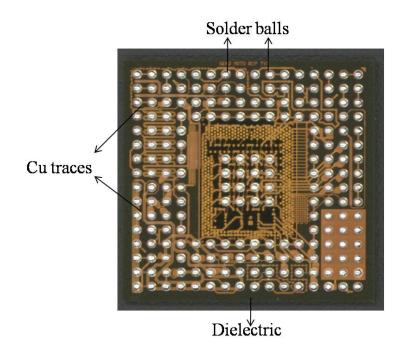

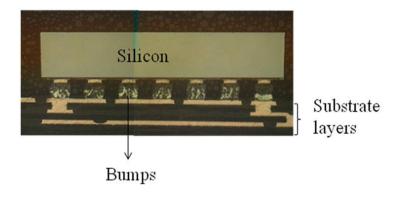

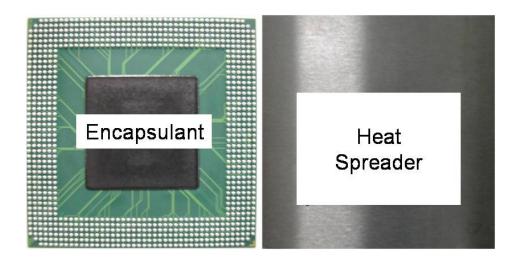

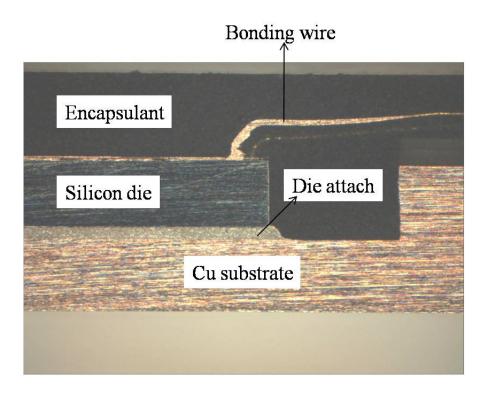

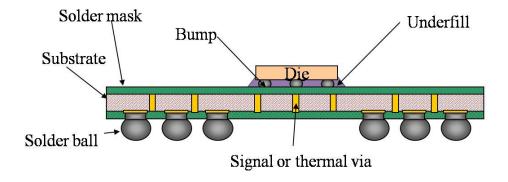

Figure 1-1 shows an example of a FCBGA package with a heat spreader, while Figure 1-2 shows a cross-section view of the package. The package consists of an organic substrate, a die, underfill materials to protect the die, flip chip bumps and solder balls for interconnects, a large copper heat spreader and some capacitors. In addition,

a layer of thermal interface materials provides a thermal pathway between the heat spreader and the die. The periphery of the heat spreader is affixed to the substrate.

Figure 1-1 Images of a FCBGA package [Prismark, 2007]

Figure 1-2 A cross section view of the package [Prismark, 2007]

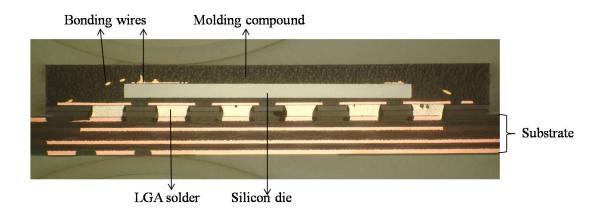

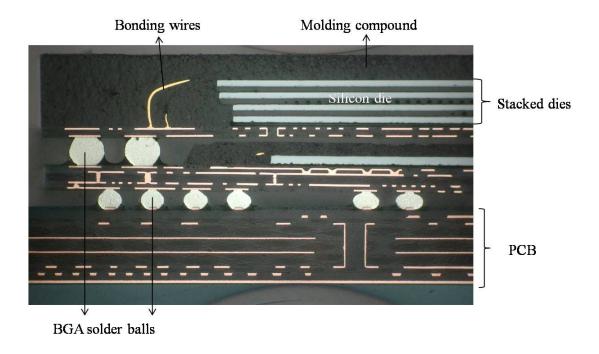

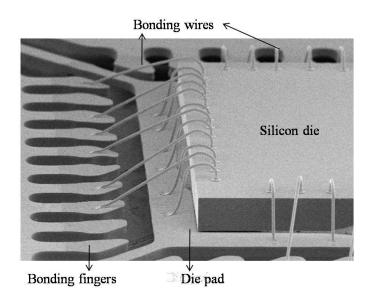

Besides FCBGA packages, other technologies have been widely used, including various BGA packaging technologies using wire bond interconnects. Figure 1-3 shows a simple wire bond Land Grid Array (LGA) package, while Figure 1-4 shows a more complicated stack-up BGA package

Figure 1-3 A cross section of a wire bond LGA package [Prismark, 2008]

Figure 1-4 A cross section of a stacked BGA package [Prismark, 2008]

It is obvious that package technologies can be complicated. Moreover, their associated assembly processes and application conditions can post many reliability challenges. For example, the flip chip bumps can fail due to fatigue-induced cracking, the

silicon die can fail due to the inner layer dielectric (ILD) layer delamination, and there can be interface delamination and package cracking failures. In addition, the advancement in packaging processes and materials will require new approaches for the reliability enhancement or characterization of reliability models. In the following section, key factors in the structures will be described:

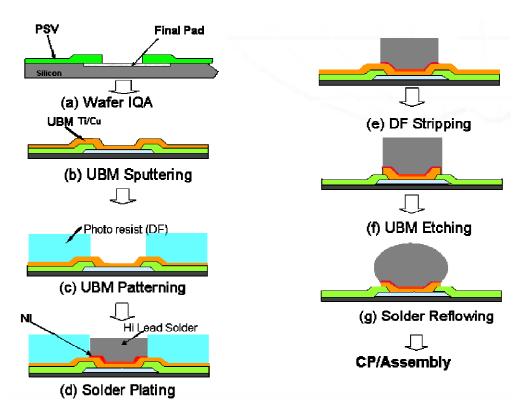

#### 1.1.1 Interconnects

Interconnections in package systems include bonding wires, flip chip bumps and the solder balls/leads. Obviously, interconnection failures will cause loss of function.

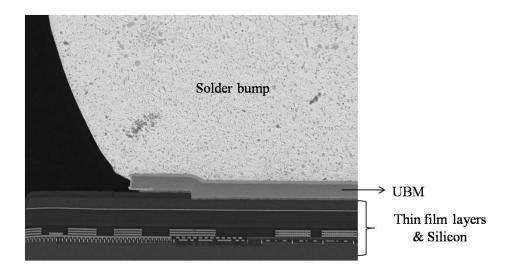

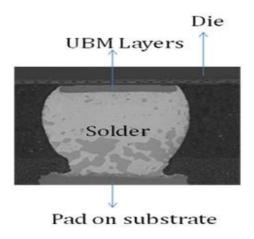

There are many variables influencing the interconnect reliability, such as interconnect materials, interconnect geometry and dimensions, process defects and other packaging materials that surround the interconnect. For example, flip chip bumps can be made of high lead solder, eutectic solder or copper. Different bump materials will demonstrate different reliability performance with the same packaging materials set. In addition, different bump materials might require comparable Under Bump Metrology (UBM) structures and stack-up to achieve desired bump reliability.

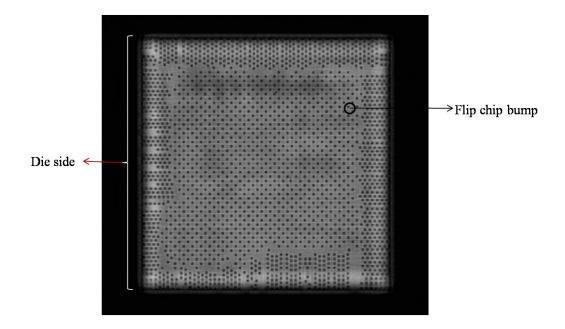

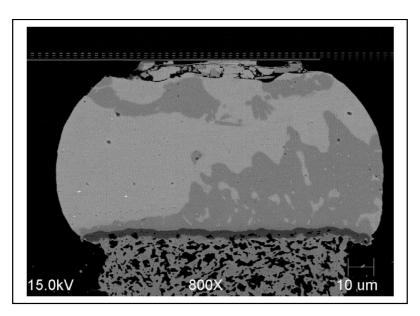

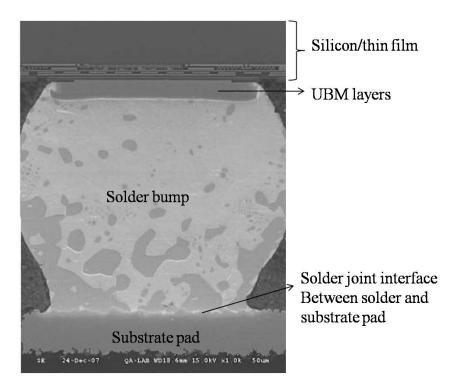

Figure 1-5 shows a C-mode Scanning Acoustic Microscopy (CSAM) image of solder bumps Figure 1-6 showed a close-up bump structure.

Figure 1-5 A CSAM image of the solder bumps

Figure 1-6 A close-up view of bump/UBM interfaces

#### 1.1.2 Lead frames and substrates

Lead frames and substrates can be used as carriers to connect the die to the PCBs. However, they will add new challenges to the reliability of the package, due to their material variations, the surface finishes of the contacts and dimensions/geometries. In addition, the trends for high density substrates and high performance will aggregate the challenges.

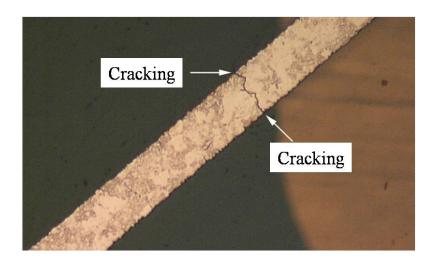

### 1.1.3 Low-k / Cu silicon technology

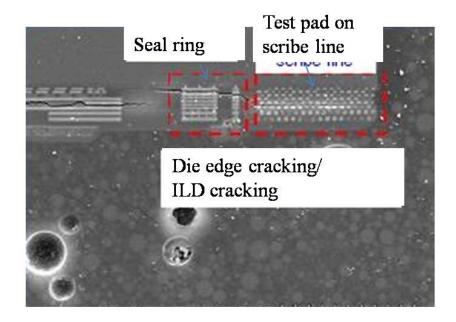

With the demand for high performance and small form factor products, most advanced products are moving to low-k Cu silicon. The tradeoff for adopting low-k Cu silicon is the reliability challenges associated with low-k materials and the scale down of the gate length and other critical dimensions. For example, in low-k Cu silicon, low-k dielectric cracking and thin film delamination failures are dominant new failure mechanisms. The adoption of low-k Cu silicon will challenge the materials suppliers to come out with a compatible set of packaging materials to mitigate the risks in the package structure, such as the optimization of underfill materials in FCBGA packages. Figure 1-7 shows the ILD cracking failures due to the interaction between the silicon and packaging materials.

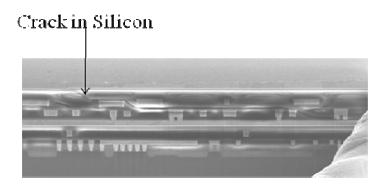

Figure 1-7 Low-k dielectric cracking in silicon [Yang and Walls, 2007]

## 1.1.4 Power dissipation and thermal profiles

Since the number of transistors packaged in a die is now higher, the power dissipation has dramatically increased. In addition, the use conditions in thermal profiling are more complex. As a result, the junction temperature and reliability performance of the devices are affected.

## 1.1.5 Package reliability prediction and the failure rate estimation

In general, when package reliability has been discussed, it often refers to conducting tests such as thermal cycling (TC), Highly Accelerated Stress Test (HAST) and High Temperature Operating Life (HTOL), etc., for the packages. The expectation is that tests will be passed based on pre-determined test conditions and durations. Little

knowledge has been obtained on the reliability life in the field, or on the estimation of failure rate. However, with more and more focus on reliability prediction, there is a need to understand the reliability life in the field, as well as the failure rate. Therefore, more reliability studies will be carried out in order to collect failure data and develop prediction models. The reliability assessment described in this dissertation will focus on the failure data collected and then, estimate the failure rate or reliability life under the use conditions.

## 1.2 Reliability considerations in semiconductor packages

## 1.2.1 Reliability concepts

The reliability of semiconductor packages is defined as the probability of a package to perform its function for a given time period, under specified conditions, without failures.

However, in industrial practices, the package reliability is usually judged by passing or failing required tests. The activities are usually limited to conducting stress tests and then attempting to identify and understand the failure mechanisms, if there are any failures. If necessary, changes are made to the packaging materials, assembly processes and package designs, in order to improve reliability performance.

## 1.2.2 Package failure categories

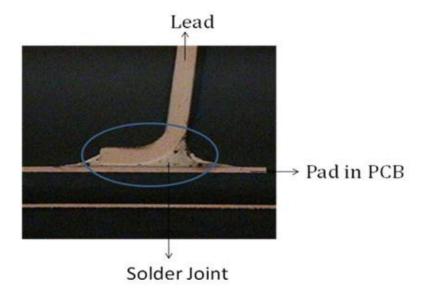

The package failures can be classified as solder joint failures and non-solder joint related failures. There are different ways to process the data from different failure categories. However, in field applications it is possible to analyze all of them with a similar approach.

Solder joint failures are often, worn-out fatigue failures and usually, these are associated with an increased failure rate. Various life prediction models for solder joint reliability are developed based on simulation or empirical data. However, there is a need to characterize those models, especially when there are new advancements in packaging materials, manufacturing processes and package designs. Additionally, the accuracy of the acceleration models for the life prediction of solder joints shall be validated.

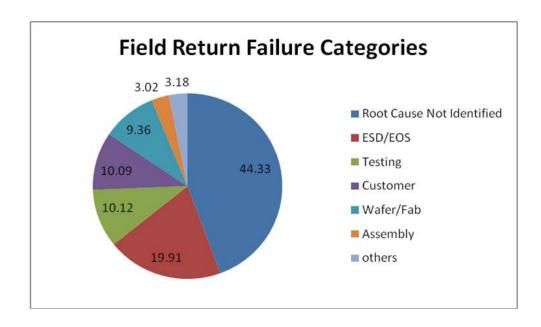

Non-solder related package failures refer to failures not associated with solder joint failures. They account for the majority of the field failures but, are not well modeled. Table 1-1 lists results of studies concerning common field-return failures from company A, while Table 1-2 shows the failure percentage breakdown related to the packages. Indeed, the study shows solder joint fatigue failure is not one of the dominant failure model/mechanisms observed.

Table 1-1 Research data based on field-return failures from Company A between 2006 to 2007 (Yang et al., 2007)

| Failure Mechanism              | Descriptions                                                              | # of Returns | % of Re- |

|--------------------------------|---------------------------------------------------------------------------|--------------|----------|

| Categories                     |                                                                           |              | turns    |

| Troubles not identified        | No root causes identified.                                                | 3219         | 27.58%   |

| ESD/EOS                        | Failures due to ESD and EOS failures.                                     | 2323         | 19.91%   |

| Unsuccessful analysis          | Cannot find out what is wrong and/or parts damaged.                       | 1955         | 16.75%   |

| Test (including soft-<br>ware) | Failures due to insufficient test coverage or gaps in software.           | 1181         | 10.12%   |

| Customer                       | Failures due to customer application set-ups or handlings.                | 1178         | 10.09%   |

| Wafer                          | Failures related to wafer fabrication processes.                          | 1092         | 9.36%    |

| Assembly                       | Failures related to packages (reliability or quality, manufacturing etc.) | 352          | 3.02%    |

| Other failure mechanisms       | Other than those identified                                               | 152          | 1.30%    |

| Lab services                   | Failures due to lab analysis.                                             | 100          | 0.86%    |

| Design                         | Failures due to product design issues.                                    | 53           | 0.45%    |

| Distribution                   | Failures due to logistics issues.                                         | 38           | 0.33%    |

| Customer services              | Returns due to customer service errors.                                   | 24           | 0.21%    |

| Product software               | Failures due to product software application.                             | 3            | 0.03%    |

| Total returns = 11670          | ]                                                                         |              | 100%     |

Table 1-2 Package assembly related field-return failures [Yang et al., 2007]

| Items                               | Failure Me-<br>chanisms | Description                                                               |

|-------------------------------------|-------------------------|---------------------------------------------------------------------------|

| Broken wires/bonds and lifted wires | 32.2%                   | Failures seen at the second stitch bonds on the lead frame or substrates. |

| Die cracking                        | 15.54%                  | Die chipping, passivation cracking or metal traces cracking in the die.   |

| Delamination                        | 12.71%                  | Any interface delamination, such as mold/die interface.                   |

| Die damage/wafer defects            | 12.15%                  | Die surface damage or scratch.                                            |

| Package/substrate cracking          | 10.17%                  | Organic substrate cracks and solder mask cracks.                          |

| Others                              | 17.23%                  | Other failures including solderability, foreign materials.                |

It should be reminded that the field failure data can be skewed, depending on the mainstream package types used by the companies.

## 1.2.3 Reliability assessment, prediction and failure rate modeling

One of the objectives of the reliability assessment is to understand the weakest links of the package and improve the reliability performance by eliminating the weakest links. The reliability studies will help with the collection of failure data in the accelerated stress tests to predict the time-to-failure, as well as the failure rates in the field based on the reliability models developed.

One of the difficulties in reliability prediction is the rarity of failure data from the stress-based approach. Instead of collecting the failure data, the intention is to pass the tests with zero failures. In order to validate or develop the models for reliability

prediction, a test-to-fail approach shall be adopted. The failure data observed in the stress tests will be required to understand the failure mechanism and predict the failure rate.

The reliability and failure rate models developed can be used to; (1) understand the life margin of the packages in the field application; and (2) predict the failure rate in the field. If necessary, the process will help reduce the failure returns in the field by screening out early failures. Reliability prediction and the modeling approach will help save time and reduce the cost of the package and production qualification process.

#### 1.3 Accelerated stress tests and acceleration factors (AF)

In accelerated stress tests, high stress stimuli are applied to a package to turn latent defects into observable failures within a short time period. The benefit of amplifying the occurrence of failures due to product deficiencies in accelerated stress testing is that product deficiencies become more apparent earlier in the process. However, the stress applied in these acceleration tests shall not introduce failure mechanisms which will not normally be seen in the field applications. In order to use the knowledge gained in accelerated stress testing, the failure mechanism shall be the same under both the stress conditions and the use conditions.

The common stress stimuli used in accelerated stress tests are listed below:

1. Elevated temperature. Testing a product for an extended period of time at an elevated temperature is probably the most common form of stress testing.

Marginal product designs often exhibit a temperature threshold beyond which the product will not function satisfactorily, and failure modes that involve chemical or diffusion processes can often be effectively accelerated at elevated temperature.

- Temperature cycling. A number of interconnection and packaging failures

modes are stimulated by temperature cycling. Faulty surface mount solder

joints or weak interfaces, for example, tend to fail intermittently and will fail

during temperature cycling.

- 3. Power cycling. Turning a product on and off is a common form of stress testing and is often done with or without other stress loads. The temperature transients that occur during power-up can stimulate thermo-mechanical defects, similar to the thermal cycling test. For semiconductor systems involving possible variable conditions resulting from an abrupt shutdown, on/off powering may also reveal design deficiencies associated with ill-defined start-up conditions. Power cycling can also detect certain failures which will not be detectable under thermal cycling test conditions, especially the thermal cycling tests without in-situ reading monitoring.

- 4. Voltage variations. Varying the voltage supplied to an semiconductor system can reveal design margin problems and marginal performance of specific components. It is often combined with testing at temperature limits to increase the detection of marginal conditions.

- 5. Vibration and mechanical shock. Vibration and mechanical shock stressing has traditionally been used to reveal structural support problems. In addition, problems with surface mount solder joints, has also increasingly been addressed using vibration testing. Another form of mechanical impact tests is drop testing.

- 6. Elevated humidity. Elevated humidity testing is usually done in conjunction with high temperature testing to reveal problems with corrosion or high voltage isolation breakdown.

In general, the industry has adopted established test types and conditions defined in JEDEC test standards [JEDEC, 2004]. Examples of the reliability test conditions are shown in Table 1-3. During the reliability study, the test conditions and durations can be selected based on the package material and use conditions. Table 1-4 demonstrates the tests, the failure mechanisms detected by the tests, and the associated reliability models.

Table 1-3 Standard stress tests used in semiconductor package studies

| Test                                                               | Conditions                              | Target failure mechanisms                                                       |

|--------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|

| Preconditioning                                                    | JESD 22A<br>113                         | Cracking, delamination, interconnect damage failures                            |

| Unbiased and biased<br>highly accelerated stress<br>testing (HAST) | JESD22A118                              | Corrosion, delamination, contamination and migration, polymer aging failures    |

| High temperature sto-<br>rage                                      | JESD22A103                              | Diffusion, oxidation, degradation of materials properties, IMC, creep failures. |

| Temperature humidity bias (or no bias) (THB)                       | JESD22A101                              | Corrosion, contamination and migration failures                                 |

| Temperature cycling (TC)                                           | JESD22A104                              | Cracking, deamiantion, fatigue failures.                                        |

| Power thermal cycling                                              | JESDA105                                | Cracking and delamination, fatigue, material degradation failures               |

| Mechanical shock (drop test)                                       | JESD22B104                              | Cracking and delamination and fatigue, brittle fracture failures                |

| Vibration                                                          | JESD22-<br>B103B                        | Solder joint failures. Cracking and impact failures.                            |

| Bending (monotonic and cyclic)                                     | JESD22B113;<br>JS9702                   | Package, solder joint failures, cracking, and delamination.                     |

| Thermal shock (TS)                                                 | JESD22A106                              | Cracking, delamination and fatigue, brittle fracture failures                   |

| Autoclave (PCT)                                                    | JESD22A102                              | Corrosion, delamination and migration, interface contamination failures         |

| Drop Test                                                          | JESD22-B111                             | Failures in the solder joints.                                                  |

| Cyclic Bending Test                                                | JESD22-B114<br>and<br>IPC/JEDEC<br>9702 | Failures in the solder joints.                                                  |

| Board level SJR                                                    | IPC/JEDEC<br>9701                       | Thermo-mechanical solder joint failures.                                        |

Table 1-4 Stress tests and associated failure mechanisms and models

| Test Types                                      | Stress                                       | Mechanisms                                                                                                                                       | Accelerating Variables               | Typical<br>Models                             |

|-------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------|

| Bake                                            | high tempera-<br>ture                        | Diffusion; oxidation; di-<br>electric breakdown; degra-<br>dation of material proper-<br>ties; intermetallic forma-<br>tion; chemical reactions. | temperature                          | Arrhenius                                     |

| Thermal cycle                                   | Temperature range and max temperature.       | Fatigue, delamination or brittle fracture.                                                                                                       | Temperature range, temperature       | Coffin-<br>Manson or<br>Norris –<br>Landzberg |

| Thermal shock                                   | Temperature range                            | Fatigue; delamination; brittle fracture                                                                                                          | Temperature and time                 | Coffin-<br>Manson or<br>Norris –<br>Landzberg |

| Power cycling                                   | Temperature range, max temperature; profiles | Fatigue; generating large<br>thermal gradients; thermal<br>interface material pump<br>out; material degradation;<br>thermal solution wear-out    | N/A                                  | Coffin-<br>Manson or<br>Norris –<br>Landzberg |

| Mechanical<br>shock and<br>vibration            | Mechanical impacts                           | Fatigue; brittle fracture                                                                                                                        | NA                                   | Coffin-<br>Manson                             |

| Temperature and moisture (with or without bias) | High temperature, moisture                   | Corrosion; metal migration; dielectric material degradation; polymer aging                                                                       | Temperature;<br>humidity;<br>voltage | Peck's<br>or<br>generalized<br>Eyring         |

There is a misconception that test durations are usually fixed and that the purpose of stress testing is to pass the test. In contrast, the knowledge-based package reliability studies [Intel, 2000] [Sematech, 2000] focus on collecting failure data. The test dura-

tion for the qualification shall be determined based on the reliability life needs, the reliability models and use conditions. The failure data collected shall be used to predict the reliability life or failure rate for similar packages in the field application.

By definition, the acceleration factor for a given failure mechanism is the ratio of time or cycles it takes for a certain fraction of the population to fail, following the application of stresses or use conditions, to the corresponding time or cycles with more severe stresses or use conditions. The acceleration factor for a combination of stress factors can be the combination of AFs of the individual stress factor, as long as the same failure mechanisms are observed under the stress factors. It is clear that AF shall be associated with certain failure mechanisms. That is required in order to predict the reliability life and failure rate in the field condition, based on the failures observed in the accelerated stress tests.

## 1.4 Failure rate modeling

With a constant failure rate, the failures are not depend on time under the use conditions; those failures can be predicted by collecting the failure data from accelerated stress testing using random samples.

In industrial practice, the high temperature operating life (HTOL) test is usually applied during the qualification tests to estimate the failure rate in the field, with the assumption of expected failure mechanisms associated with temperature and voltage. Chi-square value, based on the number of failures observed from the stress tests, is used replace the number of failures observed. The acceleration factor models be-

tween the test conditions and the field application conditions are critical for the reliability life and failure rate estimation in the application conditions, as well.

When there are zero failures, the Chi-square value used in the failure rate estimation can still help estimate the failure rate. The hypotheses used in the failure rate estimation are:

- (1) Field failures will be created by the operation voltage and temperature; nothing else.

- (2) If there is no failure observed in the stress testing, then a Chi-square value of 5.99/2 can represent the upper bound of the expected number of failures. The failure rate can then be estimated using the value. Clearly, there are questions raised about the approach.

Moreover, field failures can be introduced by many stress factors besides temperature and voltage stresses. There are requests from the industry to provide a failure rate model to reflect the field applications.

## 1.5 Objectives, motivation and scope

This dissertation will assess the reliability performance of the packages, develop and validate the acceleration models used in reliability prediction, and establish the failure rate models. A proper approach for the component failure rate modeling will be proposed. In addition, the reliability performance and prediction for flip chip bump reliability under power cycling conditions will be presented. The results of the study

will help guide the test strategies and predict the life time and the failure rate of semiconductor packages and assemblies in the field applications.

# 2. REVIEW OF FAILURE MECHANISMS IN SEMICON-DUCTOR PACKAGES

#### 2.1 Introduction

A failure mechanism is described as a physical process resulting from the application of chemical, mechanical or electrical loads and leading to failures in semiconductor packages.

Failure mechanisms can be divided into two categories; overstress failures and wearout failures. Overstress failures include structural overloads that might cause structural collapse, e.g. dielectric breakdown. Wear-out failures include failures which

cause degradation in packages over time, e.g. solder joint fatigue failures. The failure mode is how the failure mechanism manifests itself. It is the symptom and not

the root causes. A failure mode might be associated with many failure mechanisms.

Table 2-1 summarizes common known failure mechanisms observed in the semiconductor packages. The failure mechanisms are categorized into several key groups and while some are defect driven, others are simply overstressed or worn-out.

Table 2-1 Categories of failure mechanisms observed in semiconductor packages

| Failure Mechanisms                                                                                               | Failure Mechanism Descriptions                                                                                                                                                                                                                                                                      | Driving Forces                                                                                 | Notable References                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die cracking; thin film or dielectric cracking; passivation cracking.                                            | Failures are shown to be open/short failures or functional failures. Failure mechanisms can be due to manufacturing defects, package design issues or materials used.                                                                                                                               | Temperature cycling; power cycling; moisture and temperature testing.                          | [Merrett et al., 1983]; [Shirley and Blish, 1987]; [Blish and Vaney, 1991]; [Zelenka, 1991]; [Omi et al., 1991]; [Hong, 1992]; [Hu et al., 1995]; [Cory, 2000]; [Chou et al., 2001]; [Nguyen et al., 2002]; [Tsai et al., 2004]                                                                                                                                                                              |

| Interface delamination                                                                                           | Delamination of any interfaces in<br>the package structure. Interface<br>delamination can happen at inter-<br>faces between the die and mold-<br>ing compound, the die and under-<br>fill materials, or between the me-<br>tallization and dielectric materials<br>in the silicon or in substrates. | Temperature cycling; power cycling; temperature and humidity testing; mechanical bending test. | [Doorselaer and Zeeuw, 1990]; [Gestel et al., 1992]; [Emerson et al., 1992]; [Nguyen, 1995]; [Amagi et al., 1995]; [Tanaka et. al., 1999]; [Aihara et al., 2001]; [Harvey et al., 2001]; [Davitt et al., 2001]; [Chung et al., 2002]; [Lin et al., 2003]; [Saitoh et al., 2003]; [Wei et al., 2003]; [Kwon et al., 2004]; [Tsao et al., 2004]; [Kwon et al., 2005]; [Braun et al., 2006]; [Son et al., 2007] |

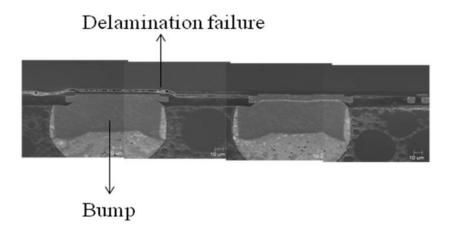

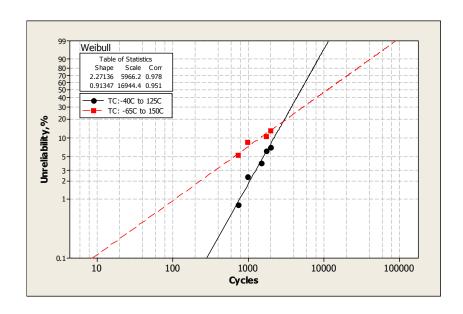

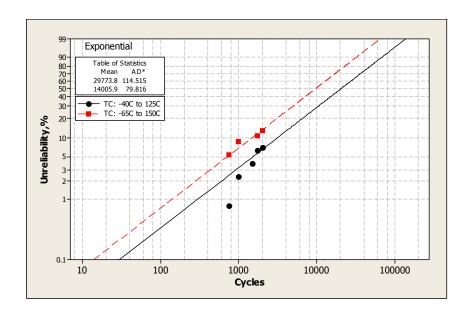

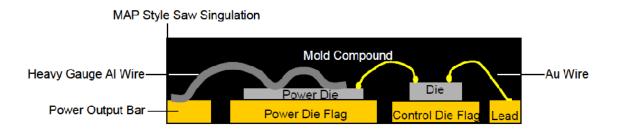

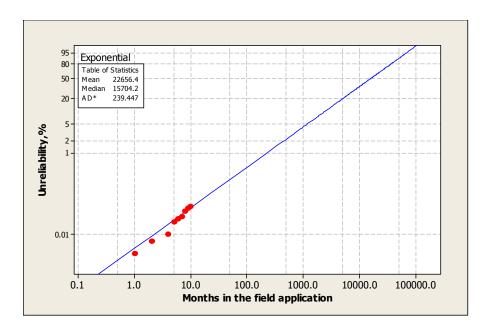

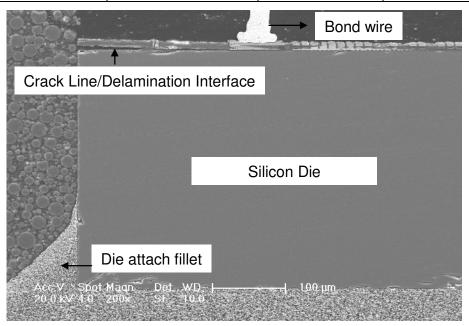

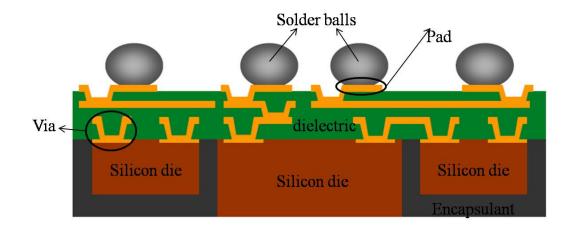

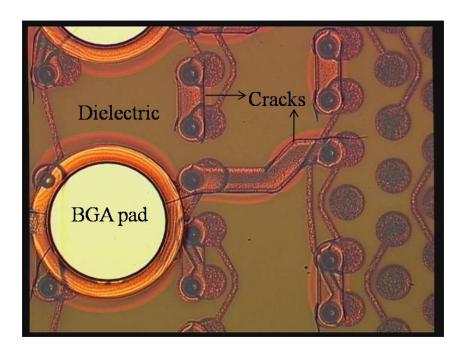

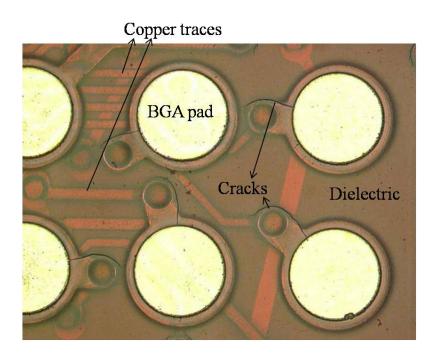

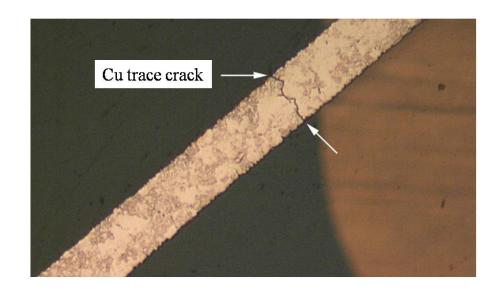

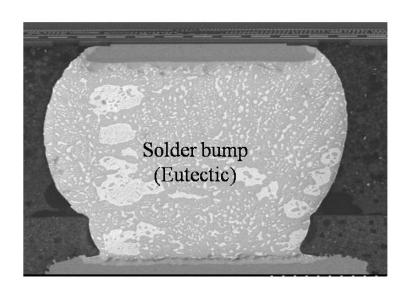

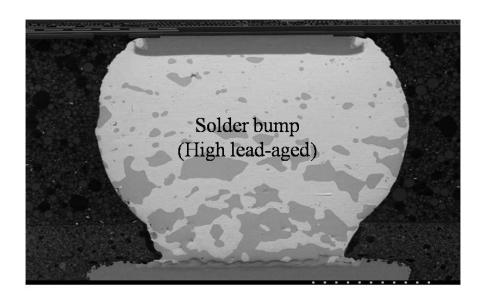

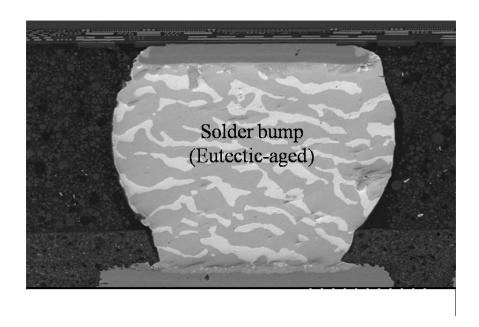

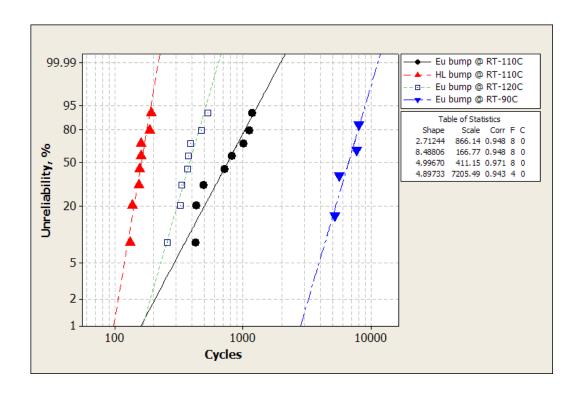

| Package cracking including substrate cracking, underfill cracking, solder mask cracking, mold compound cracking. | The cracks can be observed in the package body or internal "elements". Package cracking might be induced by interface delamination failures.                                                                                                                                                        | Temperature cycling; power cycles; temperature and humidity testing; mechanical bending.       | [Zelenka, 1991]; [Amagai, 1995]; [Dias et al., 1997]; [Ahn et al., 2000]; [lin, 2005]; [Cui, 2005];                                                                                                                                                                                                                                                                                                          |