### ABSTRACT

Dissertation Title: THE DEVELOPMENT OF COST AND SIZE ANALYSIS FOR THE ASSESSMENT OF EMBEDDED PASSIVES IN PRINTED CIRCUIT BOARDS Bevin T. Etienne, Doctor of Philosophy, 2005 Dissertation directed by: Associate Professor Dr. Peter Sandborn

Department of Mechanical Engineering

Passive components are electrical components that do not provide amplification or gain. The primary functions of passive components are to manage buses, bias, decouple power and ground (bypass), filter, tune, convert, sense and protect. In 2001, passive devices accounted for 91% of all components, 41% of board area and 92% of all solder joints in an electronic system but only 2.6% were integrated in some fashion. The integrated circuit industry is achieving faster speeds by shrinking technology. This dictates that the passive solution must also shrink. In addition, the need to drive out every cent of costs, improve product reliability and the high passive to active ratios have motivated system manufacturers to consider higher levels of passive integration. These factors have increased interest in embedded passives.

This research examines the size and cost tradeoffs associated with the use of embedded passive technology for resistors and capacitors, and creates the models and methodology necessary to determine the coupled size/cost impact of embedding passives. It also examines the effects of embedding resistors on profit margin and throughput. A version of the model for performing tradeoff analyses is delivered via the CALCE Consortium and used by board manufacturers and system designers at this time. The models developed have also been used to determine the optimal number of passive devices to embed in a given system by implementing them within a Multi-Population Genetic Algorithm (MPGA). Boards from several different applications are analyzed to demonstrate the applicability of the models and the optimization approach.

The effect of board size on the optimum embedded passive solution was studied and an assessment of whether better system solutions can be found was performed. The analysis has shown that the system size limitation when embedded passives are used is not only dependent on the quantity, type, and electrical properties of the embeddable components, but is, in fact, more dependent on layout constraints associated with the placement of the non-embeddable parts. Studies indicate that the higher the embeddable passive density, the greater the probability that placement can be improved when passives are embedded.

## THE DEVELOPMENT OF COST AND SIZE ANALYSIS FOR THE ASSESSMENT OF EMBEDDED PASSIVES IN PRINTED CIRCUIT BOARDS

by

Bevin Thomson Etienne

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in fulfillment of the requirements for the degree of Doctor of Philosophy 2005

#### **Advisory Committee:**

Associate Professor Dr. Peter A. Sandborn, Chair (Advisor) Professor Dr. Shapour Azarm Associate Professor Dr. David Bigio Associate Professor Dr. Jeffrey Hermann Professor Dr. Vincent Brannigan ©Copyright by

Bevin Thomson Etienne

2005

## **DEDICATION**

To my parents

#### ACKNOWLEDGEMENTS

I would like to take this opportunity to thank the many people who have contributed positively in one way or another in my quest to achieving this academic milestone. Firstly I would like to thank my advisor Associate Professor Peter Sandborn for granting me the opportunity to do this research under his guidance. Whenever things seem to approach a dead end he would stop and back track without loosing sight of the big picture to find ways of moving forward in this research. His advise, patience and dedication towards the completion of this work is greatly appreciated. Next I would like to thank my committee members, Professor Vincent Brannigan, Professor Shapour Azarm, Associate Professor Jeffrey Herrmann, and Associate Professor David Bigio for their advice and comments during my proposal. I am grateful for the tough but fair critique of this research by my committee members, which has brought out hidden qualities in me that will be of great benefits in my professional career. I would like to extend special thanks to Professor Davinder K. Anand for the support and encouragement he has given me over the past few years. I wish to thank the CALCE CENTER and Electronic System Cost Modeling Laboratory for equipping me with the facilities to accomplish this work. I wish to acknowledge the members of the Advanced Embedded Passives Technology (AEPT) Consortium - NCMS, ITRI, 3M, Compaq, Delphi Delco Electronics, Dupont Photopolymer & Electronic Materials, Dupont High Performance Films, ESI, Foresight Systems, MacDermid, Merix Corporation, MicroFab, Nortel Networks, ORMET Corporation, and Sanmina; the members of the NEMI Passive Components Technology Working Group; Richard Carbonneau from Storage Technology Corporation, and Matthew Realff from Georgia Tech for their inputs and comments on this work. I also wish to thank David Carey at Portelligent for providing the SENDO mobile phone data used in the analysis.

I wish to thank all the past and present students of the Electronic System Cost Modeling Laboratory who have contributed to this work. I would like to thank my friends, Ayodale Deveneaux, Arindam Goswami, Daniel Becker, Daniel Ragan, Derya Calhan, Harish Baskaran, Lawrence Salzano, Pameet Singh, Nicolas McMorris, Subroto Gunawan, Ivan Tong, and Zhen Shi for their support and encouragement over the past four years. I wish to extend my deepest gratitude to my parents for their unconditional love and support throughout my life and my brothers Dorian, Brentnol, Michael, and Gladstone, and my sisters Carol and Doreen for their unyielding support of what I do. I wish to acknowledge my dear fiancée, Kisha Lashley for her encouragement and support in this research. I also wish to acknowledge the encouragement and support from my uncles Balthazar Barrie, Simon Francis and their families, my aunt Seraphine Augustine and family and my cousins Vincia, Margaret, Brian, Peter, and Anne-Marie. Last but not least I will like to give thanks to the Almighty Creator for giving me the health, wisdom, knowledge and understand to carry on through life.

# TABLE OF CONTENTS

| DEDICATION                                          | ii  |

|-----------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                    | iii |

| LIST OF TABLES                                      | ix  |

| LIST OF FIGURES                                     | X   |

| CHAPTER 1 INTRODUCTION                              | 1   |

| 1.1 Passive Components                              | 1   |

| 1.2 Passive Growth                                  | 3   |

| 1.3 Embedded Passives (EPs)                         | 6   |

| 1.3.1 Embedded Resistors                            | 8   |

| 1.3.2 Embedded Capacitors                           | 10  |

| 1.3.3 Embedded Inductors                            | 11  |

| 1.3.4 Embedded Passive Advantages                   | 12  |

| 1.3.5 Specific Applications                         | 12  |

| 1.4 Embedded Passive Economics                      | 14  |

| 1.5 Dissertation Overview                           | 15  |

| CHAPTER 2 EMBEDDED PASSIVE COST/SIZE MODEL          | 18  |

| 2.1 Model Development                               | 19  |

| 2.1.1 Existing Embedded Passives Cost Modeling Work | 22  |

| 2.1.2 Size/Cost Model Description                   | 25  |

| 2.1.3 Profit Margin/Throughput Analysis             | 33  |

| 2.2 Summary                                         | 45  |

| CHAPTER 3 COST/SIZE ANALYSIS CASE STUDIES           | 47  |

| 3.1 Analysis of the Application Results                               | 49   |

|-----------------------------------------------------------------------|------|

| 3.1.1 Picocell Board Application                                      | 49   |

| 3.1.2 NEMI Hand-Held Product Sector Emulator                          | 53   |

| 3.1.3 Fiber Channel Card                                              | 55   |

| 3.1.4 Generalization of Embedded Bypass Capacitor Results             | 56   |

| 3.2 Optimizing Embedded Passive Content                               | 57   |

| CHAPTER 4 OPTIMIZATION OF EMBEDDED PASSIVE CONTENT IN A SYS           | STEM |

|                                                                       | 60   |

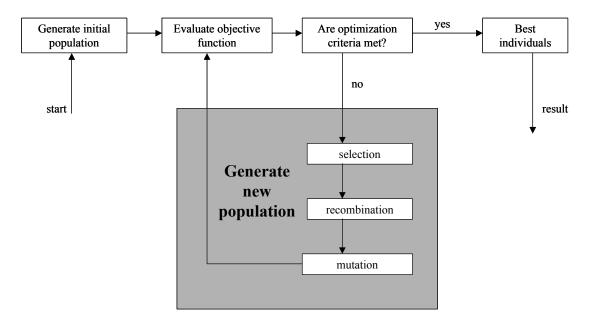

| 4.1 Brief Overview of Genetic Algorithms (GAs)                        | 60   |

| 4.1.1 The Difference Between GAs and Traditional Optimization Methods | 63   |

| 4.1.2 Multi-Population Genetic Algorithm (MPGA)                       | 65   |

| 4.2 Implementation of a Multi-Population Genetic Algorithm            | 66   |

| 4.2.1 Objective Function for Optimization of Embedded Passive Content | 66   |

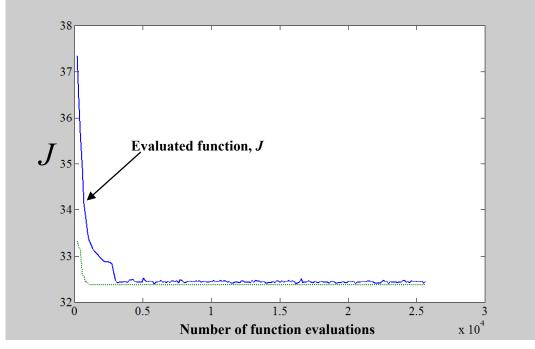

| 4.2.2 NEMI Hand Held Application Example                              | 67   |

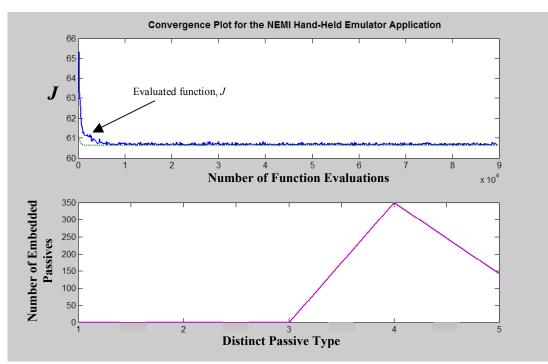

| 4.3 Analysis of MPGA Results for the NEMI Hand-Held Emulator          | 67   |

| 4.3.1 MPGA Optimization                                               | 68   |

| 4.3.2 Verification of MPGA Results                                    | 69   |

| 4.4 Summary                                                           | 73   |

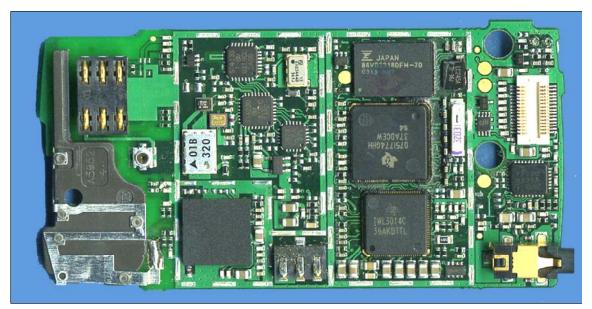

| CHAPTER 5 SENDO GSM M550 CELL PHONE CASE STUDY                        | 74   |

| 5.1 Product Description                                               | 74   |

| 5.2 Results and Discussion                                            | 77   |

| 5.3 Summary                                                           | 83   |

| CHAPTER 6 ANALYZING SYSTEM SIZE/COST TRADEOFF                         | 85   |

| 6.1 Determining Optimal Embedded Content for Selected Fixed Board Sizes86              |

|----------------------------------------------------------------------------------------|

| 6.2 General Insights Gained 102                                                        |

| 6.3 Application-specific insights gained 104                                           |

| CHAPTER 7 SUMMARY AND CONCLUSIONS 106                                                  |

| 7.1 Summary 106                                                                        |

| 7.2 Contributions of this Work 107                                                     |

| 7.3 Discussion of Modeling Work and Modeling Contributions 107                         |

| 7.3 Discussion of Global Contributions 110                                             |

| 7.3.1 Contribution #1: General Result for the Economics of Embedding Bypass            |

| Capacitors 111                                                                         |

| 7.3.2 Contribution #2: Determining and Demonstrating the Advantages of                 |

| Optimizing Embedded Passive Content 112                                                |

| 7.3.3 Contribution #3: Determining the Applicability and Limitations of the Existing   |

| Modeling Approaches 113                                                                |

| 7.4 Future Work 114                                                                    |

| 7.4.1 Switching noise analysis 114                                                     |

| 7.4.2 Optimization of resistive material selection 115                                 |

| 7.4.3 Trim/no trim decisions and reworks consideration 115                             |

| 7.4.4 Conversion of double-sided printed circuit board to single-sided printed circuit |

| board115                                                                               |

| 7.4.5 Determining the best optimization method 116                                     |

| Appendix A – Publications Associated with this Dissertation 117                        |

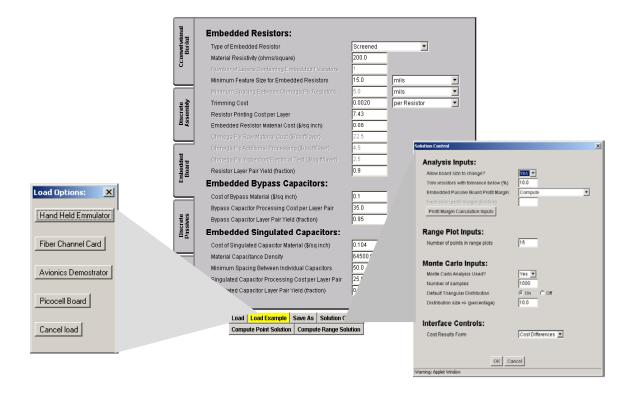

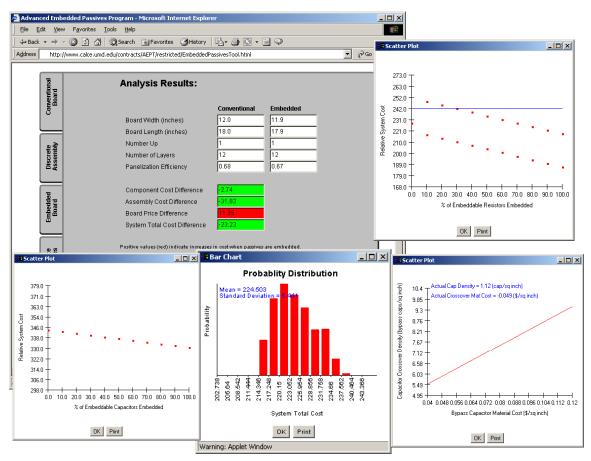

| Appendix B – Embedded/Integrated Passives Cost Analysis Software 118                   |

| Appendix C – Input and Output Variables for the Panel Trimming Model | 124 |

|----------------------------------------------------------------------|-----|

| Appendix D – Implementation of Multi-Population Genetic Algorithm    | 128 |

| GLOSSARY                                                             | 130 |

| REFERENCES                                                           | 133 |

## LIST OF TABLES

| 1-1 Passive component's physical form comparison                          | 2  |

|---------------------------------------------------------------------------|----|

| 1-2 Passive-to-active ratio of recent products                            | 4  |

| 1-3 Passive array forecast                                                | 5  |

| 1-4 Companies producing embedded resistor material technologies           | 9  |

| 1-5 Companies producing embedded capacitor material technologies          | 11 |

| 1-6 Projected market share of embedded resistors and capacitors in 2004   | 14 |

| 3-1 Picocell board, Hand-Held emulator and Fiber Channel Card application |    |

| characteristics                                                           | 48 |

| 3-2 Data assumptions used in modeling                                     | 48 |

| 4-1 Parameters for MPGA Example                                           | 67 |

| 5-1 SENDO M550/GPRS phone main board characteristics                      | 76 |

| 5-2 SENDO M550/GPRS main board system cost for varying combinations of    |    |

| embedded passive components                                               | 78 |

## LIST OF FIGURES

| 1-1 Growth of passive components in discrete systems                         |   |

|------------------------------------------------------------------------------|---|

| 1-2 Cross-sectional view of a printed circuit board                          |   |

| 1-3 Real estate savings and size reduction by embedding passives             |   |

| 1-4 Embedded resistor                                                        |   |

| 1-5 Additive and subtractive methods of embedded resistor fabrication        |   |

| 1-6 Various cuts used by industry for obtaining the resistor value           |   |

| 1-7 Embedded capacitor                                                       |   |

| 1-8 Embedded inductor design                                                 |   |

| 2-1 Model developed for the analysis of embedded passive cost and size       | ļ |

| impact on electronic systems                                                 |   |

| 2-2 Basics of Embedded resistor laser trimming process                       |   |

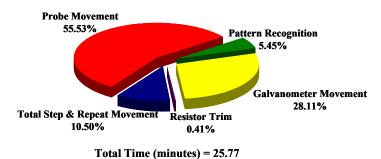

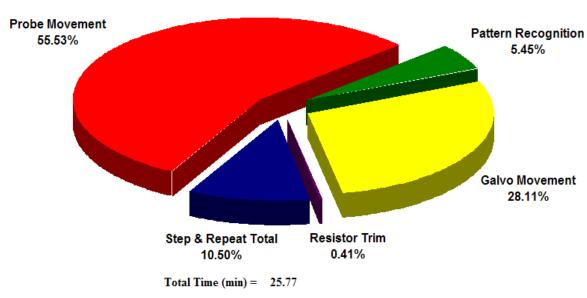

| 2-3 Cycle time for the SENDO M550 GSM cell phone bare board                  | l |

| manufacture                                                                  |   |

| 2-4 Cycle time for the NEMI Hand-Held bare board product sector emulator     | • |

|                                                                              |   |

| 2-5 Effects of trimmed resistor on panel trim time for embedded passive bare | , |

| board design                                                                 |   |

| 2-6 Laser trimming equipment utility distribution for the NEMI Hand-Held     | l |

| application on a 18 x 24 inch panel                                          |   |

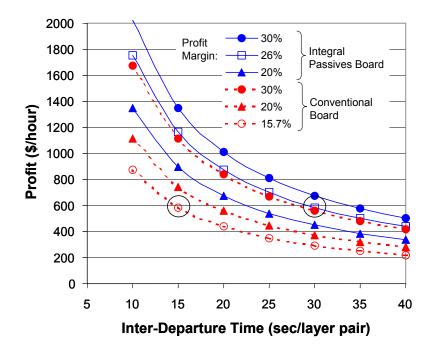

| 2-7 The relationship between profit margin and production inter-departure    | , |

| time for conventional and embedded passive board fabrication                 |   |

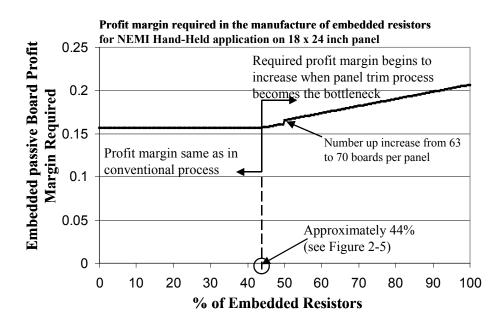

| 2-8 Effects of embedding resistor on profit margin for the NEMI Hand-Held    | l |

| application                                                                    |

|--------------------------------------------------------------------------------|

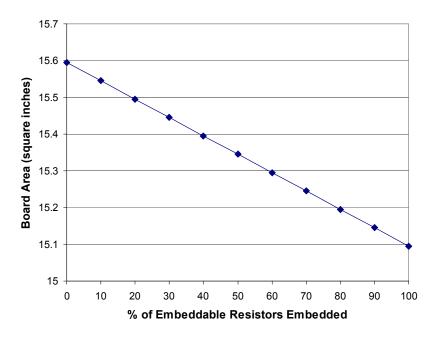

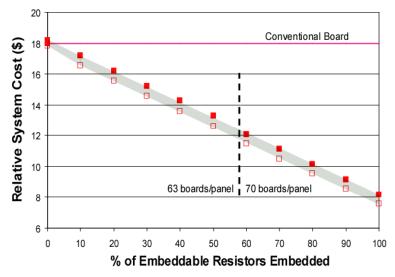

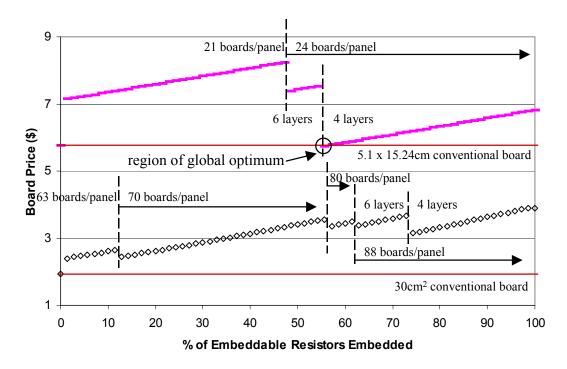

| 3-1 The economics of embedded resistors for the picocell board application     |

| 3-2 Board size decrease with resistor embedding for the picocell board         |

| application                                                                    |

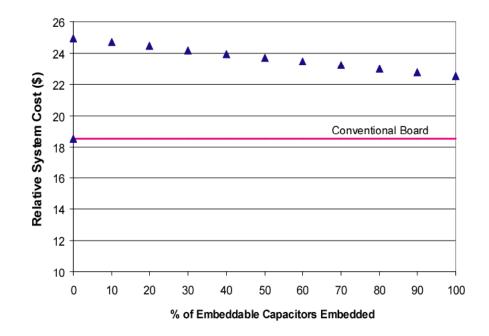

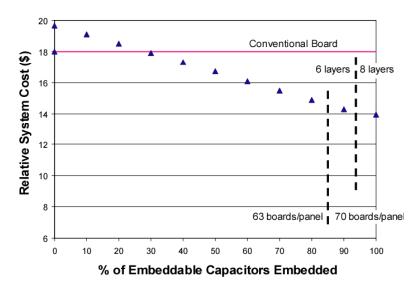

| 3-3 Capacitor embedding for the picocell application                           |

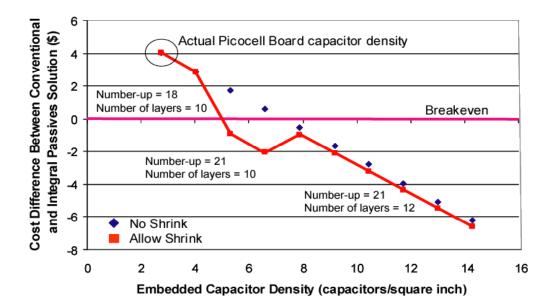

| 3-4 The impact of embeddable capacitor density on system cost for the          |

| picocell board application                                                     |

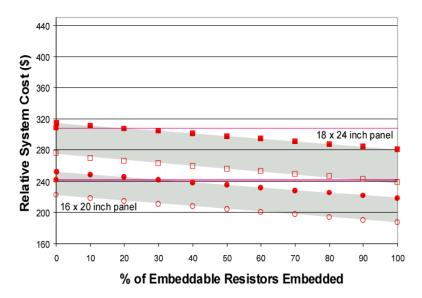

| 3-5 The economics of embedded resistors for the NEMI Hand-Held product         |

| sector emulator                                                                |

| 3-6 Capacitor embedding for the NEMI Hand-Held product sector emulator -       |

| 3-7 The economics of embedded resistors for the fiber channel card             |

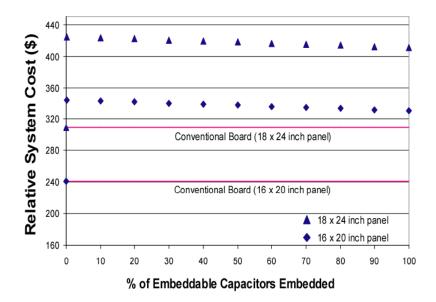

| 3-8 Capacitor embedding for the fiber channel card                             |

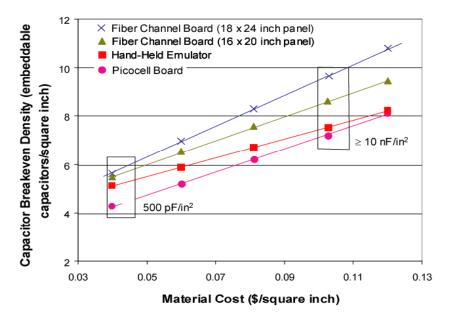

| 3-9 Bypass capacitor breakeven densities as a function of dielectric material  |

| replacement cost                                                               |

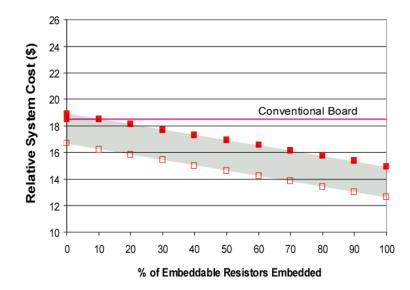

| 3-10 Effects of embedding embeddable resistors on the board price on NEMI      |

| Hand-Held emulator board                                                       |

| 4-1 Structure of a single population genetic algorithm                         |

| 4-2 Convergence plot for NEMI Hand-Held application                            |

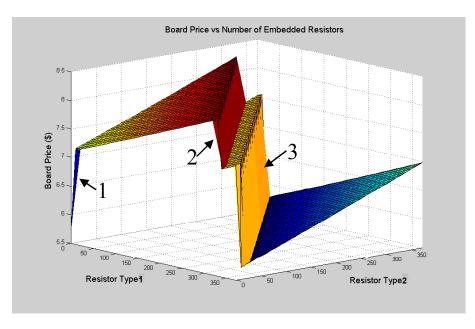

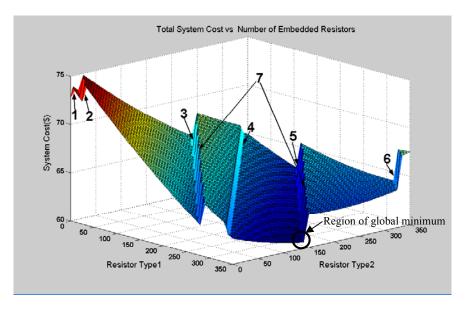

| 4-3 Surface plot showing the effects of embedding resistors on board price for |

| the NEMI Hand-Held emulator                                                    |

| 4-4 Surface plot of optimization result for system cost on the NEMI Hand-      |

| Held emulator                                                                  |

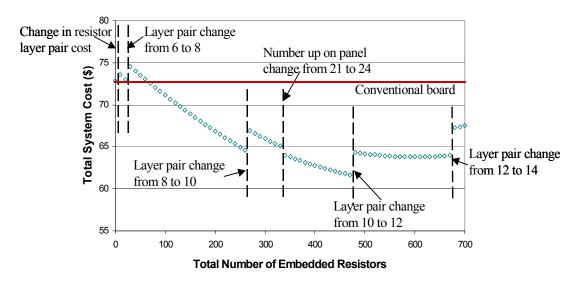

| 4-5 Cross section of the surface plot presented in Figure 4-4 for total system |

| cost                                                                                             |

|--------------------------------------------------------------------------------------------------|

| 5-1 SENDO M550                                                                                   |

| 5-2 Main board for SENDO M550 cell phone showing the majority of the                             |

| electronics in the product                                                                       |

| 5-3 Existing simple model                                                                        |

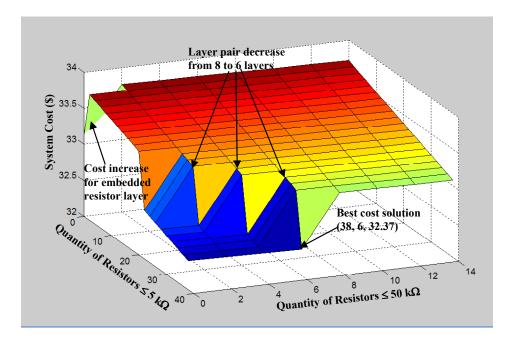

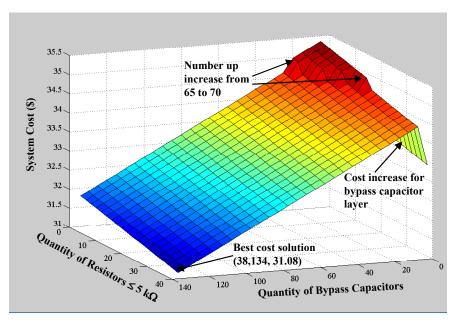

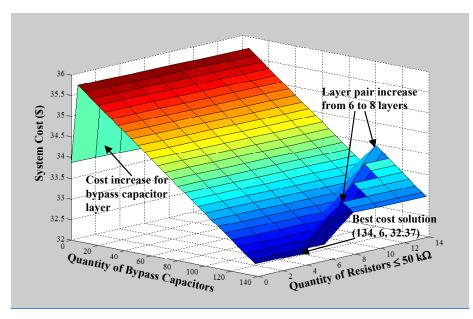

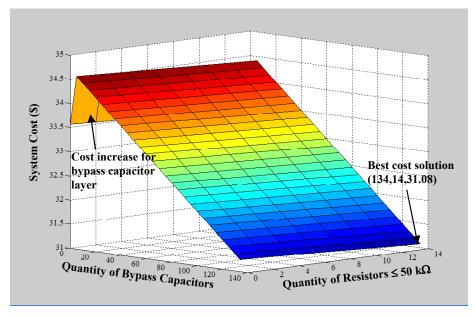

| 5-4 Surface plot showing system cost as a function of embedding resistors $\leq 5$               |

| k $\Omega$ and resistors $\leq$ 50 k $\Omega$ for the best cost solution within the new model    |

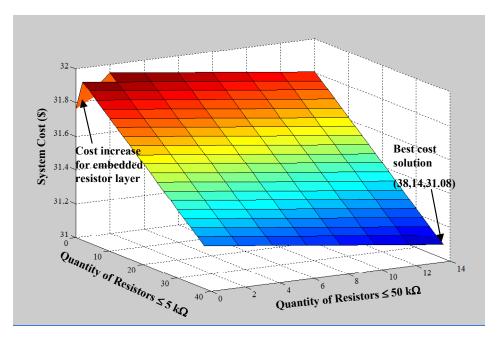

| 5-5 Surface plot showing system cost as a function of embedding resistors $\leq 5$               |

| k $\Omega$ and resistors $\leq$ 50 k $\Omega$ for the best cost solution within the simple model |

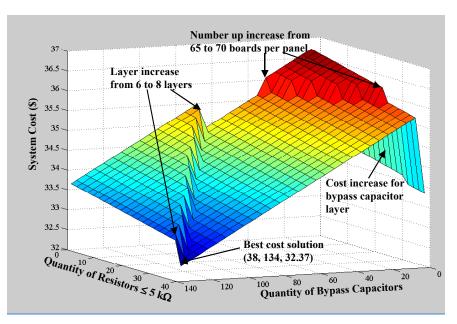

| 5-6 Surface plot showing system cost as a function of embedding resistors $\leq 5$               |

| $k\Omega$ and bypass capacitors for the best cost solution within the new model                  |

| 5-7 Surface plot showing system cost as a function of embedding resistors $\leq 5$               |

| $k\Omega$ and bypass capacitors for the best cost solution within the simple model               |

| 5-8 Surface plot showing system cost as a function of embedding resistors $\leq$ 50              |

| k $\Omega$ and bypass capacitors for the best cost solution within the new model                 |

| 5-9 Surface plot showing system cost as a function of embedding resistors $\leq$ 50              |

| k $\Omega$ and bypass capacitors for the best cost solution within the simple model              |

| 5-10 Convergence plot for the SENDO M550 GSM cell phone application                              |

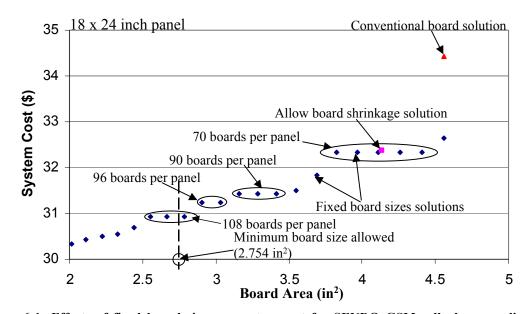

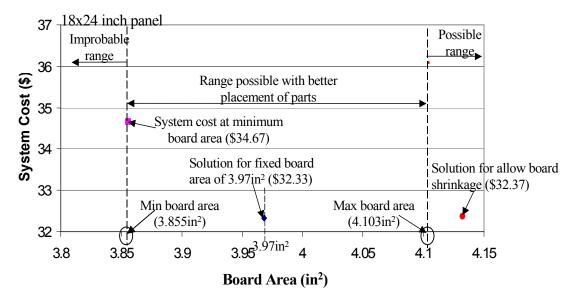

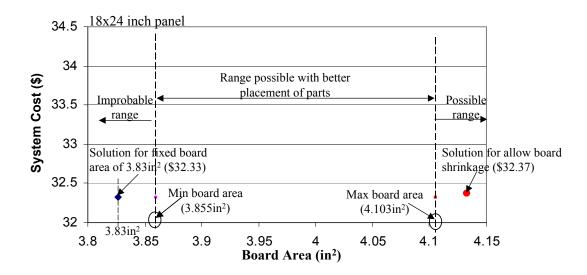

| 6-1 Effects of fixed board sizes on system cost for SENDO GSM cell phone                         |

| application                                                                                      |

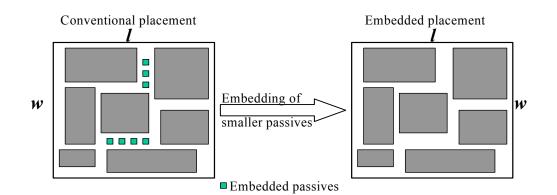

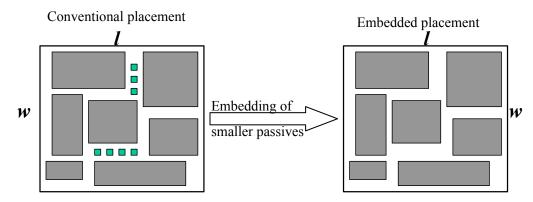

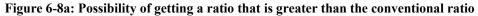

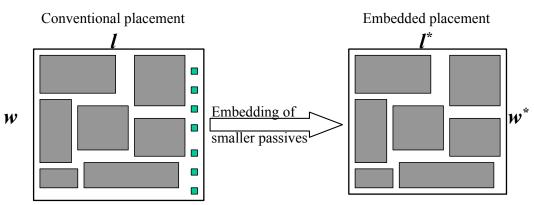

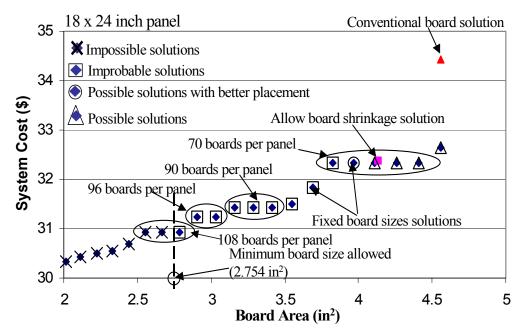

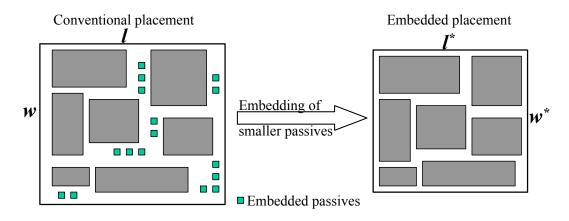

| 6-2 Effects of embedding smaller devices on packaging density                                    |

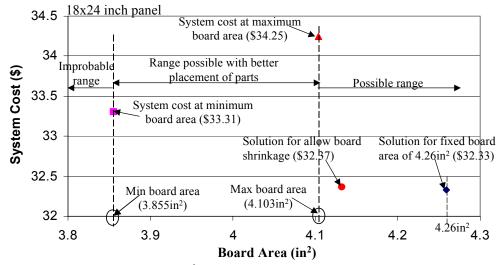

| 6-3 Effects of board size 4.26 inch <sup>2</sup> on system cost for SENDO application            |

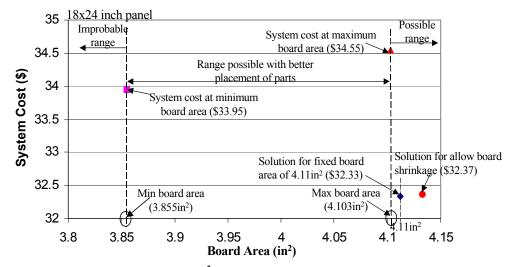

| 6-4 Effects of board size 4.11 inch <sup>2</sup> on system cost for SENDO application | 93       |

|---------------------------------------------------------------------------------------|----------|

| 6-5 Effects of board size 3.97 inch <sup>2</sup> on system cost for SENDO application | 94       |

| 6-6 Effects of board size 3.83 inch <sup>2</sup> on system cost for SENDO application | 95       |

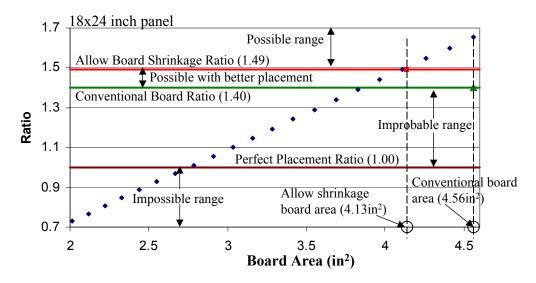

| 6-7 Ratio analysis for fix board areas for the SENDO GSM cell phone                   |          |

| application                                                                           | 95       |

| 6-8 Possibility of getting ratios less than and greater than the conventional         |          |

| ratio                                                                                 | 96       |

| 6-9 Possible and impossible board areas for the SENDO GSM application                 | 97       |

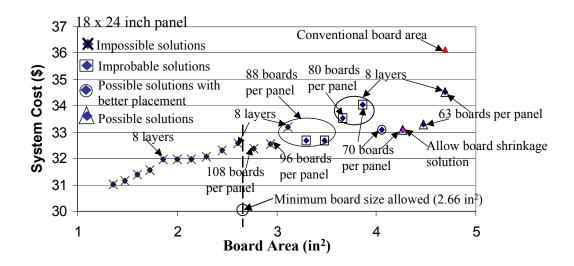

| 6-10 Effects of board size on system cost for the NEMI Hand-Held application          |          |

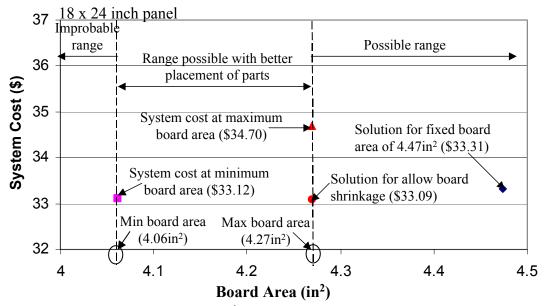

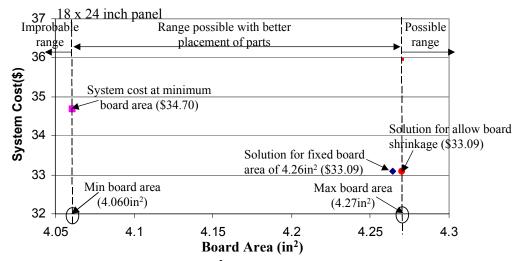

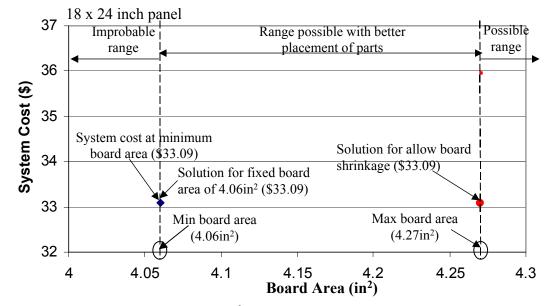

| 6-11 Effects of board size 4.47 inch <sup>2</sup> on system cost for NEMI application | 98<br>99 |

| 6-12 Effects of board size 4.26 inch <sup>2</sup> on system cost for NEMI application | 100      |

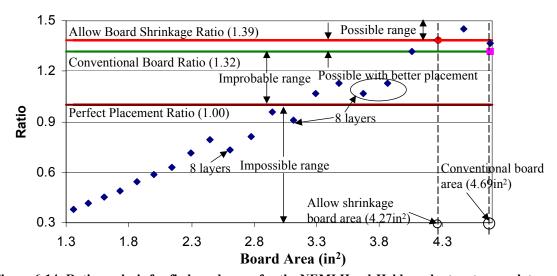

| 6-13 Effects of board size 4.06 inch <sup>2</sup> on system cost for NEMI application | 100      |

| 6-14 Ratio analysis for fix board areas for the NEMI application                      | 101      |

| 6-15 Possible and impossible areas for the NEMI application                           | 102      |

| 6-16 Effects of better placement by embedding passives                                | 105      |

| 7-1 Estimated growth rate of embedded passives compared with other                    |          |

| packaging technologies                                                                | 111      |

### **CHAPTER 1 INTRODUCTION**

#### **1.1 Passive Components**

By definition, passive components are devices that dissipate power or store energy, as opposed to active devices, such as transistors, that generate power gain [1]. Traditional passives are discrete devices, singular components enclosed in a single case, that are either through-hole or surface mounted onto a substrate. They are commonly referred to as "glue components" since they electrically "glue" integrated circuits (ICs) together to make the system. The most common examples of passive components are resistors, capacitors and inductors and their primary functions are to manage buses, bias, decouple power and ground (bypass), filter, tune, convert, sense and protect. Passive components are manufactured in many physical forms including discrete devices, integrated passive devices (arrays or networks), and embedded passives. Table 1-1 compares the various physical forms.

|                   | Discrete                                                                                                         | Arrays and<br>Networks                                                                                                                                                                                                                                                                                                                                   | Integrated Passive<br>Devices (IPD)                                                                                                                                                                                                                                                                                      | Embedded (Integral)<br>Passives                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Definition        | A single passive<br>element<br>(capacitor,<br>resistor or<br>inductor) in a<br>leaded or surface-<br>mount case. | Passive arrays<br>combine multiple<br>passive elements of<br>like function (e.g.,<br>all capacitors or all<br>resistors) in a single<br>surface-mount case.<br>Networks combine<br>passives or more<br>than one function<br>(e.g., capacitors +<br>resistors) in a single<br>surface-mount case.<br>A network typically<br>contains 4 to 12<br>elements. | Multiple passive<br>elements of more than<br>one function and<br>possibly a few active<br>elements (e.g., resistors<br>+ capacitors + diodes)<br>in a single surface<br>mount or ship scale<br>package. Typically an<br>IPD contains more than<br>20 elements. IPDs<br>may also be referred to<br>as "super components." | Passive devices that are<br>buried in the substrate<br>material rather than<br>being mounted on top.                                                                                            |

| Cost              | Good–The<br>benchmark for all<br>other<br>technologies.                                                          | Better when local<br>densities have 4 to 8<br>devices close<br>together.                                                                                                                                                                                                                                                                                 | Better when high local<br>densities are<br>application specific                                                                                                                                                                                                                                                          | Better when average<br>component density is<br>above 3 devices/cm2.<br>Cost is panel size<br>dependent.                                                                                         |

| Size              | Good–Board area<br>required for each<br>and every device                                                         | Better–50% and<br>greater board area<br>savings over<br>discretes.                                                                                                                                                                                                                                                                                       | Better–Application<br>specific IPDs can<br>replace dozens of<br>components.                                                                                                                                                                                                                                              | Best–No surface board<br>area required because<br>the devices are buried.                                                                                                                       |

| Performance       | Good–Self-<br>resonates at low<br>frequencies.                                                                   | Good–Self-resonates<br>at low frequencies.                                                                                                                                                                                                                                                                                                               | Better–Qualified out to<br>several gigahertz<br>(GHz).                                                                                                                                                                                                                                                                   | Best–Ideal components;<br>when buried underneath<br>the integrated circuit<br>(IC), it serves mainly to<br>decrease lead length and<br>avoid build up<br>inductance of the<br>connection loops. |

| Reliability       | Good–Heavy use<br>of solder joints                                                                               | Better–Reduces solder joints slightly.                                                                                                                                                                                                                                                                                                                   | Better–Significantly reduces solder joints.                                                                                                                                                                                                                                                                              | Best–Elimination of solder joints.                                                                                                                                                              |

| Flexibility       | Best–Flexible for<br>both design and<br>manufacturing                                                            | Better than IPDs and embedded passives.                                                                                                                                                                                                                                                                                                                  | Better than embedded passives.                                                                                                                                                                                                                                                                                           | Good–Requires<br>modeling and<br>simulation.                                                                                                                                                    |

| Time to<br>Market | Best–Flexibility<br>allows quick<br>turns.                                                                       | Better–Simple quad<br>and octal arrays can<br>be designed in<br>quickly                                                                                                                                                                                                                                                                                  | Good–IPDs require<br>additional design<br>iterations for<br>wireability.                                                                                                                                                                                                                                                 | Fair–Most board shops<br>require at least 5 to 7<br>days to fabricate an<br>embedded passives<br>board.                                                                                         |

| Availability      | Best–Highly<br>available from<br>multiple sources.                                                               | Better–Standard<br>parts from multiple<br>suppliers.                                                                                                                                                                                                                                                                                                     | Better–Non-standard<br>parts from multiple<br>suppliers.                                                                                                                                                                                                                                                                 | Fair–Few suppliers.                                                                                                                                                                             |

| Values            | Best–All values<br>available at<br>commodity<br>prices.                                                          | Better–Thick film<br>arrays offer high<br>values.                                                                                                                                                                                                                                                                                                        | Good–Thin films have<br>limited capacitor<br>values.                                                                                                                                                                                                                                                                     | Good–Currently limited to low values                                                                                                                                                            |

| Tolerances        | Best–Tight<br>tolerances at<br>commodity<br>prices.                                                              | Better–Both offer<br>tight tolerances.                                                                                                                                                                                                                                                                                                                   | Better–Thin films offer tight tolerances.                                                                                                                                                                                                                                                                                | Good–Loose tolerance,<br>generally 5 to 10%.                                                                                                                                                    |

Table 1-1: Passive component's physical forms comparison [2]

#### **1.2 Passive Growth**

In 2000, the passive component market share in the US was estimated at \$17.9 billion [3]. It is a huge, multi-billion dollar business, supporting electronic products in automotive, telecommunications, computer and consumer industries, for digital, analog and mixed signal applications. The resistor market in North America is expected to continue to be driven by the telecommunications and computer industries. Currently, Southeast Asia holds the largest share of the market at 47.1%, and it is driven by strong demand in the consumer electronics industry [4]. The US demand for passive components is forecast to increase 3.7 percent per year to \$21.4 billion in 2005 [3].

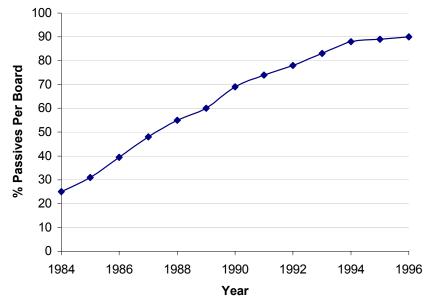

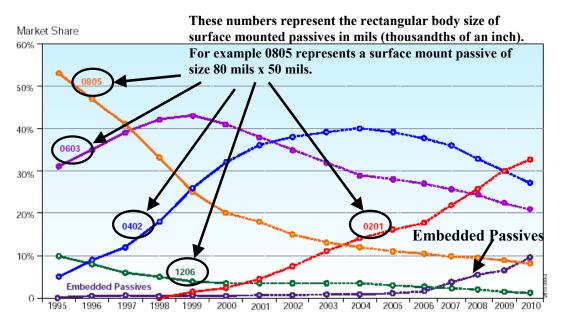

Passive components are continuing to increase in use in electronic systems. There are a large number of passive components that are used in consumer electronic products such as VCRs, camcorders, television tuners, and other communication devices. Many analysts believed discrete passives would "integrate" away into integrated circuits, however, exactly the opposite has occurred [5]. In 1984, passive devices represented 25% of all components on printed circuit boards; by 1998 this fraction grew over 90% (Figure 1-1). In 2001, passive devices accounted for 91% of all components, 41% of the board area and 29% of all solder joints [6].

Figure 1-1: Growth of passive components in electronic systems [7]

Studies have shown that the number of passive components is still greater than 80% of the total part count (e.g., Figure 1-1) and the passive-to-active ratios continue to rise in applications like PDAs, cellular phone and other portable electronic devices [8]. Table 1-2 also illustrates the passive-to-active ratio in recent products.

| System                    | <b>Total Passives</b> | Total Ics | Ratio |

|---------------------------|-----------------------|-----------|-------|

| Cellular Phones           |                       |           |       |

| Ericsson DH338 Digital    | 359                   | 25        | 14:1  |

| Ericsson E237 Analog      | 243                   | 14        | 17:1  |

| Philips PR93 Analog       | 283                   | 11        | 25:1  |

| Nokia 2110 Digital        | 432                   | 21        | 20:1  |

| Motorola Mrl 1.8 GHz      | 389                   | 27        | 14:1  |

| Casio PH-250              | 373                   | 29        | 13:1  |

| Motorola StarTAC          | 993                   | 45        | 22:1  |

| Matsushita NTT DoCoMo     | 492                   | 30        | 16:1  |

| Consumer Portable         |                       |           |       |

| Motorola Tango Pager      | 437                   | 15        | 29:1  |

| Casio QV10 Digital Camera | 489                   | 17        | 29:1  |

| 1990 Sony Camcorder       | 1226                  | 14        | 33:1  |

| Sony Handy Cam DCR-PC7    | 1329                  | 43        | 31:1  |

| Other Communication       |                       |           |       |

| Motorola Pen Pager        | 142                   | 3         | 47:1  |

| Infotac Radio Modem       | 585                   | 24        | 24:1  |

| Data Race Fax-Modem       | 101                   | 74        | 7:1   |

| PDA                       |                       |           |       |

| Sony Magic Link           | 538                   | 74        | 7:1   |

Table 1-2: Passive-to-active ratio of recent products [9]

Given the steady growth of passive utilization, the drive for miniaturization of electronic systems, the electronics industry has been forced to seek innovative ways to satisfy demands to pack more functionality into less space and reduce costs. The industry has responded by developing smaller discrete passive components and improved efficiencies and automation in the assembly process. One of the solutions to accommodate passive growth is integrating multiple passives together within a single package as networks or arrays of passives. According to a study by Prismark Partners LLC in 1996, 880 billion passive components were built of which only 2.6%, (22.86 billion passive components) were integrated and a more recent study showed that in 2001 alone, approximately 1 trillion passive components were consumed with still only 26 billion, or 2.6%, passive devices integrated in some fashion [6]. This shows that although there has been an increase in the integration of passive the percentage of integration has remained the same over the years. Table 1-3 provides a market forecast for passive arrays through 2004.

|                                     | 2000   |         | 2004   |         |

|-------------------------------------|--------|---------|--------|---------|

|                                     | Units* | Value** | Units* | Value** |

| Resistor Chip Arrays                | 6.60   | \$99.0  | 10.8   | \$140.0 |

| Capacitor Chip Arrays               | 1.47   | \$102.6 | 2.36   | \$145.0 |

| R/C Networks and Arrays (Chips)     | 0.36   | \$33.0  | 0.58   | \$46.6  |

| Total Chip Arrays (Chips)           | 8.43   | \$234.6 | 13.74  | \$331.6 |

| Total Thin Film Arrays and Networks | 0.85   | \$55.0  | 2.0    | \$105.0 |

| Total Arrays (Thick and Thin Film)  | 9.28   | \$289.6 | 15.74  | \$436.6 |

Table 1-3: Passive array forecast [6]

\* Billion

\*\* Million

Integrating passives into arrays and networks can reduce assembly costs and free surface space on substrates, however, the per unit cost of integrated passives remains higher than the discrete passive components they replace. The needs to reduce cost, miniaturization, improved product reliability and the passive to active ratios have brought about interest in embedded passives. Embedded passives (EPs) are buried inside the substrate material, and while EPs will never replace all passive components, they provide a potential advantage for many applications.

#### **1.3 Embedded Passives (EPs)**

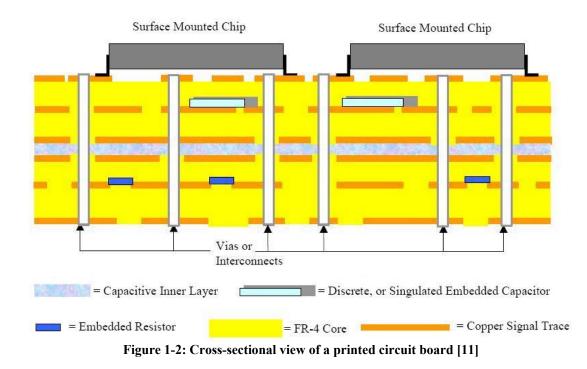

Passives, embedded into a substrate, are considered the Holy Grail in terms of integration [10]. Embedded passives, also known as "integral" passives, are passive components buried within the layers of the interconnecting substrate (the substrate is the electrical interconnection between the components, e.g., a printed circuit board). The substrate could be ceramic, a laminate (e.g., printed circuit board), or a deposited thin film. As long as the passive elements are inside of the substrate, they are called embedded passives. The defining characteristic for embedded passives is the fact that the device does not need to be mounted on or connected to the exposed substrate surface [2]. It provides the ability to free surface space area to add more active devices and has the potential of increasing functionality in small electronic systems. Although capacitors, resistors and inductors are all candidates for embedding, current interests are focusing on capacitors and resistors since they represent the majority of passive devices used on a circuit board. Inductors are currently used in such low quantities, that the equivalent per part cost is too high to incorporate any special processes or materials to make embedding inductors economically viable. The generic single board computer is generally composed of 5% integrated circuits, 4% connectors, 40% capacitors, 33% resistors and 18% miscellaneous parts [12]. Both embedded resistors and capacitors can be fabricated in singulated value form while capacitors can also be manufactured in distributed planar form. Figure 1-2 shows a cross sectional view of a printed circuit board containing

embedded passive components freeing up real estate on the substrate surface, which can be used for integrated circuits for added functionality or the board size can be decreased to obtain a smaller footprint.

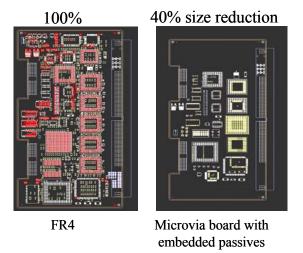

Figure 1-3 shows the real estate savings and size reduction that is possible (in part) by embedding passives.

Figure 1-3: Real estate savings and size reduction by embedding passives (Nortel Networks)

#### 1.3.1 Embedded Resistors

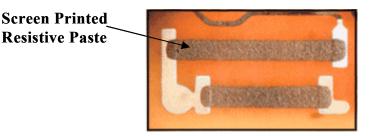

Thin and thick-film technologies are used to manufacture embedded resistors by depositing and pattering layers of resistive material in conjunction with an interconnect line within a substrate as shown in Figure 1-4. Replacing surface mount resistors with

Figure 1-4: Embedded resistor (Ibiden Circuits of America)

embedded resistors aids in achieving faster bus speed by increasing transmission efficiencies. In addition to increasing transmission efficiencies and making available real estate on the board surface, embedded resistors also improve reliability through the elimination of the solder joints and plated through-hole connections.

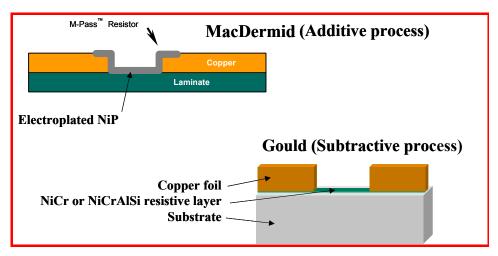

There are two methods for implementing embedded resistors: the additive and the subtractive methods. In the additive method resistive material is either plated or screenprinted onto the inner layer of the substrate. In the subtractive method a layer pair in the printed circuit board is dedicated for the resistive material, material is removed from the layer to form individual resistors via an etching process. Figure 1-5 illustrates both the additive and subtractive resistor methods of fabrication. Table 1-4 highlights companies involved in embedded resistor technologies, the materials they use and their corresponding approach for fabrication.

Figure 1-5: Additive and subtractive methods of embedded resistor fabrication

| Company                             | Technology                        | Approach    |

|-------------------------------------|-----------------------------------|-------------|

| Asahi Kasei Corporation             | Carbon paste (polymer thick film) | Subtractive |

| DuPont                              | Ceramic (polymer thick film)      | Additive    |

| Gould Electronics                   | Thin metal on copper              | Subtractive |

| Ibiden                              | Unknown-internal development      |             |

| MacDermid                           | Plated nickel phosphorus          | Additive    |

| Multiline International Europea, LP | Carbon paste (polymer thick film) | Subtractive |

| Mitsui                              | Thin metal on copper              | Subtractive |

| Ohmega Technologies                 | Nickel phosphorus on copper       | Subtractive |

| Shipley                             | Thin metal on copper              | Subtractive |

Table 1-4: Companies producing embedded resistor material technologies

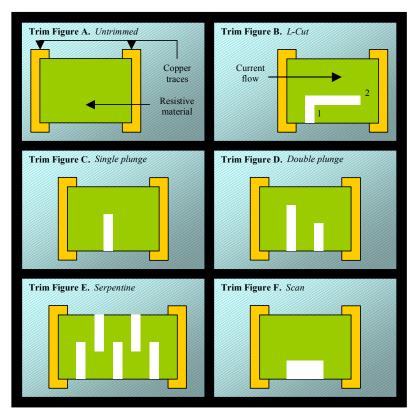

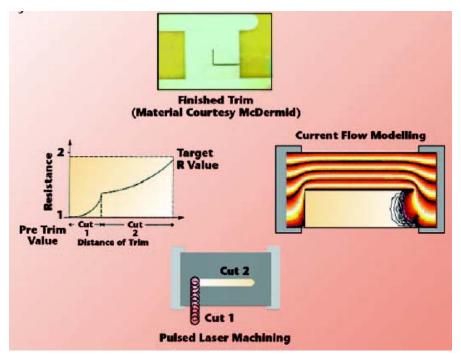

Some embedded system applications may require tight design tolerances on embedded resistor values. Laser trimming of the resistive material on the layer pair achieves these tight tolerances. Figure 1-6 shows various types of laser cuts used to increase the value of embedded resistors and satisfy these tolerances.

Figure 1-6: Various cuts used by industry for obtaining the resistor value [13]

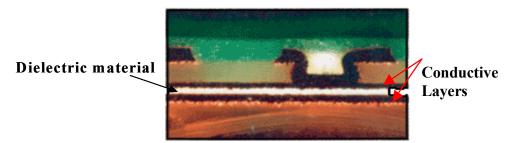

#### 1.3.2 Embedded Capacitors

Embedded capacitors are expected to provide faster clock speeds and manage switching noise in systems. Like embedded resistors they also contribute to the freeing up of real estate on the board surface, board size reduction and reduce signal-travel distances. Embedded capacitors are formed by inserting an insulating dielectric material between two conductive layers in the PCB as shown in Figure 1-7.

Figure 1-7: Embedded capacitor (Ibiden Circuits of America)

There are a wide variety of dielectric materials and technology providers available for embedded capacitor technology. Table 1-5 provides the names of various companies that are involved in embedded capacitor technologies and the materials they manufacture.

| Company        | Technology                                |

|----------------|-------------------------------------------|

| 3M             | Filled resin (sheet)                      |

| Asahi Chemical | Chemical filled paste                     |

| Dupont         | Filled and unfilled polyimide film/copper |

| Dupont         | Polymer thick film                        |

| Dupont         | Filled polyimide paste                    |

| Hitachi        | Chemical filled resin                     |

| Ibiden         | Unknown-internal development              |

| MicroCoatings  | Thin film on dielectric/copper            |

| Mitsui         |                                           |

| Nippon Paint   | Filled resin (liquid and sheet)           |

| Sanmina ZBC    | Filled resin                              |

| Shipley        | Thin film on dielectric/copper            |

| Vantico        | Filled liquid                             |

Table 1-5: Companies producing embedded capacitor material technologies [14]

#### 1.3.3 Embedded Inductors

Embedded inductors are fabricated by forming a spiral out of an interconnect material with fine line capabilities (25-50 micron) small vias (25-50 micron) and thin dielectrics (25-50 microns) as shown in Figure 1-8. Although about 80% of the inductors used in hand-held products are low enough in value (less than 200 nH) and would be small enough in size (2 to 4 mm) that they could be embedded directly into the wiring of

Figure 1-8: Embedded inductor design

a suitable substrate they are not prime candidates for embedding [3]. This is due to the fact that inductors are used in such low quantities that the equivalent per component cost will be too high to incorporate any special processes or materials to embed them into the substrate manufacturing process [15].

Conventional surface mount technology will most likely remain the best design choice for inductors in the foreseeable future. Therefore, inductors are not considered within this research effort.

#### 1.3.4 Embedded Passive Advantages

Driven by performance, size and economic concerns, embedded passives were introduced to the market in the early 1980s. The potential advantages offered as a result of embedded passives include:

- Increased circuit density through saving real-estate on PCB substrates

- Improved electrical properties through additional termination, filtering and shortening electrical connection opportunities

- Cost reduction through increased manufacturing automation

- Increased product quality through the elimination of incorrectly attached devices, and

- Improved reliability through eliminating solder joints

#### 1.3.5 Specific Applications

Embedded passives are an attractive alternative for attaining higher passive integration in the telecommunications, automotive, avionics, medical equipment, and GPSs electronic industry. Embedded passive have been used in the following applications:

- Digital electronics for pull-up/pull-down on open collectors for gate inputs

- Line terminations

- LED current limiting

- Switch pad potentiometers and power dividers

- Microwave attenuators

- Parallel and series terminating resistors fabricated into voltage plans of emittercoupled logic circuitry

- Series terminating resistors for high-speed CMOS applications, and

- Isolation resistors for burn-in boards

Alcatel Bell **CTS** Microelectronics Cannon Codex **Concurrent Computer** Control Data Corporation Cray Research Harris Computer Data General Hewlett Packard IBM Loral Defense Intel Loral Space MIPS Motorola NCR National Instruments National Semiconductor Nikon Pentax Raytheon Seagate Technology Sequent Computer Siemens Sun Microsystems

Companies currently making use of embedded passives include:

An increase in the use of embedded passive technology is expected over the next few years which will further decrease the cost of implementing the technology in a fashion similar to what was witness by the PCB industry when the move was made from through hole assembly to surface mount assembly. In the early days, surface mount components were many times more expensive than through hole components and new surface mount assembly equipment costs were off the charts. As time went on, the cost of the components, assembly equipment and all of the other infrastructure came down, so that today, in most cases, it is less expensive to build a surface mount assembly than a through hole assemble. Table 1-6 provides the projected market share for embedded resistors and capacitors in 2004.

| Type of Application | Projected Market Share for<br>embedded passives in 2004 |            |

|---------------------|---------------------------------------------------------|------------|

|                     | Resistors                                               | Capacitors |

| Hand Held           | 64%                                                     | 58%        |

| High Performance    | 40%                                                     | 40%        |

| Cost/Performance    | 20%                                                     | 20%        |

| Low Cost            | 10%                                                     | 10%        |

| Harsh Environment   | 20%                                                     | 20%        |

Table 1-6: Projected market share of embedded resistors and capacitors in 2004 [16]

#### **1.4 Embedded Passive Economics**

Miniaturization is currently a major driver within the electronics industry. Passive components are under serious scrutiny because they constitute the vast majority of components placed on a PCB. The embedded passives technology presents the PCB manufacturing industry with an avenue to attain the miniaturization that they are after. There are several inhibitors that are likely to keep embedded passive components from reaching their full market potential including the following:

- Need to demonstrate the technical viability of embedded passive substrates, including materials, processes, design and test system;

- Need to demonstrate the value or economic justification for substituting embedded passive technology for discrete capacitor and resistors;

- Potential delay to the product development cycle. Designing substrates that include embedded passives takes longer and CAD software tools that support it are either not available or immature. The economic impact of a product delay

could easily out way any cost saving in size reduction or conversion costs;

- Embedded passives reduce engineering and manufacturing flexibility.

- Qualification most of the processes, materials, vendors and products in this space are not yet qualified;

- Lack of availability from multiple suppliers;

Industry standards are required to capture the true market potential for this technology. However, the foremost concern of the embedded passive technology is whether the technology is economically feasible. Potentially the biggest single question about embedded passives is their cost, "...of all the inhibitors to achieving an acceptable market for integral substrates, the demonstration of cost savings is paramount" [9]. There is considerable controversy, however, as to whether the applications fabricated using embedded passives will be able to compete economically with discrete passive technology. On the bright side, the use of embedded passives reduces assembly costs, shrinks the required board size, and negates the cost of purchasing and handling discrete passive components. However, these economic advantages must be traded off against the increased cost (per unit area) of boards fabricated with embedded passives (a situation that will not disappear over time) and decreased throughput of the board fabrication process.

#### **1.5 Dissertation Overview**

The objective of this dissertation is to enable cost/size tradeoff analysis for the selective conversion of conventional passives to embedded passives. The cost/size tradeoff analysis capability will be used to determine the optimum set of conventional passives to replace with embedded passives on an application-specific basis. This

15

research provides a tool to determine the circumstances under which (and for what type of applications) it is economically viable to consider using the embedded passives technology. Only resistors and capacitors are considered herein (the quantities of inductors in systems are relatively small, and current methods of embedding inductors are not considered practical). This work will also only specifically consider embedding into Printed Circuit Boards (as opposed to ceramic or thin film substrates), however, the model and design methodology developed herein could be applied to other substrate types with very little or no modification. The specific tasks that have been completed to attain the objectives set forth above are:

- Task 1: Develop a board sizing (including layer count prediction) model that accounts for routing changes due to embedding of passives.

- Task 2: Develop a manufacturing cost model for embedded passive substrate fabrication and system manufacturing that can be integrated with the size analysis in Task 1.

- Task 3: Implement a Multi-Population Genetic Algorithm optimization approach that allows the optimum mixture of discrete and embedded passives to be determined on an application-specific basis.

- Task 4: Perform case studies to demonstrate and exercise the models and solution methodologies. The case studies demonstrate the applicability and limitations of existing modeling approaches as opposed to the new models developed in this dissertation, and the utility of optimizing the embedded passive content in systems.

#### Chapter 2 describes the approach to the development of the cost and size model

for embedding resistors and capacitors. Chapter 3 provides the results generated using the model developed in Chapter 2 for embedding resistors and capacitors in several different applications.

In Chapter 4, a Multi-Population Genetic Algorithm search is applied to the model developed in Chapter 2. An application from Chapter 3 is analyzed to obtain the optimal solution and demonstrate the approach. The results are also analyzed to study the sensitivity of the system cost to the design variables.

In Chapter 5, a real application, the SENDO M550 GSM cell phone main board, is analyzed to demonstrate the applicability of the model developed herein. Chapter 6 examines the effect of board size on the optimum solution (minimum cost solution) and assesses whether better system solutions can be found by varying or constraining the size of the board in different ways. Chapter 7 discuses the contributions of this research and conclude the dissertation.

### **CHAPTER 2 EMBEDDED PASSIVE COST/SIZE MODEL**

As discussed in Chapter 1, although the embedded passive technology potentially offers many benefits to the electronics industry, in order to make it a viable widespread technology the cost has to be addressed. It will be extremely difficult for the embedded passive technology to compete with the existing surface mount technology (SMT) discrete passives if its economic impact is not fully understood. The motivation for this work is to explore the potential cost savings that are present in the embedded passive technology and to identify the system variables for which the system cost is most sensitive. The model developed in this chapter addresses Tasks 1 and 2, and represents the analysis engine around which an optimization methodology can be built (Chapter 4). The model in this chapter is expected to, by itself, result in a tool that enables tradeoff analysis between conventional discrete passive systems and systems with embedded passives technology at an application-specific level.

Currently there are two well-known methods for doing cost models in electronics manufacturing, namely, Bottoms-up and Top-down methods. Bottoms-up is the cost derived by accumulating detailed estimates from individual fabrication and manufacturing processes or process steps. Bottoms-up modeling allows the impacts of major and minor changes of processes to be quantified, minimizes the risk of missing significant contributor to system cost, and is often used to calibrate Top-down models. The difficulty with Bottoms-up models are that the input data required by the model may not be available and the models may never lead to a system-level answer since it gets stuck in component-level analysis. Alternatively, Top-down models cost is derived from major system attributes. Top-down models provide system-level answers with relatively

simple models that can be evolutionarily improved by adding more layers of detail. Topdown models ultimately yield more practical solutions for performing system-level tradeoffs on application-specific variations of the use of a technology than Bottoms-up and the data required by the model is usually readily available. The one potential problem with Top-down modeling is that the utility decreases when the technology varies widely, i.e., they work well as long as they contain the appropriate attributes of the technologies being considered. The cost model developed in this section employs a parametric Topdown approach.

#### 2.1 Model Development

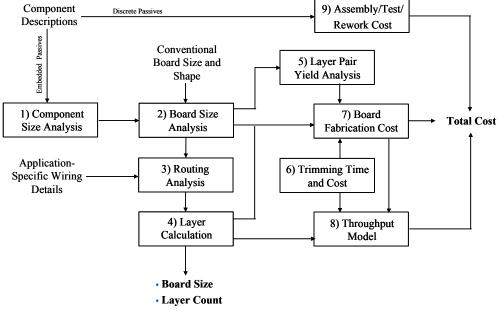

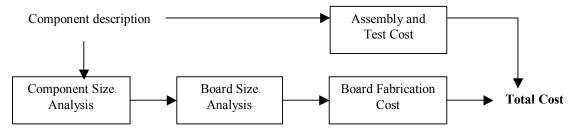

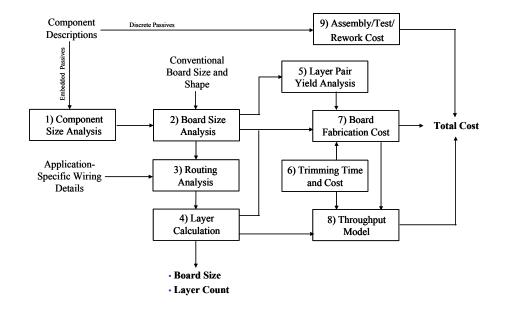

The model developed to analyze embedded passive cost trade off is summarized in Figure 2-1. Qualitatively the model in Figure 2-1 works in the following way:

- 1. Accumulate the area of the footprints of discrete passives to be embedded.

- 2. Reduce board area by the accumulated discrete passive area from step 1 maintaining the aspect ratio of the original board. This step is optional, i.e., the board area may be fixed.

- 3. Plated or Printed Resistors: Determine the area occupied by each plated or printed embedded resistor on wiring layers. Perform routing analysis removing nets and vias associated with resistors that are embedded and accounting for area blocked by embedded resistors on wiring layers. Routing is assumed to be unaffected by discrete resistors embedded using Ohmega-Ply<sup>®</sup> or similar dedicated layer subtractive approaches. Bypass Capacitors (distributed capacitors): All nets and vias associated with embedded bypass capacitors are removed from the routing problem. Singulated Capacitors: Assume that embedded singulated capacitors do

not affect routing analysis. Using these assumptions determine the relative change in routing resources due to embedding selected passives.

- 4. Using the layer requirements, the relative routing requirements for the embedded substrate and either a fixed measure of the routing efficiency associated with the conventional board or a range of possible efficiencies determined under the assumption that the conventional version of the board did not include any more layer pairs than it needed to route the problem, compute the number of required layer pairs for the embedded passive implementation.

- 5. Determine the yield of layer pairs that include embedded passives.

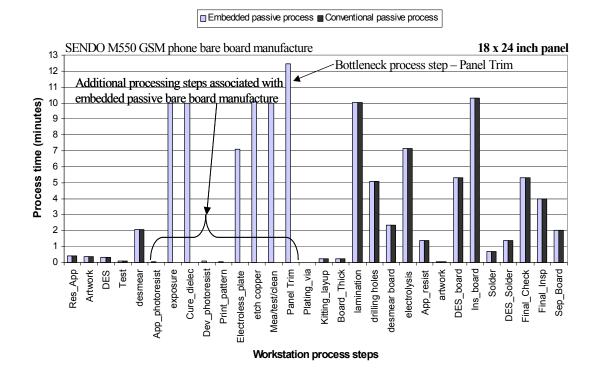

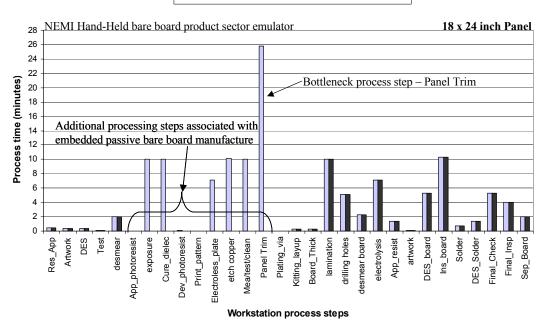

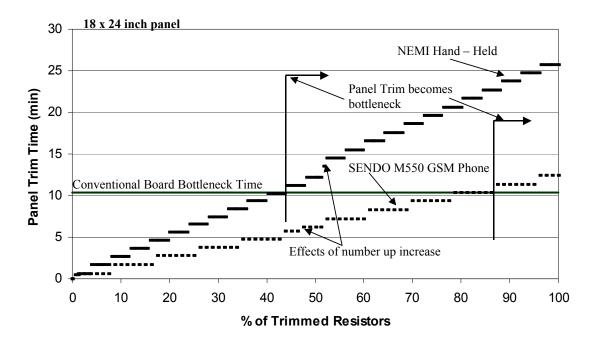

- 6. Determine the trimming cost for embedded resistors. The necessity of trimming is determined by the resistor's tolerance. The application-specific cost per trim is determined by modeling the throughput of a laser trimming process.

- Compute the number of boards per panel from the board size (number-up) and the effective panel fabrication costs from the layer and material requirements, yields, and resistor trimming costs.

- 8. Determine the relative board fabrication profit margin from layer pair throughput modeling.

- 9. Accumulate assembly cost, test, rework, and board fabrication costs (with profit margin) to obtain total relative cost.

The analysis in Figure 2-1 focuses on generating the differences in system cost between embedded passive and discrete passive solutions, therefore all cost elements that are approximately equivalent for the embedded and conventional system are ignored, e.g., all functional testing of the system and, procurement and assembly costs associated with non-embeddable parts. In the tradeoff analysis, accurately predicting differences in performance, size, cost, or reliability are more important than predicting accurately the actual properties.

Figure 2-1: Model developed for the analysis of embedded passive cost and size impact on electronic systems

The objective of the model developed and demonstrated in this research is to capture the economic impact of the following competing effects when embedded passives are present in the board:

- Decreased board area due to a reduction in the number of discrete passive components

- Decreased wiring density requirements due to the embedding of resistors and bypass capacitors into the board

- Increased wiring density requirements due to the decreased size of the board

- Increased number of boards fabricated on a panel due to decreased board size

- Increased board cost per unit area

- Decreased board yield

- Decreased board fabrication throughput

- Decreased assembly costs

- Increased overall assembly yield

- Decreased assembly-level rework.

Due to the opposing nature of many of the effects listed above, the overall economic impact of replacing discrete passives with embedded passives is not trivial to determine and, in general, yields application-specific guidelines instead of general rules of thumb. In fact the very nature of tradeoff analysis is one in which *the greater the detail necessary to accurately model a system, the less general and more application-specific the result.*

#### 2.1.1 Existing Embedded Passives Cost Modeling Work

Several authors have addressed cost analysis for embedded passives and thus provide varying degrees of insight into the economic impact of converting discrete passives to embed. The target of all these economic analyses is to determine the effective cost of converting selected discrete passive components to embedded components. The most common approach to economic analysis of embedded passives is to: 1) reduce the system cost by the purchase price and conversion costs<sup>1</sup> associated with the replaced discrete passives and determine the new number of boards on the panel, and 3) determine the new board cost based on a higher per unit area cost for the embedded passive panel fabrication and the new number-up computed in step 2. The results of these three steps determine the new system cost. The effects included in this first-order

approach are critical, however, the approach ignores several additional elements, most notably: decreased throughput for embedded passive board fabrication means that board fabricators will have to use higher profit margins for embedded passive boards to justify their production on lines that could otherwise be producing conventional boards; routing analysis of the board to determine not only what layers may be omitted, but what layers may have to be added to maintain sufficient wiring capacity as passives are embedded and the board is allowed to shrink; yield of both discrete passive components and the variation in board yield due to embedding passives; and potential reductions in rework costs (due to both assembly defects and intrinsic functional defects) associated with discrete passives.

Brown [17] presents an outline of all the potential contributions to the life cycle cost of embedded passives. Brown then provides a quantitative evaluation similar to the process outlined above for digital and RF applications. Brown concludes that the more you integrate at the design level, the higher the likely cost savings and that in the applications considered by Brown, embedded passive allowed a possible savings that ranged from 27 to 73% over conventional implementations. Rector [9] provided the economic analysis that appeared in the 1998 NEMI Passive Component Technology roadmap [18] using the first-order approach outlined above. Rector concludes that the effects in the first-order model outlined above, but does not provide a quantitative analysis to support this supposition. Ohmega Technologies Inc. has also generated a cost model for assessing cost tradeoffs associated with it's Ohmega-Ply<sup>®</sup> embedded resistor material, [19]. The Ohmega cost model follows the first-order approach described above,

<sup>&</sup>lt;sup>1</sup> Conversion costs are the handling, storage and assembly costs associated with a discrete component.

and includes yield and rework effects. Ohmega concludes that 2-4 embeddable resistors per square inch are required to make the use of the Ohmega-Ply material economically practical.

The most detailed analysis to date is from Realff and Power [20]. Realff and Power developed a technical cost model for board fabrication and assembly. The model includes test (board and assembly), yield, and rework. The focus of the model is on the equipment requirements, under the assumption that embedded resistors are fabricated using a dedicated resistor layer, they conclude that for embedded resistors to have a significant impact on the cost of a system, their use must allow the removal of equipment or in some other way fundamentally change the assembly process (e.g., changing from double to single sided assembly). Only embedded resistors are considered in [20]; Power *et al.* [20] extend the model in [21] to embedded capacitors and cast it in the form of an optimization problem targeted at choosing which discrete passives to embedded based on an assumption of assembly and substrate manufacturing process details, and material properties.

Another analysis that recently appeared focused on design tradeoffs for a GPS front end, [22]. This analysis includes detailed cost modeling of thin-film embedded resistors and capacitors performed using the Modular Optimization Environment software tool from ETH.

The model developed in this chapter incorporates quantitative routing estimation and assesses board fabrication throughput impacts for setting profit margins on board fabrication; these are effects that have not been included in previous models. Also, different technology assumptions than those used in the analyses discussed above were made, i.e.,

- Embedded resistors are fabricated directly on wiring layers via printing or plating a resistive material directly on a wiring layer only where an embedded resistor is required (e.g., [23], [24]) – as opposed to requiring dedicated embedded resistor layers as assumed previously, [19] and [20].

- 2. Bypass capacitors are embedded by dielectric substitution into an existing reference plane layer (as opposed to layer pair addition).

- 3. Singulated embedded capacitors if present are fabricated via dedicated layer pair addition.

# 2.1.2 Size/Cost Model Description

This section describes a new model that incorporates the additional effects discussed in Section 2.1.1 and allows size/cost tradeoff analysis for systems containing embedded resistors and capacitors (embedded inductors are not addressed in this work).

# Board Size and Routing Calculations

As discrete passive components are converted to embedded passives, the physical size of the board can either remain fixed or is allowed to optionally decrease by the layout area associated with the discrete passives given by,

$$A_{new} = A_{conv} - \sum_{i=1}^{N} (l_i + S)(w_i + S)$$

(1)

where S is the minimum assembly spacing,  $l_i$  and  $w_i$  are the length and width of the ith discrete passive, N is over all discrete passives that are converted to embedded passives, and  $A_{conv}$  is the conventional board area. It is assumed that if the board is allowed to shrink, its aspect ratio is preserved, thus, the new board length ( $L_{new}$ ) and width ( $W_{new}$ )

are given by,

$$L_{new} = \sqrt{\frac{A_{new}L_{conv}}{W_{conv}}}$$

(2a)

$$W_{new} = \frac{W_{conv}}{L_{conv}} L_{new}$$

(2b)

where  $L_{conv}$  and  $W_{conv}$  are the length and width of the conventional board. If the board is double sided, the calculation in (1) and (2) can be performed independently for each side of the board, the larger of the two sides determines the new board size.

The area consumed by the embedded passives on internal layers impacts the tradeoff analysis by decreasing the wiring available on internal layers. The area occupied by an embedded resistor on a board inner layer is given by,

$$A_{R} = \begin{cases} \frac{0.8R}{r} m^{2} & \text{for } 0.75R > r \\ \frac{r}{0.8R} m^{2} & \text{for } 0.75R \le r \end{cases}$$

(3)

where R is the value of the resistor, r is the resistivity of the resistor material ( $\Omega$ /square), and m is the minimum feature size for embedded resistor fabrication. Since embedded resistors are designed and fabricated to smaller (resistance) values than required and trimmed, a factor of 0.8 is included in (3). The factor of 0.8 can be derived assuming a symmetric distribution of fabricated resistor values where the lowest trimmable resistor is 55% of the application target value, a 5% design tolerance on the resistors, and maximizing the number of resistors between the high specification limit and the lowest trimmable resistor, see [25].

There are two types of capacitors that must be considered - bypass (decoupling) capacitors, and non-bypass capacitors. It is assumed that bypass capacitors can be

absorbed into dedicated bypass layer pairs (planar distributed capacitance layers) and the non-bypass capacitors must be fabricated individually on a dedicated capacitor layer pair if they are to be embedded. The area occupied by an individual non-bypass embedded capacitor on a capacitor layer pair is,

$$A_{\rm C} = \frac{\rm C}{\rm c} \tag{4}$$

where C is the value of the capacitor, and c is the capacitance per unit area of the capacitor layer pair. Assuming square capacitors, the number of embedded capacitor layer pairs (for non-bypass capacitors) required in the board is given by,

$$N_{\text{integral cap layers}} = \left[ \frac{\sum_{j=1}^{N_{c}} \left( \sqrt{A_{c_{j}}} + S_{c} \right)^{2}}{A_{\text{new}}} \right]$$

(5)

where  $N_C$  is the total number of non-bypass capacitors that are converted from discrete to individual embedded capacitors, and  $S_c$  is the effective spacing between individual embedded capacitors on the embedded capacitor layer pair.  $S_c$  is usually set larger than the minimum spacing possible to allow for perforation of the embedded capacitor layer by vias and through holes, and to allow area for interconnection.

Besides estimating the physical size of the board after the embedding of selected discrete passive components, routing requirements also needs to be considered. The following routing assumptions are made with respect to embedded passives:

The IO (effectively the nets and vias) associated with discrete resistors that are embedded are effectively removed from the routing problem, i.e., the embedded resistors are fabricated in series with the nets they are attached to on the wiring layers, however, the area occupied by the embedded resistors blocks routing and is accounted for, see (7). Non-bypass discrete capacitors converted to embedded capacitors have no effect on the routing problem. The IO (effectively the nets and vias) associated with discrete bypass capacitors converted to an embedded capacitor are effectively removed from the routing problem.

With these assumptions and the routing information from the conventional implementation, the routing requirements, and thereby the number of layers required, for an implementation that includes embedded passives can be determined. An estimation of the minimum number of layers required to route the application proceeds as follows,

$$N_{layers_{new}} = \frac{W_{used new} + W_{blocked}}{W_{layer_{new}}} \left(\frac{U_{conv}}{U_{limit}}\right)$$

(6)

where  $U_{\text{limit}}$  is the maximum fraction of the theoretically available wiring in the board that can be used for routing, and  $U_{\text{conv}}$  is the fraction of that wiring that is actually used to route the conventional application. The ratio of  $U_{\text{conv}}$  and  $U_{\text{limit}}$  measures the routing efficiency of the conventional implementation. When the ratio is large (i.e., close to one), the implementation has effectively used all the wiring that is available and any additional wiring would require the addition of another layer pair or an increase in board area. At some smaller value, any decrease in wiring would allow the omission of a layer pair.

The wiring blocked ( $W_{blocked}$ ) by embedded resistors (length of wiring that can not be used) is given by

$$W_{blocked} = \left(\frac{\sum_{i=1}^{N_{R}} A_{R_{i}}}{A_{new}}\right) \left(\frac{A_{new}}{A_{conv}} W_{layer_{conv}}\right).$$

(7)

where,  $N_R$  is the number of embedded resistors,  $A_{new}$  is given by (1) and  $A_R$  is given by (3). The second multiplier is the wiring per layer in the embedded passive board with no

embedded resistors included ( $W_{layer}$ ). The total length of wiring used for the new implementation is given by,

$$W_{used new} = f(W_{used conv})$$

(8)

where, f is the fractional change in required total wiring length. The wiring used in the conventional implementation is found from,

$$W_{used \, conv} = W_{avail \, conv} \tag{9}$$

where,  $W_{avail_{conv}}$  is the total length of wiring theoretically available in the conventional board ( $W_{layer_{conv}}$  multiplied by the number of layers in the conventional board minus layers on which wiring is not done, e.g., reference planes). Assuming that the total wiring length required is proportional to the total number of system IO that require routing (a fundamental assumption in routing estimation approaches that compare requirements and resources, [26]), f is found from,

$$f = \frac{N_{IO_{new}}}{N_{IO_{conv}}}$$

(10)

where,  $N_{IO_{new}} = N_{IO_{conv}} - 2N_R - 2N_{BC}$ , the total number of system IO in the new implementation (assuming 2 IO per resistor and capacitor), assuming resistors are printed directly onto wiring layers

$N_R$  = number of embedded resistors

$N_{BC}$  = number of bypass capacitors absorbed into a bypass capacitance layer pairs

$N_{IO_{conv}}$  = total number of system IO in the conventional implementation.

Note, N in (1) is  $N_R + N_C + N_{BC}$  where  $N_C$  is the number of non-bypass capacitors that are embedded into the board. The number of IO in the conventional implementation is given by,

$$N_{IO_{conv}} = N_{nets_{conv}} (fanout + 1)$$

(11)

where fanout = average number of IO that a net attaches together minus one (assumed to be the same for the conventional and embedded passives implementations)

$N_{nets conv}$  = number of nets in the conventional implementation.

Since layers occur in pairs in printed circuit board manufacturing, the result given by (6) is rounded up to the nearest multiple of two for use in the model. Note, the final value of  $N_{\text{layers}_{new}}$  given by (6) is independent of  $W_{\text{layer}_{conv}}$ .

# Cost Analysis

Using the size and routing relationships developed in the last section, we can predict the board fabrication costs. The price per conventional board is given by,

$$P_{conv} = (1 + M_{conv}) \frac{C_{layerpair} A_{conv} N_{layers_{conv}}}{N_{up conv}}$$

(12)

where