## ABSTRACT

| Title of dissertation:    | COMPILER-BASED PRE-EXECUTION                                                |

|---------------------------|-----------------------------------------------------------------------------|

|                           | Dongkeun Kim, Doctor of Philosophy, 2004                                    |

| Dissertation directed by: | Professor Donald Yeung<br>Department of Electrical and Computer Engineering |

Pre-execution is a novel latency-tolerance technique where one or more *helper threads* run in front of the main computation and trigger long-latency delinquent events early so that the main thread makes forward progress without experiencing stalls. The most important issue in pre-execution is how to construct effective helper threads that quickly get ahead and compute the delinquent events accurately. Since the manual construction of helper threads is error-prone and cumbersome for a programmer, automation of such an onerous task is inevitable for pre-execution to be widely used for a variety of real-world workloads.

In this thesis, we study *compiler-based pre-execution* to construct prefetching helper threads using a source-level compiler. We first introduce various compiler algorithms to optimize the helper threads; *program slicing* removes noncritical code unnecessary to compute the delinquent loads, *prefetch conversion* reduces blocking in the helper threads by converting delinquent loads into nonblocking prefetches, and *loop parallelization* speculatively parallelizes the targeted code region so that more memory accesses are overlapped simultaneously. In addition to these algorithms to expedite the helper threads, we also propose several important algorithms to select the right loops for pre-execution regions and pick up the best thread initiation scheme to invoke helper threads. We implement all these algorithms in the Stanford University Intermediate Format (SUIF) compiler infrastructure to automatically generate effective helper threads at the program source level. Furthermore, we replace the external tools to perform program slicing and offline profiling in our most aggressive compiler framework with static algorithms to reduce the complexity of compiler implementation. We conduct thorough evaluation of the compiler-generated helper threads using a simulator that models the research SMT processor. Our experimental results show compiler-based pre-execution effectively eliminates the cache misses and improves the performance of a program.

In order to verify whether prefetching helper threads provide wall-clock speedup even in real silicon, we apply compiler-based pre-execution in a real physical system with the Intel Pentium 4 processor with Hyper-Threading Technology. To generate helper threads, we use the pre-execution optimization module in the Intel research compiler infrastructure and propose three helper threading scenarios to invoke and synchronize the helper threads. Our physical experimentation results prove prefetching helper threads indeed improve the performance of selected benchmarks. Moreover, to achieve even more speedup in real silicon, we observe several issues need to be addressed a priori. Unlike the research SMT processor where most processor resources are shared or replicated, some critical hardware structures in the hyper-threaded processor are hard-partitioned in the multithreading mode. Therefore, the resource contention is more intricate, and thus helper threads must be invoked very judiciously. In addition, the program behavior dynamically changes during execution and the helper threads should adapt to it to maximize the benefit from pre-execution. Hence we implement user-level library routines to monitor the dynamic program behavior with little overhead and show the potential of having a runtime mechanism to dynamically throttle helper threads. Furthermore, in order to activate and deactivate the helper threads at a very fine granularity, having light-weight thread synchronization mechanisms is very crucial.

Finally, we apply compiler-based pre-execution to multiprogrammed workloads. When introducing helper threads in a multiprogramming environment, multiple main threads compete with each other to acquire enough hardware contexts to launch helper threads. In order to address such a resource contention problem, we propose a mechanism to arbitrate the main threads. Our simulation-based experiment shows pre-execution also helps to boost the throughput of a multiprogrammed workload by reducing the latencies in the individual applications. Moreover, when the helper thread occupancy of each main thread in the workload is not too high, multiple main threads effectively share the hardware contexts for helper threads and utilize the processor resources in the SMT processor.

# COMPILER-BASED PRE-EXECUTION

by

Dongkeun Kim

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2004

Advisory Committee:

Professor Donald Yeung, Chair/Advisor Professor Rajeev Barua Professor Manoj Franklin Professor Bruce Jacob Professor Chau-Wen Tseng © Copyright by Dongkeun Kim 2004

## ACKNOWLEDGMENTS

There are many people who helped me with making this thesis possible. First of all, I really thank my advisor, Dr. Donald Yeung. It has been always my pleasure to discuss problems and findings with him for the past four years. I also enjoyed the time when I took his ENEE446 class during the first semester in my graduate study and I worked as a TA for his class the next semester. His devotion to research and advising has inspired me throughout the entire period of my study in the graduate program.

I also thank my dad and mom, who have been always my biggest supporters and counsellors throughout my entire life. Especially, I will never forget the day when I left my country to begin the graduate study in US. Everything on my way ahead was uncertain and I had complicated feelings mixed with excitement and nervousness. Without their consistent love and caring, it would have been impossible to go through every step to arrive at this moment. I also thank my lovely sisters, Jueun and Juhyun; I admit I have not been a good brother so far, but I promise I will be from now on.

During my stay in US for the past five years, I was so lucky to have many good people around me in both Maryland and California. I thank my lab-mates in the SCAL of the University of Maryland for their help and sharing good memory: Seungryul, Gautham, Deepak, Hameed, Sumit, Wanli, Xuanhua, Ammer, Sada, Zahran, Anashua, Vinod, Aneesh, Jayanth, Brinda, Renju, Barat, and all the other members in our group. I also appreciate the members of my PhD defense committee: Dr. Manoj Franklin, Dr. Bruce Jacob, Dr. Rajeev Barua, and Dr. Chau-wen Tseng. I would like to acknowledge the Korean graduate students at Maryland and their family: Woochul, Joonhyuk, Seungjong, Yeongsun, Younggu, Kyechong, Jusub, Bongwon, Hyunmo, Bohyung, Jihwang, Yooah, Junpyo, and many others. Also, my internship experience at Intel became more enjoyable and valuable thanks to Shih-wei, Perry, Jamison, Hong, John, Xinmin, Murali, Ryan, Satish, Dan, Gerolf, Youngsoo, Daehyun, Margarita, Nancy, Chris, Chaoying, John Young, Claire, David, Kihoon, Sunghoon, Haejin, and all my colleagues and friends in the San Francisco Bay area.

My friends in both US and Korea have been always supportive and they have encouraged me to keep moving forward: Jiwon, Mikyung, Jaehyuk, Junkwan, Seongjun, Youngho, Dongook, Youngjun, Daeki, Seungkyung, Junghyun, Haejin, Hyoje, Jonghwa, Hyomin, Hongseok, Jihyun, Jonghee, Heesun, Insuk, Junho, Saekyung, Chulsung, Woojay, Daewoo, Dongeun, Taemin, Hyungchan, Jun, Seungyong, Jungsoo, Sangwoo, and all other friends of mine.

Especially, I would like to thank Dr. Hyunook Kim. He has been a good friend, devoted mentor, and hero to me, and I have always admired his passion for research. Also, I pray for God to bless his family, Hyunmi and Hanna.

And, I apologize to those I have inadvertently left out.

Lastly, I thank God for giving me opportunity to know him at the last phase of my graduate study and showing me his endless love.

# TABLE OF CONTENTS

| Li | st of '       | of Tables in                                    |    |  |  |

|----|---------------|-------------------------------------------------|----|--|--|

| Li | st of Figures |                                                 |    |  |  |

| 1  | Intr          | Introduction                                    |    |  |  |

|    | 1.1           | Motivation                                      | 1  |  |  |

|    | 1.2           | Contributions                                   | 7  |  |  |

|    | 1.3           | Roadmap                                         | 10 |  |  |

| 2  | Bac           | kground                                         | 12 |  |  |

|    | 2.1           | Helper Threading                                | 12 |  |  |

|    | 2.2           | Multithreading                                  | 14 |  |  |

|    |               | 2.2.1 Multiprogramming                          | 14 |  |  |

|    |               | 2.2.2 Parallel Processing                       | 15 |  |  |

|    |               | 2.2.3 Pre-Execution                             | 16 |  |  |

|    | 2.3           | Data Prefetching                                | 17 |  |  |

|    |               | 2.3.1 Prediction-Based Prefetching              | 18 |  |  |

|    |               | 2.3.2 Execution-Based Prefetching               | 19 |  |  |

| 3  | Ove           | erview of Compiler Algorithms for Pre-Execution | 21 |  |  |

|    | 3.1           | Identifying Targets                             | 21 |  |  |

|    |               | 3.1.1 Identification of Delinquent Loads        | 21 |  |  |

|    |               | 3.1.2 Identification of Target Code Regions     | 24 |  |  |

|    |               | 3.1.3 Code Cloning                              | 25 |  |  |

|    | 3.2           | Improving Effectiveness of Pre-Execution        | 26 |  |  |

|    |               | 3.2.1 Program Slicing                           | 27 |  |  |

|    |               | 3.2.2 Prefetch Conversion                       | 27 |  |  |

|    |               | 3.2.3 Loop Parallelization                      | 28 |  |  |

|   |     | 3.2.4   | Synchronization                                     | 29 |

|---|-----|---------|-----------------------------------------------------|----|

|   | 3.3 | Minin   | nizing Ineffectiveness of Pre-Execution             | 30 |

|   | 3.4 | Preser  | rving Program Correctness                           | 32 |

|   |     | 3.4.1   | Removing Side Effects                               | 33 |

|   |     | 3.4.2   | Handling Exceptions                                 | 33 |

| 4 | SUI | F-Base  | d Compiler Frameworks for Pre-Execution             | 34 |

|   | 4.1 | Comp    | iler Algorithms for SUIF-Based Aggressive Framework | 34 |

|   |     | 4.1.1   | Identifying Targets                                 | 35 |

|   |     | 4.1.2   | Improving Effectiveness of Pre-Execution            | 39 |

|   |     | 4.1.3   | Minimizing Ineffectiveness of Pre-Execution         | 54 |

|   |     | 4.1.4   | Preserving Program Correctness                      | 55 |

|   | 4.2 | Comp    | iler Algorithms for SUIF-Based Reduced Frameworks   | 57 |

|   |     | 4.2.1   | Eliminating Program Slicing                         | 57 |

|   |     | 4.2.2   | Prefetch Conversion without Program Slicing         | 59 |

|   |     | 4.2.3   | Eliminating Cache-Miss Profiles                     | 60 |

|   |     | 4.2.4   | Eliminating Loop Profiles                           | 62 |

|   | 4.3 | Imple   | mentation                                           | 63 |

|   |     | 4.3.1   | Summary of Compiler Frameworks                      | 64 |

|   |     | 4.3.2   | Aggressive Prototype Compiler                       | 65 |

|   |     | 4.3.3   | Reduced Prototype Compilers                         | 66 |

|   |     | 4.3.4   | Live-In Passing                                     | 67 |

|   |     | 4.3.5   | Code Generation                                     | 68 |

|   |     | 4.3.6   | ISA Support                                         | 70 |

| 5 | Eva | luation | in a Simulation-Based Environment                   | 73 |

|   | 5.1 | Exper   | imental Methodology                                 | 73 |

|   |     | 5.1.1   | Simulator Configuration                             | 73 |

|   |      | 5.1.2         | Benchmarks                                                            | 75                |

|---|------|---------------|-----------------------------------------------------------------------|-------------------|

|   | 5.2  | Result        | s of Aggressive Compiler                                              | 76                |

|   |      | 5.2.1         | Characterization of Helper Threads                                    | 77                |

|   |      | 5.2.2         | Performance Results                                                   | 81                |

|   |      | 5.2.3         | Contributions of Algorithms                                           | 84                |

|   |      | 5.2.4         | Comparison of Thread Initiation Schemes                               | 87                |

|   |      | 5.2.5         | Comparison of HW/SW Synchronization Mechanisms                        | 89                |

|   |      | 5.2.6         | Accuracy of Helper Threads                                            | 91                |

|   | 5.3  | Result        | s of Reduced Compilers                                                | 94                |

|   |      | 5.3.1         | Impact of C Compiler's Code Removal                                   | 95                |

|   |      | 5.3.2         | Impact of SUIF-Based Prefetch Converter                               | 98                |

|   |      | 5.3.3         | Impact of Eliminating Cache-Miss Profiles                             | 98                |

|   |      | 5.3.4         | Impact of Eliminating Loop Profiles                                   | 100               |

|   | 5.4  | Summ          | ary                                                                   | 101               |

| 6 | Pre- | Execut        | ion Optimization Module in the Intel Research Compiler Infrastructure | 103               |

|   | 6.1  | Uniqu         | e Aspects of a Physical System                                        | 104               |

|   |      | 6.1.1         | Hardware Resource Management                                          | 104               |

|   |      | 6.1.2         | Thread Synchronization Mechanism and Cost                             | 105               |

|   |      | 6.1.3         | Available Hardware Contexts                                           | 107               |

|   | 6.2  | Comp          | iler Algorithms for the Intel Compiler                                | 107               |

|   |      | 6.2.1         | Identifying Targets                                                   | 107               |

|   |      | 6.2.2         | Improving Effectiveness of Pre-Execution                              | 110               |

|   |      | 6.2.3         | Minimizing Ineffectiveness of Pre-Execution                           | 115               |

|   |      | 6.2.4         | Preserving Program Correctness                                        | 116               |

|   |      |               |                                                                       |                   |

|   | 6.3  | Емон          | LITE: User-Level Library Routines for Runtime Performance Monitoring  | 116               |

|   | 6.3  | Емон<br>6.3.1 |                                                                       | $\frac{116}{117}$ |

|   |      | 6.3.3   | Implementation Issues                                             | 118 |

|---|------|---------|-------------------------------------------------------------------|-----|

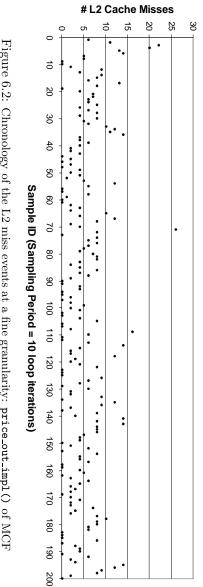

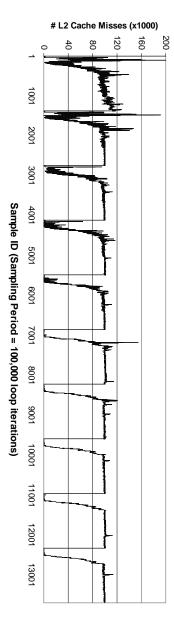

|   |      | 6.3.4   | Example Usage: Chronology of L2 Miss Events                       | 119 |

|   | 6.4  | Implei  | mentation                                                         | 120 |

|   |      | 6.4.1   | Prototype Compiler                                                | 120 |

|   |      | 6.4.2   | Live-in Passing                                                   | 121 |

|   |      | 6.4.3   | Code Generation                                                   | 121 |

| 7 | Eval | luation | in a Physical System with the Intel's Hyper-Threaded Processor    | 123 |

|   | 7.1  | Exper   | imental Evaluation                                                | 123 |

|   |      | 7.1.1   | System Configuration                                              | 123 |

|   |      | 7.1.2   | Benchmarks                                                        | 124 |

|   |      | 7.1.3   | Baseline                                                          | 126 |

|   |      | 7.1.4   | Evaluation of Static Thread Initiation Schemes                    | 127 |

|   |      | 7.1.5   | Evaluation of Dynamic Throttling of Helper Threads                | 137 |

|   |      | 7.1.6   | Sensitivity of Program's Dynamic Behavior                         | 139 |

|   | 7.2  | Key C   | Observations                                                      | 140 |

|   |      | 7.2.1   | Impediments to Speedup                                            | 141 |

|   |      | 7.2.2   | Essential Mechanisms                                              | 142 |

| 8 | Eval | luation | of Compiler-Based Pre-Execution in a Multiprogramming Environment | 143 |

|   | 8.1  | Multip  | programming Simulation Methodology                                | 143 |

|   | 8.2  | Evalua  | ation Results                                                     | 145 |

| 9 | Rela | ted Wo  | ork                                                               | 149 |

|   | 9.1  | Multit  | chreading                                                         | 149 |

|   |      | 9.1.1   | Speculative Multithreading                                        | 150 |

|   |      | 9.1.2   | Helper Threading                                                  | 151 |

|   |      | 9.1.3   | Single-Chip Multithreading Processors                             | 153 |

|   | 9.2  | Data 1  | Prefetching                                                       | 155 |

|         | 9.2.1   | Prediction-Based Prefetching                                                    | 155 |

|---------|---------|---------------------------------------------------------------------------------|-----|

|         | 9.2.2   | Execution-Based Prefetching                                                     | 156 |

| 9.3     | Pre-E   | xecution                                                                        | 158 |

|         | 9.3.1   | Compiler-Based Pre-Execution                                                    | 159 |

|         | 9.3.2   | Linker-Based Pre-Execution                                                      | 160 |

|         | 9.3.3   | Hardware-Based Pre-Execution                                                    | 162 |

|         | 9.3.4   | Physical Experimentation with Prefetching Helper Threads $\ldots \ldots \ldots$ | 163 |

| 10 C    | 1.      |                                                                                 | 105 |

| 10 Con  | clusion |                                                                                 | 165 |

| 10.1    | Summ    | ary of Contributions and Implications of the Research                           | 165 |

| 10.2    | Future  | e Direction                                                                     | 167 |

|         |         |                                                                                 |     |

| Bibliog | raphy   |                                                                                 | 169 |

# LIST OF TABLES

| 4.1 | Compilers used to generate the helper thread code for our experiments on the SMT pro-       |     |

|-----|---------------------------------------------------------------------------------------------|-----|

|     | cessor simulator. The compilers differ in how they remove the unnecessary code, select the  |     |

|     | prefetch conversion candidates, identify the delinquent load instructions, and estimate the |     |

|     | inner-most loop work.                                                                       | 64  |

| 5.1 | SMT processor simulator configuration.                                                      | 74  |

| 5.2 | Benchmark characteristics.                                                                  | 76  |

| 5.3 | Static characterization of the helper thread code generated by our aggressive compiler.     | 77  |

| 5.4 | Dynamic characterization of the helper thread code generated by our aggressive compiler.    | 79  |

| 6.1 | Hardware resource management in the Intel's hyper-threaded processor                        | 104 |

| 7.1 | Physical system configuration.                                                              | 124 |

| 7.2 | Benchmark characteristics.                                                                  | 125 |

| 7.3 | Statistics for the STRIPMINING scheme.                                                      | 128 |

| 7.4 | Percentage SD statistics. Profiles are collected without launching helper threads. $\ldots$ | 137 |

| 8.1 | Benchmarks for the multiprogramming experiments. The TDF values for each benchmark          |     |

|     | are listed in the third row, and the helper thread initiation schemes employed in each      |     |

|     | benchmark are listed in the last row. Benchmark groupings are indicated in the first        |     |

|     | row: Group 1 benchmarks have high-TDF values, Group 2 benchmarks have medium-               |     |

|     | TDF values, and Group 3 benchmarks have low-TDF values.                                     | 145 |

## LIST OF FIGURES

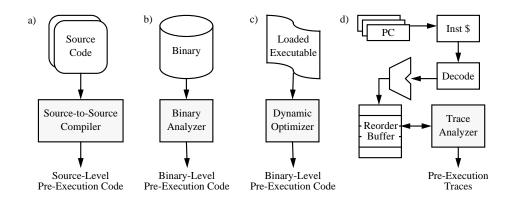

| 1.1 | Four approaches to automatically extract helper threads: a) compiler-based extraction,                                                    |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | b) linker-based extraction, c) dynamic optimizer-based extraction, and d) hardware-based                                                  |    |

|     | extraction. Techniques differ in when and how the code extraction is performed. $\ldots$ .                                                | 4  |

| 4.1 | Algorithm to compute the set of pre-execution regions, $P. \ \Phi$ denotes the empty set. To                                              |    |

|     | estimate the loop work, we rely on offline profiles for loop-trip counts. $\ldots$                                                        | 37 |

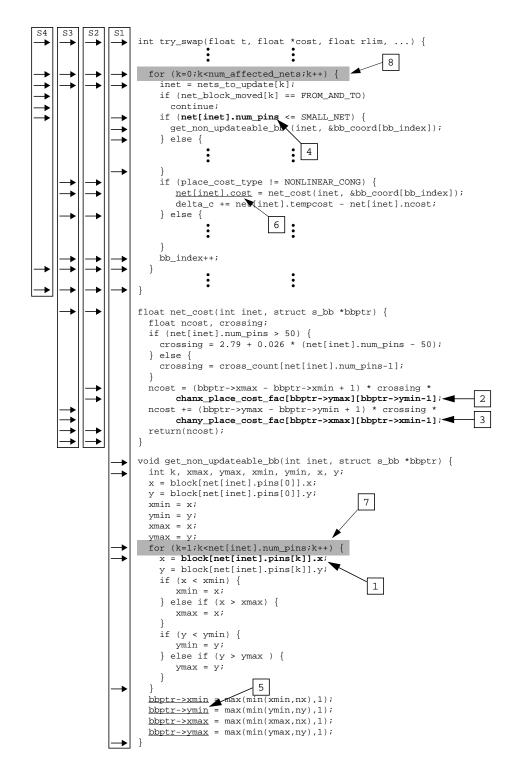

| 4.2 | VPR code example to demonstrate our program slicing. Labels "1" – "4" indicate the                                                        |    |

|     | cache-missing memory references selected for the slicing criteria. Labels "5" and "6" indi-                                               |    |

|     | cate the memory references that will be eliminated by store removal. Labels "7" and "8"                                                   |    |

|     | indicate loops that bound the scope of slicing. Labels "S1," "S2," "S3," and "S4" show                                                    |    |

|     | the slice result for the selected memory references.                                                                                      | 42 |

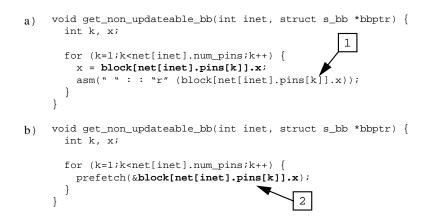

| 4.3 | Code generated by our aggressive compiler for the get_non_updateable_bb() function from                                                   |    |

|     | Figure 4.2. a) Pre-execution code after program slicing in which an <b>asm</b> macro is added                                             |    |

|     | for code pinning (labeled "1"). b) Pre-execution code after program slicing and prefetch                                                  |    |

|     | conversion (labeled "2"). Bold-face code denotes the cache-missing memory references. $% \left( \left( 1-\frac{1}{2}\right) \right) =0$ . | 46 |

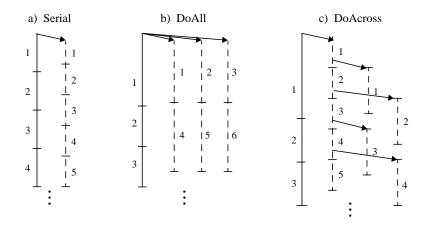

| 4.4 | Three helper thread initiation schemes: a) SERIAL, b) DOALL, and c) DOACROSS. Solid                                                       |    |

|     | lines denote the main thread, dotted lines denote the helper threads, arrows denote the                                                   |    |

|     | thread spawning, and numeric labels denote the loop iteration counts. $\ldots$                                                            | 48 |

| 4.5 | Algorithm to decide the thread initiation scheme for pre-execution regions.                                                               | 51 |

| 4.6 | Code generated by our compiler without program slicing for the get_non_updateable_bb()                                                    |    |

|     | function from Figure 4.2. An asm macro is added for code pinning (labeled "1")                                                            | 58 |

| 4.7 | Algorithm to compute the set of pre-execution regions, $P$ , without loop-trip count profiles.                                            |    |

|     | $\Phi$ denotes the empty set                                                                                                              | 63 |

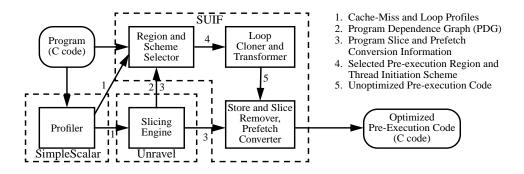

| 4.8 | Design of our most aggressive prototype compiler. This compiler uses Unravel to perform                                                   |    |

|     | program slicing and offline profiles to drive optimizations. Arrows denote the interactions                                               |    |

|     | between the compiler modules.                                                                                                             | 65 |

|     |                                                                                                                                           |    |

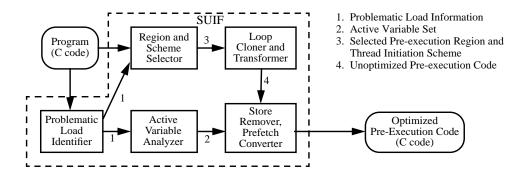

| 4.9  | Major components in our least aggressive prototype compiler. This compiler uses dead code    |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | elimination to remove the unnecessary code and static analysis to identify the delinquent    |    |

|      | loads and select the pre-execution regions. Arrows denote the interactions between the       |    |

|      | compiler modules.                                                                            | 66 |

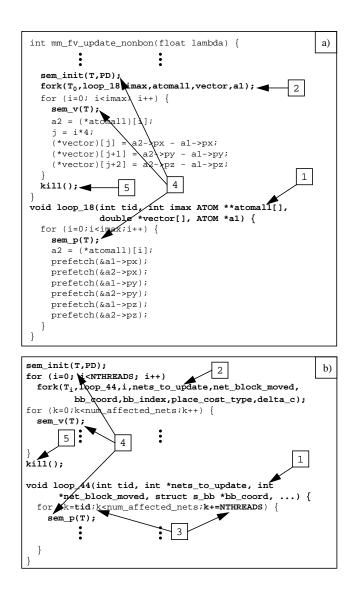

| 4.10 | Code generated by the aggressive compiler to implement a) the SERIAL scheme for the          |    |

|      | AMMP benchmark and b) the DOALL scheme for the VPR benchmark. Code to initiate               |    |

|      | pre-execution and synchronize the helper threads appears in <b>bold</b> face.                | 71 |

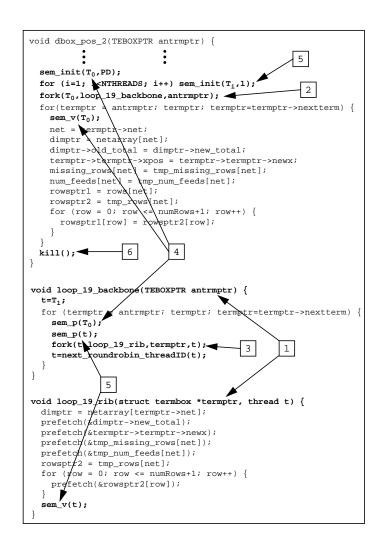

| 4.11 | Code generated by the aggressive compiler to implement the DoAcross scheme for the           |    |

|      | TWOLF benchmark. Code to initiate pre-execution and synchronize the helper threads           |    |

|      | appears in bold face.                                                                        | 72 |

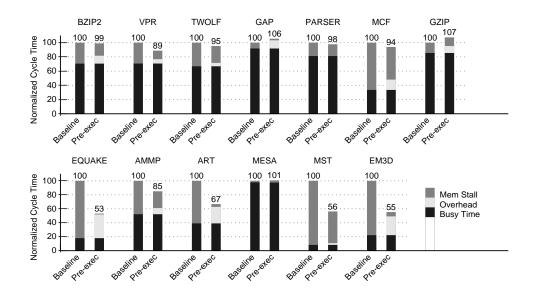

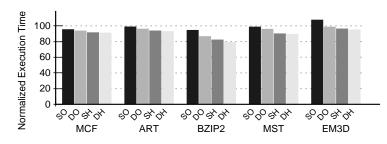

| 5.1  | Normalized execution time broken down into the "Busy Time," "Overhead," and "Mem             |    |

| 0.1  | Stall" components. The "Baseline" and "Pre-exec" bars show the performance without           |    |

|      |                                                                                              |    |

|      | and with pre-execution, respectively.                                                        | 81 |

| 5.2  | Cache-miss coverage broken down into five categories: uncovered cache misses occurring       |    |

|      | outside the pre-execution regions ("Non Region"), fully covered cache misses by pre-         |    |

|      | execution ("Full"), partially covered cache misses by pre-execution ("Partial"), remaining   |    |

|      | cache misses that hit in the L2 cache ("L2-Hit"), and remaining cache misses satisfied from  |    |

|      | main memory ("Mem").                                                                         | 83 |

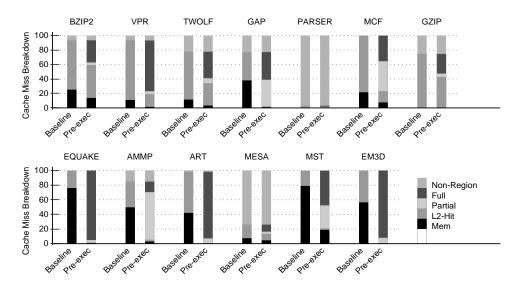

| 5.3  | Impact of individual algorithms on overall performance in the aggressive compiler. The       |    |

|      | "Parallel" bars perform pre-execution with speculative loop parallelization only; the "Slic- |    |

|      | ing" bars perform pre-execution with program slicing and speculative loop parallelization,   |    |

|      | but without prefetch conversion; and the "Pre-exec" bars perform pre-execution with all      |    |

|      | optimizations including prefetch conversion.                                                 | 86 |

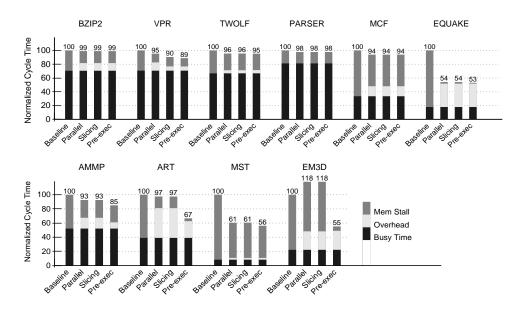

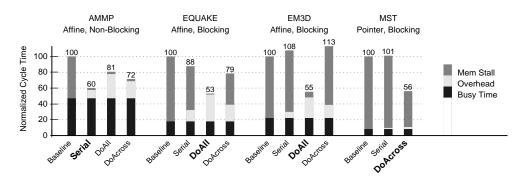

| 5.4  | Comparing the helper thread initiation schemes. The "Baseline" bars report the execu-        |    |

|      | tion time without pre-execution. The remaining bars report the execution time when the       |    |

|      | SERIAL, DOALL, and DOACROSS schemes are applied, respectively. The thread initiation         |    |

|      | schemes selected by our compiler appear in bold face.                                        | 88 |

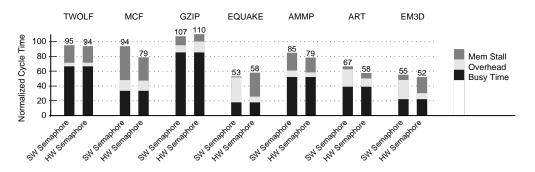

| 5.5 | Impact of architectural support for synchronization. The "SW Semaphore" and "HW                                                                                  |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Semaphore" bars report the execution time with the software and hardware counting                                                                                |     |

|     | semaphores, respectively. All bars are normalized to the "Baseline" bars from Figure 5.1.                                                                        | 90  |

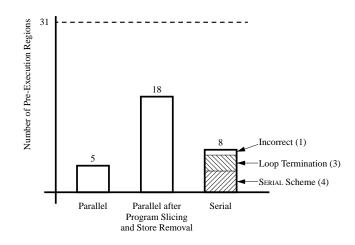

| 5.6 | Breakdown of the pre-execution regions into 3 major categories: originally parallel, parallel                                                                    |     |

|     | after program slicing and store removal, and serial. The serial category is further broken                                                                       |     |

|     | down into regions using the SERIAL scheme, regions speculatively parallelized affecting                                                                          |     |

|     | control flow only, and regions that are incorrectly parallelized. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                   | 93  |

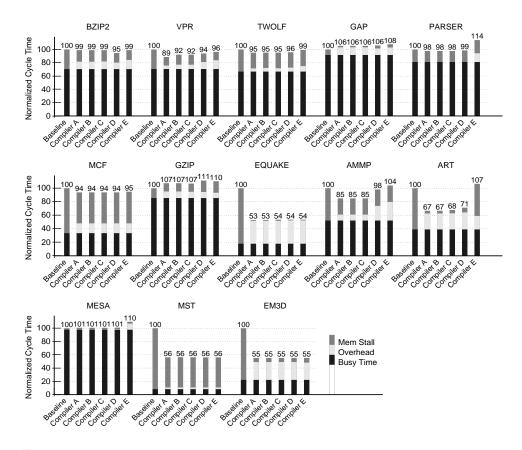

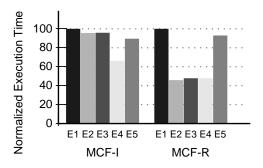

| 5.7 | Normalized execution time broken down into the "Busy Time," "Overhead," and "Mem                                                                                 |     |

|     | Stall" components. Groups of bars labeled "Compiler A" to "Compiler E" report perfor-                                                                            |     |

|     | mance for the 5 compilers from Table 4.1.                                                                                                                        | 94  |

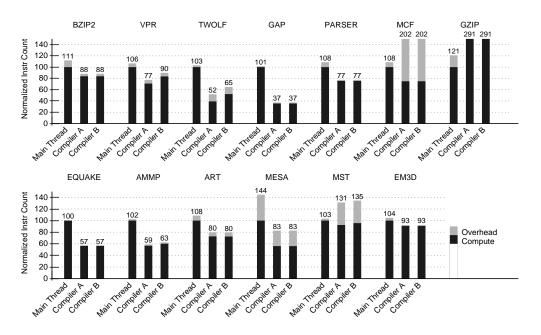

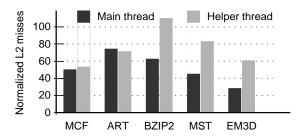

| 5.8 | Comparison of dynamic instruction counts between Compilers A and B. The "Main Thread"                                                                            |     |

|     | bars report the dynamic instruction counts for the main thread. The "Compiler A" and                                                                             |     |

|     | "Compiler B" bars report the dynamic instruction counts for the helper threads generated                                                                         |     |

|     | by Compilers A and B, respectively. Each bar is broken down into the "Compute" and                                                                               |     |

|     | "Overhead" components.                                                                                                                                           | 96  |

| 6.1 | Example of the EMONLITE code instrumentation: price_out_impl() of MCF                                                                                            | 119 |

| 6.2 | Chronology of the L2 miss events at a fine granularity: $\verb"price_out_impl()" of MCF"$                                                                        | 120 |

| 6.3 | Coarse-grain phase behavior of the L2 miss events: $\verb"price_out_impl()" of MCF"$                                                                             | 120 |

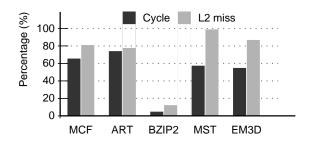

| 7.1 | VTune profiles: cycles and L2 misses associated with the identified delinquent loads $\ . \ .$                                                                   | 126 |

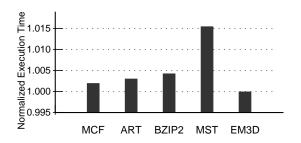

| 7.2 | Normalized execution time without thread pinning. The execution time without helper                                                                              |     |

|     | threads, but with thread pinning, is our baseline for the actual performance measurements.                                                                       | 127 |

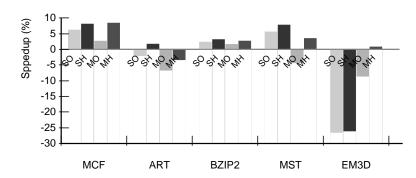

| 7.3 | Speedup of the static thread initiation schemes. From the left to right bars, we label each                                                                      |     |

|     | bar as "SO" for the SERIAL scheme with the OS API, "SH" for the SERIAL scheme with the                                                                           |     |

|     |                                                                                                                                                                  |     |

|     | hardware mechanism, "MO" for the STRIPMINING scheme with the OS API, and "MH"                                                                                    |     |

|     | hardware mechanism, "MO" for the STRIPMINING scheme with the OS API, and "MH" for the STRIPMINING scheme with the hardware mechanism. The speedup is computed by |     |

| 7.4 | Speed of the cache-miss kernels for various situations. For these experiments, we use the          |     |

|-----|----------------------------------------------------------------------------------------------------|-----|

|     | SERIAL scheme with the hardware thread synchronization mechanism. $\ldots$                         | 132 |

| 7.5 | Cache-miss coverage using the SERIAL scheme with the hardware thread synchronization               |     |

|     | mechanism.                                                                                         | 134 |

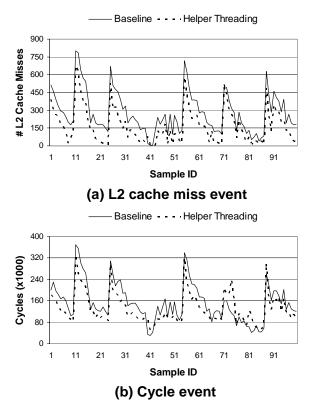

| 7.6 | Dynamic behavior of the performance events in BZIP2 with and without helper threads.               |     |

|     | a) Chronology of the L2 miss events. b) Chronology of the cycle events. $\ldots$ $\ldots$ $\ldots$ | 136 |

| 7.7 | Performance comparison between the STRIPMINING scheme and the DYNAMIC STRIPMIN-                    |     |

|     | ING scheme. From left to right bars, each bar is labeled to present the thread initiation          |     |

|     | scheme and the thread synchronization mechanism: "SO" for the $\ensuremath{STRIPMINING}$ scheme    |     |

|     | with the OS API, "DO" for the DYNAMIC STRIPMINING scheme with the OS API, "SH"                     |     |

|     | for the STRIPMINING scheme with the hardware mechanism, and "DH" for the DYNAMIC                   |     |

|     | STRIPMINING scheme with the hardware mechanism.                                                    | 139 |

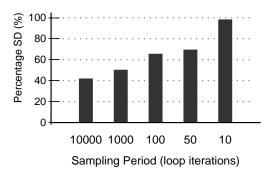

| 7.8 | Percentage SD of L2 misses for various sampling periods.                                           | 140 |

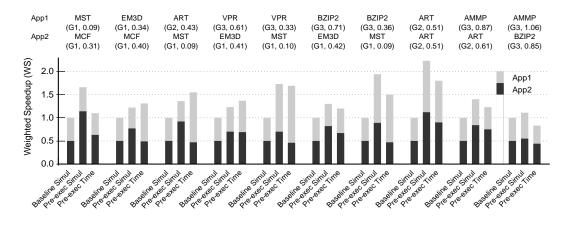

| 8.1 | Weighted speedup of the multiprogrammed workloads. "Baseline Simul" denotes simul-                 |     |

|     | taneous execution without pre-execution. "Pre-exec Simul" and "Pre-exec Time" denote               |     |

|     | pre-execution with simultaneous execution and time sharing, respectively. The TDF group            |     |

|     | that each application belongs to and the baseline IPC for the application are shown in             |     |

|     | parentheses                                                                                        | 146 |

## Chapter 1

## Introduction

## 1.1 Motivation

Pre-execution is a general latency-tolerance technique, in which one or multiple number of threads, called *helper threads*, run in front of the main computation thread (main thread for short) and trigger long-latency events, such as the last-level cache misses, on the main thread's behalf. When helper threads are effective, the main thread runs without experiencing stalls, thereby reducing the execution time. Data prefetching is a good example that clearly shows the usefulness of preexecution. Among various performance-degrading events, cache misses, especially those incurring memory access, have been the main target of many latency-tolerance techniques due to their huge impact on the program performance. Numerous research proposals have studied tolerating the large memory latency by prefetching based on repetitive memory access patterns in a program. Such *prediction-based* prefetching is very effective for affine-array access, which is easily found in many scientific workloads. However, nonscientific workloads often exhibit irregular memory access patterns that are hard to predict; such irregularities are usually found in pointer-chasing traversal, index-array reference, or hash-table access. Rather than predict, pre-execution actually *executes* certain instructions that are part of the original program to compute the cache-missing memory references so that accurate prefetches can be generated. Thanks to execution-based nature, irregularity in memory access patterns is not a problem in pre-execution; in fact, this is one of the most compelling reasons why pre-execution is a promising data-prefetching technique.

In addition to its execution capability, we find pre-execution also has much potential to uncover large amount of thread-level parallelism, especially *memory-level parallelism*. In preexecution, prefetching helper threads only execute code to compute effective addresses of longlatency cache-missing loads, called *delinquent loads*, and skip the remaining code, which the main thread must execute to ensure program correctness. Moreover, most pre-execution techniques do not allow helper threads to perform store operations. In other words, computed results by the helper threads are never integrated into the shared machine state so that pre-execution does not disrupt the main computation. Consequently, all dependences through memory are completely eliminated in the helper threads. Unless values necessary to compute the delinquent load addresses are communicated via memory, multiple helper threads can run in parallel without suffering from any dependence violation. Furthermore, since helper threads never affect the correctness of the main computation, they can be speculative and very aggressive. These unique characteristics of helper threads allow to overlap more memory accesses simultaneously, exploiting abundant amount of memory-level parallelism, which conventional multithreading techniques can hardly uncover.

Multithreading has been studied in the research community of computer architecture field for decades. Many research proposals investigate multiprogramming or parallel processing paradigms in large multiprocessor systems or recent single-chip multithreading processors. In particular, we view multithreading as a way to exploit thread-level parallelism that resides in workloads. Multiprogramming is a well-known example of multithreading where multiple independent application threads are executed on different hardware contexts available in a system. In multiprogramming, the amount of thread-level parallelism is the same as the number of applications that run together. As long as there are enough threads to be fed into the system, thread-level parallelism is easily extracted. However, it is sometimes hard to find applications to fully utilize the available hardware contexts in the system. Moreover, launching more threads may not be helpful to boost the overall processor throughput, especially when there exists hardware resource contentions among threads, e.g., memory bus saturation. Another limitation of multiprogramming is that it does not improve the performance of each individual program in the multiprogrammed workload. Thus multiprogramming is not helpful when improving single-thread performance is crucial. On the other hand, parallel processing extracts thread-level parallelism from a single program by dividing it into multiple threads to run in parallel. Parallel processing has been very effective for scientific workloads that perform intensive vector computations on huge data space. For nonscientific workloads, however, parallel processing is often ineffective since complicated dependence structures and control flow in those workloads prevent a program from being parallelized. Therefore, people have searched for new ways to uncover thread-level parallelism in a workload and exploit it, thereby improving the processor performance.

With the recent advent of single-chip multithreading processors such as the Simultaneous Multithreading (SMT) processor or Chip Multiprocessor (CMP), we believe a new era for multithreading has begun. Single-chip multithreading processors have opened up a great deal of opportunities in the multithreading paradigm due to their unique characteristics distinguished from conventional large multiprocessor systems. First, the communication delay between threads is greatly shortened compared to that of conventional multiprocessor systems since all inter-thread communications occur within a single die. Because of the small communication and thread synchronization cost, it becomes possible to exploit new types of thread-level parallelism at a much finer granularity, which was not feasible in large multiprocessor systems. Secondly, some critical hardware resources in single-chip multithreading processors are often shared or partitioned. Thus there exist intriguing tradeoffs regarding how to arbitrate those hardware resources among multiple threads. On the other hand, hardware-resource sharing is not always problematic, but sometimes opportunistic. For instance, sharing of a cache, e.g., the last-level cache that is located right above main memory, makes it possible for some of spare hardware contexts in a multithreading processor to be used for executing judiciously selected instruction sequences and bringing data cache blocks on behalf of the main computation, thereby helping the execution of the program indirectly.

Recent architectural trend in the industry is in favor of multithreading as well. Following Moore's law, the number of transistors integrated on a single die has increased exponentially, reaching almost one billion in the near future. To make use of the available transistor budget, people have started putting multiple cores and/or multiple threads on a single die to support multithreading. Since the first proposals of SMT and CMP processor models from academia, there have been a great deal of studies to examine the potential of exploiting such multithreading processors. After all those efforts, commercial single-chip multithreading processors like the Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor with Hyper-Threading Technology or IBM<sup>®</sup> POWER5 [34] have been recently released. Moreover, Sun Microsystems also announced their plan for productizing single-chip multithreading processors in the near future [51]. As the transistor count on a chip

Figure 1.1: Four approaches to automatically extract helper threads: a) compiler-based extraction, b) linker-based extraction, c) dynamic optimizer-based extraction, and d) hardware-based extraction. Techniques differ in when and how the code extraction is performed.

grows, we expect such trend toward multithreading processors to continue and there will be spare hardware contexts available for purposes other than performing useful computations, *e.g.*, *helper threading*. We believe pre-execution can play a crucial role in exploiting multithreading processors and thorough investigation of pre-execution is inevitable.

The most important issues in pre-execution is the construction of effective helper threads. Manual construction of helper threads is error-prone and cumbersome for a programmer. Hence for pre-execution techniques to be widely used for a variety of real-world workloads, this job of constructing helper threads must be fully automated. There are various approaches to generate helper threads automatically that can be categorized based on how and when in the program's lifetime helper threads are constructed.

Figure 1.1 shows four possible approaches to extract helper threads. Figure 1.1a depicts *compiler-based extraction* where a source-to-source compiler analyzes a program code and generates helper threads at the program source level [36]. Figure 1.1b illustrates *linker-based extraction*, which generates helper threads using binary analysis [41, 64]. The extracted helper thread code is in binary format and is attached to the original program binary. Figure 1.1c describes *dynamic optimizer-based extraction*<sup>1</sup>, which analyzes and extracts binary-level code similar to linker-based

$<sup>^{1}</sup>$ To our knowledge, dynamic optimizer-based extraction has not been investigated. However, we believe it to be a viable approach and include it here for completeness.

extraction, but does so at runtime using dynamic optimization techniques. Finally, Figure 1.1d shows *hardware-based extraction* [6, 19, 48, 73]. In this approach, helper threads are extracted from instruction traces at runtime by analyzing retired instructions using a special hardware structure. Extracted helper threads are cached so that they can be initiated when the corresponding code region is encountered in the future. By its very nature, the hardware approach is automated.

Each approach in Figure 1.1 exhibits very different characteristics due to the fact that code extraction is performed using different analysis techniques in different phases of a program's lifetime. This leads to several tradeoffs as described below:

- Information for code extraction. Dynamic optimizer- and hardware-based extraction makes use of runtime information to construct helper threads. However, the runtime overhead associated with dynamic optimization prevents detailed analysis, and the scope of trace analysis in hardware is limited to the size of the post-retirement queue that analyzes dependences between instructions. On the other hand, such runtime information is not available for compilerand linker-based approaches. Thus they need to rely on other sources, *e.g.*, offline profiles or static algorithms, to acquire necessary information for code extraction. However, compilerand linker-based approaches utilize high-level program information like the program or data structure, and such high-level information is more abundant in the earlier phases.

- Platform independence of extracted code. As the helper thread is extracted later in time, it becomes more dependent on the hardware platform. Since hardware-based extraction requires a special hardware structure to analyze instruction traces, it is strictly tied to the machine implementation. Whenever a new processor design is introduced, the trace analyzer must be redesigned accordingly. Linker-based extraction is less dependent on processor implementation than hardware-based extraction, but it still depends on the Instruction Set Architecture (ISA) of the target processor. For processors with different ISAs, one should have different binary analyzers to extract helper threads. Dynamic optimizer-based extraction is in the middle of hardware- and linker-based approaches; it sometimes requires special hardware that is tied with processor implementation and depends on the ISA of the proces-

sor. However, compiler-based extraction is completely independent of target platforms since it generates source code that can be compiled for any machine architecture. Consequently, this approach generates portable code.

- **Transparency to the user**. As the extraction occurs later in time, it becomes more transparent to the user. In hardware-based extraction, the trace analyzer performs analysis and constructs helper threads at runtime, and all the necessary hardware is implemented within the processor. Therefore, this approach is completely transparent to the user. Dynamic optimizer-based extraction has similar characteristics. However, the other two approaches are less transparent since they require additional compilation steps such as code analysis and offline profiling. Between the two approaches, compiler-based extraction is less transparent since it requires the program source code, which is sometimes unavailable as is the case for legacy codes.

- Hardware complexity. Compiler- and linker-based extraction does not affect hardware complexity of a processor since helper threads are extracted by software rather than hardware. Although the processor needs to support some features to handle multithreading such as suspending and forking threads, these are often provided by most multithreading processors. On the other hand, hardware-based extraction, of course, increases the hardware complexity due to the trace analyzer and cache structure for storing the extracted helper threads. Moreover, because of the newly introduced special hardware structures, the testing and validation cost increases in the hardware-based approach. Finally, hardware complexity of dynamic optimizer-based extraction depends on how much special hardware it requires.

All four approaches are worth pursuing since each approach has its own advantages as demonstrated above. In this thesis, however, we focus on compiler-based extraction due to the following reasons. First of all, compiler-based approach requires little modification to existing multithreading processors. Therefore, once a compiler for pre-execution is available, we can immediately apply and evaluate the generated helper threads. In addition, compiler-based extraction is platform-independent and the constructed helper threads, in the form of program source code, are portable. Moreover, we can utilize high-level program information to help construction of effective helper threads, and the capability of inter-procedure analysis of a compiler is another advantage of compiler-based approach. Finally, while other approaches, except for dynamic optimizer-based extraction, are evaluated previously in many research proposals, compiler-based construction of helper threads is relatively new and has not been fully investigated. Therefore, there is much room to explore.

#### 1.2 Contributions

This dissertation has several contributions as listed below.

- 1. Development of Compiler Algorithms for Pre-Execution. We develop several compiler algorithms to construct effective helper threads that perform data prefetching. At the heart of our compiler algorithms are three critical optimization techniques to expedite helper threads so that they can trigger cache misses in front of the main computation. First, program slicing eliminates noncritical code that is unnecessary for computing delinquent load addresses. Second, prefetch conversion removes blocking in helper threads by converting delinquent loads into nonblocking prefetch instructions. Third, speculative loop parallelization helps to overlap multiple memory accesses by exploiting thread-level parallelism within the target code region. In addition to these algorithms to speedup helper threads, we also propose algorithms to select optimal pre-execution regions that encompass the identified delinquent loads and to decide a proper thread initiation scheme for each pre-execution region. Finally, to evaluate compiler-based pre-execution in a real physical system, where the thread synchronization cost is significantly high, we propose three helper threading scenarios to invoke and synchronize helper threads.

- 2. Implementation of Pre-Execution Compiler Frameworks using SUIF. We implement the compiler algorithms and prototype five different compiler frameworks using the Stanford University Intermediate Format (SUIF) compiler infrastructure. We introduce one

very aggressive-complier implementation that makes use of powerful program slicer and offline profiles along with the SUIF. We also propose four reduced compilers, in which the design of compiler framework is simplified by substituting the external tools for static compiler algorithms. To the best of our knowledge, our compiler frameworks are the first source-level compiler to generate helper threads fully automatically without any manual intervention.

- 3. Development of Helper Thread Optimization Module in the Intel Compiler. We work with a group of people at Intel [35] to develop and improve the compiler optimization module to generate helper threads, which is built in the Intel Research Compiler Infrastructure (*Intel compiler* for short). The analyses and optimizations to enable pre-execution are performed on the Intel compiler's intermediate representation, IL0. Thus the compiler module is not dependent on a specific programming language, but applicable for various languages including C, C++, and FORTRAN. While the compiler module is also able to generate binaries targeting the Intel's Itanium Processor Family, in this thesis, we only generate helper threads for the IA-32 architecture as the target platform.

- 4. Evaluation of Compiler-Based Pre-Execution in a Research SMT Simulator. We perform various experiments to evaluate our SUIF-based compiler frameworks using a SimpleScalar-based SMT processor simulator that enables detailed timing simulations. In addition to measuring performance impact of pre-execution, we also investigate several aspects of the compiler algorithms, cache-miss coverage of the helper threads, contribution of each optimization algorithm to the program performance, comparison between the thread initiation schemes, and tradeoffs between the aggressive and reduced compilers. Our experimental results show the compiler-generated helper threads effectively eliminate cache misses in the main thread and significantly improve the performance of selected benchmarks from the SPEC CPU2000 and Olden Benchmark Suites. Moreover, we also show that our compilers make the right decision on selecting pre-execution regions and thread initiation schemes.

- 5. Evaluation of Compiler-Based Pre-Execution in a Real Physical System. We conduct physical experimentation to evaluate prefetching helper threads on real silicon, *i.e.*, the Intel Pentium 4 processor with Hyper-Threading Technology. We provide a complete procedure to perform physical experimentation with helper threads from collecting profile information, to generating helper threads using an optimization module in the Intel compiler, invoking and synchronizing helper threads based on static and dynamic thread initiation schemes, monitoring dynamic behavior of a program at runtime at a fine granularity, and dynamically throttling helper threads to reduce ineffectiveness of pre-execution. We believe our experimental methodology is a good reference for other kinds of physical-system-based evaluation. Our experimental results show that prefetching helper threads indeed provide wall-clock speedup for various benchmarks on the existing hyper-threaded processor.

- 6. Identification of Impediments to Speedup on Real Silicon. From our physical experimentation, we uncover impediments to speedup when applying helper threads in a real physical system. In hyper-threaded processors, hardware resource contention between the two logical processors possibly degrades the performance of the main thread when the helper thread does not help. Moreover, high thread-synchronization cost in a physical system limits frequent thread synchronization and communication at a fine granularity. To overcome these constraints in a physical system, we evaluate two different thread-synchronization mechanisms is crucial to achieve good performance gain with helper threads. In addition, certain runtime system to dynamically throttle helper threads by monitoring the program behavior can greatly help to get even more speedup with helper threads on real silicon.

- 7. Application of Compiler-Based Pre-Execution in a Multiprogramming Environment. We also apply prefetching helper threads in a multiprogramming environment. When performing pre-execution in such computing situation, multiple main threads compete with each other to acquire enough hardware contexts to launch helper threads. Since the number of hardware contexts in a multithreading processor is limited, we must intelligently allocate

this critical hardware resources to different main threads in order to maximize the overall processor throughput. We introduce mechanisms to arbitrate the main threads for hardware contexts and evaluate helper threads for selected multiprogrammed workloads on the SMT processor simulator. We observe the effectiveness of helper threads depends on the hardware context requirement of each individual workload to perform pre-execution. In summary, our experimental results show prefetching helper threads help to boost processor throughput in a multiprogramming environment by reducing latencies in individual application threads.

#### 1.3 Roadmap

The rest of the thesis is organized as follows. In Chapter 2, we provide necessary background about helper threading, multithreading execution paradigms, and previous proposals on data prefetching to better demonstrate how we get to focus on compiler-based pre-execution. Chapter 3 presents an overview of critical issues on constructing effective prefetching helper threads using a compiler. We discuss those issues in an implementation-independent way so that anyone can build a compiler framework to generate helper threads without being limited by the programming language or the target platform. Then the next four chapters, Chapters 4 through 7, introduce our compiler frameworks to construct prefetching helper threads and present the evaluation results. Chapter 4 demonstrates compiler algorithms for our SUIF-based compiler frameworks. We present various ways to design compilers for pre-execution and discuss tradeoffs between different implementations. In Chapter 5, we thoroughly investigate our SUIF-based compiler frameworks in a simulation-based evaluation environment. Chapter 6 examines many aspects of the compiler optimization module for pre-execution in the Intel compiler, and Chapter 7 reports the results of physical experimentation with prefetching helper threads in the Intel's hyper-threaded processor. We also discuss impediments to speedup with helper threads on real silicon and solutions to address those constraints. Chapter 8 investigates the performance of pre-execution in a multiprogramming environment and describes mechanisms to arbitrate multiple main threads for limited hardware contexts. Chapter 9 discusses related works, and Chapter 10 concludes the thesis and discusses

possible future directions of the research.

#### Chapter 2

## Background

This chapter provides the necessary background to better understand this thesis. We discuss three issues, *i.e.*, helper threading, multithreading, and data prefetching, and examine how pre-execution has evolved from these already-established research areas. First, we present helper threading, also known as *subordinate threading*, which works as the vehicle to realize pre-execution. While helper threading can be used for other purposes such as exception handling or fault tolerance, in this thesis, we focus on its use for latency tolerance, thereby improving a program performance indirectly. Then we introduce pre-execution as one particular example of multithreading execution paradigms. Especially, we view those multithreading paradigms, *e.g.*, multiprogramming, parallel processing, and pre-execution, as ways to exploit thread-level parallelism that resides in workloads. Finally, we focus on pre-execution's role as an effective data prefetching technique, where delinquent load addresses are *computed*, not *predicted*. Furthermore, pre-execution is a thread-based technique, in which the prefetching threads are *decoupled* from the main computation. Hence pre-execution has more freedom to control prefetching compared to conventional software prefetching techniques, where the instruction sequence for prefetching is integrated into the original program code and its progress is strictly tied with that of the main thread.

## 2.1 Helper Threading

With the advent of single-chip multithreading processors, in which multiple hardware contexts are closely tied while enjoying small communication delays, helper threading has been recognized as a very promising way to make use of the spare hardware contexts available in those multithreading processors such as the SMT or CMP [22, 14]. In helper threading, one or more helper threads run alongside the main thread to help its execution. Helper threading has two unique characteristics that open up many opportunities. First, in most helper threading techniques, the computed results by the helper threads are never integrated into the shared machine state. Thus helper threads do not contribute to boost the processor throughput, but help the execution of the main thread *indirectly.* Since helper threads never disrupt the main computation, one can apply very aggressive optimizations when constructing helper threads as long as such optimization helps to improve the performance of a program. Second, helper threads are asymmetric in that the execution of helper threads are decoupled from that of the main thread, and their code does not have to be extracted from the original program code. For instance, as to be more elaborated later in this section, one can run exception handler code on helper threads or even implement complicated hardware structures in software. Such unique characteristics of helper threading can greatly help the compiler optimization research area to develop various aggressive optimization algorithms without the need for ensuring the program correctness. Moreover, the asymmetry of helper threads also encourages development of various *helping actions* to help the program execution. In this thesis, we focus on pre-execution, which is the most popular helper threading technique to tolerate latencies in a program's execution. Since helper threading is a relatively new research area, we believe there exist many interesting aspects that have not yet fully investigated. Below, we present some of previously proposed uses of helper threading to assist the execution of a program.

Latency Tolerance. Helper threads can improve the performance of the main computation by tolerating latencies on its behalf. In this case, helper threads are extracted from the original program code and trigger long-latency delinquent events in front of the main thread, thereby hiding the latencies behind useful computations. Some examples include data prefetching [19, 36, 37, 35, 41, 42, 63, 81, 84], instruction prefetching [1], branch outcome precomputation [84], and virtual function call target prediction [61]. This type of helper thread is called *run-ahead thread* [7, 24, 73], and it is crucial to expedite helper threads so that they can trigger delinquent events early enough. In Chapters 4 and 6, we introduce various optimization algorithms to speedup helper threads.

**Exception Handling**. When an exception occurs, one can run the exception handler code on a helper thread and let the main thread keep making progress by executing instructions that are independent of the faulting instruction [86]. In this case, helper threading effectively decouples otherwise serialized code execution and overlaps the execution of the exception handler code and useful computation. The performance improvement depends on the frequency of exceptions that occur during the program execution and the amount of independent instructions, whose execution can be overlapped with the execution of the exception handler code.

**Fault Tolerance**. By running the same program redundantly on a helper thread, one can detect and recover faults that occur during a program execution. Since helper thread's execution is totally redundant, this type of helper threading neither contributes to processor throughput nor improves program performance. However, it tolerates faults to preserve the correctness of a program [50, 78].

Implementation of Structures and Algorithms in Software. Using helper threading, one can implement complicated hardware structures or algorithms in software, *e.g.*, a value predictor [85] or branch prediction algorithm [14]. This can ease the hardware complexity of a processor and reduce the testing and validation cost associated with introducing new hardware into the processor design. Note, the code running on helper threads has nothing to do with the original program, but it still helps the execution of the main thread.

## 2.2 Multithreading

Multithreading has been studied extensively in both academia and industry [3, 39, 65]. Traditionally, people have used multithreading to boost the processor throughput or to improve single program performance. In this thesis, we view multithreading as a way to uncover and exploit thread-level parallelism residing in workloads, and pre-execution effectively exploits a new form of parallelism via construction of much aggressive and speculative helper threads. Below, we examine several well-known multithreading execution paradigms and discuss how those paradigms differ from each other in exploiting thread-level parallelism in workloads.

#### 2.2.1 Multiprogramming

Multiprogramming has been a popular way to utilize multiprocessor systems and increase the overall processor throughput by running multiple independent application threads simultaneously. Since any communication or synchronization between threads is rarely required in a multiprogramming environment, one can easily extract thread-level parallelism as long as there are enough jobs to process. Hence multiprogramming exploits totally unrelated parallelism from different applications, and the amount of thread-level parallelism is the same as the number of application threads that run together. However, it is sometimes not possible to find multiple independent applications to fill up the available hardware contexts in the system. Moreover, in many multiprocessor systems, critical hardware resources such as the memory bus are often shared and even saturated with large number of actively running threads. Thus feeding more threads into the system may not help to increase the processor throughput. On the other hand, while boosting the overall processor throughput is very important, improving the single program performance is often the most crucial issue under certain circumstances. However, multiprogramming does not help to improve single program performance; even worse, it often sacrifices the performance of each individual program for the overall throughput. In the next two subsections, we discuss ways to speedup a single program via multithreading.

## 2.2.2 Parallel Processing

One way to improve the performance of a single program is to divide the program into multiple subprograms and run them in parallel on a multiprocessor system. This is called *parallel processing.* Below, we discuss two different parallel processing paradigms; one is conventional parallel processing and the other is recent thread-level data speculation technique.

**Conventional parallel processing in multiprocessor systems**. Parallel processing has been extensively used in conventional multiprocessor systems and particularly successful for scientific workloads. When partitioned into multiple subprograms, each thread usually runs almost independently, thereby exploiting thread-level parallelism in a single program. In parallel processing, all threads are completely nonspeculative and perform useful computations that contribute to the processor throughput. Therefore, a compiler or programmer must guarantee that no dependence violations occur as a consequence of parallelization, and synchronization among different threads

should be properly handled. While conventional parallel processing has been very successful in extracting thread-level parallelism from scientific workloads, it is often not effective for nonscientific codes that account for a large portion of modern workloads. This leads to the invention of thread-level speculation technique, which is discussed below.

Thread-level speculation on chip multiprocessors. With the recent advent of the CMP that supports much finer-grain thread synchronization than conventional multiprocessor systems, a new form of parallel processing, called Thread-Level Speculation (TLS), has been introduced and studied widely in the research community. In TLS, a single program is divided into multiple threads speculatively, assuming no memory dependence between threads. By running those multiple computation threads in parallel, TLS exploits thread-level parallelism in the program. In order to guarantee the correct program execution, the computed results by each thread are committed sequentially following the original program order. In addition, the TLS technique requires special hardware support to detect and recover from any dependence violation between memory operations, and adopts the versioning cache to hold intermediate results until a thread commits. As long as there is no true dependence between a store operation and later load instructions, those partitioned threads can run simultaneously and exploit thread-level parallelism. Therefore, the amount of parallelism in TLS depends on how frequently memory dependence violations occur, and it also varies based on how the target program is partitioned and the granularity of each thread. Hence it is the compiler's or programmer's responsibility to find the appropriate code regions to partition such that optimal performance can be achieved. However, while TLS tries to improve the performance of nonscientific workloads as well as scientific workloads via speculative parallelization, complicated dependence structures in nonscientific workloads often limit successful exploitation of thread-level parallelism.

#### 2.2.3 Pre-Execution

Pre-execution has received much attention from the research community as a novel latencytolerance technique. In pre-execution, one or more helper threads run in front of the main computation and trigger long-latency delinquent events that significantly degrade the performance of a program. In particular, we view pre-execution as a new source of extracting abundant amounts of thread-level parallelism from a program. This is because the helper thread code contains much less dependences than parallel processing or TLS for the following reasons. In many pre-execution techniques, helper threads are constructed as a separate instruction sequence and they never affect the correctness of the main computation since all the stores to global variables and heap objects are removed to eliminate any side effects from helper threads. In turn, this effectively breaks all dependences through memory. Since helper threads have separate code and no side effects, one has significant freedom to perform aggressive optimizations on the helper thread code without disrupting the main computation, which would be totally unacceptable in conventional optimizing compilers. One important optimization technique in pre-execution is program slicing, which eliminates noncritical code that is unnecessary to compute delinquent events. After program slicing, many of dependences through noncritical computations are removed from the helper threads, and thus helper threads can trigger those targeted delinquent events accurately even though the target code region is speculatively parallelized. In this sense, pre-execution can be viewed as a new form of *asymmetric* parallel processing technique that overlaps critical events executed in helper threads and noncritical computations performed by the main thread. We observe those kernels that compute delinquent events are easily and correctly parallelizable after program slicing and store removal. Thus compared to TLS that carries all the dependences in a program, pre-execution is a much more powerful technique in exploiting thread-level parallelism.

## 2.3 Data Prefetching

In Section 2.1, we introduce pre-execution as a general latency-tolerance technique to eliminate stalls in a program execution. In this section, we examine the use of pre-execution for data prefetching and show how exploitation of thread-level parallelism, especially memory-level parallelism, via pre-execution can result in higher program performance. We compare pre-execution with other previously proposed data prefetching techniques and discuss the interesting tradeoffs. In this thesis, we choose the data cache miss as the target delinquent event to be pre-executed since tolerating memory latency is very important for several reasons. Wulf and McKee [83] report the clock frequency of a processor increases by approximately 60% every year whereas the main memory access time improves only about 7% for the same period. Therefore, the speed-gap between a processor and memory subsystem is increasing exponentially, and the memory latency will reach thousands of cycles in the near future. This phenomenon is also known as the *Memory-wall Problem* [83]. Since the memory stall time becomes a dominant factor that limits processor performance in many workloads, there have been plethora of proposals to overcome this challenge by having cache structures in the memory hierarchy, executing instructions out-of-order, or prefetching data cache blocks. Because we believe both cache structures that hold frequently accessed data blocks and out-of-order execution are straightforward and have been extensively studied already, we rather focus on data prefetching and discuss the effectiveness of pre-execution as a novel thread-based prefetching technique.

#### 2.3.1 Prediction-Based Prefetching

One way to issue prefetches for future memory references is to watch the memory address stream and detect repetitive patterns. Based on the identified patterns, one can *predict* the next memory reference address and issue a prefetch accordingly. This type of prefetching is called *prediction-based prefetching*. There have been many proposals that belong to this category. One example is the stride prefetcher [16] where a special hardware structure monitors the address stream and captures a stride between two memory references. A slightly advanced technique is to use a hardware Markov table to hold possible future memory references or repetitive address sequences; this is also known as *Markov prefetcher* [32]. Markov prefetcher does not necessarily require stride behavior in memory access pattern, but it makes use of the correlation between load addresses. These prediction-based hardware prefetching techniques are effective for scientific workloads that exhibit regular memory access patterns. However, for those memory references without any repetitive pattern, usually found in nonscientific workloads, prediction-based prefetching techniques cannot predict future memory references and thus they are useless.

#### 2.3.2 Execution-Based Prefetching

To prefetch for memory references with both irregular and regular memory access patterns, one of the most effective ways is to actually *execute* an instruction sequence, which generates the cache-missing load addresses, earlier than the main computation. This type of prefetching is called *execution-based prefetching*. An execution-based prefetching technique relies on program semantics and extracts kernels that compute load addresses from the original program code. Execution-based prefetching has a wide spectrum of examples from conventional software prefetching, to hardwarebased techniques, and recent thread-based techniques, as described below.

Software Prefetching. Software prefetching techniques exploit a loop structure's iterative nature. In other words, the prefetch instructions are inserted into the loop body, but they target load instances in the future loop iterations [49]. Software prefetching is the most primitive form of preexecution, where only a handful of instructions are executed to compute future memory references. However, since the prefetch instructions are integrated into the main program code, there are some limitations. One is the overhead issue; the newly inserted code may delay the execution of the main thread, which is a problem if the targeted loop does not contain much work. Moreover, the speed of prefetching is strictly tied with the progress of the main thread, and thus the prefetches may not be timely depending on the dynamic cache behavior. In addition, software prefetching does not execute control flow and is often neither aggressive nor speculative. In summary, tight coupling between the main program and prefetching makes software prefetching ineffective to handle pointer-chasing traversals, and the poor execution capability in software prefetching limits its use for complicated address computation patterns, which are often found in integer applications.