#### ABSTRACT

Title of dissertation: DESIGN SPACE EXPLORATION FOR

SIGNAL PROCESSING SYSTEMS USING LIGHTWEIGHT DATAFLOW GRAPHS

Lin Li

Doctor of Philosophy, 2018

Dissertation directed by: Professor Shuvra S. Bhattacharyya

Dept. of Electrical and Computer Engineering, and Institute for Advanced Computer Studies

Digital signal processing (DSP) is widely used in many types of devices, including mobile phones, tablets, personal computers, and numerous forms of embedded systems. Implementation of modern DSP applications is very challenging in part due to the complex design spaces that are involved. These design spaces involve many kinds of configurable parameters associated with the signal processing algorithms that are used, as well as different ways of mapping the algorithms onto the targeted platforms.

In this thesis, we develop new algorithms, software tools and design methodologies to systematically explore the complex design spaces that are involved in design and implementation of signal processing systems. To improve the efficiency of design space exploration, we develop and apply compact system level models, which are carefully formulated to concisely capture key properties of signal processing algorithms, target platforms, and algorithm-platform interactions.

Throughout the thesis, we develop design methodologies and tools for integrating new compact system level models and design space exploration methods with lightweight dataflow (LWDF) techniques for design and implementation of signal processing systems. LWDF is a previously-introduced approach for integrating new forms of design space exploration and system-level optimization into design processes for DSP systems. LWDF provides a compact set of retargetable application programming interfaces (APIs) that facilitates the integration of dataflow-based models and methods. Dataflow provides an important formal foundation for advanced DSP system design, and the flexible support for dataflow in LWDF facilitates experimentation with and application of novel design methods that are founded in dataflow concepts. Our developed methodologies apply LWDF programming to facilitate their application to different types of platforms and their efficient integration with platform-based tools for hardware/software implementation. Additionally, we introduce novel extensions to LWDF to improve its utility for digital hardware design and adaptive signal processing implementation.

To address the aforementioned challenges of design space exploration and system optimization, we present a systematic multiobjective optimization framework for dataflow-based architectures. This framework builds on the methodology of multiobjective evolutionary algorithms and derives key system parameters subject to time-varying and multidimensional constraints on system performance. We demonstrate the framework by applying LWDF techniques to develop a dataflow-based architecture that can be dynamically reconfigured to realize strategic configurations in the underlying parameter space based on changing operational requirements.

Secondly, we apply Markov decision processes (MDPs) for design space exploration in adaptive embedded signal processing systems. We propose a framework, known as the Hierarchical MDP framework for Compact System-level Modeling (HMCSM), which embraces MDPs to enable autonomous adaptation of embedded signal processing under multidimensional constraints and optimization objectives. The framework integrates automated, MDP-based generation of optimal reconfiguration policies, dataflow-based application modeling, and implementation of embedded control software that carries out the generated reconfiguration policies.

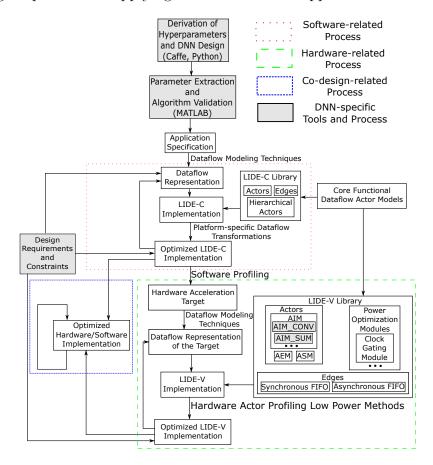

Third, we present a new methodology for design and implementation of signal processing systems that are targeted to system-on-chip (SoC) platforms. The methodology is centered on the use of LWDF concepts and methods for applying principles of dataflow design at different layers of abstraction. The development processes integrated in our approach are software implementation, hardware implementation, hardware-software co-design, and optimized application mapping. The proposed methodology facilitates development and integration of signal processing hardware and software modules that involve heterogeneous programming languages and platforms.

Through three case studies involving complex applications, we demonstrate the effectiveness of the proposed contributions for compact system level design and design space exploration: a digital predistortion (DPD) system, a reconfigurable channelizer for wireless communication, and a deep neural network (DNN) for vehicle classification.

# DESIGN SPACE EXPLORATION FOR SIGNAL PROCESSING SYSTEMS USING LIGHTWEIGHT DATAFLOW GRAPHS

by

## Lin Li

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2018

Advisory Committee:

Professor Shuvra S. Bhattacharyya, Chair/Advisor

Professor Rajeev Barua

Professor Charalampos Papamanthou

Professor Marilyn Wolf

Professor Ramani Duraiswami

Dedication

To my family

#### Acknowledgments

I would like to thank my advisor, Professor Shuvra S. Bhattacharyya, for his kind support, shepherd, and encouragement during the past few years. His intelligence, patience, and his pursuit of excellence on academics and teaching have inspired me significantly in both my Ph.D. study and my life. It is my great honor to have him as my advisor.

I also want to thank my committee members, Professor Rajeev Barua, Professor Charalampos Papamanthou, Professor Marilyn Wolf, and Professor Ramani Duraiswami for providing insightful and valuable suggestions and comments.

I am grateful to all members of DSPCAD research group and other colleagues and collaborators, especially Professor Marilyn Wolf, Professor Francesca Palumbo, Ms. Tiziana Fanni, and Dr. Timo Viitanen. I would also like to thank Marshall Plan Foundation and Fachhochschule Salzburg for providing a great opportunity for collaborative research.

Finally I give my special thanks to my parents and my boyfriend Chen Chen for their continuous and unconditional love and support.

This research was sponsored in part by the U.S. National Science Foundation, the Austrian Marshall Plan Foundation, and the Laboratory for Telecommunications Sciences.

# Table of Contents

| Lis | st of Figures                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | Introduction  1.1 Compact System Level Models                                                                                                                                                                                                                                                    |  |  |  |  |

| 2   | Constrained Optimization for Digital Predistortion (DPD) Systems 2.1 Introduction                                                                                                                                                                                                                |  |  |  |  |

| 3   | Evolutionary Optimization for DPD Architectures23.1 Introduction23.2 Related Work23.3 Adaptive Dataflow-based DPD Architecture23.4 Optimization Metrics and Design Space23.5 Multiobjective Optimization Using Evolutionary Algorithm33.6 Experimental Setup and Simulation Results33.7 Summary4 |  |  |  |  |

| 4   | ssign of Adaptive Signal Processing Systems Using Markov Decision Prosses  Introduction                                                                                                                                                                                                          |  |  |  |  |

| 5   | An Integrated Hardware/Software Design Methodology for Signal Processing Systems 7 5.1 Introduction                                                                                                                                                                                              |  |  |  |  |

| 6   | Conclusions and Future Work 15 6.1 Conclusions                                                                                                                                                                                                                                                   |  |  |  |  |

Bibliography 158

# List of Figures

| <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | Predistorter structure for the joint predistortion of PA and I/Q modulator impairments                                                                                                    | 12<br>13<br>18 |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                                           | tem. ACPR and EVM measurements are presented using absolute values — thus, higher values indicate better performance                                                                      | 20             |

| 3.1                                                       | Dataflow graph model of the predistortion filter                                                                                                                                          | 28             |

| 3.2<br>3.3                                                | Multiobjective optimization model for DPD system                                                                                                                                          | 35             |

| 3.4                                                       | PS for (a) QPSK, (b) 16–QAM, (c) 64–QAM                                                                                                                                                   | 41             |

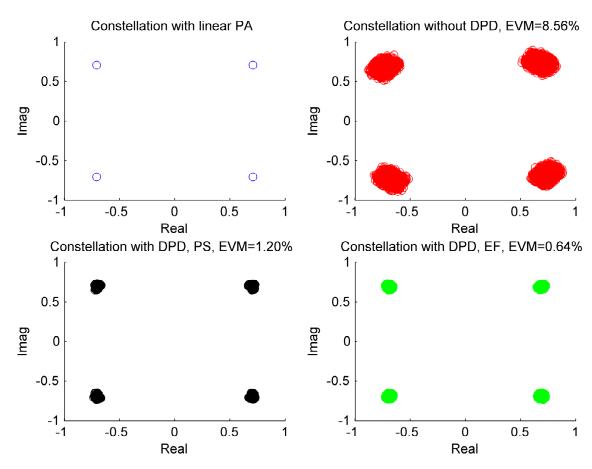

| 3.5                                                       | DPD, with DPD under configuration obtained from PS and EF Output constellation of the ideal linear PA, the Wiener PA model without DPD, with DPD under configuration obtained from PS and | 43             |

|                                                           | EF                                                                                                                                                                                        | 44             |

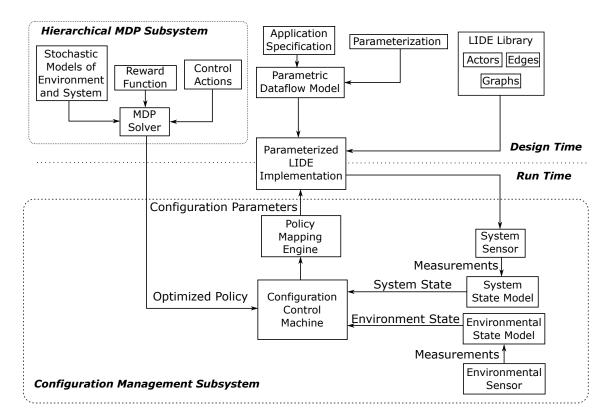

| 4.1                                                       | An illustration of the HMCSM framework for design and implemen-                                                                                                                           |                |

| 4.0                                                       | tation of adaptive signal processing systems                                                                                                                                              | 56             |

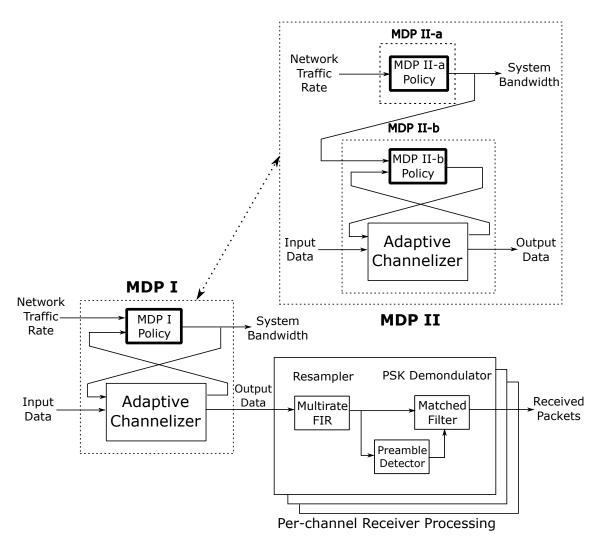

| 4.2                                                       | Block diagram of receiver signal processing and two MDP schemes                                                                                                                           | 63             |

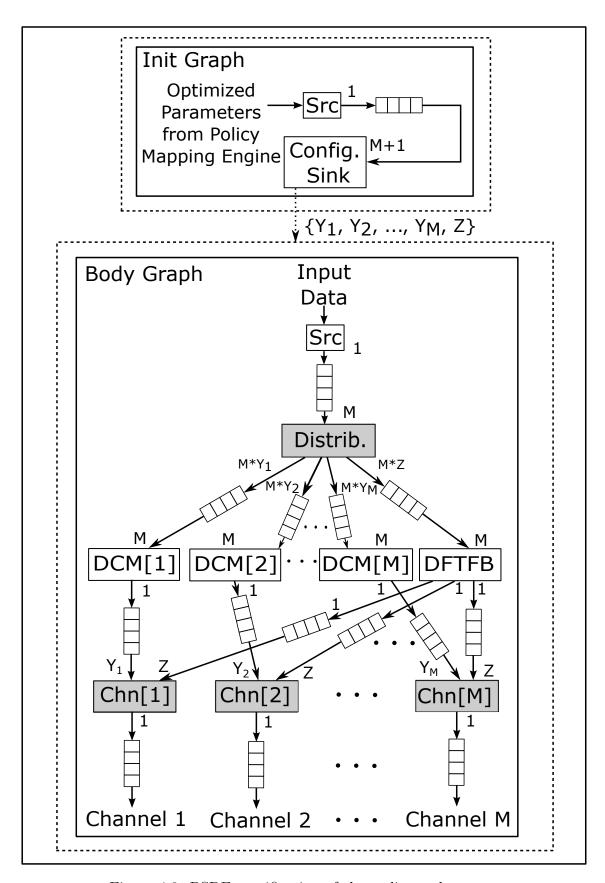

| 4.3                                                       | PSDF specification of channelizer subsystem                                                                                                                                               | 65             |

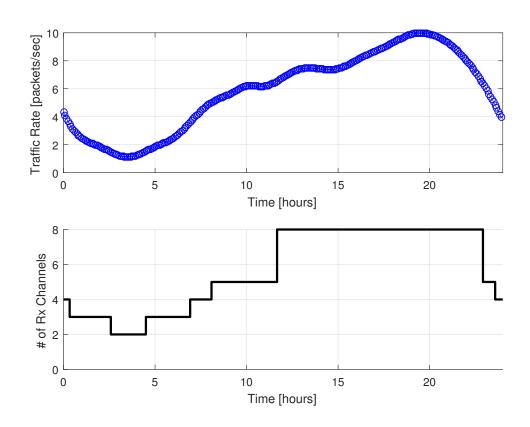

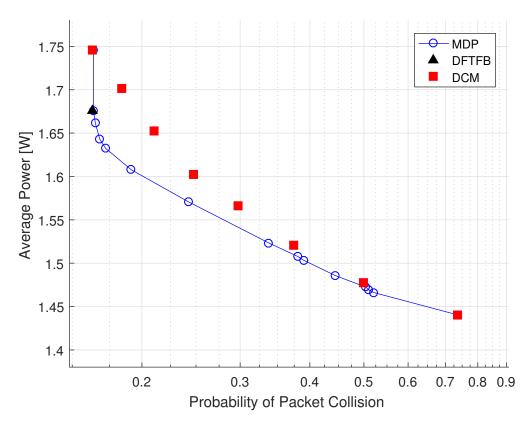

| $4.4 \\ 4.5$                                              | Simulation results for MDP-I                                                                                                                                                              | 71             |

|                                                           | designs                                                                                                                                                                                   | 73             |

| 5.1                                                       | An illustration of STMCM in the context of DNN system design                                                                                                                              | 83             |

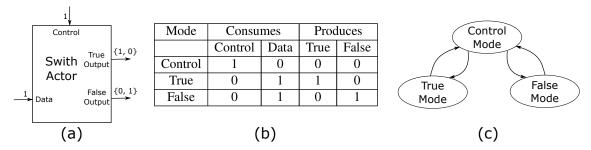

| 5.2                                                       | Switch actor in CFDF. (a) Switch Actor, (b) Dataflow Table, (c)                                                                                                                           |                |

|                                                           | Mode Transition Diagram between CFDF Modes                                                                                                                                                | 86             |

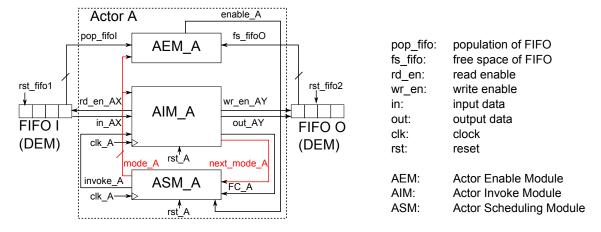

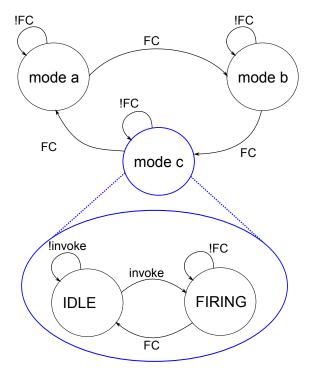

| 5.3                                                       | Illustration of an LWDF-V-based actor                                                                                                                                                     | 92             |

| 5.4                                                       | Example of an AIM FSM for a CFDF actor with three modes                                                                                                                                   | 95             |

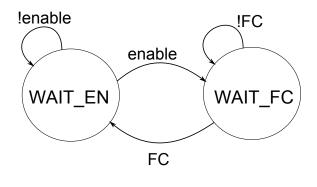

| 5.5                                                       | Illustration of LWDF-V-based actors communication                                                                                                                                         | 97             |

| 5.6                                                       | Example of a AEM with three different firing condition for three                                                                                                                          |                |

|                                                           | possible modes.                                                                                                                                                                           |                |

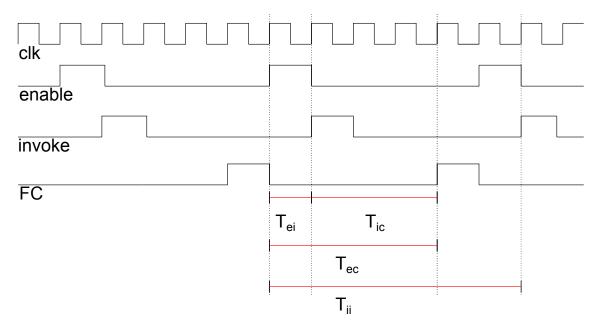

| 5.7                                                       | An example of an FSM that controls an ASM                                                                                                                                                 |                |

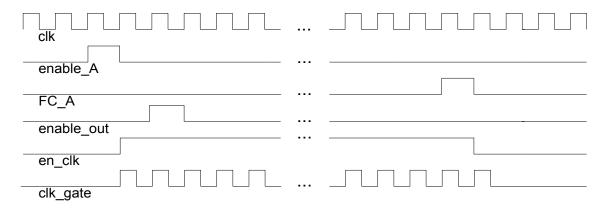

| 5.8                                                       | Examples of signal waveforms during execution of an LWDF-V actor.                                                                                                                         |                |

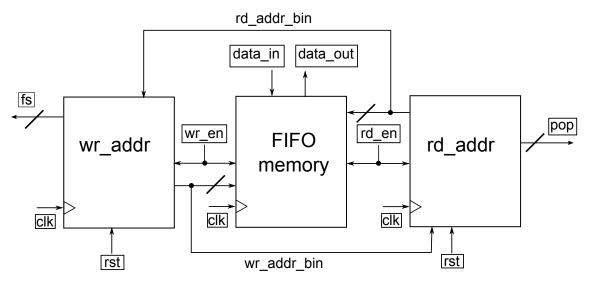

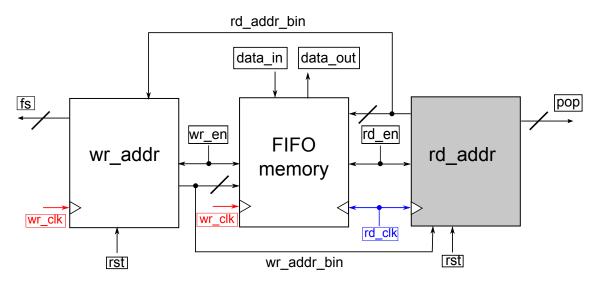

| 5.9                                                       | Synchronous FIFO design                                                                                                                                                                   | 102            |

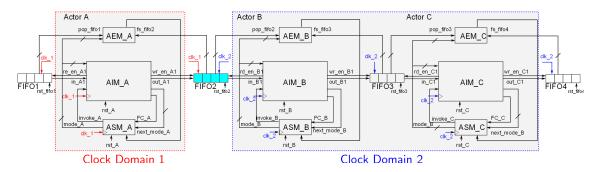

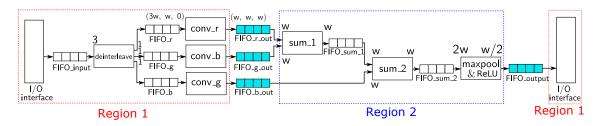

| 5.10                                                      | Illustration of an LWDF-V-based implementation of a CFDF graph                                                                                                                            | 405            |

| P 11                                                      | that consists of three actors                                                                                                                                                             |                |

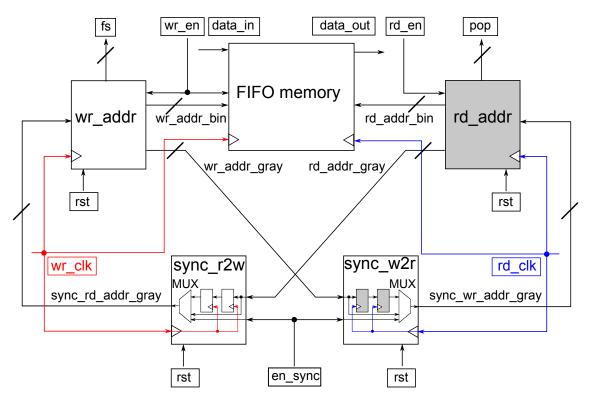

|                                                           | Asynchronous FIFO design in LIDE-V                                                                                                                                                        |                |

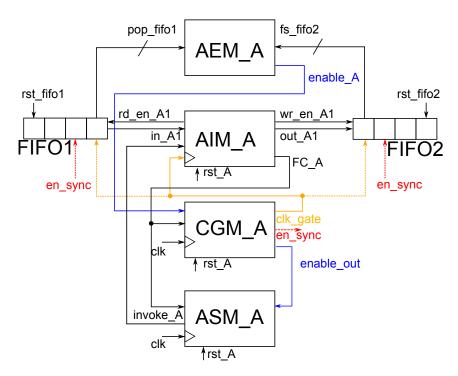

|                                                           | Clock gating in a LIDE-V actor                                                                                                                                                            |                |

|                                                           | Signal waveforms in the clock gating module                                                                                                                                               | 110            |

| .) 14                                                     | ESCHOO-VALUE FIRLL OCSION IN LATTE-V                                                                                                                                                      | 1 1 1 1        |

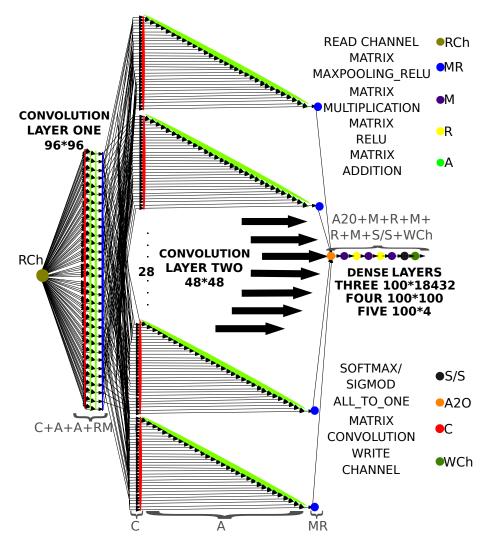

| 5.15 | DNN for automatic discrimination of four types of vehicles 113                                            |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5.16 | The code segment that implements loop tiling within the LIDE-C                                            |  |  |  |  |

|      | actor for convolution                                                                                     |  |  |  |  |

| 5.17 | LIDE-V implementation for the accelerated SFM                                                             |  |  |  |  |

| 5.18 | An illustration of the hierarchical actor associated with Design $SFM_h$ . 127                            |  |  |  |  |

| 5.19 | 5.19 Reference configuration for hardware/software co-design exploration                                  |  |  |  |  |

|      | in our experiments                                                                                        |  |  |  |  |

| 5.20 | Performance evaluation of convolution actors with different image                                         |  |  |  |  |

|      | dimensions: (a) $48 \times 48$ , (b) $96 \times 96$ , (c) $750 \times 750$ , (d) $1500 \times 1500$ . 137 |  |  |  |  |

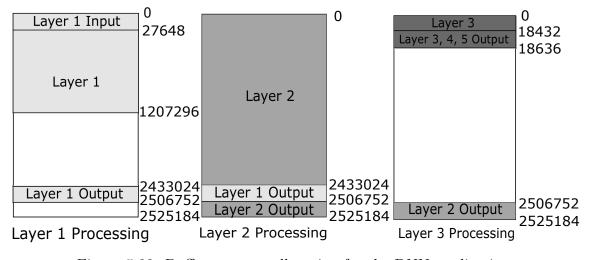

| 5.21 | Buffer memory and communication requirements in the DNN archi-                                            |  |  |  |  |

|      | tecture                                                                                                   |  |  |  |  |

| 5.22 | Buffer memory allocation for the DNN application                                                          |  |  |  |  |

## Chapter 1

#### Introduction

In recent years, increased requirements on functionality and flexibility in digital signal processing (DSP) applications have imposed significant new challenges on the design and implementation of embedded signal processing systems. Many state-of-the-art signal processing applications involve challenging requirements on flexibility and reconfigurability so that the systems can be adaptive to time-varying constraints or changes in the operational environment. Additionally, implementation of these applications is subject to multidimensional design criteria, such as competing objectives or constraints that involve power consumption, system accuracy, hardware cost, and processing speed. Thus, flexible adaptation across diverse system configurations, and efficient design space exploration are key aspects in advanced design methodologies for DSP systems.

Due to the requirements of DSP system design described above, the design space exploration for signal processing systems is both important and challenging. Effective design space exploration in this context includes experimenting with different sets of system configuration parameters, exploring alternative designs with different optimization methods, and assessing trade-offs across the relevant optimization objectives. In this work, we propose software tools, algorithms, and methodologies to efficiently and systematically explore the design space of DSP systems across

multiple levels of abstraction, including algorithm, software, and hardware.

## 1.1 Compact System Level Models

In this thesis, we develop new algorithms, software tools and design methodologies to systematically explore the complex design spaces that are involved in deploying signal processing systems. To improve the efficiency of design space exploration, we develop and apply compact system level models, which are carefully formulated to concisely capture key properties of signal processing algorithms, target platforms, and algorithm-platform interactions.

Throughout the thesis, we develop design methodologies and tools for integrating new compact system level models and design space exploration methods with lightweight dataflow (LWDF) techniques for design and implementation of signal processing systems [1]. LWDF is a previously-introduced approach for integrating new forms of design space exploration and system-level optimization into design processes for DSP systems. LWDF provides a compact set of retargetable application programming interfaces (APIs) that facilitates the integration of dataflow-based models and methods with different hardware platforms and their associated platform-based design tools.

Dataflow provides an important formal foundation for advanced DSP system design [2, 3], and the flexible support for dataflow in LWDF facilitates experimentation with and application of novel design methods that are founded in dataflow concepts [4]. Our developed methodologies apply LWDF programming to facilitate

their application to different types of platforms and their efficient integration with platform-based tools for hardware/software implementation. Additionally, we introduce novel extensions to LWDF to improve its utility for digital hardware design and adaptive signal processing implementation.

## 1.2 Application Areas

We investigate three major application areas of signal processing systems to demonstrate our contributions in design space exploration using compact system level models and lightweight dataflow techniques. These are the areas of digital predistortion (DPD) and channelizer design for wireless communications, and deep neural networks (DNNs) for computer vision.

## 1.2.1 Digital Predistortion

Digital predistortion (DPD) is an application area in wireless communications that we have applied our proposed design place exploration methods to. DPD is a technique to counteract impairments, such as I/Q mismatch, power amplifier (PA) nonlinearities, and local oscillator (LO) leakage, that compromise the linearity of radio transmitter amplifiers [5]. Using our proposed design space exploration techniques, we have developed a novel reconfigurable DPD architecture. The architecture provides flexible configuration across different combinations of polynomial orders, bit-widths, and filter orders that are relevant to key trade-offs in DPD system operation.

In Chapter 2 and Chapter 3, we present a dataflow-based implementation of our DPD architecture as a case study of our design optimization framework. Through this case study, we concretely introduce new methods for multiobjective design optimization on which the framework is based. These methods are applied to efficiently navigate the complex design spaces associated with DPD implementation. Through extensive experiments, we demonstrate the effectiveness of our configurable DPD architecture and design optimization framework in enabling efficient, adaptive DPD system operation.

#### 1.2.2 Channelizer Design

In wireless communication, the channelizer is a key part of a receiver that extracts one or more radio channels of distinct bandwidths from a digitized wideband input signal. By adapting the configuration of the channelizer based on the communication scenario, we seek to optimize its energy efficiency while ensuring that it extracts the number of channels that is required by the communication scenario at any given time.

In Chapter 4, we develop a novel adaptive signal processing architecture to achieve these objectives, and we apply lightweight dataflow techniques to implement the architecture efficiently on a state-of-art embedded processing platform.

#### 1.2.3 Deep Neural Networks

Deep learning is another application area in which efficient design space exploration is of great importance. Deep learning is a sub-field of machine learning that has attracted a large amount of attention from academia and industry in recent years. The core component of a deep learning system is the deep neural network (DNN), a neural network with hidden layers to optimize an objective function for the targeted learning purpose. Deep learning has been applied in numerous fields, such as speech recognition, computer vision, machine translation, and autonomous driving, with huge success in cases where a sufficient volume of labeled data is available for training (e.g., see [6]).

Presently, there is a growing trend of deploying deep learning algorithms on mobile devices, such as smart phones and tablets, in real-time applications. For example, Facebook has presented a real-time video style transfer on mobile devices using Caffe2Go, a lightweight deep learning framework [7]. The migration of DNNs from high-end machines with huge amounts of computational resources to low-end devices with limited resources is challenging. For example, a DNN with many layers may not fit into the random access memory (RAM) of a mobile device. In Chapter 5, as a case study of our proposed new hardware/software design methodologies, we explore in depth the design space of a DNN application for vehicle classification.

#### 1.3 Outline of Thesis

The remainder of this dissertation is organized as follows.

The emphasis of Chapter 2 and Chapter 3 is on design space optimization for DPD systems. In particular, Chapter 2 presents models and methods for efficient search of the complex, multidimensional design spaces associated with DPD systems, and Chapter 3 extends the work in Chapter 2 by proposing a novel evolutionary algorithm framework for multiobjective optimization of DPD systems. In Chapter 3, we demonstrate the proposed framework by applying it to develop an adaptive DPD architecture.

In Chapter 4, we propose the Hierarchical MDP framework for Compact System-level Modeling (HMCSM), which applies Markov decision processes (MDPs) to enable autonomous adaptation of embedded signal processing under multidimensional constraints and optimization objectives. The framework integrates automated, MDP-based generation of optimal reconfiguration policies, dataflow-based application modeling, and implementation of embedded control software that carries out the generated reconfiguration policies. The effectiveness of HMCSM is demonstrated through experiments with an adaptive channelizer for wireless communications.

In Chapter 5, we develop a dataflow-based methodology, along with supporting software tools and libraries, for integrated hardware/software co-design and design optimization of signal processing systems. As outlined above in Section 1.2.3, we develop a DNN implementation for vehicle classification as a demonstration of the proposed design methodology.

We conclude in Chapter 6 with a summary of the thesis followed by a discussion on useful directions for future work.

## Chapter 2

Constrained Optimization for Digital Predistortion (DPD) Systems

As a starting point of design space exploration for DPD systems, in this chapter, we develop new models and methods for exploring multidimensional design spaces associated with digital predistortion (DPD) systems. DPD systems are important components for power amplifier linearization in wireless communication transceivers. In contrast to conventional DPD implementation methods, which are focused on optimizing a single objective — most commonly, the adjacent channel power ratio (ACPR) — without systematically taking into account other relevant metrics, we consider DPD system implementation in a multiobjective optimization context. In our targeted multiobjective context, trade-offs among power consumption and multiple DPD performance metrics are jointly optimized subject to performance constraints imposed by the given modulation scheme. Through synthesis and simulation results, we demonstrate that DPD systems derived through our design space exploration techniques exhibit significantly improved trade-offs among multidimensional implementation criteria, including energy consumption, ACPR, and symbol error-rate. Additionally, we perform experiments using three different Long-Term Evolution (LTE) modulation schemes, and we demonstrate that our multiobjective optimization approach significantly enhances system adaptivity in response to changes in the employed modulation scheme.

Material in this chapter was published in [8].

#### 2.1 Introduction

In wireless communication systems, power amplifier (PA) nonlinearities, I/Q mismatch, and leakage in the local oscillator (LO) introduce power leakage into adjacent bands, interference between I and Q baseband signals, and direct current (DC) offset, respectively. In the frequency domain of the transmitted signal, the effects of these impairments are translated as power leakage into adjacent channels. Digital predistortion (DPD) is a widely investigated technique (e.g., see [9, 10, 11, 12, 13]) to counteract such impairments by applying carefully-calculated distortion to the signal prior to transmission. In this chapter, we develop new methods for design optimization of field-programmable gate array (FPGA)—based DPD systems that are novel in their adaptability to different modulation constraints, and their support for multidimensional design space exploration. Specifically, we develop methods to formulate and perform multiobjective optimization across the key DPD operational metrics of power consumption, adjacent channel power ratio, and error vector magnitude, which we abbreviate as PAE.

Our work builds on the DPD algorithm introduced in [5]. In this chapter, we go beyond the work in [5] through a deep investigation into implementation aspects of this DPD algorithm. In contrast, the study in [5] is primarily at the levels of theoretical analysis and algorithm-level (MATLAB) simulation evaluation.

Unlike earlier DPD architectures (e.g., see [10, 14]), the DPD algorithm pro-

posed in [5] is one of the first DPD techniques that jointly compensates for PA nonlinearities and I/Q modulator impairments. Conventional digital predistorters are constructed using serial configurations. For example, the work in [10] is focused on modeling and compensation of frequency-dependent gain/phase imbalance and DC offset. For more details on this serial digital predistorter structure, we refer the reader to [10]. Instead of using a serial structure, the DPD architecture in [5] employs an extended parallel Hammerstein structure, which decomposes DPD operation into direct and conjugate predistortion subsystems. Such a decomposed structure provides additional degrees of freedom in the predistorter design compared to the serial structures used in traditional DPD systems.

The problem of parameter optimization for DPD systems has been studied extensively in prior work. These works can be distinguished in terms of three key (vector-valued) DPD parameters — the filter orders, polynomial orders, and filter coefficients. For example, Çiflikli and Yapící and Sperlich et al. apply genetic algorithms to optimize the filter coefficients while assuming fixed filter and polynomial orders [9, 15]. In contrast, Abdelhafiz et al. jointly optimize all three parameters [16]; however, this optimization is performed with respect to only a single objective — the adjacent channel power ratio (ACPR). Freiberger et al. determine DPD filter coefficients based on constrained multiobjective optimization [17]; however, the work in this chapter also assumes fixed polynomial and filter orders, and is specialized to a specific modulation scheme (64–QAM).

To the best of our knowledge, the work of this chapter is the first to go beyond the aforementioned works by simultaneously (1) considering joint optimization of all three DPD implementation parameters; (2) optimizing the derived DPD architectures in a multiobjective context (PAE); (3) and demonstrating applicability to multiple modulation schemes, for example, Quadrature Phase Shift Keying (QPSK), 16–Quadrature Amplitude Modulation (QAM), and 64–QAM in LTE) under their respective, modulation-specific constraints.

#### 2.2 Design Space Exploration for DPD Systems

Given a multidimensional design evaluation space (MDES), we view a multiobjective optimization (MOO) process as a process that searches the associated design

space in an effort to derive a set of Pareto-optimal solutions. A solution in an MDES

is Pareto-optimal if no solution in the space is superior to it when all objectives are

considered. Our design optimization problem for DPD system implementation can

be viewed as an MOO problem where the MDES is defined by the PAE metrics

defined in Section 2.1. In this section, we provide details on these metrics and the

DPD parameters — the filter coefficients, filter orders and polynomial orders — that

define the design space that is investigated in our work.

To implement the DPD algorithm in [5], we develop a dataflow representation for part of the overall DPD system. This DPD algorithm operates in two stages. In the *coefficient estimation* stage, the DPD filtering coefficients are estimated. The estimated coefficients are then employed in the *DPD filtering* stage for actual predistortion of the input signal. Since the coefficient estimation stage of this system is performed off-line [5], and our objective is to investigate FPGA implementation

of the on-line (real-time) part, we implement only the second stage — predistortion filtering — in the dataflow graph.

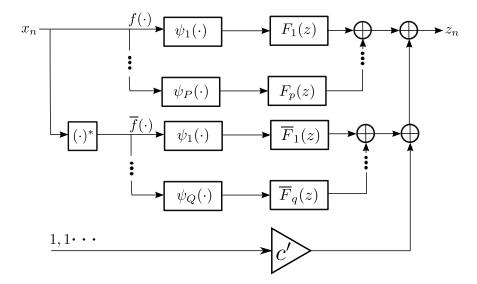

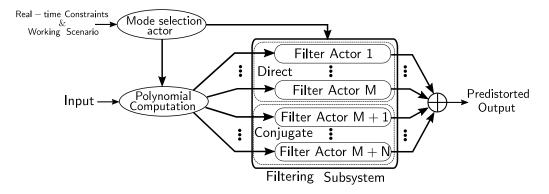

The structure of the predistortion filtering system is shown in Fig. 2.1. The DPD system is split into two branches, namely direct and conjugate predistortions. The output of the predistortion filter can be expressed as

$$z_n = \sum_{p \in I_P} f_{p,n} \star \psi_p(x_n) + \sum_{q \in I_Q} \bar{f}_{q,n} \star \psi_q(x_n^*) + c' , \qquad (2.1)$$

where  $\star$  denotes convolution;  $x_n$  and  $x_n^*$  are the direct and conjugate input samples, respectively;  $I_P$  and  $I_Q$  are the employed sets of direct and conjugate term orders, respectively;  $\psi_p$  and  $\psi_q$  are polynomial basis functions for the direct and conjugate branches, respectively;  $f_{p,n}$  and  $\bar{f}_{q,n}$  are the Finite-Impulse-Response (FIR) filter coefficients for the direct and conjugate polynomials, respectively; and c' is the LO leakage compensation component. The maximum polynomial order used can be different for the direct and conjugate branches of the predistorter [5].

Given  $r \in \{p, q\}$ , the polynomial basis function  $\psi_r$  can be expressed as

$$\psi_r(x_n) = \sum_{k \in I_r} u_{k,r} |x_n|^{k-1} x_n, \ r \in I_R \ , \tag{2.2}$$

where  $I_R$  denotes the set of term orders employed in the given DPD configuration  $(I_R = I_P \text{ if } r = p, \text{ and } I_R = I_Q \text{ if } r = q)$ ;  $I_r$  denotes the subset of  $I_R$  that contains only of term orders up to r in  $I_R$ ; and  $\{u_{k,r}\}$  denotes the polynomial weights. Here, given a polynomial  $\rho = a_0 + a_1 x + \ldots + a_n x^n$ , we define each monomial  $a_i x^i$  to be a term of  $\rho$ , and we define i to be the associated term order. According to [5], only

Figure 2.1: Predistorter structure for the joint predistortion of PA and I/Q modulator impairments.

odd-order polynomials are used to avoid the computation of the square-root within  $|x_n|^{k-1}$ , which is a computation-saving option that has been applied in the proposed implementation.

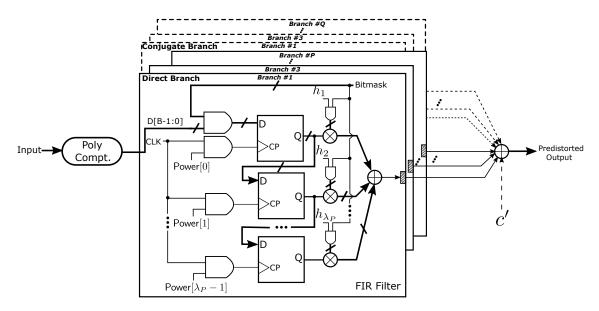

The dataflow model for this second stage is illustrated in Fig. 2.2. The actor labeled *Poly Compt.* in Fig. 2.2 represents a polynomial computation module that produces a polynomial basis function  $\psi_p$ , which is used for both the direct and conjugate branches.

## 2.2.1 Optimization Metrics

The power consumption of the DPD system is an important metric that we carefully take into account in our design optimization approach. We implement the FIR filters in Fig. 2.2 in hardware using the Altera EP2C35F672C6 FPGA from the Cyclone II family, and we estimate the total power consumed by all of the instantiated filters by modeling the power consumption as a function of the DPD

Figure 2.2: Dataflow graph model of the predistortion filter.

parameters. We employ such a model-based estimation approach for assessing power consumption because detailed measurement of total power consumption would be time-consuming when exploring the large multidimensional DPD design space, which is elaborated on in the following section.

Our approach to system-level DPD power estimation starts by first measuring the total power consumption of a single branch under all valid filter order and bit-width values using Altera PowerPlay Analyzer. The power consumption for a specific DPD configuration is then estimated as

$$Power_{est} = \sum_{p \in I_P} Power_p(bw_p, fo_p) + \sum_{q \in I_Q} Power_q(bw_q, fo_q) , \qquad (2.3)$$

where  $bw_x$  and  $fo_x$  are the bit-width and filter order for branch x, respectively, and  $Power_x(bw_x, fo_x)$ , the power consumed by branch x with bit-width  $bw_x$  and filter order  $fo_x$ , is obtained from the aforementioned power measurement process.

During MOO, we are interested in the power *comparison* result of two configurations instead of their actual power consumption levels. This is because, as we explore different pairs of design points during the search process, we are interested in determining which configuration in any given pair is "better" than the other. Thus, we can validate the utility of the above power estimator in our estimation context using the *estimation fidelity*, which is defined by (e.g., see [18]):

Fidelity =

$$\frac{2}{M(M-1)} \left( \sum_{i=1}^{M-1} \sum_{j=i+1}^{M} f_{ij} \right)$$

, (2.4)

where M is the number of configurations that we generate to calculate the fidelity. Here,  $f_{ij} = 1$  if  $sign(S_i - S_j) = sign(F_i - F_j)$ , and  $f_{ij} = 0$  otherwise. The terms  $S_i$  and  $S_j$  denote the simulated average power consumption levels of configurations i and j, respectively;  $F_i$  and  $F_j$  are the corresponding estimates from the power estimation function F; and sign(x) equals -1 if x < 0, 0 if x = 0, and 1 if x > 0.

We generate 100 uniformly distributed system configurations to calculate the fidelity of the power estimators used in our work for three LTE modulation schemes — QPSK, 16–QAM, and 64–QAM. The respective fidelity values resulting from these experiments are 0.79, 0.78, and 0.81. The proposed power estimation method and corresponding fidelity calculation method are not restricted to FPGA implementation, and can be adapted readily to implementations on other types of platforms.

In addition to imposing constraints on system power consumption, the LTE standard requires the ACPR and error vector magnitude (EVM) levels of the transmitted signal to stay below certain values. Different modulation schemes impose dif-

ferent constraints on the transmitter; thus, we incorporate ACPR and EVM as two distinct optimization objectives in our MOO framework. ACPR is commonly used to quantitatively assess the extent of out-of-band energy leakage [12], while EVM measures the distortion of the original signal under the influence of non-linearities introduced by the PA and DPD subsystems. More details of ACPR metric for DPD systems are discussed in Section 3.4.1.2.

## 2.2.2 Design Space for DPD Implementation

## 2.2.2.1 Polynomial Orders

Since the DPD algorithm proposed in [5] splits its signal processing into a direct part and a conjugate part, which enables use of different polynomial orders for direct and conjugate signal terms. For example, a DPD system can be realized with fifth-order for the direct signal and only third-order for the conjugate signal. We denote the polynomial order for the direct signal by P, and that for the conjugate signal by Q. The ordered pair (P,Q) is referred to as the polynomial order parameter in the DPD design space. Following [5], we allow only odd-valued term orders. For example, if P = 5 and Q = 3, then  $I_P = \{1, 3, 5\}$ , and  $I_Q = \{1, 3\}$ . If x denotes the input signal to be filtered, then each term order  $i \in I_P$  corresponds to the processing of  $|x|^{i-1}x$  by an FIR filter, and similarly, each term order  $j \in I_Q$  corresponds to FIR filtering of  $|x*|^{j-1}x*$ . Thus, the number of instantiated FIR filters for this example in Fig. 2.2 is 5.

#### 2.2.2.2 FIR Filter Orders

We define the filter order parameter in our DPD design space to be the ordered pair  $(\lambda_P, \lambda_Q)$ , where  $\lambda_P$  represents the FIR filter order for the direct branch, and similarly,  $\lambda_Q$  represents the common FIR filter order for the conjugate branch. Thus, we allow heterogeneous filter orders across branches, but all filters in the same branch have the same order.

## 2.2.2.3 Bit-width

We introduce the bit-width B of the input data samples and FIR filter coefficients as another DPD design space parameter. We assume that all of the employed filters have the same bit-width, which is defined by the design space parameter B.

## 2.3 Experimental Setup and Simulation Results

As described in Section 2.2, the design space for our DPD system is based on the following parameters: (P,Q),  $(\lambda_P,\lambda_Q)$ , and B. We explore the design space defined by these parameters across the following ranges of admissible values for the different parameter components — P and Q:  $\{1, 3, 5\}$ ;  $\lambda_P$  and  $\lambda_Q$ :  $\{1, 2, 3, 4, 5\}$ ; and B:  $\{5, 6, \ldots, 15\}$ . This results in a total of  $3^2 \times 5^2 \times 11 = 2475$  distinct configurations, which we evaluate exhaustively with the aid of our proposed power estimator.

The constraint on ACPR used in this chapter for all three modulation schemes is -45.0 dBc. The constraints on EVM are -15.1 dB, -18.1 dB, and -21.1 dB for

QPSK, 16–QAM, and 64–QAM, respectively. We also impose a constraint on the symbol error rate (SER), which is measured as the average rate of erroneous symbol transmissions. We filter out the configurations with non-zero SER levels to further increase the accuracy of the DPD system. To measure the ACPR, EVM, and SER for a given DPD configuration under a specific modulation scheme, we generate 10,240 OFDM symbols with a baseband sampling rate of 5 MHz and an upsampling rate of 8. This procedure is repeated 100 times and averages are calculated over these 100 trials to derive values for the three performance metrics.

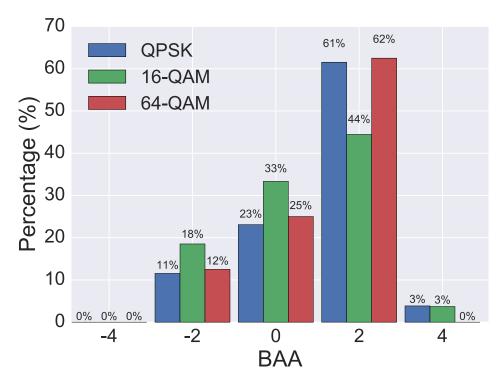

After the aforementioned DPD design space exploration, we obtain 26, 27, and 8 Pareto-optimal configurations for QPSK, 16–QAM, and 64–QAM, respectively. We find that for most of the derived Pareto-optimal settings,  $P \geq Q$ , which validates the argument in [5] that the higher orders of the conjugate predistorters are weak, and a smaller Q value is therefore preferred. To further explore the utility of this kind of asymmetry between the direct and conjugate branches, we define the branch asymmetry attribute (BAA) of a DPD configuration as the associated value of (P - Q), and we plot the BAA distribution of the obtained Pareto-optimal settings in Fig. 2.3.

From Fig. 2.3, we see that there is a high concentration of design points with (P-Q)=2 for all three modulations. This concentration involving asymmetric direct and conjugate branch processing validates the utility of decomposing DPD signal processing into these two separate parts. Our validation here, which is implementation-oriented, is complementary to the algorithm-level validation in [5] of such decomposed processing.

Figure 2.3: BAA distribution of the derived Pareto-optimal settings.

For each LTE modulation scheme, we select three representative DPD configurations among the Pareto-optimal design points derived from our multiobjective optimization approach. These configurations are selected from diverse regions of the design evaluation space. The selected configurations along with their associated figures of merit are listed in Table 2.1.

To further evaluate the effectiveness of the selected DPD structures, we also provide — in Table 2.1 — a comparison of transmitter performance with (a) a randomly-selected, fixed-configuration DPD system, and also with (b) a transceiver setup that does not use DPD. Values in boldface violate the aforementioned constraints. From the results in Table 2.1, we see that the fixed-configuration DPD system does not satisfy the ACPR constraint of any of the three modulation schemes, the EVM constraint of 64–QAM, and the SER constraint of 16–QAM and 64–QAM.

Table 2.1: Pareto-optimal configurations for three LTE modulation schemes. The configurations are shown in the format  $(P, Q, \lambda_P, \lambda_Q, B)$ , and the measurements in the format (Power, ACPR, EVM, SER) with units (mW, dBc, dB, error per symbol). The configuration of the fixed DPD system is (5, 1, 5, 2, 14).

| Mod.   | Configuration | Pareto-optimized DPD        | Configfixed DPD             | Without DPD          |

|--------|---------------|-----------------------------|-----------------------------|----------------------|

|        | (3,1,1,1,10)  | (349.98,-45.61,-27.97,0)    | (387.50,-44.53,-37.98,0)    |                      |

| QPSK   | (3,1,1,2,12)  | (356.02, -46.35, -28.07, 0) |                             | (NA,-40.85,-21.21,0) |

|        | (3,3,1,3,15)  | (376.61,-46.68,-28.07,0)    |                             |                      |

|        | (3,1,2,1,10)  | (352.86, -45.79, -27.88, 0) | (383.95,-40.98,-25.41,+)    |                      |

| 16-QAM | (3,1,4,4,14)  | (376.74, -46.49, -28.34, 0) |                             | (NA,-40.82,-11.24,0) |

|        | (3,3,5,3,15)  | (392.67,-46.55,-28.66,0)    |                             |                      |

|        | (3,1,2,2,10)  | (354.98, -45.15, -21.54, 0) |                             |                      |

| 64-QAM | (3,3,3,1,10)  | (360.32-46.07,-22.17,0)     | (388.59, -42.58, -20.39, +) | (NA,-40.84,-4.98,+)  |

|        | (3,1,2,4,14)  | (369.79,-46.34,-22.27,0)    |                             |                      |

Furthermore, we see that most of the constraints are violated when no DPD is used. In contrast, the DPD system with our selected set of optimized configurations can meet the modulation-specific requirements in all cases, and with relatively low power consumption.

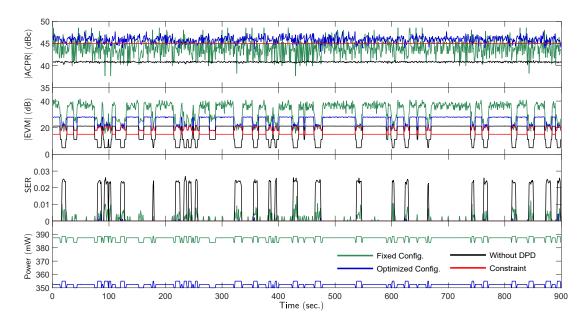

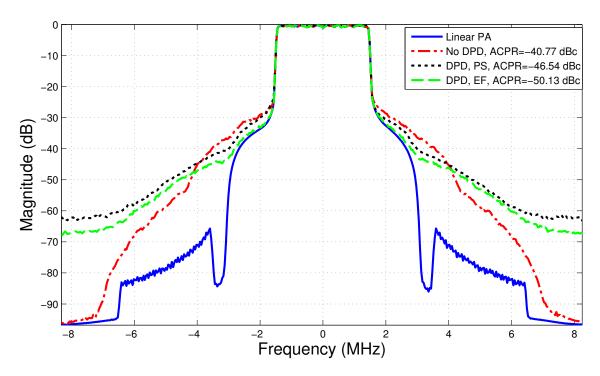

Next, we consider an optimized adaptive DPD (OAD) system that can switch itself to the most power-efficient configuration (as obtained from Table 2.1) associated with the current modulation scheme so that the DPD system can always satisfy the relevant real-time constraints with optimized power consumption. In Fig. 2.4, we compare predistortion figures of merit among transmitters with our OAD system; the non-optimized, fixed-configuration DPD system represented in Table 2.1; and a transmitter that does not use DPD. We perform this comparison using a time-varying sequence M of LTE modulation schemes, where M is derived from simulations using the ns-3 network simulator. In these simulations, we consider a single-user scenario where the COST231 path loss channel model from ns-3 is selected, base station position is constant, and user equipment mobility is modeled using a Gaussian Markov model. This comparison neglects the overhead (expected

to be relatively small) of switching between alternative configurations in the OAD system. A more comprehensive evaluation that accounts for this overhead is a useful direction for further work.

Figure 2.4: Real-time power and performance comparison involving the OAD system. ACPR and EVM measurements are presented using absolute values — thus, higher values indicate better performance.

The results in Fig. 2.4 demonstrate the potential of the OAD system, which is derived using our proposed DPD design optimization approach as a foundation, in achieving significantly improved trade-offs compared to the fixed-configuration and no-DPD alternatives.

# 2.4 Summary

In this chapter, we have developed new methods for exploring the design space for digital predistortion (DPD) system implementation. Our methods are developed to jointly optimize power consumption and multiple DPD performance objectives subject to constraints imposed by the given modulation scheme. We have also demonstrated the utility of an adaptive DPD technique that switches among optimized configurations that are derived using our multidimensional design optimization methods. As part of the design space exploration process, we have applied an approach to efficiently estimate DPD system power, and we have validated the fidelity of this estimation approach. Simulation results demonstrate the capability of our proposed DPD design optimization techniques to support diverse signal processing trade-offs, and to significantly outperform a fixed-configuration DPD design under time-varying operational scenarios.

## Chapter 3

## Evolutionary Optimization for DPD Architectures

In Chapter 2, we introduced a design space exploration method for DPD that performs exhaustive search over a reduced subset of the design space. This process can be time-consuming and may not sufficiently explore the overall (original) design space. It is therefore useful to investigate more automated and thorough methods to search large DPD design spaces.

Additionally, to help maximize effectiveness, such design space exploration should be performed based on multidimensional operational criteria. With this motivation, we develop in this chapter a novel evolutionary algorithm framework for multiobjective optimization of DPD systems. We demonstrate our framework by applying it to develop an adaptive DPD architecture, called the *adaptive*, *dataflow-based DPD architecture* (*ADDA*), where Pareto-optimized DPD parameters are derived subject to multidimensional constraints to support efficient predistortion across time-varying operational requirements and modulation schemes. Through extensive simulation results, we demonstrate the effectiveness of our proposed multiobjective optimization framework in deriving efficient DPD configurations for runtime adaptation.

Material in this chapter has been published in [19] and [20].

#### 3.1 Introduction

A major challenge in deploying DPD architectures for cognitive radio systems is the dynamic optimization of key DPD parameters subject to time-varying and multidimensional constraints on system performance. A general approach to such optimization is to perform efficient search at design time (i.e., off-line) across alternative DPD configurations, and to then select from the search results a set of configurations that are Pareto-optimal, and that effectively cover the targeted range of operational scenarios and their trade-offs. These selected, "Pareto-optimized" configurations can then be stored in memory, and switched across during system operation based on time-varying changes in communication system requirements. Here, "Pareto-optimized" configurations refer to configurations that are Pareto-optimal with respect to the applied search process, while "Pareto-optimal" configurations refer to configurations that are globally optimal in a Pareto sense.

In this chapter, we develop a novel framework for systematic derivation of Pareto-optimized DPD system configurations that can be applied to adaptive DPD implementations. Our framework builds on the methodology of multiobjective evolutionary algorithms (e.g., see [21]), and incorporates adaptations of this methodology to efficiently handle distinguishing characteristics of DPD system optimization. We refer to our framework for DPD system optimization as the framework for Evolutionary Adaptive DPD Implementation (EADI) or ("EADI Framework").

We demonstrate the EADI Framework in this chapter by applying it to develop an adaptive DPD architecture, called the *adaptive*, *dataflow-based DPD architecture*,

chitecture (ADDA), where Pareto-optimized DPD parameters are derived subject to multidimensional constraints to support efficient predistortion across time-varying operational requirements and modulation schemes. While the ADDA architecture is used to concretely demonstrate the capabilities of the EADI Framework, the EADI Framework is not specific to any particular DPD architecture, and can readily be adapted to work across a variety of parameterized DPD architectures. Exploring such adaptations is a useful direction for future work that emerges from the developments of this chapter.

Similar to the work in 3, the design evaluation metrics (optimization objectives) targeted in our development of the EADI Framework and ADDA architecture in this chapter are system energy consumption, adjacent channel power ratio (ACPR), and system accuracy. We abbreviate this set of metrics as EAA. The ADDA is a parameterized architecture that can be configured dynamically to achieve a range of EAA trade-offs. The DPD design space that we consider consists of three design parameters: the polynomial order, bit-width, and filter order. This design space is modeled in the EADI Framework, and optimization results from the framework are used to extract a subset of generated Pareto-optimized configurations (settings of the DPD parameter values). This subset of configurations provides the set of DPD system modes that will be implemented in the ADDA architecture. The set of DPD modes provided in the ADDA configuration set is made available during operation such that predistortion trade-offs can be reconfigured among the different options in the configuration set based on dynamically changing operational requirements.

To demonstrate and experiment with the ADDA, we apply the *lightweight* dataflow environment (LIDE), which is a design tool for dataflow-based design and implementation of signal processing systems [22]. Dataflow graphs provide a useful form of model-based design in many areas of signal processing, and wireless communications (e.g., see [23]). We map the signal flow structure of the ADDA into actors (dataflow-based signal processing components) in LIDE, and implement the internal functionality of these actors using the Verilog hardware description language (HDL).

We demonstrate the effectiveness of the EADI Framework through extensive simulations, and validate the capabilities of the ADDA through hardware synthesis.

## 3.2 Related Work

In this chapter, we exploit the decomposed, parallel structure of the DPD method introduced in [5], and we present new methods to search the design space, and derive Pareto-optimized realizations for this form of DPD architecture.

In architectures for cognitive radios, adaptive DPD systems that operate under Pareto-optimized configurations are highly desirable due to the multidimensional space of relevant implementation metrics. However, prior work on system-level DPD optimization has emphasized single-objective optimization of ACPR [13, 9]. These works employ a form of search technique called genetic algorithms, which are closely related to evolutionary algorithms, to optimize DPD ACPR performance. However, the resulting solutions may not be efficient in terms of energy consumption or accuracy. Furthermore, the underlying design methodology does not produce multiple

alternative configurations that may be employed for dynamic reconfiguration based on time-varying changes in operational requirements. The methods that we develop in this chapter address these limitations, respectively, through development of the (1) EADI Framework for multidimensional, Pareto-optimized DPD configuration, and (2) ADDA for reconfigurable DPD architecture implementation based on configurations that are derived by the EADI Framework.

The DPD design optimization problem addressed in our work can be viewed as a multiobjective optimization problem, where the multiple objectives are generally conflicting, preventing simultaneous optimization of all objectives. One approach to such a problem is to transform all of the objective functions into a single composite function — a common method for such an approach is to use a weighted sum of the objective functions. In this case, small changes to the weights may lead to large differences in the solution set, and proper selection of the weights can be a major problem. Also, the optimization method generally returns a solution set that is preferred by the applied weights, and thus has less diversity [24]. Another general approach is to attempt to compute a representative subset of the entire Pareto set of design points. The EADI framework developed in this chapter adopts this second approach, and therefore, does not suffer from the aforementioned limitations of the weighted sum approach.

A preliminary version of this chapter has been presented in [19]. This chapter goes beyond the previous optimization framework presented in [19] by employing fidelity-based validation of our employed power estimation approach, and applying an improved system accuracy measurement for DPD design space exploration. More

specifically, in Section 3.4, computation of estimation fidelity is integrated to verify the accuracy of the proposed power estimator, and the EVM measurement is modified to better represent the accuracy of the system. In Section 3.6, the simulation results are updated based on this new EVM measurement approach.

## 3.3 Adaptive Dataflow-based DPD Architecture

The ADDA architecture developed in this chapter is based on the algorithm presented in [5]. Since the first stage is intended for off-line computation, the ADDA architecture and EADI optimization process are focused only on the second (filtering) stage.

The structure of the predistortion filtering system is shown in Fig. 2.1. Details of the DPD structure have been shown in Section 2.2 of Chapter 2.

Fig. 3.1 illustrates the dataflow model of the DPD filtering subsystem that is employed in the ADDA. Here, the mode selection actor dynamically selects the DPD operational mode based on the current application scenario (i.e., based on the current modulation and requirements on EAA) and finds the corresponding parameter settings for that mode in its local memory, and distributes these DPD parameter values to the polynomial computation actor and all of the filter actors. Following [5], we decompose the signal processing for the applied DPD algorithm into separate direct and conjugate parts.

With the parameters obtained from the mode selection actor, the polynomial computation actor computes the polynomial basis function defined in Equ. 2.2 for

Figure 3.1: Dataflow graph model of the predistortion filter.

both the direct and conjugate branches. The computed polynomials are then sent to their corresponding branches and filtered by the filter actors in those branches. These filter actors are implemented with integrated use of LIDE and Verilog, as described in Section 3.1. As shown in Fig. 3.1, according to Equ. 2.1, the filtered samples (one output sample from each filter) are summed to produce a single sample as the final predistorted output.

Based on the analysis in [11], where a similar dataflow model is constructed for the DPD algorithm in [5], most of the computation and energy consumption is concentrated in the filter actors. Thus, in this chapter, we map only the filter actors to hardware, and focus our design optimization processes on the filter actors.

# 3.4 Optimization Metrics and Design Space

# 3.4.1 Optimization Metrics

In this subsection, we elaborate on the three objectives in our targeted design optimization problem. As defined in Section 3.1, we refer to these metrics collectively as EAA.

## 3.4.1.1 Energy Measurement

As explained in Section 3.3, we focus our energy measurement on the energy consumed by the filtering subsystem, and the figure of merit that we employ is the filtering energy expended to producing a single output sample, which is denoted by the energy per sample (eps). To calculate eps, we use the total power consumption of all FIR filters used in the predistortion subsystem, which we denote as  $P_{FIR}$ . The eps metric is then defined as eps =  $P_{FIR} \times C/F$ , where C represents the average number of clock cycles required by the filter actors to process a single new input sample, and F represents the clock frequency. In our design, both F and C are fixed for each configuration. Thus, eps is proportional to  $P_{FIR}$ , and we can therefore use  $P_{FIR}$  as optimization objective for our evolutionary algorithm process. Also, we report results for  $P_{FIR}$  in Section 3.6 (instead of eps) as our assessment of the energy efficiency of each configuration.

We implement the DPD filtering subsystem using the Altera EP2C35F672C6 field-programmable gate array (FPGA) from the Cyclone II family. To facilitate efficient design space exploration within the EADI optimization process, we model the power consumption as a function of the design vector  $[P \ Q \ \mathbf{BW}^T \ \mathbf{FO}^T]^T$ . The definitions of the quantities P, Q,  $\mathbf{BW}$  and  $\mathbf{FO}$  are given in Section 3.5.

We apply the same system-level DPD power estimation as described in 2.2.1.

### 3.4.1.2 ACPR Measurement

ACPR is a metric that is commonly used to assess the extent of out-of-band energy leakage [12]. ACPR is defined as the ratio of the mean power centered on the adjacent channel to the mean power centered on the desired channel, as shown in (3.1).

$$ACPR = 10 \log_{10} \frac{\int_{\omega_A} S(\omega) d\omega}{\int_{\omega_D} S(\omega) d\omega} . \tag{3.1}$$

Here,  $S(\omega)$  denotes the power spectral density of the postdistorter input signal  $s_n$ , and  $\omega_A$  and  $\omega_D$  denote the frequency bands of the adjacent channel and desired channel, respectively.

# 3.4.1.3 Accuracy Measurement

We measure the accuracy of candidate DPD designs by the error vector magnitude (EVM) and symbol error rate (SER). The former is considered as an optimization objective and the latter as a constraint on the derived configurations. The EVM measures the distortion of original symbols under the influence of non-linearities introduced by the PA and DPD. This distortion is calculated as

$$EVM(Pf) = \left(\frac{\sum_{k=1}^{K} |X_0(k) - \hat{X}^{Pf}(k)|^2}{\sum_{k=1}^{K} |X_0(k)|^2}\right)^{\frac{1}{2}},$$

(3.2)

where Pf represents a certain profile (finite sequence)  $X_0(1), X_0(2), \dots, X_0(K)$  of symbols to be transmitted, and  $\hat{X}^{\text{Pf}}(k)$  is the kth actual transmitted symbol under

Pf.

SER is measured as the average rate of erroneous symbol transmissions. This rate is determined as

SER(Pf) =

$$\frac{1}{K} \sum_{k=1}^{K} I(X_0(k) - \hat{X}^{Pf}(k))$$

, (3.3)

where I(x) (the *indicator function*), has value 1 if  $x \neq 0$  and 0 otherwise. We require that all of the configurations extracted for mapping into the ADDA must have zero SER.

# 3.4.2 Design Space

In this section, we elaborate on the selected DPD parameters that define the predistorter design space associated with the ADDA.

# 3.4.2.1 Polynomial Orders

In this chapter, polynomial orders are defined in the same way as Section 2.2.2.1. Thus, the number of branches (or filter actors) that is employed in a specific DPD configuration is given by  $N_{branch} = (P+1)/2 + (Q+1)/2$ . In our experiments, we set the domain D of valid values for both P and Q as  $D = \{1, 3, 5, 7, 9\}$ . Thus, there are in total 25 P - Q combinations in our targeted design space.

#### 3.4.2.2 Bit-widths

Intuitively, smaller bit-widths for data storage and computation lead to less energy consumption. However, signal processing accuracy may be traded off as a consequence. To incorporate this trade-off between energy efficiency and accuracy, we incorporate bit-width as a parameter of ADDA, and as a design space component of EADI. Considering requirements on system accuracy and constraints on hardware resources, we set the range of allowable bit-widths in our experiments as  $\{5, 6, \ldots, 15\}$ . Additionally, we allow different branches to be configured with different bit-widths in the same design. This leads to great flexibility in design optimization, and a correspondingly large design space — if there are m branches used in a specific design, then the total number of valid bit-width combinations is  $11^m$ .

### 3.4.2.3 Filter Orders

Similar to the bit-width design, the filter used in each branch may also have different number of coefficients. We denote this parameter as  $filter\ order$ . The filter order parameters would also significantly affect the trade-offs among EAA. The range of filter order in this chapter is set to be  $\{1, 2, 3, 4, 5\}$ .

According to the above description, our design space is too huge for exhaustive search. As a numerical example, given the aforementioned ranges for the system parameters, the design space would contain more than  $55^{10}$  configurations.

## 3.5 Multiobjective Optimization Using Evolutionary Algorithm

As motivated in Section 3.4, the DPD design space addressed in this work is a complex multidimensional space that is too large to be evaluated using exhaustive search techniques. Therefore, we apply a heuristic search strategy called *evolutionary algorithms* (EAs), including a particular form of EA, called *strength Pareto EA* (SPEA), that is suited for multiobjective optimization [21]. We select the SPEA approach due to its efficiency and scalability in addressing complex optimization problems, and its customizability to different kinds of design spaces and optimization criteria. This latter feature makes the EADI Framework readily adaptable across different kinds of DPD architectures and communication system constraints.

## 3.5.1 Problem Encoding

The parameters involved in the DPD design optimization problem are polynomial orders, bit-widths, and filter orders. Each configuration can be represented throughout the EA process by a vector, specified as  $[P\ Q\ \mathbf{BW}^T\ \mathbf{FO}^T]^T$ . Here, P and Q are the direct and conjugate polynomial order, respectively. As described in Section 3.4, the maximum number of branches considered in the design space is 10 (at most 5 branches for both the direct signals and the conjugate signals). Thus,  $\mathbf{BW}$  is a vector with 10 dimensions representing bit-width settings for up to 10 branches, where each dimension represents the bit-width associated with the corresponding branch. For the branches that are not used, the corresponding vector elements are set to zero. Similar conventions are applied to generate the 10-dimensional vector

### **FO** of filter order settings.

As discussed in Section 3.1, the objective space of the EADI Framework encompasses average power consumption, ACPR and EVM. Thus, the objective vector can be formulated as  $[P_{FIR}$  ACPR EVM] with units (mW, dBc, %). Here,  $P_{FIR}$  is the power consumption, as estimated by the method discussed in in Section 3.4, and ACPR and EVM are calculated according to (3.1) and (3.2), respectively.

### 3.5.2 Optimization Process

The EADI optimization process is executed separately for each modulation type that is to be supported in the targeted ADDA platform. The resulting Pareto-optimized configurations for the different modulation types are then collected and stored in the ADDA memory. This enables the ADDA to dynamically to select among different modulation types, and among different operational trade-offs for each modulation type.

As mentioned previously, the work flow of the EADI optimization process is based on the SPEA methodology for multidimensional search. For details on SPEA, we refer the reader to [21].

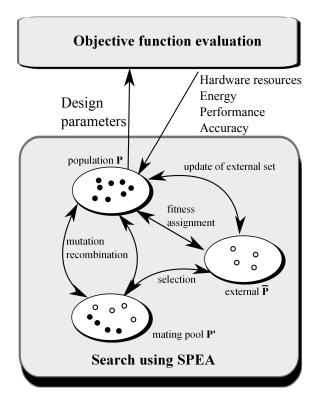

The SPEA-based optimization workflow used in our work is illustrated in Fig. 3.2.

According to SPEA, the population set (set of candidate solutions or *individuals*)  $\rho$  contains the individuals generated during each SPEA iteration, and the external set  $\bar{\rho}$  maintains selected non-dominated individuals among all individuals

Figure 3.2: Multiobjective optimization model for DPD system.

generated so far up through the current iteration. Here, we say that an individual x dominates another individual y if x is superior to y in terms of at least one design evaluation metric, and x is not inferior to y in terms of any metric. A non-dominated individual is one that is not dominated by any individual.

We initialize  $\rho$  with a well-distributed population across the design space. For each possible P-Q combination, we generate two design vectors by selecting the corresponding bit-width and filter order values randomly from their valid ranges. Thus, the size of  $\rho$ , denoted by  $\mathbf{N}$ , is 50 individuals.

During each iteration, each individual in  $\rho$  is evaluated to generate the objective vector [ $P_{FIR}$  ACPR EVM]. The individuals that do not satisfy certain modulation-specific constraints (defined in Section 3.6) are ignored. Only the re-

maining non-dominated individuals are copied to  $\bar{\rho}$ . If the size of  $\bar{\rho}$  exceeds a predefined maximum population size  $\bar{N}_{max}$ , a k-means clustering algorithm is used to classify the members in  $\bar{\rho}$  into  $\bar{N}_{max}$  groups. This allows us to limit the size of  $\bar{\rho}$  while maintaining a diverse population in  $\bar{\rho}$  by retaining a "representative" individual of each group in  $\bar{\rho}$  [21].

After updating of  $\bar{\rho}$  during an optimization iteration (generation), individuals from both  $\rho$  and  $\bar{\rho}$  are selected to generate a "mating pool"  $\rho'$ . This selection process is performed randomly in a manner such that the probability of an individual's selection for the mating pool is larger for individuals with smaller fitness values. Here, "fitness" is a measure of the quality of an individual; smaller fitness values imply higher quality solutions. The recombination operator selects pairs of individuals ("parents") in  $\rho'$ , and for each selected pair, two new individuals ("children") are generated with probability  $p_r$ .

Each generated child (from recombination) undergoes a process of random modification by a mutation operator with probability  $p_m$ . After all recombination and mutation operations are completed on the mating pool  $\rho'$ , the resulting new population is assigned as the current population  $\rho$  for the next generation. The individuals that comprise the set  $\bar{\rho}$  after  $\mathbf{T}$  generations are the Pareto-Optimized solutions obtained by the EADI Framework. Here,  $\mathbf{T}$  is a pre-defined number of optimization iterations that is to be executed by the SPEA.

The values  $p_r$ ,  $p_m$ , and **T** are design parameters of the optimization process that can be set through experimentation or by selecting commonly-used values from the literature.

These general concepts of fitness measures, recombination operators, and mutation operators are standard components of EAs. They are applied to form an optimization process that has analogies to processes by which living species evolve. However, these three operators need to be designed specifically for each optimization context. In the remainder of this section, we discuss how these operators have been designed in the EADI Framework.

#### 3.5.3 Fitness Measure

Based on the SPEA approach, each individual  $\mathbf{i} \in \bar{\rho}$  is assigned a real value  $S(\mathbf{i}) \in [0,1)$ , which is referred to as the *strength* of  $\mathbf{i}$ . If N represents the number of individuals in the set  $\rho$ , then  $S(\mathbf{i})$  is calculated as the ratio of (a) the number of individuals in  $\rho$  that are dominated by  $\mathbf{i}$  to (b) (N+1). The fitness of  $\mathbf{i}$  is equal to  $S(\mathbf{i})$ . The fitness of an individual  $\mathbf{i} \in \rho$  is calculated by summing the strengths of all individuals  $\mathbf{j} \in \bar{\rho}$  that dominate  $\mathbf{i}$ , and then adding one to this sum. We add one to the sum here in order to guarantee that members in  $\bar{\rho}$  have better fitness than members in  $\rho$  (since fitness is to be minimized).

# 3.5.4 Recombination Operator

Recombination is a process of selecting parent solutions and producing child solutions from them that integrate properties of the corresponding parent solutions. The inputs of the recombination operation are the configuration vectors of the two selected parents  $\mathbf{Y_1}$  and  $\mathbf{Y_2}$ , and the outputs are either (a) the same two parents  $\mathbf{Y_1}$

and  $\mathbf{Y_2}$  (with probability  $(1-p_r)$ ) or (b) the configuration vectors of two generated children (with probability  $p_r$ ), denoted by  $\mathbf{C_1}$  and  $\mathbf{C_2}$ .

In the latter case (when children are generated), the process of generating each child individual  $C_k$ , k = 1, 2 from the two parents is summarized as follows: (i) assign P, Q values (polynomial orders) from  $Y_1$  or  $Y_2$  to  $C_k$  with equal probability subject to the requirement that the generated pair of P and Q values for  $C_1$  and  $C_2$  cannot be identical to each other; (ii) set the bit-width and filter order values of each child  $C_k$  to the corresponding values of an average vector  $Y_{avg}$ :  $Y_{avg} = \gamma(Y_1, Y_2)$ , where  $\gamma(Y_1, Y_2)$  first computes the average  $(Y_1 + Y_2)/2$ , and for each component in this average vector that is not integer-valued, the operator replaces the component by its floor or ceiling with equal probability; and (iii) set the bit-widths and filter orders of the unused branches in the children to be zero.

# 3.5.5 Mutation Operator

In EAs, mutation operators are employed to help promote diversity from one generation of a population to the next by randomly modifying selected solution components ("genes") within individuals. In the EADI Framework for ADDA implementation, the genes for potential mutation are taken to be the vector-valued settings of **BW** and **FO**. The specific gene (**BW** or **FO**) to which modification is to be applied is selected randomly with equal probability, and then a single component of the selected vector that is to be modified is selected randomly (with equal probability among all vector components). The mutation operator replaces the value

of the selected vector component with a uniform random value drawn between the given upper and lower bounds for that component.

## 3.6 Experimental Setup and Simulation Results

To validate the EADI Framework and ADDA platform, and to demonstrate their capabilities, we experiment with three Long-Term Evolution (LTE) modulation schemes — Quadrature Phase Shift Keying (QPSK), 16–QAM, and 64–QAM. The multiobjective optimization process is performed separately for each of the three modulation schemes, and then the resulting Pareto-optimized solution sets are integrated into the ADDA as discussed in Section 3.5. For all three modulation schemes, we employ the following SPEA parameter settings: (i)  $\mathbf{T} = 100$  (number of generations); (ii)  $\mathbf{N} = 50$  (population size); (iii)  $\bar{\mathbf{N}}_{\text{max}} = 20$  (maximum size of external set); (iv)  $p_r = 0.8$  (recombination rate); (v)  $p_m = 0.2$  (mutation rate). These values for generic SPEA settings are values that are commonly used in the literature (e.g., see [21, 25]).

The constraint on ACPR used in the EADI Framework for all three modulations is -45.0 dBc. The constraints on EVM are 17.5%, 12.5%, and 8% for QPSK, 16–QAM, and 64–QAM, respectively. The constraint on SER is that it should be zero.

To help validate the effectiveness of the EADI Framework in deriving high quality DPD configurations, we apply a  $partial\ search\ (PS)$  method to solve the same multiobjective optimization problem. PS involves performing a complete search on

a reduced design space. PS is also a widely-applied method for obtaining Pareto fronts in multiobjective optimization problems (e.g., see [26]).

In our PS approach, we reduce the search space by equalizing the bit-widths and filter orders of all the filters used in all branches and apply the same valid parameter value ranges as used in the SPEA process. Thus, the reduced design space contains  $5 \times 5 \times 11 \times 5 = 1375$  configurations. We evaluate these 1375 configurations exhaustively with the  $P_{FIR}$ , ACPR, SER and EVM computations, as described in Section 3.4. We then remove the undesirable solutions based on the same SER, ACPR and EVM constraints as applied in the SPEA. Finally, we collect all of the non-dominated configurations from the resulting design space as the Pareto front obtained by the PS.

In the PS process, we estimate  $P_{FIR}$  using relevant FPGA design tools (Altera PowerPlay Analyzer), while in the EADI process, we estimate  $P_{FIR}$  using the power estimator introduced in Section 3.4. The estimator of Section 3.4 enables faster power estimation (at some expense in accuracy), which is important because very large numbers of candidate solutions are evaluated during the EADI process. For the Pareto-optimized configurations achieved by EADI, we also estimate  $P_{FIR}$  using FPGA tools to obtain more accurate power estimation results for the derived Pareto front. In the results that we report in the remainder of this section, the comparison between the quality of the two solution sets (PS and EADI) is based on the same (more accurate) power estimation method — i.e., using FPGA tools.

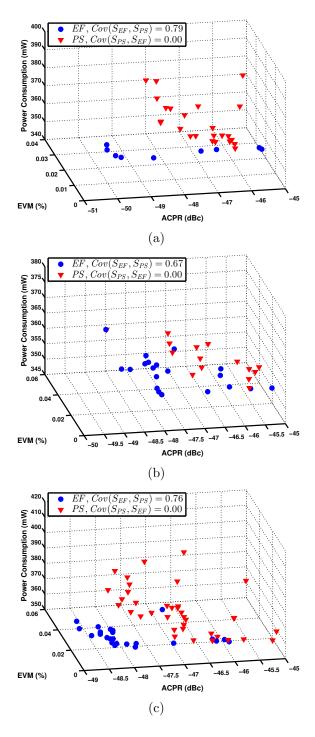

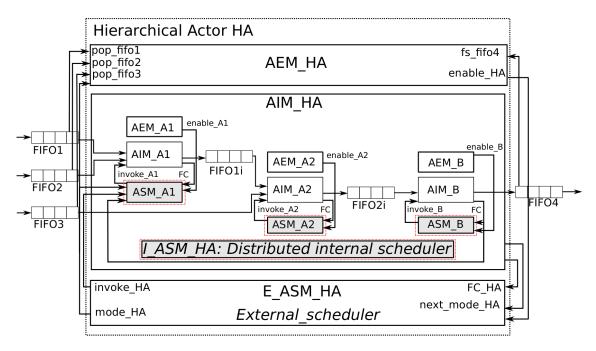

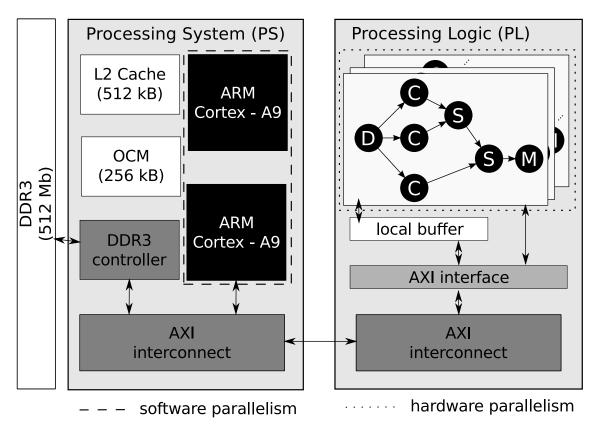

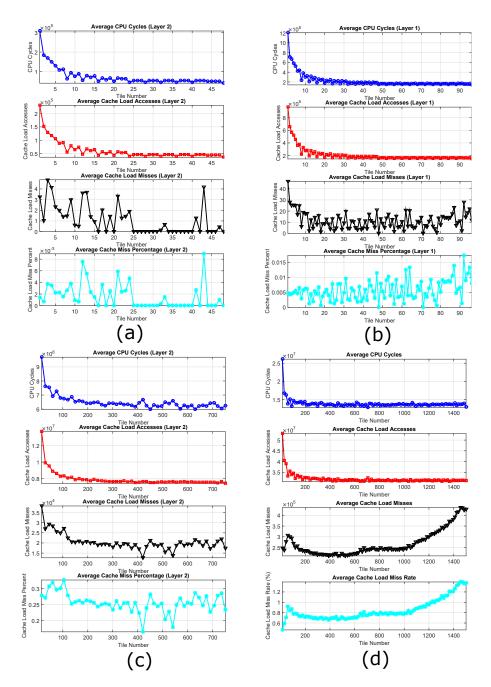

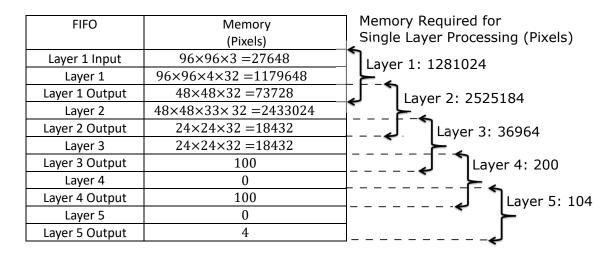

The Pareto fronts derived by the EADI Framework and PS for the three selected modulations are shown in Fig. 3.3(a) to 3.3(c). We use *coverage of two sets*