# ABSTRACT

Title of DissertationFAILURE MECHANISM INVESTIGATION<br/>FOR SILICON CARBIDE POWER DEVICES<br/>Xiaohu Zhang, Doctor of Philosophy, 2006Directed By:Associate Professor, Dr. Joseph B. Bernstein,<br/>Department of Mechanical Engineering

Silicon carbide (SiC), as one of the wide bandgap semiconductors, is a promising material for next-generation power devices due to its high critical electric field, high thermal conductivity, and high saturated electron drift velocity properties. Extensive studies have been focused their electrical characterizations. Failure mechanisms of SiC devices, however, have not been fully explored. In this work the failure mechanisms of SiC power devices, including Schottky diodes, power MOSFETs and IGBTs, are investigated.

The characteristics of SiC Schottky diodes have been investigated and simulated based on the drift-diffusion model. Interface state degradation has been identified as the mechanism responsible for the non-catastrophic failure happened in Schottky diode. Experimental and simulation results are provided to support this conclusion. Single-event burnout (SEB) and single-event gate rupture (SEGR) failure mechanisms have been investigated for SiC power MOSFETS in details in this work since power MOSFETs have been used in very critical applications. The features of SiC power MOSFET SEB and SEGR failures have been simulated successfully and compared to those of Si power MOSFETs. The much better robustness of SiC power MOSFES against SEB failures has been demonstrated by the simulation results. At last the latch-up failure mechanism has been investigated for SiC IGBTs. Compared to Si IGBTs, the results show that SiC IGBTs have a stronger capability against the latch-up failure.

The design and application guideline for SiC power devices can be made base on the results obtained in this work.

•

# FAILURE MECHANISMS IN WIDEBAND SEMICONDUCTOR POWER DEVICES

By

Xiaohu Zhang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2006

Advisory Committee: Professor Joseph B. Bernstein Chair/Advisor Professor Martin Peckerar Professor Mohammad Modarres Professor Ali Mosleh Professor Carol Smidts © Copyright by Xiaohu Zhang 2006

# Acknowledgements

This dissertation is a result of five years of hard work through which I have been accompanied and supported by many people. It is my pleasure to have this opportunity to express my gratitude to all of them.

First of all, I would like to thank my advisor, Professor Joseph B. Bernstein, for his guidance and financial support throughout my doctoral study, for the privileges he gave me to work on various challenging and interesting projects. I am always impressed and inspired by his sharp insight, deep wisdom and profound knowledge.

Second, I would like to thank Dr. Martin Peckerar, Dr. Mohammad Modarres, Dr. Ali Mosleh, and Dr. Carol Smidts for kindly consenting to be on my thesis committee and their time, comments and suggestions.

Also, I would like to thank Dr. Neil Goldsman for helping me on the device modeling work and sharing the codes from his research group with me.

Last but certainly not least, I am especially indebted to my parents, my wife, and my sister for their encouragement, support, and love, as always.

# Table of Contents

| Acknowledgements                                                                  | ii   |

|-----------------------------------------------------------------------------------|------|

| Table of Contents                                                                 | iii  |

| List of Tables                                                                    | v    |

| List of Figures                                                                   | vi   |

| Chapter 1: Introduction                                                           | 1    |

| 1.1 Why SiC                                                                       | 1    |

| 1.2 Failure Mechanism of power devices                                            | 5    |

| 1.2.1 Failure mechanism of Schottky diodes                                        | 5    |

| 1.2.1.1 Catastrophic failure mechanisms of Schottky diodes                        | 6    |

| 1.2.1.2 Non-catastrophic failure mechanisms of Schottky diodes                    | 7    |

| 1.2.2 Failure mechanism of power MOSFETs                                          | 9    |

| 1.2.2.1 Inherent parasitic structures in power MOSFET                             | . 11 |

| 1.2.2.2 Failure mechanisms in power MOSFETs                                       | . 12 |

| 1.2.3 Failure Mechanisms in IGBTs                                                 | . 19 |

| 1.3 Numerical simulation of failure mechanisms of SiC power devices               | . 27 |

| Chapter 2: Drift-Diffusion Modeling for SiC Power Devices                         | . 28 |

| 2.1 Poisson's Equation                                                            | . 28 |

| 2.2 Current Continuity equations                                                  |      |

| 2.3 Drift-diffusion current equations                                             |      |

| 2.4 The Drift-Diffusion Model                                                     | . 36 |

| 2.5 Boundary Conditions                                                           |      |

| Chapter 3: Characterizations and failure mechanism investigation for SiC Schottky | /    |

| Diodes                                                                            |      |

| 3.1 Numerical Simulation of SiC Schottky Diodes                                   |      |

| 3.1.1 Introduction                                                                |      |

| 3.1.2 Physical Models of SiC Schottky Diodes                                      | . 48 |

| 3.1.3 Simulation Results and Discussion                                           |      |

| 3.2 Non-catastrophic failure mechanisms of SiC Schottky diodes                    |      |

| 3.2.1 Introduction                                                                |      |

| 3.2.2 Simulation of I-V characteristic degradation of SiC Schottky diodes         |      |

| 3.2.3 Results and Discussion                                                      |      |

| 3.2.4 The modified diode equation                                                 |      |

| Chapter 4: Failure Mechanisms Investigation for SiC Power MOSFETs                 |      |

| 4. 1. Two-dimensional simulation study of the single-event burnout for SiC Pow    |      |

| MOSFETs                                                                           |      |

| 4.1.1 Introduction                                                                |      |

| 4.1.2 SEB threshold current density for SiC and Si power MOSFET                   |      |

| 4.1.3 Device simulation structure and physical models                             |      |

| 4.1.4. Simulation Algorithm                                                       |      |

| 4.1.5 Results and discussion                                                      |      |

| 4.2 Two-dimensional simulation study of single-event gate rupture for SiC Power   |      |

| MOSFETs                                                                           | . 90 |

| Chapter 5 Failure Mechanism Investigation for SiC Insulated Gate Bipolar |     |

|--------------------------------------------------------------------------|-----|

| Transistors (IGBTs)                                                      | 96  |

| 5.1 Introduction                                                         | 96  |

| 5.2 Latch-up failure mechanisms of IGBTs                                 | 97  |

| 5.3 Simulation Algorithms                                                | 102 |

| 5.4 Simulation Result                                                    | 104 |

| 5.4.1 Comparison with the same geometry and doping profile               | 104 |

| 5.4.2 Comparison with same voltage rating                                | 126 |

| Chapter 6: Summary and Future Work                                       | 134 |

| 6.1 Summary                                                              | 134 |

| 6.2 Future Work                                                          |     |

| 6.2.1 Experimental verifications                                         | 136 |

| 6.2.2 Circuit Simulation                                                 | 137 |

| References                                                               | 138 |

# List of Tables

| Table 1. 1 The properties of 4H-SiC, 6H-SiC and Si                         | 2       |

|----------------------------------------------------------------------------|---------|

| Table 3. 1 Parameters for 4H-SiC device simulation                         | 50      |

| Table 3. 2 Device dimension and doping profiles for the simulation         | 61      |

| Table 4. 1 Physical Models for the 4H-SiC power MOSFET                     | 71      |

| Table 5. 1 The voltage drops along p-base region in Si IGBT                | 119     |

| Table 5. 2 The voltage drops along p-base region in SiC IGBT               | 120     |

| Table 5. 3 The voltage drops along p-base region in SiC IGBT with the same | voltage |

| rating                                                                     | 132     |

# List of Figures

| Fig.1. 1(a) A carbon atom situated above the center of a tetragon of Si atoms (b) A | 1  |

|-------------------------------------------------------------------------------------|----|

| unit cell of 4H-SiC                                                                 |    |

| Fig. 1. 2 A simple CCM PFC circuit                                                  | 2  |

| Fig.1. 3 The schematic cross-section of a Schottky diode                            |    |

| Fig.1. 4 Vertical DMOS Cross Section                                                |    |

| Fig.1. 5 Parasitic NPN transistor and diode inherent to DMOS                        |    |

| Fig.1. 6 SEGR of power MOSFET                                                       |    |

| Fig.1. 7 Equivalent circuit of a power MOSFET                                       |    |

| Fig.1. 8 SEB of power MOSFET                                                        |    |

| Fig.1. 9 A synchronous rectifiers with power MOSFETs                                |    |

| Fig.1. 10 The vertical cross section of the PT and NPT IGBT structures              | 20 |

| Fig.1. 11 The operation of the turn-on process of IGBTs                             | 21 |

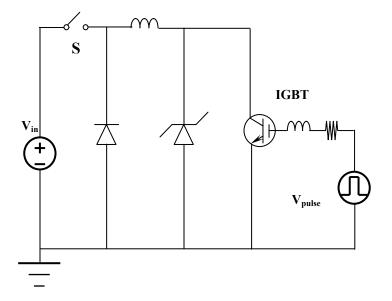

| Fig.1. 12 Test circuit for IGBTs for short circuits failures                        | 23 |

| Fig.1. 13 A clamped inductive switching circuit used for IGBTs                      |    |

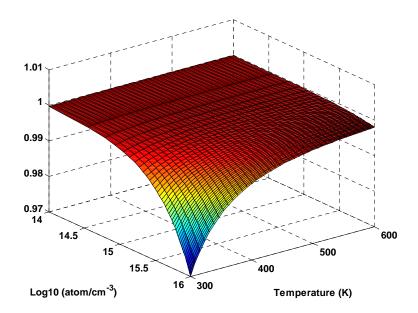

| Fig.2. 1 The incomplete Ionization of n-type 4H SiC doped with Nitrogen             | 33 |

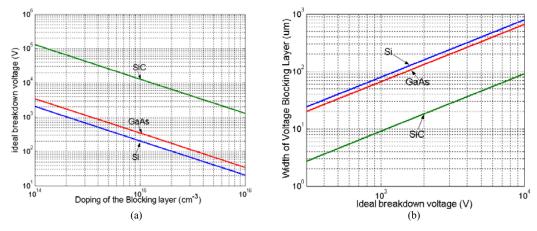

| Fig.3. 1 Comparison of the ideal breakdown voltages of SiC, GaAs and Si devices (   |    |

| for different doping levels (b) for different the blocking layer thickness          |    |

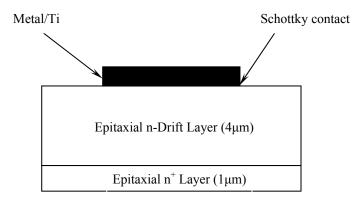

| Fig.3. 2 The schematic cross-section of the active layers of SiC Schottky diode     |    |

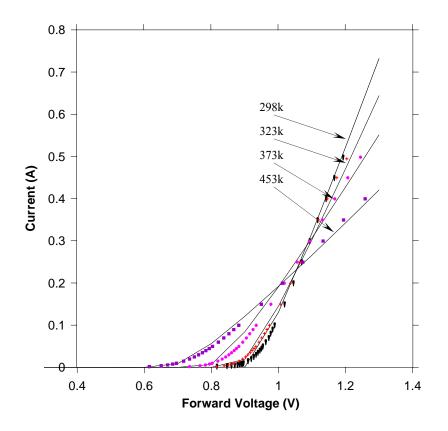

| Fig.3. 3 Simulation of forward I-V characteristics of Ti/4H-SiC Schottky diode for  |    |

| different Temperatures (solid curve). Experimental results of Ti/4H-SiC Schottky    |    |

| diodes are compared (dot curve).                                                    | 51 |

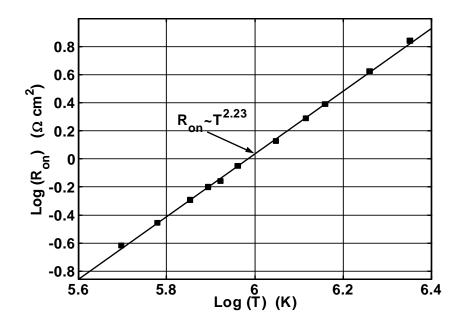

| Fig.3. 4 Temperature dependence of on-resistance                                    |    |

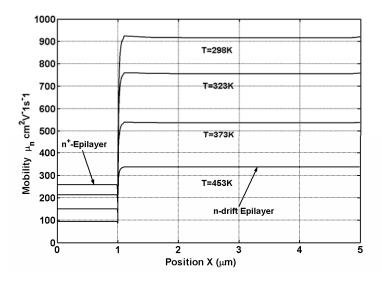

| Fig.3. 5 Mobility variation from $n^+$ epilayer to n-drift epilayer under different | 01 |

| temperature                                                                         | 56 |

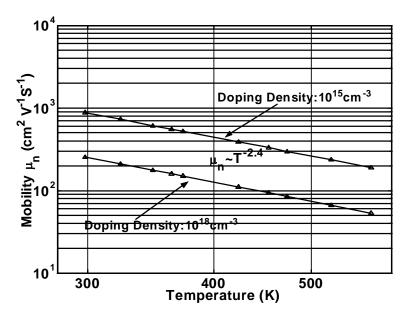

| Fig.3. 6 Average mobility for different doping density under different temperature  |    |

| from the drift-diffusion model                                                      | 56 |

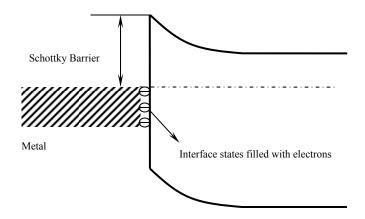

| Fig.3. 7 The Band diagram of an n-type Schottky diode with interface states         |    |

| Fig.3. 8 The Schematics of SiC Schottky diode with field plate                      |    |

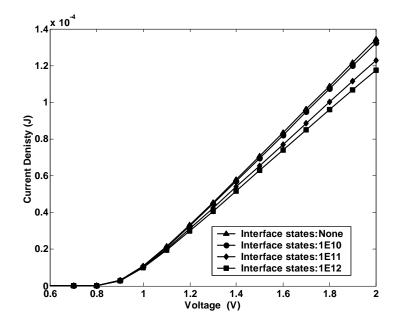

| Fig.3. 9 Simulation results of SiC Schottky diode with different interface states   |    |

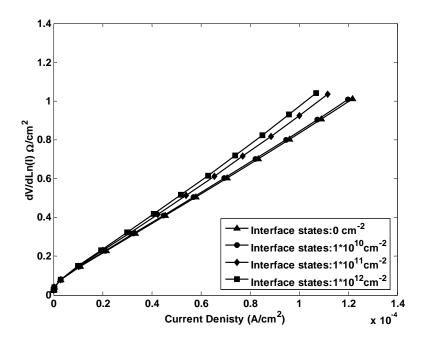

| Fig.3. 10 The $dV/dLn(I)$ versus I plot for the simulated Schottky diode            |    |

| Fig.3. 11 A modified equivalent circuit model for Schottky diode                    |    |

| Fig.4. 1 The SEB failure in an n-type power MOSFET                                  |    |

|                                                                                     |    |

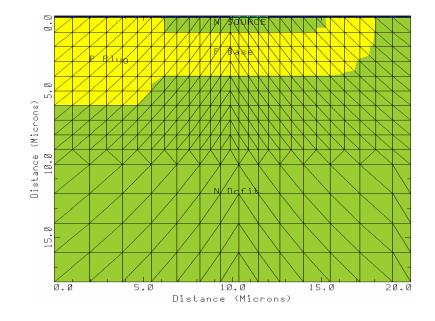

| Fig.4. 2 The mesh grid of the simulated power MOSFET                                |    |

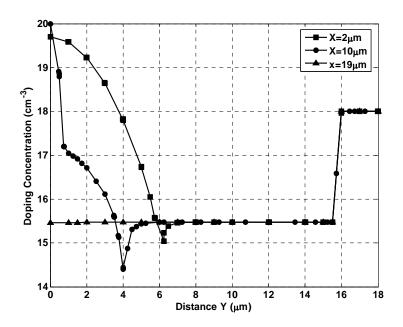

| Fig.4. 3 The doping profile of the simulated power MOSFET                           |    |

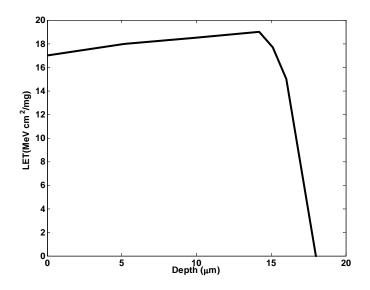

| Fig.4. 4 The LET file used in simulation                                            |    |

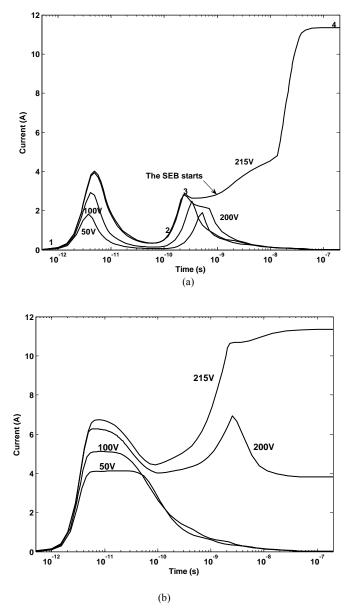

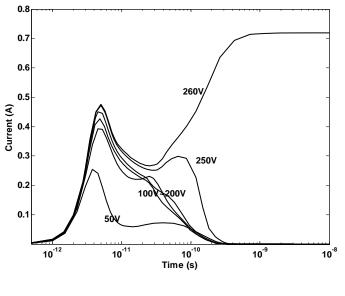

| Fig.4. 5 Transient drain currents of the simulated SiC power MOSFET under differe   |    |

| drain-source voltages at (a) The channel region: The Gate-Channel-N-drift region, ( |    |

| The source region: The $N^+$ source-P-base-N-drift region.                          |    |

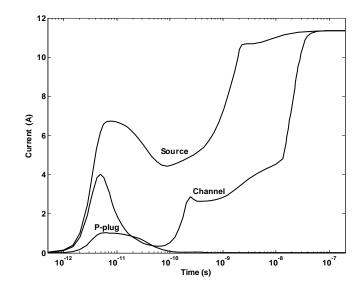

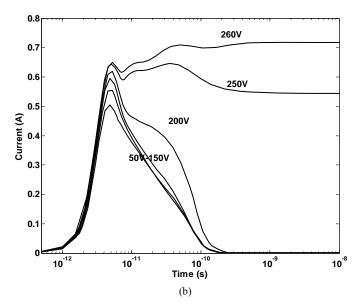

| Fig.4. 6 Transient drain currents at different impact positions for SiC power MOSFI |    |

|                                                                                     | 77 |

| Fig.4. 7 The comparison of Si and SiC power MOSFSET SEB sensitivity at $V_{DS}$ =75 |    |

|                                                                                     | 78 |

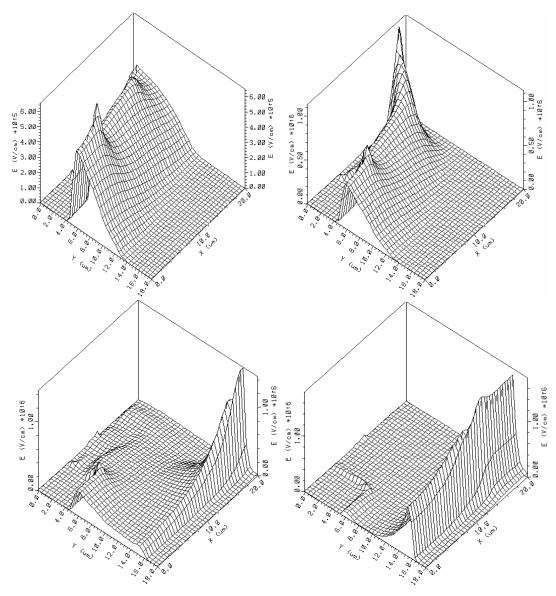

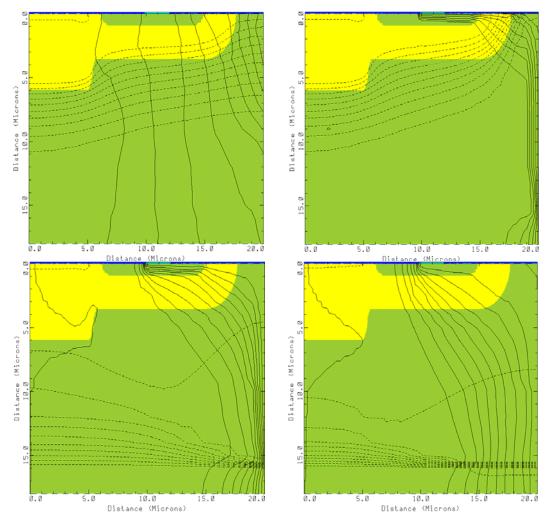

| Fig.4. 8 Electric field evolution inside SiC power MOSFET before and after the SE                  | EB<br>. 79 |

|----------------------------------------------------------------------------------------------------|------------|

| Fig.4. 9 Equipotential lines (horizontal dash line) and current flow lines (Vertical d             |            |

| line) inside the device before and after the SEB                                                   | . 80       |

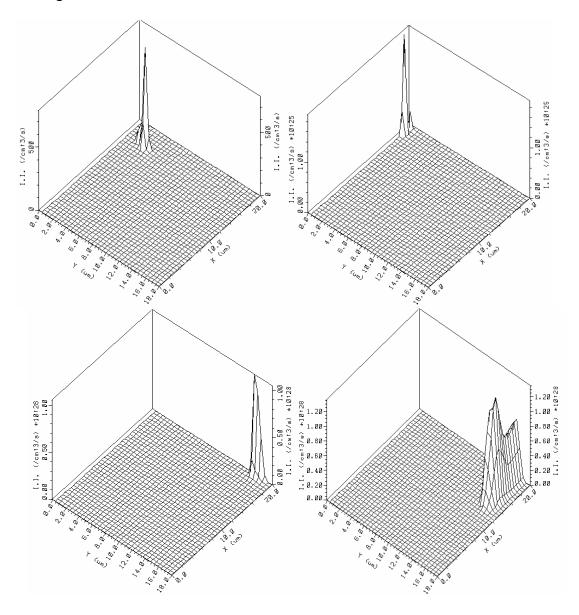

| Fig.4. 10 Impact ionization generation rate of the device before and after the SEB.                | . 81       |

| Fig.4. 11 The hole concentration change within the device before and after the SEE                 | 382        |

| Fig.4. 12 The scaled mesh grid of the new SiC power MOSFET                                         |            |

| Fig.4. 13 Transient drain currents of the new designed SiC power MOSFET under                      |            |

| different drain-source voltages at (a) The channel region (b) The source region                    | . 86       |

| Fig.4. 14 Transient drain currents at different impact positions for the new SiC por               |            |

| MOSFET                                                                                             |            |

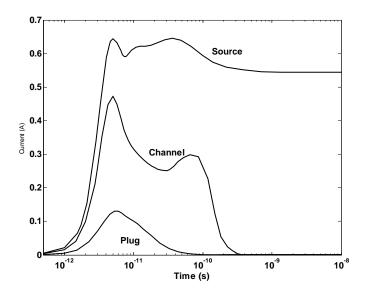

| Fig.4. 15 The parasitic n <sup>+</sup> source/ p-base/n-drift transistor (a) structure and (b) dop | oing       |

| profile                                                                                            |            |

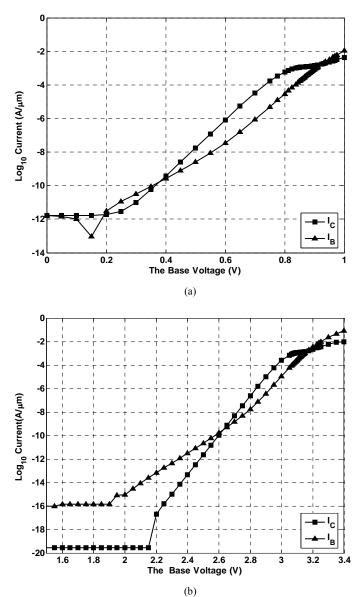

| Fig.4. 16 The IV Characteristics of the parasitic BJT in the power MOSFET (a) Si                   |            |

| (b) SiC                                                                                            |            |

| Fig.4. 17 SEGR of a power MOSFET                                                                   | . 91       |

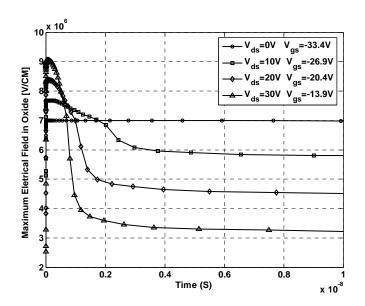

| Fig.4. 18 The transient maximum vertical electric field in oxide versus time                       |            |

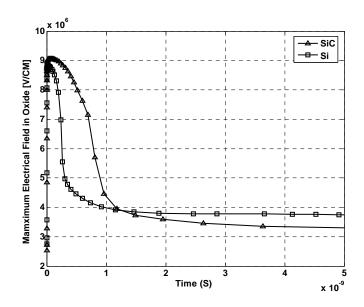

| Fig.4. 19 The transient response comparison between SiC power MOSFET and Si                        |            |

| • • • •                                                                                            | . 93       |

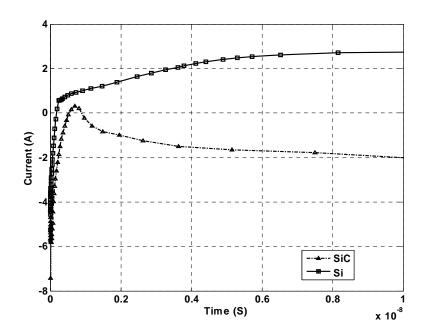

| Fig.4. 20 The transient current response comparison between SiC power MOSFET                       |            |

| and Si power MOSFET.                                                                               |            |

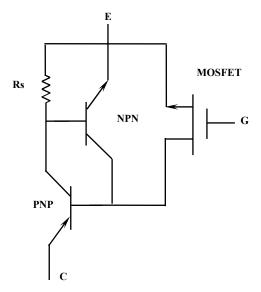

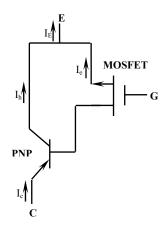

| Fig.5. 1 Equivalent circuit of the IGBT                                                            |            |

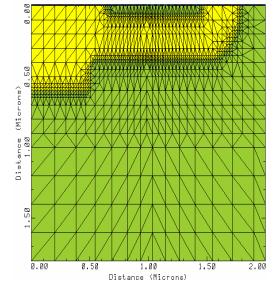

| Fig.5. 2 The PNP/MOSFET equivalent circuit model of a IGBT                                         |            |

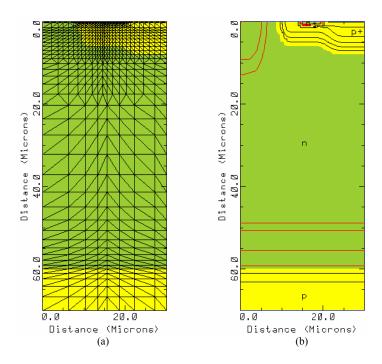

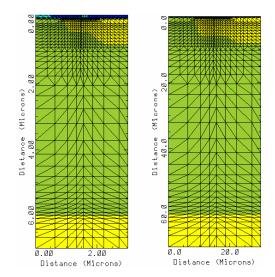

| Fig.5. 3 (a) The device mesh grid and (b) The doping profile contours                              |            |

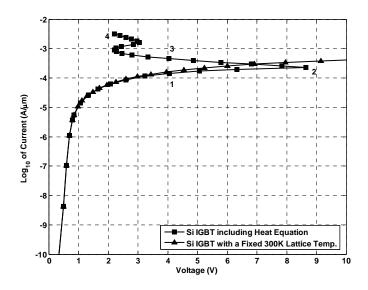

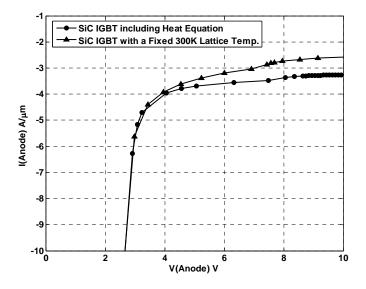

| Fig.5. 4 The nonisothermal and isothermal I-V characteristics of the simulated Si                  |            |

| IGBT                                                                                               | 106        |

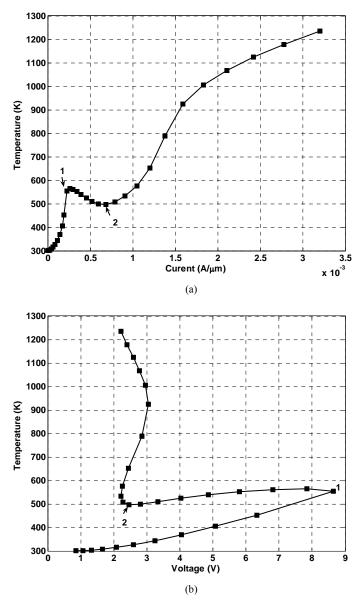

| Fig.5. 5 The maximum temperature increase within Si IGBT vs. (a) current, (b)                      |            |

| voltage                                                                                            | 107        |

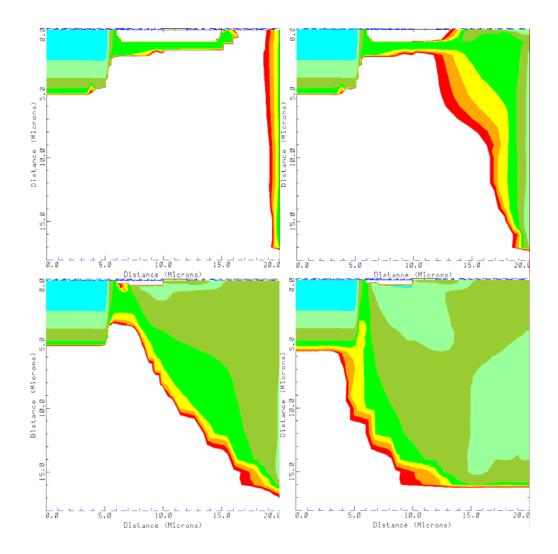

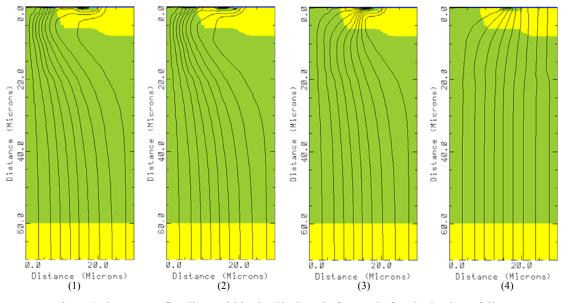

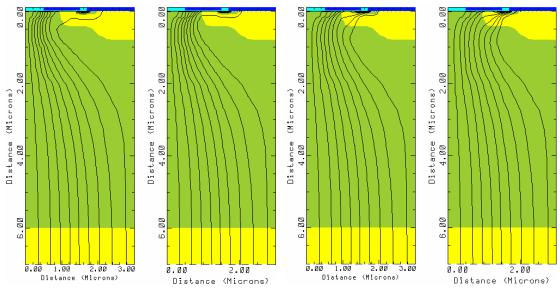

| Fig.5. 6 The current flowlines within the Si IGBT before and after the latch-up fail               | ure        |

|                                                                                                    |            |

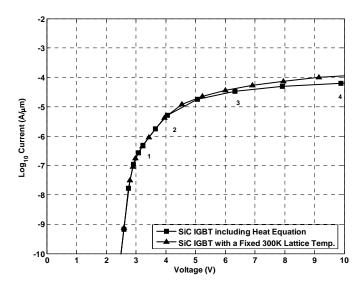

| Fig.5. 7 The nonisothermal and isothermal I-V characteristics of the SiC IGBT                      | 109        |

| Fig.5. 8 The maximum temperature growth within the SiC IGBT vs. current                            |            |

| Fig.5. 9 The current flowlines within the SiC IGBT                                                 |            |

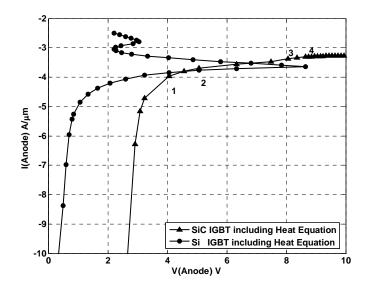

| Fig.5. 10 The nonisothermal I-V characteristics comparison between Si IGBT and                     |            |

| SiC IGBT                                                                                           | 112        |

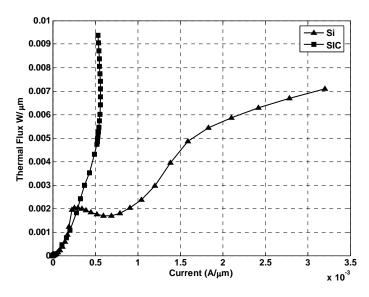

| Fig.5. 11 The thermal flux compassion between Si IGBT and SiC IGBT                                 |            |

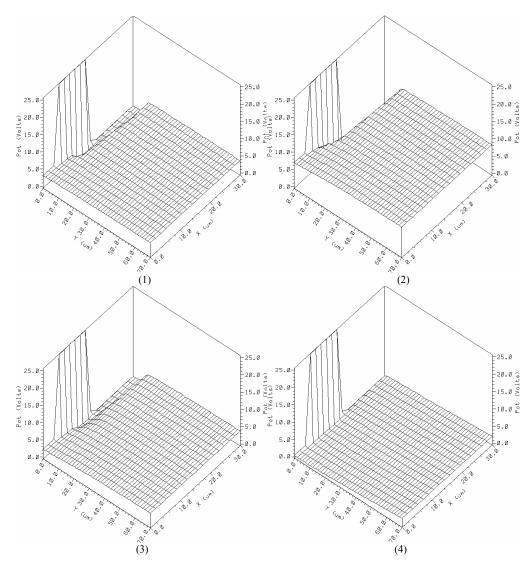

| Fig.5. 12 3D Potential plot corresponding to four stages of the Latch-up happened                  |            |

| Si IGBT                                                                                            |            |

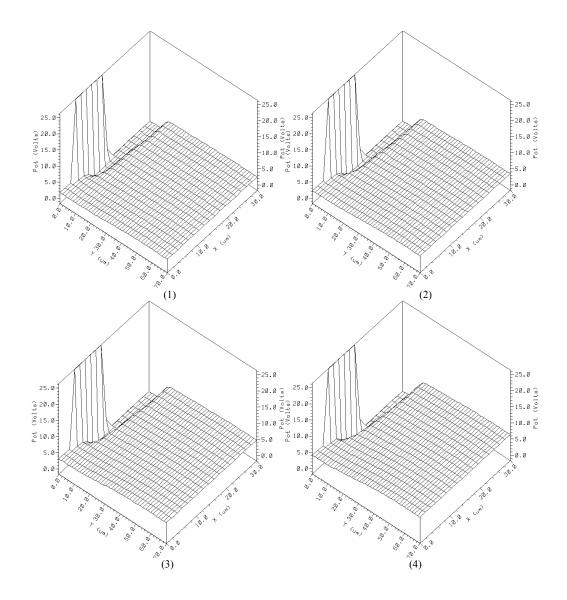

| Fig.5. 13 3D potential plots for SiC IGBT                                                          | 114        |

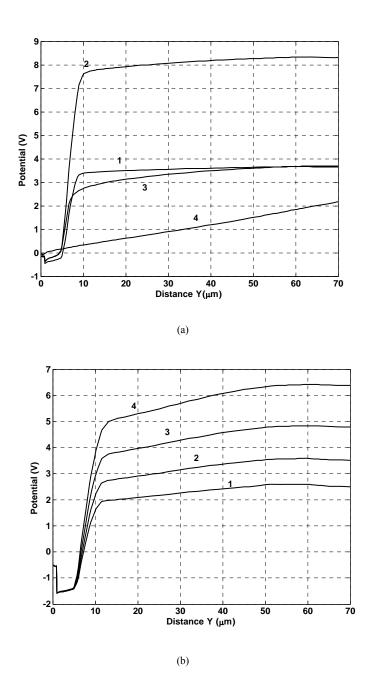

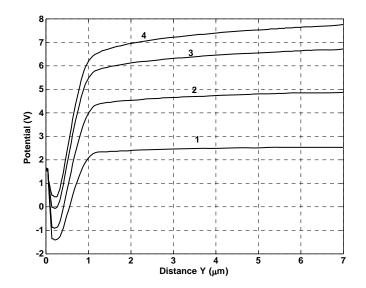

| Fig.5. 14 (a) 1D potentials for Si IGBT at x=20um (b) 1-D potentials for SiC IGBT                  |            |

| x=20um                                                                                             |            |

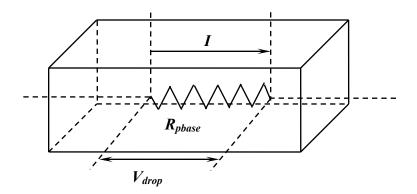

| Fig.5. 15 The rectangular box approximation of p-base region within the IGBT                       |            |

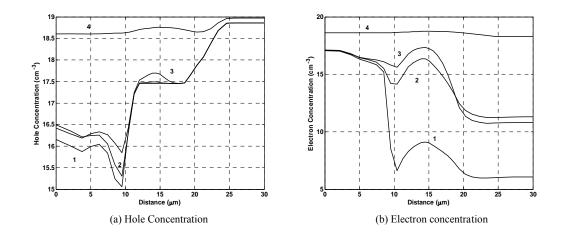

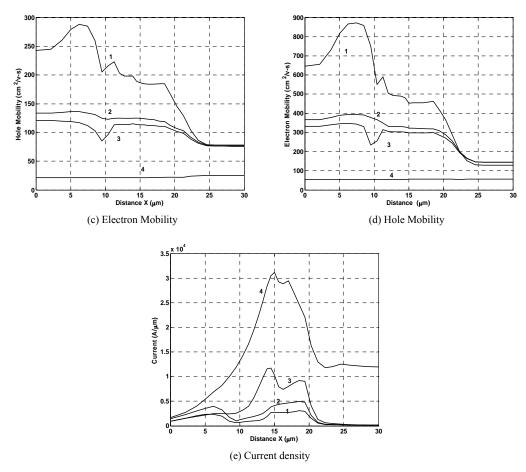

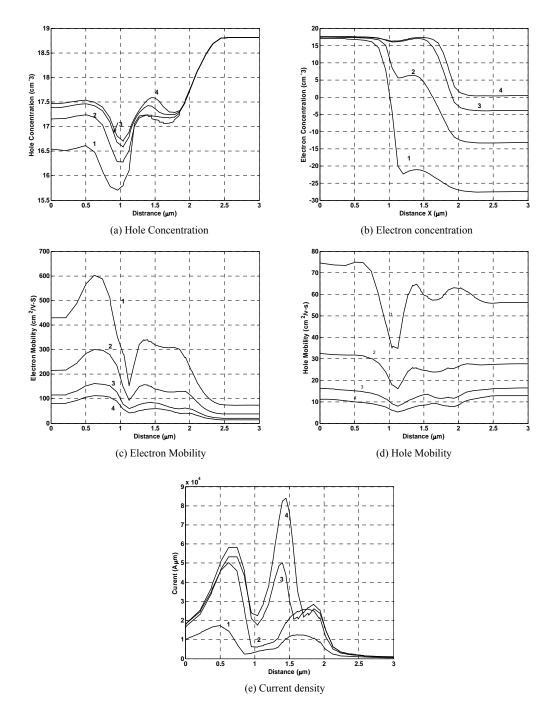

| Fig.5. 16 The current density, carrier concentration and mobility change within the                |            |

| simulated Si IGBT before and after the latch-up.                                                   |            |

| Fig.5. 17 The 1D current density plots at $y=1.5 \ \mu m$                                          |            |

|                                                                                                    |            |

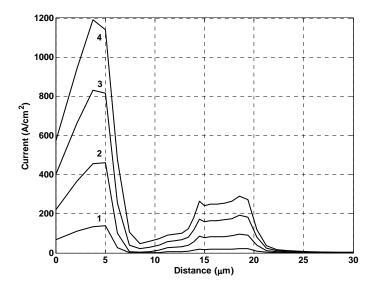

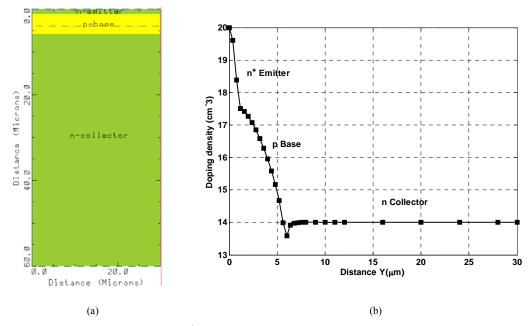

| Fig.5. 18 The extracted parasitic n <sup>+</sup> source/ p-base/n-drift transistor: (a) structure, (b | )  |

|-------------------------------------------------------------------------------------------------------|----|

| the doping profile                                                                                    | 22 |

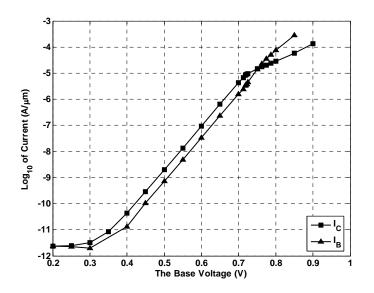

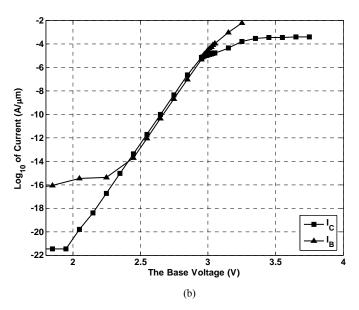

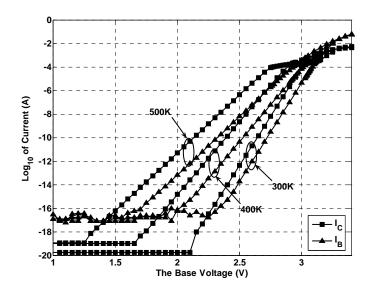

| Fig.5. 19 The I-V characteristics of the parasitic NPN transistors: (a) Si (b) SiC 12                 | 23 |

| Fig.5. 20 The I-V characteristics of the Si NPN transistors under 300K, 400K and                      |    |

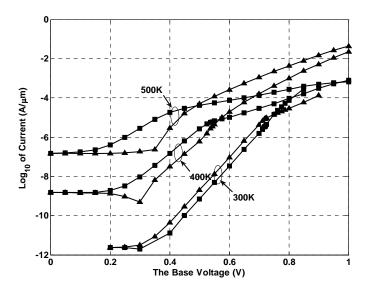

| 500K                                                                                                  | 24 |

| Fig.5. 21 The I-V characteristics of the SiC NPN transistor under 300K, 400K and                      |    |

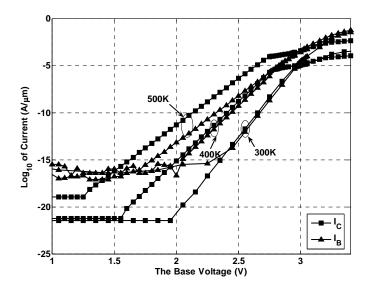

| 500K                                                                                                  | 25 |

| Fig.5. 22 The mesh grid of the simulated SiC and Si IGBT with a same voltage ratin                    | ıg |

|                                                                                                       | 26 |

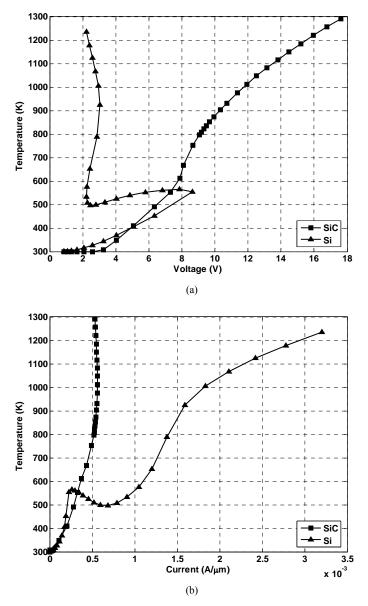

| Fig.5. 23 The simulation results for SiC IGBT with same voltage rating 12                             | 27 |

| Fig.5. 24 The I-V characteristic comparison between Si IGBT and SiC IGBT 12                           | 27 |

| Fig.5. 25 The maximum lattice temperature comparison between SiC IGBT and Si                          |    |

| IGBT (a)vs.Voltage (b)vs. Current                                                                     | 28 |

| Fig.5. 26 The thermal flux comparison between SiC IGBT and Si IGBT 12                                 | 29 |

| Fig.5. 27 The current flowlines of the SiC IGBT 12                                                    | 29 |

| Fig.5. 28 The potential changes at $x=0.8\mu m$ with the applied bias up to 8V 1.                     | 30 |

| Fig.5. 29 The current density, carrier concentration and mobility change within the                   |    |

| simulated SiC IGBT 12                                                                                 | 31 |

| Fig.5. 30 The I-V characteristics of the new SiC NPN transistor under 300K, 400K                      |    |

| and 500K1.                                                                                            | 33 |

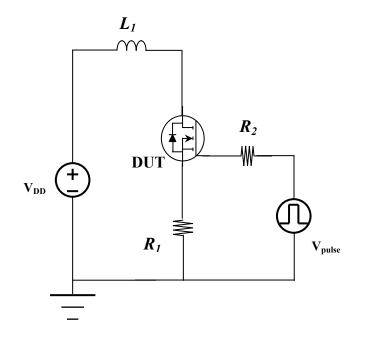

| Fig.6. 1 An unclamped inductive test circuit                                                          | 37 |

# **Chapter 1: Introduction**

# 1.1 Why SiC

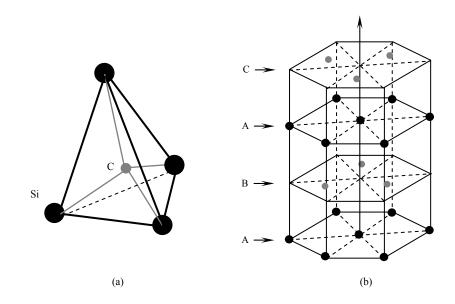

Silicon carbide (SiC), as one of the wide bandgap semiconductors, is the promising material for next-generation power devices due to its wide bandgap, high critical electric field, high thermal conductivity, and high saturated electron drift velocity. SiC has many polytypes. Out of all kind of polytypes, 4H-SiC and 6H-SiC are the most used ones for electronic devices. Both polytypes have a hexagonal frame with a carbon atom situated at the center of a tetragon of Si atoms as shown in the Fig.1.1. (a). The difference between the polytypes is the stacking order between succeeding layers of carbon and silicon atoms. A unit cell of 4H-SiC with the CABA stack sequence is shown in Fig.1.1. (b) meanwhile a unit cell of 6H-SiC has a stack sequence CBABCA. This study is only focused on in 4H-SiC.

Fig.1. 1(a) A carbon atom situated above the center of a tetragon of Si atoms (b) A unit cell of 4H-SiC

The typical properties of 4H-SiC, 6H-SiC and Si are compared in Table 1.1 below.

|                                            | 4H-SiC              | 6H-SiC              | Si                  |

|--------------------------------------------|---------------------|---------------------|---------------------|

| Bandgap (eV)                               | 3.26                | 3.03                | 1.12                |

| Critical Electric Field (V/cm)             | $2.2 \times 10^{6}$ | 2.4×10 <sup>6</sup> | 2.5×10 <sup>5</sup> |

| Thermal Conductivity (W/cm·K@RT)           | 3.0-3.8             | 3.0-3.8             | 1.5                 |

| Saturated Electron Drift Velocity (cm/sec) | 2.0×10 <sup>7</sup> | 2.0×10 <sup>7</sup> | 1.0×10 <sup>7</sup> |

Table 1. 1 The properties of 4H-SiC, 6H-SiC and Si

The high bandgap of SiC results in a very low intrinsic carrier concentration and negligible junction leakage currents. This allows high-temperature operation of SiC devices without excessive leakage current and avoiding thermal runaway.

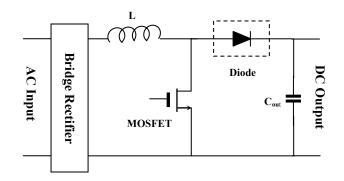

The high critical electric field  $E_c$  of SiC enables drift layers that are 10 times smaller than those of Si for a given blocking voltage, thus reduces both the storage of minority carriers ( $Q_{rr}$ ) and associated switching losses at a given switching frequency. One of applications of this feature is to use SiC Schottky diodes instead of traditional Si PiN diodes in the continuous conduction mode power factor correction circuits. A simple CCM-PFC circuit is shown in Fig.1.2.

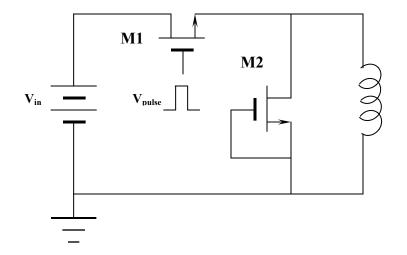

Fig.1. 2 A simple CCM PFC circuit

This circuit achieves near-unity power factor by chopping the full wave rectified input with a fast switch (MOSFET), and then stabilizing the resulting DC waveform using a capacitor. Traditionally a Si PiN diode is used in this circuit to prevent the current flow back from the capacitor. During the switching transient, a large current resulting from the large reverse recovery current of the Si PiN diode and the rectified input current rushes into the MOSFET. This large current is a big burden of the MOSFET switch, limiting the frequency and efficiency of the circuit.

However, due to the majority carrier transport property of SiC Schottky diode, it can offer very low reverse recovery switching loss in this PFC circuit while still keeping comparable on-state performance as conventional silicon rectifiers. In this case, only a small capacitive current flows through the MOSFET during its turn-off transient.

The high thermal conductivity makes SiC a better thermal conductor. Heat will flow more readily through SiC than Si materials. This property enables SiC devices to operate at extremely high power levels and still dissipate the large amount of excess heat.

With the availability of high quality commercial 4H-SiC and 6H-SiC SiC wafers, it has become more and more practical to make SiC power devices such as Schottky diodes, power MOSFETs and IGBTs. However, research studies on SiC power devices have been mainly focused on the electrical characterizations of them.

Little attention has been paid to studying the failure mechanisms of SiC power devices. This dissertation attempts to conduct some typical failure mechanism investigation for SiC power devices and contribute in this research area. The most frequently used power devices, Schottky diodes, power MOSFETs and IGBTs have been chosen and studied in this work. The failure mechanisms of these SiC power devices have been investigated and compared with traditional Si power devices.

The outline of this dissertation is as follows. In this introduction chapter the general failure mechanisms of these power devices have been categorized and introduced. In chapter 2 the drift-diffusion model has been introduced in details since it is the basis of the simulations conduced in this work. In chapter 3 the DC characteristics of a SiC Schottky diode have been measured and simulated to verify the correctness of the physical models used for 4H SiC. A non-catastrophic failure mechanism has been investigated for the SiC Schottky diode. In chapter 4 the Single-event-burnout (SEB) and the Single-event-gate rupture failure mechanisms have been studied for SiC power MOSFETs. Investigating these two failure mechanisms is crucial since the failures triggered by them happen in very critical applications. In chapter 5 the latch-up failure mechanism has been investigated for SiC IGBTs. Finally the study conduced in this work has been summarized. We will begin by introducing the general failure mechanisms happened in power Devices.

# **1.2 Failure Mechanism of power devices**

In this section the failure mechanisms of Schottky diodes, power MOSFETs and IGBT are introduced respectively.

# **1.2.1 Failure mechanism of Schottky diodes**

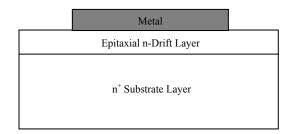

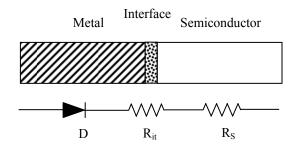

A Schottky diode is typically made by a piece of metal layer and a piece of semiconductor material layer (n-type or p-type). The schematic cross-section of a Schottky diode is shown in Fig.1.3. As a majority carrier device, Schottky diodes have the primary advantages of very low forward voltage drop and near to zero switching time. These characteristics make them the ideal switching devices used extensively in the power supply industry. However, few complete reports about the failure mechanisms happened in Schottky diodes have been documented. Thus a summary of failure mechanisms of Schottky diodes is provided in this section which can be used for device design guideline.

Fig.1. 3 The schematic cross-section of a Schottky diode

As the simplest semiconductor device, the failure mechanisms of Schottky diodes can be categorized into two groups: non-catastrophic and catastrophic. noncatastrophic failures happen when the characteristics of Schottky diodes degrade over time due to the non-catastrophic failure mechanism. The diode cannot perform as required after a certain amount of device lifetime. In contrast, catastrophic failure mechanisms result in failures happened suddenly in the Schottky diode during their normal operation. The two types of failure mechanisms are introduced respectively in the following sections.

#### **1.2.1.1 Catastrophic failure mechanisms of Schottky diodes**

Catastrophic failures of Schottky diode are one of major failures happened in field for Schottky diodes. Research efforts have been made to identify the failure mechanisms behind the failures. Lin *et al.* reported catastrophic failures of GaAs Schottky diodes in [1]. The failure analysis showed that the inside cracks were formed due to the release of high structure overstress caused by the high junction temperature within the device during its long time operation. When the cracks propagated into the Schottky contact region, it will cause the abrupt electrical change of the device and lead to a catastrophic failure. Catastrophic failures of GaAs Schottky diode was also investigated by Brandt *et al.* in [2]. In the designed tests, GaAs Schottky diodes were driven in a forward operation mode with a high current density. Hot spots or hot filaments were generated inside the bulk material because of the high local current density. Then catastrophic failure was observed in the

device with a destroyed GaAs layer. The failure mechanism was attributed to this thermal degradation inside the device.

Another type of catastrophic failure mechanism of Schottky diodes is known as diode avalanche breakdown. When the applied reverse voltage applied on the Schottky diodes, the electric field within the diode is so strong that thermally generated electrons and holes can get enough kinetic energy to knock on atoms and generate extra electron-hole pairs within the diode. With these newly generated electron-hole pairs, this process will continue and be amplified under the high electrical field. As a result, a dramatically increased reverse current will generate within device and destroy the device thermally over a certain time period.

# 1.2.1.2 Non-catastrophic failure mechanisms of Schottky diodes

Non-catastrophic failure happens in Schottky diodes. The characteristics of the Schottky diodes such as I-V characteristics can be seriously degraded during their normal operation. Lin *et al.* defined the non-catastrophic failure criteria for the tested GaAs Schottky diodes when any of three conditions is met: (1) the ideality factor  $\eta$  changes by 10%, (2) the series resistance  $R_s$  change by 20%, (3) the turn-on voltage  $V_0$  (voltage where current is 1µA) change by more than 20% [1]. In the following accelerating tests they performed, non-catastrophic failures were recorded when the diode characteristics slowly degraded to the failure criteria. The SEM image of the non-catastrophically failed device showed no crack within the diode. Schubler *et al*,

conducted another reliability test on Schottky diodes under electrical pulse stress in [3]. I-V characteristic degradation of Schottky diodes was also observed. However the failure mechanisms responsible for these non-catastrophic failures in Schottky diode were not clear to the authors.

In this work, the interface state degradation between the metal and semiconductor layer is believed to be responsible for these non-catastrophic failures. Interface states were experimentally proved to be thermally active. The formation of interface traps in Au/InGaP Schottky diodes was reported in [4]. The interface states were generated during heat treatment. The origin of these interface states was attributed to the transformation of a simple phosphorus vacancy to antisite-related defect such as Ga<sub>p</sub>, and In<sub>p</sub>. Interface states generated during the annealing process in Ti/n-GaAs Schottky diode were also investigated in [5]. The interface states were attributed to the annealing processing which removed the passivation effect of the native oxide layer and reactivated these surface defects. Similar results were obtained for n-type 6H-SiC Schottky diodes in [6]. During annealing process significant reactivation of the passivated defects was shown to start at some temperature between 350 and 400 °C. Thus in this study the interface states is proposed to be responsible for these non-catastrophic failures of Schottky diodes. Detailed numerical simulations for proving this will be introduced in Chapter 3.

# 1.2.2 Failure mechanism of power MOSFETs

Power MOSFETs are the key components in power electronic circuits. They have been used extensively in all kinds of industry applications. A complete understanding of the failure mechanisms of power MOSFETs will help to provide guidelines for field applications and prevent failures.

Traditional lateral MOSFETs have the drain-to-source current confined to a thin planar volume of silicon lying parallel to the gate. The device conduction area and power handling capability, however, are limited by this geometry. Power MOSFETs solved this problem with a vertical conduction channel. The rating of power MOSFETs can reach to hundreds of voltages and hundreds of amperes with the greatly increased conduction area.

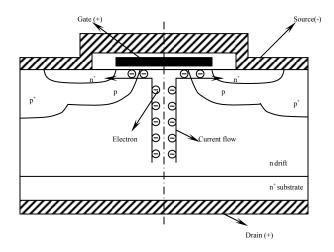

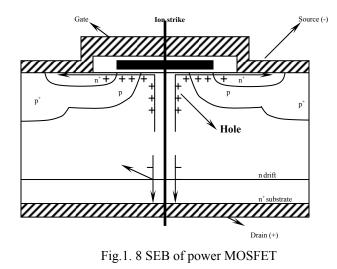

There are two main vertical gate structure designs for power MOSFETs: DMOS and VMOS. Fig.1.4 shows the vertical cross-section of a DMOS structure. The current path in the device is created by inverting the p-base region under the gate which is the same approach used for the lateral MOSFETs.  $N^+$  source current flows underneath the gate area and vertically through the drain region. As majority carrier devices with gate control, Power MOSFETs have many advantages over traditional power bipolar transistors, such as very fast switching speed and simple gate-driven circuits.

Fig.1. 4 Vertical DMOS Cross Section

The failure mechanisms of power MOSFETs are different from those of traditional lateral MOSFETs due to their special structures. For example, hot carrier degradation (HCD) is one of failure mechanisms of lateral MOSFETs, but is not an issue for power MOSFETs since the gate region and drain region of it are separated at the two ends of the device. Compared to the extensive study of failure mechanisms of lateral MOSFETs, a review of failure mechanisms of power MOSFETs is needed. The main failures of power MOSFETs can be categorized into two groups: gate oxide breakdown and the activation of parasitic structures inherent in power MOSFETs. The activation of parasitic structures of power MOSFET can be further divided into two categories: the activation of parasitic bipolar transistor (BJT) in power MOSFETs and the activation of parasitic diode in power MOSFETs. These failures can be triggered by different mechanisms when powers MOSFETs are used in different harsh environment, such as extreme transient stress or high radiation environment. The inherent parasitic bipolar and diode structure in power MOSFETs are introduced

in the next section followed by the discussion of the failure mechanisms of power MOSFETs.

#### **1.2.2.1 Inherent parasitic structures in power MOSFET**

Since the gate structure of power MOSFETs are similar to that of lateral MOSFETs, only the inherent parasitic structures of power MOSFET are addressed here. The inherent parasitic structures in power MOSFET include a parasitic bipolar transistor and a parasitic diode.

A parasitic *NPN* bipolar transistor inherent in a DMOS is shown on the left side of Fig.1.5. The source, p-region, and n drift region of this power MOSFET comprise the emitter, base and collector region of the parasitic bipolar transistor respectively. In normal operation of the power MOSFET, this parasitic bipolar transistor is always off since the source and p-region is connected by the same metallization layer that shorts the base-emitter junction of the bipolar transistor.

The parasitic body diode formed between the source and the drain is shown on the right side of Fig.1.5. The source acts as anode of the diode and the drain acts as cathode of the diode. This diode is usually reverse biased since the drain voltage is normally larger than the source voltage.

Fig.1. 5 Parasitic NPN transistor and diode inherent to DMOS

The parasitic BJT and diode introduced above are the weaknesses of power MOSFETs. Although those parasitic devices keep inactive under normal condition, failure can still occur when the turn-on of those devices is triggered under certain circumstances. The failure mechanisms of them will be introduced and summarized in the following.

# 1.2.2.2 Failure mechanisms in power MOSFETs

# Gate Dielectric breakdown in power MOSFETs

Gate dielectric breakdown is inherent in MOS devices since the unique MOS gate structure is used to control the turn-on and turn-off of the devices. Two failure mechanisms have been identified for gate dielectric breakdown in power MOSFETs:

Time-dependent dielectric breakdown (TDDB) and Single-event-gate-rupture (SEGR).

## **Time Dependent Dielectric Breakdown (TDDB)**

As the most common failure mechanism in MOSFETs, time dependent dielectric breakdown (TDDB) has been studied extensively. Generally speaking, Time-dependent dielectric breakdown (TDDB) means the destruction of gate dielectric layers over time. This breakdown is related to the defect accumulation within the dielectric material. The basic idea is that with the electric field stress over time, defects are built up in the SiO<sub>2</sub> gate. When the defect density reaches a critical level, a conduction path is formed. Abrupt increased gate current is observed and eventually the MOSFET lost its gate voltage controllability. Different mechanisms have been proposed to explain how the defected inside SiO<sub>2</sub> is created and accumulated. Among them the thermochemical model, the hydrogen model and the anode-hole-injection (AHI) model are widely accepted ones. The thermochemical model, also known as E model, assumes a direct correlation in existence between the electric field and the oxide degradation. The weak chemical bonds (Si-Si bonds) in SiO2 associated with oxygen vacancies experience heavy strains due to the high electric field applied across the oxide and some bonds may obtain enough thermal energy to break off and create defects. The hydrogen model states that a hydrogen atom will be kicked out from the SiO<sub>2</sub>/Si interface when electron reaches the anode. This atomic hydrogen then will diffuse into the oxide bulk. When it encounters an oxide defect, presumably an oxygen vacancy, it can turn the defect into a trap that

contributes to breakdown. The anode-hole-injection (AHI) model proposes that the origin of the positive trapped charges in the oxide after stress is due to anode injection of holes. It should be pointed out that these models can only fit experimental data in a certain range of electric field. Great care should be taken in using them in field.

# Single-event-gate-rupture (SEGR) in Power MOSFETs:

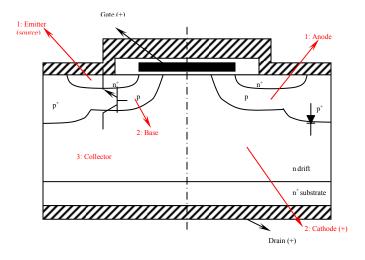

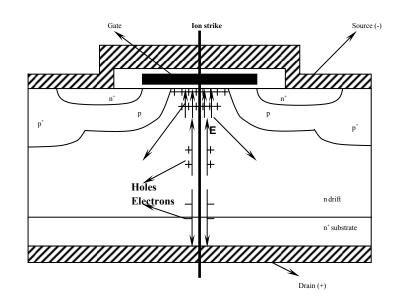

SEGR is another failure mechanism of oxide breakdown happened in power MOSFETs. Power MOSFETs are often used in space system because of their outstanding electrical characteristics. However they are vulnerable to SEGR failures when exposed to the radiation environment of space. The natural space contains high-energy protons and heavy ions as the existing of extensive radiation. When a heavy ion penetrates the gate region of a power MOFET while the drain is under positive bias (n-channel), the electron-hole pairs generated along the path of the ion start to separate as shown in Fig.1.6. The holes are driven toward the gate and the electrons flow toward the drain. A net positive charge accumulates in the silicon at the Si-SiO<sub>2</sub> interface as a result of this charge separation. The charge buildup results in a transient electric field increase upon the gate oxide. If the increased electric field exceeds the critical oxide breakdown field  $E_{cr}$ , oxide breakdown occurs and results in a permanent short circuit through the oxide. This failure mechanism has been studied extensively in the 90's. Different aspects about this failure mechanism has been reported in literature, including oxide thickness dependence, temperature dependence and ion threshold energy, etc  $[7] \sim [13]$ .

### Activation of parasitic bipolar transistor (BJT) in power MOSFETs

The parasitic BJT structure in a power MOSFET is shown in Fig.1.5. As we mentioned before the parasitic BJT is normally inactive since the base-emitter junction is shorted together. However the BJT can still be turned on under some circumstances, even though the base-emitter junction is shorted externally. This will cause the device to lose the gate control and result failures of power MOSFETs. Two types of mechanisms that can active the parasitic BJT in power MOSFETs were identified. One mechanism is activated during the turn-off of power MOSFETs. When a power MOSFET is turned off, the very high dV/dt or dI/dt can activate the parasitic BJT. The other mechanism is triggered when power MOSFET is used in a high radiation environment. The parasitic BJT can be turned on when a heavy ion strike on the power MOSFETs device.

## Activation of parasitic BJT during the turn-off of power MOSFETs

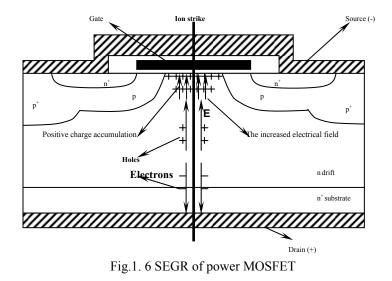

In order to explain how the activation of parasitic BJT in power MOSFETs occurs, the equivalent circuit for an n-channel power MOSFET is shown in Fig.1.7 where a NPN parasitic bipolar transistor is included.  $C_{gd}$  and  $C_{gs}$  represent the parasitic capacitances between gate to drain and gate to source.  $C_{db}$  is another parasitic capacitance existing between drain and source.  $Z_{gs}$  is the gate-to-source impedance and  $R_{be}$  is the resistance along the source channel.

Fig.1. 7 Equivalent circuit of a power MOSFET

Failure can happen during the turn-off of a power MOSFET. A sudden increase in drain voltage (dV/dt) changes the voltage across capacitor  $C_{db}$ , a displacement current flows through resistor  $R_{be}$  when a power MOSFET is turning off. The current generates a voltage drop in the base-emitter junction. When  $V_{be}$ , the voltage across the  $R_{be}$ , is increased to approximately 0.7V, the parasitic bipolar transistor, shown in Fig.1.5 and Fig.1.7, is turned on. When the parasitic bipolar transistor is on, the device lose its gate control and the breakdown voltage of the device is reduced from  $BV_{CBO}$  to  $BV_{CEO}$  which is 50~ 60% of  $BV_{CBO}$ . If a drain voltage is larger than  $BV_{CEO}$  is supplied, the device falls into an avalanche breakdown. If the avalanche current is not limited externally, the device can be destroyed thermally.

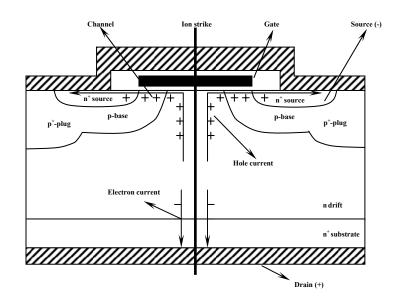

# Single-event-burnout (SEB) in Power MOSFETs

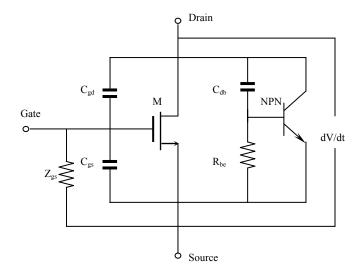

Similar to SEGR, SEB is also initiated when a heavy ion strike through a power MOSFET biased in the OFF state. As the heavy ion traverses the device, electron-hole pairs are generated along its track length and create transient currents in which holes flow up towards source via the lateral base region and electrons toward drain. This current leaking through the p-base region will generate a voltage drop in the base-emitter junction as shown in Fig.1.8. When the voltage drop is larger than a threshold value it will turn on the parasitic bipolar junction transistor inherent in power MOSFETs. Due to a regenerative feedback mechanism, high current and voltage will occur in the device channel and trigger the second breakdown of power MOSFET and destroy the device.

17

+

# Parasitic diode avalanche breakdown in power MOSFETs

Avalanche breakdown can happens in the parasitic diode in power MOSFETs. As shown in Fig.1.5 the parasitic diode formed between the source and drain of the power MOSFETs. The source acts as the anode and the drain acts as the cathode. Since this diode is always under reverse biased, a sudden increased drain-source voltage can result in an avalanche breakdown in this diode.

As an example, a synchronous-rectified converter is constructed in Fig.1.9 to illustrate this failure mechanism. The power MOSFETs are used as synchronous rectifiers in this half-bridge switching circuit with an inductive load. In this circuit, the high-side power MOSFET  $(M_1)$  is first turned on to load the inductor L to the desired current level first. Then  $M_1$  is turned off to force the inductor current to freewheel through the body-diode of the low side MOSFET  $(M_2)$ . Finally  $M_1$  is

turned on again to turn the diode off. However after the  $M_1$  is turned off, a very high voltage can be created in the inductance which is much larger than  $V_{in}$ . This voltage is completely applied on  $M_2$ . The abnormal high voltage can cause avalanche breakdown in the Mdiode within  $M_2$ .

Fig.1. 9 A synchronous rectifiers with power MOSFETs

# **1.2.3 Failure Mechanisms in IGBTs**

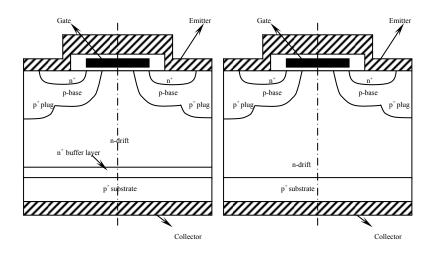

IGBTs (Insulated gate bipolar transistors) are another type of important power devices widely employed in hard-switching applications, such as include power conversion and motor drives. By combining the best features of BJT and MOSFET, IGBTs have many desirable properties including a MOS input gate, high switching speed, low conduction voltage drop, high current carrying capability and wide SOA. IGBTs have either a punch-through structure (PT) or non-punch-through structure (NPT) which features different characteristics [14]. Fig.1.10 shows the vertical cross section of a PT and a NPT IGBT structure. IGBT structure is similar to the power MOSFET structure except an additional p+ layer has been added to the drain side of the MOSFET. It consists of a four-layer sandwich of  $n^+/p/n/p^+$ . The gate consists of a polysilicon layer which is separated by an oxide layer grown on the top surface of the silicon wafer. The polysilicon layer overlaps the  $n^+$ -source, p-base and n-drift regions. The emitter is made of metal contact which overlaps the  $n^+$ -source and p-base regions on the top. The collector is made by metal contact on the  $p^+$ -region in the bottom.

Fig.1. 10 The vertical cross section of the PT and NPT IGBT structures

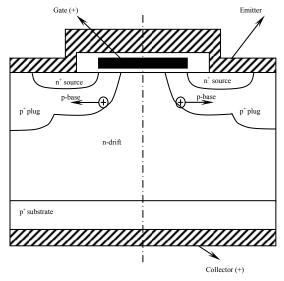

In the normal operation mode, the collector is positive with respect to emitter. If the gate is at zero potential with respect to emitter, no main current flows from collector to the emitter. As shown in Fig.1.11 when gate potential becomes positive with respect to emitter, electrons are attracted in the p region below the gate oxide and eventually inverting the polarity of p type to n type. This inversion layer hence provides an n-channel from the  $n^+$  layer to the n layer. Electrons are injected from the n+ emitter contact into the n- region thus lowering the potential of this region and forward biasing the  $p^+ n^-$  junction from the collector side. Hence holes are injected from the collector into the n-drift layer.

Fig.1. 11 The operation of the turn-on process of IGBTs

The excess holes and electrons in the n- region reduce the resistivity of this region. This is known as conductivity modulation, which reduces the on-state resistance of the device. This is why for a similar voltage design, an IGBT has a lower on-state resistance than a power MOSFET which does not exhibit conductivity modulation. In the PT structure, the injected holes from the p+ collector have to cross over the n+ buffer layer to reach n- base. Some of these holes are lost in the buffer layer due to recombination process. Consequently, the injection efficiency of the p+ is reduced. This has a significant influence on the dynamic characteristics of the IGBT.

# Thermally assisted carrier multiplication

Thermally assisted carrier multiplication was proposed as the failure mechanism of IGBTs in [15]. Current flow through a region with high-electric field within IGBTs will lead to significant power dissipation. This dissipated power results in self-heating within the device and raises the working temperature of the device. The raised temperature will greatly increase the intrinsic carrier concentration and the net carrier multiplication rate of IGBTs. Again since IGBTs are used in high current conditions, the large current leads to a redistribution of charges and the electric field within the device. The increased charge density leads to higher peak electric field at the reverse-biased junction. This results in higher impact generation rate at the junction with a lower breakdown voltage than static conditions. With the combination effects of these two factors, IGBTs can fail under certain conditions. The most common high stress switching conditions for IGBTs are short circuit and clamped inductance switching conditions. How IGBTs failure because of thermally assisted carrier multiplication under these two conditions are introduced below.

# Short circuits failure

Short-circuit switching is one of the most severe stress conditions for power devices, since a large current flows through the device while it is supporting the entire bus voltage. A test circuit for IGBT short circuits failures was used in [15] as shown in Fig.1.12. The IGBT was turned on with full bus voltage across and turned off after

a desired duration of stress. The results showed that the device subjected to this short-circuit stress failed after 15µs of stress [15].

Fig.1. 12 Test circuit for IGBTs for short circuits failures

During the test the device can turned off successfully when gate voltage is removed and the temperature is within safe limits. The inversion channel under the gate is removed when the gate voltage is below the threshold value and electron current is abruptly cut off in the channel. Because the current out of the emitter is only the hole current, the current density is much lower and temperature within the device gradually falls off. The trapped excess charge in the drift region decays due to recombination.

However if the device is allowed to operate over a long duration under short condition, the temperature will rise steadily. Current crowding around the reversebiased junction curvature will result in a much higher impact generation rate. The carrier density is dramatically increased. Thus, there will have a local maximum of impact generation around the p-base/n-drift junction. The high impact generation and temperature in this region will initiate a regenerative process and the device will eventually break down due to this thermally assisted carrier multiplication. Under this condition, the current of IGBTs will rise uncontrollably while voltage falls down. The device fails to turn off even after gate voltage is removed and result in a catastrophic device failure.

# **Clamped inductive switching failure**

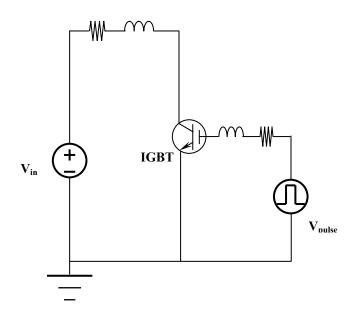

Most common loads in power electronic circuits are inductive in nature. Thermally assisted carrier multiplication as the failure mechanism can also happen in IGBTs under clamped inductive switching condition [15]. A clamped inductive switching circuit for IGBTs is shown in Fig.1.13.

Fig.1. 13 A clamped inductive switching circuit used for IGBTs

In this circuit the switch S and the IGBT are turned on at the same time. After the inductor charges up through the device to a desired current level, the switch and IGBT are turned off simultaneously. The current will flow through IGBT and the freewheel diode D. Because the gate voltage is removed, the voltage on IGBT starts increasing rapidly to support the external current. The Zener diode will clamp the device voltage to the Zener diode breakdown voltage and prevent IGBT failure due to excessive rise in voltage. Once the voltage on IGBT beyond the Zener diode breakdown voltage, current will divert to the Zener diode and IGBT current decays with a recombination-dominated current tail.

In the on-state of IGBT, the electrons flow through the MOS channel and holes flow laterally in the p base. When the gate voltage is removed, electron current will be cut off. The inductive load, however, will still force the current through the device. This current can only be supported by the hole current and the displacement current of expanding depletion region in the device bulk. The hole current will rise up to meet the external current requirements within the IGBT. With the voltage on the IGBT rising up to support the inductor current, the electric field and impact generation rate at the p-base n-drift region junction keep increasing. The power dissipation will be significant with the high current density and high electric field in this region. Beyond a threshold value of power dissipation, the temperature rise is high enough to lead to device destruction. IGBT failure in this condition is due to thermally assisted carrier multiplication along the parallel plane reverse-biased junction of p base with the n-drift region.

### Latch up failure in IGBTs

The IGBT structure shown in Fig.1.10 has a parasitic thyristor structure (NPNP) between the collector and the emitter. When the parasitic thyristor is turned on, the IGBT current will not be controlled by the MOS gate. The IGBT could be destroyed because of the excessive power dissipation produced by the high current flowing through the devices. The parasitic thyristor latch up can occur in IGBTs in two modes: static lat-up mode and dynamic latch-up mode. In the static mode, when the steady-state current density exceeds a critical value the latch-up will occur. The dynamic latch-up happens during switching conditions [16].

### Static latch-up:

Since the conductivity of the drift region under the gate electrode is increased by the introduction of electron current through the channel, most of the holes injected into the drift region are injected at p-base region under the channel and flow to the source metal along the bottom of n<sup>+</sup>-source. Due to this, the lateral voltage drops across the p-base region. If the voltage drop becomes greater than a threshold value, electrons are injected from the n<sup>+</sup>-emitter to the p-base, and the parasitic NPN transistor (n<sup>+</sup>-emitter, p-base and n-drift) is turned on. If the sum of the two NPN, PNP parasitic transistors base transport gain becomes larger than 1 ( $\alpha_{TNPN}+\alpha_{TPNP}\geq 1$ ), the parasitic thyristor will be turned on and latch-up occurs [17]. As shown in Fig.1.10 the introduction of a deep, high concentration of p<sup>+</sup> region in IGBT device is used to reduce the resistance of p-base region and the potential drop caused by the hole current along the n<sup>+</sup>-emitter and p-base junction. Once the voltage drop in that junction can be control under the threshold voltage, the parasitic NPN transistor will be disabled.

### **Dynamic latch-up**

Dynamic latch-up occurs in IGBTs under switching conditions. It is very interesting to know that the dynamic latching current is identical to the static latching current when latch-up happens during the turn-on of IGBTs and lower during gate-controlled turn-off of IGBTs [17]. When the IGBT is turned off, the depletion layer of the N<sup>-</sup> drift and P base junction is abruptly extended to support the rising voltage, this increased depletion layer will increase the resistance of p base region. In addition to the displacement current, IGBT can latch up at a current lower than 1/2 of the static latch-up current.

### 1.3 Numerical simulation of failure mechanisms of SiC power devices

Two-dimensional numerical simulation approach has been used in this work to study the failure mechanisms of SiC power devices. The simulation algorithm is based on the basic semiconductor drift-diffusion model including Poisson equation, current continuity equation and carrier drift-diffusion equation. The detailed driftdiffusion model introduction is given in Chapter 2. The failure mechanisms of SiC Schottky diode, power MOSFETs and IGBTs are studied and studied in Chapter 3, Chapter 4, and Chapter 5 respectively.

# **Chapter 2: Drift-Diffusion Modeling for SiC Power Devices**

The drift-diffusion model is frequently used to describe the characteristics of semiconductor devices which is the basis for all the numerical simulations conducted in this work. The basic equations included in the drift-diffusion model are introduced in details in this chapter. Different SiC physical models associated with the drift-diffusion model are discussed.

# 2.1 Poisson's Equation

Poisson equation relates the potential in a semiconductor material to its charge density by a divergence relationship:

$$\vec{\nabla}^2 \phi - \frac{q}{\varepsilon} \left( n - p + N_a^- - N_d^+ \right) = 0 \quad (2.1)$$

Where  $\phi$  is the potential, *e* is the electron charge,  $\varepsilon$  is the dielectric permittivity of the semiconductor, *n* and *p* are the electron and hole concentrations, and  $N_d^+$  and  $N_d^-$  are the ionized donor and acceptor concentration.

The values of  $N_d^+$  and  $N_d^-$  in equation (2.1) are usually taken the initial carrier doping values. However the results obtained in this way will be only approximated ones without taking the incomplete ionization effect into consideration. The incomplete ionization in SiC can be modeled as [18]:

$$N_d^+ = \frac{N_d}{1 + g_d \frac{n}{N_c} \exp\left(\frac{E_c - E_d}{K_B T}\right)} \quad (2.2)$$

for donors and

$$N_a^- = \frac{N_a}{1 + g_a \frac{p}{N_v} \exp\left(\frac{E_a - E_v}{K_B T}\right)} \quad (2.3)$$

for acceptors.

Where  $N_d^+$  and  $N_a^-$  are the ionized (activated) donor and acceptor concentration while  $N_d$  and  $N_a$  are the initial donor and acceptor doping values respectively, n and p are the electron and hole concentration,  $g_d$  is the ground-state degeneracy of donor impurity levels in SiC and  $g_a$  is the ground-state degeneracy of acceptor impurity levels,  $N_c$  is the conduction band effective density of states and  $N_v$  is the valence band effective density of states,  $E_c$  is the conduction band minimum energy and  $E_d$  is the valence band maximum energy,  $E_d$  is the inner-gap energy level for donor impurity

states and  $E_a$  is for acceptors,  $k_B$  and T are the Boltzmann constant and ambient temperature, respectively.

In equations (2.2) and (2.3) the energy difference  $\Delta_d = E_c - E_d$  and  $\Delta_a = E_a - E_v$ are the thermal ionization energy needed for the donor and accepter impurity atoms respectively.

The relationship between the electron concentration *n*, hole concentration *p*, and the conduction band minimum energy level  $E_c$  and valence band maximum energy level  $E_v$  are given by:

$$n = N_c \exp\left(\frac{E_f - E_c}{k_B T}\right) \quad (2.4)$$

and

$$p = N_v \exp\left(\frac{E_v - E_f}{k_B T}\right) \quad (2.5)$$

Where  $E_f$  is the Fermi level.

The Fermi level  $E_f$  is only quoted under thermal equilibrium condition. However two quasi-Fermi levels for electron and hole are needed to be introduced to handle nonequilibrium cases. The quasi-Fermi levels for electrons and hole are related to the intrinsic carrier concentration and the electron and hole concentrations respectively. They are defined as follows:

$$E_{fn} = E_i + k_B T \ln\left(\frac{n}{n_i}\right) \quad (2.6)$$

for electrons and

$$E_{fn} = E_i + k_B T \ln\left(\frac{n}{n_i}\right) \quad (2.7)$$

Where  $E_i$  is the intrinsic Fermi level.

Because of the lattice structure of silicon carbide, impurity atoms can occupy different types of sites in the crystal. For examples there are two inequivalent (C or Si) sites in 4H-SiC, one with cubic (k) surrounding and the other with hexagonal (h) surrounding as described in [19]. Since each site has different ionization energy for the dopants, this indicates different values of  $\Delta_d$  or  $\Delta_a$ . The model for incomplete ionization in (2.2) can be expanded as:

$$N_d^+ = \sum_i \frac{\delta_i N_d}{1 + g_d \frac{n}{N_c} \exp\left(\frac{E_c - E_{di}}{k_B T}\right)} \quad (2.8)$$

for electrons and

$$N_a^- = \sum_i \frac{\delta_i N_a}{1 + g_d \frac{p}{N_v} \exp\left(\frac{E_{ai} - E_v}{k_B T}\right)} \quad (2.9)$$

for holes.

Where  $\delta_i$  is the probability of a site being ionized at the i<sup>th</sup> site and  $E_{di}$  and  $E_{ai}$  are the ionization energy associated with that site. Based the assumption that average contribution is from the different ionization levels, the value of  $\delta_i$  in (2.8) is 1/2 for 4H-SiC since it has two sites for donor impurity to occupy. And the value of  $\delta_i$  for 6H-SiC is 1/3 since it mainly has three main ionization energy levels. The values of  $g_a$  and  $g_d$  in the equations are equal to the reciprocal of  $\delta_i$ .

The most common dopant for n-type SiC is *N*. Doping with *N* leads to a donor (substituting on C-site) which has two different energy levels below the conduction band. The reason for the two ionization energies is that in 4H-SiC there are two inequivalent C (or Si) sites, one with cubic (k) surrounding and the other with hexagonal (h) surrounding [20]. Nitrogen atoms substituting on these sites experience somewhat different surroundings, giving rise to different ionization energies. In fact, it was found in [3] that *k*-type *N* causes deeper levels than *h*-type *N*. It is also expected that the number of *k*-type and *h*-type donors are more or less the same. In 4H-SiC the two ionization energies are  $E_c$ - $E_h$  = 52 meV,  $E_c$  -  $E_k$  = 92 meV where  $E_c$  denotes the conduction band minimum and  $E_h$  ( $E_k$ ) the energy level of the cubic (hexagonal) *N* donor. Then from equation (2.8) we have that

$$\frac{N_d^+}{N_d} = \frac{1}{2} \times \left(\frac{1}{1 + 2 \times \frac{n}{N_c} \exp\left(\frac{0.052}{k_B T / q}\right)} + \frac{1}{1 + 2 \times \frac{n}{N_c} \exp\left(\frac{0.092}{k_B T / q}\right)}\right) \quad (2.10)$$

$$N_{c} = 2 * \left(\frac{2\pi k_{B} T m_{n}^{*}}{h^{2}}\right)^{3/2} \quad (2.11)$$

Where  $N_c$  is the averaged density of states,  $m_n^*$  is the effective mass for the conduction bands, *h* is Planck's constant, and  $k_B$  is Boltzman's constant. For 4H-SiC,  $m_n^*$  equals 0.76m<sub>o</sub>. The incomplete ionization of n-type 4H SiC doped with Nitrogen is plotted in Fig.2.1. The results show that the incomplete ionization will not be a problem until the doping concentration is up to  $1 \times 10^{17}$  cm<sup>-3</sup>.

Fig.2.1 The incomplete Ionization of n-type 4H SiC doped with Nitrogen

# 2.2 Current Continuity equations

The change rate of electrons within a one-dimensional distance dx can be modeled as [21]

$$\frac{\partial n}{\partial t}Adx = \left(\frac{\vec{J}_n}{-q} - \frac{\vec{J}_n(x+dx)}{-q}\right)A + (G_n - R_n)Adx \quad (2.11)$$

Where *A* is the cross section area,  $G_n$  and  $R_n$  represent the generation and recombination rates of electrons within dx,  $J_n$  is the electron current density.

Equation  $\left(\frac{\vec{J}_n}{-q} - \frac{\vec{J}_n(x+dx)}{-q}\right)$  stands for the net increase of electron within dx. The

second term in equation  $J_n(x+dx)$  can be expanded by a Taylor series:

$$\vec{J}_n(x+dx) = \vec{J}_n(x) + \frac{\partial \vec{J}_n}{\partial x}dx + \cdots$$

(2.12)

Then equation (2.11) can be simplified as:

$$\frac{\partial n}{\partial t} = \frac{1}{q} \frac{\partial J_n}{\partial x} + (G_n - R_n) \quad (2.13)$$

The analogous equation for holes is given by

$$\frac{\partial p}{\partial t} = -\frac{1}{q} \frac{\partial \vec{J}_p}{\partial x} + (G_p - R_p) \quad (2.14)$$

Equations (2.13) and (2.14) are called current continuity equations. The current continuity equations state that the time varying charge density is equal to the

net increase rate of carrier densities flow into the space plus the net carrier generation within the space.

### 2.3 Drift-diffusion current equations

# **Drift Current**

In the drift-diffusion model, the current composes of two components: drift current and diffusion current. The current due to carrier drift under the applied field is called drift current. This drift electron current density can be found by summing the product of the charge of each electron times its drift velocity over all the carriers n within per unit volume:

$$\vec{J}_{n-drift} = -qn\vec{v}_n \quad (2.15)$$

Where  $\vec{v}_n$  is the average electron drift velocity due to an applied electrical field. The drift velocity is related to electron mobility and the applied electric field  $\vec{E}$  as:

$$\vec{v}_n = -\mu_n \vec{E} \quad (2.16)$$

Then we have

$$\vec{J}_{n-drift} = qn\mu_n \vec{E} \quad (2.17)$$

# **Diffusion Current**

The carriers tend to mover from a region of high concentration to a region of low concentration. The current associated with this diffusion process in semiconductor is called diffusion current. Again the electron diffusion current in a one-dimensional distance dx can be expressed as:

$$\vec{J}_{n-diff} = -qD_n(n(x) - n(x + dx))$$

(2.18)

With a similar Taylor series expansion and first order approximation to (2.12), we have:

$$\vec{J}_{n-diff} = qD_n \frac{dn}{dx} \quad (2.19)$$

Where  $D_n$  is the electron diffusion coefficient and can be can be related to the electron mobility using the Einstein relation:

$$\frac{D_n}{\mu_n} = \frac{k_B T}{q} \quad (2.20)$$

# **2.4 The Drift-Diffusion Model**

The total electron transport current can be simply obtained by adding up the drift current and the diffusion current:

$$\vec{J}_n = \vec{J}_{n-drift} + \vec{J}_{n-diff} = qn\mu_n \vec{E} + qD_n \frac{dn}{dx} \quad (2.21)$$

A similar total hole transport current can be derived as:

$$\vec{J}_p = \vec{J}_{p-drift} + \vec{J}_{p-diff} = qn\mu_p \vec{E} + qD_p \frac{dp}{dx} \quad (2.22)$$

Where  $D_p$  is the hole diffusion coefficient and has a similar Einstein relation as equation (2.20).

Replacing the electric field *E* in equations (2.21) and (2.22) based on the relationship  $E = -d\phi/dx$ , the drift-diffusion model is expressed as:

$$\vec{\nabla}^{2}\phi - \frac{q}{\varepsilon}\left(n - p + N_{a}^{-} - N_{d}^{+}\right) = 0 \quad (2.1)$$

$$\frac{\partial n}{\partial t} = \frac{1}{q}\frac{\partial \vec{J}_{n}}{\partial x} + \left(G_{n} - R_{n}\right) \quad (2.13)$$

$$\frac{\partial p}{\partial t} = -\frac{1}{q}\frac{\partial \vec{J}_{p}}{\partial x} + \left(G_{p} - R_{p}\right) \quad (2.14)$$

Where current densities  $\vec{J}_n$  and  $\vec{J}_p$  are defined as

$$\vec{J}_n = -qn\mu_n \frac{\partial \phi}{\partial x} + qD_n \frac{dn}{dx} \quad (2.21)$$

$$\vec{J}_{p} = -qn\mu_{p}\frac{\partial\phi}{\partial x} - qD_{p}\frac{dp}{dx} \quad (2.22)$$

It is apparent that recombination, generation, and mobility play important roles in the model of drift-diffusion. The models used to describe these physical phenomena will be introduced in the following.

# **Generation and Recombination**

### **Shockley-Read-Hall Recombination:**

There are many recombination centers in semiconductor bulk that determine the lifetime of carriers. They have localized electrons states with energies within the forbidden gap, typically close to the intrinsic Fermi level. The theory for recombination through these localized centers is called *Shockley-Read-Hall* theory [4]:

$$R^{SRH} = \frac{np - n_i^2}{\tau_n \left[ p + n_i \exp\left(\frac{E_i - E_t}{kT}\right) \right] + \tau_p \left[ n + n_i \exp\left(\frac{E_i - E_t}{kT}\right) \right]} \quad (2.23)$$

$$\tau_n = \frac{1}{N_t v_{th} \sigma_n} \quad (2.24)$$

$$\tau_p = \frac{1}{N_t v_{th} \sigma_p} \quad (2.25)$$

Where  $N_t$  is the density of state,  $v_{th}$  is the electron thermal velocity,  $\sigma_n$  is called the capture cross section describing the effectiveness of the localized state in capturing an

electron,  $\sigma_p$  is the capture cross section for holes.  $\tau_n$  and  $\tau_p$  are the lifetime of electrons and holes, respectively.

Since most elective recombination centers are close to the intrinsic Fermi level, equation (2.23) can be simplified as:

$$R^{SRH} = \frac{np - n_i^2}{\tau_n(n + n_i) + \tau_n(p + n_i)} \quad (2.26)$$

The lifetimes  $\tau_n$  and  $\tau_p$  as a function of doping and temperature are given by the following equations [22]:

$$\tau_{n,p} = \frac{\tau_{no,po} (\frac{T}{300})^{\gamma_{n,p}}}{1 + (\frac{C}{C_{n,p}^{ref}})^{\alpha_{n,p}}} \quad (2.27)$$

Where  $\tau_{no}$  and  $\tau_{po}$  are the intrinsic minority carrier lifetimes,  $\gamma_{n,p}$ ,  $\alpha_{n,p}$  and  $c_n^{ref}$  are empirical modeling parameters

### **Auger Recombination**

Auger recombination describes the direct recombination process of electrons and holes [21]. When excess carriers recombine in a region that has a high doping concentration the probability of direct recombination between holes and electrons may not be negligible compared to the probability of recombination through traps (SHR recombination). This direct recombination process is called Auger recombination. In Auger recombination, three free carriers interact, either two electrons and a hole, or two holes and an electron. Two of the carriers recombine and the third carries away the momentum of the oncoming carriers and the energy released by the recombination event. Because of the need for the simultaneous interaction of three carries we can expect that Auger recombination is highly unlikely expect in heavily doped material. An expression for the Auger recombination rate  $R^4$  is

$$R^{A} = \Gamma_{n} n \left( pn - n_{i}^{2} \right) + \Gamma_{n} p \left( pn - n_{i}^{2} \right) \quad (2.28)$$

Where  $\Gamma_n$  is the coefficient representing interactions in which the remaining carrier is an electron, and  $\Gamma_p$  is the coefficient representing interactions in which the remaining carrier is a hole. Extracted and derived values for the recombination models in SiC are found in [6].

#### **Impact Ionization Generation**

Some carriers in the devices may reach very high transport speeds. These high-speed particles are also high in energy, and this energy may contribute to the generation of excess electron-hole pairs. The generation occurs when the high energy particle collides with a bonded particle resulting in one additional free electron and one additional free hole. This type of generation is referred to as avalanche or impact ionization generation. The impact ionization model can be expressed by [22]

$$G^{II} = \alpha_{n,ii} \frac{\vec{J}_n}{q} + \alpha_{p,ii} \frac{\vec{J}_p}{q} \quad (2.29)$$

Where  $\alpha_{n,ii}$  and  $\alpha_{p,ii}$  are the electron and hole impact ionization coefficients. As described in [22][24,25], the ionization coefficients for 4H-SiC can be expressed in terms of the local electric field according to

$$\alpha_{n,ii} = 1.66 \times 10^6 \exp\left[-\left(\frac{2.2 \times 10^7}{E_{n,||}}\right)\right]$$

(2.30)

$$\alpha_{p,ii} = 5.86 \times 10^6 \exp\left[-\left(\frac{1.4 \times 10^7}{E_{p,\parallel}}\right)\right] \quad ((2.31)$$

Where  $E_{n,||}$  and  $E_{p,||}$  are the electric field components in the direction of current flow.

# **Mobility Model**

The Caughey-Thomas model is used for 4H-SiC low-field mobility modeling [22]:

$$\mu_{n,p}^{LF}(T,C) = \mu_{n,p}^{\min} + \frac{\mu_{n,p}^{\delta}(\frac{T}{300})^{\alpha_{n,p}} - \mu_{n,p}^{\min}}{1 + (\frac{C}{C_{n,p}^{ref}})^{\gamma_{n,p}}} \quad (2.32)$$

Where  $\alpha$ ,  $\gamma$  and  $C^{ref}$  are model parameters and *C* is the net ionization doping. The high field mobility model used is [22]:

$$\mu_{n,p}^{HF}(T,C) = \frac{\mu_{n,p}^{LF}}{\left(1 + \left(\frac{\mu_{n,p}^{LF} |\vec{E}|}{\upsilon_{n,p}^{sat}}\right)^{\beta_{n,p}}\right)^{1/\beta_{n,p}}} \quad (2.33)$$

# **2.5 Boundary Conditions**

The boundary conditions associated with the drift-diffusion model on silicon carbide power device modeling are needed to be addressed here.

# **Ohmic Contacts**

Ohmic contact is defined as the contact itself offers negligible resistance to current flow when compared to the bulk [21]. That means that when voltage is applied across a device with ohmic contacts, the voltage dropped across the ohmic contact is negligible compared to voltage drops elsewhere in the device. Thus no power is dissipated in the contact. An importance and useful consequence of this property is that all free-carrier densities at an ohmic contact are unchanged by current flow. It is well-known that the material potentials of a doped semiconductor in thermal equilibrium can be modeled by the following equations:

$$\phi_n = V_T \ln \frac{N_d^+}{n_i} \quad (2.34)$$

for n-type semiconductor and

$$\phi_p = V_T \ln \frac{N_a^-}{n_i} \quad (2.35)$$

for p-type semiconductor.

Where  $n_i$  is the intrinsic carrier concentration,  $V_T$  is the thermal voltage, and  $N_d^+$  and  $N_a^-$  are the ionized (activated) donor and acceptor concentrations respectively. There is no voltage drop across the ohmic contact, so the boundary condition for electrostatic potential at the contact-semiconductor boundary is equal to

$$\phi_n' = V_a + \phi_n \quad (2.36)$$

for ohmic contacts at n-type material side and

$$\phi_p' = V_a + \phi_p \quad (2.37)$$

for ohmic contacts at p-type material side.

Because of the no-power-loss property of the ideal ohmic contact, thermal equilibrium, and therefore charge neutrality, can be assumed at the contact-semiconductor boundary. The total charge density  $\rho$  is given by

$$\rho = q(p - n + C) = 0$$

(2.38)

Where  $C = N_d^+$  and  $N_a^-$  which is the net ionization doping concentration. Since it is under thermal equilibrium conditions, the mass action law  $np = n_i^2$  holds. Then we have that:

$$n = \frac{C}{2} + \frac{\sqrt{D^2 + 4n_i^2}}{2}, p = \frac{n_i^2}{n} \quad (2.39)$$

for n-type material and

$$p = -\frac{C}{2} + \frac{\sqrt{D^2 + 4n_i^2}}{2}, n = \frac{n_i^2}{p} \quad (2.40)$$

for p-type material.

# Chapter 3: Characterizations and failure mechanism investigation for SiC Schottky Diodes

As discussed in Chapter 1, Schottky diodes can provide the benefits of very low forward voltage drop and much quick switching time as a majority carrier device. These features make Schottky diodes very good switching devices used in power supplies. With the properties of high breakdown voltage and high thermal conductivity, SiC Schottky diodes can offer extra advantages over traditional Si and GaAs Schottky diodes. For Schottky diode the maximum blocking voltage can be simply described by equation:

$$V_{\rm max} = \frac{E_c W}{2} \quad (3.1)$$

Where E is the critical breakdown electric field of the material and W is the depletion width of the Schottky diode which is determined by

$$W = \sqrt{\frac{2\varepsilon_s(V_{bi} - V_a)}{qN_d}} \quad (3.2)$$

Where  $\varepsilon_s$  is the dielectric constant of the material,  $V_{bi}$  is the build-in potential of the diode,  $V_a$  is the applied reverse bias, and  $N_d$  is the doping density of the material. The critical electric field  $E_c$  for 4H SiC, Si and GaAs are  $2.2 \times 10^6$  (V/cm),  $2.5 \times 10^6$  (V/cm),

and  $3 \times 10^5$  (V/cm) respectively. The calculated results for ideal results for ideal breakdown voltage of SiC and GaAs and Si Schottky diode are plotted in Fig.3.1 which shows the advantages of SiC when used in power devices.

Fig.3. 1 Comparison of the ideal breakdown voltages of SiC, GaAs and Si devices (a) for different doping levels (b) for different the blocking layer thickness

The results in Fig.3.1 (b) showed that SiC Schottky diodes can be made with a much smaller physical size compared to Si and GaAs diodes for a same block voltage requirement. This advantage is also applicable to all other SiC power devices. In this chapter the experimental and simulation of 4H SiC Schottky diode are introduced first in section 3.2. The correctness of the drift-diffusion model with the associated SiC physical models and parameters is verified by agreement between the experimental and simulation results. The failure mechanism investigation for non-catastrophic failures happened in Schottky diodes is conducted in the following section.

# 3.1 Numerical Simulation of SiC Schottky Diodes

### **3.1.1 Introduction**

With material progress and the development of high quality single crystal 4H-SiC wafers, high voltage 4H-SiC Schottky diodes have been fabricated in [26]~[29]. To get more reliable and quantitative information about the 4H-SiC Schottky diodes, detailed device characterizations are needed.

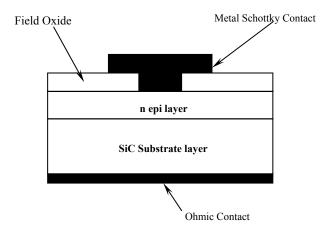

Experimental and simulation results on n-type Ti/4H-SiC Schottky diodes conducted in this work. I-V measurements for 4H-SiC Schottky diodes at different temperatures were first performed using an ITS8000 testing system. This system allows the I-V characteristic to be recorded from 273K-550K. The electrical characteristics were then simulated based on the drift-diffusion model. The simulated device structure is presented in Fig.3.3. It includes a 4 $\mu$ m epitaxial n-drift layer and a 1 $\mu$ m epitaxial n<sup>+</sup> layer. The two layers are uniformly doped by 1×10<sup>15</sup> cm<sup>3</sup> and 1×10<sup>18</sup> cm<sup>3</sup> respectively.

Fig.3. 2 The schematic cross-section of the active layers of SiC Schottky diode

### **3.1.2 Physical Models of SiC Schottky Diodes**

To simulate the characteristics of 4H-SiC Schottky diodes under different temperatures, the carrier mobility, and intrinsic concentration, generation and recombination models, including their temperature dependence were used in the driftdiffusion model with proper boundary conditions.

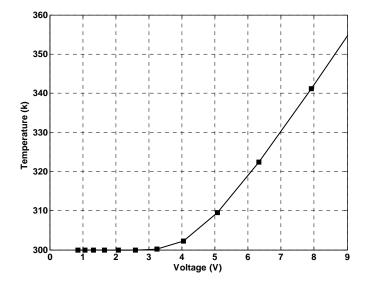

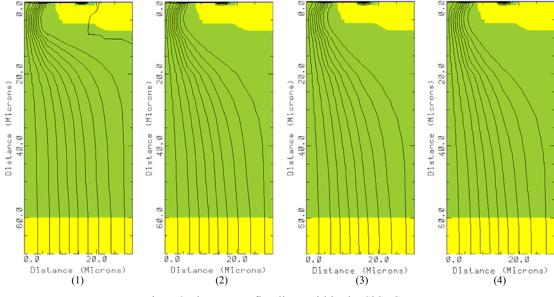

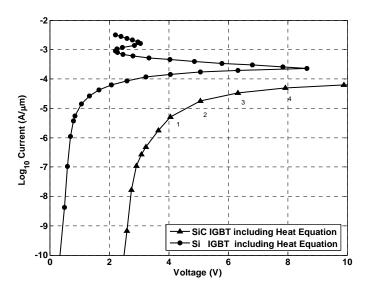

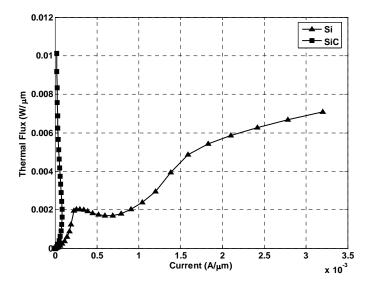

### **Drift-Diffusion Model**