## ABSTRACT

| Title of Dissertation:    | DEFECTS AND STRAIN IN SILICON<br>METAL-OXIDE-SEMICONDUCTOR (MOS)<br>QUANTUM DOTS |

|---------------------------|----------------------------------------------------------------------------------|

|                           | Ryan Matthew Stein<br>Doctor of Philosophy, 2021                                 |

| Dissertation Directed by: | Professor John Cumings, Department of<br>Materials Science and Engineering       |

|                           | Dr. Michael D. Stewart, Jr.<br>National Institute of Standards and Technology    |

Silicon-based single electron devices (SEDs), fabricated using gate-defined quantum dots are some of the world's most sensitive devices. Local charge fluctuations and disorder caused by defects in the oxide or substrate impurities can profoundly affect device operation. While most workers consider the above when fabricating SEDs in the Si MOS system, they do not typically consider strain. The fabrication process and gate material deposition usually results in a thin film under a significant amount of stress, which locally modulates the silicon conduction band. Additionally, the coefficient of thermal expansion mismatch between typical MOS gate materials, such as aluminum, and the underlying silicon substrate also produces strain, which further modifies the conduction band. For quantum dot devices measured at cryogenic temperatures, this local modification of the conduction band is strong enough to lead to the formation of unintentional quantum dots and to affect the tunnel coupling between dots. To realize the potential of quantum devices, gate-induced strain must be understood so as to be mitigated or exploited.

In this work, we investigate the role of gate-induced strain in quantum dot devices by comparing measurements of the 4-terminal I(V) characteristics of tunnel barrier devices at cryogenic temperatures. From this, we demonstrate a new electrical measurement of gate-induced strain using tunnel junctions (TJs). Our COMSOL simulations of these devices show that the gate-induced strain will modify the barrier height, depending on both the magnitude and sign of inhomogeneous stress. We fabricate MOS devices on bulk silicon wafers with a variety of gate electrodes, including aluminum and titanium. By comparing nearly identical tunnel junction devices fabricated with two different gate materials, Al and Ti, we measure a relative strain difference consistent with our experimentally measured coefficients of thermal expansion. Our results show that the commonly used bulk parameters for simulating strain effects in silicon QDs do not work well in practice.

Additionally, we present measurements of oxide defect densities (fixed charge and interface trap density) as a function of forming gas anneal temperature for three different gate metals: Al, Ti/Pd, and Ti/Pt. We also investigate the effect of these anneals on the mechanical properties of the gate material, such as the intrinsic film stress and coefficient of thermal expansion. The combination of our charge defect and mechanical measurements show that there is no way to simultaneously minimize the effects of both using the forming gas anneal. This result puts tension on designing fabrication processes for MOS QDs where one must choose between setting the anneal such that defects are minimized or the strain-induced modulation of the conduction band is minimized. Additionally, we find that our measured values of the coefficient of thermal expansion deviate significantly from the expected bulk values. This suggests that the common material parameters used to simulate gateinduced strain in MOS QD are not accurate.

Building towards the goal of controlling non-idealities in silicon MOS QDs requires methods of measuring strain under relevant conditions while also finding ways to adjust processing to minimize the impact of other non-idealities. The work in thesis represents a significant step towards that goal. The devices presented easily lend themselves to future work exploring deposition parameters and anneals to manipulate inhomogeneous strain. Our method for measuring relative strain satisfies the sensitivity, spatial resolution and low-temperature requirements relevant for MOS QDs. Moreover, the fabrication and measurements are similar to those for QDs so that this method is directly relevant for QD devices. Our data provide an important step forward in assessing gate-induced strain in QD devices in-situ while highlighting the need for further experimental work and a greater theoretical understanding of the electrostatics and strain behavior.

# DEFECTS AND STRAIN IN SILICON METAL-OXIDE-SEMICONDUCTOR (MOS) QUANTUM DOTS

by

Ryan Matthew Stein

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2021

Advisory Committee: Professor John Cumings, Chair/Advisor Dr. Michael D. Stewart Jr., Co-Advisor Professor Ichiro Takeuchi Professor Lourdes G. Salamanca-Riba Professor Martin C. Peckerar

© Copyright by Ryan Matthew Stein 2021

# Foreword

Chapter 4 is partially reproduced from: "The effect of strain on tunnel barrier height in silicon quantum devices", Journal of Applied Physics, 128(2):024303, July 2020. with the permission of AIP publishing. (I am the first author of this paper).

Chapter 5 is partially reproduced from: "Alternatives to aluminum gates for silicon quantum devices: defects and strain" currently under review by the Journal of Applied Physics. (I am the first author of this paper).

### Acknowledgments

During last six years as a PhD student working at NIST, I have had the privilege interacting with many people around me who have enabled me to thrive during my PhD career. First, I would like to thank my advisor at NIST, Dr. Michael Stewart, Jr., for giving me an invaluable opportunity to work at NIST and guiding me through my research the last six years. He has always made himself available when I needed help or advice even in the probably too frequent occurrences where I wandered into his office to discuss some random idea or problem I had. I would also like to thank Professor John Cumings, my advisor at College Park, for his helpful guidance during my PhD career.

I would also like to thank all of the group members I have crossed paths with over the last six years. I am grateful to Roy Murray and Binhui Hu, both of whom were post-docs early on during my time at NIST, for their help when I was first learning how to fabricate devices in the cleanroom. I would also like to thank the PIs at NIST: Dr. Neil Zimmerman, Dr. Josh Pomeroy, and Dr. Garnett Bryant, for providing feedback and support on my research particularly during our group meetings and journal clubs. I would also like the other group members whom I have worked closely with during my time at NIST: Dr. Aruna Ramanayaka, Zac Barcikowski, Yanxue Hong, Dr. Ke Tang, Dr. Hyun Soo Kim, and Dr. Kevin Dwyer. Finally, I would to thank all of my committee members: Professor Ichiro Takeuchi, Professor Lourdes G. Salamanca-Riba and Professor Martin Peckerar for reviewing and helping me improve this dissertation.

# Table of Contents

| Table of Contents       vii         List of Tables       viii         List of Figures       is         Chapter 1: Introduction       1         1.0.1 Motivation       2         1.0.2 Quantum computing       2         1.0.3 Quantum current standard       5         1.1 Quantum dots in Silicon       7         1.1.1 Why silicon?       7         1.1.2 Material systems       9         1.2 Physics of Quantum Dots (QDs)       11         1.2.1 Coulomb Blockade       11         1.2.2 Confinement       12         1.2.3 Transport characteristics       16         1.3 Non-idealities in silicon quantum dots       18         1.3.1 Charge defects       21         1.3.2 Inhomogenous strain       23         1.3.3 Materials considerations       26         1.4 Outline of thesis       27         Chapter 2: Stress and strain in the silicon MOS system       31         2.1 Overview of general stress and strain       33         2.1.1 Strain and displacement       33         2.1.2 Stress       36         2.1.3 Hooke's Law       38         2.1.4 Simple analytical example       44         2.2 Strain and the silicon band structure       45 | Forewor    | 1                                                                                                                                                                                                                                                                                                                | ii                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| List of Tables       vii         List of Figures       is         Chapter 1: Introduction       1         1.0.1 Motivation       2         1.0.2 Quantum computing       2         1.0.3 Quantum current standard       5         1.1 Quantum dots in Silicon       7         1.1.1 Why silicon?       7         1.1.2 Material systems       7         1.1.2 Material systems       7         1.2 Physics of Quantum Dots (QDs)       11         1.2.1 Coulomb Blockade       11         1.2.3 Transport characteristics       16         1.3 Non-idealities in silicon quantum dots       18         1.3.1 Charge defects       21         1.3.2 Inhomogenous strain       22         1.3.3 Materials considerations       26         1.4 Outline of thesis       27         Chapter 2: Stress and strain in the silicon MOS system       31         2.1 Overview of general stress and strain       33         2.1.1 Strain and displacement       33         2.1.2 Stress       36         2.1.3 Hooke's Law       36         2.1.4 Simple analytical example       44         2.3 Thin film stress measurements       52                                          | Acknow     | edgements                                                                                                                                                                                                                                                                                                        | iii                                                                           |

| List of Figures       is         Chapter 1: Introduction       1         1.0.1 Motivation       2         1.0.2 Quantum computing       2         1.0.3 Quantum current standard       5         1.1 Quantum dots in Silicon       7         1.1.1 Why silicon?       7         1.1.2 Material systems       6         1.2 Physics of Quantum Dots (QDs)       11         1.2.1 Coulomb Blockade       11         1.2.2 Confinement       12         1.2.3 Transport characteristics       16         1.3 Non-idealities in silicon quantum dots       18         1.3.1 Charge defects       21         1.3.2 Inhomogenous strain       22         1.3.3 Materials considerations       26         1.4 Outline of thesis       27         Chapter 2: Stress and strain in the silicon MOS system       31         2.1 Overview of general stress and strain       33         2.1.1 Strain and displacement       33         2.1.2 Stress       36         2.1.3 Hooke's Law       36         2.1.4 Simple analytical example       45         2.2 Strain and the silicon band structure       48         2.3 Thin film stress measurements       52                    | Table of   | Contents                                                                                                                                                                                                                                                                                                         | v                                                                             |

| Chapter 1:       Introduction       1         1.0.1       Motivation       2         1.0.2       Quantum computing       2         1.0.3       Quantum current standard       5         1.1       Quantum dots in Silicon       7         1.1.1       Why silicon?       7         1.1.2       Material systems       5         1.2       Physics of Quantum Dots (QDs)       11         1.2.1       Coulomb Blockade       11         1.2.2       Confinement       12         1.2.3       Transport characteristics       16         1.3       Non-idealities in silicon quantum dots       18         1.3.1       Charge defects       21         1.3.2       Inhomogenous strain       23         1.3       Materials considerations       26         1.4       Outline of thesis       27         Chapter 2:       Stress and strain in the silicon MOS system       31         2.1       Stress       36         2.1.1       Strain and displacement       33         2.1.2       Stress       36         2.1.3       Hooke's Law       36         2.1.4       Simple analytical example       45                                                                | List of 7  | ables                                                                                                                                                                                                                                                                                                            | viii                                                                          |

| 1.0.1       Motivation       2         1.0.2       Quantum computing       2         1.0.3       Quantum current standard       5         1.1       Quantum dots in Silicon       7         1.1.1       Why silicon?       7         1.1.2       Material systems       5         1.2       Physics of Quantum Dots (QDs)       11         1.2.1       Coulomb Blockade       11         1.2.2       Confinement       12         1.2.3       Transport characteristics       16         1.3       Non-idealities in silicon quantum dots       18         1.3.1       Charge defects       21         1.3.2       Inhomogenous strain       26         1.4       Outline of thesis       27         Chapter 2:       Stress and strain in the silicon MOS system       31         2.1       Overview of general stress and strain       33         2.1.1       Strain and displacement       33         2.1.2       Stress       36         2.1.3       Hooke's Law       38         2.1.4       Simple analytical example       45         2.2       Strain and the silicon band structure       48         2.3       Th                                             | List of H  | igures                                                                                                                                                                                                                                                                                                           | ix                                                                            |

| 1.4       Outline of thesis       27         Chapter 2:       Stress and strain in the silicon MOS system       31         2.1       Overview of general stress and strain       33         2.1.1       Strain and displacement       33         2.1.2       Stress       36         2.1.3       Hooke's Law       36         2.1.4       Simple analytical example       45         2.2       Strain and the silicon band structure       48         2.3       Thin film stress measurements       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.1<br>1.2 | 1.0.1Motivation1.0.2Quantum computing1.0.3Quantum current standardQuantum dots in Silicon1.1.1Why silicon?1.1.2Material systemsPhysics of Quantum Dots (QDs)1.2.1Coulomb Blockade1.2.2Confinement1.2.3Transport characteristicsNon-idealities in silicon quantum dots1.3.1Charge defects1.3.2Inhomogenous strain | $ \begin{array}{c} 1\\2\\5\\7\\9\\11\\11\\12\\16\\18\\21\\23\\26\end{array} $ |

| 2.1       Overview of general stress and strain       33         2.1.1       Strain and displacement       33         2.1.2       Stress       36         2.1.3       Hooke's Law       36         2.1.4       Simple analytical example       45         2.2       Strain and the silicon band structure       48         2.1       Conduction band       48         2.3       Thin film stress measurements       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.4        |                                                                                                                                                                                                                                                                                                                  | $\frac{20}{27}$                                                               |

| 2.2.1Conduction band482.3Thin film stress measurements52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.1        | Overview of general stress and strain                                                                                                                                                                                                                                                                            | 31<br>33<br>33<br>36<br>38<br>45                                              |

| 2.4 Simulations in COMSOL 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 2.2.1 Conduction band                                                                                                                                                                                                                                                                                            | 48<br>48<br>52<br>57                                                          |

|              | 2.4.1  | Bimetallic strip in COMSOL                                                | . 61  |

|--------------|--------|---------------------------------------------------------------------------|-------|

| Chapte       | r 3: C | Charge Defects in the MOS system                                          | 65    |

| 3.1          |        | luction to the MOS system                                                 |       |

|              | 3.1.1  | MOS physics                                                               |       |

|              | 3.1.2  | Interface trap density, $D_{it}$                                          |       |

|              | 3.1.3  | Mobile Ion Charge, $Q_m$                                                  |       |

|              | 3.1.4  | Trapped Oxide Charge, $Q_{ot}$                                            |       |

|              | 3.1.5  | Fixed Oxide Charge, $Q_f$                                                 | . 75  |

| 3.2          | Capac  | titance-Voltage (CV) measurements                                         |       |

|              | 3.2.1  | Frequency dependence of CV measurements                                   |       |

|              | 3.2.2  | Measurement setup                                                         | . 80  |

|              | 3.2.3  | Measurement of $Q_f$ : Flatband voltage extraction                        | . 82  |

|              | 3.2.4  | Measurement of $D_{it}$ : High Frequency-Quasi-static (HF-QS)             |       |

|              |        | $method  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |       |

|              | 3.2.5  | Measurement of $D_{it}$ : Conductance method                              |       |

|              | 3.2.6  | Converting Gate Voltage to Energy                                         | . 95  |

|              | 3.2.7  | Measurement of $Q_m$ : Triangular voltage sweep (TVS)                     |       |

|              | 3.2.8  | Series Resistance $(R_{series})$ Corrections                              | . 102 |

| Charte       | - 1. N | for successful of staring weight MOC to an all investigates               | 107   |

| Chapte:      |        | Measurement of strain using MOS tunnel junctions                          | 107   |

| 4.1 $4.2$    |        | t of strain on a tunnel junction                                          |       |

| 4.2<br>4.3   |        |                                                                           |       |

| 4.3<br>4.4   |        | r modeling                                                                |       |

| 4.4<br>4.5   |        | ty of electrostatic model                                                 |       |

| 4.6          |        | mination of Relative Strain from Tunnel Junction Measure-                 | . 121 |

| 4.0          |        | with Strain                                                               | 130   |

|              | menus  |                                                                           | . 100 |

| Chapter      | r 5: C | Controlling the defect densities and strain via annealing                 | 134   |

| 5.1          | Metho  | odology                                                                   | . 135 |

| 5.2          | Chang  | ges in defect densities with anneal                                       | . 137 |

| 5.3          | Chang  | ges in intrinsic film stress with anneal                                  | . 146 |

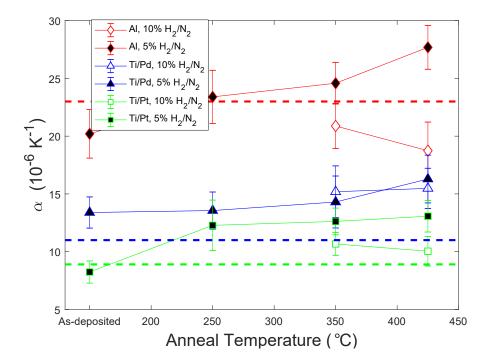

| 5.4          | Chang  | ges in coefficient of thermal expansion with anneal                       | . 147 |

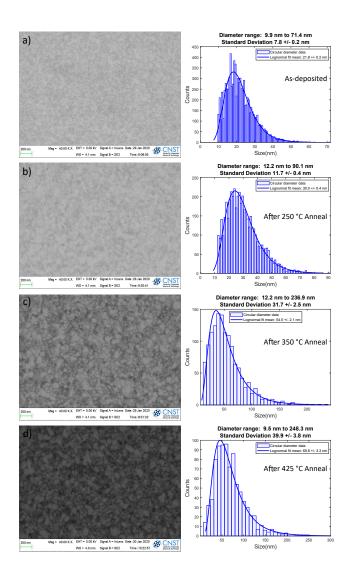

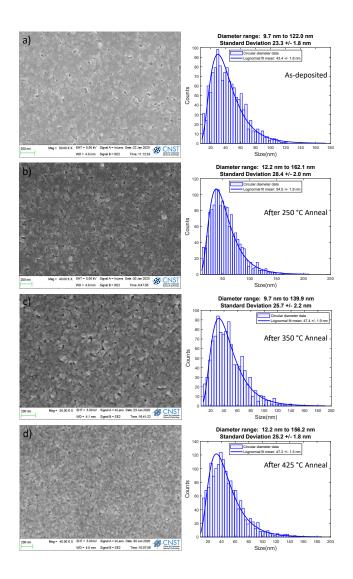

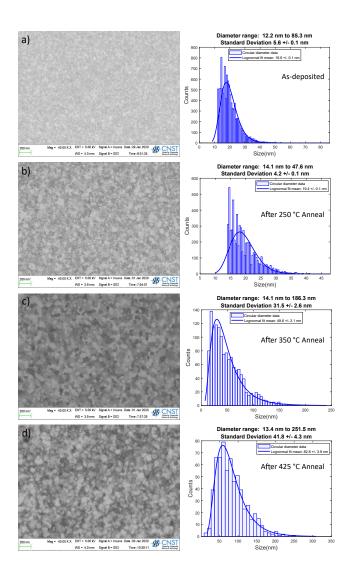

| 5.5          |        | structure anaylsis                                                        |       |

| 5.6          | Simula | ations of strain induced modulation                                       | . 156 |

| 5.7          | Implic | eations for QD design and fabrication                                     | . 158 |

| Chapte       | r G· N | Measurement of asymmetric tunnel junctions                                | 162   |

| 6.1          |        | ations                                                                    |       |

| $6.1 \\ 6.2$ |        | e Fabrication                                                             |       |

| 0.2          | 6.2.1  | Changes to fabrication from previous run                                  |       |

|              | 6.2.1  | Alignment to control gap length                                           |       |

| 6.3          |        | emperature electrical measurements                                        |       |

| 6.4          |        | capacitor measurements                                                    |       |

| 0.4          | 11100  |                                                                           |       |

| 6.5 Discussion of disorder in tunnel junction devices               | . 181 |

|---------------------------------------------------------------------|-------|

| Chapter 7: Conclusions and Future Work                              | 185   |

| 7.1 Conclusions                                                     | . 185 |

| 7.2 Future Work                                                     | . 187 |

| 7.2.1 Additional materials charaterization                          | . 188 |

| 7.2.2 Measurement of strain using magnetoresistance oscillations.   | . 190 |

| 7.2.3 Low temperature measurement of the interface trap density     |       |

| 7.2.4 Simulation improvements                                       | . 194 |

| 7.2.5 Outlook $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |       |

| Appendix A: Tunneling Barrier Fitting                               | 198   |

| A.1 Matlab files for Brinkman-Dynes-Rowell (BDR) model              | . 198 |

| A.1.1 Converting DC sampling for use in fitting                     |       |

| A.1.2 BRD function file                                             |       |

| A.1.3 BRD fitting m-file                                            |       |

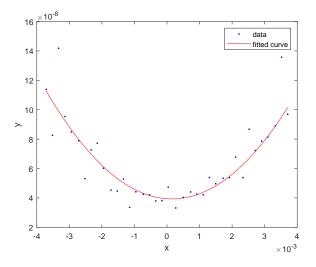

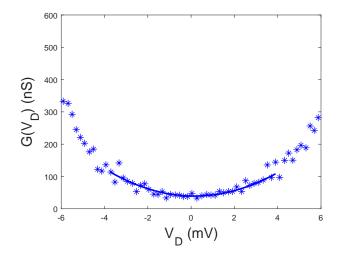

| A.2 Example fits                                                    |       |

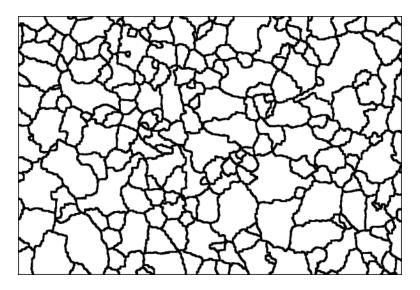

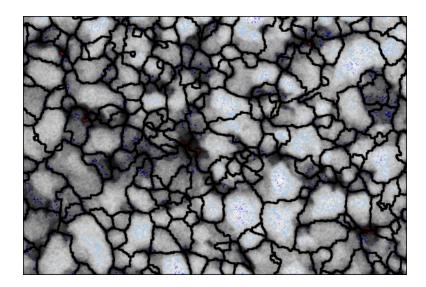

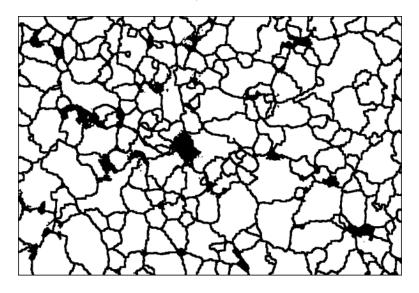

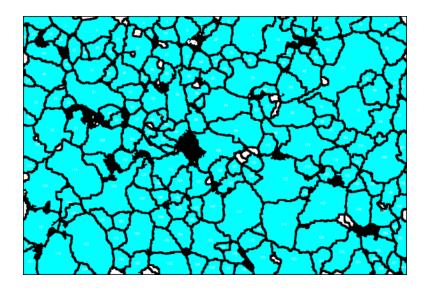

| Appendix B: Image Processing for Grain Size analysis                | 216   |

| B.1 Image processing steps                                          | . 216 |

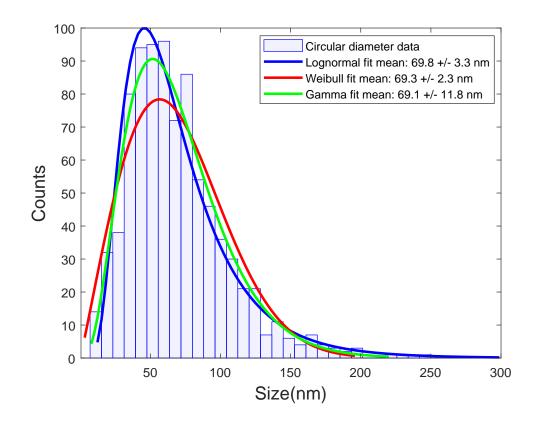

| B.2 Distributions for grain size analysis                           | . 223 |

| B.3 Additional grain size analysis for other films                  |       |

| B.3.1 Summary of average grains sizes from mean of lognormal dis-   |       |

| tribution fits                                                      |       |

| B.3.2 Summary of grains size analysis from standard deviation of    |       |

| lognormal distribution fits                                         | . 226 |

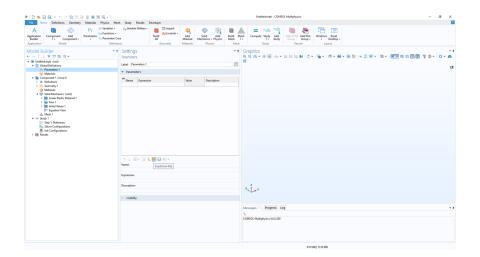

| Appendix C: Setting up COMSOL simulations                           | 228   |

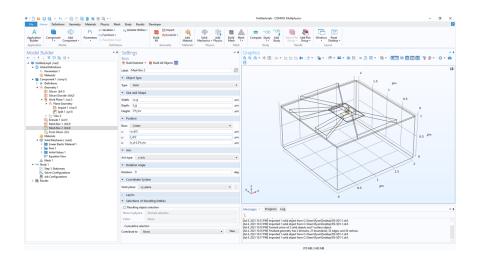

| C.1 Initial model setup                                             | . 228 |

| C.2 Building the model geometry                                     | . 229 |

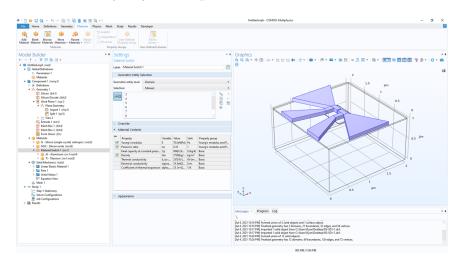

| C.3 Adding materials to the model                                   | . 231 |

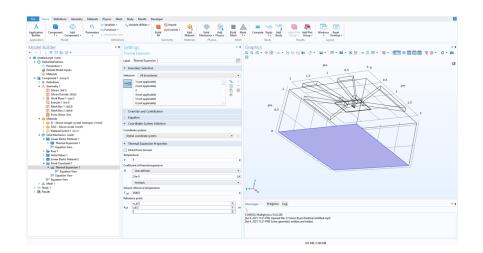

| C.4 Setting up the Solid Mechanic module                            | . 232 |

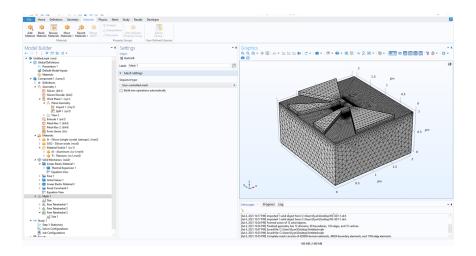

| C.5 Meshing the model                                               | . 234 |

| C.6 Running the computation                                         | . 235 |

| C.7 Plotting 1d linecuts of $\Delta E_c$                            | . 236 |

| Appendix D: AC tunnel junction measurements                         | 237   |

| Bibliography                                                        | 240   |

# List of Tables

| <ul><li>2.1</li><li>2.2</li></ul> | List of room temperature bulk elastic constants for FCC metals com-<br>monly used as MOS gate materials. $c_{ii}$ are in units of GPa and $s_{ii}$<br>are in units of $10^{-12}$ Pa <sup>-1</sup> . From Ref [1]                                                                | . 41           |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.3                               | a silicon (100) wafer where the z direction is aligned along the (001) crystal axis. List of room temperature compliance matrix for orthotropic materials                                                                                                                       | . 42           |

| 2.0                               | used in MOS QDs in units of GPa.                                                                                                                                                                                                                                                | . 42           |

| 2.4                               | List of bulk room temperature coefficients of thermal expansion for commonly used materials in MOS QD                                                                                                                                                                           | . 44           |

| 4.1                               | Comparison of the extracted barrier widths (s), measured lithographic sizes using a SEM, and threshold voltage for the four TJ devices presented in this work.                                                                                                                  | . 127          |

| 4.2                               | Comparison of the capacitive lever arms, $\beta$ , obtained from 2D con-<br>ductance data by performing a linear fit at constant conductance<br>following Ref [2] (column 1) and by calculating the slope of the data<br>sets in Fig. 4.10(a) (column 2).                       |                |

| 5.1                               | List of forming gas anneals commonly used in the fabrication of silicon MOS QDs                                                                                                                                                                                                 | . 136          |

| 6.1                               | Summary of the yield of all tunnel junctions fabricated and measured<br>at cryogenic temperatures in this work. Here, we define the TJ yield<br>as the number of TJ measured that showed little to no evidence of<br>UQDs or disorder divided by the total number of TJ devices | . 182          |

| B.1<br>B.2<br>B.3<br>B.4          | Average grain size summary for Al films from chapter 5 Average grain size summary for Ti/Pd films from chapter 5 Average grain size summary for Ti/Pt films from chapter 5 Lognormal distribution standard deviations for Al films from chapter                                 | . 226<br>. 226 |

| B.5                               | 5                                                                                                                                                                                                                                                                               |                |

| ט.ם                               | ter 5                                                                                                                                                                                                                                                                           |                |

| B.6                               | Lognormal distribution standard deviations for Ti/Pt films from chap-<br>ter 5                                                                                                                                                                                                  | . 227          |

# List of Figures

| 1.1  | Cross section schematic of a silicon MOS two qubit device.                         | 3  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Schematic of silicon MOS QD device used as single electron pump                    | 5  |

| 1.3  | Schematic overview of the material stacks and confining potentials                 |    |

|      | used in silicon based SEDs                                                         | 10 |

| 1.4  | Schematic of the formation of QD in silicon MOS device.                            | 13 |

| 1.5  | Energy diagrams of a quantum dot when there is and is not current                  |    |

|      | through the device.                                                                | 15 |

| 1.6  | Circuit diagram for a single electron device.                                      | 17 |

| 1.7  | Bias spectroscopy of silicon MOS silicon-on-insulator (SOI) SEDs.                  | 19 |

| 1.8  | Contour plot from simulations of the potential modulations in the                  |    |

|      | silicon caused by different random densities of charge defects in the              |    |

|      | oxide of a MOS device.                                                             | 21 |

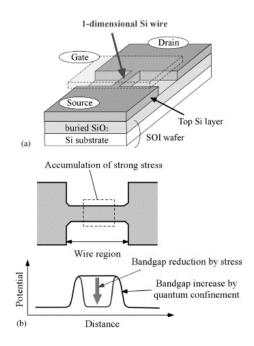

| 1.9  | Schematic of the Pattern Dependent OXidation(PADOX) formation                      |    |

|      | of inhomogeneous strain induced QDs.                                               | 23 |

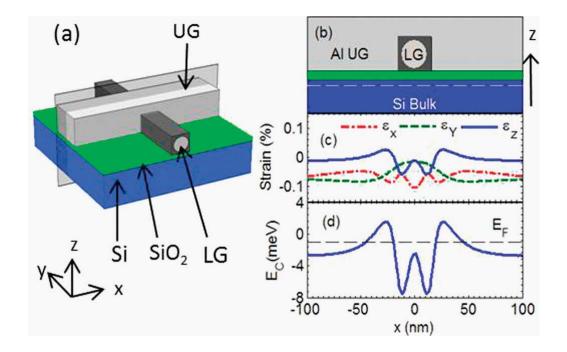

| 1.10 | Modeling and results studying gate-induced strain in COMSOL                        | 25 |

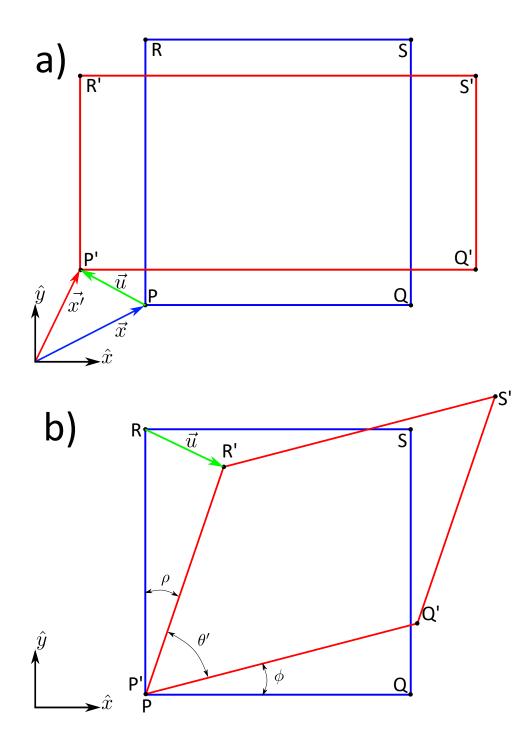

| 2.1  | Schematic showing the deformation of a 2d rectangle                                | 32 |

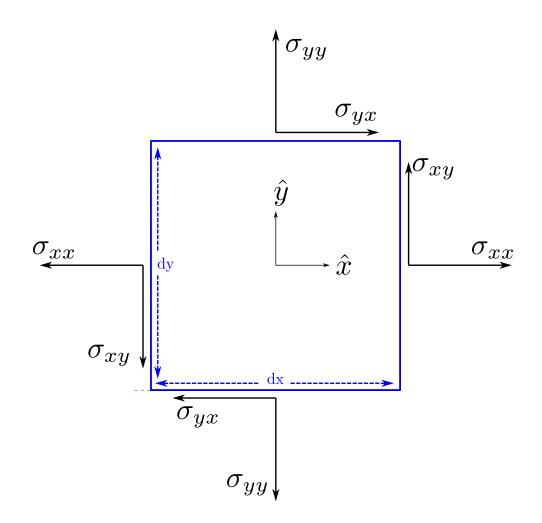

| 2.2  | Schematic showing the stress components for a 2d rectangle                         | 36 |

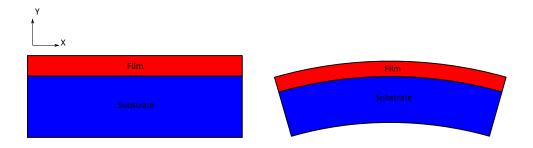

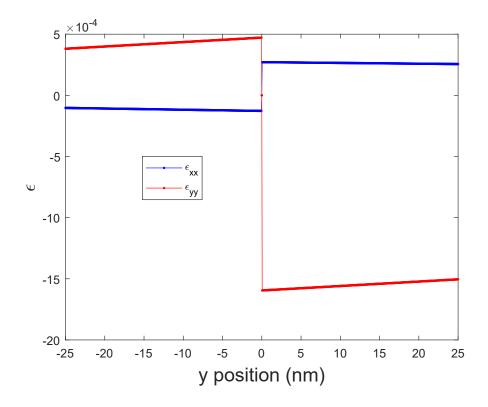

| 2.3  | Schematic of the bimetallic strip.                                                 | 45 |

| 2.4  | Plot of the strain in a SiO <sub>2</sub> -Si bimetallic strip. $\ldots$            | 47 |

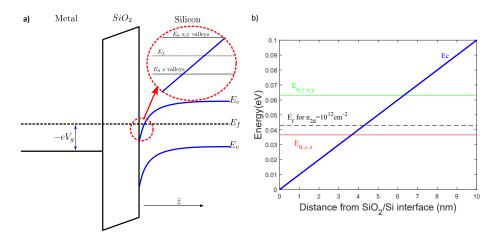

| 2.5  | Band diagram of the MOS system when the silicon is in inversion                    | 49 |

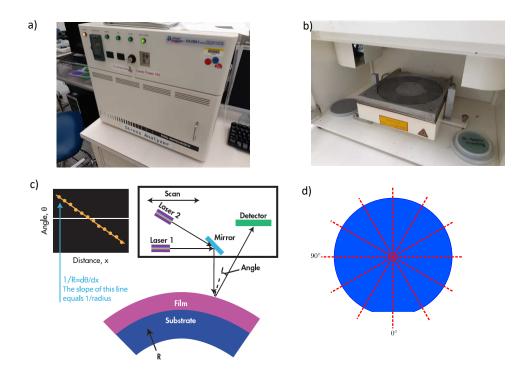

| 2.6  | Overview of the wafer curvature measurements of thin film stress                   | 53 |

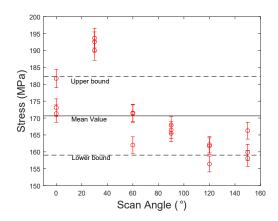

| 2.7  | Angular dependence of stress measurements on 100 nm thick Al film.                 | 54 |

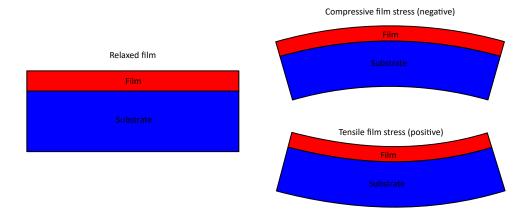

| 2.8  | Diagram of the sign conventions used for wafer curvature measurements.             | 55 |

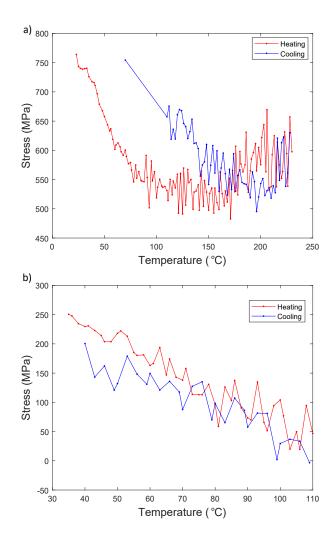

| 2.9  | Plots of measurements of $\alpha_{film}$ by measuring stress as a function of      |    |

|      | temperature for Al films.                                                          | 56 |

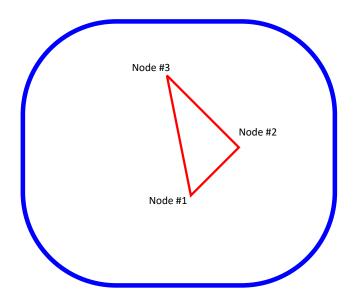

| 2.10 | An arbitrary sized object with a triangular node used to build a FEM               |    |

|      | model                                                                              | 59 |

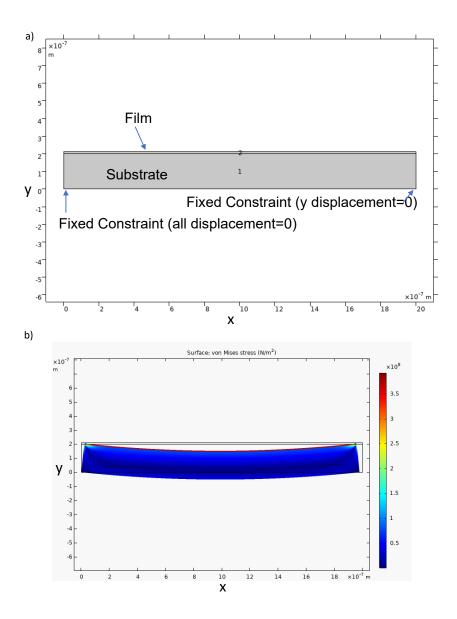

| 2.11 | Diagram of the bimetallic strip model in COMSOL.                                   | 62 |

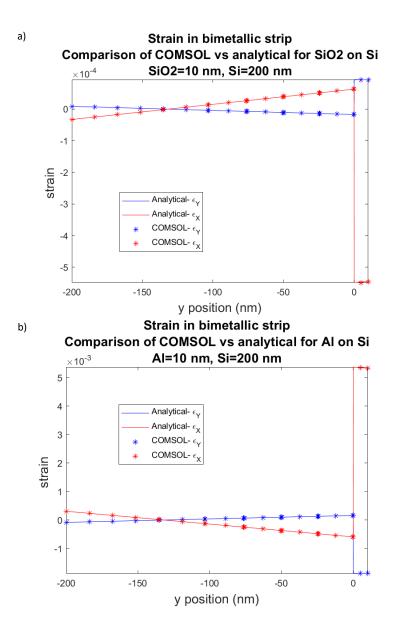

| 2.12 | Comparison of analytical and COMSOL solutions for a bimetallic strip.              | 63 |

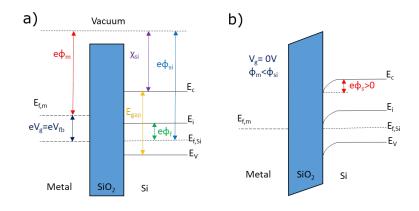

| 3.1  | Band diagrams for various gate voltage configurations for the MOS                  |    |

|      | system where the silicon is a p-type substrate.                                    | 66 |

| 3.2  | Band diagrams for various for space charge regions for p-type Si MOS.              | 67 |

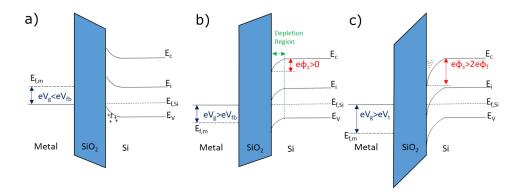

| 3.3  | Plot of the space charge density, $Q_s$ , in the silicon as function of $\phi_s$ . | 68 |

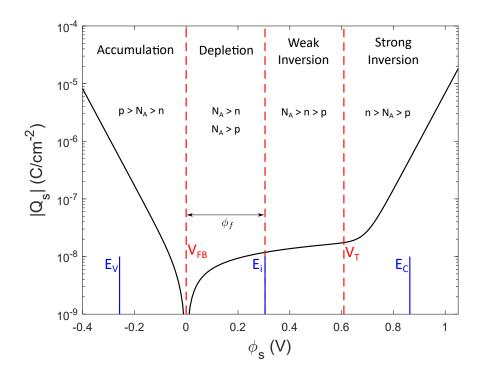

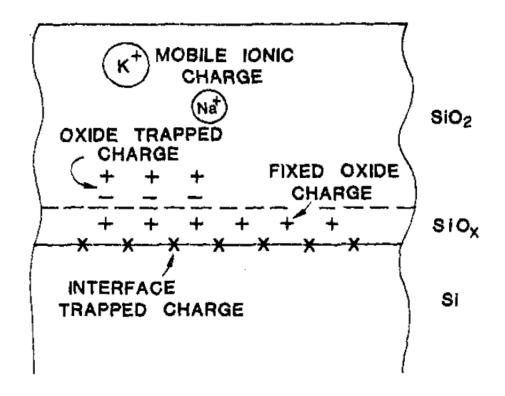

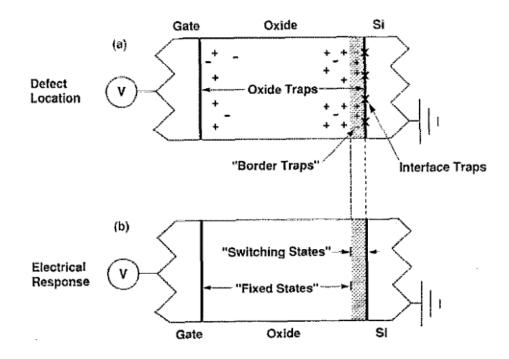

| 3.4         | Schematic of the four main types of charge defects in $SiO_2$ identified                           | 70   |

|-------------|----------------------------------------------------------------------------------------------------|------|

| 0 F         | by the Deal committee in 1979                                                                      | 72   |

| 3.5         | Schematic showing the differences between $D_{it}$ , $Q_{ot}$ , and $Q_{bt}$ in SiO <sub>2</sub> . | 77   |

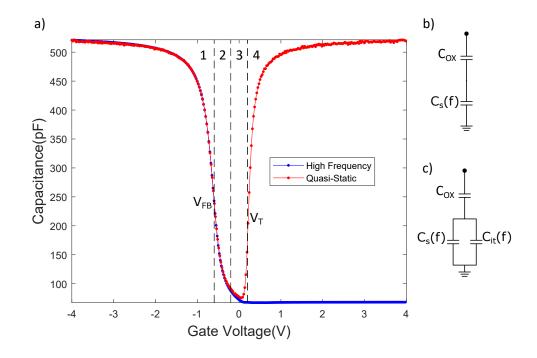

| 3.6         | Example of typical measured high frequency and quasi-static CV curves.                             | 79   |

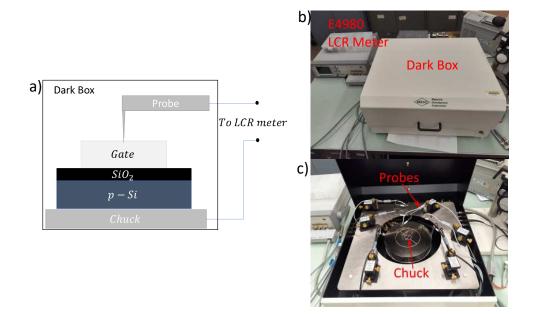

| 3.7         | Schematic drawing of the CV measurement setup                                                      | 81   |

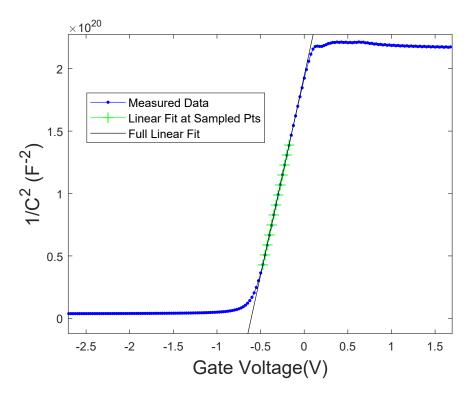

| 3.8         | Example plot used for extracting flatband voltage.                                                 | 82   |

| 3.9         | Example of a HFCV and QSCV measurements for a Al gated MOSCAP                                      | ~ ~  |

| 0.10        | with a high level of $D_{it}$ .                                                                    | 85   |

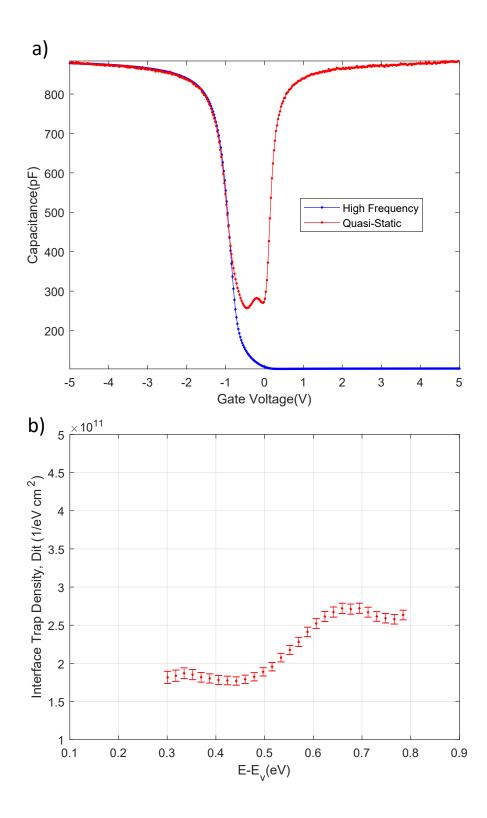

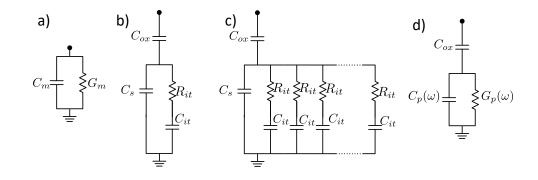

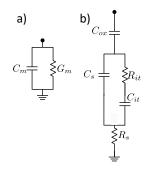

|             | Circuit diagrams for the measured admittance using a LCR meter                                     | 88   |

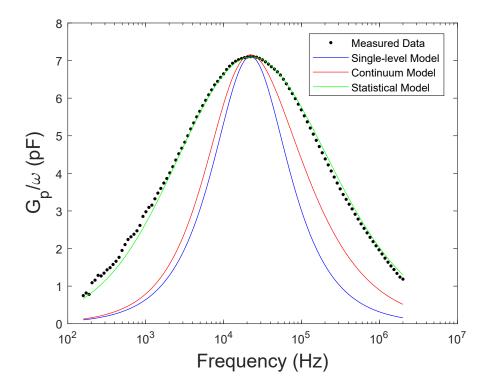

| 3.11        | Examples of the three models for measured conductance response                                     |      |

|             | from $D_{it}$ compared with measured data from an Al-gated MOSCAP.                                 | 92   |

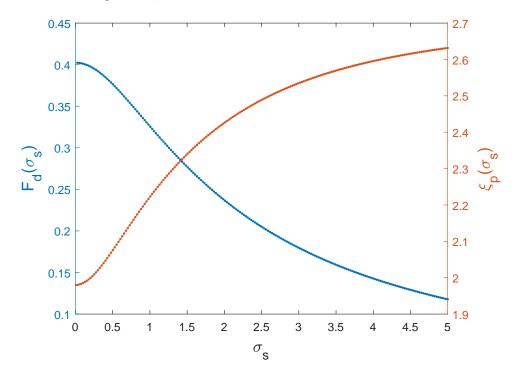

| 3.12        | Plots of the statistical model factors $F_d$ and $\xi_p$ from Eqs. 3.24 and                        | ~ ~  |

|             | 3.26 respectively as a function of $\sigma_s$ .                                                    | 95   |

| 3.13        | Example of conductance measurements for a Al gated MOSCAP with                                     |      |

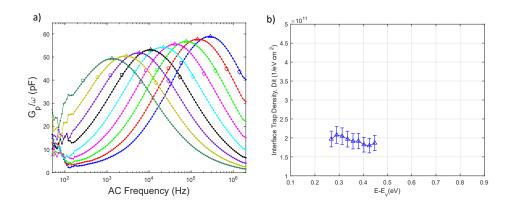

|             | a high level of $D_{it}$ .                                                                         | 96   |

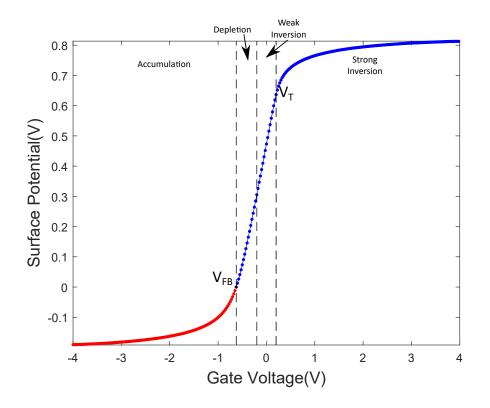

| 3.14        | Example of the surface potential vs gate voltage relationship obtained                             | ~ -  |

|             | from equation 3.29.                                                                                | 97   |

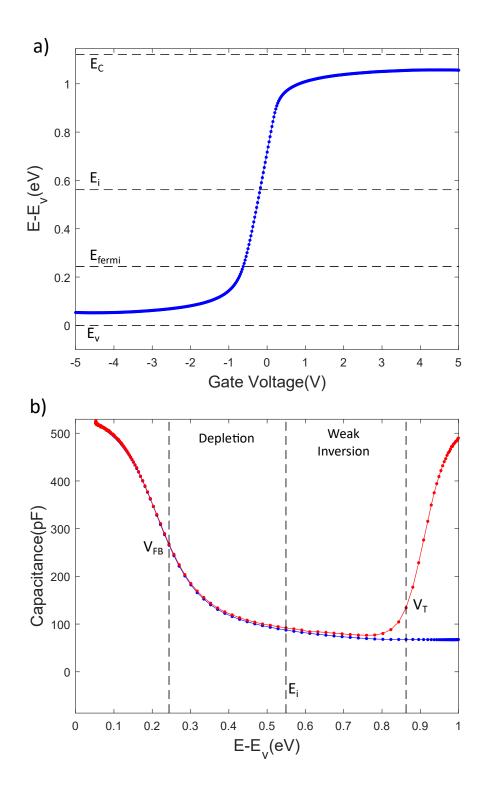

| 3.15        | Example of the $E - E_v$ vs Gate Voltage relationship obtained from                                | ~ ~  |

|             | equation 3.30                                                                                      | 99   |

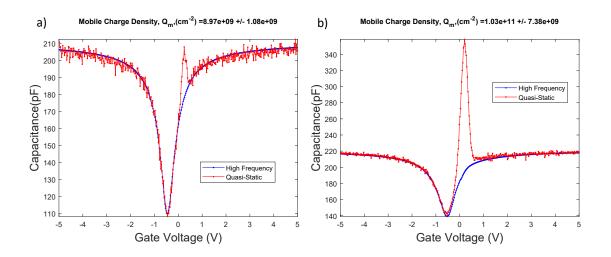

|             | Examples of a TVS of the mobile ion density in thermally grown $SiO_2$ .                           |      |

|             | Circuit models used in the series resistance corrections                                           | 103  |

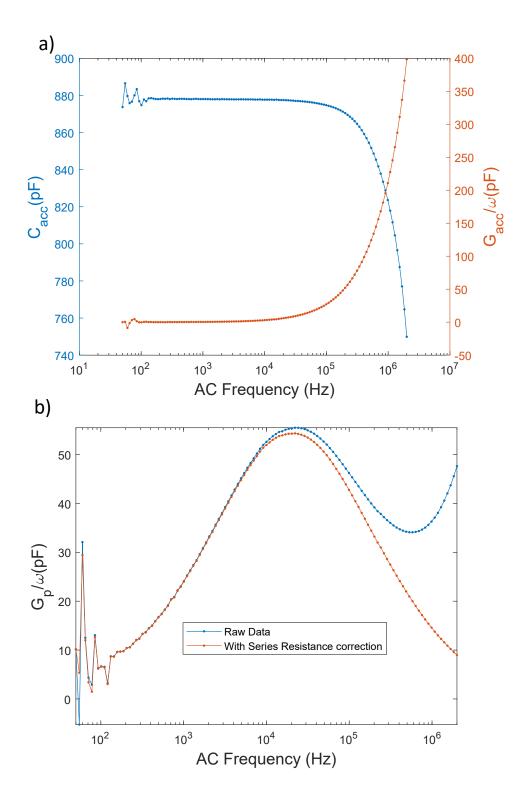

| 3.18        | Plot of the measured frequency dependence of the capacitance and                                   |      |

|             | conductance in accumulation used for correcting for series resistance                              |      |

|             | effects.                                                                                           | 104  |

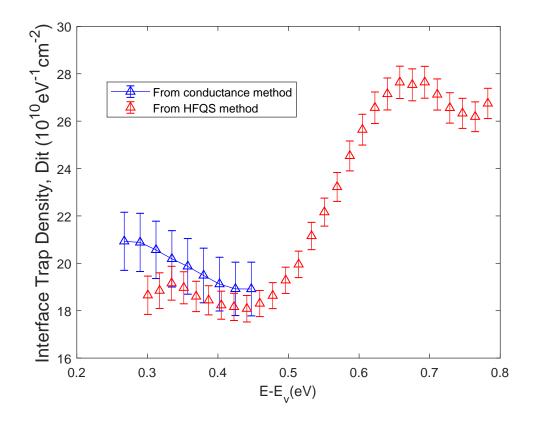

| 3.19        | Comparison of $D_{it}$ extracted from the HFQS (red) and conductance                               |      |

|             | methods (blue) for the same Al-gated MOSCAP from Figures 3.9 and                                   |      |

|             | 3.13 respectively.                                                                                 | 105  |

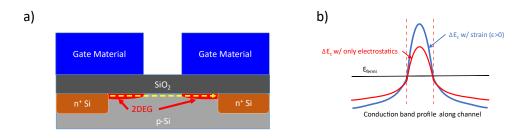

| 4.1         | Schematic cross-section of the metal-oxide-semiconductor (MOS) tun-                                |      |

| 4.1         |                                                                                                    | 109  |

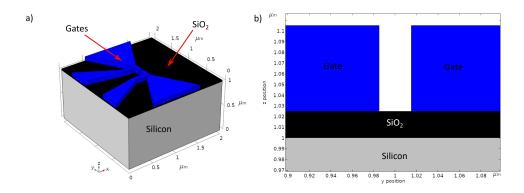

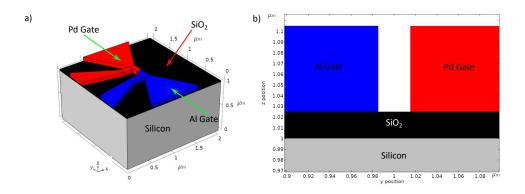

| 4.2         | Image of the 3d tunnel junction device model used for simulating                                   | 105  |

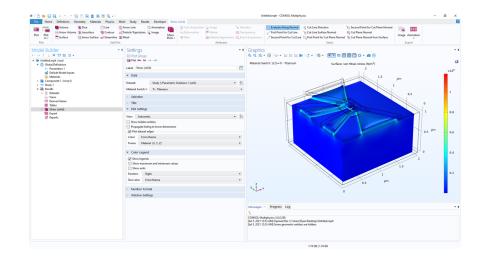

| 4.4         | strain in COMSOL.                                                                                  | 111  |

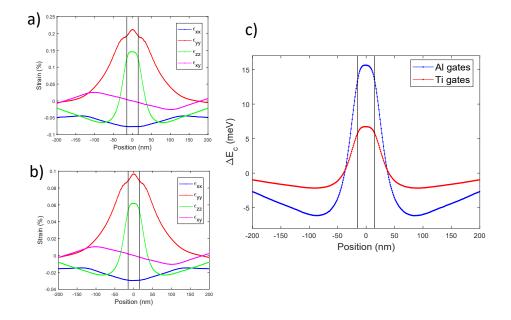

| 4.3         | Plots of the $\alpha$ -induced strain from cooling a TJ device from 300 K                          |      |

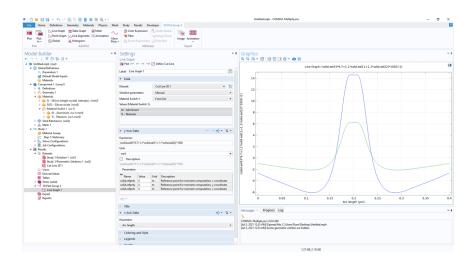

| 4.0         | down to 2 K for: Al gates and Ti gates.                                                            | 119  |

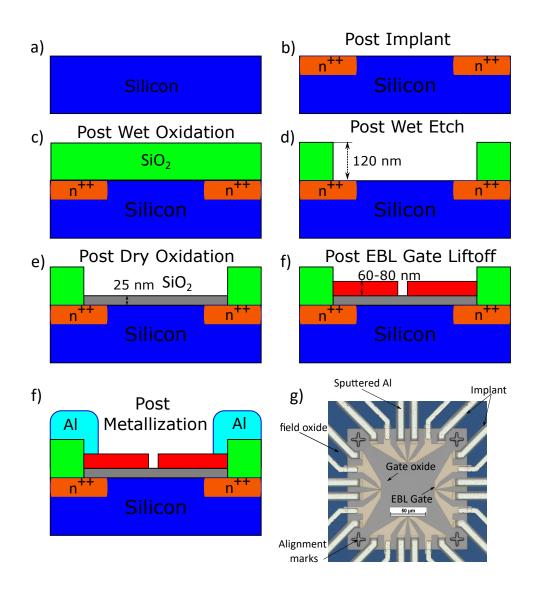

| 4.4         | Schematic of our TJ device fabrication process.                                                    |      |

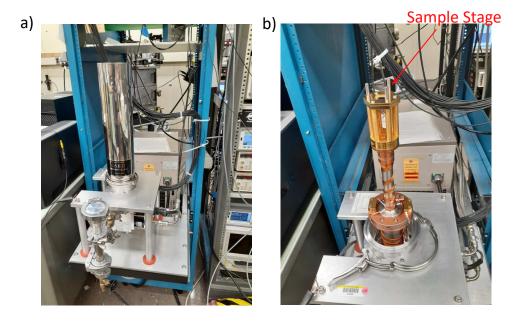

| 4.5         | Images of the 2 K closed cycle cryostat used for low temperature                                   | 114  |

| 4.0         | measurements of the devices in this work                                                           | 118  |

| 4.6         | Turn on for a TJ device at 2 K using different combinations of ohmics                              | 110  |

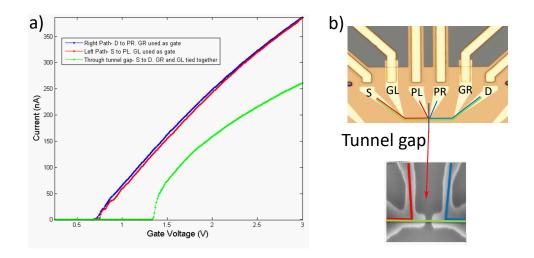

| 4.0         | and gates.                                                                                         | 110  |

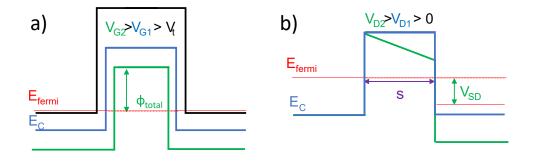

| 4.7         | Schematic of the expected electrostatic dependence in the trapezoidal                              | 115  |

| т.1         | barrier model.                                                                                     | 120  |

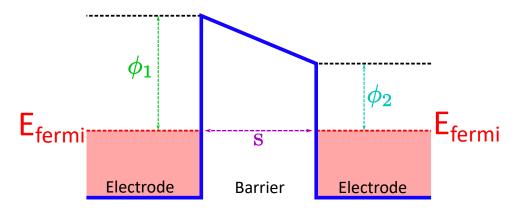

| 4.8         | Diagram of the trapezoidal barrier model used in the Brinkman-                                     | - 20 |

| <b>1.</b> 0 | Dynes-Rowell (BDR) model.                                                                          | 123  |

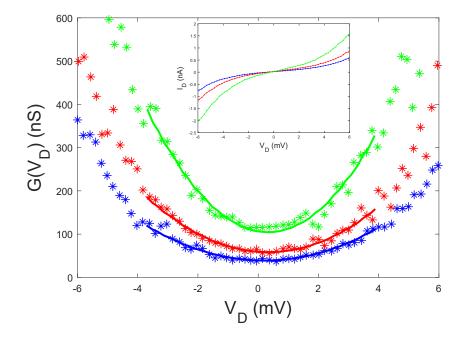

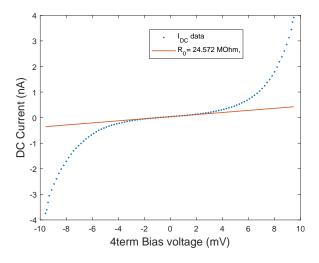

| 4.9         | 4-terminal DC transport data for a Ti-gated tunnel junction device.                                |      |

| т.Ј         | i terminar DO transport data for a 11-gated tunnel junction device.                                | -20  |

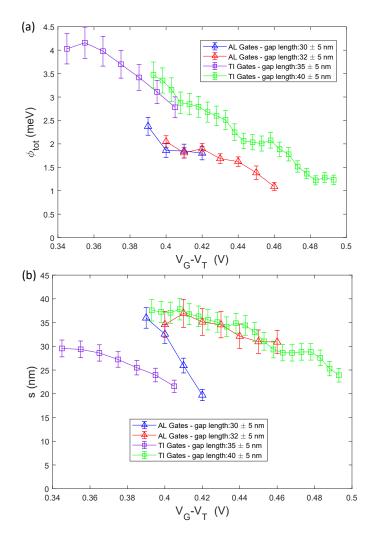

| 4.10 | Barrier height and barrier width as a function of gate voltage for<br>different MOS tunnel junctions                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

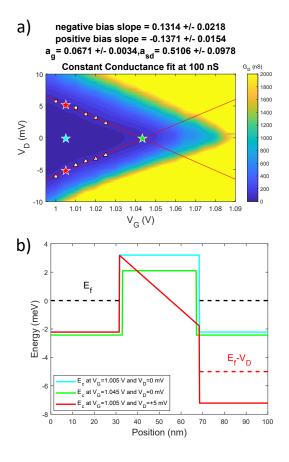

| 4.11 | Determination of gate and source-drain capacitive couplings to the<br>barrier region from 2-dimensional conductance map for a titanium-<br>gated device at 2 K        |

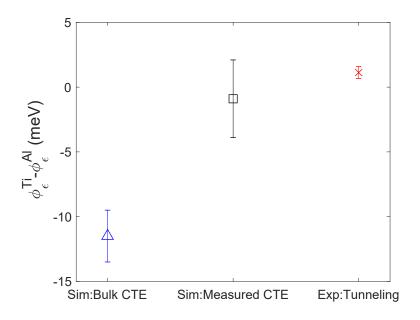

| 4.12 | Comparison of the barrier height difference between Ti and Al devices.131                                                                                             |

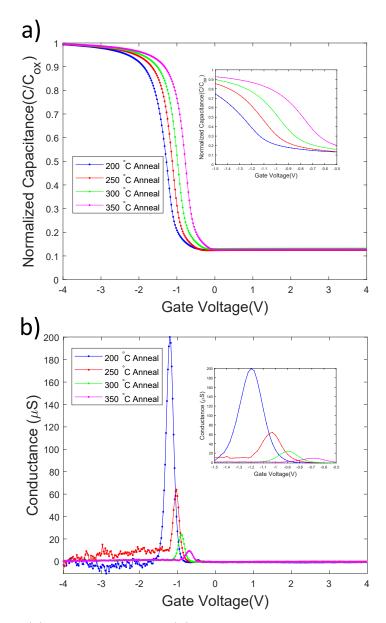

| 5.1  | (a) capacitance and (b) conductance vs Gate voltage for Pd-gated MOS capacitors for different anneal temperatures in 10 % forming gas.140                             |

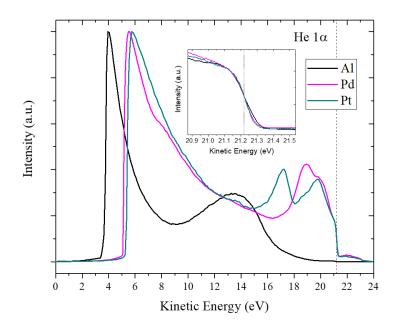

| 5.2  | Representative ultraviolet photoelectron spectroscopy (UPS) spectra of 60 nm Al, Pd, and Pt thin films on $SiO_2/Si$ wafers                                           |

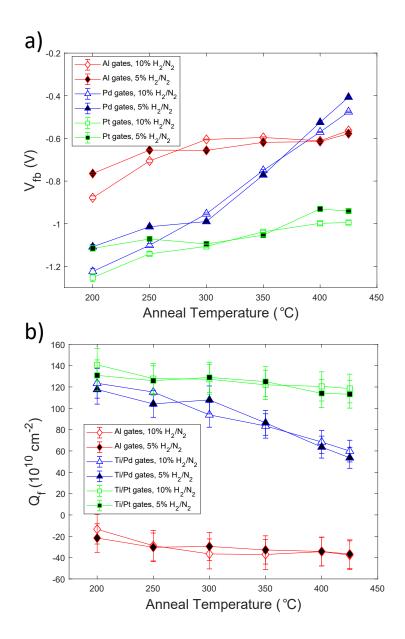

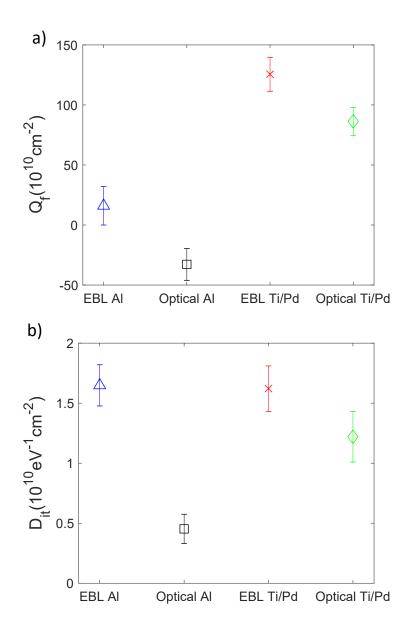

| 5.3  | (a) Flatband voltage, $V_{fb}$ , and (b) Fixed charge density, $Q_f$ , as a function of anneal temperature for Al, Ti/Pd, and Ti/Pt gates in 10 % and 5 % forming gas |

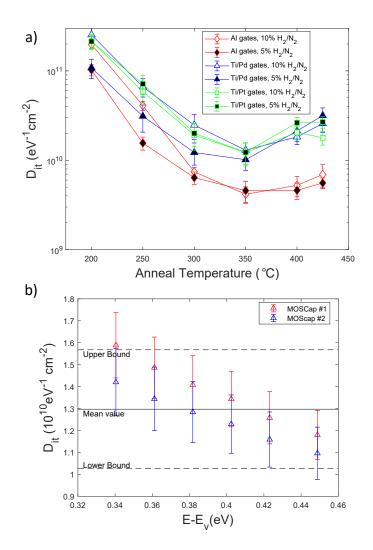

| 5.4  | Interface trap density, $D_{it}$ , vs anneal temperature for Al, Ti/Pd, and                                                                                           |

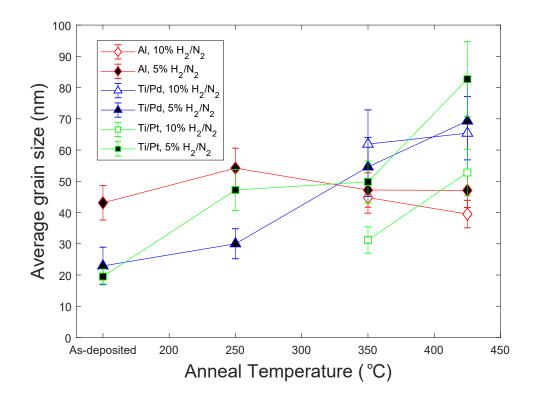

| 5.5  | Ti/Pt gates in 10 % and 5 % forming gas                                                                                                                               |

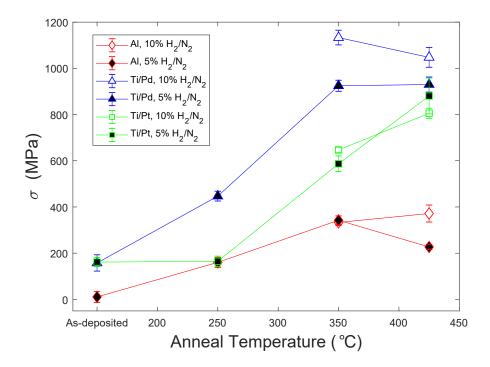

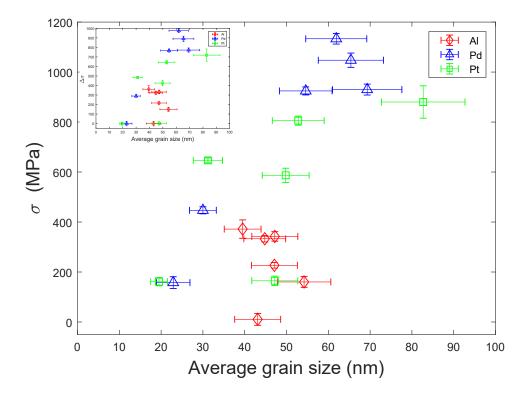

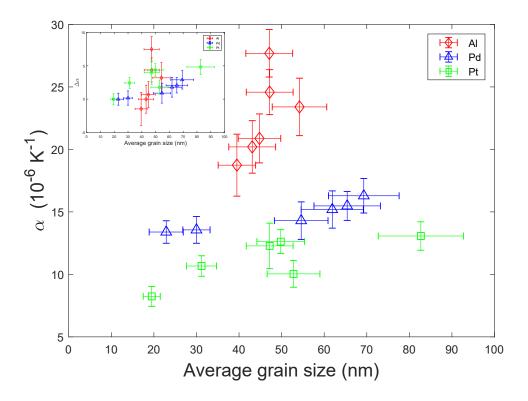

| 5.6  | Film stress $(\sigma)$ vs anneal temperature                                                                                                                          |

| 0.0  | for Al, Ti/Pd, and Ti/Pt films                                                                                                                                        |

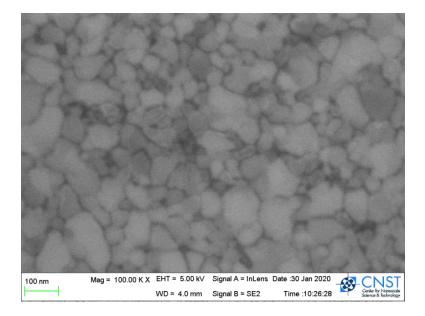

| 5.7  | SEM images and histograms of Ti/Pd films                                                                                                                              |

| 5.8  | SEM images of Al films                                                                                                                                                |

| 5.9  | SEM images of Ti/Pt films                                                                                                                                             |

| 5.10 |                                                                                                                                                                       |

|      | Film stress vs average grain size                                                                                                                                     |

|      | The change in the coefficient of thermal expansion with average grain size                                                                                            |

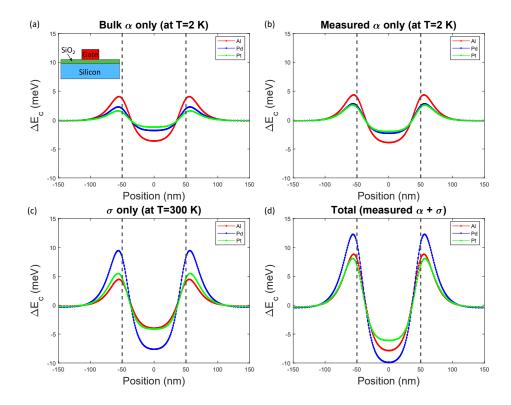

| 5.13 | Simulated conduction band modulation $(\Delta E_c)$ due to strain for 100 nm wide metal gate on top of 25 nm SiO <sub>2</sub> on a silicon substrate 157              |

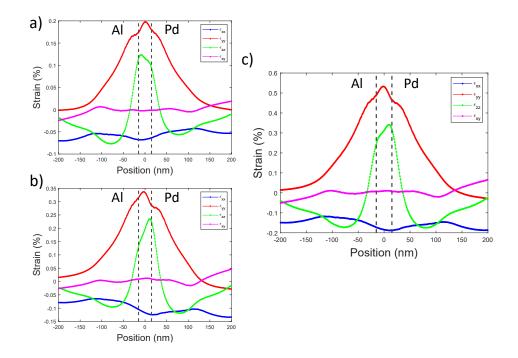

| 6.1  | Image of the 3d tunnel junction device model used for simulating strain in COMSOL                                                                                     |

| 6.2  | Plots of various strain components for Al/Pd asymmetric TJ device                                                                                                     |

|      | with 30 nm wide gap                                                                                                                                                   |

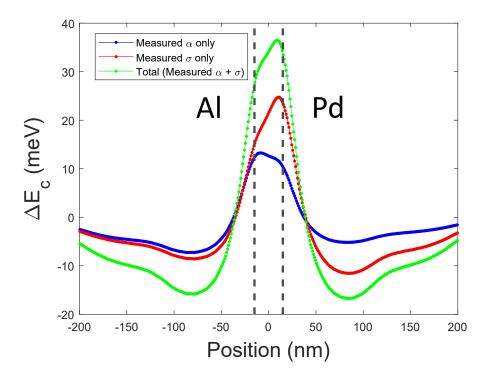

| 6.3  | Modulation of the conduction band $(\Delta E_c)$ for an asymmetric tunnel<br>with Al and Ti/Pd gates                                                                  |

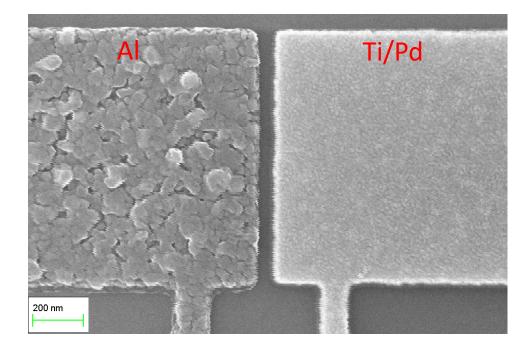

| 6.4  | SEM image of an asymmetric TJ device                                                                                                                                  |

| 6.5  | Measurements of the tunnel gap widths obtained via alignment in a                                                                                                     |

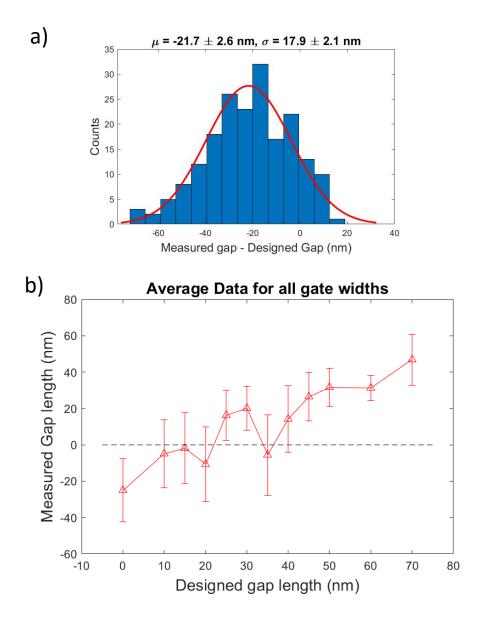

|      | Jeol 6300-FS electron beam lithography tool                                                                                                                           |

| 6.6  | C Turn on for a asymmetric TJ device at 2 K using different combi-<br>nations of ohmics and gates taken with a constant source-drain bias                             |

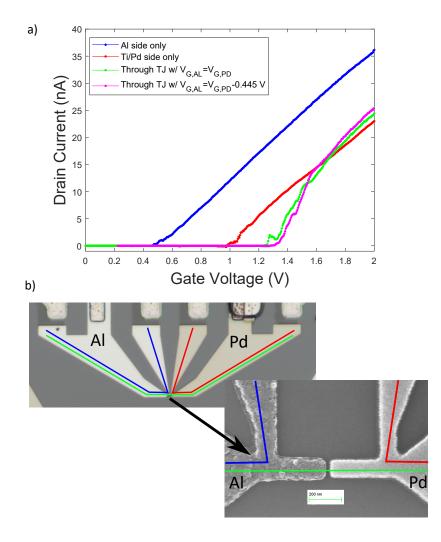

|      | $(V_{SD})$ of +500 $\mu$ V applied to the drain contact                                                                                                               |

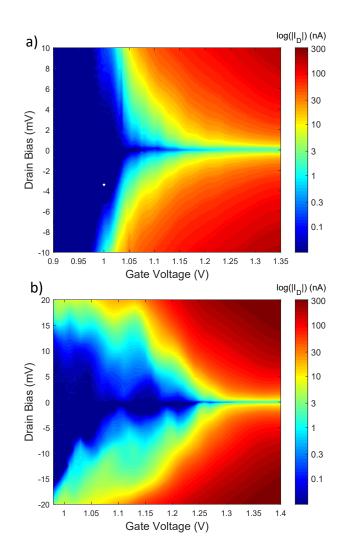

| 6.7  | Examples of 2d DC transport data for representative asymmetric TJs. 176                                                                                               |

| 6.8  | Optical image of diagnostic MOS capacitors fabricated on chip with                                                                                                    |

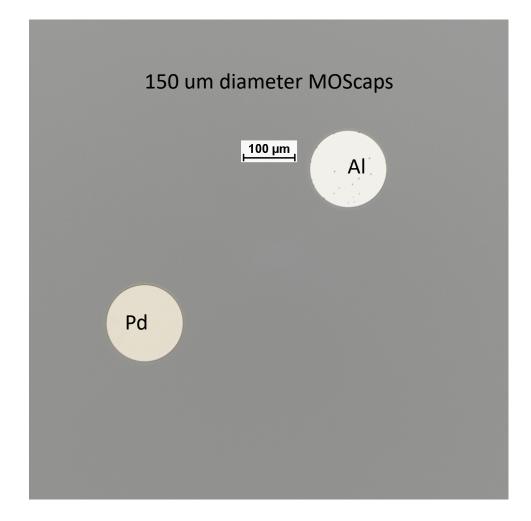

|      | tunnel junction devices                                                                                                                                               |

| 6.9                                                                                      | Comparison of defect densities: (a) measured fixed charge density,<br>$Q_f$ and (b) average interface trap density, $D_{it}$ from electron beam<br>lithography (EBL) MOS capacitors |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

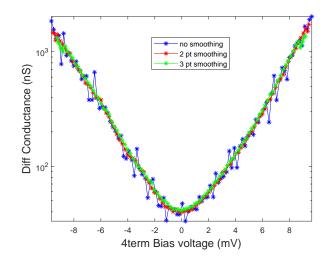

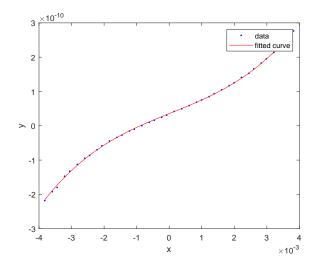

| A.1<br>A.2<br>A.3<br>A.4<br>A.5                                                          | $I(V_D)$ plot and zero-bias resistance fit produced by RSampLoop.m 203<br>Differential conductance plot produced by RSampLoop.m                                                     |

| B.1                                                                                      | Original SEM image for a Ti/Pd film after a forming gas anneal in 5 %H2/N2 at 350°C                                                                                                 |

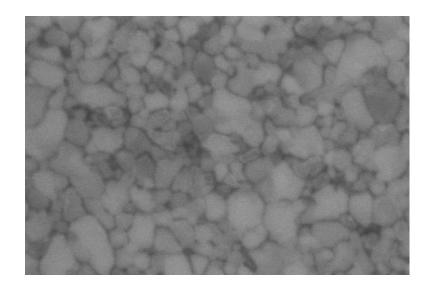

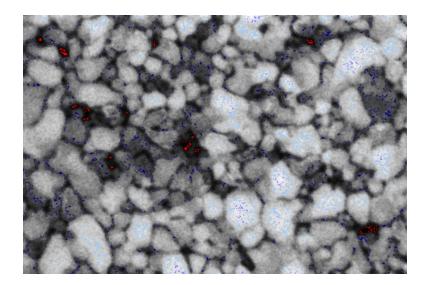

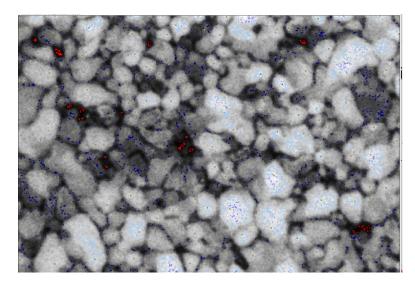

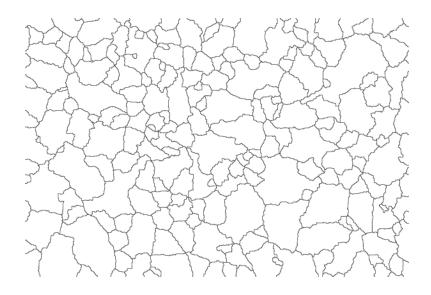

| <ul> <li>B.2</li> <li>B.3</li> <li>B.4</li> <li>B.5</li> <li>B.6</li> <li>B.7</li> </ul> | SEM image after cropping out the information bar at the bottom in<br>ImageJ                                                                                                         |

|                                                                                          | SEM image after using 'AND' segmented image and despeckled image<br>in ImageJ                                                                                                       |

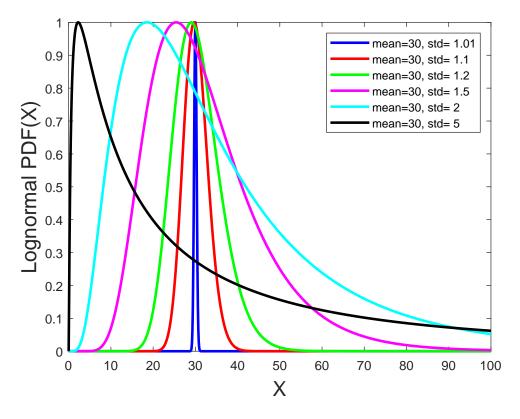

| B.12                                                                                     | Lognormal PDF for different mean and standard deviations                                                                                                                            |

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7                                            | Blank model produced by COMSOL model builder                                                                                                                                        |

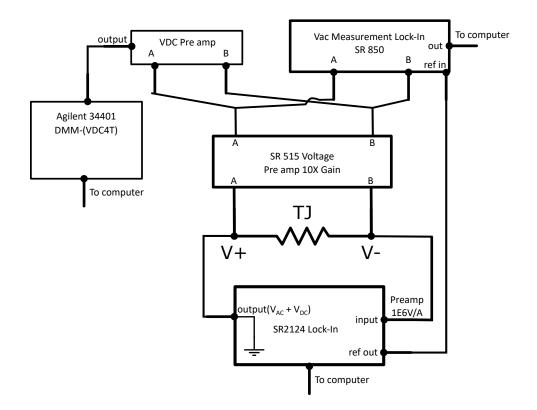

| D.1                                                                                      | Circuit diagram for AC measurements of TJ devices                                                                                                                                   |

### Chapter 1: Introduction

Silicon-based single electron devices (SEDs), fabricated using gate-defined quantum dots are some of the world's most sensitive devices. The sensitivity and single-electron nature of SEDs leads to a wide array of potential applications including nanoscale electrometry [3, 4] and thermometry [5], low power logic and memory [6, 7], electrical metrology as a quantum current standard [8, 9, 10], and solidstate quantum computing [11, 12, 13]. Local inhomogeneity and disorder caused by defects in the oxide, substrate impurities, or strain can profoundly affect device operation. Characterizing and controlling the sources of inhomogeneity is key to the full realization of any of the applications of silicon-based SEDs.

This chapter provides an overview of the fundamental physics and limitations of SEDs in silicon. The building block of the silicon SEDs we are interested in this work are quantum dots (QDs). Although most of the results presented in this work are not directly from QDs, all of results will be relevant towards their fabrication and design. In the first section, we discuss the major applications of interest specifically for quantum computing and quantum current standards. Next, we will provide some background information on the basic properties of generic QDs. Using this background; we will then focus our discussion towards QDs in silicon and how they are impacted by non-idealities, such as charge defects and inhomogeneous strain. The final portion of this chapter will lay the groundwork for understanding the interplay between these non-idealities and QDs.

#### 1.0.1 Motivation

Quantum dots (QDs) are conducting regions where charge can be isolated using electrostatic potentials. The confinement must be strong enough in 3-dimensions so that the energy levels associated with system are no longer degenerate. In this way, the discrete states of the QD are similar to that found in atoms so that QDs are sometimes referred to as artificial atoms. In reality, a QD is composed of a large number of atoms with a comparable number of electrons and holes bound to the nuclei. The properties of QDs, such as charge transport and bias dependence, are ultimately set by a much smaller number, from one to a few hundred, of free carriers isolated on the dot. In general, a QD can be occupied by either electrons or holes. For simplicity, the discussion in the following sections will focus on electrons, but similar physical arguments could be easily applied to holes.

### 1.0.2 Quantum computing

A quantum computer has the potential to efficiently solve certain computational problems, which have no efficient solution on a classical computer. Quantum computation works with quantum bits, or qubits. In contrast to a classical bit that can be described as either 0 or 1, a qubit can be in a superposition of quantum

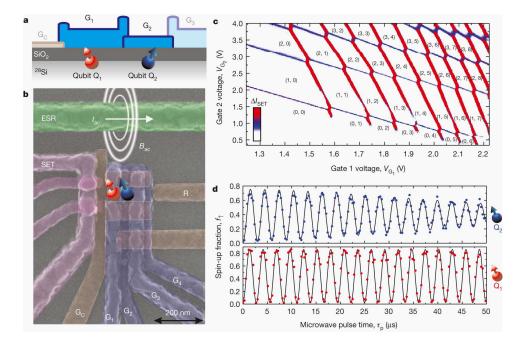

Figure 1.1: (a) Cross section schematic of a silicon MOS two qubit device. (b) SEM image of the two-qubit device. (c) Charge stability diagram of the two qubit device where gates  $G_1$  and  $G_2$  both have a single electron confined under them. (d) Individual Rabi oscillations for each qubit performed via ESR. Reprinted from Veldhorst, M., Yang, C., Hwang, J. et al. A two-qubit logic gate in silicon. Nature 526, 410–414 (2015). https://doi.org/10.1038/nature15263 with the permission of Spring Nature [11].

states |0 > or |1 >. Any two level quantum system with two well-defined quantum states that can be coupled could act as a qubit. Here, well-defined refers to true a two level system with no other states for the system to leak into. In practice, the requirements for building a quantum computer are much more complicated. In 2000, DiVincenzo identified several other important requirements in what is now referred to as "DiVincenzo Criteria" [14]:

- 1. A scalable physical system with well characterized qubits.

- 2. The ability to initialize the state of the qubits.

- 3. Coherence times long compared to the gate operation time.

- 4. The ability to perform one and two-qubit gates.

- 5. The ability to read-out the qubit state.

Over the past few decades, a wide array of different systems have been demonstrated and/or proposed as architectures for building a quantum computer. This includes trapped ions [15, 16], superconducting circuits [17, 18, 19, 20], neutral atoms in a optical lattice [21, 22], photonic devices [23, 24], liquid-state nuclear magnetic resonance [25, 26], topological qubits [27, 28], optical color centers in diamond [29, 30] and semiconducting devices [13, 31, 32]. The semiconductor spins approach to quantum computation offers a high degree of control over the device design, fabrication, and operation. In 1998, Loss and DiVincenzo proposed the use of electron spins in semiconductor QDs as qubits [13]. Here, the spin of the electron, which can be  $\pm \frac{1}{2}$ , is used to encode the qubit state with the two basis states being the spin-up and spin-down states. This proposal was built upon the usage of QDs in semiconducting structures, where a qubit is composed of a single QD that has a single confined electron. Fig. 1.1 shows an example of a silicon MOS based two-qubit device. Here, two QDs each occupied with one electron are formed under the gates labeled  $G_1$ and  $G_2$  in Fig. 1.1 (a) and (b). It is important to note that even though there are only two qubits in the device in Fig. 1.1 that gate layout is already complex. In addition to the gates  $G_1$  and  $G_2$  for controlling the qubits, there are layers for controlling the size of the QD  $(G_C)$ , moving electrons from a reservoir onto or off the QDs (R), and an extra QD used as a charge sensor for the qubits (labeled SET for single electron transistor). This level of complexity for only a two qubit device means that understanding the limitations and improving the MOS QD fabrication process and device design is key to achieving the scalability necessary for quantum computing.

# (a) Upper gate (Polycrystalline Si) Si wire 5102 $V_{\rm EXIT}$ VENT (b) G2 G1 Electron Ejection Γ $E_{\rm add}$ $\mathbf{I}_1$ D Loading Island

#### 1.0.3 Quantum current standard

Figure 1.2: (a) Schematic of silicon MOS QD device used as single electron pump. (b) Energy diagram in the silicon device showing the potential modulation used to pump electrons. Reprinted from Gento Yamahata, Stephen P. Giblin, Masaya Kataoka, Takeshi Karasawa, and Akira Fujiwara, "Gigahertz single-electron pumping in silicon with an accuracy better than 9.2 parts in 10<sup>7</sup>", Applied Physics Letters 109, 013101 (2016) https://doi.org/10.1063/1.4953872 with the permission of AIP Publishing [33].

The ampere, which is the SI base unit for current, has no good standard for use in metrology. A previous standard defined the ampere as a "constant current which, if maintained in two straight parallel conductors of infinite length, of negligible circular cross section, and placed 1 meter apart in vacuum, would produce between these conductors a force equal to  $2 \times 10^{-7} N$  per meter of length" [34]. From a practical perspective, this current standard is difficult to achieve. In 2019, the SI base units were redefined in terms of fundamental physical constants [35]. Thus, the ampere was defined in terms of the elementary charge of the electron e and the hyperfine transition frequency of cesium-133,  $\Delta \nu_{cs}$ . While the ampere is a base unit of the SI, as a practical matter it is treated as a derived unit from the voltage and resistance standards. In the case of other electrical SI units, such as resistance (R) and voltage (V), the standard is based on a physical system derived from quantum properties and ultimately derived from fundamental physical constants such as elementary charge (e) and Planck's constant (h). For the resistance standard, the quantum standard for the Ohm is based on the Quantum Hall effect [36]. Here, the quantum hall resistance is given as  $R_{QHR} = \frac{h}{e^2}$ . Similarly, the quantum voltage standard is based on the Josephson effect [37] and given as  $V_{JV} = \frac{nhf}{2e}$ . Based on the quantum resistance and voltage standards, a much simpler and practical current standard would be based on the charge of an electron. A single electron pump [38] is a device that acts as a quantum standard analogous to resistance and voltage, but for current. Similar to applications in quantum computing with semiconducting devices, the building block of single electron pump is the QD. An example of a silicon based single electron pump is shown in Fig. 1.2. Here, a QD is induced between the gates  $G_1$  and  $G_2$  in a silicon nanowire device. By applying an AC voltage to  $G_1$ , electrons can be shuttled through the device from the source (S) to the QD then off to the drain (D). In the ideal case, this process will eject a single electron from the QD to the drain once every cycle of the AC signal on  $G_1$ . If the AC signal has a frequency, f, then the current  $(I_P)$  through the pump will be given by:  $I_P = ef$ . For a typical pumping frequency around 1 GHz, the single electron pump will generate a current around 160 pA.

### 1.1 Quantum dots in Silicon

### 1.1.1 Why silicon?

Many of the early demonstrations of SEDs in semiconductor devices were in GaAs/AlGaAs heterostructures [39, 40, 41, 42, 43]. In fact much of the foundational work on quantum computing with semiconductor spins was performed in SEDs in GaAs including coherent manipulation of a single spin [12, 44], electrical single shot readout of a spin state [45], and the implementation of two-qubit gate operations [46]. From the perspective of quantum computing, one of the major problems with making qubits in III-V heterostructures, such as the GaAs/AlGaAs, is the relative abundance of non-zero nuclear spins. Any qubits fabricated in such systems will couple to this nuclear spin bath and experience decoherence [47], which refers to how long a quantum state can be held in a superposition before losing information to its environment as described by the third DiVincenzo criteria discussed above. Silicon has a significant advantage in this area since its most common nuclear spin isotope

(<sup>28</sup>Si, 92% in natural abundance) [48] has zero spin and the non-zero spin isotope (<sup>29</sup>Si) is only around 4.7% abundance in natural silicon. Additionally, methods exist to isotopically purify it such that the nuclear spin bath no longer dominates the sources of qubit decoherence [49].

For charge pumps, devices have also been fabricated in GaAs/AlGaAs [10, 50] and silicon [9, 33]. One of the major differences between charge pumps in the two material systems is that GaAs/AlGaAs devices typically have used large magnetic fields to achieve their reported accuracies and performance [51]. Silicon devices don't appear to need such large magnetic fields to achieve the same current and uncertainty. These large magnetic fields are not compatible with the quantum resistance and voltage standards. Since one of the desired goals of any quantum current standard it to perform the experiments using all three standards, silicon-based charge pumps have an advantage over GaAs.

For applications in quantum computing and a quantum current standard, the scalability of the devices is a key component in the choice of the material system. For quantum computing, if one qubit is formed by a single QD we will need millions of QDs to build a functional quantum computer. Similarly for a quantum current standard to make it comparable to the voltage and resistance standards, it would be advantageous to have a quantized current on the order of 1  $\mu A$  [52]. This would necessitate running many charge pumps in parallel. Silicon-based devices have a significant advantage from the scalability and fabrication perspective due to ubiquitous usage of silicon in industrial transistors. The mature fabrication history and infrastructure of the silicon industry could offer a promising path towards scaling for

large qubit systems and charge pumps. For this reason, silicon is one on the more attractive semiconductor material systems for quantum computing and quantum current standards.

#### 1.1.2 Material systems

Within the subset of silicon SEDs there are three main materials systems of interest: metal-oxide-semiconductor (MOS) heterostructures, Si/SiGe heterostructures, and individual donors. Fig. 1.3 shows an overview of these different material systems. The Si MOS and Si/SiGe devices (the bottom row in Fig. 1.3) are very similar to each other. Both systems rely on a 2-dimensional electron gas (2DEG) in silicon confined at an interface between silicon and a different material: silicon dioxide in the MOS case and silicon germanium alloy in the Si/SiGe case. The formation of QDs in both systems is achieved by using gates to used further confine the 2DEG as shown in the third column of Fig. 1.3. Individual donors are quite different as the donor nuclear potential acts as the source of the 3-dimensional confinement needed for a QD and the gate is used to move electrons on or off the donor. A single donor will also act as a QD with three available states: ionized  $(D^+)$ , neutral  $(D^0)$ , and negatively charged  $(D^-)$  as shown in the second column of Fig. 1.3. Meanwhile, QDs in silicon MOS and Si/SiGe will show a ladder of many different electron occupations. These different material systems have all shown promising demonstrations of their capabilities. All three systems have demonstrated devices with single electron occupations [53, 54, 55] and coherent manipulation of single

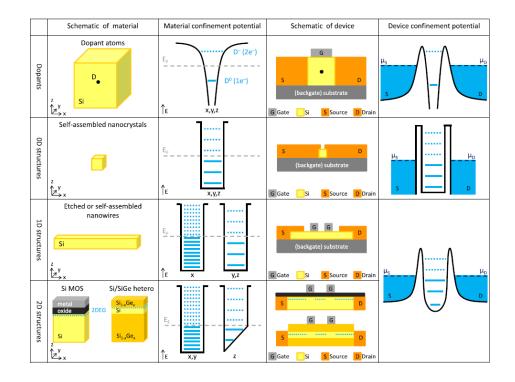

Figure 1.3: Schematic overview of the material stacks and confining potentials used in silicon based SEDs. The first column shows the primary materials used including individual dopants, Si 0D and 1D nanostructures, and 2d electrostatically defined devices in silicon metal-oxide-semiconductor (MOS) and Si/SiGe heterostructures. The second column shows the confining potential used to make the SED. States occupied by electrons are shown as solid lines and unoccupied states are shown as dashed lines. The third column shows a schematic of the typical device structure used to make the SED including the gate used to control the QD potential and the source/drain that act as reservoirs of electrons for the QD. Fourth column shows the potential landscape seen by electron in the QD devices from the third column. Reprinted with permission from Floris A. Zwanenburg et al. Silicon quantum electronics. Reviews of Modern Physics 10.1103/RevModPhys.85.961. Copyright 2012 by the American Physical Society.

spins [11, 56, 57]. In this work, we will focus on SEDs in the silicon MOS system.

### 1.2 Physics of Quantum Dots (QDs)

In order to understand how non-idealities will affect the potential applications of SEDs discussed above, we will first cover the basics of how QDs operate. In this section, we will define the requirements for making QDs and their ideal electrical properties. This foundation of the ideal behavior will provide the context for how non-idealities ultimately present themselves on the device performance.

### 1.2.1 Coulomb Blockade

The foundation of quantum dot physics and operation is the effect known as Coulomb blockade. In the case of QDs, we will see that Coulomb blockade will dominate transport and lead to oscillations in the measured current. To understand Coulomb blockade, consider the toy model of an isolated conducting disk. Initially, if the disk is uncharged we can add an electron to it without any energetic cost. Now if we try to add an additional electron, then we must overcome the Coulomb repulsion between the two electrons. The energy needed to overcome the repulsive Coulomb forces and add an additional electron onto the disk is defined as the charging energy  $(E_{ch})$ .  $E_{ch}$  is simply related to the energy stored in a capacitor with capacitance C as  $E_{ch} = \frac{q^2}{2C}$ . In the case of this isolated disk, C is the self-capacitance given as  $C = 8\pi\epsilon_r r$ , where r is the radius of the disk and  $\epsilon_r$  is the relative permittivity. Importantly, there is an additional constraint we need to satisfy in order to be able to see the individual charging events due to blockade. Consider a metallic disk with a radius of 100 nm. This gives a self-capacitance of 7 aF. Here, the charging energy would be roughly 11 meV. At room temperature, the thermal energy ( $k_bT \approx 26$ meV) would exceed the charging energy so that any single electron charging events would be thermally smeared out. This means in order to observe the single electron charging events signifying blockade we would need to move towards much lower temperatures. For example, at 1 K the thermal energy is roughly 86  $\mu$ eV or more than two orders of magnitude smaller than the charging energy. In this way, we can now define our first criteria for operation of QDs:  $E_{ch} >> k_bT$ . From this, we can also infer that we will need QD with small dimensions so that the charging energy stays reasonably large.

### 1.2.2 Confinement

QDs in silicon are most often formed electrostatically through the application of voltages to gates arranged in specific geometries to confine electrons. Fig. 1.4 shows a generic layout of gate structure for a silicon MOS QD. The operation of the gates in these QD devices is similar to a conventional MOS field effect transistor (MOSFET). In the case of a conventional MOSFET, the gate is used to control the conductivity of the channel formed between two heavily doped regions, referred to as the source and drain. The conducting channel is confined in the direction perpendicular to the oxide-silicon interface (z-direction in Fig. 1.4) by the electric field from gate, forming a 2-dimensional electron gas (2DEG). With the application

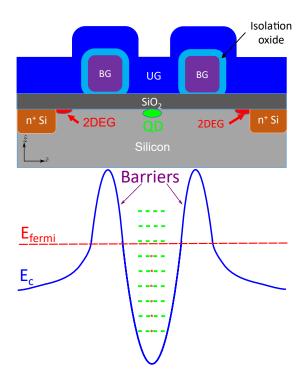

Figure 1.4: Schematic of the formation of QD in silicon MOS device. In this device, there are three gates total: two gates that are used to form barriers(purple) and one gate that used turn on conduction from the source to drain and control the dot chemical potential (blue). The bottom portion of the diagram shows the ideal conduction band profile for such a QD device. The dashed green lines indicate the dot levels and the red circles indicate when the level is occupied.

of a small bias voltage difference between the source and drain  $(V_{SD})$  current will flow between through the device  $(I_{SD})$ . When the gate voltage is below a certain value, known as the threshold voltage  $(V_t)$ , the conduction band in the channel  $(E_c)$  is above the fermi level  $(E_f)$  in the source/drain regions forming a electrostatic barrier. In this case, no current flows and the MOSFET is "off". When the gate voltage is above  $V_t$ ,  $E_c$  is now less than  $E_f$  in the channel, the 2DEG is formed, and the MOSFET is "on". The operation of an QD will follow the same principles as the MOSFET, but in the case of a QD the gate is split up into multiple regions so as to create a confining potential. The generic QD layout in Fig. 1.4 has a total of three gates, where two of the gates (purple) are used to form tunnel barriers or raise  $(E_c)$ above  $(E_f)$  selectively in different portions of the channel. The other gate (blue) is used for two purposes: 1) to turn on conduction outside of the barrier regions similar to the normal MOSFET and 2) to control the potential of the region where the QD is formed. In Fig. 1.4, we have drawn a ladder of evenly spaced states in the QD region where the spacing equals the charging energy of the dot. Dot levels that fall below  $E_f$  will be occupied (shown as red dots in Fig. 1.4) by electrons that tunnel on to the QD from source/drain.

In order to add or remove electrons, we need to couple the QD to some reservoir(s) of electrons. This coupling comes from the tunnel barriers discussed above and shown in Fig. 1.4. The tunnel barrier must be resistive enough that the tunneling lifetime, or the RC time constant of the QD, and charging energy of the dot satisfy the Heisenberg uncertainty principle,  $\Delta E \Delta t > \frac{\hbar}{2}$ , where  $\Delta E = \frac{e^2}{2C}$  and  $\Delta t = RC$ . In more practical terms, this means the tunnel barrier resistance (R) must be greater than the resistance quantum ( $R_Q = \frac{\hbar}{e^2}$ ) or 25.8 k\Omega. This forms the second criteria we need in order to see single charging events in QD devices. Importantly, this only sets the lower limit of the barrier resistance. The barrier resistance must also not be so high such that the current is not measurable. This means that ultimately the barrier resistance will need to be less than  $G\Omega$ .

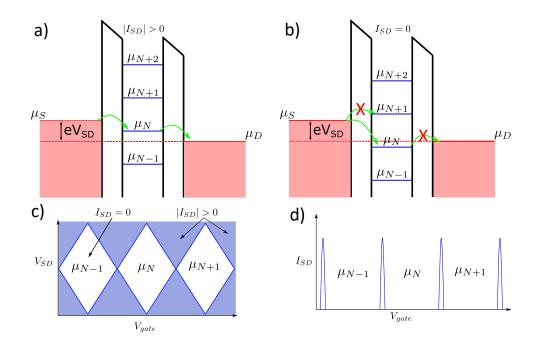

Figure 1.5: (a) Energy diagram of a quantum dot when there is current through the device  $(|I_{SD}| > 0)$ , where  $\mu_i$  refers to the chemical potential of the *i*th level. Here, electrons from the source  $(\mu_S)$  are able to sequentially tunnel onto the dot level  $(\mu_N)$  and onto the drain  $(\mu_D)$ . This is because  $\mu_N$  lies between the source and drain chemical potentials, which are separated by a small source-drain bias voltage  $(V_{SD})$ . (b) Energy diagram of a quantum dot when there is no current  $(I_{SD} = 0)$ and the device is the Coulomb blockade regime. Here, electrons from the source  $(\mu_S)$ are able to tunnel onto the dot level  $(\mu_N)$  but it is not energetically favorable to tunnel onto the drain since  $\mu_N$  is no longer in between  $\mu_S$  and  $\mu_D$ . (c) 2d transport diagram of an ideal quantum dot, where the x-axis is the gate voltage used to control the dot chemical potential and y-axis is the source-drain bias. Inside the diamonds, the device is blockaded as shown in (b) and there is no current. Outside of the diamonds, there is transport through the device as shown in (a) and there is a measurable current. (d) Schematic showing the expected behavior of current through the quantum dot with changes in gate voltage at constant source-drain bias.

### 1.2.3 Transport characteristics

Transport through the QDs will only occur when at least one of the discrete dot chemical potential levels  $(\mu)$  is within the bias window formed by the sourcedrain bias voltage (ie  $\mu_S > \mu_N > \mu_D$ ), as illustrated in Fig. 1.5(a). When the source-drain bias is small enough  $(eV_{SD} < E_{ch})$ , and the temperature is low enough, there may be only one state in the transport window and current through the device will be measured. In Fig 1.5(a), the chemical potential level  $\mu_{N-1}$  is occupied by an electron that has tunneled on to the dot from the source since  $\mu_{N-1} < \mu_S$ , but the electron is unable to tunnel off to the drain since  $\mu_{N-1} < \mu_D$ . Fig 1.5(b) shows the case of Coulomb blockade, where there are no states available that can allow an electron to tunnel from source to dot to drain (ie  $\mu_S > \mu_D > \mu_N$ ). Electrons will fill any states that are below the source or drain chemical potentials trapping the electron(s) on the dot. At larger source-drain bias  $(V_{SD})$ , the situation in Fig 1.5(a) changes as eventually multiple states on the dot will be available for transport and blockade will not occur. This happens once  $eV_{SD}$  exceeds the charging energy of the dot. The gate voltage can be used to move the chemical potential of the dot relative to the level of the source and drain. Therefore, transport through the QDs is allowed only for specific combinations of gate voltage and source-drain bias. Hence, the current through the SED will oscillate with gate voltage. This effect can be seen in the bias spectroscopy for QD shown in Fig 1.5(c). Here the no current regions (white) correspond to regions of Coulomb blockade and higher current regions (blue) correspond to electron transport through the dot. The shape of the blockade regions are typically referred to as the Coulomb Diamonds, where the height of the diamonds on the y-axis  $(V_{SD})$  gives the charging energy of the dot. Fig 1.5(d) shows a line cut through (c) showing the effect of sweeping only the gate voltage at low  $V_{SD}$ . Here, we can identify the signature of SED transport, an oscillating current as a function of gate voltage with a single period.

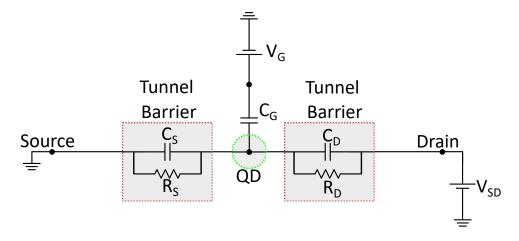

Figure 1.6: Circuit diagram for a single electron device. Tunnel barriers are represented as a parallel combination of a capacitor and resistor.

The period of the current oscillations and the slopes of the diamonds in Fig. 1.5 are determined by the gate  $(C_G)$ , source  $(C_S)$ , and drain  $(C_D)$  capacitances to the QD. A simplified circuit diagram for an SED is shown in Fig. 1.6. In this model, the tunnel barriers are treated as a parallel combination of a capacitor and resistor between the QD and either the source or drain. Meanwhile, the gate control of QD chemical potentials is purely capacitive. This means that the current oscillations as a function of gate voltage in Fig. 1.5 are inversely proportional to this gate-to-dot capacitance ( $\Delta V = \frac{e}{C_G}$ ). It is important to note in an ideal QD when sweeping this gate voltage, there should be oscillations with only a single period. Any behavior in a 1d gate voltage sweep or in the Coulomb diamond maps that shows something different from this suggests that the transport is due to more than one QD in device.

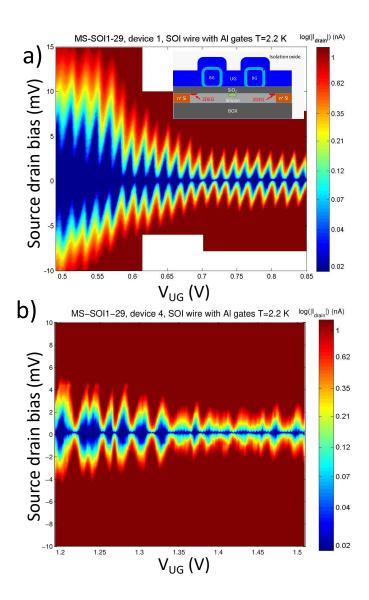

### 1.3 Non-idealities in silicon quantum dots

The discussion surrounding QDs so far has assumed that the local environment is ideal. In reality, this is not the case. The tremendous advantage of electrostatically defined QDs is that aspects such as the tunnel rates through barriers, the occupancy of electrons on the dot, and depth of the electrostatic potential well can all be controlled through gate voltages. This is high degree of tunability is one of the major reasons electrostatically defined QDs are considered good candidates for the potential applications previously mentioned. While electrostatically controlled tunnel barriers form the basis for QDs, their nature creates additional complexity through the fact that the tunnel barrier properties are highly sensitive to non-idealities in the local environment. Fig. 1.7 shows Coulomb Diamond maps for two MOS QDs fabricated on silicon-on-insulator (SOI) substrates by Binhui Hu at NIST. The data here are taken by sweeping the upper gate voltage ( $V_{UG}$  as shown in the inset of Fig. 1.7) and keeping the barrier gate voltages  $(V_{BG})$  fixed. Importantly, both of these devices are nominally identical. They were fabricated on the same  $1 \ cm^2$  chip and the measurements were taken during the same cryostat cooldown. Under these conditions, we would expect that transport measurements through the two devices would also be identical. It is easy to see in Fig. 1.7 that this is not the case. Fig. 1.7(a) shows nearly ideal behavior for a single QD: many