#### ABSTRACT

Title of Dissertation: NANO-ENGINEERING AND SIMULATING

ELECTROSTATIC CAPACITORS FOR ELECTRICAL

**ENERGY STORAGE**

Lauren Christine Haspert, Doctor of Philosophy, 2012

Dissertation directed by: Professor Gary W. Rubloff

Minta Martin Professor of Engineering,

Department of Materials Science and Engineering and the

Institute for Systems Research

Electrical energy storage solutions with significantly higher gravimetric and volumetric energy densities and rapid response rates are needed to balance the highly dynamic, time-variant supply and demand for power. Nanoengineering can provide useful structures for electrical energy storage because it offers the potential to increase efficiency, reduce size/weight, and improve performance. While several nanostructured devices have shown improvements in energy and/or power densities, this dissertation focuses on the nanoengineering of electrostatic capacitors (ESC) and application of these high-power electrostatic capacitors in electrical energy storage systems.

A porous nano-template with significant area enhancement per planar unit area coated with ultra-thin metal-insulator-metal (MIM) layers has shown significant improvements in areal capacitance. However, sharp asperities inherent to the initial nano-template localized electric fields and caused premature (low field) breakdown, limiting the possible energy density ( $E = \frac{1}{2} CV^2/m$ ). A nanoengineering strategy was

identified for rounding the template asperities, and this showed a significant increase in the electrical breakdown strength of the device, providing rapid charging and discharging and an energy density of 1.5 W-h/kg – which compares favorably with the best state-of-the-art devices that provide 0.7 W-h/kg.

The combination of the high-power ESC with a complementary high-energy-density electrochemical capacitor (ECC) was modeled to evaluate methods resulting in the combined power-energy storage capabilities. While significant improvements in the ESC's energy density were reported, the nanodevices display nonlinear leakage resistance, which directly relates to charge retention. The ECC has distinctly different nonlinearities, but can retain a greater density of charge for significantly longer, albeit with slower inherent charging and discharging rates than the ESC. The experimentally derived dynamic model simulating the nonlinear performance of the ESC and ECC devices indicated this hybrid-circuit reduces the time required to charge the ECC to near-maximum capacity by a factor of up to ~ 12.

# NANO-ENGINEERING AND SIMULATING ELECTROSTATIC CAPACITORS FOR ELECTRICAL ENERGY STORAGE

by

Lauren Christine Haspert

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment

Of the requirements for the degree of

Doctor of Philosophy

2012

# **Advisory Committee:**

Professor Gary W. Rubloff, Chair Professor Sang Bok Lee Professor Manfred Wuttig Professor Lourdes Salamanca-Riba Professor John Cumings © Copyright by Lauren Christine Haspert 2012

# Dedication

To my father and mother Dr. J. Kent and Karen Haspert

# Acknowledgements

I am sincerely thankful to my advisor, Prof. Gary Rubloff, for his support, guidance and help throughout my graduate school career. His enthusiasm and creativity for research have truly been inspiring. I am also grateful to Prof. Sang Bok Lee as my unofficial co-advisor for his continued encouragement, support and guidance.

I would like to acknowledge my colleagues for their discussions and collaborations. In particular, I would like to give a special thanks to Dr. Israel Perez for being my mentor and encouraging me to learn MatLab. I would also like to give many thanks to Dr. Parag Banerjee and Dr. Stefanie Sherrill for their support and thoughtful collaboration over the years.

I would like to acknowledge the University of Maryland NanoCenter and give thanks to the NanoCenter Staff. None of this work would be possible without funding support from NSF's support of the NispLab as a MRSEC Shared Experimental Facility. This work has been supported by the Laboratory for Physical Sciences (LPS) and the Department of Energy (DOE). Supported by Nanostructures for Electrical Energy Storage (NEES), an Energy Frontier Research Center funded by the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences under Award Number DESC0001160.

Last but certainly not least, I thank my family, especially my parents and sisters, and friends for their endless moral support, patience and encouragement.

# Table of Contents

| Dedication                                                                             | i  |

|----------------------------------------------------------------------------------------|----|

| Acknowledgements                                                                       | ii |

| Table of Contents                                                                      | iv |

| List of Tables                                                                         | V  |

| List of Figures                                                                        |    |

| Chapter 1: Introduction                                                                | 1  |

| 1.1 Background and Motivation                                                          | 1  |

| 1.2 Electrostatic capacitors for electrical energy storage                             | 4  |

| 1.2.1 Methods of increasing charge storage capacity                                    |    |

| 1.2.2 Influence of nano-template on electrical performance                             | 7  |

| 1.2.3 Ultra-thin metal-insulator-metal layers                                          |    |

| 1.2.4 Basic processing sequence of fabricating nano-electrostatic capacitors           | 9  |

| 1.3 Overview of Dissertation                                                           | 10 |

| 1.3.1 Objectives                                                                       | 10 |

| 1.3.2 Outline                                                                          | 11 |

| Chapter 2: Anodic Aluminum Oxide (AAO)                                                 | 12 |

| 2.1 Introduction                                                                       |    |

| 2.2 Structure properties of AAO                                                        |    |

| 2.3 Fabrication a highly ordered porous AAO nanotemplate                               |    |

| 2.4 Theories for self-alignment and ordering mechanisms of AAO                         | 18 |

| 2.4.1 Enhanced field-assisted mechanism                                                |    |

| 2.4.2 Mechanical forces by volume expansion                                            |    |

| 2.5 Formation of non-porous anodic alumina                                             | 22 |

| 2.6 Methods for fabricating AAO templates                                              |    |

| Chapter 3: Atomic Layer Deposition (ALD)                                               |    |

| 3.1 Introduction                                                                       |    |

| 3.1.1 Processing sequence                                                              |    |

| 3.1.2 Applications                                                                     |    |

| 3.2 ALD coatings on complex nanostructures                                             |    |

| 3.3 Nanolaminate ALD films                                                             |    |

| 3.4 Doping ALD films to improve electrical performance                                 |    |

| 3.4.1 Improving dielectric performance of TiO <sub>2</sub> with Al-doping (ATO)        |    |

| 3.4.2 Optimizing conduction of transparent Al-doped ZnO (AZO)                          | 37 |

| 3.5 Deposition recipes for MIM trilayers                                               |    |

| Chapter 4: Nanoengineering strategies for metal-insulator-metal electrostatic capacito |    |

| 4.1 Abstract                                                                           |    |

| 4.2 Introduction                                                                       |    |

| 4.3 Theory and Results                                                                 |    |

| 4.3.1 Geometric modeling and Optimization of Nanocapacitors and Arrays                 |    |

| 4.3.2 Device and Template Optimization                                                 |    |

| 4.3.3 Smoothing Template Nanotopography                                                |    |

| 4.3.4 Electrical Consequences of BAA Smoothing Layer                                   |    |

| 4.3.5 ALD Passivation Layers to Suppress Impurity Diffusion                            |    |

| 4 4 Discussion                                                                         | 56 |

| 4.5 Conclusion                                                            |  |

|---------------------------------------------------------------------------|--|

| Chapter 5: Hybrid Circuits to Exploit Electrostatic and Electrochemical E |  |

| Nanostructures                                                            |  |

| 5.1 Abstract                                                              |  |

| 5.2 Introduction                                                          |  |

| 5.2.1 Trade-off between energy density and power density                  |  |

| 5.2.2 Opportunities and limitations of nanostructures                     |  |

| 5.3 Devices overview                                                      |  |

| 5.3.1 Electrostatic capacitors (ESC)                                      |  |

| 5.3.2 Electrochemical capacitor (ECC)                                     |  |

| 5.3.3 Creating a hybrid system                                            |  |

| 5.4 Modeling dynamic behavior                                             |  |

| 5.5 Results                                                               |  |

| 5.5.1 Charge capture and transfer efficiencies                            |  |

| 5.5.2 Hybrid charging rates and energy efficiencies                       |  |

| 5.6 Discussion                                                            |  |

| 5.7 Conclusions                                                           |  |

| Chapter 6: Conclusions and Outlook                                        |  |

| 6.1 Summary                                                               |  |

| 6.2 Outlook                                                               |  |

| References                                                                |  |

# List of Tables

| Table 3.1 A list of examples in literature of ALD coatings on various nan | ostructures and |

|---------------------------------------------------------------------------|-----------------|

| their applications. *PVC: Polyvinyl chloride, PS: polystyrene, PC:        | polycarbonate,  |

| PP: polypropylene, PMMA: polymethylmethacrylate                           | 31              |

| Table 3.2. A list of some examples in literature using ALD nanolaminate   | es for improved |

| performance properties.                                                   | 33              |

# List of Figures

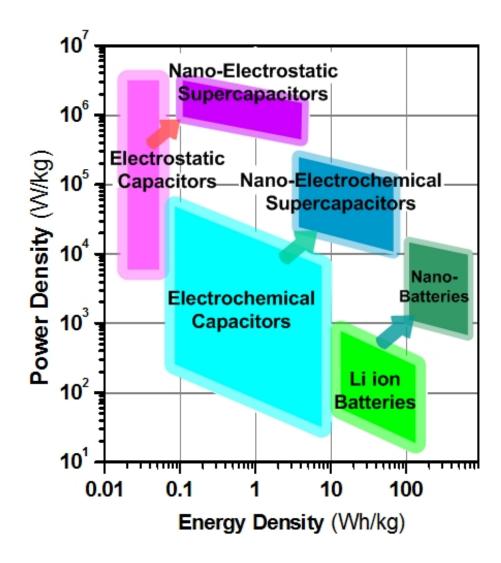

| Figure 1.1 Ragone plot showing the power density and energy density of electrostatic                                        |

|-----------------------------------------------------------------------------------------------------------------------------|

| capacitors, electrochemical capacitors and Li on batteries. Nanostructures have                                             |

| shown improvements in the energy density and/or energy density                                                              |

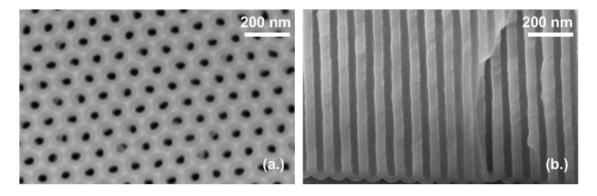

| Figure 1.2 (a) Top-view SEM image of a porous anodic aluminum oxide template with                                           |

| hexagonally periodically spaced pores and (b) cross-section of the pore base showing                                        |

| highly aligned, vertical pore growth.                                                                                       |

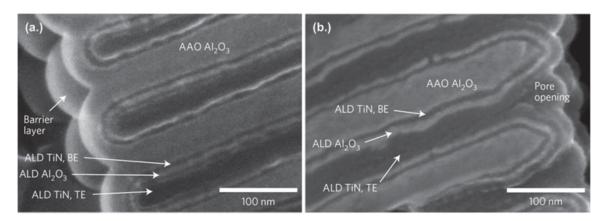

| Figure 1.3 (a) SEM images of MIM capacitor fabricated in AAO template at the pore                                           |

| base and (b) at the pore opening shows conformal deposition of the TiN-Al <sub>2</sub> O <sub>3</sub> -TiN                  |

| metal-insulator-metal layers. [Reprinted from Banerjee <i>et al.</i> <sup>28</sup> ]                                        |

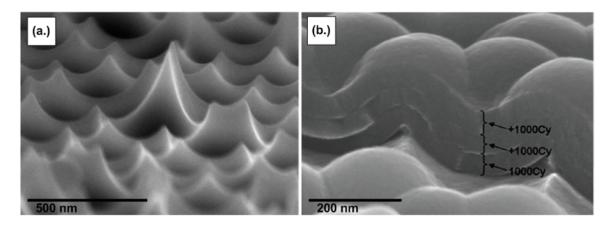

| Figure 1.4 (a) Peak asperities on an rough surface resembling the interpore peaks on the                                    |

| AAO templare and (b) introducing several layers of ALD on top of a non-planar                                               |

| surface smoothes the surface. [Reprinted from Cleveland <i>et al.</i> $^{30}$ ]                                             |

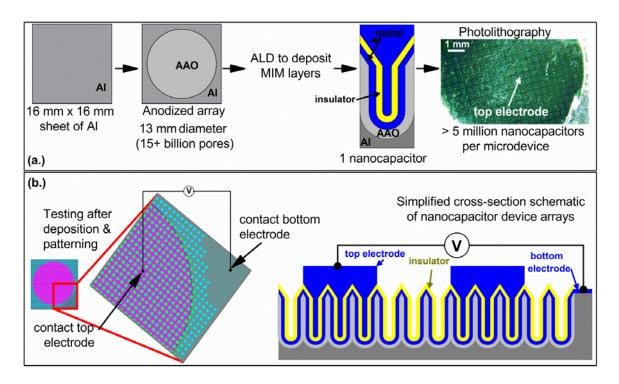

| Figure 1.5 (a) Left to right: shows process flow of anodizing the sheet of the aluminum                                     |

| for creating a massive porous array. Within a 13 mm diameter window more than 5                                             |

| billion pores are available for use as nanocapacitors. A photograph shows the AZO                                           |

| electrodes that have been patterned for electrical characterization and testing. (b).                                       |

| Schematic of the AAO template on Al with patterned AZO top electrodes (green) are                                           |

| individually contacted when probing the top electrode (left). A simplified schematic                                        |

| shows how contact is made to the bottom and top electrodes (right)                                                          |

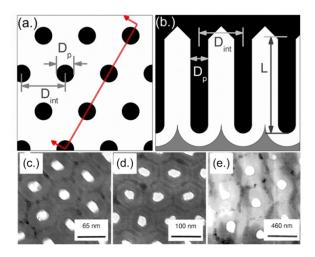

| Figure 2.1 (a) Top-view schematic of ordered AAO and (b) cross-section schematic of                                         |

|                                                                                                                             |

| AAO template, where $D_{\text{int}}$ is the intepore spacing, $D_{\text{p}}$ is the pore diameter and $L$ is the            |

| pore depth. Top-view TEM images of AAO templates anodized under various                                                     |

| anodization chemistries, resulting in different $D_{\text{int}}$ and $D_{\text{p}}$ of (c) 66.3 nm and 24 nm,               |

| (d) 105 nm and 31 nm, and (e) 501 nm and 158.4 nm, respectively. [c-e are reprinted                                         |

| from Nielish et al. $^{42}$ ]                                                                                               |

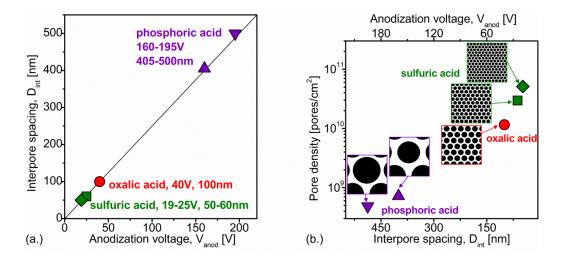

| Figure 2.2 (a) Dependence of anodization voltage on interpore spacing, $D_{\text{int}}$ , for various                       |

| ordering regimes (as indicated by acids). [Adapted from Lee <i>et al.</i> <sup>40</sup> ] (b) The effect                    |

| $D_{\text{int}}$ on the pore density (shown for mild anodization conditions) has an inverse                                 |

| relationship, bottom axis. The associated $V_{anod}$ is shown on the top axis. Insets                                       |

| represent the relative interpore spacing. 14                                                                                |

| Figure 2.3 Schematic representing the ionic movement responsible for the dissolution of                                     |

| Al <sub>2</sub> O <sub>3</sub> by ejecting Al <sup>3+</sup> (aq) into solution and oxidation of Al through the migration of |

| OH <sup>-</sup> /O <sup>2-</sup> to the metal-oxide interface                                                               |

| Figure 2.4 (a) Current density versus time profile for potentiostatic anodization of Al,                                    |

| showing the current contribution from oxide formation and pore formation. [Adapted                                          |

| from Hoar et al. <sup>48</sup> and Eftekahri et al. <sup>45</sup> ] (b) Oxide formation at various stages. Stage            |

| a: forms an oxide barrier coating on the Al surface. Stage b: cracks propagate                                              |

| through oxide barrier. Stage c: pore cells form and break down barrier oxide. Stage                                         |

| d: lateral and steady-state pore growth. [Reprinted from Eftekhari et al. <sup>45</sup> ]                                   |

| Figure 2.5 Schematics of AAO processing sequence for ordered AAO templates: (a) first                                       |

| anodization has random pore spacing at pore top (SEM, top left) and ordered pores at                                        |

| pore bottom (SEM, bottom right), (b) etch oxide for scalloped Al surface (SEM                                               |

| bottom), and (c) second anodization for ordered template                                                                    |

|                                                                                                                             |

| Figure 2.6 (a) Schematic representing the ionic conduction during steady-state pore                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------|

| growth and mobility of electrolytic anions through the cross-sectional barrier layer.                                                |

| [Adapted from Patermarakis et al. <sup>51</sup> and Eftekhari et al. <sup>45</sup> ] (b) Anion incorporation as                      |

| a result of electrolytic solution at pore base. [Adapted from Eftekhari et al. 45] 18                                                |

| Figure 2.7 Schematic for the field-enhanced pore formation mechanism. The field at the                                               |

| oxide-electrolyte interface, E <sub>1</sub> , and the field at the metal-oxide interface, E <sub>2</sub> , are                       |

| shown. [Adapted from Chen <i>et al.</i> <sup>52</sup> ]                                                                              |

| Figure 2.8 Schematic for the volume-expansion formation mechanism. The electric field                                                |

|                                                                                                                                      |

| is concentrated at the base of the pore, causing the sidewalls to move upward. [Adapted from Jessensky <i>et al.</i> <sup>53</sup> ] |

| Figure 2.9 Schematic representing the difference in oxide growth during initial Al                                                   |

| anodization for porous AAO and non-porous AAO when ridges in Al surface are                                                          |

| present. The oxide growth formed prior to porous AAO growth is non-uniform (left),                                                   |

| while the oxide formed with an anodization chemistry for creating non-porous films,                                                  |

| barrier anodic aluminum (BAA), is uniform.                                                                                           |

| Figure 2.10 Current versus time for forming a BAA layer in an aqueous neutral                                                        |

| electrolytic solution for 150 s. Increasing $V_{\text{anod}}$ increases the current and thus,                                        |

| •                                                                                                                                    |

| increases the thickness of the barrier anodic aluminum (BAA), or non-porous oxide                                                    |

| film thickness. For all current-time curves, the continual decrease in current with                                                  |

| time indicates no porous oxide formation                                                                                             |

| Figure 3.1 Schematic of one complete metal-oxide ALD cycle (clockwise): initial                                                      |

| hydroxyl functionalized surface, pulsing a metal-organic precursor (ML <sub>4</sub> ) reacts with                                    |

| surface sites, purge removes unreacted precursor and byproducts, H <sub>2</sub> O pulse reacts                                       |

| with remaining ligands attached to metal site, final purge removes any unreacted                                                     |

| precursor and byproducts. At the end of one cycle, one monolayer of material MO <sub>2</sub>                                         |

| uniformly and conformal coats the entire surface                                                                                     |

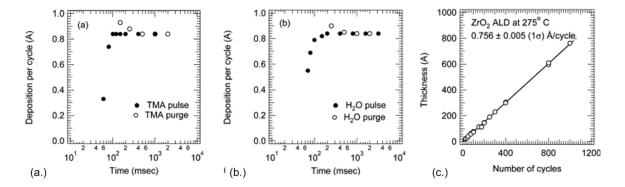

| Figure 3.2 The effect of pulse and purge time on deposition per cycle of an Al <sub>2</sub> O <sub>3</sub> film                      |

| (tri-methyl aluminum, TMA, and H <sub>2</sub> O precursors). (a) Effect of TMA pulse and                                             |

| purge time and (b) effect on H <sub>2</sub> O pulse and purge time. Saturation and self-limiting                                     |

| behavior occurs when GPC is 0.084 nm. (c) The thickness for a ZrO <sub>2</sub> film increases                                        |

| linearly with the number of cycles. [Reprinted from Sneh <i>et al.</i> 62]                                                           |

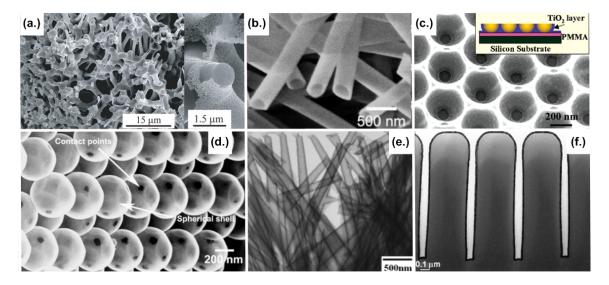

| Figure 3.3 ALD coating on various 3D nano-structures. (a) SEM carbon aerogel coated                                                  |

| with Ru (left) and a closer image (right) shows the broken carbon liagment and                                                       |

| nucleation clusters of Ru. [Reprinted from Biener <i>et al.</i> <sup>71</sup> ] (b) SEM image of Al <sub>2</sub> O <sub>3</sub>      |

|                                                                                                                                      |

| nanotubes created after deposition onto polyvinyl alcohol fibers and subsequent                                                      |

| removal of fibers, inset shows hollow center of nanotubes. [Reprinted from Peng et                                                   |

| al. 72] (c) SEM image of nanobowls fabricated using polystrene spheres on PMMA,                                                      |

| ion milling and etching of the spheres. [Reprinted from Wang et al. <sup>80</sup> ] (d) FESEM                                        |

| image of inverse opal structure fabricated by depositing TiO <sub>2</sub> onto silica spheres.                                       |

| [Reprinted from King et al. <sup>81</sup> ] (e) TEM image of ZrO <sub>2</sub> nanotubes fabricated with a                            |

| polycarbonate carbonate template. [Reprinted from Shin et al. <sup>82</sup> ] (f) TEM image of                                       |

| high aspect ratio SiO <sub>2</sub> coated with 20 nm ZrO <sub>2</sub> shows 100% conformality. [Reprinted                            |

| from Sneh $et al.$ 62] 30                                                                                                            |

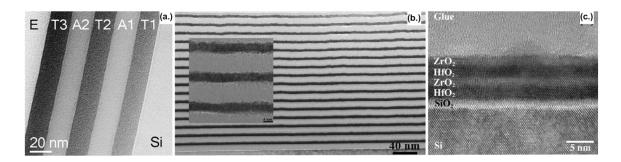

| Figure 3.4 (a) TEM image showing a stack of alternating TiO <sub>2</sub> and Al <sub>2</sub> O <sub>3</sub> on Si, where             |

| T1-3 indicates TiO <sub>2</sub> and A1-2 indicates Al <sub>2</sub> O <sub>3</sub> layers, and sharp interfaces are                   |

| observed. [Reprinted from Mitchell et al. <sup>92</sup> ] (b) SEM image of W/Al <sub>2</sub> O <sub>3</sub> stack on                 |

| [ 1] (1) 2=11 11120 0111120 01111120 011111120 011111111                                                                             |

| Si(100) (dark layers are W and lighter layers are Al <sub>2</sub> O <sub>3</sub> ), repeated 16 times and inse      |

|---------------------------------------------------------------------------------------------------------------------|

| of TEM image showing a higher resolution image of the stack and the sharp bilayer                                   |

| interfaces. [Reprinted from Fabreguette et al. <sup>94</sup> ] (c) HRTEM image of a nano-                           |

| laminate structure on SiO <sub>2</sub> containing HfO <sub>2</sub> and ZrO <sub>2</sub> layers shows no significant |

| intermixing of the two materials. Subsequent deposition of ZrO <sub>2</sub> induces                                 |

| crystallization of the previous HfO <sub>2</sub> layer and epitaxial growth of subsequent layers                    |

| follows. [Reprinted from Kim <i>et al.</i> <sup>98</sup> ]                                                          |

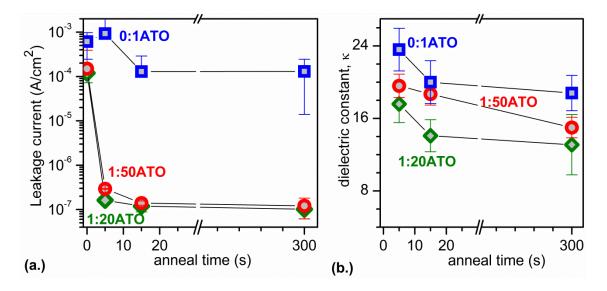

| Figure 3.5 Improving the performance of dielectric films with ALD. (a) Effect of doping                             |

| as a function of annealing time on leakage current densities at 1 MV/cm. Dramatic                                   |

| decrease in leakage currents after 5 s of annealing at 600°C for 1:50ATO and                                        |

| 1:20ATO (1:50 and 1:20 represent the supercycle ratio). (b) The dielectric constant                                 |

| for the films shown in (a) measured at 10 kHz.                                                                      |

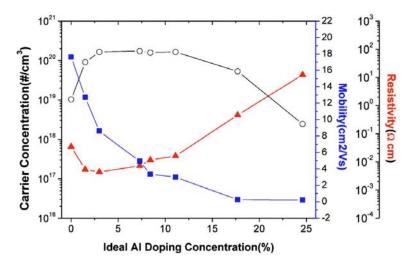

| Figure 3.6 Electrical characterization of AZO with various Al-doping concentrations                                 |

| showing low-level doping by ALD has improved electrical performance. Doping                                         |

| level ~2.5% has largest carrier concentration (-o-), increased mobility (-□-) and                                   |

| lowest resistivity (-Δ-). [Reprinted from Banerjee et al. 118]                                                      |

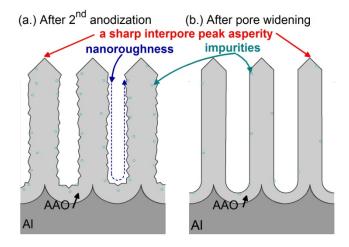

| Figure 4.1 Schematic of AAO cross-section depicting the challenges of using AAO as a                                |

| template for MIM capacitors. (a) Inherent interpore peak asperities cause premature                                 |

| breakdown, while nanoroughness of sidewalls and trapped impurities increase                                         |

| leakage current densities. (b) Pore widening smoothes sidewalls removes impurities                                  |

| but does not blunt interpore peak asperities and does not reduce interpore asperities                               |

| 43                                                                                                                  |

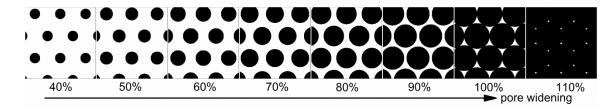

| Figure 4.2 Schematic top-view of AAO template, where white regions indicate oxide and                               |

| black regions indicate the pore openings. Pore widening increases the sidewal                                       |

| surface area, but widening beyond 100% degrades template integrity and stability. 44                                |

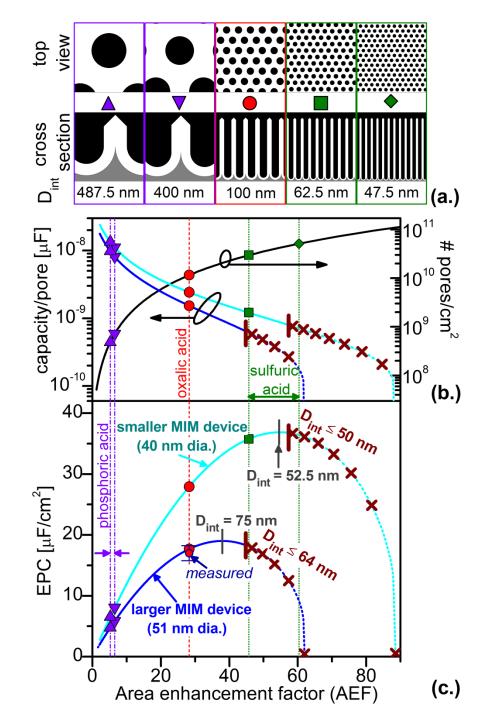

| Figure 4.3 (a) Schematics of various anodization chemistries. Anodization voltages from                             |

| left to right: 195, 160, 40, 25, and 19 V, where purple, red, and green symbols                                     |

| indicate phosphoric, oxalic, and sulfuric chemistries. (b) Increasing nanopore density                              |

| (i.e., reduced $D_{\rm int}$ ) increases the area enhancement factor (AEF) but narrower pores                       |

| reduce the capacity of each nanocapacitor. (c) Effective planar capacitance (EPC) for                               |

| various anodization chemistries and AEFs for $L = 1 \mu m$ , $D_p = 0.8 D_{int}$ , dielectric                       |

| constant, $\kappa = 9$ . The times symbols (×) indicate where the specified finite MIM layers                       |

| no longer fit within the pore diameters. 45                                                                         |

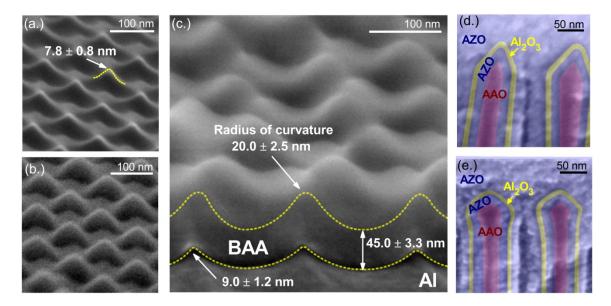

| Figure 4.4 (a) SEM image of first anodized Al surface shows scalloped texture. (b)                                  |

| Formation of a BAA layer (40 V) on the first anodized surface smoothes scallor                                      |

| asperities. (c) Cross-section of the BAA shows the radius of curvature above and                                    |

| below the BAA layer. (d) Cross-sectional SEM for MIM capacitor fabricated without                                   |

| BAA intermediate step, resulting in sharp interpore asperities. (e) SEM for MIM                                     |

| capacitor fabricated with BAA intermediate step, resulting in rounded interpore                                     |

| peaks                                                                                                               |

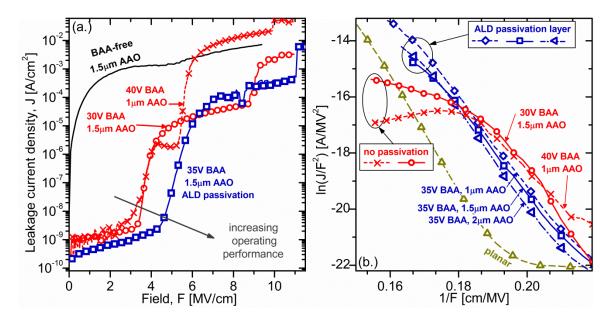

| Figure 4.5 (a) Representative IV curves for AZO-Al <sub>2</sub> O <sub>3</sub> -AZO capacitors fabricated in        |

| AAO templates showing influence of BAA smoothing layer and ALD TiN                                                  |

| passivation layer. (b) Linear segment indicate FN tunneling regime, which occurs for                                |

| wider ranges and higher fields with the introduction of an ALD TiN passivation layer                                |

| 53                                                                                                                  |

|                                                                                                                     |

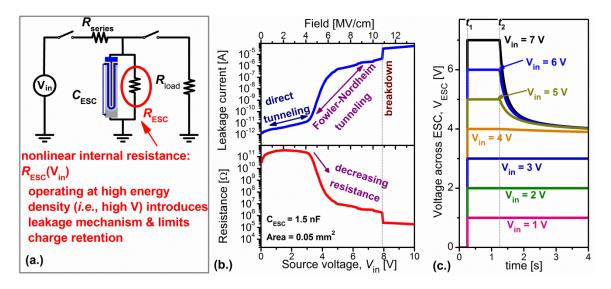

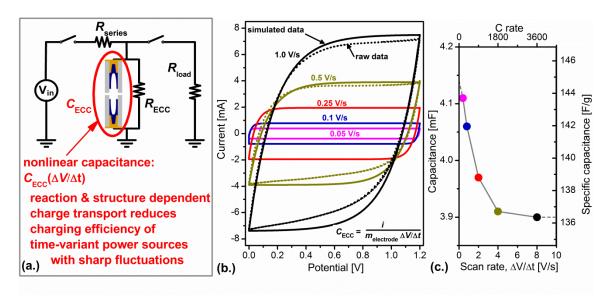

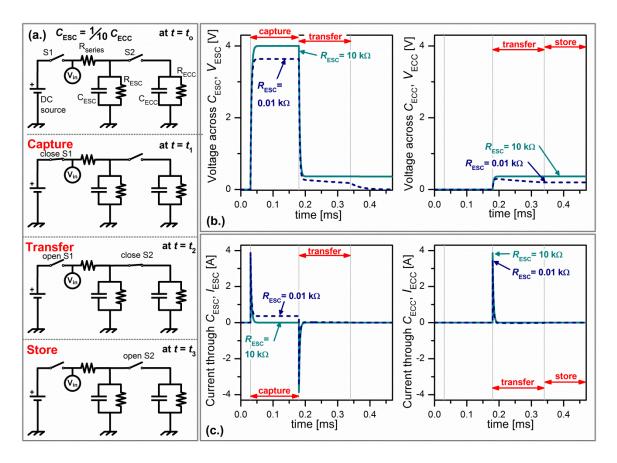

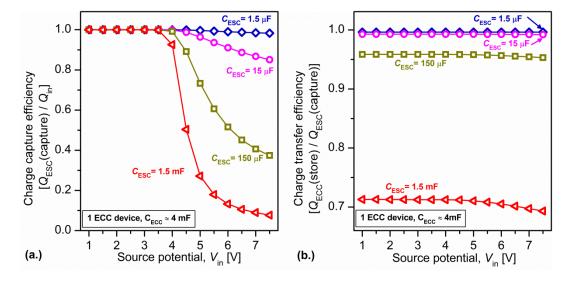

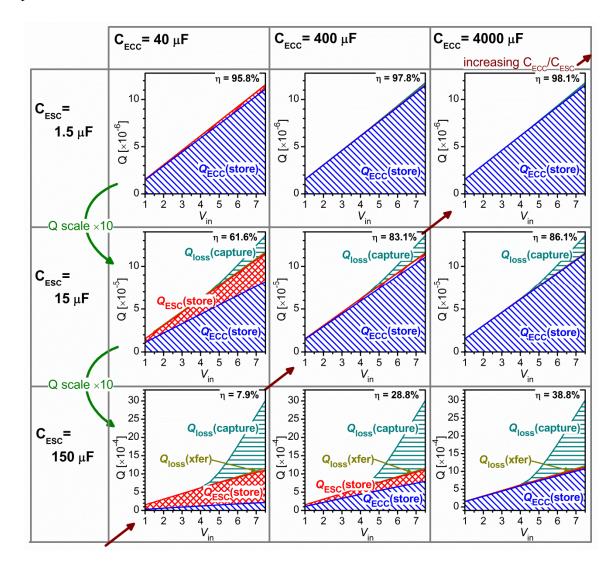

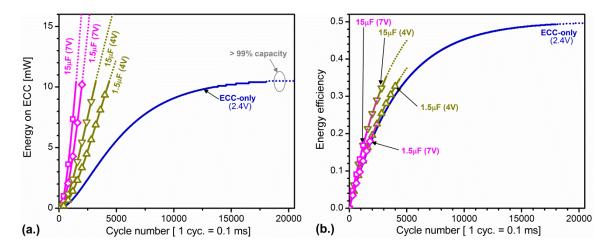

Figure 5.1 Electrostatic capacitor (ESC). (a) ESC as stand-alone device for supplying power/energy to an external load  $(R_{load})$  is not ideal for storing large amounts of energy for significant time. (b) Nonlinear leakage current as a function of  $V_{\rm in}$  due to various leakage mechanisms (top). Leakage is low with  $V_{in} \le 4 \text{ V}$  but rises > 4 V. The sharp rise in current (~8 V) indicates catastrophic breakdown. Nonlinear resistance as a function of  $V_{\rm in}$  shows drop in resistance > 4 V (bottom). (c) After  $t_2$ , the voltage across the capacitor,  $V_{ESC}$ , for  $V_{in}$  = 5-7 V drops rapidly until  $V_{ESC}$  drops to ~4 V, where the discharge rate, R<sub>ESC</sub>C<sub>ESC</sub>, becomes much slower as the internal Figure 5.2 Electrochemical capacitor (ECC) (a) ECC as stand-alone device for supplying power to an external load (R<sub>load</sub>) is not ideal when time-varying power sources, e.g., step-wave power sources drop ECC charging efficiency to 93% (capacitance at infinite rise in potential assumed to be 7.68 mF.) (b) Simulated cyclic voltammograms of one electrode ECC (top) from which the capacitance can be calculated, where  $\Delta V/\Delta t$  is the scan rate, i is the current, and me is the mass. Dotted lines show raw data for 1 V/s and 0.5 V/s. (c) The capacitance (left) and specific capacitance (right, melectrode=  $5.72 \times 10^{-2}$  mg) as a function of the  $\Delta V/\Delta t$  for a Figure 5.3 Simple hybrid ESC-ECC circuit operation (linear devices). (a) Circuit design of two capacitors with switching scheme and time (top to bottom) shown.  $R_{\rm ECC}$ remains relatively large while  $R_{\rm ESC}$  is either 10 k $\Omega$  (solid) or 0.01 k $\Omega$  (dashed). (b) The voltage across  $C_{\rm ESC}$  (left) and voltage across  $C_{\rm ECC}$  (right) during transfer and store stages ( $V_{\rm in} = 4$  V). The potentials at from  $t \approx 0.2$  ms to  $t_3$  are equal ( $V_{\rm eq}$ ) and its value largely depends on the ratio of  $C_{\rm ESC}$  to  $C_{\rm ECC}$ . Reducing  $R_{\rm ESC}$  results reduces voltage across ESC during capture and leaks away charge remaining on ESC during and after transfer. (c) Current through  $C_{\rm ESC}$  spikes and exponentially decays upon charging and reverses when charge is transferred to  $C_{\rm ECC}$  (left) where current through  $C_{\rm ECC}$  spikes at  $t_2$  (right). Figure 5.4 Hybrid circuit performance (nonlinear devices). (a.) Charge capture efficiency for various hybrid ESC-ECC circuits keeping  $C_{\rm ECC}$  fixed and varying  $C_{\rm ESC}$ as a function of  $V_{\rm in}$ . Capture efficiency increases with increasing CR ( $C_{\rm ESC} << C_{\rm ECC}$ ) since the  $R_{\rm ESC}$  scales as  $R_{\rm ESC}/N$  and is relatively constant at  $V_{\rm in} \leq 4$  V but drops with increasing  $V_{\rm in}$  for all designs. (b) Charge transfer efficiency as a function of  $V_{\rm in}$  for the various circuits shown in (a). Transfer efficiency drops with increasing N and with  $V_{\rm in} > 4 \text{ V}.$ Figure 5.5 Charge distribution in hybrid circuit (nonlinear devices). The collective charge distribution of various hybrid circuits with regions indicating the amount of charge stored on ECC after transfer, Q<sub>ECC</sub>(store), charge remaining on ESC after transfer, Q<sub>ESC</sub>(store), charge lost during transfer, Q<sub>loss</sub>(xfer), and charge lost during ESC capture, Q<sub>loss</sub>(capture), respectively). Rows have same C<sub>ESC</sub> value, columns have Figure 5.6 **Performance during charging**. Energy and energy efficiencies for charging the ECC component to 99% efficiency with 1.0% duty cycle. (a) For the same pulsing sequence, hybrid circuits charge significantly faster - 4.1 and 8.9x faster for

$1.5\mu F$  with  $V_{in} = 4V$ , and 5.6 and 12.2x faster for  $15\mu F$  with  $V_{in} = 7$  V. (b)

# Chapter 1: Introduction

### 1.1 Background and Motivation

Electrical energy storage solutions incorporated within power grids offer the ability to balance electricity generation from conventional sources (*i.e.*, coal, gas, oil) and renewable energy sources (*i.e.*, wind and solar) with electricity consumption and distribution for meeting instantaneous load demands.<sup>1,2</sup> Strong fluctuations in renewable energy generation have a vastly dynamic, time-variant profile.<sup>1</sup> Integrating energy storage systems into power grids can capture energy fluctuations to smooth the renewable energy generation profile and/or release the energy to supply additional power as needed.<sup>1,3</sup> Therefore, effective and efficient electrical energy storage solutions must be able to capture, store, and release energy quickly and in large quantities.

Energy storage devices and systems for managing energy supply and demands on the power grid should have the ability to respond quickly to abrupt fluctuations (high power density) and supply large amount of energy under abrupt or extended dips in source generation (high energy density). Conventional energy storage devices each rely on fundamentally different charging mechanisms (batteries, electrochemical capacitors and electrostatic capacitors shown in Figure 1.1). Batteries store electrical energy through faradaic chemical reactions occurring at electrode surfaces, providing very large charge capacities (high energy) but the response time is limited by the redox reaction rates (low power). Batteries are commonly used for storing energy as they have very large capacities but in applications where spurts of high power (fast discharging of the

battery) are needed, large currents are drawn increasing the temperature, degrading the capacity and reducing lifetime. For higher power applications, electrochemical capacitors can be used. In electrochemical capacitors (moderate energy, power) ionic charges build on the solid-electrolyte interface forming an electrical double layer capacitance, which responds faster than batteries.<sup>4</sup> However, electrochemical capacitors also experience some capacity degradation over their lifetime and their cost versus energy capacity make them a less competitive option to batteries.<sup>5</sup> Electrostatic capacitors are ideal for high power applications and find various uses in modern electronics<sup>4</sup> – ranging from trench capacitors in dynamic access memories for storing binary information, <sup>6,7</sup> integrated circuits for filtering out noise, micro-electro-mechanical systems driving sensors or actuators,<sup>8</sup> to power applications for power smoothing or conditioning. Electrostatic capacitors do not experience capacity fade and can rapidly transfer the equal and opposite non-faradaic surface charge stored at metal-insulator interfaces (high power) but the amount of charge stored is limited by the geometric and materials properties (low energy) and are typically not used for storing large amounts of energy.

Continuing research focuses on the development of innovative solutions for energy storage solutions that are affordable, efficient, compact/portable, have large gravimetric and volumetric energy densities and are able to respond quickly for balancing energy supply and demand. This proves to be a challenge as Figure 1.1 shows power and energy densities in conventional devices are often a trade-off. Nanostructured devices offer the potential to greatly improve the performance of electrical energy storage devices. The ability to control the dimensionality and morphology of heterogeneous nanostructures can result in faster charging rates by optimizing electronic and/or ionic

conduction pathways and diffusion lengths.<sup>10</sup> Additionally, nanostructures have high surface-to-volume ratios increasing the active surface area per unit volume for charge storage. Devices built on nanostructured foundations can be more efficient, reduce the overall system weight and size and with demonstrate improved performance (refer to Figure 1.1).<sup>11</sup> This dissertation focuses on nanostructuring electrostatic capacitors for increasing energy density for energy storage applications.

Figure 1.1 Ragone plot showing the power density and energy density of electrostatic capacitors, electrochemical capacitors and Li on batteries. Nanostructures have shown improvements in the energy density and/or energy density.

#### 1.2 Electrostatic capacitors for electrical energy storage

Material and geometric properties determine the capacitance of the electrostatic capacitor. In parallel plate electrostatic capacitors the capacitance, C, is given by  $C = \varepsilon_0 \kappa A/d$ , where  $\varepsilon_0$  is the permittivity of free space,  $\kappa$  is the dielectric constant of the insulator, A is the cross-sectional metal-insulator interface, and d is the thickness of the insulator. Methods of increasing the capacitance include reducing the thickness of the insulator, using a high- $\kappa$  insulating material, and increasing the surface area for charge storage. While these methods of increasing the capacitance are intended to increase the energy density, the methods should not limit or effect the maximum voltage that can be applied since energy, E, is given by  $E = \frac{1}{2} CV^2$ .

#### 1.2.1 Methods of increasing charge storage capacity

An insulating material of some nominal thickness ( $\geq 5$  nm) should be used to maintain an adequate energetic barrier to charge tunneling, otherwise, reducing the barrier thickness increases the probability for direct electron tunneling (*i.e.*, leakage currents) reducing the ability to retain charge over time. An insulating material with a higher dielectric constant,  $\kappa$ , can be used but these materials often have higher leakage currents as a result of reduced Schottky barrier height and catastrophic failure (breakdown) occurs at lower fields. An alternative method of increasing capacitance is to increase the cross-sectional area, A, but for planar capacitors this does not satisfy the electronics miniaturization trend. Instead, the challenge in increasing device capacity (while maintaining some nominal insulator thickness and reducing footprints) can be met with 3D substrate geometries to increase the surface area for charge storage per planar unit area. Roozeboom *et al.* Preported capacitors for radio frequency microelectronics in

an etched Si template (trenches 1.5 μm in diameter, spaced 3.5 μm apart, 150 μm deep using 30 nm oxide-nitride-oxide dielectric material) had 100× increase in capacitance over planar devices. Templates with higher aspect ratios and closer pore spacing (higher array density) have shown further improvements in areal capacitance, however, this can be a challenge using conventional lithography and etching techniques. Other templating fabrication techniques have relied on self-assembly processes for, potentially offering time and cost advantages over conventional lithographic techniques. For example, anodic aluminum oxide (AAO) templates are fabricated electrochemically and result in a self-aligned, highly periodic porous structure with few processing steps. A top-view scanning electron microscopy (SEM) image of an AAO template and cross-section SEM image of the pore base are shown in Figure 1.2(a) and Figure 1.2(b), respectively. Pores are hexagonally self-organized from the pore opening to pore base.

Figure 1.2 (a) Top-view SEM image of a porous anodic aluminum oxide template with hexagonally periodically spaced pores and (b) cross-section of the pore base showing highly aligned, vertical pore growth.

Shelimov *et al.*<sup>22</sup> reported electrostatic capacitors in an open-ended template with a ~250 aspect ratio had an areal capacitance of ~2.5  $\mu$ F/cm<sup>2</sup> using carbon as the top and bottom electrodes and boron nitride as the insulator (d = 70 nm,  $\kappa \approx 2.5$ ).<sup>22</sup> Other reports

have documented increased capacity using the porous oxide template as part of the insulating material. Lee *et al.*, reported coating a ~400 aspect ratio AAO template with  $TiO_2$  resulted in a capacity ~480  $\mu F/cm^2$ . While all showed an increase in the areal capacity, none reported leakage current or breakdown field measurements or described these as performance shortcomings.  $^{22-27}$

Leakage currents and breakdown fields of metal-insulator-metal (MIM) electrostatic capacitors in an AAO template were reported by Banerjee *et al.*<sup>28,29</sup> Figure 1.3(a)-(b) shows MIM electrostatic capacitors at the bottom and top regions of the AAO template, respectively.<sup>28</sup> The areal capacitance was found to be dependent on template thickness (~10 μF/cm² in a 1 μm thick template to ~100 μF/cm² in a 10 μm thick template), while the leakage current densities (5×10<sup>-9</sup> A/cm² at 3 MV/cm) and breakdown fields (~4 MV/cm) were independent of template thickness.<sup>28</sup> Even though the breakdown field was ~3× lower than the expected strength of the insulator an order of magnitude increase in the energy density (~0.7 Wh/kg) over conventional electrostatic devices was reported.<sup>28</sup>

Figure 1.3 (a) SEM images of MIM capacitor fabricated in AAO template at the pore base and (b) at the pore opening show conformal deposition of the TiN-Al<sub>2</sub>O<sub>3</sub>-TiN metal-insulator-metal layers. [Reprinted from Banerjee *et al.*<sup>28</sup>].

#### 1.2.2 Influence of nano-template on electrical performance

The premature breakdown reported by Banerjee *et al.*<sup>28,29</sup> was attributed to the interpore sharp asperities located at the pore opening (refer to Figure 1.3(b)). These asperities are locations with very small radii of curvature, which cause localization of an enhanced electric field and result in premature (low field) electrical breakdown. This significantly restricts the maximum voltage and field usable for energy storage. An effective technique able to smooth the regular interpore peaks is necessary to improve the overall performance. Breakdown fields near the strength of the insulator could further improve the energy density close to an additional order of magnitude.

In the work reported by Banerjee *et al.*,  $^{28,29}$  a 15 nm passivation layer coated the porous template (reducing the initial available 80 nm pore diameter to 50 nm) prior to the MIM deposition to act as a passivation layer and to smooth the inherently sharp asperities. This smoothing effect was reported by Cleveland *et al.*,  $^{30}$  where a surface consisting of sharp ridges (height  $\sim$  42 nm) resembling the interpore peaks shown in Figure 4.2(a) could be smoothed after coating the rough surface with an atomic layer deposition (ALD) film shown in Figure 1.4(b).  $^{30}$  A dramatic reduction in the estimated surface area to the planar equivalent area was not found until after a film  $\sim$  3× thicker than the one deposited by Banerjee *et al.*  $^{29-31}$  Introducing a thicker passivation layer to smooth the nanoroughness on the template would introduce design constraints and complexities on the subsequent MIM layers.

Figure 1.4 (a) Peak asperities on an rough surface resembling the interpore peaks on the AAO template and (b) introducing several layers of ALD on top of a non-planar surface smoothes the surface. [Reprinted from Cleveland *et al.*<sup>30</sup>].

#### 1.2.3 Ultra-thin metal-insulator-metal layers

The pore radius defines the maximum thickness of the MIM layer stack for fabricating the full device within each pore, where the total thickness of the three active layers should not exceed the radius of the pore. Thin metallic layers (~ 10 nm) can be deposited having the same low-resistivity of the bulk material but decreasing the thickness of the metallic layers (< 10 nm) may reduce the conductivity of the film.<sup>32</sup> Introducing significant electrode series resistance limits the power, P, since  $P = V^2/R_e$ , where  $R_e$  is series resistance. Therefore, not only does the insulator layer need to be of some nominal thickness, the conducting layers must also be of some nominal thickness in order to maintain the high power capability inherent to the electrostatic capacitors. Furthermore, process capability is very important since few approaches have the thickness control and conformality needed to produce ultrathin uniform layers inside very high aspect ratio nanopores.

While the insulator will be of some nominal thickness, some reduction in its leakage resistance is expected with increasing the applied voltage. As charge

accumulates the energy bands shift, causing the insulating energetic barrier to become trapezoidal and increasing the probability for electron tunneling at these thinner barrier regions, referred to as Schottky tunneling. As template nanoengineering extends the voltage threshold of the device to higher potentials, the charge retention as affected by reduced leakage resistance should be analyzed. Using the electrostatic capacitor for charge capture and transferring charge to an alternative energy storage device for long-term charge storage may provide an electrical energy storage hybrid solution with fast response time and large charge storage.

#### 1.2.4 Basic processing sequence of fabricating nano-electrostatic capacitors

The basic processing sequence of the MIM electrostatic capacitor devices is shown in Figure 1.5(a). Anodizing high-purity aluminum fabricates the porous template. The top conducting layer (*i.e.*, top electrode) is patterned by conventional photolithography methods to create 250 µm diameter electrode pads, creating several hundred devices per sample and each device wires more than 5 million nanocapacitors together in parallel per microcapacitor device. Devices are characterized (Figure 1.5(b)) with current-voltage (IV) sweeps were measured with a HP 4145B for determining leakage currents and breakdown fields and capacitance-voltage (CV) measurements to determine the capacitance per planar unit area with an Agilent 4980A LCR meter at 20 Hz applying 100 mV (AC). Analytic SEM was performed with a Hitachi SU-70 to verify the structure the device.

Figure 1.5 (a) Left to right: shows process flow of anodizing the sheet of the aluminum for creating a massive porous array. Within a 13 mm diameter window more than 5 billion pores are available for use as nanocapacitors. A photograph shows the AZO electrodes that have been patterned for electrical characterization and testing. (b). Schematic of the AAO template on Al with patterned AZO top electrodes (green) are individually contacted when probing the top electrode (left). A simplified schematic shows how contact is made to the bottom and top electrodes (right).

#### 1.3 Overview of Dissertation

#### 1.3.1 Objectives

The following objectives focus on improving the energy density of electrostatic capacitors (ESC) and the role of this device in energy storage applications.

1. Identify effective nano-engineering strategies for modifying the nanotopography of the porous anodic aluminum oxide (AAO) template, increasing breakdown fields to the strength of the insulator,  $E = \frac{1}{2} CV^2$ .

- 2. Develop and simulate a dynamic, experimentally derived ESC model that depicts the nonlinearities of the ESC and determine its application in energy storage systems.

- 3. Expand the model to simulate an ESC-electrochemical capacitor hybrid circuit. Determine methods for efficiently capturing, transferring and storing charge and demonstrate high-energy high-power capability.

#### 1.3.2 Outline

Chapter 2 discusses the anodic aluminum oxide fabrication process, the various properties of the template and methods in which these properties may be modified, along with widely accepted theoretical formation and ordering mechanisms. The atomic layer deposition (ALD) process used to deposit the MIM layers is discussed in Chapter 3. The basic processing sequence and various examples of nanostructures fabricated using ALD in literature are presented. Combining these two key technologies to fabricate electrostatic capacitors, Chapter 4 will discuss optimization of the electrostatic device configuration and the template nanoengineering strategy significantly increasing the breakdown field, and thus improving the energy density to 1.5 Wh/kg. The practical applications of the nano-electrostatic device are presented in Chapter 5, focusing on the combination of an electrostatic capacitor with an electrochemical capacitor to create a nano-hybrid circuit able to achieve both high power and high energy. Chapter 6 will summarize the major research findings and provide discussion on future work and challenges.

# Chapter 2: Anodic Aluminum Oxide (AAO)

#### 2.1 Introduction

Anodization of aluminum for protective coatings has been known since the early  $1920s.^{33}$  In the past decades, research has focused on creating a highly-regular, highly-ordered porous alumina oxide membrane because it can serve as a template for creating a very high density array of nanotubes, nanowires or nanorods for applications including photovoltaics,  $^{34,35}$  catalysts,  $^{34,36}$  sensors,  $^{34,37}$  chemical and biological separation,  $^{37.39}$  and electronic and magnetic devices.  $^{40,41}$  The aspect ratio of the pores is determined by the anodization conditions and the length of the anodization. The top-view and cross-section schematics shown in Figure 2.1(a) and Figure 2.1(b), respectively, indicate the pore diameter,  $D_p$ , interpore spacing,  $D_{int}$ , and thickness also referred to as the pore depth, L. The self-aligning, self-assembly formation process results in uniform hexagonally spaced nanopores that can range from 50 - 500 nm. Figure 2.1(c)-(e) shows transmission electron microscopy (TEM) images of various templates all having similar symmetry with  $D_p$  and  $D_{int}$  increasing from Figure 2.1(c) to Figure 2.1(e).

The electrochemical process for fabricating anodic alumina oxide (AAO) templates requires few processing steps, whereas conventional template fabrication techniques require several complex and challenging lithographic processes and/or etching chemistries for fabricating high aspect ratio features. Additionally, the array size of the AAO membrane can be scaled without the need to additional equipment or sensitive measurements for extended template uniformity.

Figure 2.1 (a) Top-view schematic of ordered AAO and (b) cross-section schematic of AAO template, where  $D_{\rm int}$  is the interpore spacing,  $D_{\rm p}$  is the pore diameter and L is the pore depth. Top-view TEM images of AAO templates anodized under various anodization chemistries, resulting in different  $D_{\rm int}$  and  $D_{\rm p}$  of (c) 66.3 nm and 24 nm, (d) 105 nm and 31 nm, and (e) 501 nm and 158.4 nm, respectively. [c-e are reprinted from Nielsch *et al.*<sup>42</sup>]

# 2.2 Structure properties of AAO

Porous AAO can be formed under either galvanostatic (constant current) or potentiostatic (constant voltage) conditions. Potentiostatic conditions provide more control over template dimensions and are the focus of the discussion below.<sup>45</sup>

The discrete ordering regimes in which the highly-ordered template is formed depends largely on the electrolytic solution and the anodizing potential,  $V_{\text{anod}}$ . <sup>45</sup> Commonly used anodization chemistries are as follows: sulfuric acid with  $V_{\text{anod}}$  between 19-25 V, <sup>42,46,47</sup>, oxalic acid with V<sub>anod</sub> at 40 V, <sup>20,42</sup>, and phosphoric acid with V<sub>anod</sub> between 160-195 V. <sup>21,42,46</sup>. Figure 2.2(a) shows a linear relationship between anodization potential and interpore spacing,  $D_{\text{int}}$ , can be estimated by  $V_{\text{anod}}[V] \approx 2.5 \times D_{\text{int}}[\text{nm}]$ . Given this relationship the pore density of the hexagonally spaced arranged cells can be calculated by  $2/(3^{\frac{1}{2}} \times (D_{\text{int}}[\text{nm}] \times 10^{-7})^{-2})$ . Figure 2.2(b) plots the pore density as a

function of anodization voltage and interpore spacing, where the inset schematics represent the relative spacing for each anodization condition.

Figure 2.2 (a) Dependence of anodization voltage on interpore spacing,  $D_{\rm int}$ , for various ordering regimes (as indicated by acids). [Adapted from Lee *et al.*<sup>40</sup>] (b) The effect  $D_{\rm int}$  on the pore density (shown for mild anodization conditions) has an inverse relationship, bottom axis. The associated  $V_{\rm anod}$  is shown on the top axis. Insets represent the relative interpore spacing.

# 2.3 Fabrication a highly ordered porous AAO nanotemplate

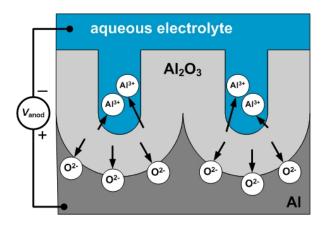

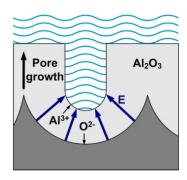

Two reaction mechanisms are necessary for the formation of porous AAO: (1) ejection of mobile Al<sup>3+</sup> ions at the oxide-electrolyte interface into the electrolyte solution and (2) migration of OH<sup>-</sup>/O<sup>2-</sup> ions towards the metal-oxide interface, represented in the schematic in Figure 2.3. The ejection of Al<sup>3+</sup> is associated with the dissolution of the oxide at the oxide-electrolyte interface where the following reaction occurs:

$$Al_2O_3 + 6H^+ \rightarrow 2Al^{3+}(aq) + 3H_2O$$

The migration of OH<sup>-</sup>/O<sup>2-</sup> is associated with oxide formation at the metal-oxide interface, where the following reaction takes place:

$$2A1 + 3O^{2} \rightarrow Al_2O_3 + 6e^{-}$$

During steady-state pore formation, these reactions are balanced, resulting in equal dissolution and oxidation rates.

Figure 2.3 Schematic representing the ionic movement responsible for the dissolution of  $Al_2O_3$  by ejecting  $Al^{3+}(aq)$  into solution and oxidation of Al through the migration of  $OH^2/O^{2-}$  to the metal-oxide interface.

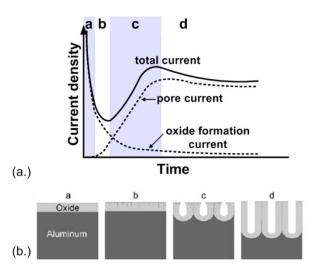

The anodization process for pore formation can be divided into 4 stages as reflected in the shape of the current density versus time plot. Figure 2.4(a) shows the current density as a function of time (stages a, b, c and d)<sup>45,48</sup> and Figure 2.4(b) schematically represents the structure of the oxide at each stage. 45 Initially (stage a), the ionic OH<sup>-</sup>/O<sup>2</sup>-conduction is very high and results in the formation of an oxide barrier layer. The oxide formation current dominates the total current and decreases as the oxide layer thickens. During the second stage (stage b), cracks randomly propagate through the oxide barrier layer. Localized current flows to repair the crack, enhancing dissolution and oxide formation through this point. During stage b, the oxide formation current continues to decrease while the pore formation current begins to rise, resulting in a minimum total current, where stage c begins. The enhanced ionic conduction causes the pore formation current to create the pore cells causes and breakdown the initial oxide barrier. At the final stage (stage d), pore formation and growth begins as the current at the pore bases becomes uniform. Steady-state pore growth results in balanced and continued dissolution of the oxide near the oxide-electrolyte interface and formation of the oxide near the metal-oxide interface.

Figure 2.4 (a) Current density versus time profile for potentiostatic anodization of Al, showing the current contribution from oxide formation and pore formation. [Adapted from Hoar *et al.*<sup>48</sup> and Eftekhari *et al.*<sup>45</sup>] (b) Oxide formation at various stages. Stage a: forms an oxide barrier coating on the Al surface. Stage b: cracks propagate through oxide barrier. Stage c: pore cells form and break down barrier oxide. Stage d: lateral and steady-state pore growth. [Reprinted from Eftekhari *et al.*<sup>45</sup>]

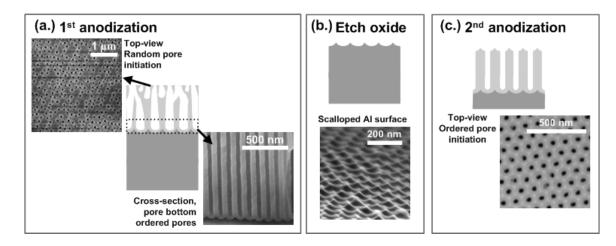

Because pore initiation is random and as some pores continue to propagate while others are hindered by more dominating pores and the top of the porous membrane is random but the pores align near the base with continued anodization. Highly ordered templates (aligned pores from the top to the pore base) can be fabricated following a two-step anodization procedure. Figure 2.5(a) shows the first anodization oxide. It generally requires that the first anodization forms 30-40 µm of the porous oxide before optimum and uniform ordering is achieved at the pore base. Removing the oxide formed during first anodization leaves the Al surface with a scalloped texture (Figure 2.5(b)). This texturized surface results in highly ordered pores from the top to the base with subsequent anodization (Figure 2.5c).

Figure 2.5 Schematics of AAO processing sequence for ordered AAO templates: (a) first anodization has random pore spacing at pore top (SEM, top left) and ordered pores at pore bottom (SEM, bottom right), (b) etch oxide for scalloped Al surface (SEM bottom), and (c) second anodization for ordered template.

Pre-texturing the surface with the scalloped texture is necessary for creating an ordered template from top to bottom. Upon second anodization the current initially localizes at the ridges forming a non-uniform barrier oxide – oxide is thicker at the ridges and flattens the metal-oxide interface. Shimizu *et al.*<sup>49</sup> and Thompson *et al.*<sup>50</sup> reported the growth of non-uniform oxide introduces stress within the oxide material between the thinner and thicker oxide regions, causing successive crack-and-heal events until the current concentrates at the (bottom) thinner oxide locations, where dissolution and oxidation continue and lateral pore formation begins.<sup>49,50</sup>

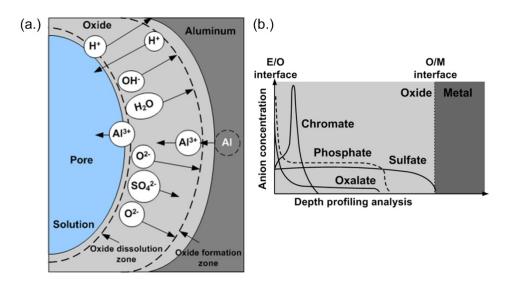

During the formation of the oxide anions from the electrolytic solution get trapped within the porous oxide sidewalls. Figure 2.6(a) shows the variety and movement of ions present during anodization in sulfuric acid.<sup>45,51</sup> The depth and concentration of anion incorporation depends on the mobility and conductivity of the species. Figure 2.6(b) shows the relative incorporation of various electrolytic ion species incorporations within the pore base.<sup>45</sup> Sulfate ions are nearly equally distributed through the entire oxide layer, while phosphate and oxalate anion concentrations remain equally distributed through

about <sup>3</sup>/<sub>4</sub> of the oxide layer and rise sharply near the oxide-electrolyte interface. Chromate ions reach a maximum concentration about <sup>1</sup>/<sub>4</sub> through the oxide formation layer from the electrolyte-oxide interface.

Figure 2.6 (a) Schematic representing the ionic conduction during steady-state pore growth and mobility of electrolytic anions through the cross-sectional barrier layer. [Adapted from Patermarakis *et al.*<sup>51</sup> and Eftekhari *et al.*<sup>45</sup>] (b) Anion incorporation as a result of electrolytic solution at pore base. [Adapted from Eftekhari *et al.*<sup>45</sup>]

# 2.4 Theories for self-alignment and ordering mechanisms of AAO

Two well accepted theories which explain the self-alignment phenomenon are the enhanced field-assisted mechanism and the volume expansion between alumina and aluminum are presented below. Several theories on the lateral growth of self-aligned pores have been proposed, and can be found elsewhere.<sup>45</sup>

#### 2.4.1 Enhanced field-assisted mechanism

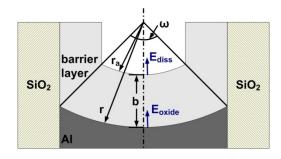

Chen *et al.*<sup>52</sup> proposed lateral pore growth mechanism occurs from the enhanced field at the scalloped pore base. Figure 2.7 represents the electric field and pore geometry of the pore base, showing the angle of the pore base,  $\omega$ , the radius of curvature

of the pore base at the metal-oxide interface, r, and the radius curvature of the pore base at the electrolyte-oxide interface,  $r_a$ , and the thickness of the barrier layer, b.

Figure 2.7 Schematic for the field-enhanced pore formation mechanism. The field at the oxide-electrolyte interface,  $E_1$ , and the field at the metal-oxide interface,  $E_2$ , are shown. [Adapted from Chen *et al.*<sup>52</sup>]

This theory suggests the self-alignment is a result of the shape of the barrier oxide layer determining the local electric fields responsible for porous oxide formation – the local electric field at oxide-electrolyte interface  $(r = r_a)$  is responsible for dissolution and the local field at the oxide-metal interface  $(r = r_a + b)$  is responsible for oxidation. The field across the barrier layer, E(r), can be expressed as  $E(r) = J/\sigma$  where J is the current density  $(J = I/[\omega r^2]$ , and I is current,  $\omega$  is the angle of the scalloped barrier region). Solving for the constant voltage across the oxide, V, which is equal to the integral of E(r) with limits from  $r_a+b$  to  $r_a$  and where  $E(r) = I/(\sigma \omega r^2)$ , puts the electric field in terms of r,  $r_a$  and b is given by the following equation:

$$E(r) = \frac{r_a \cdot (r_a + b)}{r^2} \frac{V}{b}$$

The local electric field at the top of the pore base (oxide-electrolyte interface) proportional to the rate of oxide dissolution where  $r = r_a$ ,  $E_{diss}(r = r_a)$  is given by

$$E_{diss}(r_a) = \frac{(r_a + b)V}{r_a}$$

The local field at the bottom of the pore base (oxide-metal interface) proportional to the rate of oxide formation where  $r = r_a + b$ ,  $E_{\text{oxide}}(r = r_a + b)$  is given by

$$E_{oxide}(r_a + b) = \frac{r_a}{(r_a + b)} \frac{V}{b}$$

Under steady-state conditions, the rate of dissolution and rate of oxidation are equal. Therefore, the dimensions of the  $r_a$ , b and r should remain constant under steady-state formation. If, however,  $r_a$  decreases (decreasing radius of curvature at electrolyte-oxide interface),  $E_{\rm diss}(r_a)$  will increase to speed the rate of dissolution. If  $r_a$  increases (increasing the radius of curvature at the at the electrolyte-oxide interface),  $E_{\rm diss}(r_a)$  will decrease to slow the dissolution of the oxide. A similar effect is observed for non-equilibrium values of b. If b becomes large,  $E_{\rm oxide}(r_a+b)$  will decrease to slow the rate of oxidation at the oxide-metal interface. Conversely, if b becomes small,  $E_{\rm oxide}(r_a+b)$  will increase and the rate of oxidation increases.

Chen et al.<sup>52</sup> also described the self-correcting nature of uniform porous dimension growth by the angle of the scalloped barrier region,  $\omega$ . Because E(r) is inversely proportional to  $\omega$ , if  $\omega$  is less than the equilibrium value (small cell size), then E(r) must increase until the value of  $\omega$  is restored to its larger equilibrium value, causing the size of the pore cell to increase. In a scenario where  $\omega$  is small and a competing neighboring pore cell has a maximum  $\omega$ , ( $\omega = 180^{\circ}$  flat pore base) then E(r) in the flat base cell will be smaller than E(r) in the cell base with  $\omega \neq 180^{\circ}$ . Lateral pore growth will stop in the flat bottom base cell where  $\omega = 180^{\circ}$  and continue in the cell where  $\omega \neq 180^{\circ}$ .

#### 2.4.2 Mechanical forces by volume expansion

Jessensky *et al.*<sup>53</sup> and Nielsch *et al.*<sup>42</sup> reported hexagonally, self-organized pores occur from the moderate volume expansion during the conversion of aluminum to alumina leading to mechanical stresses which provide repulsive forces between neighboring cells, forcing the lateral upward growth of the pore sidewalls. A schematic of this mechanism is shown in Figure 2.8.<sup>53</sup>

Figure 2.8 Schematic for the volume-expansion formation mechanism. The electric field is concentrated at the base of the pore, causing the sidewalls to move upward. [Adapted from Jessensky *et al.*<sup>53</sup>]

The volume expansion,  $\Delta$ , (also known as the Pilling-Bedworth Ratio) is defined as the ratio of volume of the oxide produced during anodization,  $V_{\text{oxide}}$ , to the volume of the aluminum consumed during oxidation,  $V_{\text{Al}}$ . The volume of the oxide,  $V_{\text{oxide}} = M_{\text{oxide}} / \rho_{\text{oxide}}$ , where  $M_{\text{oxide}}$  is the molar mass of the oxide, and  $\rho_{\text{oxide}}$  is the density of the oxide  $(\rho_{\text{oxide}} = 3.2 \text{ g/cm}^3)$ . The volume of the total aluminum consumed  $V_{\text{Al}} = (2\text{-Al atoms/Al}_2O_3)M_{\text{Al}} / \rho_{\text{Al}}$ , where  $M_{\text{total}}$  is the molar mass of the oxide, and  $\rho_{\text{Al}}$  is the density of the oxide  $(\rho_{\text{Al}} = 2.7 \text{ g/cm}^3)$ . Therefore, the volume expansion can be determined by

$$\Delta = \frac{M_{oxide} \cdot \rho_{Al}}{2M_{Al} \cdot \rho_{oxide}} f$$

The factor f takes into account the fraction of  $Al^{3+}$  ions contributing to the oxide formation, equal to  $[1-(\#Al^{3+}\ ions)/(total\ Al\ atoms)]$  since the formation process requires dissolution of the oxide by ejecting mobile  $Al^{3+}$  ions into the electrolytic solution. If all of the aluminum consumed is converted to oxide  $f\approx 1$  and a maximum volume expansion ratio will occur ( $\Delta\approx 1.6$ ). It was shown that  $f\approx 0.77$  (meaning 23% Al atoms are ejected into the electrolytic solution as  $Al^{3+}$ ), results in the optimum hexagonally, self-ordered structure with large ordering domain size, and thus  $\Delta\approx 1.2$ . If  $1.6>\Delta>1.2$ , the volume expansion is large and results in irregular growth, structural defects, and reduced ordering domain size. 42.45.53 If a greater amount of  $Al^{3+}$  ions are ejected into solution during anodization  $\Delta<1.2$ , repulsive forces between neighboring cells is not large enough to promote ordering creating disordered pore arrays.

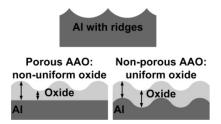

### 2.5 Formation of non-porous anodic alumina

The formation of non-porous anodic alumina referred to as barrier anodic alumina, BAA, occurs when aluminum is anodized in a neutral electrolytic solution. This is different to the formation of porous AAO, which occurs from anodizing in an acidic solution. The key difference in non-porous oxide formation mechanism is that Al<sup>3+</sup> ions are not outwardly ejected into the electrolytic solution. Rather, mobile Al<sup>3+</sup> ions heal any cracks at the oxide-electrolyte interface.<sup>33</sup> In a neutral solution there are more deprotonated species *i.e.*, anions, which can react with mobile Al<sup>3+</sup> ions at the oxide-electrolyte interface and can form a complex oxide.<sup>54</sup> The oxide formation that forms is uniform, unlike the initial barrier layer formed for fabricating the porous oxide.<sup>49,50</sup> A schematic in Figure 2.9 represents the barrier layer formation on an aluminum surface

containing ridges for porous and non-porous anodization conditions. The barrier layer formed in the non-porous structure is uniform maintaining a non-flattened profile at the metal-oxide interface, unlike the barrier oxide layer formed during porous AAO anodization is non-uniform and flattens the metal-oxide interface.

Figure 2.9 Schematic representing the difference in oxide growth during initial Al anodization for porous AAO and non-porous AAO when ridges in Al surface are present. The oxide growth formed prior to porous AAO growth is non-uniform (left), while the oxide formed with an anodization chemistry for creating non-porous films, barrier anodic aluminum (BAA), is uniform.

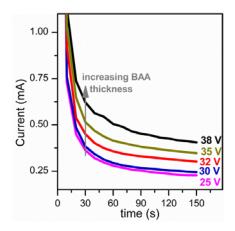

During anodization of a non-porous layer, the current versus time continues to exponentially decay with time<sup>55</sup> because the ionic conduction decreases with barrier film thickness. Figure 2.10 shows current-time curves for the formation of BAA on aluminum at various  $V_{\text{anod}}$ . Increasing  $V_{\text{anod}}$  increases the ionic conduction corresponding to the formation of a thicker oxide layer.

Figure 2.10 Current versus time for forming a BAA layer in an aqueous neutral electrolytic solution for 150 s. Increasing  $V_{\rm anod}$  increases the current and thus, increases the thickness of the barrier anodic aluminum (BAA), or non-porous oxide film thickness. For all current-time curves, the continual decrease in current with time indicates no porous oxide formation.

### 2.6 Methods for fabricating AAO templates

Template preparation starts with electropolishing high purity 99.99% Alfa-Aesar Al sheets in 1:5 perchloric acid to ethanol solution. Porous AAO templates were fabricated following a two-step anodization procedure in 0.3 M oxalic acid at 40 V. Templates were highly ordered, with hexagonally spaced pores ( $D_{\rm int} \sim 100$  nm and  $D_{\rm p} \sim 40$  nm), resulting in pore densities of  $\sim 1.15 \times 10^{10}$  pores/cm<sup>2</sup>. Initial pore diameters were widened to  $D_{\rm p} \sim 80$  nm in a 1:1 NH<sub>4</sub>OH:H<sub>2</sub>O solution. The final pore diameter can be controlled as a function of pore depth, L, and etching time, t. It was found that the pore depth does not contribute largely to the etching rate (assuming L  $\leq 10$  µm) and the final pore diameter can be estimated more simply by  $D_{\rm p}$  [nm]  $\approx 2.5$  [nm/min]  $\times$  t [min].

The non-porous oxide, BAA was formed by anodizing an Al surface in a 2:1 KOH:oxalic acid electrolytic solution. Forming BAA on a first anodized Al surface altered the surface texture. (see Chapter 4.)

# Chapter 3: Atomic Layer Deposition (ALD)

#### 3.1 Introduction

Atomic Layer Deposition (ALD) was developed as a method for depositing thin, defect-free, high-purity films.<sup>56</sup> It has become a key processing technique in the display and microelectronics industries where miniaturization has required precise atomic control of film thickness and conformal deposition.<sup>57</sup> Unlike Chemical Vapor Deposition (CVD), where precursors react in the gas-phase, ALD is a cyclic and self-limiting process based on sequential binary surface reactions.<sup>30,58-61</sup> ALD can be used to coat a variety of substrate materials (with typically amorphous) films because it is a low temperature process. Various recipes can be deposited consecutively since each precursor is introduced separately and many recipes have a wide deposition temperature window. Furthermore, this process is scalable, able to coat large and/or multiple substrates.<sup>61</sup>

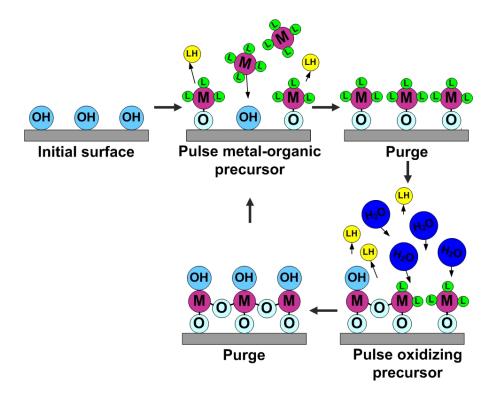

#### 3.1.1 Processing sequence

Figure 3.1 shows an example of an ALD sequence for depositing a binary metal-oxide compound,  $MO_2$  (M represents a metal and O is oxygen), onto a hydroxyl functionalized surface. The basic deposition sequence includes the 4 following basic steps, also referred to as two half-cycles: (1) Exposure of the first precursor,  $ML_4$  (L represents a ligand group, e.g.  $N(CH_3)_2$ ), fully saturating the surface by reacting with all available surface sites and forming byproducts. The following surface reaction occurs:

$$OH^* + ML_4 \rightarrow O-ML_3^* + LH$$

Where \* indicates the surface group. The reaction results in a -ML<sub>3</sub> terminated surface and with LH as the byproduct. (2) A system purge removes remaining unreacted precursor and LH byproducts, completing the first half-cycle. (3) Exposure of a second oxidizing precursor, H<sub>2</sub>O, reacts at the remaining metal-ligand sites and the following reaction occurs:

$$O-ML_3* + 2H_2O \rightarrow O_2-M(OH)* + 3LH$$

(4) A second purge removes remaining unreacted precursor and byproducts from the system, completing the second half-cycle and one full cycle. The surface is –OH terminated (same to initial surface). The 4 basic steps are repeated with subsequent cycling, adding one monolayer of MO<sub>2</sub> film per cycle.

Figure 3.1 Schematic of one complete metal-oxide ALD cycle (clockwise): initial hydroxyl functionalized surface, pulsing a metal-organic precursor ( $ML_4$ ) reacts with surface sites, purge removes unreacted precursor and byproducts,  $H_2O$  pulse reacts with remaining ligands attached to metal site, final purge removes any unreacted precursor and byproducts. At the end of one cycle, one monolayer of material  $MO_2$  uniformly and conformal coats the entire surface.

The pulse-purge half-cycles must be optimized to ensure conformal coating of the substrate surface. The following example shows optimized pulse-purge half-cycles for deposition of  $Al_2O_3$  with trimethylaluminum (TMA) and  $H_2O$  precursors, resulting in a growth rate per cycle (GPC) of 0.084 nm.<sup>62</sup> Figure 3.2(a) shows the effect of the first half cycle pulse-purge lengths on deposition thickness per cycle (TMA precursor).<sup>62</sup> Increasing the TMA pulse increases GPC until ~100 ms and then GPC plateaus indicating full saturation of the substrate surface and that the half-cycle is self-limiting. Increasing TMA purge time, however, causes GPC to fall before it plateaus where there is sufficient time for removing excess molecules (high GPC indicates somewhat of a CVD reaction). Figure 3.2(b) shows similar trends of the pulse and purge time on the GPC for the  $H_2O$  half-cycle with GPC plateauing at longer pulse-purge lengths than for the TMA half-cycle.<sup>62</sup> Recipes with self-limiting pulse-purge half-cycles result in linear monolayer growth with cycle number, as shown in Figure 3.2(c) for a  $ZrO_2$  film thickness as a function of cycle number.

Figure 3.2 The effect of pulse and purge time on deposition per cycle of an  $Al_2O_3$  film (tri-methyl aluminum, TMA, and  $H_2O$  precursors). (a) Effect of TMA pulse and purge time and (b) effect on  $H_2O$  pulse and purge time. Saturation and self-limiting behavior occurs when GPC is 0.084 nm. (c) The thickness for a  $ZrO_2$  film increases linearly with the number of cycles. [Reprinted from Sneh  $et\ al.^{62}$ ]

#### 3.1.2 Applications

A variety of materials can be deposited using ALD such as HfO<sub>2</sub>, ZrO<sub>2</sub>, TiO<sub>2</sub> dielectrics for high-κ applications, <sup>58,60</sup> transition metal nitrides like TiN and TaN for metallization barriers and gate metals, <sup>60,63,64</sup> and continuing development of precursors and recipes for depositing metals, like W and Ru. <sup>61,65</sup> The range of materials that can be deposited by ALD makes this a versatile deposition process in the semiconductor industry creating devices like dynamic access memory (DRAM), field-effect transistors (FET) and non-volatile memory (NVM) devices. <sup>58</sup> ALD is also used in the fabrication of transparent thin film transistors, sensitivity sensors, photovoltaics, biological implants, <sup>61</sup> micro- MEMS devices and protective coatings. <sup>60</sup>

#### 3.2 ALD coatings on complex nanostructures

ALD is not a line-of-sight process because precursors diffuse to available surface sites resulting in conformal films on 2D and nano-3D geometries. Compared to other deposition techniques, the ALD processing temperature is relatively low around 100-200 °C<sup>66-69</sup> and a deposition temperature as low as 33 °C has been reported for Al<sub>2</sub>O<sub>3</sub>. Therefore, a variety of materials can be used as substrates that would otherwise decompose at higher temperature processes, like many organic materials such as polymers, fibers and aerogels. Deposition onto organic materials (*i.e.*, a disordered network of tangled fiber strands or a porous polymer sheet) coats the internal structure as precursors diffuse through voids/pores and adsorb onto available surface sites if the surface is not functionalized. The binary reaction with the adsorbed precursor during the second half-cycle and continued cycling forms clusters that coalesce, eventually

coating the entire surfaces and a continuous film is deposited. Thus, ALD is used for encapsulating such materials. Figure 3.3(a) shows an SEM of carbon aerogel coated with  $Ru^{71}$  and Figure 3.3(b) shows  $Al_2O_3$  nanotubes coated on sacrificial polyvinyl alcohol fibers.