# THESIS REPORT Ph.D.

Supported by the National Science Foundation Engineering Research Center Program (NSFD CD 8803012), Industry and the University

# VLSI Architectures for Real-Time Signal Processing

by C. Chakrabarti Advisor: J.F. JáJá

# VLSI ARCHITECTURES FOR REAL-TIME SIGNAL PROCESSING

by

### Chaitali Chakrabarti

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland in partial fulfillment of the requirements for the degree of Doctor of Philosophy

1990

#### Advisory Committee:

Professor Joseph F. JáJá, Chairman

Professor John Baras

Professor Hung C. Lin

Professor Shihab Shamma

Professor Azriel Rosenfeld

#### ABSTRACT

Title of Dissertation: VLSI Architectures for Real-Time Signal Processing

Chaitali Chakrabarti, Doctor of Philosophy, 1990

Dissertation directed by: Joseph F. JáJá, Professor, Electrical Engineering

We address the problems of developing efficient special-purpose VLSI architectures for computing some important real-time signal processing tasks, namely, one-dimensional Discrete Hartley (DHT) and Discrete Cosine transforms (DCT), multidimensional transforms, template matching and block matching. An important requirement of all these architectures is that they should process huge amounts of data at very high throughput rates.

The first problem that we address involves developing systolic array architectures for computing one-dimensional DHT and DCT over N points, when N is factorizable into mutually prime factors  $N_1$  and  $N_2$ . We map the one-dimensional transform into a two-dimensional transform over  $(N_1 \times N_2)$  points such that the algorithm consists of computing one-dimensional transform over columns and rows of the two-dimensional data array. The hardware requirement is considerably reduced because of this mapping. The architecture consists of simple and regular units which are completely pipelined.

Next we look at the more general problem of computing any  $(N \times N \times ... \times N)$ d-dimensional linear separable transform (DXT). Here we develop a family of optimal architectures with area-time trade-offs. The architecture consists of one-dimensional DXT(N) transform computation units which compute DXT(N) over one index, and permutation units which order data so that in the next iteration DXT(N) can be computed over the next index. The architecture has an area  $A = O(N^{d+2a})$  and computation time  $T = O(dN^{\frac{d}{2}-a}b)$  for all a in the range  $\frac{1}{2}\log_N b \le a \le \frac{d}{2}$ , where  $b = O(\log M)$  is the precision.

The third problem that we address is developing efficient architectures for computing very high input/output (I/O) bandwidth operations, like template matching and block matching. Here we develop a linear semi-systolic array architecture which balances computations in the processor array with the I/O requirements. The I/O bandwidth is reduced by storing part of the input image on-chip in shift registers in each processor, and by circulating the shift registers. The architecture achieves optimal speed-up.

# Contents

| 1 | Intr | oduction                                                       | 1  |

|---|------|----------------------------------------------------------------|----|

|   | 1.1  | Architectural requirements                                     | 2  |

|   | 1.2  | Architectures                                                  | 3  |

|   |      | 1.2.1 Systolic arrays                                          | 4  |

|   |      | 1.2.2 Array processor system                                   | 8  |

|   | 1.3  | Architecture evaluation                                        | 14 |

|   | 1.4  | Main Contributions                                             | 16 |

|   |      | 1.4.1 Discrete Hartley Transform and Discrete Cosine Transform | 16 |

|   |      | 1.4.2 Multi-dimensional Transforms                             | 19 |

|   |      | 1.4.3 Template Matching                                        | 21 |

|   |      | 1.4.4 Block matching                                           | 23 |

|   | 1.5  | Thesis organization                                            | 26 |

| 2 | One-dimensional DHT and DCT |                                                        |    |  |  |  |

|---|-----------------------------|--------------------------------------------------------|----|--|--|--|

|   | 2.1                         | Introduction                                           |    |  |  |  |

|   | 2.2                         | Preliminaries                                          | 28 |  |  |  |

|   |                             | 2.2.1 One-dimensional Discrete Hartley Transform (DHT) | 28 |  |  |  |

|   |                             | 2.2.2 One-dimensional Discrete Cosine Transform (DCT)  | 31 |  |  |  |

|   |                             | 2.2.3 Related work                                     | 34 |  |  |  |

|   | 2.3                         | Mapping into two dimensions                            | 35 |  |  |  |

|   |                             | 2.3.1 Mapping of DHT                                   | 36 |  |  |  |

|   |                             | 2.3.2 Mapping of DCT                                   | 43 |  |  |  |

|   | 2.4                         | Bit-Serial Systolic Implementation                     | 50 |  |  |  |

|   | 2.5                         | Conclusion                                             | 58 |  |  |  |

| 3 | Mu                          | ltidimensional Transforms                              | 61 |  |  |  |

|   | 3.1                         | Introduction                                           | 61 |  |  |  |

|   | 3.2                         | Preliminaries                                          | 62 |  |  |  |

|   |                             | 3.2.1 Definitions                                      | 62 |  |  |  |

|   |                             | 3.2.2 Model of computation                             | 63 |  |  |  |

|   |                             | 3.2.3 Related work                                     | 65 |  |  |  |

|   | 3.3 | Architectures for $d \geq 2$                      | 67 |

|---|-----|---------------------------------------------------|----|

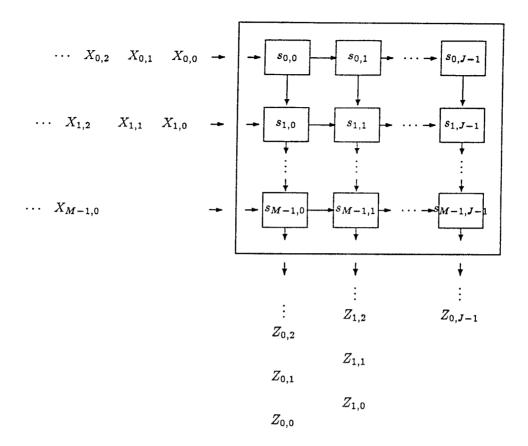

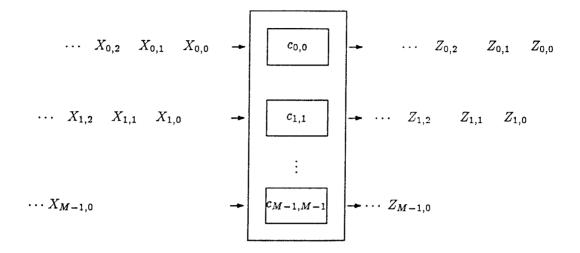

|   |     | 3.3.1 Input is in a single file                   | 67 |

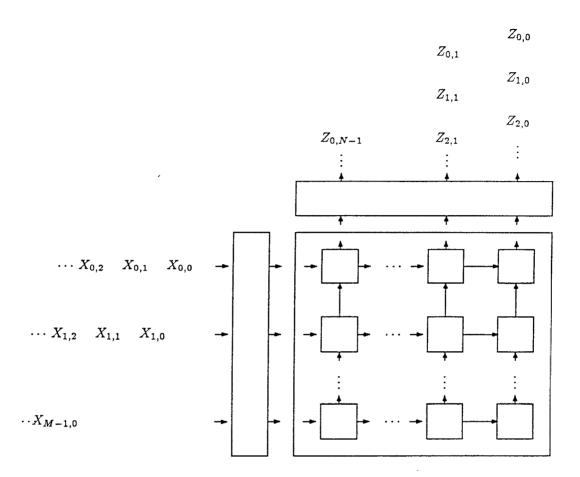

|   |     | 3.3.2 Area-time trade-offs                        | 74 |

|   | 3.4 | Conclusion                                        | 84 |

| 4 | Tem | aplate Matching                                   | 85 |

|   | 4.1 | Introduction                                      | 85 |

|   | 4.2 | Preliminaries                                     | 86 |

|   |     | 4.2.1 Definition                                  | 86 |

|   |     | 4.2.2 Related work                                | 88 |

|   | 4.3 | Overview                                          | 89 |

|   |     | 4.3.1 Model                                       | 89 |

|   |     | 4.3.2 Algorithm and Mapping for Template Matching | 91 |

|   | 4.4 | Detailed description                              | 93 |

|   |     | 4.4.1 Processor Architecture                      | 93 |

|   |     | 4.4.2 Processor Algorithm                         | 95 |

|   |     | 4.4.3 I/O operations                              | 98 |

|   | 4 5 |                                                   | റാ |

| 5 | Blo | ck Mat  | ching                                    | 104 |

|---|-----|---------|------------------------------------------|-----|

|   | 5.1 | Introd  | uction                                   | 104 |

|   | 5.2 | Prelim  | inaries                                  | 105 |

|   |     | 5.2.1   | Definition                               | 105 |

|   |     | 5.2.2   | Related work                             | 107 |

|   | 5.3 | Overvi  | iew                                      | 108 |

|   |     | 5.3.1   | Model                                    | 108 |

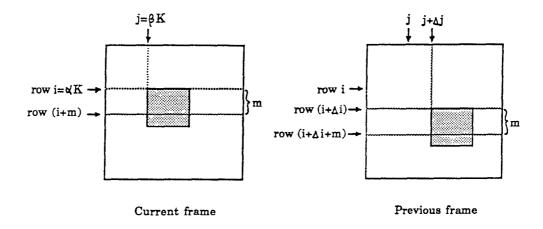

|   |     | 5.3.2   | Algorithm and Mapping for Block Matching | 110 |

|   | 5.4 | Detaile | ed description                           | 112 |

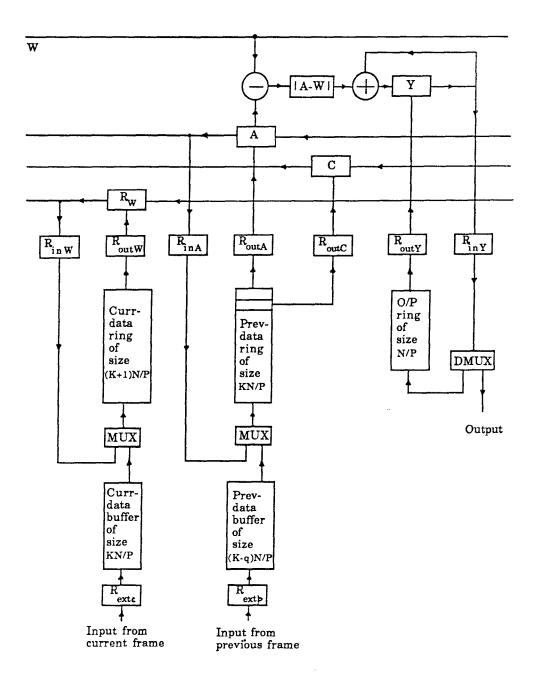

|   |     | 5.4.1   | Processor Architecture                   | 113 |

|   |     | 5.4.2   | Processor Algorithm                      | 118 |

|   |     | 5.4.3   | I/O operations                           | 122 |

|   | 5.5 | Conclu  | asion                                    | 126 |

| 6 | Con | ıclusio | n                                        | 127 |

# List of Figures

| 1.1 | Systolic array configurations: a) Linear array b) Orthogonal array     |    |

|-----|------------------------------------------------------------------------|----|

|     | c) Hexagonal array                                                     | 5  |

| 1.2 | Multiplication of banded matrix $A$ ( $p = 2, q = 4$ ) with vector $x$ |    |

|     | of size 6                                                              | 6  |

| 1.3 | Data flow through the systolic array during the computation of         |    |

|     | Steps 2 through 7 of the matrix-vector algorithm                       | 7  |

| 1.4 | 2-dimensional mesh of size 16                                          | 10 |

| 1.5 | Binary tree network of size 15                                         | 11 |

| 1.6 | Pyramid network of size 21                                             | 12 |

| 1.7 | 4-dimensional hypercube network                                        | 13 |

| 1.8 | Butterfly network for $q=3$ and $P=4.2^3$                              | 14 |

| 2.1 | Matrices $S_4$ , $\hat{C}_4$ , $T_4$ in the computation of DHT(4)      | 29 |

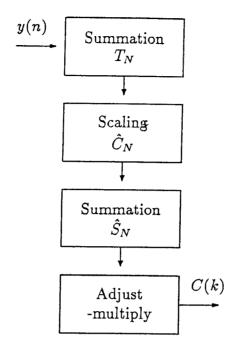

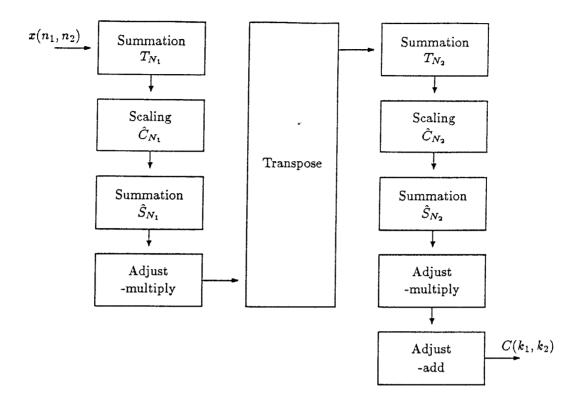

| 2.2 | Block diagram for computing one-dimensional $\operatorname{DHT}(N)$    | 30 |

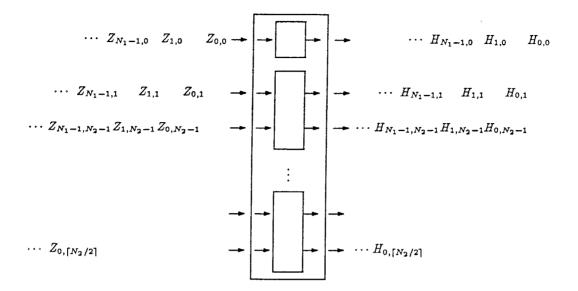

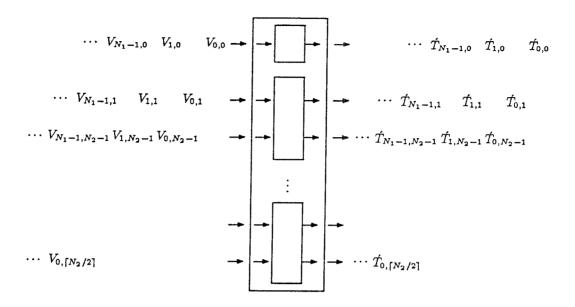

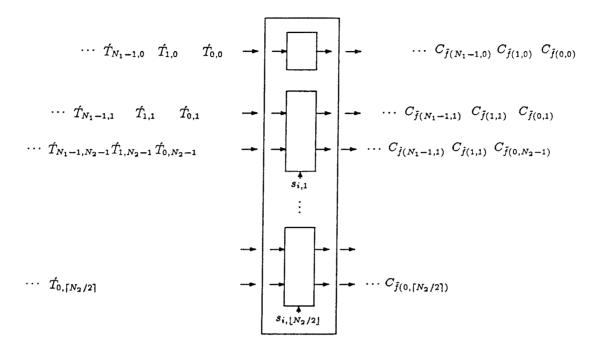

| 2.3  | Block diagram of one-dimensional $\operatorname{DCT}(N)$                     | 32 |

|------|------------------------------------------------------------------------------|----|

| 2.4  | Matrices $P_4$ and $\hat{S}_4$ in the computation of one-dimensional DCT(4)  | 33 |

| 2.5  | Input and output index mappings for DHT over (4 $\times$ 5) points .         | 37 |

| 2.6  | Block diagram for computing two-dimensional DHT over ( $N_1$ ×               |    |

|      | $N_2$ ) points, where $N_1$ , $N_2$ are mutually prime                       | 39 |

| 2.7  | Row permutation in intermediate data array $Y$ after computing               |    |

|      | DHT(4) over columns during the computation of DHT over $(4 \times 5)$        |    |

|      | points                                                                       | 41 |

| 2.8  | Matrices $Q_5$ and $\tilde{S}_5$ in the computation of DHT(5)                | 43 |

| 2.9  | Column permutation in intermediate data array ${\cal Z}$ after comput-       |    |

|      | ing DHT(5) over rows during the computation of DHT over $(4 \times 5)$       |    |

|      | points                                                                       | 44 |

| 2.10 | Input index mapping for DCT over $(4 \times 5)$ points                       | 45 |

| 2.11 | Output index mapping for DCT over $(4 \times 5)$ points                      | 46 |

| 2.12 | Block diagram for two-dimensional DCT over $(N_1 \times N_2)$ points,        |    |

|      | where $N_1$ , $N_2$ are mutually prime                                       | 48 |

| 2.13 | Data array $\hat{T}$ after computing $DC\hat{T}(4)$ over columns followed by |    |

|      | $DCT(5)$ over rows during the computation of DCT over $(4 \times 5)$         |    |

|      | points                                                                       | 49 |

| 9.14 | Showed data array $Y$ of size $M \times N$                                   | 50 |

| 2.15 | Bit level description of rows $0, 1, 2$ of the data array $\dots$                 | 51 |

|------|-----------------------------------------------------------------------------------|----|

| 2.16 | Data flow through the summation unit                                              | 52 |

| 2.17 | Data flow through the scaling unit                                                | 53 |

| 2.18 | Data flow through the transpose unit                                              | 54 |

| 2.19 | Data flow through the adjust-add unit of DHT                                      | 55 |

| 2.20 | Data flow through the second adjust-multiply unit of DCT                          | 56 |

| 2.21 | Data flow through the adjust-add unit of DCT                                      | 57 |

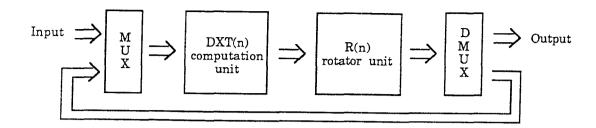

| 3.1  | Architecture for $d$ -dimensional $\mathrm{DXT}(n)$ when the input is in a        |    |

|      | single file                                                                       | 68 |

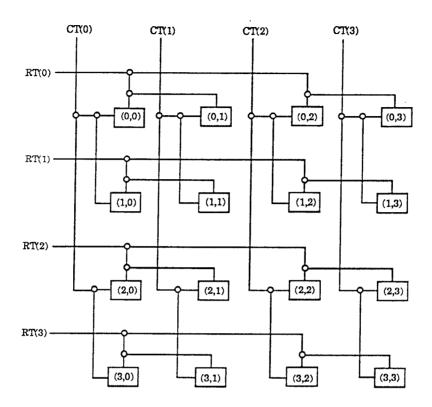

| 3.2  | $(4 \times 4)$ mesh of trees network                                              | 70 |

| 3.3  | DXT(N) computation unit with $AT^2 = O(N^2 \log^2 N)$                             | 71 |

| 3.4  | Layout of a rotator unit for $N=3, d=2 \ldots \ldots$ .                           | 73 |

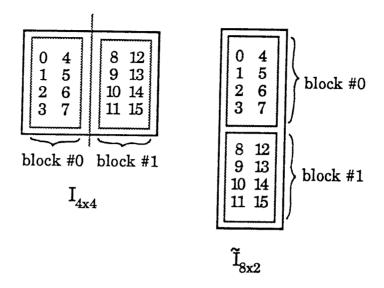

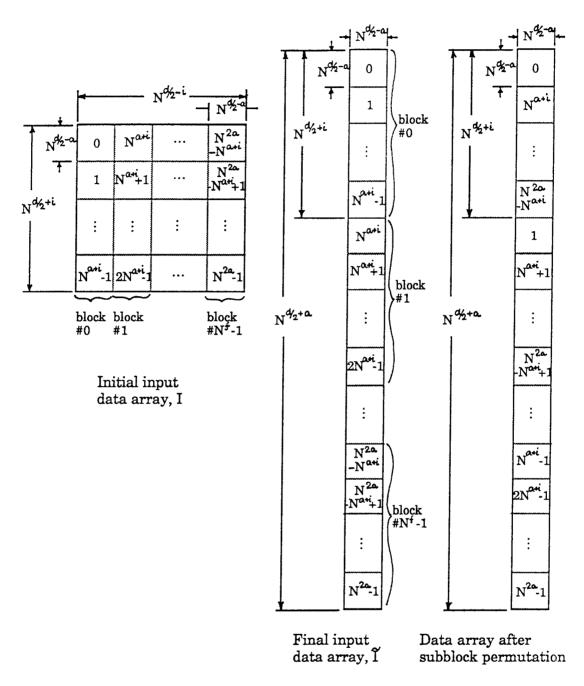

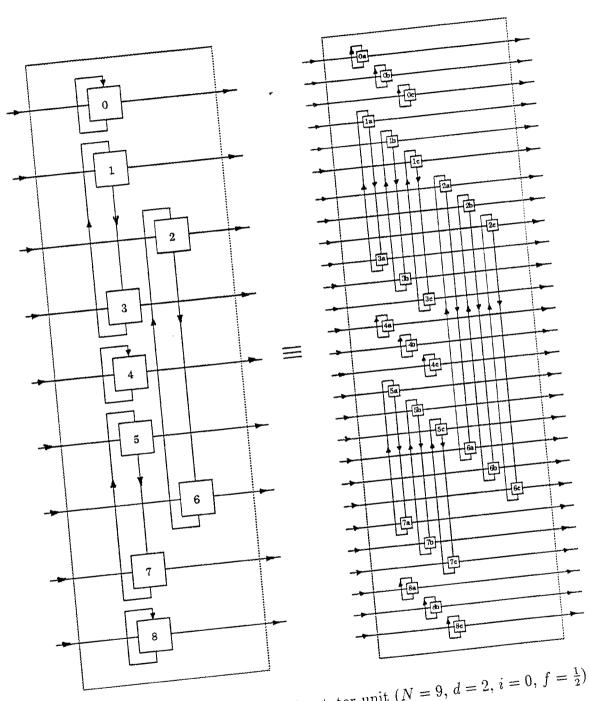

| 3.5  | Input data configuration $(N=4, d=2, i=0, f=\frac{1}{2})$                         | 75 |

| 3.6  | Subblock configurations in $I,$ in $\widetilde{I},$ and after subblock rotation . | 76 |

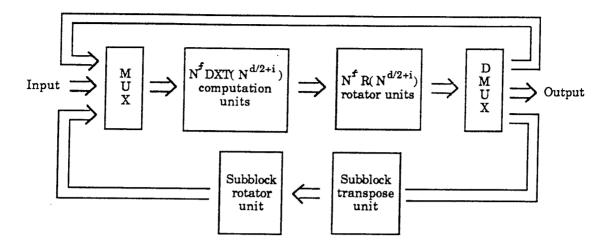

| 3.7  | Architecture for $d$ -dimensional DXT when the input data is a                    |    |

|      | two-dimensional array of size $N^{\frac{d}{2}+a} \times N^{\frac{d}{2}-a}$        | 78 |

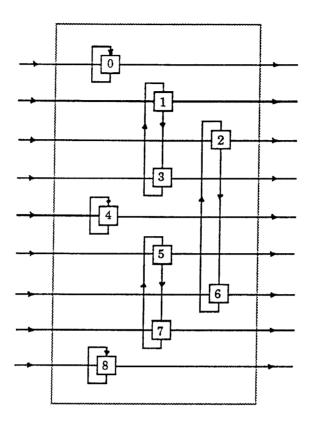

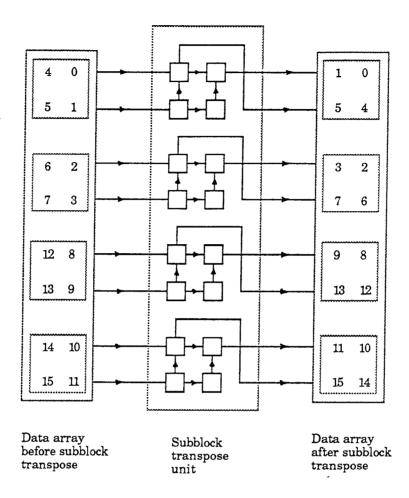

| 3.8  | Subblock transpose unit $(N=4, d=2, i=0, f=\frac{1}{2})$                          | 79 |

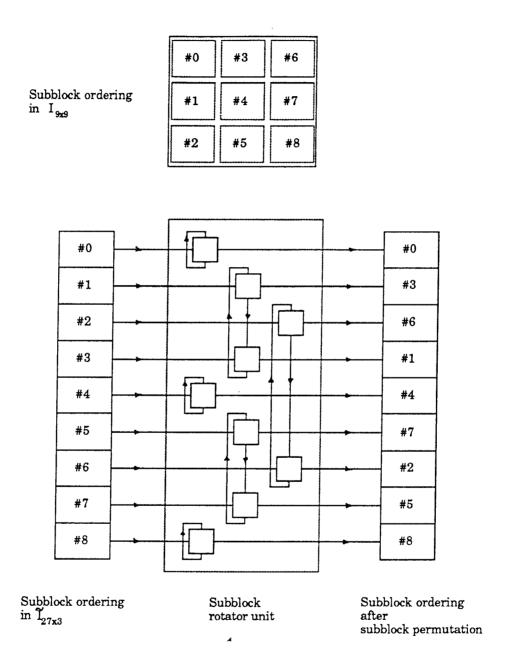

| 3.9  | Subblock rotator unit $(N = 9, d = 2, i = 0, f = \frac{1}{2})$                    | 81 |

| 3.10 | Layout of a subblock rotator unit $(N=9,d=2,i=0,f=\frac{1}{2})$ .              | 82  |

|------|--------------------------------------------------------------------------------|-----|

| 4.1  | Input image $I$ , template $W$ and a particular match configuration            | 87  |

| 4.2  | P-processor architecture                                                       | 90  |

| 4.3  | A match configuration during the computation of template match-                |     |

|      | ing outputs of row $i$                                                         | 91  |

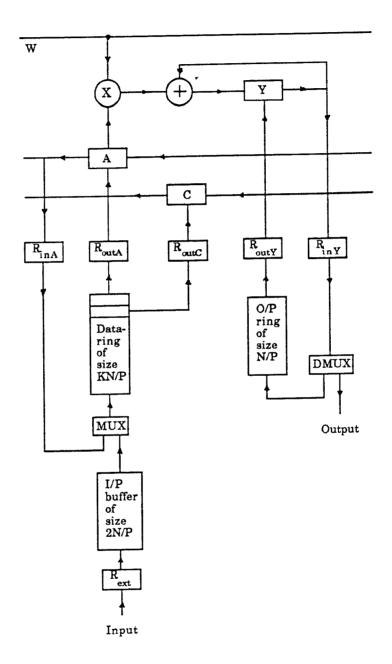

| 4.4  | Design of a processor for template matching                                    | 94  |

| 4.5  | Data ring configuration prior to the computation of $Y[1, *, 0]$ and           |     |

|      | contents of registers $A$ and $C$ during the computation of $Y[1,*,0]$         |     |

|      | in example A                                                                   | 97  |

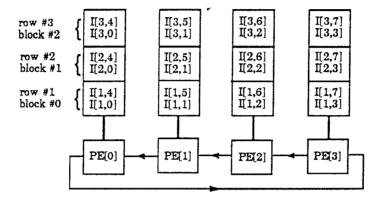

| 4.6  | Data ring configuration of processor $p$ during the computation of             |     |

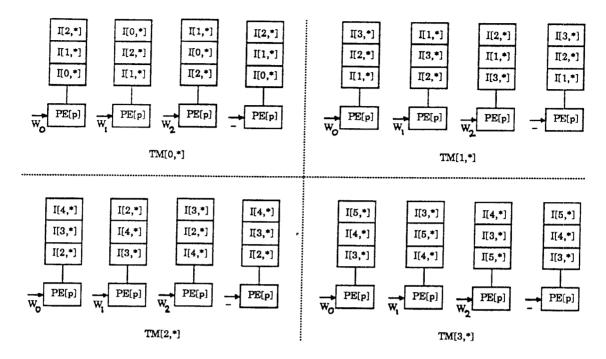

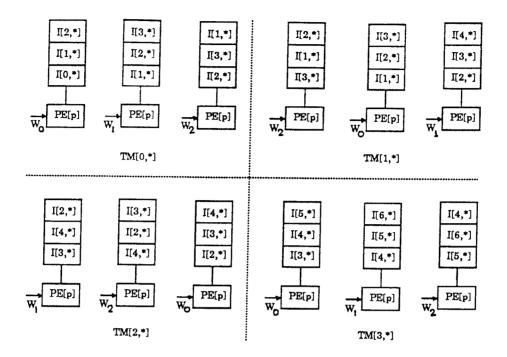

|      | TM[0,*],TM[1,*],TM[2,*],TM[3,*] by Scheme 1 in example A                       | 99  |

| 4.7  | Data ring configuration of processor $p$ during the computation of             |     |

|      | TM[0,*],TM[1,*],TM[2,*],TM[3,*] by Scheme 2 in example A                       | 101 |

| 4.8  | Algorithm for computing template matching when the size of the                 |     |

|      | image is $(N \times N)$ , the size of the template is $(K \times K)$ , and the |     |

|      | number of processors is $P$                                                    | 103 |

| 5.1  | Reference block $B_c(i,j)$ and candidate blocks $B_p(i,j)$ , $B_p(i+1)$        |     |

|      | $\Delta i, j + \Delta j$ ) in search area $S(i, j)$                            | 106 |

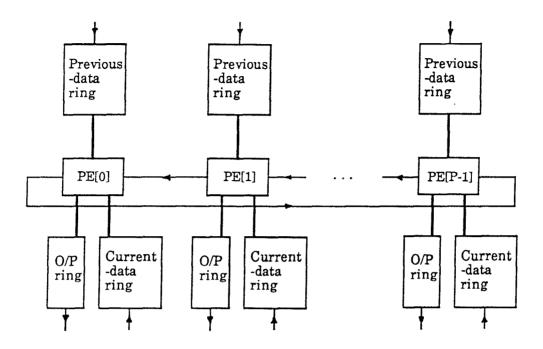

| 5.2  | P-processor architecture                                                       | 109 |

| 5.3 | A match configuration during the computation of $(\Delta \hat{i}, \Delta \hat{j})_{i,j}$                                                                                                                          | 111 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

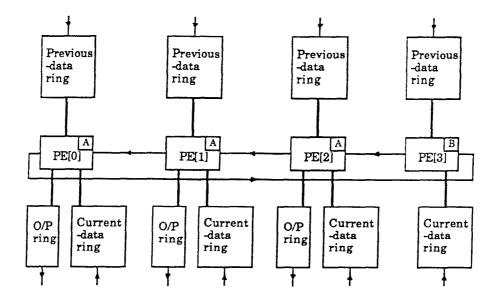

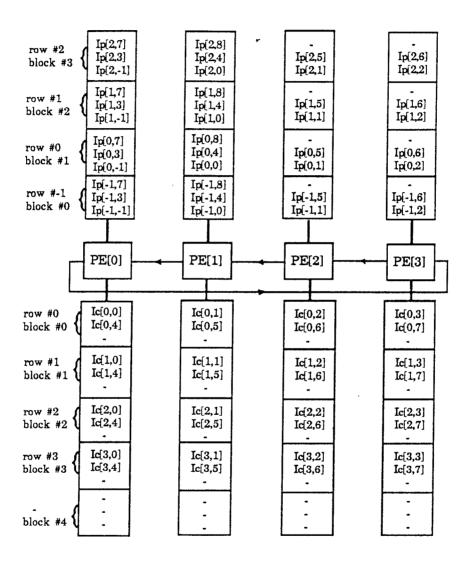

| 5.4 | Processors of types $A$ and $B$ in example $\mathbf{B}$                                                                                                                                                           | 114 |

| 5.5 | Design of a processor of type $A$ for block matching                                                                                                                                                              | 115 |

| 5.6 | Previous-data ring and current-data ring configurations prior to the computation of $blk.dist(0,-1)$ in example B                                                                                                 | 117 |

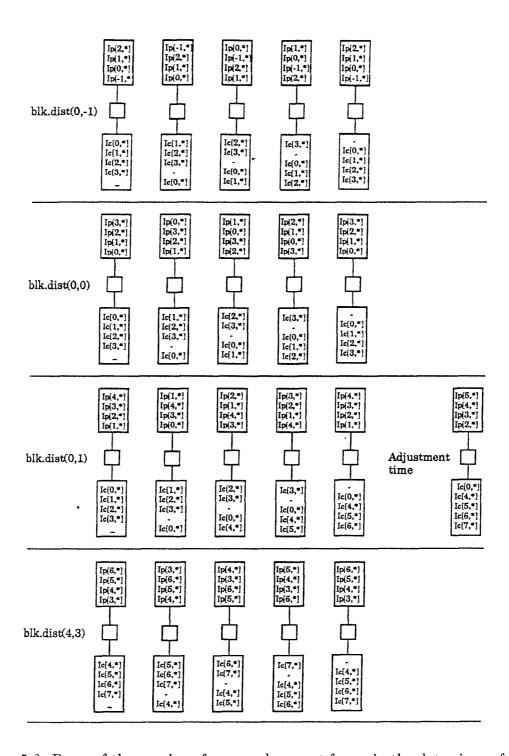

| 5.7 | Contents of registers $A, C, R_W$ during the computation of $Y_{0,0}[-1, *, *]$ in example B                                                                                                                      | -   |

| 5.8 | Rows of the previous frame and current frame in the data rings of a processor during the computation of $blk.dist(0,-1), blk.dist(0,0),$ $blk.dist(0,1),$ and $blk.dist(4,3)$ in example B                        | 124 |

| 5.9 | Algorithm for computing block matching when the size of the image is $(N \times N)$ , the size of the block is $(K \times K)$ , the size of the search area in the previous frame is $(K + q) \times (K + q)$ and |     |

|     | the number of processors is $P$                                                                                                                                                                                   | 125 |

© Copyright by

Chaitali Chakrabarti

1990

To Ma-Baba

### Acknowledgements

First and foremost, I would like to express my gratitude to my advisor and mentor, Joseph JáJá. I am indebted to Joseph for his guidance, sustained encouragement and whole-hearted support throughout the course of my graduate study. By advice and example, he taught me the essentials of being a good researcher (and I hope I learnt it!).

I thank the other members of my thesis committee, Prof. John Baras, Prof. Hung C. Lin, Prof. Azriel Rosenfeld and Prof. Shihab Shamma for their help and insightful comments. Nariman Farvardin, Kazuo Nakajima and Dave Mount provided periodic comments and suggested helpful research directions.

I would like to thank the Systems Research Center and the Electrical Engineering Department for the excellent resources and the stimulating research environment.

Maryland is not all research! My stay here would not have been this much fun without the company of my friends. Let me begin by thanking my roommates or rather my "family" at Maryland – Sukanya, Dulcy and Sharmila. I could not have asked for a more compassionate, caring and loving trio! Thank you PJ for being such a wonderful and supportive friend; Rajasekar for the good times at 7404 Rhode Island Avenue; Sharat, Rim, Vijay, Alice and Tom for your encouragement and support; Sridhar, Jagannathan, Ravi, Shu-Sun, Yingmin, Ryu for making the VLSI Lab a fun place to work in; Sukla, Prosenjitda, Dheeraj, Malini, Raghu, Madhura, Soma, Vivek and Venu for the wonderful memories of the times spent together. Thank you all!

Members of my immediate family – my sister, my parents and my grandparents – have been a constant source of emotional support and encouragement through all phases of my studenthood, and I take this opportunity to express my gratitude for them.

Finally I would like to thank my closest friend and confidant, Rao, who entered my life during this period and stood by me through thick and thin. I owe this thesis to him.

# Chapter 1

## Introduction

Many computational tasks involved in image processing, video processing and speech processing schemes require the ability to carry out the operations in real-time. Real-time signal processing tasks involve processing huge amounts of data at very high throughput rates. To give an estimate of the throughput, consider the computation of template matching when the image is of size (512 × 512), the template is of size (8 × 8) and the frame rate is 30 Hz. The number of multiplication-accumulation operations is then 60 MOPs (million operations per second). It is not unusual for a real-time application to have a throughput as high as 1000 MOPs. Clearly such high computational rates cannot be achieved by sequential systems. In fact, even general-purpose parallel computers cannot match the speed and volume requirements because of severe system overheads. The only way to meet the high computational rates of real-time signal processing tasks is by developing special-purpose architectures which exploit the regularity, recursiveness and locality of the signal processing algorithms. Architectures

which consist of locally interconnected networks (and thereby circumvent the communication problem) and which incorporate both parallel processing and pipelining are well suited for such algorithms. Systolic arrays [32], wavefront arrays [33] are examples of such architectures.

The organization of the rest of this chapter is as follows. We discuss the desired characteristics of such architectures in Section 1.1 and then briefly review some architectures which can handle real-time operation in Section 1.2. In Section 1.3 we make some remarks about its evaluation. In Section 1.4 we give an overview of the architectures that we developed for handling the following signal processing tasks: one-dimensional Discrete Hartley transform (DHT) and Discrete Cosine transform (DCT), multi-dimensional linear separable transforms, template matching, and block matching. We conclude with the thesis organization in Section 1.5.

### 1.1 Architectural requirements

In this section we briefly describe the requirements of special-purpose architectures for real-time signal processing [32, 33]:

Simplicity and regularity of design: This is an important factor in VLSI design. If the design is simple, and if it consists of a few different types of units, then the design cost would be low enough to justify limited applicability. Moreover such a design is more likely to be modular.

Parallel and pipelined processing: The degree of concurrency in a special-purpose architecture is determined by the underlying algorithm, and whether the algorithm can be mapped into an architecture with high degrees of parallel and pipelined processing. Pipelining increases the throughput rate which is a very important system performance factor. Pipelining at all levels (bit-level, word-level and array-level) need to be exploited.

Communication: This is a very critical factor in VLSI design. In fact, interprocessor communications dominate the cost of parallel algorithms and systems. Local and regular communication schemes for both data transactions and control flow are essential to enable efficient implementation.

Balancing computation with input/output: Real-time signal processing operations are computation-bound, that is, the total number of computations is larger than the number of input/output (I/O) operations. Thus for applications with large throughput, multiple computations have to be performed per I/O access. For some applications repetitive use of data items may require it to be stored on-chip. Thus the computation rate has to be balanced with both the external and the internal memory bandwidth.

#### 1.2 Architectures

There are two approaches to the design of special-purpose architectures for realtime signal processing. One is to design dedicated hard-wired systems and the other is to design programmable array processor systems. Systolic arrays and their variations are used in many dedicated systems. In this section we first briefly review systolic arrays, and then describe some other parallel array processor systems.

#### 1.2.1 Systolic arrays

A systolic array is defined by Kung and Leiserson [34] as a "network of processors which rhythmically compute and pass data through the system". The function of a processor is analogous to that of a heart. Each processor regularly pumps data in and out, each time performing some simple computation, so that a regular flow of data in maintained in the network. A systolic array has the following important properties [32, 33].

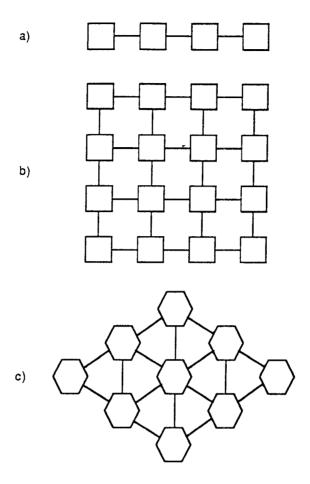

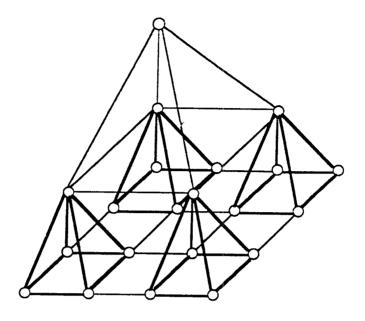

Modularity and regularity: A systolic array consists of simple and modular processors interconnected in a regular pattern. Examples of such patterns are linear (one-dimensional), orthogonal (two-dimensional), hexagonal (see Figure 1.1). The array can be extended indefinitely.

Spatial and temporal locality: The processors communicate with each other via a local interconnection structure (spatial locality). Signal transactions from one processor to the next can be completed in one unit time (temporal locality).

Pipelinability: A systolic array has a very high degree of pipelining. Once a data item is fetched from the memory, it is used to compute/update intermediate results in each processor while being 'pumped' from processor to processor along the array. Such a data flow scheme is ideal for computation-bound operations,

Figure 1.1: Systolic array configurations: a) Linear array b) Orthogonal array c) Hexagonal array

where multiple operations are performed on each data item.

Synchrony: In a systolic array the data passes through the array in a regular, rhythmic pattern. All data movements are synchronized by a global clock.

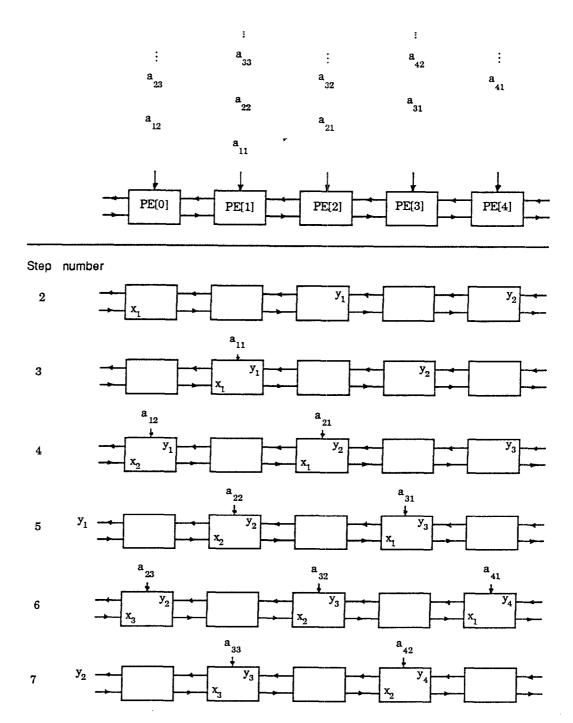

We illustrate the operation of a systolic array with the help of a matrix-vector multiplication example. Consider the problem of multiplying a matrix A with a vector x. Here A has a bandwidth w = p + q - 1 (see Figure 1.2). The architecture consists of a linear array of w inner product processors. The

Figure 1.2: Multiplication of banded matrix A (p=2, q=4) with vector x of size 6

data flow through the array is as follows. The  $y_i$ s move to the left, the  $x_i$ s move to the right and the  $a_{ij}$ s are fed from the top. Figure 1.3 illustrates the data flow in an example where p=4, q=2, and |x|=6. We next trace the computation of  $y_2$  through this array.  $y_2$  is initially set to 0 and input from the right hand side of the array in Step 2. It is updated by PE[2] in Step 4  $(y_2=a_{21}*x_1)$ , by PE[1] in Step 5  $(y_2=a_{21}*x_1+a_{22}*x_2)$ , and by PE[0] in Step 6  $(y_2=a_{21}*x_1+a_{22}*x_2+a_{23}*x_3)$ . In this way the correct value of  $y_2$  is output in Step 7.

Figure 1.3: Data flow through the systolic array during the computation of Steps 2 through 7 of the matrix-vector algorithm

Systolic architectures have a very high performance for any computationbound problem that is regular, that is, for applications which involve repetitive computations on a large set of data. Examples include convolution, filters (IIR, FIR, median), transforms, matrix computations, graph algorithms, language recognition, etc.

Semi-systolic architectures: For many signal processing applications such a rigorous framework is too rigid. In some applications it is advantageous to broadcast data or to time-share the processing elements for sequences of different operations. In some other applications it is necessary to store data in a distributed manner (in shift register memories, local pointer addressed memories, etc.) in the array. Sometimes it is necessary to design efficient I/O interfaces which are not necessarily fully regular (an example is an interface consisting of shift registers that have a conditional clock which activates only when new data is available at the inputs). Architectures which are essentially systolic but which incorporate such variations are referred to as semi-systolic architectures.

Wavefront arrays [33] are an extension of systolic arrays where the intercell synchronization is accomplished by local handshakes, instead of a global clock.

### 1.2.2 Array processor system

An array processor system consists of four major components: host computer, interface unit, processor array and interconnection network [33]. It is used in applications where flexible processing is important.

The functions of the various components in an array processor system are as follows. The host computer provides system monitoring, data storage, program scheduling. The interface unit is responsible for loading/unloading and buffering data to the processor array. The processor array consists of a number of processing elements each equipped with a simple computation unit and (in most cases) a local memory. The mode of operation is either SIMD (Single Instruction Multiple Data stream) <sup>1</sup> or MIMD (Multiple Instruction Multiple Data stream) <sup>2</sup>. The processors communicate with other processors via the interconnection network. Some examples of interconnection network are mesh, binary tree, pyramid, hypercube, and butterfly. Since communication is expensive in VLSI, interconnection networks play an important role in the design of array processor systems. In the rest of this section we present various interconnection networks and state the signal/image processing applications that are suited for each of the networks.

#### Mesh network:

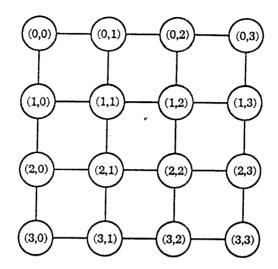

In a d-dimensional mesh, the P processors are logically arranged in a d-dimensional  $(\sqrt[d]{P} \times \sqrt[d]{P} \times \ldots \times \sqrt[d]{P})$  array. The processor at location  $(i_{d-1}, i_{d-2}, \ldots, i_0)$  is connected to the processor at location  $(i_{d-1}, \ldots, i_j \pm 1, \ldots, i_0), 0 \le j \le d-1$ . In a 2-dimensional mesh, each internal processor is connected to 4 neighboring

<sup>&</sup>lt;sup>1</sup>In an SIMD architecture, a single controller broadcasts instruction to all the processors.

The processors then execute the instructions simultaneously.

<sup>&</sup>lt;sup>2</sup>In an MIMD architecture each processor reads instructions from its private memory, decodes them, and executes these instructions.

Figure 1.4: 2-dimensional mesh of size 16

processors (see Figure 1.4). The strength of such a network lies in the ease of construction and the high performance of local neighborhood operations. The weakness lies in algorithms where data have to be moved long distances, in which case it may take  $O(\sqrt{P})$  time. Algorithms which require  $O(\sqrt{P})$  communication operations but perform only  $O(\log P)$  calculations are best solved if the mesh network is augmented with a tree of processors. Such a network is known as the mesh of trees network (see Section 3.3.1). In a  $(\sqrt{P} \times \sqrt{P})$  mesh of trees network, each row of processors as well as each column of processors form the leaves of a binary tree (see Figure 3.2).

#### Binary tree network

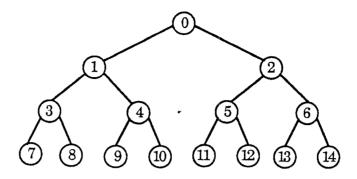

In a binary tree network, the  $P = 2^d - 1$  processors are connected by a complete binary tree of depth (d-1). Each internal processor in the *i*th level is connected

Figure 1.5: Binary tree network of size 15

to its two children in the (i+1)th level and to its parent in the (i-1)th level. Thus processor j is connected to processor (2j+1), processor (2j+2) and processor  $\lfloor j/2 \rfloor$  (see Figure 1.5). (The leaf processors are connected only to their parents and the root processor is connected only to its children.) Such a network is suitable for problems which can be decomposed in a hierarchical way as in dictionary and database problems. Recursive algorithms may also perform better on this network.

#### Pyramid network

In a pyramid network, the  $P = (4^{d+1} - 1)/3$  processors are connected by a pyramid of depth d, such that the ith level is a mesh connected network with  $4^i$  processors,  $0 \le i \le d-1$ . Each internal processor in the ith level is connected to its 4 children in the (i+1)th level, to its 4 nearest neighbors in the ith level and to its parent in the (i-1)th level (see Figure 1.6). All algorithms on the mesh can be run at the lowest level of the pyramid. Algorithms on mesh of trees

Figure 1.6: Pyramid network of size 21

can be run by using only the vertical connections and the horizontal connections in the base of the pyramid. Such a network is useful in image processing for analyzing images at multiple levels of resolution.

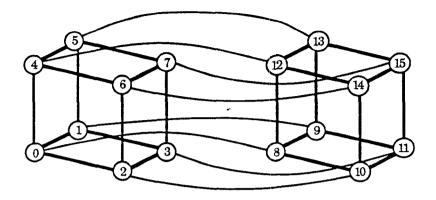

#### Hypercube network:

In a hypercube network, the  $P=2^d$  processors are connected by a d-dimensional Boolean cube. If the binary representation of i is  $i_{d-1}i_{d-2}\ldots i_0$ , then processor i is connected to all processors  $i^j$ , where  $i^j$  is represented by  $i_{d-1}\ldots \bar{i_j}\ldots i_0$ ,  $\bar{i_j}=1-i_j$  and  $0\leq j\leq d-1$ . A hypercube has a recursive structure: a d-dimensional hypercube can be viewed as being two (d-1)-dimensional hypercubes with connections between the corresponding corners of the smaller hypercubes (see Figure 1.7). A hypercube has a high bandwidth and can solve

Figure 1.7: 4-dimensional hypercube network

many problems very fast. However they are difficult to build, since there are  $\log P$  wires conected to each processor. Shuffle-exchange and cube-connected cycles have a performance comparable to hypercubes but have fixed number of interconnections.

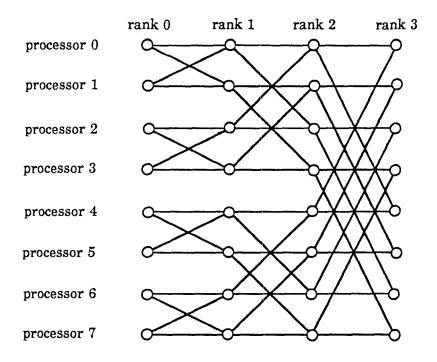

#### Butterfly network:

In a butterfly network, the  $P=(q+1)2^q$  processors are organized into (q+1) ranks with  $2^q$  processors in each rank. Processors i and  $i^r$  in rank r+1 are connected to processors i and  $i^r$  in rank r, where  $i^r$  is denoted by  $i_{q-1} \dots \bar{i_r} \dots i_0$ ,  $0 \le r \le q$ , and  $0 \le i < 2^q$ . These four connections form a 'butterfly' pattern (see Figure 1.8). This network is ideally suited for computing fast transforms like FFT (Fast Fourier Transform). It can also be used to solve problems like merging, sorting, etc. very fast. Actually this network is equivalent to the shuffle-exchange and is slightly less powerful than the hypercube.

Figure 1.8: Butterfly network for q = 3 and  $P = 4.2^3$

### 1.3 Architecture evaluation

Here we would like to make some remarks about the important features in the evaluation of a VLSI architecture. The basic parameters of any VLSI computation are chip area A and computation time T. Chip area is a measure of the fabrication cost and computation time is a measure of the operating cost. While VLSI designers measure the chip area in  $mm^2$  of silicon and computation time in nanoseconds, VLSI computation theorists estimate the area and computation time asymptotically using the VLSI model of computation.

In the VLSI model of computation [6, 54], a VLSI circuit is a computation graph whose vertices are nodes which perform simple logical functions, and

whose edges are wires which carry signals to and from nodes. The total area A is the number of unit squares in the smallest rectangle that encloses the circuit consisting of nodes and wires. The computation time T is the number of time units between the appearance of the first input bit on some port and the appearance of the last output bit on some port.

The VLSI model of computation relies on asymptotic analysis to evaluate the area and time complexities. Such an analysis has the advantage of being very simple and yet pointing out the bottlenecks of the design. Moreover it provides a simple framework for the evaluation and explanation of various designs. However such an analysis does not contain the constant factors that are crucial when the number of sample points is small. Also, VLSI technology still cannot support the one-chip design for a large number of sample points. So a theoretically optimal design may not necessarily be the 'best' design in terms of actual hardware implementation. From a designers' point of view what is more important is whether the design is regular and simple, whether all the processors are active most of the time, whether the communication bandwidth between processors as well as with the external world is low, whether the data flow is regular, and so on. In this thesis we develop architectures which are on the one hand realizable using today's technology and on the other hand as close as possible to the theoretical optimality criteria.

## 1.4 Main Contributions

In this section we give an overview of the architectures that we developed for computing some important signal processing tasks, namely, one-dimensional Discrete Hartley and Discrete Cosine transforms, d-dimensional linear separable transforms, template matching, and block matching. For each of these problems we briefly describe the importance, the definition, the existing schemes and the proposed scheme.

# 1.4.1 Discrete Hartley Transform and Discrete Cosine Transform

The Discrete Hartley transform (DHT) and the Discrete Cosine transform (DCT) are important transforms in signal processing. DCT is widely used to encode speech and video signals in data compression schemes because of its close performance to the statistically optimal Karhunen-Loève transform. DCT is also used for realizing filter banks in frequency-division multiplexing and time-division multiplexing systems. DHT is used in spectral analysis and other signal processing schemes. In fact, it has the same potential as the Discrete Fourier transform (DFT) and can be used in almost all schemes which employ DFT. DHT and DCT are favored in schemes which require the computation of multi-dimensional transforms, since both these transforms are real and do not require computations involving complex arithmetic (as in DFT).

#### Problem definition:

The one-dimensional DHT of N points is defined [2] by

$$H(k) = \frac{1}{\sqrt{N}} \sum_{n=0}^{N-1} x(n) cas(\frac{2\pi}{N}nk), \quad 0 \le k \le N-1,$$

where cas(x) = cos(x) + sin(x). The one-dimensional DCT of N points is defined [1] by

$$C(k) = \frac{2}{N}e(k)\sum_{n=0}^{N-1} x(n)\cos[\frac{\pi}{2N}(2n+1)k], \quad 0 \le k \le N-1,$$

where,

$$e(k) = \begin{cases} \frac{1}{\sqrt{2}} & \text{if } k = 0\\ 1 & \text{otherwise} \end{cases}$$

Our aim here is to develop systolic array architectures for one-dimensional DHT and DCT when N is factorizable into mutually prime factors  $N_1$  and  $N_2$ .

#### Existing schemes:

There exist linear systolic array architectures [14, 55] as well as two-dimensional systolic array architectures [14] for computing DCT. While the former is a direct realization of the matrix vector algorithm, the latter computes DCT by multiplying the output of DFT over  $(N_1 \times N_2)$  points with appropriate factors. There also exist general-purpose architectures for DCT [57]. To the best of the author's knowledge no systolic array architectures have been proposed for DHT.

#### Our contribution:

Our approach for computing one-dimensional DHT and DCT consists of mapping the one-dimensional transforms over N points into two-dimensional transforms over  $(N_1 \times N_2)$  points, and then realizing them by two-dimensional systolic arrays. The algorithm consists of computing one-dimensional transforms over columns and rows of the two-dimensional data array, followed by some adjustments. Our architecture is strictly systolic. All the components are completely pipelined, resulting in very high throughput.

There is a considerable reduction in hardware as a result of mapping the onedimensional transform into two-dimensions. This is because the same hardware can be used to compute on multiple columns (rows). The reduction in hardware is at the expense of a larger computation time. The number of multipliers in our architecture is considerably less than those of the existing architectures [13, 14, 55]. This feature is important since the chip area is dominated by the area occupied by the multipliers. Let f(N) be the number of multipliers required to compute an N point DFT on real data. Then the number of multipliers in our architecture for DHT is  $f(N_1) + f(N_2)$  and the number of multipliers in our architecture for DCT is  $3f(N_1) + 3f(N_2)$ . In comparison the number of multipliers in the existing architectures for DCT is  $2f(N_1) + 4f(N_2) + 4N_2$  in [14], N in [55], and  $N^2$  in [13]. Moreover the size of the multipliers in our architecture are smaller compared to those of [14, 55], since the multipliers are fixed and can hence be embedded in the hardware.

#### 1.4.2 Multi-dimensional Transforms

Multi-dimensional transforms are a powerful tool for multi-dimensional signal processing. Some of the important applications of such transforms are in the areas of spectrum analysis, signal reconstruction, speech processing, tomography, computer vision and image processing. Examples of such transforms are DFT, DHT, and DCT. We refer to these transforms as DXT.

#### Problem definition:

An  $(N \times N \times ... \times N)$  d-dimensional linear separable transform is defined by

$$X(k_1, k_2, \dots, k_d) = \sum_{n_d} \dots \sum_{n_2} \sum_{n_1} x(n_1, n_2, \dots, n_d) \alpha_1(n_1, k_1) \alpha_2(n_2, k_2) \dots \alpha_d(n_d, k_d),$$

where the  $\alpha_i$ 's are the one-dimensional transform functions (like DFT, DHT, DCT),  $0 \le k_i, n_i \le N - 1$  for  $1 \le i \le d$ .

Our aim here is to develop optimal architectures for computing such transforms. An optimal architecture is one whose  $AT^2$  matches the  $AT^2$  lower bound for computing such transforms, where A is the area, T is the computation time. The  $AT^2$  lower bound for d-dimensional DXT is  $AT^2 = \Omega(n^2 \log^2 M)$ , where  $n = N^d$ , and M = N + 1.

#### Existing schemes:

The schemes for computing  $(N \times N \times ... \times N)$  d-dimensional transforms consist of computing either a sequence of one-dimensional transform each of size

N, or a matrix-vector product. The architecture of [24] which is based on the first scheme, has an area  $A = O(n^2)$ , computation time  $T = O(d \log^2 n)$  and is not optimal. The architecture of [4] which is based on the second scheme, has an area  $A = O(n^2 \log^2 M/T^2)$  and is optimal for all T in the range  $[\Omega(\log n), O(\sqrt{n \log M})]$ .

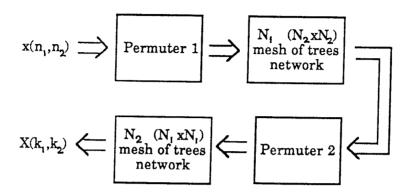

#### Our contribution:

Our approach for computing  $(N \times N \times ... \times N)$  d-dimensional DXT is based on the first scheme. The architecture consists of one-dimensional DXT(N) computation units which compute DXT(N) over one index, and permutation units which order data so that in the next iteration DXT(N) can be computed over the next index. Our architecture has an area  $A = O(N^{d+2a})$  and computation time  $T = O(dN^{\frac{d}{2}-a}b)$  for all a in the range  $\frac{1}{2}\log_N b \le a \le \frac{d}{2}$ , where  $b = O(\log M)$  is the precision. Thus an architecture with small value of a is one with small area while an architecture with large value of a is one with small computation time.

Our scheme consists of a family of architectures with area-time trade-offs. The architecture of [24] (which is for the case when the input data is in a single file) is a member of this family. For the same single file input data configuration, the computation time of our design is  $O(d \log M)$  compared to  $O(d \log^2 n)$  of [24]. The architecture of [4] is optimal for the same range of area and computation time as our architecture. For the case when d is constant, our architecture is superior to that of [4] since it is simpler, more regular, more modular, and hence easier to implement in VLSI. It is not unreasonable to make such an assumption

about the constancy of d, since for all known applications of multidimensional transforms,  $d \leq 4$ .

# 1.4.3 Template Matching

Image template matching is used to find the similarity or disagreement between a template and an equivalent size area of the input image. It is representative of many window based image processing tasks. It is used in image location, scene matching, filtering, edge detection, finding lines, spots, curves, etc.

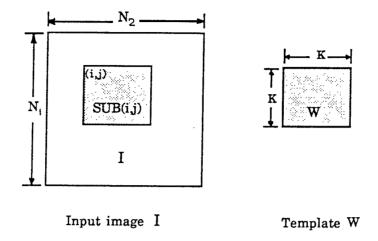

#### Problem definition:

Let the input image be of size  $(N \times N)$  and let the template be of size  $(K \times K)$ , then template matching is the inner product of the template with an equivalent size area of the input image.

$$TM[i,j] = \sum_{m=0}^{K-1} \sum_{n=0}^{K-1} I[i+m,j+n] * W[m,n], \quad 0 \le i,j \le N-K.$$

Our aim here is to develop a systolic architecture for template matching which efficiently balances the computations in the processor array with the I/O bandwidth. The input image is read in the line scan mode <sup>3</sup>.

<sup>&</sup>lt;sup>3</sup>In line scan mode, the pixels are run left to right and from top to bottom in a frame.

#### Existing schemes:

The systolic and semi-systolic architectures for template matching which address the I/O bandwidth problem can be divided into two classes: architectures which store part of the input on-chip, and architectures which store part of the input in an external memory. The I/O bandwidth for architectures with an external memory is K pixels per clock cycle [27, 51], while that of architectures with on-chip storage in only one pixel per clock cycle [17, 41]. The on-chip storage devices are FIFO line memory [17], shift-buffer pipeline [41], shift registers, RAM, etc. There are other architectures [28] which balance the large bandwidth of the first class of architectures and the large on-chip storage of the second class by including both an external memory and an on-chip storage, albeit smaller. Such architectures are suitable for large templates.

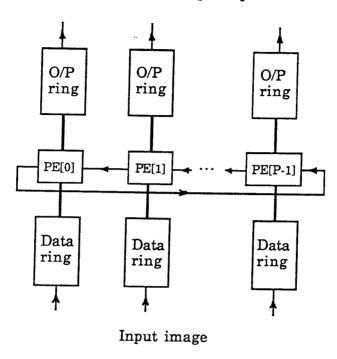

#### Our contribution:

Our architecture for computing template matching consists of a semi-systolic linear array of processors. A part of the input image is stored on-chip in shift registers distributed among the processors. The number of processors in our architecture is a function of the frame size, the template size and the internal clock cycle. This feature makes our architecture more versatile compared to those of [17, 28, 41], where the number of processors is fixed at  $K^2$  irrespective of the frame specifications. An additional advantage of our scheme is that since the on-chip storage is distributed among the processors, no additional circuitry is required to ensure regular data flow from the on-chip storage devices to the

processor array.

# 1.4.4 Block matching

In many applications of digital image processing like video-phone and teleconferencing, there is very little motion in the entire scene. Thus successive frames are highly correlated. In such applications, algorithms based on motion compensation can be used to reduce information redundancy, and thereby achieve high data compression. Block matching is a popular motion compensation algorithm which is used to remove interframe redundancy.

In block matching the current frame is divided into reference blocks, and for each reference block, the best matched block in the previous frame is searched. It is assumed that the best matched block lies in an area surrounding the position of the reference block. The displacement between the reference block position and that of the best matched one in the previous frame is called the *displacement vector*. The receiver can construct the current frame using the available previous frame, the displacement vector and the block difference. This scheme results in tremendous bit rate reduction in interframe coding.

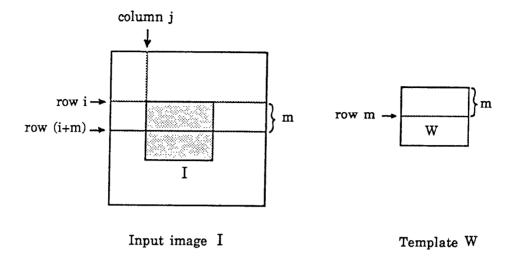

#### Problem definition

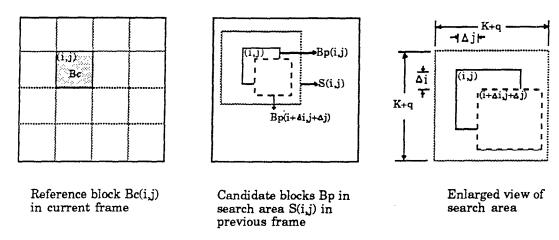

Let the current frame of size  $(N \times N)$  be divided into reference blocks of size  $(K \times K)$ . Let  $B_c(i,j)$  be one such reference block whose top-leftmost coordinate is (i,j).  $B_c(i,j)$  is matched with candidate blocks in the previous frame which lie

in a search area S(i,j). Let  $L_{i,j}(\Delta i, \Delta j)$  be the block-distance between reference block  $B_c(i,j)$  and candidate block  $B_p(i+\Delta i,j+\Delta j)$

$$L_{i,j}(\Delta i, \Delta j) = \sum_{m=0}^{K-1} \sum_{n=0}^{K-1} |x_c(i+m, j+n) - x_p(i+m+\Delta i, j+n+\Delta j)|,$$

$-\frac{q}{2} \leq \Delta i, \Delta j \leq \frac{q}{2}$ . The best match criteria is based on the minimum value of block-distance. The displacement vector  $(\Delta \hat{i}, \Delta \hat{j})_{i,j}$  for reference block  $B_c(i,j)$  is given by

$$(\Delta \hat{i}, \Delta \hat{j})_{i,j} = \min_{\Delta i, \Delta j}^{-1} L_{i,j}(\Delta i, \Delta j).$$

Our aim here is to develop a systolic architecture for block matching which efficiently balances the computations in the processor array with the I/O bandwidth. Data from the current frame and the previous frame memory are read in line scan mode.

#### Existing schemes

There exist many systolic and semi-systolic architectures for block matching [7, 18, 20, 30, 61] which compute the displacement vectors very efficiently but are not so efficient in handling the I/O operations. Block matching, like template matching, is an operation with a very high I/O bandwidth. A way of reducing the large I/O bandwidth is by storing part of the image which is accessed multiple times, on-chip in a storage device. Shift registers, RAMs, line buffers, register chains, etc [7, 18, 30] are popular on-chip storage devices. In almost all these architectures, the input data is fed from the frame memories

into the on-chip storage devices in block scan mode 4.

#### Our contribution

Our architecture for computing block matching consists of a semi-systolic linear array of processors which handles both the computations and the I/O bandwidth problem efficiently. Data from both the current frame and the previous frame-memory are read in line scan mode and stored on-chip in shift registers distributed among the processors. For this mode of data access, the linear array is a more suitable architecture (compared to the two-dimensional array). The number of processors in our architecture is a function of the frame specification (frame size, frame frequency), search area size, and internal clock rate. Our architecture can be very easily reconfigured for different problem specifications unlike the existing architectures where the number of processors is fixed [7, 18, 20, 30]. The data flow in our architecture is very regular. There is no additional circuitry to ensure that the right data are incident on the processor array as in [18]. The number of I/O pins in our architecture is only two compared to  $1 + (q + K)^2/K^2$  in [7].

<sup>&</sup>lt;sup>4</sup>In block scan mode, blocks of  $(K \times K)$  pixels are run left to right and from top to bottom in a frame.

# 1.5 Thesis organization

In this thesis we present the systolic and semi-systolic architectures that we developed for computing some important real-time signal processing tasks.

In Chapter 2 we develop completely pipelined, bit-serial systolic array architectures for computing one-dimensional DHT and DCT when the number of sample points N is factorizable into mutually prime factors  $N_1$  and  $N_2$ .

In Chapter 3 we develop a family of optimal architectures with area-time trade-offs for computing  $(N \times N \times ... \times N)$  d-dimensional linear separable transforms. The criteria for optimality is as defined by VLSI complexity theory.

In Chapters 4 and 5 we develop semi-systolic linear array architectures for computing template matching and block matching respectively. The architecture handles the computations as well as the I/O bandwidth requirements efficiently.

In Chapter 6 we summarize the results obtained in this dissertation and suggest some directions for future research in this area.

# Chapter 2

# One-dimensional DHT and DCT

# 2.1 Introduction

In this chapter we address the problem of developing systolic array architectures for computing one-dimensional DHT and DCT over N points, when N is factorizable into mutually prime factors  $N_1$  and  $N_2$ . The one-dimensional transform over N points is mapped into a two-dimensional transform over  $(N_1 \times N_2)$  points, such that the algorithm consists of computing one-dimensional transform over columns and rows of the two-dimensional data array, followed by some adjustments. The hardware requirement is considerably reduced because of this mapping. The number of multipliers in our architecture is significantly less than those of the existing architectures [13, 14, 55]. The number of multipliers for our DHT architecture is  $f(N_1) + f(N_2)$  and that of our DCT architecture is  $3f(N_1) + 3f(N_2)$ , where f(N) is the number of multipliers required to compute

an N point DFT on real data. Our architecture consists of a few types of regular and modular units. All the units are completely pipelined, resulting in very high throughput.

The rest of the chapter is organized as follows. In Section 2.2 we define one-dimensional DHT and DCT and show how these transforms can be mapped into systolic architectures. In Section 2.3 we give the index mappings that map one-dimensional DHT and DCT to two-dimensional DHT and DCT, and show how the two-dimensional transforms can be mapped into systolic array architectures with reduced hardware. We give the details of the bit-serial systolic array implementations in Section 2.4. In Section 2.5 we make some concluding remarks.

# 2.2 Preliminaries

# 2.2.1 One-dimensional Discrete Hartley Transform (DHT)

The one-dimensional DHT of N points, DHT(N), is defined [2] by

$$H(k) = \frac{1}{\sqrt{N}} \sum_{n=0}^{N-1} x(n) cas(\frac{2\pi}{N}nk), \quad 0 \le k \le N-1,$$

(2.1)

where cas(x) = cos(x) + sin(x). Since the factor  $\frac{1}{\sqrt{N}}$  in equation 2.1 is a constant, it is sufficient to consider the DHT-like equation

$$H(k) = \sum_{n=0}^{N-1} x(n) \cos(\frac{2\pi}{N}nk), \quad 0 \le k \le N-1.$$

(2.2)

There are various schemes for computing one-dimensional DHT [2, 3, 25, 31, 52]. They are based on either decompositions of the form radix-2 decimation-in-time,

$$S_4 = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & -1 \end{pmatrix}, \hat{C}_4 = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & -1 \end{pmatrix}, T_4 = \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & -1 & 1 & -1 \\ 1 & 0 & -1 & 0 \\ 0 & -1 & 0 & 1 \end{pmatrix}$$

Figure 2.1: Matrices  $S_4$ ,  $\hat{C}_4$ ,  $T_4$  in the computation of DHT(4)

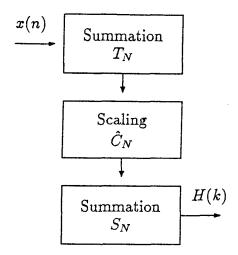

radix-2 decimation-in-frequency, split radix, radix-4, or Winograd transform, or recursion. We choose the Winograd-Hartley transform (WHT) algorithm [52] because of the reduced number of multiplications ( $\approx N$ ). Moreover this algorithm can be mapped into an architecture with reduced number of multipliers. The WHT algorithm is expressed as  $H = S_N \hat{C}_N T_N x$ , where  $S_N$  is an  $N \times J$  incidence  $^1$  matrix,  $T_N$  is a  $J \times N$  incidence matrix and  $\hat{C}_N$  is a  $J \times J$  diagonal matrix with real entries,  $J \approx N$  for small N algorithms. This algorithm is very similar to the Winograd Fourier transform (WFT) algorithm [23], which is expressed as  $F = S_N C_N T_N x$ .  $\hat{C}_N$  of WHT is related to  $C_N$  of WFT by  $\hat{C}_N = Re[C_N] - Im[C_N]$ . Figure 2.1 describes the matrices  $S_4$ ,  $\hat{C}_4$  and  $T_4$  for computing DHT(4).

The WHT algorithm can be mapped into a systolic architecture in a way similar to the mapping of the WFT algorithm in [47]. The incidence matrices  $S_N$  and  $T_N$  are mapped into systolic units, called *summation* units. These units consist of arrays of 1-bit adders, 1-bit subtractors or 1-bit delays corresponding

<sup>&</sup>lt;sup>1</sup>An incidence matrix is a matrix whose elements are -1, 0 or 1.

Figure 2.2: Block diagram for computing one-dimensional  $\operatorname{DHT}(N)$

to entries +1, -1 or 0 in the incidence matrices. The diagonal matrix  $\hat{C}_N$  is mapped into a systolic unit, called *scaling* unit. This unit consists of an one-dimensional array of J fixed multipliers, corresponding to the J diagonal elements. Figure 2.2 describes the block diagram of the corresponding architecture.

The bottleneck of this architecture is the large number ( $\approx N$ ) of multipliers in the scaling unit. The number of multipliers can be reduced to ( $\approx N_1 + N_2$ ) by mapping the one-dimensional transform into two dimensions. In Section 2.3.1 we describe such a transformation.

# 2.2.2 One-dimensional Discrete Cosine Transform (DCT)

The one-dimensional DCT of N points, DCT(N), is defined [1] by

$$C(k) = \frac{2}{N}e(k)\sum_{n=0}^{N-1} x(n)\cos[\frac{\pi}{2N}(2n+1)k], \quad 0 \le k \le N-1,$$

(2.3)

where,

$$e(k) = \begin{cases} \frac{1}{\sqrt{2}} & \text{if } k = 0\\ 1 & \text{otherwise} \end{cases}$$

Since the factor  $\frac{2}{N}e(k)$  results only in a slight modification of C(k), it is sufficient to consider the DCT-like equation

$$C(k) = \sum_{n=0}^{N-1} x(n) \cos\left[\frac{\pi}{2N}(2n+1)k\right] \quad 0 \le k \le N-1.$$

(2.4)

There are various schemes for computing one-dimensional DCT [11, 26, 39, 43, 46, 56]. They are based on either factorization of the DCT matrix, or rotation of the output of a Fourier or Hartley transform, or recursion. We choose a scheme based on rotation of the Hartley transform [43].

In the method proposed by Malvar [43], the input x(n) is permuted so that the cosine argument in equation 2.4 is changed to  $\cos\left[\frac{\pi}{2N}(4n+1)k\right]$ . DHT can then be used to compute C(k). Let y(n) be a permutation of x(n) defined by

$$y(n) = \begin{cases} x(2n) & 0 \le n \le \lceil N/2 \rceil - 1 \\ x(2N - 2n - 1) & \lceil N/2 \rceil \le n \le N - 1. \end{cases}$$

(2.5)

Then

$$C(k) = \frac{1}{2} [H(k)cas(-\frac{k\pi}{2N}) + H(N-k)cas(\frac{k\pi}{2N})],$$

(2.6)

where H(k) is the DHT of y(n). Let  $\sum_{n} y(n) \cos\left[\frac{\pi}{2N}(4n+1)k\right]$  be denoted by DCT of y(n). Then C(k) in equation 2.6 is the DCT of y(n). We choose the

Figure 2.3: Block diagram of one-dimensional DCT(N)

Winograd-Hartley transform algorithm to compute DHT of y(n). In that case the number of multiplications is only  $\approx 3N$ .

The above algorithm can be mapped into a systolic architecture in the following way. H(k) can be computed in a systolic manner by the summation and scaling units as described in Section 2.2.1. C(k) can be computed in a systolic fashion from H(k) (see equation 2.6) by a systolic unit called the *adjust-multiply* unit. This unit consists of an one-dimensional array of N subunits, each of which consists of two fixed multipliers and one 1-bit adder. Figure 2.3 describes the block diagram of this architecture.

In order that the adjust-multiply unit (see Figure 2.3) be systolic, H(k) and H(N-k) have to be adjacent to each other. This is achieved by modifying  $S_N$

$$P_4 = \left( egin{array}{cccc} 1 & 0 & 0 & 0 \ 0 & 1 & 0 & 0 \ 0 & 0 & 0 & 1 \ 0 & 0 & 1 & 0 \end{array}

ight), \qquad \hat{S}_4 = \left( egin{array}{cccc} 1 & 0 & 0 & 0 \ 0 & 0 & 1 & 1 \ 0 & 0 & 1 & -1 \ 0 & 1 & 0 & 0 \end{array}

ight)$$

Figure 2.4: Matrices  $P_4$  and  $\hat{S}_4$  in the computation of one-dimensional DCT(4) to  $\hat{S}_N$  in the following way. Let  $G = S_N \hat{C}_N T_N x$  and let  $\hat{G}$  be a permutation of G, such that  $\hat{G} = (G(0) G(1) G(N-1) \dots G(k) G(N-k) \dots)^T$ , where G(i) represents the ith row of G,  $1 \le k \le \lfloor N/2 \rfloor$ . When N is even, there is only one G(N/2) in  $\hat{G}$ .  $\hat{G}$  can be expressed as  $P_N G$ , where  $P_N$  is a permutation matrix with the following characteristics:

$$P_N(0,0)=1$$

For even  $i, \quad i\neq 0, \quad P_N(i,N-i/2)=1$  For odd  $i, \quad P_N(i,\lceil i/2\rceil)=1$

Note that since  $P_N$  is a permutation matrix,  $\hat{S}_N$  is an incidence matrix, and hence can be directly embedded into the summation unit. Figure 2.4 describes the permutation matrix  $P_4$  and the incidence matrix  $\hat{S}_4 = P_4 S_4$ .

As in the case of DHT, the bottleneck of this architecture is the large number of multipliers ( $\approx N$  in the scaling unit and  $\approx 2N$  in the adjust-multiply unit). This can be reduced to  $\approx 3(N_1 + N_2)$  by mapping the one-dimensional transform into two dimensions. In Section 2.3.2 we describe such a transformation.

#### 2.2.3 Related work

We have seen earlier in this section that the existing algorithms for computing one-dimensional DHT and DCT over N points can be divided into two classes: N is a power of 2 and N is factorizable into mutually prime factors  $N_1$  and  $N_2$ . For the case when N is a power of 2, an FFT-like structure is obtained for both DHT and DCT. For the case when  $N = N_1 N_2$  and  $N_1$ ,  $N_2$  are mutually prime, the one-dimensional transform is mapped into a two-dimensional transform over  $(N_1 \times N_2)$  points with appropriate input and output index mappings.

When N is a power of 2, the VLSI architectures for DCT map the butterfly-like flow diagram of a fast algorithm directly into silicon [12, 29, 53]. The multipliers are replaced by ROM accumulators which incorporate distributed arithmetic in the architectures of [12, 53]. The architectures for DHT consist of CORDIC processors and systolic shuffle units [44], or their pipelined variations [48].

When N is factorizable into mutually prime factors, the DCT implementation of [57] is not special-purpose and contains complicated arithmetic and control units. Recently [14] proposed an algorithm for DCT with the additional constraint that  $N_1$  and  $N_2$  are odd. The architecture of [14] consists of two DFT computation units of [47] and an additional multiplier unit to rotate the DFT output. The number of multipliers in their architecture is  $2f(N_1)+4f(N_2)+4N_2$ , where f(N) is the number of multipliers required to compute an N point DFT on real data.

Both DHT and DCT can be implemented by a systolic architecture based on the matrix-vector algorithm. There exist linear array architectures for DCT [14, 55] which consist of N multipliers. The data flow of the DCT coefficients for both these architectures is complicated. The architecture of [13] is a CCD implementation of the matrix-vector algorithm and consists of  $N^2$  fixed multipliers.

# 2.3 Mapping into two dimensions

Any one-dimensional linear transform over N points,

$$f(k) = \sum_{n} a(k, n)x(n), \quad 0 \le n, k \le N - 1$$

(2.7)

can be mapped into a two-dimensional transform over  $(N_1 \times N_2)$  points,  $N = N_1N_2$ , by choosing the input and output index mappings appropriately. We assume that  $N_1$  and  $N_2$  are mutually prime. Let  $\mathcal{N}$  be the set of integers 0 through N-1, let  $\mathcal{N}_1$  be the set of integers 0 through  $N_1-1$  and let  $\mathcal{N}_2$  be the set of integers 0 through  $N_2-1$ . Let  $g_1(n)=(n_1,n_2)$  be the input index mapping from  $\mathcal{N}$  to  $\mathcal{N}_1 \times \mathcal{N}_2$ ,  $n \in \mathcal{N}$ ,  $n_1 \in \mathcal{N}_1$ ,  $n_2 \in \mathcal{N}_2$  and let  $g_2(k)=(k_1,k_2)$  be the output index mapping from  $\mathcal{N}$  to  $\mathcal{N}_1 \times \mathcal{N}_2$ ,  $k \in \mathcal{N}$ ,  $k_1 \in \mathcal{N}_1$ ,  $k_2 \in \mathcal{N}_2$ . If  $g_1$  and  $g_2$  are one-to-one, then f(k) can be mapped into a two-dimensional function  $f(k_1, k_2)$ , where

$$f(k_1, k_2) = \sum_{n_2} \sum_{n_1} a(k_1, k_2, n_1, n_2) x(n_1, n_2).$$

(2.8)

The main motive behind this transformation is to map the computation into a systolic two-dimensional array of size  $(N_1 \times N_2)$ . The ideal transformation

would be such that expression 2.8 can be computed by a set of column(row) operations on the two-dimensional data followed by a set of row(column) operations. The number of bit-serial systolic steps  $^2$  will then be reduced from O(bN) to  $O(b(N_1+N_2))$ , where b is the precision. In this section we briefly discuss such transformations for one-dimensional DHT and DCT and then sketch procedures to execute them by systolic arrays.

## 2.3.1 Mapping of DHT

One-dimensional DHT, H(k), can be mapped into a two-dimensional DHT,  $H(k_1, k_2)$ ,

$$H(k_1, k_2) = \sum_{n_2=0}^{N_2-1} \sum_{n_1=0}^{N_1-1} x(n_1, n_2) cas\left(\frac{2\pi}{N_1} n_1 k_1 + \frac{2\pi}{N_2} n_2 k_2\right),$$

(2.9)

with the following input and output index mappings [2]

$$n = N_2 n_1 + N_1 n_2 \mod N$$

$$k = (N_2^{-1} \mod N_1) N_2 k_1 + (N_1^{-1} \mod N_2) N_1 k_2 \mod N.$$

(2.10)

Since in general,  $cas(\alpha + \beta) \neq cas(\alpha)cas(\beta)$ , equation 2.9 is not a simple DHT over columns of  $x(n_1, n_2)$  followed by a DHT over rows.

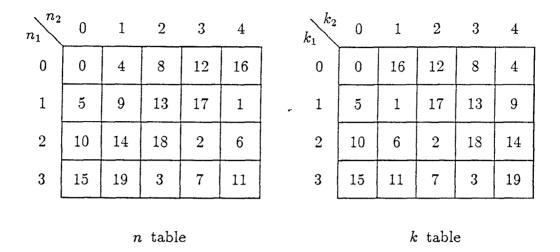

Figure 2.5 illustrates the input and output index mappings for an example where N = 20 ( $N_1 = 4$ ,  $N_2 = 5$ ). The mappings are represented in the form of tables with  $N_1$  rows and  $N_2$  columns, such that location ( $n_1, n_2$ ) of the input  $\frac{1}{2}$  bit-serial systolic step is a 1-bit computation step (add, subtract, delay) in bit-serial systolic architectures.

Figure 2.5: Input and output index mappings for DHT over  $(4 \times 5)$  points index mapping table contains n and location  $(k_1, k_2)$  of the output index mapping table contains k (refer to equation 2.10).

Sorensen, et.al. [52] proposed a method of computing  $H(k_1, k_2)$  by computing  $DHT(N_1)$  over columns of the data array, followed by combining some of the elements of the intermediate array and then computing  $DHT(N_2)$  over rows of the resulting array. The method proposed by Bracewell, et.al. [3], on the other hand, consists of computing  $DHT(N_1)$  over columns of the data array followed by  $DHT(N_2)$  over rows of the intermediate array and then combining some of the elements of the resulting array.

The scheme proposed in [52] is summarized as follows. Let

$$A(k_1, n_2) = \sum_{n_1=0}^{N_1-1} x(n_1, n_2) cas\left(\frac{2\pi}{N_1} n_1 k_1\right), \qquad (2.11)$$

be the outcome after computing  $DHT(N_1)$  of the columns, and let

$$B(k_1, n_2) = \frac{1}{2} (A(k_1, n_2) + A(N_1 - k_1, n_2) + A(k_1, N_2 - n_2) - A(N_1 - k_1, N_2 - n_2)).$$

(2.12)

Then  $H(k_1, k_2)$  is obtained by computing  $DHT(N_2)$  over rows of array B.

$$H(k_1, k_2) = \sum_{n_2=0}^{N_2-1} B(k_1, n_2) cas\left(\frac{2\pi}{N_2} n_2 k_2\right)$$

(2.13)

The algorithm for DHT(N) [52] can then be expressed as follows.

- 1. Compute  $DHT(N_1)$  over columns.

- 2. Compute B from A (equation 2.12).

- 3. Compute  $DHT(N_2)$  over rows.

Steps 1 and 3 can be mapped directly into a systolic architecture consisting of summation and scaling units (refer to Section 2.2.1). Step 2 can be computed by a systolic unit after modifying Steps 1 and 3 appropriately [8].

We next describe the scheme proposed by [3] for computing  $H(k_1, k_2)$ . We will describe it in details because of its similarity with the DCT algorithm (see Section 2.3.2). Let  $T(k_1, k_2)$  be the temporary outcome obtained after computing DHT of the columns followed by DHT of the rows.

$$T(k_1, k_2) = \sum_{n_2=0}^{N_2-1} \left\{ \sum_{n_1=0}^{N_1-1} x(n_1, n_2) cas(\frac{2\pi}{N_1} n_1 k_1) \right\} cas(\frac{2\pi}{N_2} n_2 k_2)$$

(2.14)

Then  $H(k_1, k_2)$  can be expressed as the sum of four temporary outcomes.

$$H(k_1, k_2) = \frac{1}{2} (T(k_1, k_2) + T(N_1 - k_1, k_2) + T(k_1, N_2 - k_2) - T(N_1 - k_1, N_2 - k_2))$$

$$(2.15)$$

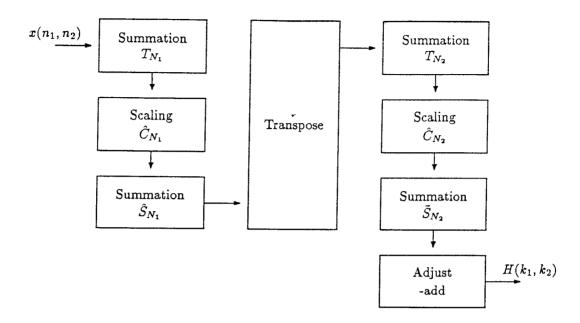

Figure 2.6: Block diagram for computing two-dimensional DHT over  $(N_1 \times N_2)$  points, where  $N_1$ ,  $N_2$  are mutually prime

Note that  $H(N_1 - k_1, k_2)$ ,  $H(k_1, N_2 - k_2)$  and  $H(N_1 - k_1, N_2 - k_2)$  can also be expressed as sums of  $T(k_1, k_2)$ ,  $T(N_1 - k_1, k_2)$ ,  $T(k_1, N_2 - k_2)$  and  $T(N_1 - k_1, N_2 - k_2)$ . The algorithm for DHT(N) [3] is as follows.

- 1. Compute  $DHT(N_1)$  over columns.

- 2. Compute  $DHT(N_2)$  over rows.

- 3. Compute H from T (equation 2.15).

Steps 1 and 2 can be mapped directly into summation and scaling units (refer to Section 2.2.1). Since  $\mathrm{DHT}(N_1)$  is computed over columns and  $\mathrm{DHT}(N_2)$  is computed over rows, a systolic transpose unit is needed to transpose the

intermediate result obtained after computing DHT( $N_1$ ) over columns. Step 3 can be mapped into a systolic unit called the *adjust-add* unit. Figure 2.6 shows the interconnections of the various units for DHT over ( $N_1 \times N_2$ ) points, where  $N_1$ ,  $N_2$  are mutually prime.

We next describe the modifications in the algorithm for DHT(N) that are required in order that the adjust-add unit (see Figure 2.6) be systolic. The algorithm has to be tailored so that  $T(k_1, k_2)$ ,  $T(N_1 - k_1, k_2)$ ,  $T(k_1, N_2 - k_2)$  and  $T(N_1-k_1,N_2-k_2)$  are adjacent to each other. This can be done by permuting the rows of  $Y(k_1, n_2)$  after computing Step 1 of the algorithm and by permuting the columns of  $T(k_1, k_2)$  after computing Step 2. The row permutation is such that  $Y(k_1, n_2)$  and  $Y(N_1 - k_1, n_2)$  are adjacent to each other for  $1 \le k_1 \le k_1$  $\lceil N_1/2 \rceil - 1$ ,  $0 \le n_2 \le N_2 - 1$ . Such a permutation is possible by embedding  $\hat{S}_{N_1}$  (instead of  $S_{N_1}$ ) in the summation unit of DHT( $N_1$ ), where  $\hat{S}_{N_1} = P_{N_1} S_{N_1}$ (refer to Section 2.2.2). Similarly the column permutation is such that  $T(k_1, n_2)$ and  $T(k_1, N_2 - n_2)$  are adjacent to each other for  $0 \le k_1 \le N_1 - 1$  and  $1 \le n_1 \le n_2 \le n_2$  $n_2 \leq \lceil N_2/2 \rceil - 1$ . This is possible by embedding  $\hat{S}_{N_2}$  (instead of  $S_{N_2}$ ) in the summation unit of DHT( $N_2$ ), where  $\hat{S}_{N_2} = P_{N_2} S_{N_2}$ . Note that since  $P_{N_1}$  and  $P_{N_2}$  are permutation matrices,  $\hat{S}_{N_1}$  and  $\hat{S}_{N_2}$  are incidence matrices and hence can be directly mapped into summation units. Figure 2.7 illustrates the row permutation in intermediate data array Y as a result of embedding  $\hat{S}_4$  in the summation unit in the computation of DHT(4) over columns for the example where N = 20  $(N_1 = 4, N_2 = 5)$ .

The next step in the procedure is to efficiently compute  $H(k_1, k_2)$ ,  $H(N_1 -$

$$\begin{bmatrix} Y_{0,0} & Y_{0,1} & Y_{0,2} & Y_{0,3} & Y_{0,4} \\ Y_{1,0} & Y_{1,1} & Y_{1,2} & Y_{1,3} & Y_{1,4} \\ Y_{3,0} & Y_{3,1} & Y_{3,2} & Y_{3,3} & Y_{3,4} \\ Y_{2,0} & Y_{2,1} & Y_{2,2} & Y_{2,3} & Y_{2,4} \end{bmatrix}$$

Figure 2.7: Row permutation in intermediate data array Y after computing DHT(4) over columns during the computation of DHT over  $(4 \times 5)$  points

$k_1, k_2$ ),  $H(k_1, N_2 - k_2)$  and  $H(N_1 - k_1, N_2 - k_2)$  from  $T(k_1, k_2)$ ,  $T(N_1 - k_1, k_2)$ ,  $T(k_1, N_2 - k_2)$  and  $T(N_1 - k_1, N_2 - k_2)$  using a systolic unit. Let  $A = T(k_1, k_2)$ ,  $B = T(N_1 - k_1, k_2)$ ,  $C = T(k_1, N_2 - k_2)$ ,  $D = T(N_1 - k_1, N_2 - k_2)$ . Then  $H(k_1, k_2) = \frac{1}{2}(A + B + C - D)$ . In the algorithm proposed by [3],  $H(k_1, k_2)$  is obtained by computing the 'diagonal excess' defined by E = 1/2[(A + D) - (B + C)] and then doing in-place replacement of the form  $A \leftarrow A - E$ ,  $B \leftarrow B + E$ ,  $C \leftarrow C + E$  and  $D \leftarrow D - E$ . Though this algorithm employs only seven adds and one shift per four outputs, the systolic implementation is cumbersome. Since the adjustments for A, B, C and D are different, an additional control input line is required to distinguish between data  $T(k_1, k_2)$  and  $T(N_1 - k_1, k_2)$  for all  $k_2$ , that is, between A and B, C and D. This increases the complexity of the circuit.

Here we suggest a method to compute H from T with simpler systolic implementation. Let Z be the new temporary outcome defined by

$$Z(k_1, k_2) = \frac{1}{2} [T(k_1, k_2) + T(k_1, N_2 - k_2)]$$

$$Z(k_1, N_2 - k_2) = \frac{1}{2} [T(k_1, k_2) - T(k_1, N_2 - k_2)]$$

(2.16)

for  $1 \le k_1 \le N_1 - 1$  and  $1 \le k_2 \le \lceil N_2/2 \rceil - 1$ . Then H can be defined by

$$H(k_1, k_2) = Z(k_1, k_2) + Z(N_1 - k_1, N_2 - k_2)$$

$$H(k_1, N_2 - k_2) = Z(k_1, k_2) - Z(N_1 - k_1, N_2 - k_2).$$

(2.17)

Note that  $H(k_1,0) = Z(k_1,0) = T(k_1,0)$ ,  $H(0,k_2) = Z(0,k_2) = T(0,k_2)$  and in addition, if  $N_1$  is even,  $H(N_1/2,k_2) = Z(N_1/2,k_2) = T(N_1/2,k_2)$ , and if  $N_2$  is even,  $H(k_1,N_2/2) = Z(k_1,N_2/2) = T(k_1,N_2/2)$ . This scheme employs only one add per output. Moreover no additional control input line is required. There is no need for an extra unit to compute Z from T (equation 2.16).  $Z(k_1,k_2)$  can be obtained at the end of Step 2 (instead of  $T(k_1,k_2)$ ) by modifying the matrix  $\hat{S}_{N_2}$  that is embedded in the summation unit of DHT( $N_2$ ) in the following way.

Let  $\dot{T} = \hat{S}_{N_2} \hat{C}_{N_2} T_{N_2} Y$ , where  $\dot{T}$  is a permutation of the temporary matrix T such that  $T(k_1, k_2)$ ,  $T(N_1 - k_1, k_2)$ ,  $T(k_1, N_2 - k_2)$  and  $T(N_1 - k_1, N_2 - k_2)$  are adjacent to each other, Y is the output after computing DHT $(N_1)$  over columns and  $\hat{S}_{N_2}$ ,  $\hat{C}_{N_2}$  and  $T_{N_2}$  are defined as before. Z can be expressed as  $Q_{N_2} \dot{T}$ , where the matrix  $Q_{N_2}$  has the following characteristics:

$$Q_{N_2}(0,0)=1$$

For odd  $i, \qquad Q_{N_2}(i,i)=0.5, \qquad \qquad Q_{N_2}(i,i+1)=0.5$  For even  $i$  and  $i\neq 0, \qquad Q_{N_2}(i,i)=-0.5, \qquad \qquad Q_{N_2}(i,i-1)=0.5,$

$1 \leq i \leq N_2 - 1$ . In addition, if  $N_2$  is even,  $Q(N_1 - 1, N_2 - 1) = 1$ . Thus by modifying  $\hat{S}_{N_2}$  to  $\tilde{S}_{N_2}$ , where  $\hat{S}_{N_2} = Q_{N_2} \hat{S}_{N_2}$ ,  $Z(k_1, k_2)$  is obtained at the

$$Q_{5} = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0.5 & 0.5 & 0 & 0 \\ 0 & 0.5 & -0.5 & 0 & 0 \\ 0 & 0 & 0 & 0.5 & 0.5 \\ 0 & 0 & 0 & 0.5 & -0.5 \end{pmatrix}, \qquad \tilde{S}_{5} = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & -1 & 0 \\ 1 & 1 & -1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 1 \end{pmatrix}$$

Figure 2.8: Matrices  $Q_5$  and  $\hat{S}_5$  in the computation of DHT(5)

end of Step 2. The nature of  $Q_{N_2}$  and  $\hat{S}_{N_2}$  3 is such that their product is an incidence matrix. This means that  $\tilde{S}_{N_2}$  can be mapped into a summation unit. Figure 2.8 describes the matrices  $Q_5$  and  $\tilde{S}_5$ . Figure 2.9 describes the column permutation in data array Z as a result of embedding  $\tilde{S}_5$  in the summation unit in the computation of DHT(5) over rows for the example where N=20  $(N_1=4, N_2=5)$ . Note that  $Z(k_1, k_2)$ ,  $Z(N_1-k_1, k_2)$ ,  $Z(k_1, N_2-k_2)$  and  $Z(N_1-k_1, N_2-k_2)$  are adjacent to each other.

The 'adjust-add' unit in Figure 2.6 is a systolic unit which computes H from Z (see equation 2.17). Its design is simpler than that of the systolic unit which computes H from T. We will describe it in Section 2.4.

<sup>&</sup>lt;sup>3</sup>For all known small N algorithms,  $\hat{S}_N$  is such that either both or none of the (i, j)th and (i+1, j)th element is 0, for i odd and  $1 \le i \le N-2$ . This is because  $S_N$  is such that either both or none of the (i, j)th and (N-1, j)th element is  $0, 1 \le i \le \lceil N/2 \rceil - 1$ .

$$\begin{bmatrix} Z_{0,0} & Z_{0,1} & Z_{0,4} & Z_{0,2} & Z_{0,3} \\ Z_{1,0} & Z_{1,1} & Z_{1,4} & Z_{1,2} & Z_{1,3} \\ Z_{3,0} & Z_{3,1} & Z_{3,4} & Z_{3,2} & Z_{3,3} \\ Z_{2,0} & Z_{2,1} & Z_{2,4} & Z_{2,2} & Z_{2,3} \end{bmatrix}$$

Figure 2.9: Column permutation in intermediate data array Z after computing DHT(5) over rows during the computation of DHT over  $(4 \times 5)$  points

# 2.3.2 Mapping of DCT

The existing algorithms for prime-factor decomposed DCT computation consists of computing  $DCT(N_1)$  over columns, followed by computing  $DCT(N_2)$  over rows, followed by combining the elements of the resulting data array [39, 57]. We develop a systolic architecture based on a modified version of the algorithm proposed by Lee [39]. Let  $T(k_1, k_2)$  be the output after computing  $DCT(N_1)$  over columns followed by  $DCT(N_2)$  over rows [39].

$$T(k_1, k_2) = \sum_{n_2=0}^{N_2-1} \left\{ \sum_{n_1=0}^{N_1-1} x(n_1, n_2) \cos\left[\frac{\pi}{2N_1} (2n_1 + 1)k_1\right] \right\} \cos\left[\frac{\pi}{2N_2} (2n_2 + 1)k_2\right]$$

(2.18)

We have seen in Section 2.2.2 how one-dimensional DCT can be computed from one-dimensional DHT if the cosine argument is  $\cos\left[\frac{\pi}{2N}(4n+1)k\right]$  (instead of  $\cos\left[\frac{\pi}{2N}(2n+1)k\right]$ ). The cosine argument can be changed by appropriate choice of input index mapping.

|          | $n_1$ $n_2$ | 0  | 1  | 2  | 3  | 4  |

|----------|-------------|----|----|----|----|----|

| n table: | 0           | 0  | 7  | 15 | 16 | 8  |

|          | 1           | 10 | 2. | 5  | 13 | 18 |

|          | 2           | 19 | 12 | 4  | 3  | 11 |

|          | 3           | 9  | 17 | 14 | 6  | 1  |

Figure 2.10: Input index mapping for DCT over  $(4 \times 5)$  points

We propose the following input index mapping  $g_1(n) = (n_1, n_2)$ . Let

$$\bar{n}_1 = n \mod 2N_1$$

$$\bar{n}_2 = n \mod 2N_2$$

$$n_1 = \begin{cases}

\bar{n}_1/2 & \text{if } \bar{n}_1 \text{ is even} \\

N_1 - (\bar{n}_1 + 1)/2 & \text{otherwise}

\end{cases}$$

$$n_2 = \begin{cases}

\bar{n}_2/2 & \text{if } \bar{n}_2 \text{ is even} \\

N_2 - (\bar{n}_2 + 1)/2 & \text{otherwise}

\end{cases}$$

(2.19)

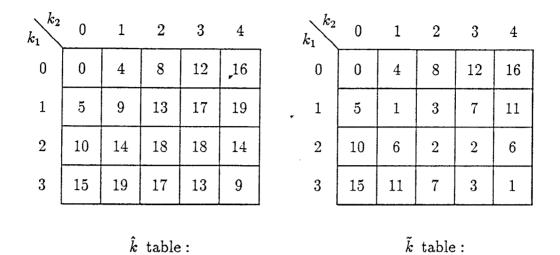

It can be easily shown that  $g_1$  is a one-to-one mapping. Figure 2.10 describes the input index mapping for an example where N = 20 ( $N_1 = 4, N_2 = 5$ ). The index mapping is represented in the form of a table with  $N_1$  rows and  $N_2$  columns, where location  $(n_1, n_2)$  of the table contains n (see equation 2.19). With this index mapping let  $\hat{T}(k_1, k_2)$  be the new temporary outcome defined by

$$\dot{T}(k_1, k_2) = \sum_{n_2=0}^{N_2-1} \left\{ \sum_{n_1=0}^{N_1-1} x(n_1, n_2) \cos\left[\frac{\pi}{2N_1} (4n_1 + 1)k_1\right] \right\} \cos\left[\frac{\pi}{2N_2} (4n_2 + 1)k_2\right].$$

(2.20)

Figure 2.11: Output index mapping for DCT over  $(4 \times 5)$  points Thus  $T(k_1, k_2)$  is the output obtained after computing DCT over columns followed by DCT over rows.

We define the output index mapping along the same lines as the input index mapping of [39]. Let  $\hat{f}$  and  $\tilde{f}$  be mappings from  $\mathcal{N}_1 \times \mathcal{N}_2$  to  $\mathcal{N}$  such that