# THESIS REPORT

Supported by the National Science Foundation Engineering Research Center Program (NSFD CD 8803012), the University of Maryland, Harvard University, and Industry

# VLSI Algorithms and Architectures for Time-Recursive Discrete Sinuoidal Transforms with Applications to Real-Time Video Communications

by C-T. Chiu Advisor: K.J.R. Liu

### **Abstract**

Title of Dissertation: VLSI Algorithms and Architectures

for Time-Recursive Discrete Sinuoidal

Transforms with Applications to Real-Time Video Communications

Ching-Te Chiu, Doctor of Philosophy, 1992

Dissertation directed by: Assistant Professor K. J. Ray Liu

Department of Electrical Engineering

In this dissertation, we address the problem of developing efficient VLSI algorithms and architectures for discrete sinusoidal transforms in real-time applications for video communication systems. The major difficulty of this problem is that the resulting architectures should compute a huge amount of data at very high speed for real-time video applications and match the requirement of VLSI architectures, regularity, modularity and locality. In traditional FFT based algorithms, the serial data is buffered and then transformed using the FFT scheme.

We propose a "time-recursive" approach to perform transforms that merge the buffering and transform operations into a single unit. The transformed data are updated according to a recursive formula, whenever a new datum arrives. Therefore the waiting time is completely eliminated. The unified lattice and IIR architectures for time-recursive transforms are proposed. The resulting architectures are regular, modular, and have only local interconnections and are better suited for VLSI implementations. There is no limitation on the transform size N and the number of multipliers required for computing the DCT by lattice and IIR structures are 6N-8 and 2N-2 respectively. In the case of dual generation of the DCT and DST by IIR structure, only 1.5N multipliers are required for each transform on average. The throughput of this scheme is one input sample per clock cycle.

We also apply the time-recursive approach to multidimensional separable transforms. The resulting d-dimensional structures are fully-pipelined and consist of only d 1-D transform arrays and shift registers for computing a d-D DXT. The delay time due to transpositions of the conventional d-D transforms is eliminated in our approach. It is shown that the architecture is optimal in the sense that the number of the multipliers used is minimum and both speed and area are asymptotically optimal.

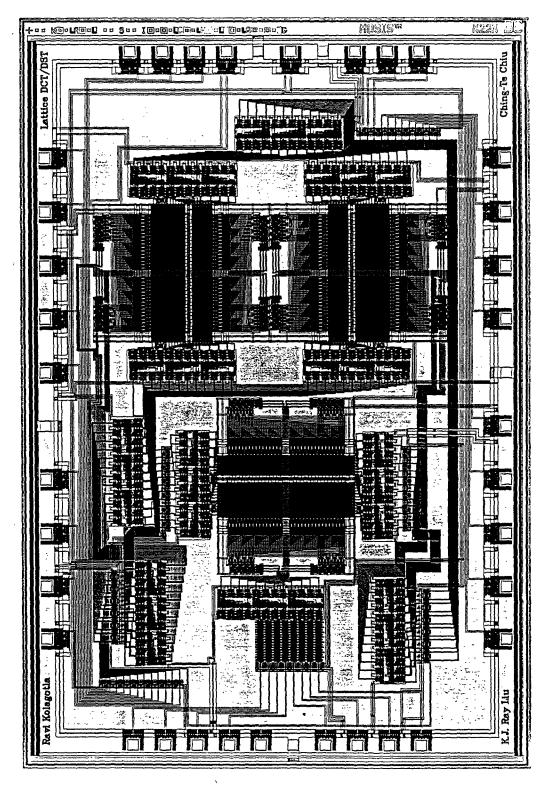

The VLSI implementation of the lattice module based on the distributed arithmetic is also described. The chip can dually generate the DCT and DST simultaneously. It has been fabricated under  $2\mu m$  double-metal CMOS technology and tested to be fully functional with a throughput rate 14.5-MHz and a data processing rate of 116Mb/s.

# VLSI Algorithms and Architectures for Time-Recursive Discrete Sinuoidal Transforms with Applications to Real-Time Video Communications

by

### Ching-Te Chiu

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland in partial fulfillment of the requirements for the degree of Doctor of Philosophy

1992

### Advisory Committee:

Assistant Professor K. J. Ray Liu, Chairman/Advisor

Professor Joseph F. JáJá

Professor Ramalingam Chellappa

Professor Robert Newcomb

Associate Professor Clyde P. Kruskal

# Dedication

To MY DEAR HUSBAND, CHIEN-JEN(SIMON) CHEN for his support, consideration and infinite love.

To MY LOVELY SON, MARK(SHIN-HANN) CHEN for being the enjoyable source of my life.

|  |  | · |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

# Acknowledgements

First and foremost, I would like to express my gratitude to my advisor, K. J. Ray Liu for his guidance, sustained encouragement and support throughout my graduate study. His brilliant problem-shooting skills and dedication to work will always be an inspiration to me.

I would like to thank Prof. Joseph Ja'Ja' for his valuable discussions and comments on my thesis. I would also like to thank the other members of my thesis committee: Profs. Rama Chellappa, Robert Newcomb, and Clyde Kruskal for their insightful comments and suggestions and thank Profs. Yung Ju Chen and Neil Goldsman for helping me in various ways during my study in Maryland.

I would like to thank the Systems Research Center, Electrical Engineering Department, and the National Science Fundation under the grant ECD-8803012 for giving me the financial support and providing excellent resources and study environment.

I am grateful to Ravi Kolagotla for collaborating the DCT/DST projects and also to many friends here for their help in using computer facilities: Ying-Min Huang, Jenn-Sen Leu, Hung-WeinChiou, Nol Ranaand, Shu-Suu Yu, Po-Yang F. Lin, Nam Phamdo, Vishnuuss Srinivasan, Xiaonong Ran, Guu-Chang Yang, and An-Yeu Wu.

I would like to thank my family: my husband, my son, my parents, and my parents-in-law, for their spiritual support and encouragement throughout my study.

# Contents

| Li | st of | Tables                                                               | ix |

|----|-------|----------------------------------------------------------------------|----|

| Li | st of | Figures                                                              | xi |

| 1  | Intr  | oduction                                                             | 1  |

|    | 1.1   | Standards on the video coding systems                                | 2  |

|    | 1.2   | Significances and applications of various discrete sinusoidal trans- |    |

|    |       | forms                                                                | 5  |

|    | 1.3   | Evolution of the algorithms and architectures                        | 6  |

|    | 1.4   | Motivation                                                           | 7  |

|    | 1.5   | Main contribution                                                    | 9  |

|    | 1.6   | Organization                                                         | 11 |

| 2  | Para  | allel Lattice Structures                                             | 13 |

|    | 2.1   | Introduction                                                         | 14 |

|    | 2.2   | Dual Generation of DCT and DST                                       | 15 |

|    |       | 2.2.1 Time-Recursive Discrete Cosine Transform                       | 16 |

|    |       | 2.2.2 Time-Recursive Discrete Sine Transform                         | 17 |

|    |       | 2.2.3 The Lattice Structures                                         | 17 |

|    | 2.3   | Inverse Transforms                                                   | 24 |

|   |     | 2.3.1 Time-Recursive IDCT                                      | 24       |

|---|-----|----------------------------------------------------------------|----------|

|   |     | 2.3.2 Time-Recursive IDST                                      | 27       |

|   | 2.4 | Discrete Hartley Transform (DHT)                               | 31       |

|   | 2.5 | Block Processing                                               | 34       |

|   |     | 2.5.1 Block Processing of time-recursive DCT and DST 3         | 34       |

|   | 2.6 | Multiplier-Reduction of the lattice structure                  | 39       |

|   |     | 2.6.1 <i>SISO</i> Approach                                     | 39       |

|   |     | 2.6.2 Double-lattice Approach                                  | 45       |

|   | 2.7 | Comparisons of Architectures                                   | 47       |

|   | 2.8 | Filter Bank Interpretation                                     | 52       |

|   |     | 2.8.1 Synthesis bank structure based on DCT 5                  | 52       |

|   |     | 2.8.2 Synthesis bank structure of the DST and DHT 5            | 55       |

|   | 2.9 | Summary                                                        | 57       |

| 3 | Two | o-Dimensional DCT Lattice Structures 5                         | 59       |

|   | 3.1 | Introduction                                                   | 60       |

|   | 3.2 | Dual Generation of 2-D DCT and DSCT                            | 63       |

|   |     | 3.2.1 Frame-Recursive 2-D Discrete Cosine Transform 6          | 63       |

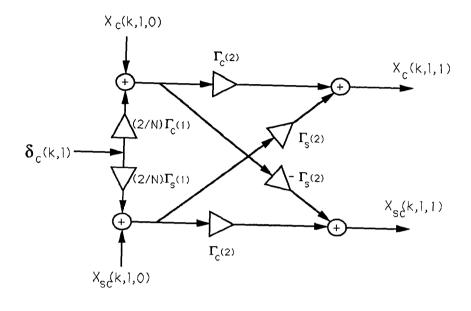

|   |     | 3.2.2 Lattice structures for frame-recursive 2D-DCT 6          | 66       |

|   | 3.3 | Architectures of Frame-Recursive Lattice 2D-DCT and 2-D DSCT 7 | 70       |

|   |     |                                                                |          |

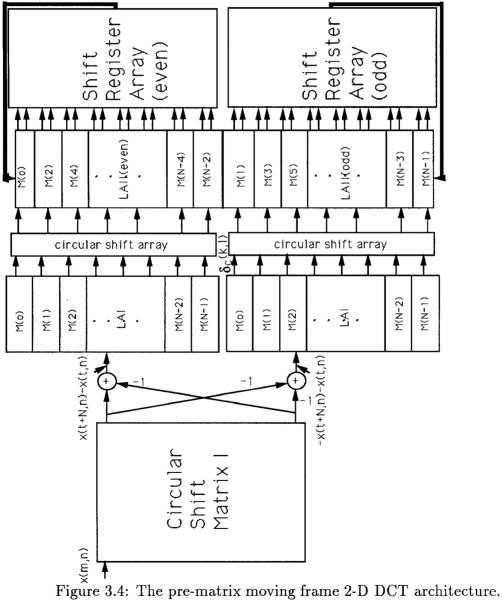

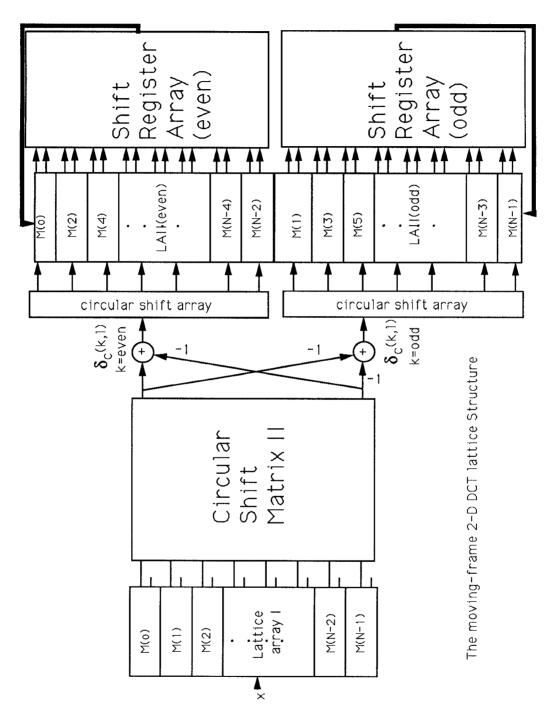

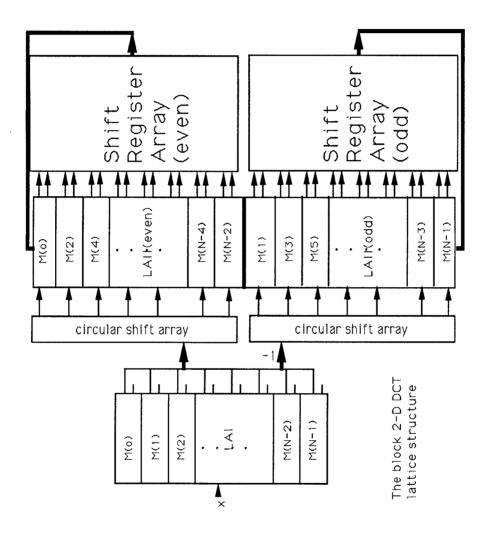

|   |     | 3.3.1 The Moving Frame 2-D DCT Architectures                   | 71       |

|   |     | 3.3.1 The Moving Frame 2-D DCT Architectures                   |          |

|   | 3.4 |                                                                | 78       |

|   | 3.4 | 3.3.2 The Block 2-D DCT Architecture                           | 78<br>82 |

| 4 | Op                                                        | otimal Unified IIR Architectures                                        | 92                                                                                                                  |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|   | 4.1                                                       | Introduction                                                            | . 93                                                                                                                |

|   | 4.2                                                       | Lattice Structure for Discrete Sinusoidal Transforms                    | . 95                                                                                                                |

|   | 4.3                                                       | Optimal Time-Recursive Architectures                                    | . 99                                                                                                                |

|   |                                                           | 4.3.1 Transfer Function Approach                                        | . 99                                                                                                                |

|   |                                                           | 4.3.2 The Unified IIR Filter Architectures                              | . 102                                                                                                               |

|   | 4.4                                                       | Architectures for Inverse Transforms                                    | . 108                                                                                                               |

|   | 4.5                                                       | Theoretical Basis                                                       | . 111                                                                                                               |

|   | 4.6                                                       | Time-Recursive Multi-dimensional Transforms                             | . 120                                                                                                               |

|   |                                                           | 4.6.1 Time-Recursive Structures for 3-D DCT                             | . 120                                                                                                               |

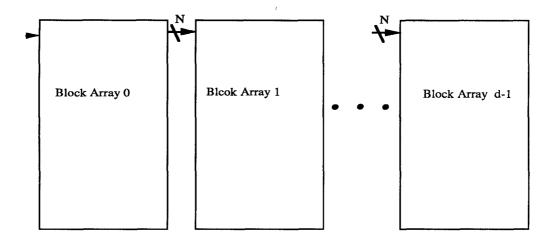

|   |                                                           | $4.6.2  \hbox{Time-Recursive Structures for Multi-Dimensional DXT} \ .$ | . 130                                                                                                               |

|   | 4.7                                                       | Summary                                                                 | . 135                                                                                                               |

| 5 | <b>T</b> 7 <b>T</b>                                       | CI Il                                                                   |                                                                                                                     |

| J | VΙ                                                        | LSI Implementation of DCT/DST Lattice Structures                        | 137                                                                                                                 |

| J | 5.1                                                       | Introduction                                                            |                                                                                                                     |

| J |                                                           |                                                                         | . 138                                                                                                               |

| J | 5.1                                                       | Introduction                                                            | . 138                                                                                                               |

|   | 5.1<br>5.2                                                | Introduction                                                            | <ul><li>. 138</li><li>. 139</li><li>. 143</li></ul>                                                                 |

|   | 5.1<br>5.2                                                | Introduction                                                            | <ul><li>. 138</li><li>. 139</li><li>. 143</li><li>. 143</li></ul>                                                   |

|   | 5.1<br>5.2                                                | Introduction                                                            | <ul><li>. 138</li><li>. 139</li><li>. 143</li><li>. 143</li><li>. 148</li></ul>                                     |

|   | 5.1<br>5.2                                                | Introduction                                                            | <ul><li>. 138</li><li>. 139</li><li>. 143</li><li>. 143</li><li>. 148</li><li>. 148</li></ul>                       |

|   | 5.1<br>5.2                                                | Introduction                                                            | <ul><li>. 138</li><li>. 139</li><li>. 143</li><li>. 148</li><li>. 148</li><li>. 148</li></ul>                       |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Introduction                                                            | <ul> <li>. 138</li> <li>. 139</li> <li>. 143</li> <li>. 148</li> <li>. 148</li> <li>. 148</li> <li>. 150</li> </ul> |

|   | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduction                                                            | . 138<br>. 139<br>. 143<br>. 143<br>. 148<br>. 148<br>. 150                                                         |

References 171

# List of Tables

| 2.1 | Comparison of different DCT algorithms                             | 8  |

|-----|--------------------------------------------------------------------|----|

| 2.2 | Comparision of the number of multipliers                           | .9 |

| 2.3 | Comparision of the number of adders                                | 9  |

| 2.4 | Comparision of the latency                                         | .9 |

| 2.5 | Comparision of different DHT algorithms,*m.p. means "mutual        |    |

|     | prime" 5                                                           | 1  |

| 3.1 | Comparisons of different 2-D DCT algorithms                        | 34 |

| 3.2 | Comparisions of the number of multipliers                          | 35 |

| 3.3 | Comparisions of the number of adders                               | 35 |

| 4.1 | Coefficients of the Lattice structure for the DXT                  | 8  |

| 4.2 | Coefficients of the universal IIR filter structure for the DXT 10  | 3  |

| 4.3 | Number of multipliers and adders for different transforms with     |    |

|     | IIR filter realizations(Here * denotes complex operations) 10      | 6  |

| 4.4 | Corresponding coefficients in the Recurrence Formula for different |    |

|     | DXT11                                                              | 3  |

| 5.1 | Summary of the DCT lattice module chip                             | 6  |

| 5.2 | The SNR of different channels under 17 bit 2's commplement re-     |    |

|     | alization for lattice structure with reset                         | 2  |

| 5.3 | The SNR of different channels under 12 bit 2's commplement re-    |

|-----|-------------------------------------------------------------------|

|     | alization for lattice structure with reset                        |

| 5.4 | The SNR of different channels under 17 bit 2's commplement re-    |

|     | alization for lattice structure without reset                     |

| 5.5 | The SNR of different channels under 12 bit 2's commplement re-    |

|     | alization for lattice structure with reset                        |

| 5.6 | The SNR of different channels for IIR realization with reset 165  |

| 5.7 | The SNR of different channels for direct form IIR structure with- |

|     | out reset                                                         |

# List of Figures

| 2.1  | The lattice module                                                 | 18 |

|------|--------------------------------------------------------------------|----|

| 2.2  | The lattice structure for the DCT and DST with coefficients        |    |

|      | C(k)'s and $D(k)$ 's, $k = 0, 1, 2,, N - 1, N$                     | 21 |

| 2.3  | The parallel lattice structure for the DCT and DST                 | 22 |

| 2.4  | The lattice structure for the IDCT and AIDST                       | 26 |

| 2.5  | The pre-lattice structure for the IDST and AIDCT                   | 29 |

| 2.6  | The post-lattice structure for the IDST and AIDCT                  | 30 |

| 2.7  | The lattice structure for the DHT for $k=1,2,,N-1$                 | 33 |

| 2.8  | The lattice structure for the DHT for $k=0,\ldots,\ldots$          | 34 |

| 2.9  | The lattice structure for block-size-two operation on the DCT and  |    |

|      | DST                                                                | 36 |

| 2.10 | The lattice structure for block-size- $m$ operation on the DCT and |    |

|      | DST                                                                | 38 |

| 2.11 | The general lattice module                                         | 40 |

| 2.12 | The model of multiplier-reduction.                                 | 40 |

| 2.13 | The multiplier-reduced lattice module                              | 43 |

| 2.14 | The complete parallel multiplier-reduced lattice structure         | 44 |

| 2.15 | The double-lattice form of the post-lattice realization            | 47 |

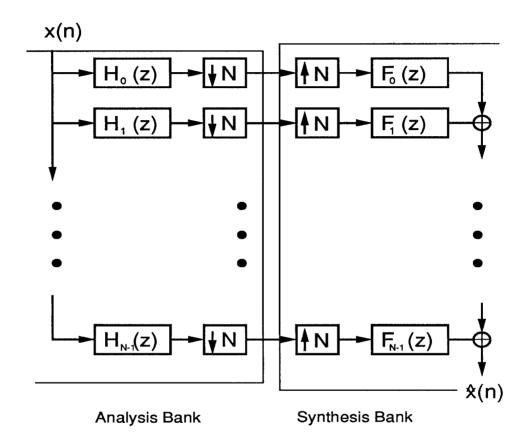

| 2.16 | The filter bank structure                                          | 53 |

| 2.17                                          | The synthsis bank structure of the DCT                                |

|-----------------------------------------------|-----------------------------------------------------------------------|

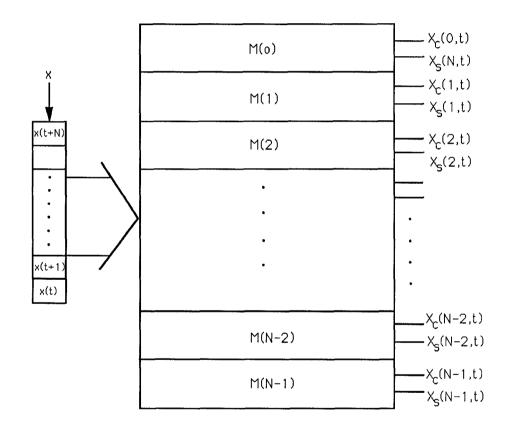

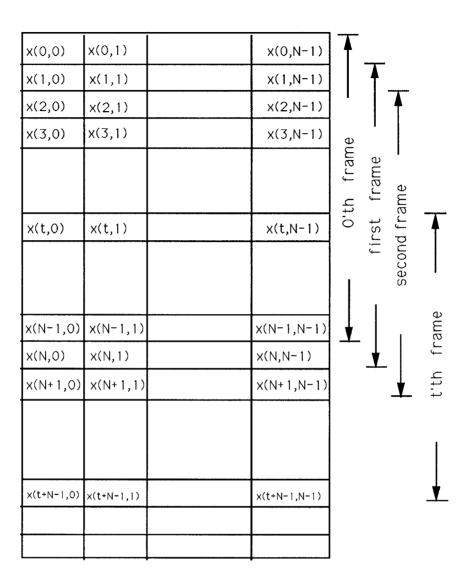

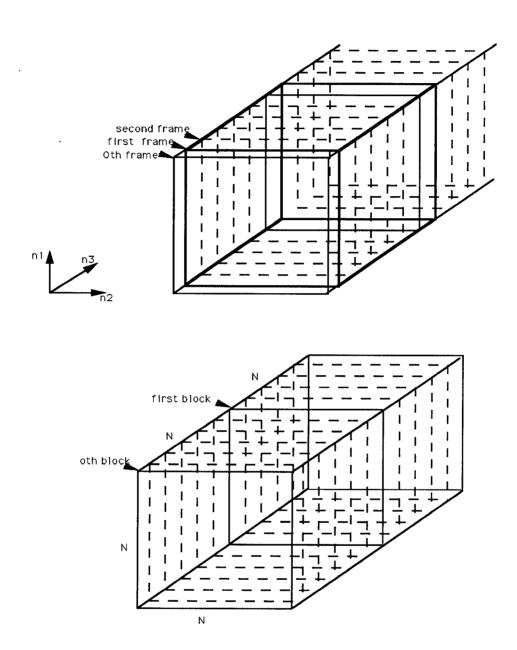

| 3.1                                           | The 2-D successive data frame                                         |

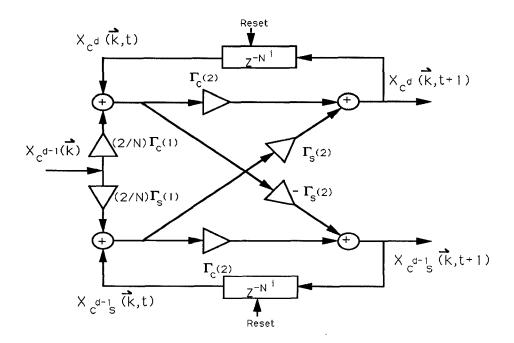

| 3.2                                           | The lattice module of lattice array II                                |

| 3.3                                           | The lattice module of lattice array I                                 |

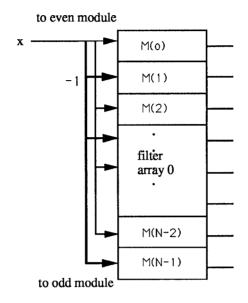

| 3.4                                           | The pre-matrix moving frame 2-D DCT architecture                      |

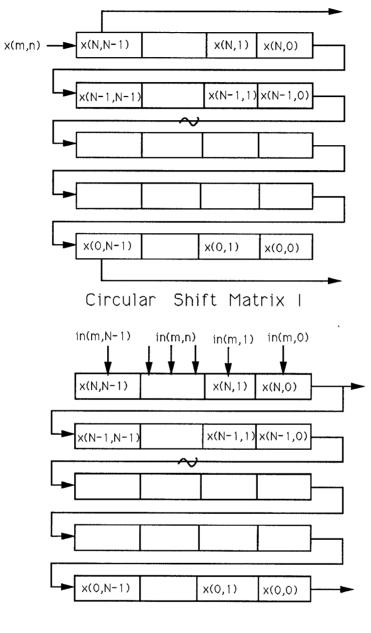

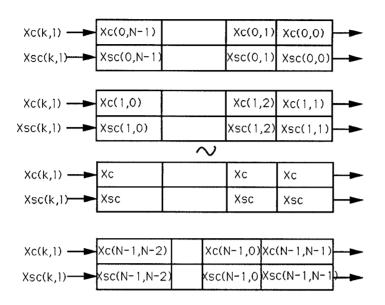

| 3.5                                           | The circular shift matrix $(CSM)$ I and II                            |

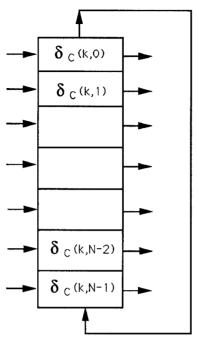

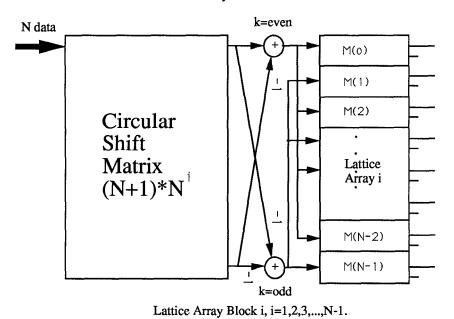

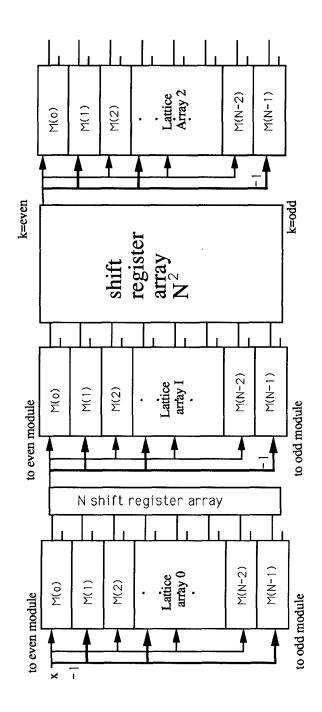

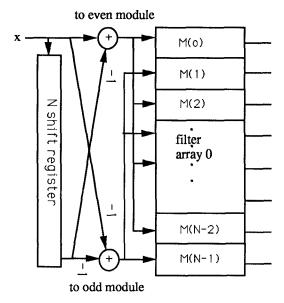

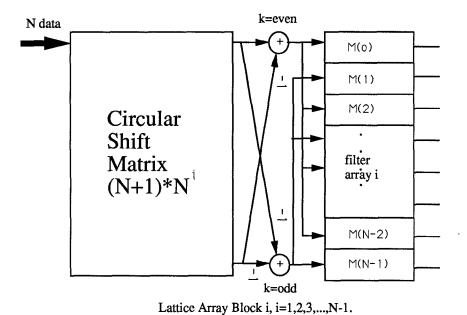

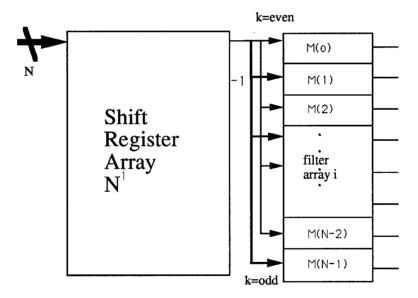

| 3.6                                           | The circular shift array (CSA)                                        |

| 3.7                                           | The Shift Register Array                                              |

| 3.8                                           | The post-matrix moving frame 2-D DCT architecture 79                  |

| 3.9                                           | The block 2-D DCT architecture                                        |

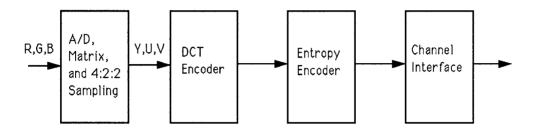

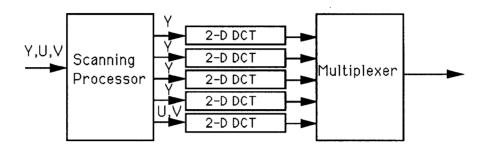

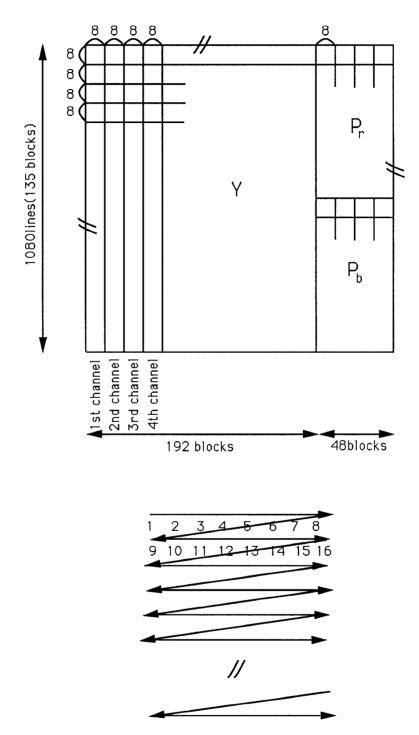

| 3.10                                          | System diagram of the DCT based HDTV coder 87                         |

| 3.11                                          | The block diagram of the DCT encoder                                  |

| 3.12                                          | Block construction of a Video frame and proposed scanning pattern. 90 |

|                                               |                                                                       |

| 4.1                                           | The universal lattice module                                          |

| 4.1<br>4.2                                    | The universal lattice module                                          |

|                                               |                                                                       |

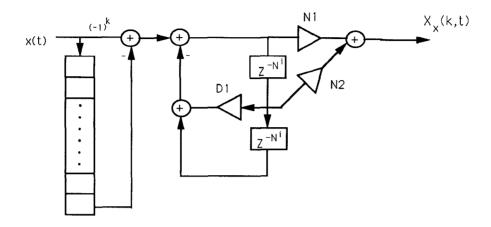

| 4.2                                           | The universal IIR filter module                                       |

| 4.2<br>4.3                                    | The universal IIR filter module                                       |

| 4.2<br>4.3<br>4.4                             | The universal IIR filter module                                       |

| 4.2<br>4.3<br>4.4<br>4.5                      | The universal IIR filter module                                       |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6               | The universal IIR filter module                                       |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7        | The universal IIR filter module                                       |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | The universal IIR filter module                                       |

| 4.12 | The lattice module                                                            |

|------|-------------------------------------------------------------------------------|

| 4.13 | The architecture for the frame-recursive 3-D DCT 126                          |

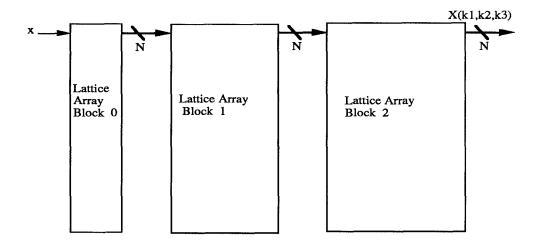

| 4.14 | The structure for Lattice Array Blocks                                        |

| 4.15 | The architecture for block 3-D DCT                                            |

| 4.16 | The configuration of the direct form filter 3-D block DCT 130                 |

| 4.17 | The block diagram of the d-D DXT                                              |

| 4.18 | The basic building structure of the moving-frame DXT 133                      |

| 4.19 | The basic structure of the block DXT                                          |

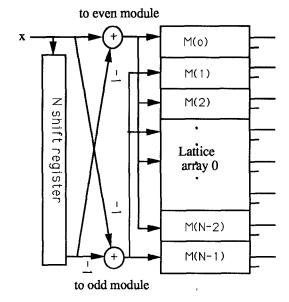

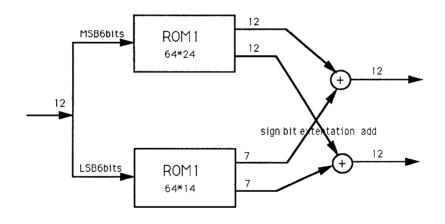

| 5.1  | The realization of the lattice module using one ROM                           |

| 5.2  | The realization of the lattice module using three ROMs 142                    |

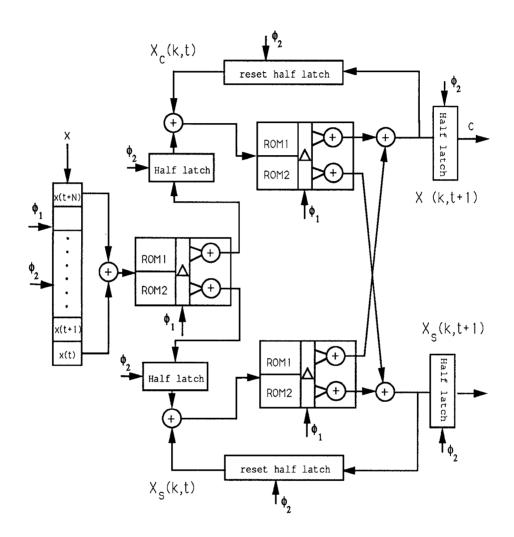

| 5.3  | The bulding blocks of the lattice module with clocks 144                      |

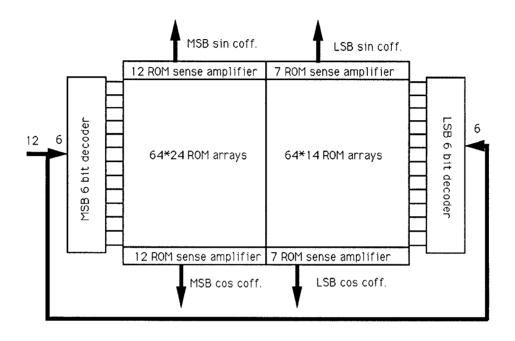

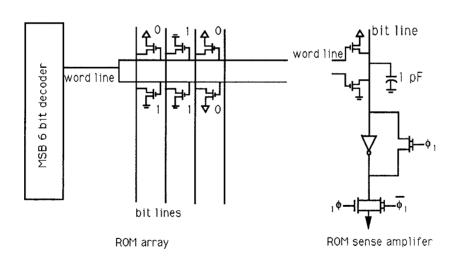

| 5.4  | The logical diagram of ROM                                                    |

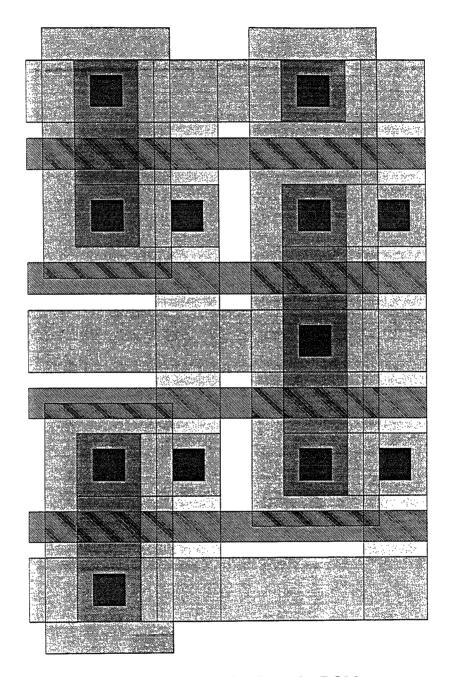

| 5.5  | The layout of cells in the ROM array                                          |

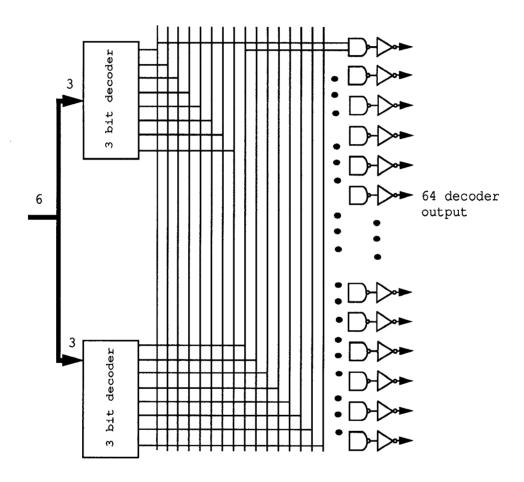

| 5.6  | The logical diagram of the 6-bit decoder                                      |

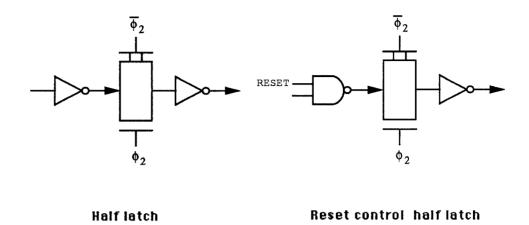

| 5.7  | The logical diagram of half-latch and reset controlled half-latch. $$ . $150$ |

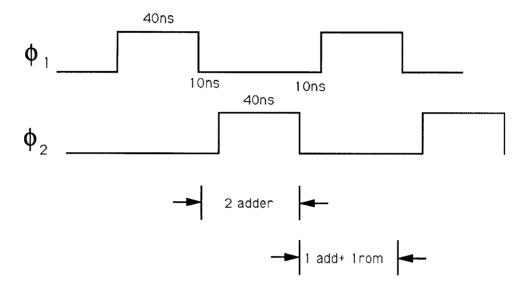

| 5.8  | The signal diagram of the clock signals                                       |

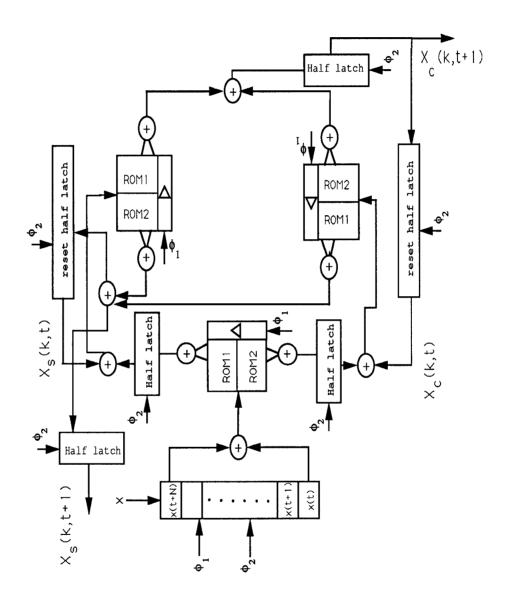

| 5.9  | The floorplan diagram of the lattice module                                   |

| 5.10 | The physical layout diagram of the lattice module                             |

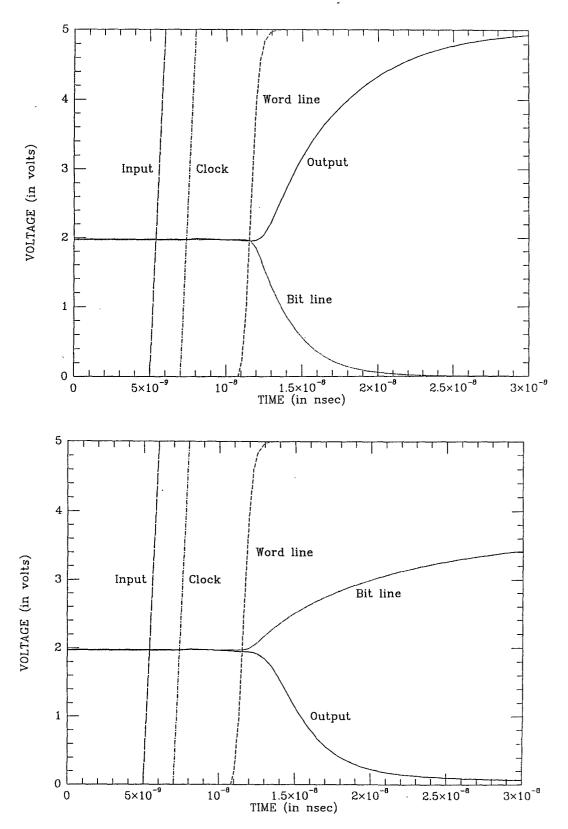

| 5.11 | The timing simulation of the ROM using SPICE                                  |

| <del></del> - |                |   |  |

|---------------|----------------|---|--|

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                | • |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               | N <sub>c</sub> |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                |   |  |

|               |                | • |  |

|               |                |   |  |

# Chapter 1

# Introduction

The field of signal processing has developed dramatically over the last several decades owing to applications in such diverse fileds as speech, image, and video communication, biomedical engineering, acoustics, sonar, radar, seismology, consumer electronics, and many others. Discrete sinusoidal transforms such as discrete cosine transform (DCT), discrete sine transform (DST), and discrete Hartley transform (DHT), discrete Fourier transform (DFT), Lopped Orthogonal Transform (LOT), and Complex Lapped Transform (CLT) are powerful tools in many applications of signal processing. Due to the advances in ISDN network and high definition television (HDTV) technology, high speed transmission and processing of speech, image and video signals become very desirable. Therefore, many computational tasks involved with digital signal transmission and processing require real-time operations. Real-time operation means the speed of the computational tasks can match the signal sampling or transmission rate. Clearly the high computational rates required in HDTV systems cannot be achieved by general-purpose parallel computers because of severe system overheads. The only way to meet the high computational rates of real-time signal processing is

by developing special-purpose architectures which exploit the regularity, recursiveness, and locality of the signal processing algorithms. In this dissertation, we focus on developing real time VLSI algorithms and architectures for discrete sinusoidal transforms for video applications.

The organization of the rest of this Chapter is as follows. The applications and techniques involved in video communication are described in Section 1.1. We describe the significances and applications of various transform coding schemes in Section 1.2 and review the evolution of the algorithms and architectures of these transforms in Section 1.3. The motivation for using time-recursive approach for achieving real time computation of these discrete transforms is given in Section 1.4. In Section 1.5, we give an overview of the results that we use from the time-recursive concept to handle the following signal processing tasks: unified one-dimensional lattice structures for discrete sinusoidal transform, two-dimensional DCT lattice structures with application to HDTV systems, optimal unified architectures for discrete sinusoidal transform, and VLSI implementation of the dual generated DCT and DST lattice structure. We conclude with the dissertation organization in Section 1.6.

# 1.1 Standards on the video coding systems

With the advances in technologies such as video compression, telecommunication, consumer electronics, the era of digital video has arrived. This new technology accelerates the availability of video applications such as digital laser-disc, electronic camera, videophone, videoconferencing, image and interactive video tools on computers, HDTV, and multimedia systems.

Unlike the digital audio technology of the past few decades, the data involved with still or motion pictures are so huge that data compression is inevitable. Compression methods are based on the nonlinearity of human vision which is more sensitive to energy with lower spatial frequency. Hence pictures can be lossly encoded with much less data than the original image without significantly decreasing the quality of the reconstructed image. For still images, data compression exploits correlation in space and for video signals, in both space and time. It is hard to distinguish a reconstructed image that was encoded with a 20:1 compression ratio from the original. Video data, even after compression at ratios at 100:1, can be decompressed with close to analog videotape quality. Among many transforms, the DCT is most widely used in speech and image processing for data compression. This is due to its better energy compaction property and its near optimal performance which is closest to that of the Karhunen-Loeve Transform (KLT) among many discrete transforms for highly correlated signals, especially for the first order Markov process [22, 1, 4].

When we develop high data compression schemes to reduce transmission/storage capacity, we also require sophisticated picture coding technology to integrate the whole system performance. In order to make the signals in different systems be compatible, standards for picture coding are strongly required. Three digital video standards that have been proposed are the Joint Photographics Experts Group (JPEG) standard for still picture compression; the Consultative Committee on International Telephony and Telegraphy (CCITT) Recommendation H.261 for video teleconferencing; and the Moving Pictures Experts Group (MPEG) for full-motion compression on digital storage media [31, 94, 93, 91].

The JPEG baseline algorithm is based on the transform coding approach.

The source image is divided into non-overlapping blocks of 8 × 8 pixels which is then transformed using the 8 × 8 two-dimensional DCT. The resulting 2-D DCT coefficients represent the frequency content of the given block where most of the energy concentrate near the zero-frequency or direct current term. Next, the DCT coefficients are quantized. Following quantization, the coefficients are zigzag scanned to arrange in the order of ascending frequency. Then, the dc and low frequency coefficients are encoded by using Huffman-style coding schemes. There is another DCT-based JPEG algorithm called the extended system which provides higher compression performance through arithmetic coding. The third mode of JPEG coding is the independent function which untilizes a 2-D Differential Pulse Code Modulation technique. The DCT-based algorithms can achieve higher compression ratio but are lossy. The spatial prediction algorithm has lower compression performance compared with the DCT-based algorithm [31].

The CCITT Recommendation H. 261 specifies a method of communication for videoconferencing and videophone [31] It is also known as the p\*64 standard because the data rate on the communication channel is p times 64-kb/s, where p is a positive integer in the range 1 to 30. For p=1, then low-quality video signal for use in picture phones can be transmitted over a 64-kb/s line. If p=30, a high quality video signal for teleconferencing can be transmitted over a 2-Mb/s line. The CCITT H.261 encoder is a hybrid coder which combines motion compensated interframe prediction with the DCT.

The MPEG standard is designed for motion picture coding for digital storage media whose data throughput rate is 1.5Mb/s. A hybrid coding scheme known as, the motion compensated interframe prediction and DCT, is also used in MPEG. The prediction scheme not only predicts from the past but also from

the future. There are three function associated with prediction: forward motion compensation, backward motion compensation, and interpolative motion compensation.

From the discussion of these standards mentioned above, we observe that the DCT is a very important technique in video signal processing. Due to the high data rate in the video communication systems, special-purpose chip sets are required to perform real-time computation and match the computation speed. For example, the HDTV system proposed by General Instrument Corporation require a video data rate at 14.38Mb/s[30]. In this dissertation, we propose a promising DCT architecture which can achieve the high speed requirement of the HDTV systems.

# 1.2 Significances and applications of various discrete sinusoidal transforms

The DCT is the most popular transform coding used in data compression. Other discrete sinusoidal transforms, like the DST, DHT, DFT, LOT, and CLT are also very effective in many signal processing applications.

Jain in [5] show that the performance of the DST approaches that of the KLT for a first-order Markov sequence with given boundary conditions, especially for signal with low correlation coefficients [5, 6]. Rose, Heiman, and Dinstein proposed a new image coding method for low bit rates which is based on alternate use of the DCT and DST on image blocks. This procedure achieves the removal of redundancies in the correlation between neighboring blocks, as well as the preservation of continuity across the block boundaries.

In 1983, Bracewell introduced the DHT [2] which uses a transform kernel similar to that of the discrete Fourier transform (DFT), except that it is a real-valued transform. Therefore, it is simpler than the DFT with respect to the computational complexity [7]. Like the DCT and DST, the DHT has found many applications in signal and image processing [2, 3, 53, 57].

The lapped orthogonal transforms introduced by Cassereau, Staelin, and Jager with the basis functions upon which the signal is projected are overlapped for adjacent blocks. The LOT can reduce the artifacts near block boundaries which are generated by traditional block transform for low bit rate coding [76]. The CLT introduced by Young and have good performance in the application of the motion estimation [62].

# 1.3 Evolution of the algorithms and architectures

Since the introduction of DCT, many algorithms have been proposed to improve the computation speed and to reduce the hardware complexity. These algorithms can be classified into the following categories: (1) indirect computation, (2) matrix factorization, (3) recursive computation, and (4) systolic structure implementation. The indirect computation [8, 9, 10, 11, 12] applies the existing fast algorithms in the DFT or the Walsh-Hadamard transform to the DCT. It is not particularly efficient because the inherent properties of the DCT are not exploited. The matrix factorization [13, 15, 85, 55] decomposes the DCT into multiplications of many sparse matrices, therefore the numbers of multiplications and additions can be substantially reduced. The recursive computations

[45, 7] calculate higher-order DCT coefficients from lower-order ones, but their signal flow architectures need global communication which is not suitable for VLSI implementation. By using the recursive properties effectively, this kind of DCT algorithms has fewer multipliers and adders, while additional multiplexers are required. As for the systolic structure implementation [46, 69, 56], it uses existing systolic architectures for the DFT or other transforms to implement the DCT in a systolic manner. But some of the methods require that the number of samples of the signal must be decomposed into mutually prime numbers. Like the DCT, many fast algorithms have been proposed to improve the performance of the DST, DFT, and DHT [3, 48, 49, 5, 6]. Basically, they can be classified into the same ways as those of the DCT and similar advantages and disadvantages can also been found.

### 1.4 Motivation

In this section we first briefly describe the requirements of special-purpose architectures for real-time signal processing [77, 78].

- 1. Simplicity, modularity, and regularity of design: This is an important factor in VLSI design because this will greatly reduce the design time and cost.

- 2. Parallel and pipelined processing: The degrees of parallelism and pipelined structures determine the concurrency and throughput of the system.

- 3. Communication: Local and regular communication for data flow determine the cost and efficiency of VLSI implementation.

Fast and efficient algorithms to implement transform coding schemes have been of interest for the past decade. Most of the algorithms proposed are focused on reducing the computational time and hardware complexity by assuming that all the input signals are available at the same time. However, in the high speed image system such as HDTV, digitized images are available in a sequential or stream fashion. Waiting for data to become ready will slow down these algorithms. Moreover, the architectures of these algorithms require global communication, that is, they need more wire connections, which increase the complexity of the circuitry and reduce the system performance.

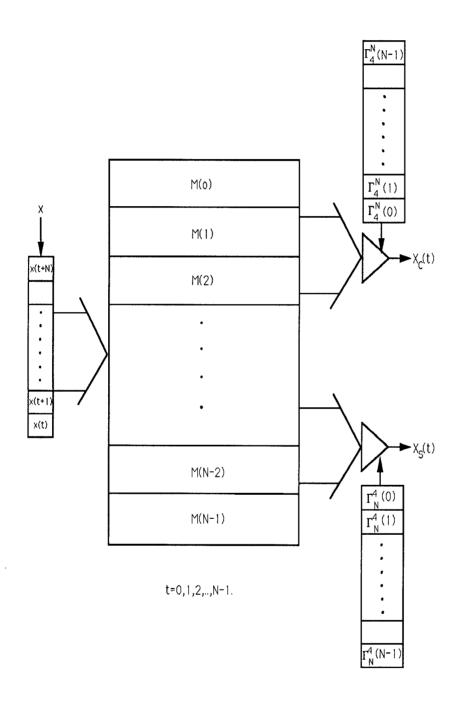

In real-time signal processing applications, especially in speech/image communications and radar/sonar signal processing, input data arrive serially. In traditional fast algorithms (such as the FFT), the serial data is buffered and then transformed using the FFT scheme of complexity  $O(N \log N)$  [60]. Buffering the serial data requires O(N) time. The goal of this dissertation is to study a novel architecture that merges the buffering and transform operations into a single unit of total hardware complexity O(N). Unlike the FFT, this architecture has only local interconnections and is better suited for VLSI implementations. It is important to note that the proposed architectures generate time-recursive transforms, not just block transforms, i.e., the transform of the N points  $[x(t+1), x(t+2), \dots, x(t+N)]$  is generated one clock cycle after the transform of  $[x(t), x(t+1), \dots, x(t+N-1)]$  is generated. To generate timerecursive transforms, the traditional fast algorithms based architectures require O(log N) time using O(N log N) hardware, while the architectures we propose require only a constant time with O(N) hardware. Time-recursive transforms are currently gaining widespread use in motion estimation, video signal processing, and in reducing blocking effects in data compression.

### 1.5 Main contribution

We propose a "time-recursive" approach to perform transform coding on a real time basis. The transformed data are updated according to a recursive formula, whenever new data arrive. Therefore the waiting time required for other algorithms is completely eliminated. Based on this new idea, several significant results are developed and are summarized as follows.

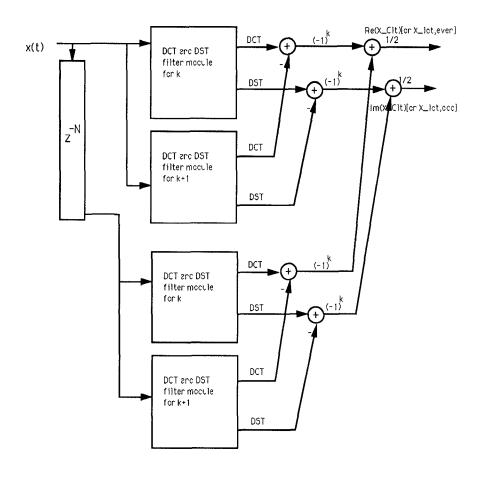

This is the first unified algorithm proposed that can be used to compute all the discrete sinusoidal transforms. We also discover the fundmental dual generation properties between these transforms.

A new unified parallel lattice architecture for the DCT/DST/DHT/DFT/LOT/CLT that are useful in image processing is derived. Here "unified" architecture means that different transforms can be computed using the same structure. We reduce the number of multipliers from  $\frac{N}{2} * \ln N$  to 6N-8 for 1-D DCT. Moreover, the resulting architectures are regular, modular, locally-connected and suitable for VLSI implementation. From the speed point of view, this unified architecture can obtain the the transform results immediately whenever a new datum arrives. Therefore, the system throughput rate is highly increased and is better than others for matching the high speed requirement of video communication systems. The other unique contribution of this architecture is that there is no constraint on the size of the image.

Data processed in image and video signal processing are two-dimensional (2-D) information. The drawback of the conventional 2-D transforms is the delay

time due to a operation called "transposition". We derive a new time-recursive parallel 2-D DCT structure which can eliminate the transposition time. The system is fully-pipelined with throughput rate N clock cycles for  $N \times N$  successive input data frame. The conventional 2-D DCT systolic array's throughput rate is 2N+1 clock cycles. The basic building block of this architecture is the unified architecture just described, therefore it presevers all the advantages mentioned above.

Although the number of multipliers of our lattice structure is a linear function of N, while that of the others is  $O(N \ln(N))$ . The number of multiplier of the lattice structure is larger than others when N is small. We further derive a direct IIR structure that can reduce the number of multipliers of 1-D DCT from 6N-8 to 2N-2. In the time-recursive lattice architecture, two transforms called the dual generated pairs, are obtained simultaneously. The unified direct IIR structure is more suitable for applications where only one transform is required. We also provide a theoretical justification for the fact that any discrete transform whose basis functions satisfy the Fundamental Recurrence Formula has a second-order autoregressive structure in its filter realization. We also demonstrate that dual generation transform pairs share the same autoregressive structure. We extend these time-recursive concepts to multi-dimensional transforms. The resulting d-dimensional structures are fully-pipelined and consist of only d 1-D transform arrays and shift registers.

In addition to theoretical derivations, the implementation of these algorithms into workable VLSI chips is also an important part of this thesis. The VLSI implementation of the lattice module based on the distributed arithmetic is also described. This is the first chip that can dually generate the DCT and

DST simultaneously. It has been fabricated using  $2\mu m$  double-metal CMOS technology and has been tested to be fully functional with a throughput rate 14.5-MHz and a data processing rate of 116Mb/s.

## 1.6 Organization

In this thesis we present unified parallel algorithms and architectures for real time computation of the time-recursive discrete sinusoidal transforms.

In Chapter 2 we develop unified parallel lattice structures that can dually generate the DCT and DST simultaneously as well as the DHT are developed. This structure can compute the DCT and DST simultaneously and immediately whenever the input data arrives. The architecture is regular, modular, and without global communication. Besides, there is no limitation on N and the total number of multipliers is a linear function of N. This makes it very suitable for VLSI implementation and real time video signal processing.

In Chapter 3 we develop a new real-time parallel 2-D DCT lattice structure which is fully-pipelined with throughput rate N clock cycles for  $N \times N$  successive input data frame. The 2-D DCT architecture is module, regular, and requires only two 1-D DCT blocks which can be extended directly from the 1-D DCT and and no transposition is required.

In Chapter 4 an optimal unified architecture that can efficiently compute the DCT, DST, Hartley, Fourier, Lapped Orthogonal, and Complex Lapped transforms for a continuous input data stream is proposed. This structure uses only half as many multipliers as the lattice structure.

In Chapter 5 the VLSI implementation of the lattice module is described. The

chip has been fabricated using MOSIS facilities under  $2\mu m$  CMOS technology and the chip can be operated at 14.5MHz.

In Chapter 6 we summarize the results obtained in this dissertation and suggest some directions for future research in this area.

# Chapter 2

# **Parallel Lattice Structures**

The problems of unified efficient computations of the DCT, DST, DHT, and their inverse transforms are considered. In particular, a new scheme employing the time-recursive approach to compute these transforms is presented. Using such an approach, unified parallel lattice structures that can dually generate the DCT and DST simultaneously as well as the DHT are developed. It is also shown that the DCT, DST, DHT and their inverse transforms share an almost identical lattice structure. The lattice structures can also be formulated into prelattice and post-lattice realizations. Two methods, the SISO and double-lattice approaches, are developed to reduce the number of multipliers in the parallel lattice structure by 2N and N respectively. The trade-off between time and area for the block data processing is also considered. The concept of filter bank interpretation of the time-recursive sinusoidal transforms is also discussed.

### 2.1 Introduction

Transform coding has found lots of applications in image, speech, and digital signal transmission and processing. Due to the advances in ISDN network and HDTV technology, high speed transmission of digital video signal becomes very desirable. Among many transforms, the discrete cosine transform (DCT), discrete sine transform (DST), and discrete Hartley transform (DHT) are very effective in transform coding applications to digital signals such as speech and image signals.

In this Chapter, we propose unified time-recursive lattice structures that can be used for the discrete orthogonal transforms mentioned above, i.e., the DCT, DST, and DHT. We consider the orthogonal transforms from a timerecursive point of view instead of the whole block of data. We do so because in digital signal transmission, data arrive serially. Also, many operations such as filtering and coding are done in a time-recursive way. Based on this approach, the resulting architectures are almost identical for the DCT, DST, and DHT, and their inverses. Our structures decouple the transformed data components, hence, there is no global communication needed. Besides, the number of multipliers in these structures is a linear function of N, so they require fewer multipliers than most other algorithms when N is large. Therefore, our architectures are very suitable for VLSI implementation. One of the important characteristics of these structures is that the transform size N can be any integer, which is not the case for most of the fast algorithms for discrete transforms which do have certain constraints on N. Another important result is that based on the time-recursive approach, the dual generation properties of the DCT, DST, and DHT, as well as some related inverse transforms, can be obtained.

The rest of the Chapter is organized as follows. In Section 2.2, the dual generation of lattice structures for the DCT and DST with the time-recursive approach is considered. The inverse discrete cosine transform (IDCT) and inverse discrete sine transform (IDST) based on the lattice structures are discussed in Section 2.3. In Section 2.4, the time-recursive lattice structure for the DHT is presented. All the above time-recursive properties are derived by updating the time index by one. With block data processing, the time index is updated by more than one. The detailed effects and results of block data processing are discussed in Section 2.5. Denormalized methods to reduce the number of multipliers in those lattice structures are considered in Section 2.6. Then we compare these kinds of lattice structures with other architectures in terms of the number of multipliers and adders in Section 2.7. The synthesis bank structures based on the time-recursive concept is discussed in Section 2.8. Finally, we give the conclusion in Section 2.9.

# 2.2 Dual Generation of DCT and DST

We will show an efficient implementation of the DCT from the time-recursive point of view as an alternative to find fast algorithms through matrix factorizations or convert the DCT to DFT, which can be implemented on various existing architectures. Focusing on the sequence instead of the block of input data, we can obtain not only the time-recursive relation between the DCT of two successive data sequences, but also a fundamental relation between DCT and DST. In the following, the time-recursive relation for the DCT will be considered first.

# 2.2.1 Time-Recursive Discrete Cosine Transform

The one-dimensional (1-D) DCT of a sequential input data starting from x(t) and ending with x(t+N-1) is defined as

$$X_{c}(k,t) = \frac{2C(k)}{N} \sum_{n=t}^{t+N-1} x(n) \cos \left[ \frac{\pi[2(n-t)+1]k}{2N} \right]$$

$$k = 0, 1, ..., N-1, \qquad (2.1)$$

where

$$C(k) = \begin{cases} \frac{1}{\sqrt{2}} & \text{if } k = 0 \text{ or } k = N, \\ 1 & \text{otherwise.} \end{cases}$$

Here the time index t in  $X_c(k,t)$  denotes that the transform starts from x(t). Since the function C(k) has a different value only when k=0, we can consider those cases that C(k)'s equal one (i.e. k=1,2,...,N-1.) first and re-examine the case for k=0 later on. In transmission systems data arrive seriesly, therefore we are interested in the the 1-D DCT of the next input data vector [x(t+1), x(t+2),...,x(t+N)]. From the definition, it is given by

$$X_c(k,t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \cos \left[ \frac{\pi [2(n-t-1)+1]k}{2N} \right].$$

(2.2)

This can be rewritten as

$$X_{c}(k,t+1) = \overline{X}_{c}(k,t+1)\cos\left(\frac{\pi k}{N}\right) + \overline{X}_{s}(k,t+1)\sin\left(\frac{\pi k}{N}\right), \qquad (2.3)$$

where

$$\overline{X}_c(k,t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \cos \left[ \frac{\pi [2(n-t)+1]k}{2N} \right], \tag{2.4}$$

and

$$\overline{X}_{s}(k,t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \sin \left[ \frac{\pi[2(n-t)+1]k}{2N} \right]. \tag{2.5}$$

As we can see, a DST-like term  $\overline{X}_s(k,t+1)$  appears in (2.5). This motivates us to investigate the time-recursive DST.

#### 2.2.2 Time-Recursive Discrete Sine Transform

There are several definitions for the DST. Here we prefer the definition proposed by Wang in [49]. The 1-D DST of a data vector [x(t), x(t+1), ..., x(t+N-1)] is defined as

$$X_s(k,t) = \frac{2C(k)}{N} \sum_{n=t}^{t+N-1} x(n) \sin\left[\frac{\pi[2(n-t)+1]k}{2N}\right],$$

$$k = 1, ..., N. \quad (2.6)$$

Note that the range of k is from 1 to N. Again, we consider those cases that D(k)'s equal one first, *i.e.*

$$X_s(k,t) = \frac{2}{N} \sum_{n=t}^{t+N-1} x(n) \sin\left[\frac{\pi[2(n-t)+1]k}{2N}\right]. \tag{2.7}$$

The DST of the time update sequence [x(t+1), x(t+2), ..., x(t+N)] is given by

$$X_s(k,t+1) = \frac{2}{N} \sum_{n=t+1}^{t+N} x(n) \sin\left[\frac{\pi[2(n-t-1)+1]k}{2N}\right]$$

$$= \overline{X}_s(k,t+1) \cos\left(\frac{\pi k}{N}\right) - \overline{X}_c(k,t+1) \sin\left(\frac{\pi k}{N}\right). \tag{2.8}$$

Here the terms  $\overline{X}_s(k,t+1)$  and  $\overline{X}_c(k,t+1)$  that are used in (2.3) to generate  $X_c(k,t+1)$  appear in the equation of the new DST transform  $X_s(k,t+1)$  again. This suggests that the DCT and DST can be dually generated from each other.

### 2.2.3 The Lattice Structures

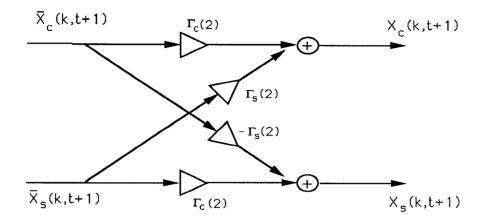

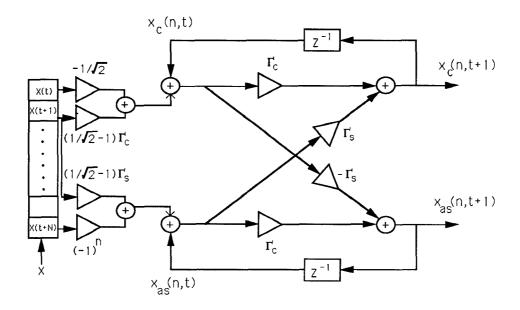

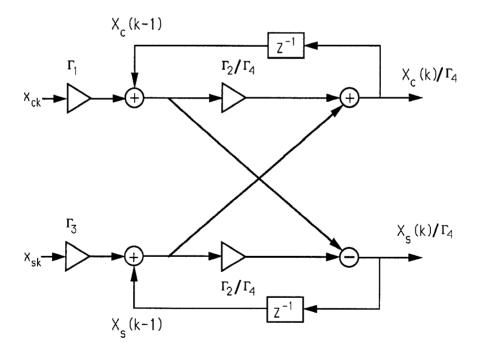

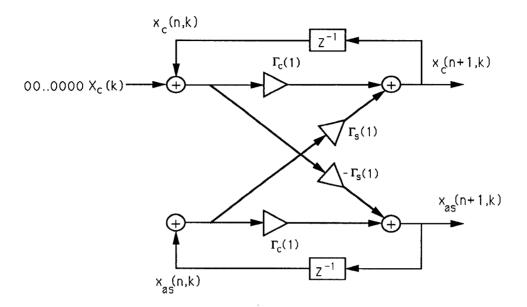

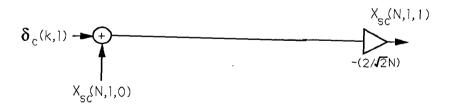

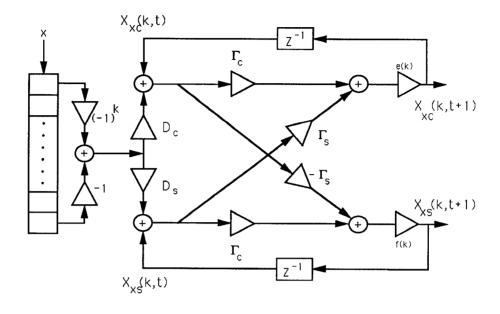

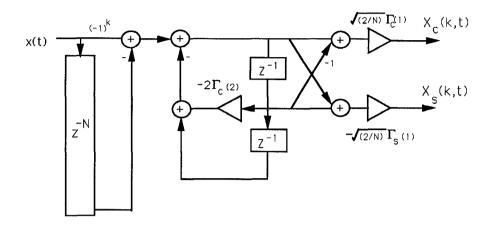

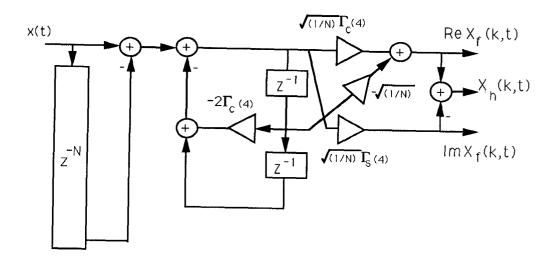

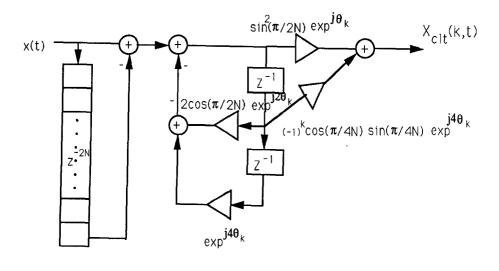

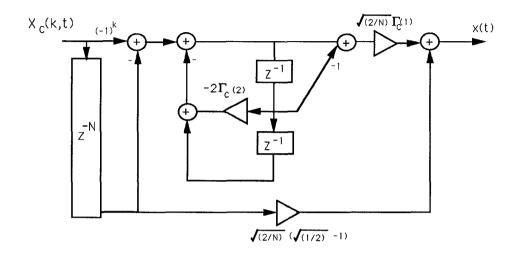

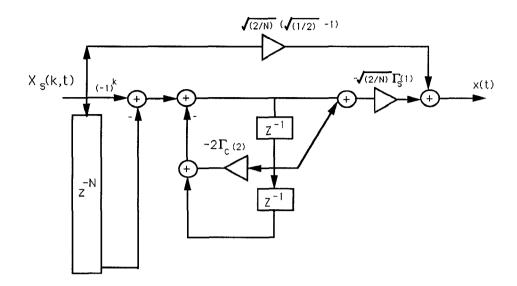

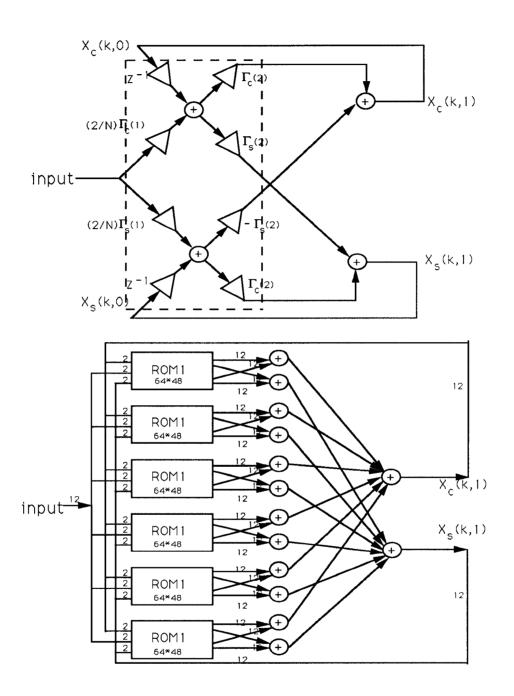

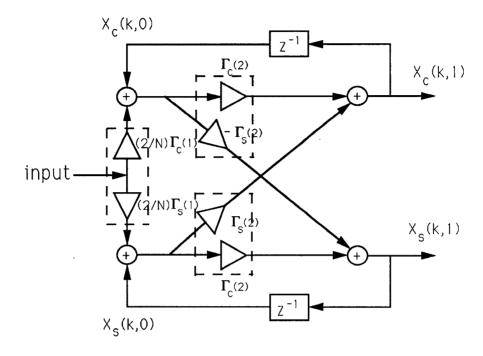

From (2.3) and (2.8), it is noted that the new DCT and DST transforms  $X_c(k, t+1)$  and  $X_s(k, t+1)$ , can be obtained from  $\overline{X}_c(k, t+1)$  and  $\overline{X}_s(k, t+1)$  in the lattice form as shown in Fig. 2.1. The next step is to update  $\overline{X}_c(k, t+1)$  and  $\overline{X}_s(k, t+1)$  from the previous transforms  $X_c(k, t)$  and  $X_s(k, t)$ . We notice that  $X_c(k, t)$  and  $\overline{X}_c(k, t+1)$  have similar terms except the old datum x(t) and the

$\Gamma_{\rm C}(n) = \cos(\pi k n/2N)$ ,

$\Gamma_{\rm S}({\rm n}) = \sin(\pi k {\rm n}/2{\rm N})$

Figure 2.1: The lattice module.

incoming new datum x(t+N). Therefore  $\overline{X}_c(k,t+1)$  and  $\overline{X}_s(k,t+1)$  can be obtained by deleting the term associated with the old datum x(t) and updating the new datum x(t+N) as

$$\overline{X}_{c}(k,t+1) = X_{c}(k,t) - x(t) \left(\frac{2}{N}\right) \cos\left(\frac{\pi k}{2N}\right)$$

$$+x(t+N) \left(\frac{2}{N}\right) \cos\left[\frac{\pi(2N+1)k}{2N}\right]$$

$$= X_{c}(k,t) + \left[-x(t) + (-1)^{k}x(t+N)\right] \left(\frac{2}{N}\right) \cos\left(\frac{\pi k}{2N}\right), \qquad (2.9)$$

and

$$\overline{X}_{s}(k,t+1) = X_{s}(k,t) - x(t) \left(\frac{2}{N}\right) \sin\left(\frac{\pi k}{2N}\right)

+ x(t+N) \left(\frac{2}{N}\right) \sin\left[\frac{\pi(2N+1)k}{2N}\right]

= X_{s}(k,t) + \left[-x(t) + (-1)^{k}x(t+N)\right] \left(\frac{2}{N}\right) \sin\left(\frac{\pi k}{2N}\right).$$

(2.10)

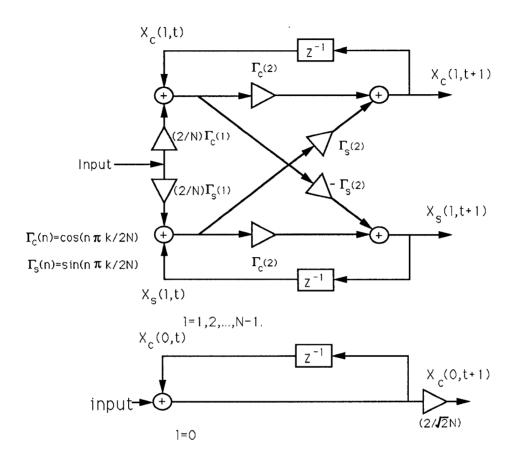

From (2.3), (2.8), (2.9), and (2.10), the new transforms  $X_c(k, t+1)$  and  $X_s(k, t+1)$  and  $X_s(k, t+1)$  can be calculated from the previous transforms  $X_c(k, t)$  and  $X_s(k, t)$  by adding the effect of input signal samples x(t) and x(t+N). This demonstrates that the DCT and DST can be dually generated from each other in a recursive way. The time-recursive relations for the new transforms  $X_c(k, t+1)$  and  $X_s(k, t+1)$  as well as the previous transforms  $X_c(k, t)$  and  $X_s(k, t)$  are given by

$$X_c(k,t+1) = \left\{ X_c(k,t) + \left[ -x(t) + (-1)^k x(t+N) \right] \left( \frac{2}{N} \right) \cos \left( \frac{\pi k}{2N} \right) \right\} \cos \left( \frac{\pi k}{N} \right)$$

$$+ \left\{ X_s(k,t) + \left[ -x(t) + (-1)^k x(t+N) \right] \left( \frac{2}{N} \right) \sin \left( \frac{\pi k}{2N} \right) \right\} \sin \left( \frac{\pi k}{N} \right) (2.11)$$

and

$$X_s(k,t+1) = \left\{ X_s(k,t) + \left[ -x(t) + (-1)^k x(t+N) \right] \left( \frac{2}{N} \right) \sin\left(\frac{\pi k}{2N} \right) \right\} \cos\left(\frac{\pi k}{N}\right)$$

$$-\left\{ X_c(k,t) + \left[ -x(t) + (-1)^k x(t+N) \right] \left( \frac{2}{N} \right) \cos\left(\frac{\pi k}{2N} \right) \right\} \sin\left(\frac{\pi k}{N}\right) (2.12)$$

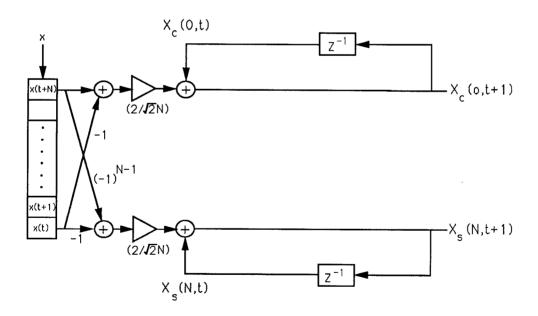

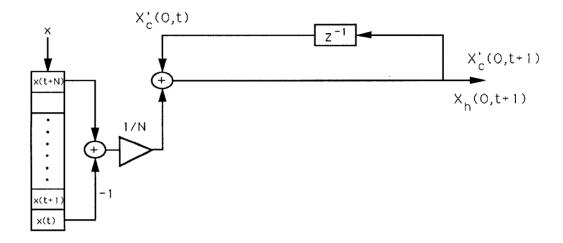

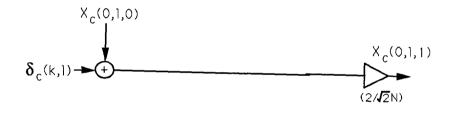

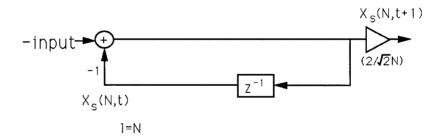

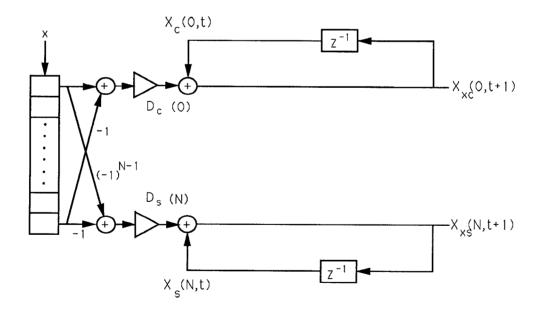

Now, let us consider the cases for k=0 in the DCT and k=N in the DST respectively. According to (2.1), the 1-D DCT of the time-update input vector [x(t+1), x(t+2), ...x(t+N)] for k=0 is

$$X_c(0,t+1) = \frac{2}{N\sqrt{2}} \sum_{n=t+1}^{t+N} x(n).$$

(2.13)

The relation of  $X_c(0, t+1)$  with the old transformed datum  $X_c(0, t)$  is

$$X_c(0,t+1) = X_c(0,t) + \frac{2}{N\sqrt{2}} \left[ -x(t) + x(t+N) \right]. \tag{2.14}$$

And, the time-recursive relation between the new transforms  $X_s(N, t + 1)$  and the previous transforms  $X_s(N, t)$  is

$$X_s(N,t+1) = \frac{2}{N\sqrt{2}} \sum_{n=t+1}^{t+N} x(n)(-1)^{n-t-1}$$

$$= X_s(N,t) + \frac{2}{N\sqrt{2}} \left[ -x(t) + (-1)^{N-1} x(t+N) \right]. (2.15)$$

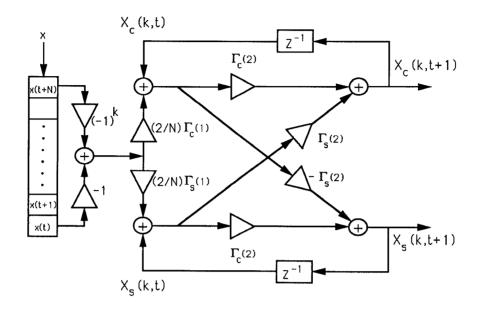

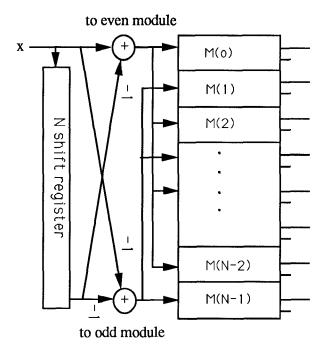

The complete time-recursive lattice modules for (k = 0, 1, 2, ..., N-1.) are shown in Fig. 2.2. It consists of a N+1 shift register and a normalized digital filter performing the plane rotation. The multiplications in the plane rotation can be reduced to addition and substration for k = 0 in the DCT and k = N in the DST respectively. The following illustrates how this dually generated DCT and DST lattice structure works to obtain the DCT and DST with length N of a series of input data [x(t), x(t+1), ..., x(t+N-1), x(t+N), ...] for a specific k. The initial values of the transformed signals  $X_c(k, t-1)$  and  $X_s(k, t-1)$  are set to zero; so are the initial values in the shift register in the front of the lattice module. The input sequence [x(t), x(t+1), ...] shifts sequentially into the shift register as shown in Fig. 2.2. Then the output signals  $X_c(k,t)$  and  $X_s(k,t)$ , k = 0, 1, ..., N - 1, N, are updated recursively according to (2.11), (2.12), (2.14)and (2.15). After the input datum x(t+N-1) shifts into the shift register, the DCT and DST of the input data vector [x(t), x(t+1), ..., x(t+N-1)] are obtained at the output for this index k. It takes N clock cycles to get the  $X_c(k,t)$ and  $X_s(k,t)$  of the input vector [x(t), x(t+1), ..., x(t+N-1)]. Since there are N different values for k, the total computational time to obtain all the transformed data is  $N^2$  clock cycles, if only one lattice module is used. In this case, the delay time and throughput are the same  $N^2$  clock cycles.

A parallel lattice array consists of N lattice modules can be used for parallel computations and it improves the computational speed drastically as shown in Fig. 2.3. Here we have seen that the transform domain data X(k,t) have been decomposed into N disjoint components that have the same lattice modules with different multiplier coefficients in them. In this case the total computational delay time decreases to N clock cycle. It is important to notice that when the

Figure 2.2: The lattice structure for the DCT and DST with coefficients C(k)'s and D(k)'s, k=0,1,2,...,N-1,N.

Figure 2.3: The parallel lattice structure for the DCT and DST.

next input datum x(t+N) arrives, the transformed data of the input data vector [x(t+1), x(t+2), ..., x(t+N)] can be obtained immediately. Likewise, it takes only one clock cycle to generate the transformed data of subsequent inputs. That is, the latency and throughput of this parallel system are N and 1 respectively.

It is obvious that this lattice structure is quite different from the signal flow graph realization obtained from the fast DCT algorithms [13, 15]. Since there is no global communication and the structure is modular and regular, it is suitable for practical VLSI implementation. The most interesting result is that this architecture can be applied to any value of N. From this point of view, it is more attractive than existing algorithms. In fact, most algorithms [73, 69] are limited to the sequence length N which either must be power of 2 or must be decomposable into mutually prime numbers. In addition, this lattice structure reveals some interesting properties of the DCT and DST, i.e., the DCT and DST can be generated simultaneously. The DCT is near optimal to the KLT transform in highly correlated signals, while the DST approaches the KLT in signals with low correlation coefficient. As we are able to obtain the DCT and DST at the same time, this lattice structure is very useful especially when we do not know the statistics of the incoming signal. Furthermore, we can use a single lattice module with only 6 multipliers and 5 adders to recursively compute any N-point DCT and DST simultaneously. To obtain the transformed data in parallel, we need N lattice modules. As mentioned before, it is suitable for VLSI implementation since all the modules have the same structure except the 0'th module which can be simplified as shown in Fig. 2.2. This parallel lattice structure requires 6N-4 multipliers and 5N-1 adders.

### 2.3 Inverse Transforms

#### 2.3.1 Time-Recursive IDCT

According to the definition of the DCT in (2.1), the IDCT for the transform domain sequence [X(t), X(t+1), ..., X(t+N-1)] is

$$x_c(n,t) = \sum_{k=t}^{t+N-1} C(k-t)X(k) \cos\left[\frac{\pi(2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, ..., N-1.$$

(2.16)

The coefficients C(k)'s are given in (2.1). From the time-recursive point of view, the IDCT of the new sequence [X(t+1), X(t+2), ..., X(t+N)] can be expressed as

$$x_c(n,t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)\cos\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right].$$

(2.17)

Similar to the previous sections, we can decompose (2.17) into

$$x_c(n,t+1) = \overline{x}_c(n,t+1)\cos\left[\frac{\pi(2n+1)}{2N}\right] + \overline{x}_{as}(n,t+1)\sin\left[\frac{\pi(2n+1)}{2N}\right],$$

(2.18)

where

$$\overline{x}_c(n,t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)\cos\left[\frac{\pi(2n+1)(k-t)}{2N}\right],$$

(2.19)

and

$$\overline{x}_{as}(n,t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)\sin\left[\frac{\pi(2n+1)(k-t)}{2N}\right]. \tag{2.20}$$

In order to be a dually generated pair of the IDCT given in (2.16), we define the auxiliary inverse discrete sine transform (AIDST) as

$$x_{as}(n,t) = \sum_{k=t}^{t+N-1} C(k-t)X(k)\sin\left[\frac{\pi(2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, ..., N-1.$$

(2.21)

Although this definition utilizes the same sine functions as the transform kernel, it is not the inverse transform of the DST. To differentiate it from the IDST, we call this the AIDST. Comparing to the IDST defined in (2.26), we observe that the AIDST has the special coefficients  $C(0) = \frac{1}{\sqrt{2}}$  associated with the first term, while the IDST with the last term. The AIDST for the data sequence [X(t+1), X(t+2), ..., X(t+N)] can be written as

$$x_{as}(n,t+1) = \sum_{k=t+1}^{t+N} C(k-t-1)X(k)\sin\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right].$$

(2.22)

By using the trigonometric function expansions,  $x_{as}(n, t+1)$  becomes

$$x_{as}(n,t+1) = \overline{x}_{as}(n,t+1)\cos\left[\frac{\pi(2n+1)}{2N}\right] - \overline{x}_{c}(n,t+1)\sin\left[\frac{\pi(2n+1)}{2N}\right]. \quad (2.23)$$

### Lattice Structure for IDCT

Combining (2.18) and (2.23), we observe that the IDCT and the AIDST can be generated in exactly the same way as the dual generation of the DCT and DST. Therefore, the lattice structure in Fig.2.1 can be applied here except that the coefficients must be modified. Since the coefficients C(k)'s are inside the expression in the inverse transform, the relation between  $x_c(n,t)$  and  $\overline{x}_c(n,t+1)$  will be different from what we have in the DCT. Equations (2.16) and (2.19) as well as (2.20) and (2.21) have the same terms for  $k \in \{t+2, t+3, ..., t+N-1\}$ . After adding the effects of the terms for k = t and k = t+1, we obtain

$$\overline{x}_c(n,t+1) = x_c(n,t) - \frac{1}{\sqrt{2}}X(t) + \left(\frac{1}{\sqrt{2}} - 1\right)\cos\left[\frac{\pi(2n+1)}{2N}\right]X(t+1), \quad (2.24)$$

and

$$\overline{x}_{as}(n,t+1) = x_{as}(n,t) + (-1)^n X(t+N) + \left(\frac{1}{\sqrt{2}} - 1\right) \sin\left[\frac{\pi(2n+1)}{2N}\right] X(t+1).$$

(2.25)

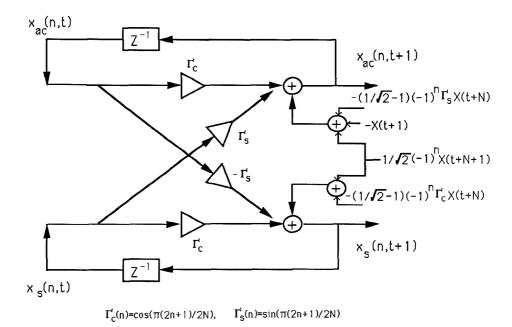

$\vec{\Gamma}_{c}(n)=\cos(\pi(2n+1)/2N), \quad \vec{\Gamma}_{s}(n)=\sin(\pi(2n+1)/2N)$

Figure 2.4: The lattice structure for the IDCT and AIDST.

The complete lattice module for the IDCT and AIDST is shown in Fig.2.4. This IDCT lattice structure has the same lattice module as that of the DCT except for the input stage where one more adder and one more multiplier are required. The procedure to calculate the inverse transformed data is the same. Therefore, this IDCT lattice structure has the same advantages as that of the DCT. To obtain the inverse transform in parallel, we need N such IDCT lattice modules where 7N multipliers and 6N adders are required. Again, we see that the numbers of adders and multipliers are linear functions of N. Here we should notice that to obtain the inverse transform of the original input data sequence, for example, [x(0), x(1), x(2), ..., x(N-1)] and [x(N), x(N+1), ..., x(2N-1)], it is sufficient only to send the transformed data corresponding to these two blocks, i.e., [X(0), X(1), ..., X(N-1)] and [X(N), X(N+1), ..., X(2N-1)] respectively, although we have all the intermediate transformed data. Then by

applying the time-recursive algorithm mentioned above, we obtain the original data after X(N-1) and X(2N-1) arrive, the intermediate data obtained by the inverse transform are redundant.

### 2.3.2 Time-Recursive IDST

From the definition of the DST in (2.6), the IDST for the transform domain sequence [X(t+1), X(t+2), ..., X(t+N)] is given by

$$x_s(n,t) = \sum_{k=t+1}^{t+N} D(k-t)X(k) \sin\left[\frac{\pi(2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, ..., N-1.$$

(2.26)

The coefficients D(k)'s are given in (2.6). Analogous to Section 3.1, we define the auxiliary inverse discrete cosine transform (AIDCT)

$$x_{ac}(n,t) = \sum_{k=t+1}^{t+N} D(k-t)X(k)\cos\left[\frac{\pi(2n+1)(k-t)}{2N}\right],$$

$$n = 0, 1, ..., N-1,$$

(2.27)

which is the dually generated counterpart of the IDST. The IDST and AIDCT of the new sequence of transformed data [X(t+2), X(t+3), ..., X(t+N+1)] are given respectively by

$$x_s(n,t+1) = \sum_{k=t+2}^{t+N+1} D(k-t-1)X(k)\sin\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right], \qquad (2.28)$$

and

$$x_{ac}(n,t+1) = \sum_{k=t+2}^{t+N+1} D(k-t-1)X(k) \cos\left[\frac{\pi(2n+1)(k-t-1)}{2N}\right].$$

(2.29)

Same as before, we can decompose (2.28) and (2.29) to

$$x_s(n, t+1) = \overline{x}_s(n, t+1) \cos\left[\frac{\pi(2n+1)}{2N}\right] - \overline{x}_c(n, t+1) \sin\left[\frac{\pi(2n+1)}{2N}\right], (2.30)$$

Figure 2.6: The post-lattice structure for the IDST and AIDCT.

signals are added at the end of the lattice. From now on, we call this lattice structure a post-lattice module and the previous ones as pre-lattice modules. This post-lattice module needs 7 multipliers and 7 adders, less than required for the corresponding pre-lattice module. A parallel post-lattice structure, which generates N transformed data simultaneously, requires 7N multipliers and 7N adders. All the forward and inverse transform pairs mentioned above have pre-lattice and post-lattice structures. Not all post-lattice structures are superior to their pre-lattice counterparts in the hardware complexity. For example, the IDCT and AIDST post-lattice form can be expressed as

$$x_{as}(n, t+1) = \cos\left[\frac{\pi(2n+1)}{2N}\right] x_{as}(n, t) - \sin\left[\frac{\pi(2n+1)}{2N}\right] x_{c}(n, t)$$

$$-\left(\frac{1}{\sqrt{2}}\right) \sin\left[\frac{\pi(2n+1)}{2N}\right] X(t)$$

$$+(-1)^{n} X(t+N) \cos\left[\frac{\pi(2n+1)}{2N}\right], \qquad (2.38)$$

and

$$x_{c}(n,t+1) = \cos\left[\frac{\pi(2n+1)}{2N}\right]x_{c}(n,t) + \sin\left[\frac{\pi(2n+1)}{2N}\right]x_{as}(n,t)$$

$$-\left(\frac{1}{\sqrt{2}}\right)\cos\left[\frac{\pi(2n+1)}{2N}\right]X(t) - X(t+1) + \left(\frac{1}{\sqrt{2}} - 1\right)X(t+1)$$

$$+(-1)^{n}\sin\left[\frac{\pi(2n+1)}{2N}\right]X(t+N). \tag{2.39}$$

This post-lattice module has 9 multipliers and 7 adders which are more than its pre-lattice realization. As to the DCT and DST, the post-lattice form can be expressed as

$$X_{c}(k,t+1) = \cos\left(\frac{\pi k}{N}\right) X_{c}(k,t) + \sin\left(\frac{\pi k}{N}\right) X_{s}(k,t) + \left(\frac{2}{N}\right) \cos\left(\frac{\pi k}{2N}\right) \left[-x(t) + (-1)^{k} x(t+N)\right], \quad (2.40)$$

and

$$X_{s}(k,t+1) = \cos\left(\frac{\pi k}{N}\right) X_{s}(k,t) - \sin\left(\frac{\pi k}{N}\right) X_{s}(k,t)$$

$$-\left(\frac{2}{N}\right) \sin\left(\frac{\pi k}{2N}\right) \left[-x(t) + (-1)^{k} x(t+N)\right]. \tag{2.41}$$

In this case, the pre-lattice and post-lattice modules have the same numbers of multipliers and adders.

# 2.4 Discrete Hartley Transform (DHT)

According to Bracewell's definition of the DHT in [2], the data sequence x(n) and the DHT transformed data X(k) have the following relation

$$X_{h}(k,t) = \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) cas\left(\frac{2\pi k(n-t)}{N}\right)$$

$$= \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \left[\cos\left(\frac{2\pi k(n-t)}{N}\right) + \sin\left(\frac{2\pi k(n-t)}{N}\right)\right],$$

$$k = 0, 1, ..., N-1.$$

(2.42)

The DHT uses real expressions  $\cos(\frac{2\pi k(n-t)}{N}) + \sin(\frac{2\pi k(n-t)}{N})$  as the transform kernel, while discrete Fourier transform (DFT) uses the complex exponential expression  $\exp(\frac{i2\pi k(n-t)}{N})$  as the transform kernel. Because the kernel of the DHT is a summation of cosine and sine terms, we can separate them into a combination of a DCT-like and a DST-like transforms as follows:

$$X_h(k,t) = \acute{X}_c(k,t) + \acute{X}_s(k,t),$$

(2.43)

where

$$\dot{X}_{c}(k,t) = \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \left[ \cos \left( \frac{2\pi k(n-t)}{N} \right) \right],$$

(2.44)

and

$$\dot{X}_{s}(k,t) = \frac{1}{N} \sum_{n=t}^{t+N-1} x(n) \left[ \sin \left( \frac{2\pi k(n-t)}{N} \right) \right].$$

(2.45)

The  $\dot{X}_c(k,t)$  is the so-called DCT-I and the  $\dot{X}_s(k,t)$  is the DST-I that are defined by Yip and Rao in [51]. Since the DHT can be decomposed into the combination of the DCT-I and DST-I, the dual generation of both for the DHT is thus possible. The DCT-I and the DST-I of the data sequence [x(t+1), x(t+2), ..., x(t+N)]are

$$\dot{X}_c(k,t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \cos \left[ \frac{2\pi k(n-t-1)}{N} \right],$$

(2.46)

and

$$\hat{X}_s(k,t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \sin \left[ \frac{2\pi k(n-t-1)}{N} \right].$$

(2.47)

The new transforms  $\dot{X}_c(k,t+1)$  and  $\dot{X}_s(k,t+1)$  can be further expressed as

$$\dot{X}_c(k,t+1) = \overline{\dot{X}}_c(k,t+1)\cos\left(\frac{2\pi k}{N}\right) + \overline{\dot{X}}_s(k,t+1)\sin\left(\frac{2\pi k}{N}\right), \qquad (2.48)$$

and

$$\dot{X}_s(k,t+1) = \overline{\dot{X}}_s(k,t+1)\cos\left(\frac{2\pi k}{N}\right) - \overline{\dot{X}}_c(k,t+1)\sin\left(\frac{2\pi k}{N}\right), \qquad (2.49)$$

Figure 2.7: The lattice structure for the DHT for k = 1, 2, ..., N - 1.

where

$$\overline{\dot{X}}_{c}(k,t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \cos\left(\frac{2\pi k(n-t)}{N}\right)

= \dot{X}_{c}(k,t) + \frac{1}{N} \left[-x(t) + x(t+N)\right],$$

(2.50)

and

$$\overline{\dot{X}}_{s}(k,t+1) = \frac{1}{N} \sum_{n=t+1}^{t+N} x(n) \sin\left(\frac{2\pi k(n-t)}{N}\right)$$

$$= \dot{X}_{s}(k,t). \tag{2.51}$$

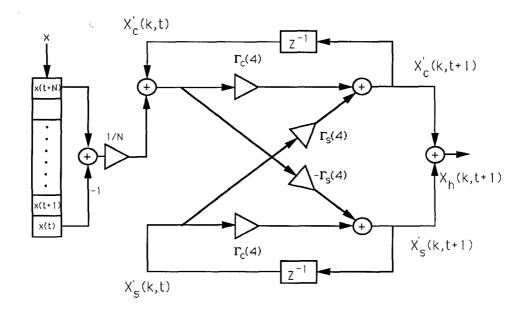

The lattice module for the DHT for k=1,...,N-1 is shown in Fig. 2.7 and Fig. 2.8. From Fig. 2.7, we can see that the numbers of multipliers and adders are less than those of the dual generation of the DCT and DST. The total numbers of multipliers and adders in the parallel DHT lattice architecture are 5N-4 and 5N-3 respectively.

Figure 2.8: The lattice structure for the DHT for k = 0.

# 2.5 Block Processing

All the time-recursive discrete transforms derived above are based on the block-size-one update which means the time index is updated by one. That is, at each iteration only the effect of one old datum is removed and the information of one new datum is added. We are interested in the relation between the area-time complexity (AT) and block size. This motivates us to discuss the effect on the lattice structure when the block size is increased.

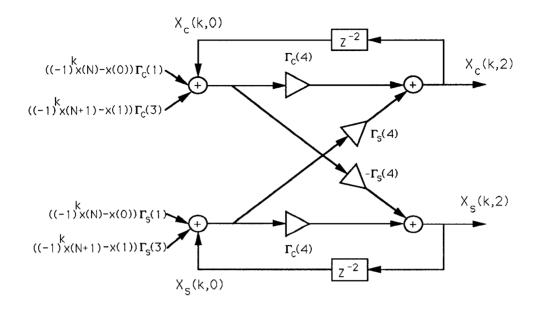

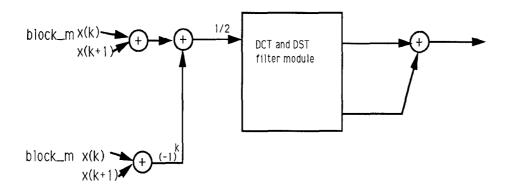

## 2.5.1 Block Processing of time-recursive DCT and DST

We begin the discussion of block processing with the block-size-two update. Here we assume the time index t in (2.1) is zero for simplicity, and we will use this in the following discussions. As before, the transformed data  $X_c(k,2)$  and  $X_s(k,2)$

are defined as the DCT and DST of the input vector [x(2), x(3), ..., x(N), x(N + 1)]. That is,

$$X_c(k,2) = \sum_{n=2}^{N+1} x(n) \cos\left\{\frac{\pi[2(n-2)+1]k}{2N}\right\},\tag{2.52}$$

and

$$X_s(k,2) = \sum_{n=2}^{N+1} x(n) \sin\left\{\frac{\pi[2(n-2)+1]k}{2N}\right\}.$$

(2.53)

To obtain  $X_c(k,2)$  from  $X_c(k,0)$  and  $X_s(k,2)$  from  $X_s(k,0)$  directly, we can rewrite  $X_c(k,2)$  and  $X_s(k,2)$  as

$$X_c(k,2) = \overline{X}_c(k,2)\cos\left(\frac{2\pi k}{N}\right) + \overline{X}_s(k,2)\sin\left(\frac{2\pi k}{N}\right),\qquad(2.54)$$

and

$$X_s(k,2) = \overline{X}_s(k,2)\cos\left(\frac{2\pi k}{N}\right) - \overline{X}_c(k,2)\sin\left(\frac{2\pi k}{N}\right),\tag{2.55}$$

where

$$\overline{X}_{c}(k,2) = \sum_{n=2}^{N+1} x(n) \cos \left[ \frac{\pi(2n+1)k}{2N} \right]

= X_{c}(k,0) + \left[ -x(0) + (-1)^{k} x(N) \right] \cos \left( \frac{\pi k}{2N} \right)

+ \left[ -x(1) + (-1)^{k} x(N+1) \right] \cos \left( \frac{3\pi k}{2N} \right),$$

(2.56)

and

$$\overline{X}_{s}(k,2) = \sum_{n=2}^{N+1} x(n) \sin \left[ \frac{\pi(2n+1)k}{2N} \right]

= X_{s}(k,0) + \left[ -x(0) + (-1)^{k} x(N) \right] \sin \left( \frac{\pi k}{2N} \right)

+ \left[ -x(1) + (-1)^{k} x(N+1) \right] \sin \left( \frac{3\pi k}{2N} \right).$$

(2.57)

The lattice module for the block-size-two update is shown in Fig. 2.9. There are two more multipliers in the lattice, *i.e.*, the total number of multipliers is eight.

Figure 2.9: The lattice structure for block-size-two operation on the DCT and DST.

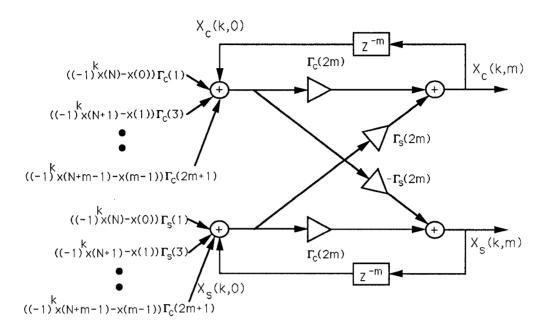

To obtain the transformed data in parallel, we need N such lattice modules. The latency for this kind of parallel structure is N/2 and the total number of multipliers is 8N. Since there is no complex communication problem in the lattice structure, the area-time complexity (AT) can be approximated by the product of the number of multipliers and the time latency, plus the area-time complexity of the adders, which is  $o(m \log(m))$  for adding m data. Next, let us consider the more general case for the block-size-m update, where m ranges from one to N. The 1-D DCT and DST of block-size-m update are to obtain the transform of [x(m), x(m+1), ..., x(N+m-1)] directly from the transform of [x(0), x(1), ..., x(N-1)]. We have

$$X_c(k,m) = \sum_{n=m}^{N+m-1} x(n) \cos \left[ \frac{\pi [2(n-m)+1]k}{2N} \right], \qquad (2.58)$$

and

$$X_s(k,m) = \sum_{n=m}^{N+m-1} x(n) \sin \left[ \frac{\pi [2(n-m)+1]k}{2N} \right].$$

(2.59)

Applying the same procedure in the case of block-size-two update, we can write (2.58) and (2.59) as

$$X_c(k,m) = \overline{X}_c(k,m)\cos\left(\frac{m\pi k}{N}\right) + \overline{X}_s(k,m)\sin\left(\frac{m\pi k}{N}\right),\tag{2.60}$$

and

$$X_s(k,m) = \overline{X}_s(k,m)\cos\left(\frac{m\pi k}{N}\right) - \overline{X}_c(k,m)\sin\left(\frac{m\pi k}{N}\right). \tag{2.61}$$

where

$$\overline{X}_{c}(k,m) = \sum_{n=m}^{N+m-1} x(n) \cos \left[ \frac{\pi(2n+1)k}{2N} \right]

= X_{c}(k,0) - \sum_{n=0}^{m-1} x(n) \cos \left( \frac{\pi(2n+1)k}{2N} \right)

+ \sum_{n=N}^{N+m-1} x(n) \cos \left[ \frac{\pi(2n+1)k}{2N} \right]

= X_{c}(k,0)

+ \sum_{n=0}^{m-1} [-x(n) + (-1)^{k} x(N+n)] \cos \left[ \frac{\pi(2n+1)k}{2N} \right], (2.62)$$

and

$$\overline{X}_{s}(k,m) = \sum_{n=m}^{N+m-1} x(n) \sin \left[ \frac{\pi(2n+1)k}{2N} \right]

= X_{s}(k,0) - \sum_{n=0}^{m-1} x(n) \sin \left[ \frac{\pi(2n+1)k}{2N} \right]

- \sum_{n=N}^{N+m-1} x(n) \sin \left[ \frac{\pi(2n+1)k}{2N} \right]

= X_{c}(k,0)

+ \sum_{n=0}^{m-1} [-x(n) + (-1)^{k} x(N+n)] \sin \left[ \frac{\pi(2n+1)k}{2N} \right]. (2.63)$$

Figure 2.10: The lattice structure for block-size-m operation on the DCT and DST.

Combining those input terms with same cosine and sine multiplier coefficients together, we can obtain the lattice module for block size m as shown in Fig. 2.10. To obtain the transform data X(k) in parallel, N lattice modules of Fig. 2.10 are required. The total number of multipliers of the parallel structure is (4+2m)N, the total number of adders is (3m+2)N, and the throughput is 1. The area-time complexity due to multipliers and adders are (4+2m)N and  $(3m+2)N\log((3m+2)N)$  respectively. Denote ATm as the area-time complexity of the block-size-m update, then  $ATm = (4+2m)N + (3m+2)N\log((3m+2)N)$ . For example,  $AT1 = 6N + [5N\log(5N)]$  and  $AT2 = 8N + [8N\log(8N)]$ . In the limiting case of the block-size-N update, i.e., we move a whole block of the input data sequence,  $ATN \simeq (4+2N)N + 3N^2\log(3N^2)$ . In general, the area-time product gets smaller as block size m decreases. We found that when m = 1, the

minimum AT complexity is achieved.

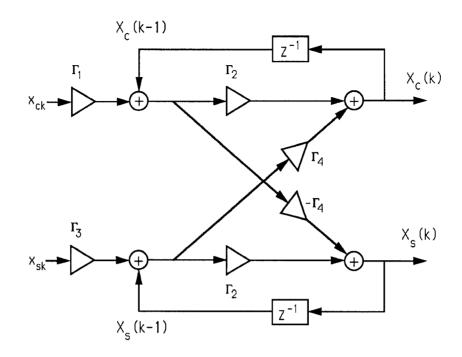

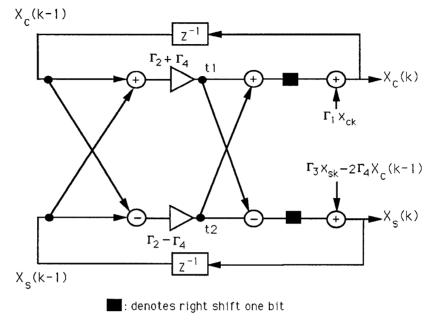

# 2.6 Multiplier-Reduction of the lattice structure

In the VLSI implementation, the number of multipliers is an important factor to the cost and complexity of the system. In this section, we develop two methods to reduce the number of multipliers in our parallel lattice structures. The first scheme makes use of a series input series output (SISO) approach and 2N multipliers can be saved; the trade-off is that the latency and throughput is increased. The second approach, which reconstructs the structure into a double-lattice realization, saves N multipliers and the latency remains intact.

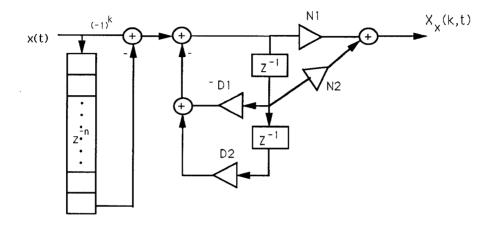

## 2.6.1 SISO Approach

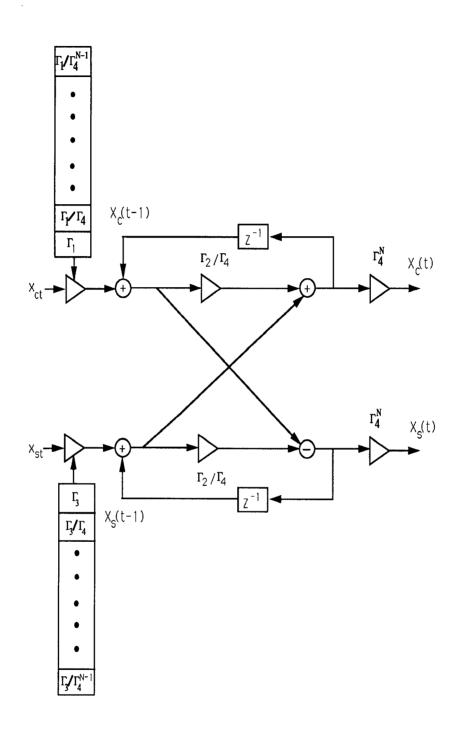

Let us consider this problem through a general lattice structure as shown in Fig. 2.11. Denote the output and input data at time t as  $(X_c(t), X_s(t))$  and  $(x_{ct}, x_{st})$  respectively, where the input and output have the following relations

$$X_{c}(t) = [X_{c}(t-1) + \Gamma_{1}x_{ct}]\Gamma_{2} + [X_{s}(t-1) + \Gamma_{3}x_{st}]\Gamma_{4},$$

$$X_{s}(t) = [X_{s}(t-1) + \Gamma_{3}x_{st}]\Gamma_{2} - [X_{c}(t-1) + \Gamma_{1}x_{ct}]\Gamma_{4}.$$

(2.64)

By dividing both equations by  $\Gamma_4$ , we have

$$X_{c}(t)/\Gamma_{4} = [X_{c}(t-1) + \Gamma_{1}x_{ct}] \Gamma_{2}/\Gamma_{4} + [X_{s}(t-1) + \Gamma_{3}x_{st}],$$