**ABSTRACT**

Title of thesis: IMPACT OF HARDWARE OBSOLESCENCE ON

SYSTEM SOFTWARE FOR SUSTAINMENT-

DOMINATED ELECTRONIC SYSTEMS

Degree Candidate: Arindam Goswami

Degree and Year: Master of Science, 2004

Thesis directed by: Associate Professor Peter A. Sandborn

The last two decades have witnessed manufacturers of sustainment-dominated long field life electronic systems incorporate Commercial Off the Shelf (COTS) technology products into their systems on a large scale. Many of these products, however, have lifetimes of significantly shorter duration than the systems they are incorporated into and as a result become obsolete long before the system's intended duration of useful life is over.

This problem is especially prevalent in avionics and military systems, where systems may encounter obsolescence problems even before they are fielded and always during their support life. Manufacturing that takes place over long periods of time exacerbates this problem.

Many part obsolescence mitigation strategies exist including: lifetime buy, last-time buy, part replacement, aftermarket source, uprating, emulation, reengineering, salvage, and ultimately redesign of the system. Design refresh (or redesign) has the advantage of treating multiple existing and anticipated obsolescence problems concurrently and additionally allows for functional upgrades.

Hitherto, there have been studies concentrated on determining the optimum combination of different obsolescence strategies by using life cycle cost as the deciding criterion. However, these studies take into account *only* hardware life cycle costs. In many systems, such as avionics systems, software life cycle costs (redesign, rehosting and requalification) have a significant bearing on total life cycle cost. Thus software redesign due to part obsolescence triggered hardware redesign should also be addressed during life cycle management planning.

This thesis describes a methodology and it's implementation for determining the hardware part obsolescence impact on life cycle sustainment costs for system software based on future production projections, maintenance requirements and part obsolescence forecasts. The methodology extends the MOCA (Mitigation of Obsolescence Cost Analysis) methodology/tool that determines the optimum design refresh plan during the field-support-life of the

product in order to minimize life cycle cost. The design refresh plan consists of a set of design refresh activities and their respective calendar dates.

The methodology incorporates the use of two software commercial cost analysis models: PRICE S and COCOMO.

The methodology developed in this thesis has been validated using a Navy test case (VH-60N Digital Cockpit Upgrade Program). It has also been applied to Honeywell International, Inc.'s AS900 engine controller. The results obtained demonstrate the necessity of taking software redesign analysis into account during life cycle management planning.

# IMPACT OF HARDWARE OBSOLESCENCE ON SYSTEM SOFTWARE FOR SUSTAINMENT-DOMINATED ELECTRONIC SYSTEMS

by

#### Arindam Goswami

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science 2004

# **Advisory Committee:**

Associate Professor Peter A. Sandborn, Chair Professor Donald B. Barker Associate Professor Omar Ramahi © Copyright by

Arindam Goswami

2004

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to all those who have helped me along the way to the point that I find myself at as I write this thesis. For starters, I wish to thank my advisor, Dr. Peter Sandborn, for his guidance and support and a million other things that have not only helped me during my research but will also stand me in good stead all my life. As it is with pretty much every student in the Sandborn group, to him I owe a lot. I am also grateful to the members of my dissertation committee: Dr. Donald Barker for being very patient and accommodating as I wrote my thesis and postponed my defense more than once and Dr. Omar Ramahi for having agreed to be on my committee at such short notice.

Thanks are due to all my lab mates and friends (together this list is big enough for me to not take individual names – but you all know who you are), past & present, for all their support.

Finally, I would like to thank my family for their love and support. I can never put into words all the gratitude that I feel – so, I shall not even try.

# TABLE OF CONTENTS

| LIST OF TABLESvii                                                                |

|----------------------------------------------------------------------------------|

| LIST OF FIGURESviii                                                              |

| Chapter 1 - Introduction                                                         |

| 1.1 The Use of Commercial Off the Shelf (COTS) Technology in Avionic Systems 1   |

| 1.2 The Problem of Component Obsolescence                                        |

| 1.3 Motivation For Tackling Part Obsolescence in a Proactive Manner              |

| 1.3.1 Short-Term Obsolescence Mitigation                                         |

| 1.3.2 Long-Term Obsolescence Mitigation                                          |

| 1.4 The Impact Of Part Obsolescence On System Software                           |

| 1.5 The Objective of this Thesis                                                 |

| Chapter 2 - Solution Architectures                                               |

| 2.1 Hardware Obsolescence Precipitated Change in System Software                 |

| 2.2 Software Design Refresh by Quantifying Change in the Number of Source        |

| Lines of Code (SLOC) Due to a Hardware Part Obsolescence Event                   |

| 2.3 Software Design Refresh by Fault Tree Based Analysis of Functional Blocks 22 |

| 2.4 Remarks                                                                      |

| Chapter 3 - Software Redesign Analysis Applied to Design Refresh Planning        | . 30 |

|----------------------------------------------------------------------------------|------|

| 3.1 Introduction                                                                 | . 30 |

| 3.2 Overall MOCA Methodology And The Incorporation Of Software Redesign          |      |

| Analysis                                                                         | . 30 |

| 3.2.1 The Problem Addressed by MOCA                                              | . 32 |

| 3.2.2 MOCA Analysis Algorithm                                                    | . 33 |

| 3.3 MOCA Interfaces For Collecting Inputs Pertinent To Software Redesign         |      |

| Analysis                                                                         | . 40 |

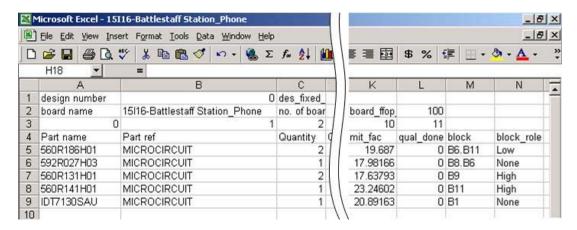

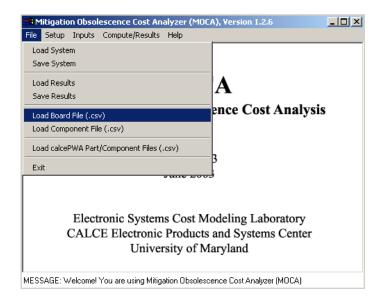

| 3.3.1 Board-Specific Parts List                                                  | . 41 |

| 3.3.2 Functional Blocks Data                                                     | . 43 |

| 3.3.3 PRICE S/COCOMO Data                                                        | . 45 |

| 3.4 Cost Analysis Models                                                         | . 47 |

| 3.4.1 PRICE S                                                                    | . 47 |

| 3.4.2 COCOMO                                                                     | . 50 |

| 3.5 Remarks                                                                      | . 57 |

| Chapter 4 - Results                                                              | . 59 |

| 4.1 Introduction                                                                 | . 59 |

| 4.2 Application of the Methodology to the AS900's FADEC System                   | . 59 |

| 4.2.1 Part Obsolescence impact on life cycle cost (Software and Hardware) of the |      |

| A \$900 system                                                                   | 61   |

| 4.2.2 Part Obsolescence impact on life cycle cost of AS900 system software    |    |

|-------------------------------------------------------------------------------|----|

| alone                                                                         | 52 |

| 4.2.3 Impact of "Design refresh look-ahead time"                              | 54 |

| 4.3 Validation Of the "Software Design Refresh" Analysis Methodology          | 67 |

| 4.3.1 Implementation of the methodology                                       | 57 |

| 4.3.2 Validation                                                              | 71 |

| 4.4 Remarks                                                                   | 73 |

| Chapter 5 - Conclusions and Future Work                                       | 74 |

| 5.1 Summary                                                                   | 74 |

| 5.2 Contributions                                                             | 74 |

| 5.3 Future Work                                                               | 75 |

| 5.3.1 Spare Replenishment                                                     | 75 |

| 5.3.2 Software Design Refresh by Fault Tree Based Analysis of Functional      |    |

| Blocks                                                                        | 77 |

| 5.3.3 Improving Efficiency                                                    | 77 |

| Appendix A: Function/Feature Point Counting                                   | 78 |

| A.1 Overview                                                                  | 78 |

| A.1.1 Introduction to Function/Feature Point Counting and the factors used in |    |

| these techniques                                                              | 78 |

| A.1.2 Definitions                                                             | 32 |

| A.1.3 Counting Function Points and Sizing System Software                     | 85 |

| Appendix B: MOCA | PRICE S Inputs Pe | rtinent to Software | Redesign Analysis | 91  |

|------------------|-------------------|---------------------|-------------------|-----|

| REFERENCES       |                   |                     |                   | 100 |

# LIST OF TABLES

| Table 2.1: Enumeration of steps common to the two approaches for software design     |    |

|--------------------------------------------------------------------------------------|----|

| refresh explained in Sections 2.1 and 2.2                                            | 25 |

| Table 2.2: Tabular representation of dependency of functional blocks on one another  | 26 |

| Table 3.1: Enumeration of possible design refresh schedules for the case depicted in |    |

| Figure 3.2                                                                           | 37 |

| Table 3.2: Effort Adjustment Factors                                                 | 57 |

| Table 4.1: SLOC and APPL values for the functional blocks in the test case           | 70 |

| Table 4.2: Actual cost incurred by the Navy (Data provided by PRICE systems)         | 72 |

# LIST OF FIGURES

| Figure 1.1 Industry wise usage of electronic components in 1999 [Condra, 1999]           | . 2 |

|------------------------------------------------------------------------------------------|-----|

| Figure 1.2 Shrinking trend in component technology life cycles [Condra, 1999]            | . 3 |

| Figure 1.3: Technology element lifetimes compared to product lifetimes for airplanes and |     |

| computers [Condra, 1997]                                                                 | . 5 |

| Figure 1.4: The link between functional description and hardware and software            |     |

| components of the system                                                                 | 10  |

| Figure 2.1: Software design refresh by quantifying change in the number of source lines  |     |

| of code (SLOC) due to hardware part obsolescence event.                                  | 14  |

| Figure 2.2: Fault tree for a hypothetical system                                         | 23  |

| Figure 2.3: Software design refresh by Fault tree based analysis of functional blocks    | 24  |

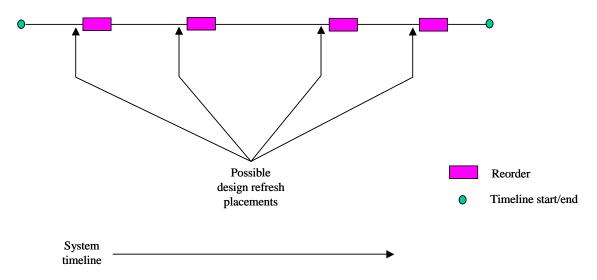

| Figure 3.1: MOCA system timeline                                                         | 35  |

| Figure 3.2: Associating design refreshes with reorders [Singh, 2001]                     | 36  |

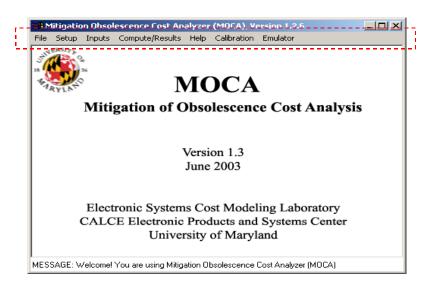

| Figure 3.3: The MOCA tool                                                                | 41  |

| Figure 3.4: An example of a comma-delimited file for loading a board specific parts list |     |

| into MOCA                                                                                | 43  |

| Figure 3.5: MOCA interface for loading a board-specific part list                        | 43  |

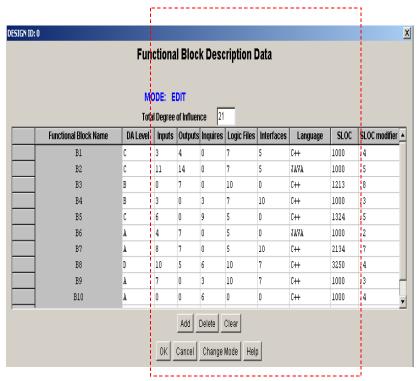

| Figure 3.6: Interface for collecting Functional Blocks inputs                            | 44  |

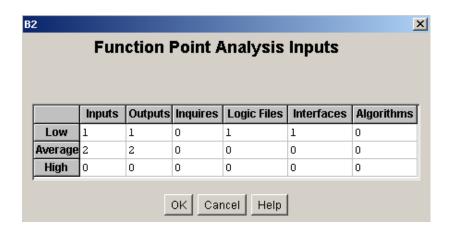

| Figure 3.7: Inputs required for function point counting                                  | 44  |

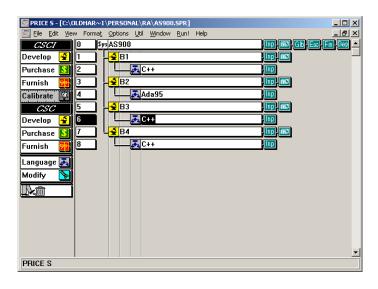

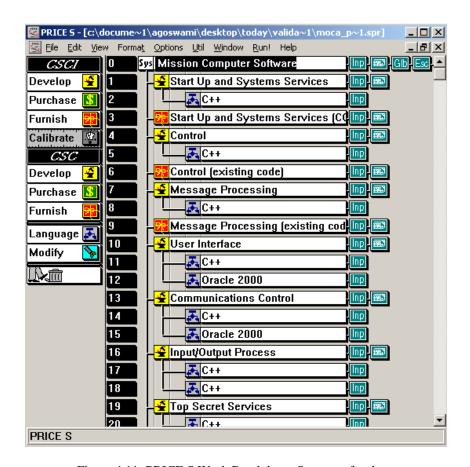

| Figure 3.8: PRICE S EBS                                                                  | 45  |

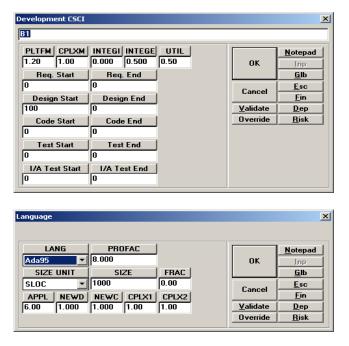

| Figure 3.9: PRICE S Interface for collecting the main inputs                             | 46  |

| Figure 3.10: MOCA Interface for collecting COCOMO inputs                                 | 46  |

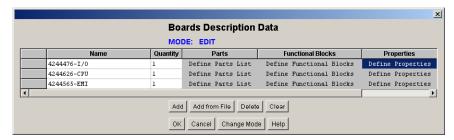

| Figure 4.1 Boards Dialog box                                                             | 59  |

| Figure 4.2: Functional Blocks Dialog box                                              | . 60 |

|---------------------------------------------------------------------------------------|------|

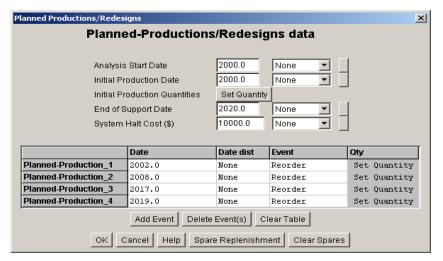

| Figure 4.3: Production schedule for the AS900 system                                  | . 60 |

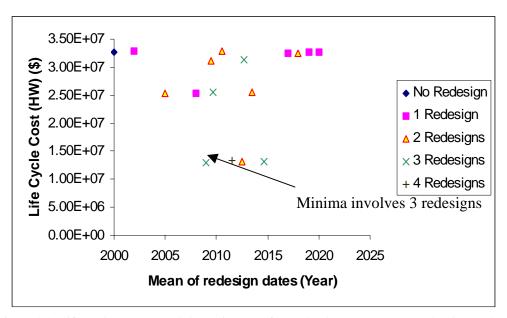

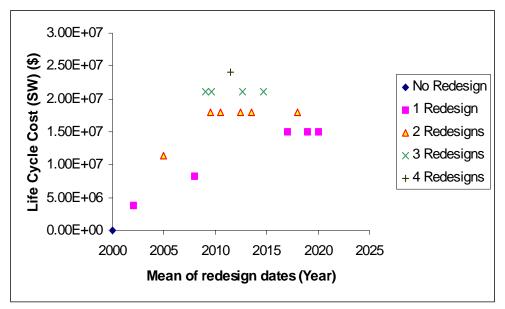

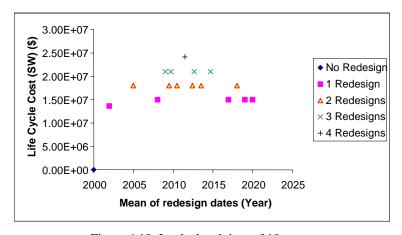

| Figure 4.4: Life cycle cost accrued due to impact of part obsolescence on system      |      |

| hardware alone                                                                        | . 62 |

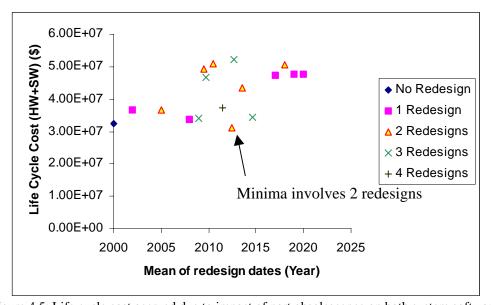

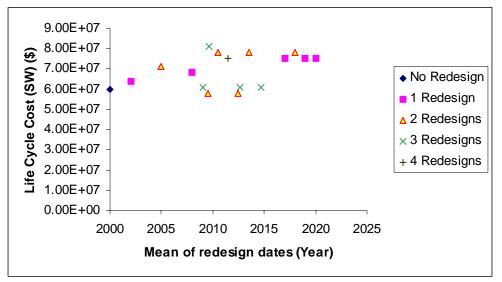

| Figure 4.5: Life cycle cost accrued due to impact of part obsolescence on both system |      |

| software and system hardware                                                          | . 62 |

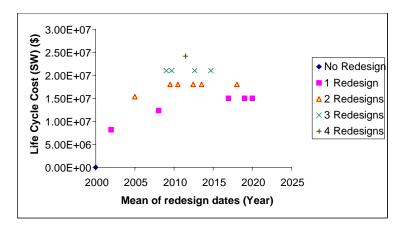

| Figure 4.6: Life cycle cost accrued due to impact of part obsolescence on system      |      |

| software alone                                                                        | . 63 |

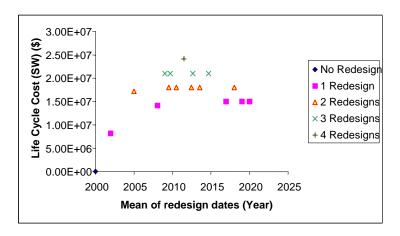

| Figure 4.7: Life cycle cost accrued due to "impact of part obsolescence on system     |      |

| software" and "software maintenance"                                                  | . 64 |

| Figure 4.8: Look-ahead time of 3 years                                                | . 66 |

| Figure 4.9: Look-ahead time of 5 years                                                | . 66 |

| Figure 4.10: Look-ahead time of 10 years                                              | . 66 |

| Figure 4.11: PRICE S Work Breakdown Structure for the test case                       | . 71 |

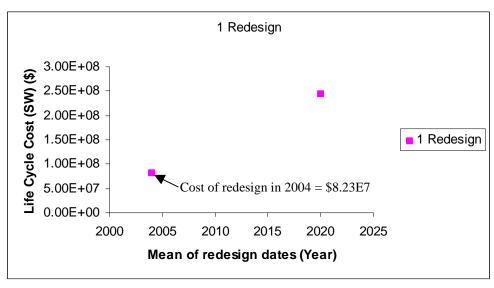

| Figure 4.12: Software redesign cost incurred due to hardware upgrade of test case     | . 72 |

| Figure 5.1: Model for spare replenishment                                             | . 75 |

## **Chapter 1 - Introduction**

### 1.1 The Use of Commercial Off the Shelf (COTS) Technology in Avionic Systems

Electronic components are ubiquitous in airplane systems: they are found in almost every system, including those that are primarily mechanical, hydraulic, and pneumatic. The solid-state electronics industry has grown in parallel with the airplane industry. Until the mid nineteen eighties, commercial aerospace manufacturers depended on a well-developed military electronic components and specifications infrastructure to assure long-term availability of components that met their needs. This was possible because the military market sector alone comprised about 25% of the total market for electronic components [Condra, 1999]; it was responsible for a good deal of the device innovation, and therefore owned many device designs. As a result, military and commercial aerospace electronic design, manufacturing, procurement, operation, maintenance, and support decisions had traditionally been based on two assumptions:

- 1. The supply of electronic components specified to operate in aerospace environments is unlimited; and

- 2. Component designs will remain stable for long periods of time.

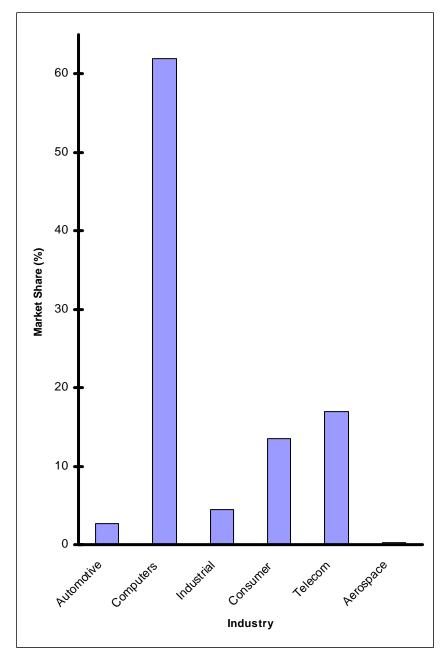

However, these assumptions are no longer true, especially sine 1992, when many major manufacturers of electronic components, including Motorola, Intel, and Philips, exited the military market [Wright et. al., 1997]. As shown in Figure 1.1, the entire aerospace industry now consumes less than one per cent of the electronic components produced. The major component markets are computers, consumer electronics, and others, which do

not have the demanding environmental or long production life cycle requirements of aerospace products.

Figure 1.1: Industry wise usage of electronic components in 1999 [Condra, 1999]

As a result of these trends, the availability of components actually specified for aerospace applications is decreasing. The response of the aerospace industry has been to

incorporate, on a large scale, commercial off the shelf (COTS) technology in its systems.

COTS refers to commercially available products that can be purchased and integrated into existing systems with little or no customization and thereby lead to cost savings as compared to designing new parts every time.

Especially in the case of military applications, the focus on commercial support of aviation systems is driven by the modernization needs faced by all the branches of the military at a time when resources for acquisition of new defense systems are increasingly constrained. The procurement lull in new system acquisition, and the increasing reliance on aging platforms far past their original planned life cycle, is expanding the need for a concerted effort to upgrade and maintain existing systems. Innovative approaches for the support of existing systems can be used to produce life cycle savings, reduce cycle times and improve performance [JACG, 1999].

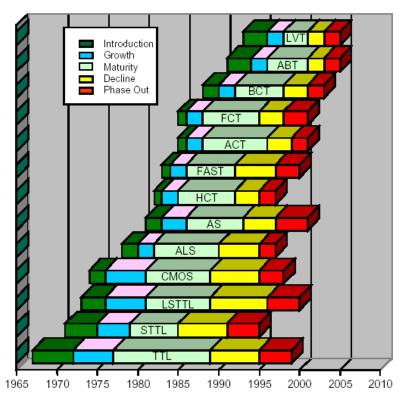

Figure 1.2: Shrinking trend in component technology life cycles [Condra, 1999]

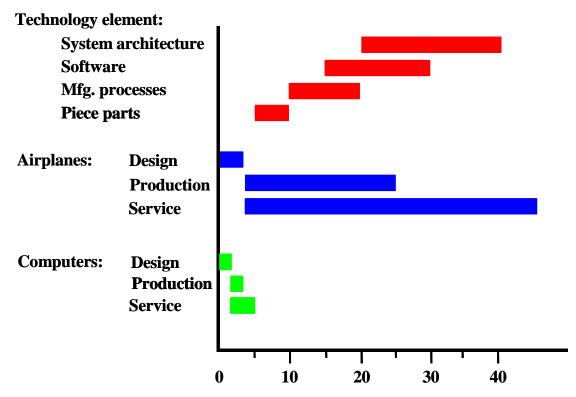

However, there are many challenges associated with doing so. Figure 1.2 shows that the life cycles of all integrated circuit technologies are shrinking, almost to the point where the term *component technology life cycle* is meaningless [Baca, 1997]. Even stable component designs are modified constantly to reduce cost, improve yields, and enhance performance. The modifications are evaluated and characterized for high volume applications, such as computers, but the applications of low volume users such as aerospace are rarely considered. The lifetime of a typical jet airplane will encompass many generations of electronic component design, as illustrated in Figure 1.3. For example, the F/A-22, which entered dedicated initial operational test and evaluation (DIOT&E) in 2003, was already suffering due to this life cycle mismatch, with technology refreshment required before the aircraft has even reached operational service [MAT, 2003].

Thus we are confronted with a situation in which the aerospace industry depends on electronic components, but can no longer count on sources of stable supply that are specified for its specific applications. The aerospace industry must learn how to use components conceived and produced for other industries (these components having a much shorter life cycle than the system they go into) while keeping total life cycle costs at an acceptable level. This mismatch becomes especially critical because over their extended lifetime these systems are faced with the following situations [Singh, 2001]:

- a) Field failures Defects in the system may cause it to fail before its field life is completed necessitating the manufacturing of additional spare units.

- Design changes Additional requirements may be added after the design stage is completed.

c) Production spread out over the lifetime of the product - Production may be distributed over time either in a planned fashion or as the result of additional orders for the product.

Figure 1.3: Technology element lifetimes compared to product lifetimes for airplanes and computers [Condra, 1997]

## 1.2 The Problem of Component Obsolescence

The aerospace industry has responded to the changing scenario by implementing activities that can be broadly grouped into three categories: (1) How to anticipate occurrences of component obsolescence; (2) How to react to occurrences of component obsolescence; and (3) How to quantitatively estimate, during the design process, the impact of the life cycle mismatch between avionic systems and the components that go into them. It is important to understand the problem of part obsolescence in order to fully appreciate these activities.

A part is obsolete when the technology that defines the part is no longer implemented. Diode Transistor Logic (DTL) and Resistor Transistor Logic (RTL) parts are examples of obsolete part technologies. There are many reasons why parts go obsolete, including [Singh, 2001]

- Manufacturing of the part is not cost effective for the current manufacturers.

- The manufacturers have better opportunities in the market for other products and therefore their interests migrate.

- The market is governed by products with large-scale production and therefore

manufacturers refuse to produce smaller volume specialized products (if the

requirement for the obsolete part(s) is relatively small).

- The raw material or equipment needed for the manufacturing of obsolete parts is hard to maintain or procure.

- Changes in legislation make the materials or processes associated with a part impractical or illegal to continue using.

There may be more specific reasons why parts go obsolete depending upon the part and the market conditions, however in most cases it is the technology push (i.e., development and introduction of a new technology) and the manufacturer's interests, which lead to part obsolescence.

An appreciation of these driving factors along with an understanding of component technology trends (for example, Moore's law), taking into account technology roadmaps and building flexibility into the original design (for example, partitioning designs to place high-risk components on throwaway modules) will enable system designers to be better prepared to tackle the problem of component obsolescence.

#### 1.3 Motivation For Tackling Part Obsolescence in a Proactive Manner

Component obsolescence entails issues that have a direct and significant impact on the total life cycle cost. It influences both hardware and software (as discussed in the next section). Consider, for example [Singh, 2001], that a manufacturer, which manufactures a long field life system, has a need to manufacture additional systems. Assume in this case that some of the parts required to manufacture the system are obsolete. The manufacturer would try to procure those obsolete parts from external vendors, who purchased and stored obsolete parts for later sale. These vendors inflate the price of the obsolete parts they have been storing and therefore these obsolete parts are then procurable at some cost penalty to the manufacturer. The manufacturer has little choice but to incur the cost increase. Now the manufacturer has two options for handling the increased cost. One option (not possible in many cases because of contractual obligations) is to carry over the extra cost of the obsolete parts to the buyer (customer). The second option (most likely the real world scenario) is that the manufacturer bears the extra expenses of the obsolete part itself. This extra cost increases the life cycle cost to the manufacturer. It can be clearly understood that for aircraft with 30-plus year production lives, unforeseen part obsolescence costs can mount significantly if one depends on reactive solutions. On the one hand is the option of facing up to the obsolescence problem in a purely "reactive manner". This entails performing obsolescence management only when intimation about an obsolescence event is received - no planning is done at an earlier stage to mitigate the obsolescence of parts. When a notice indicating that a part is going to become obsolete in the near future is received from the part manufacturer, various obsolescence management strategies are evaluated

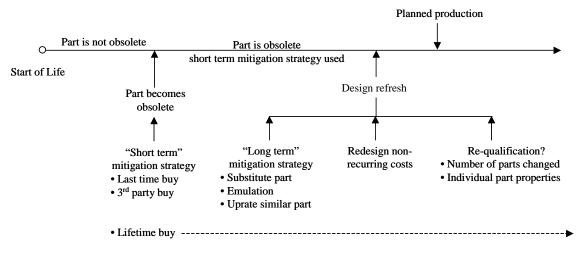

and the most economically feasible option is chosen. However, the costs incurred on account of such unplanned activities can be quite large. It is much more prudent to be pro-active and take cognizance of the problem beforehand and consider all possible combinations of different obsolescence mitigation strategies which can minimize sustainment costs. As can be seen from the above example, the manufacturer will be motivated to explore different obsolescence mitigation approaches in order to minimize the total costs incurred by him. These mitigation approaches, e.g., short-term approaches (for example, last-time buy) or long-term approaches (for example storing the obsolete part for the lifetime of the system or eliminating the need for that part completely by redesigning it) then need to be ranked against each other so that the most cost effective mitigation or combination of various mitigation strategies can be adopted. Two broad categories of these strategies are discussed below.

### 1.3.1 Short-Term Obsolescence Mitigation

Short-term obsolescence mitigation involves taking necessary steps to delay the effect of part obsolescence on product sustainment costs until more rigorous measures can be taken to remove the part obsolescence problem, e.g., buy enough parts to last until the part is either replaced by a similar part or the product is redesigned to eliminate use of the part. This strategy is termed as "last-time buy".

#### 1.3.2 Long-Term Obsolescence Mitigation

Long-term obsolescence mitigation is defined as measures taken to either eliminate the obsolete part from the product permanently or to sustain the supply of the obsolete part throughout its lifetime by storing it. The elimination of the obsolete part may involve complete removal of the obsolete parts from the product by redesigning the

product, replacement of obsolete parts with a suitable equivalent substitute part, replacement the obsolete parts with an emulated version of the part, or thermal uprating of a non-obsolete commercial version of the part [Wright, 1997].

Several combinations of different obsolescence mitigation strategies can be adopted at different "time-points" during the lifetime of a system. A tool called MOCA (discussed in Chapter 3) has been developed at the University of Maryland, which through a detailed cost analysis determines the best possible combination vis-à-vis total life cycle cost.

#### 1.4 The Impact Of Part Obsolescence On System Software

Total life cycle cost, generated using life cycle cost analysis (LCCA), is used as a metric to quantify the impact of various factors that have a bearing on it. Life cycle cost is defined as the sum of present values of investment costs, capital costs, installation costs, energy costs, operating costs, maintenance costs, and disposal costs over the lifetime of the project, product, or measure [McArthur, 1989]. LCCA is particularly suited to the evaluation of design alternatives that satisfy a required performance level, but that may have differing investment, operating, maintenance, or repair costs; and possibly different life spans. LCCA can be applied to any capital investment decision, and is particularly relevant when high initial costs are traded for reduced future cost obligations. The MOCA tool allows its users to choose a combination of several possible obsolescence mitigation approaches and then based on the production plan, other system characteristics and system qualification costs carries out a cost analysis - the final output of which is a design refresh plan that defines the best "time-points" in the life of a system at which to carry out design refreshes. A design refresh in the context of MOCA and also

this thesis is defined, [Singh, 2001], as an activity that involves bringing about changes in the design of a system to incorporate one or more of the following:

- a) New or improved functionality

- b) Removal of part obsolescence and other related issues

- c) Aesthetic improvement of product

- d) Ease of use or more user-friendly

- e) Reliability improvement of the system

- f) To make the system more maintainable and repairable

- g) Change in documentation/engineering drawings

- h) Incorporate new technology/innovations

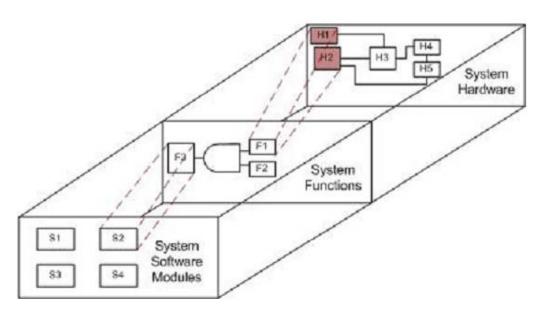

Hitherto, MOCA did not take into account costs arising due the impact of a design refresh activity on the system software. A system's hardware and software components together enable an implementation of its functionality. One or more of the interlinked hardware components execute the functional subtasks - the logic of this execution being determined by the software components. Therefore, there is a link between these components and the functional description of the system. This link is depicted in Figure 1.4.

A design refresh event, as defined above, during the lifetime of a system may result in the introduction of new hardware components or redesign of existing ones. A need to modify the system software arises as a result of that. This modification of system software can entail high costs. These costs are due not only to modification of existing code but also development of new code and software re-qualification. Therefore, there is a need to associate these changes in hardware with the changes in software precipitated

by them in order to quantify the impact of the latter on life cycle cost. The MOCA tool represents an effort to address the problem of hardware obsolescence. The work embodied in this thesis aims at extending this effort to quantifying the impact of software change precipitated a change in hardware incorporate the resulting analysis into MOCA.

Figure 1.4: The link between functional description and hardware and software components of the system [Szabó, 2000]

#### 1.5 The Objective of this Thesis

The starting point for the work done in this thesis is the set of different design refresh plans generated by MOCA. MOCA ranks these different design refresh plans according to the total life cycle cost that each one entails. However, as mentioned above, this life cycle cost did not include the cost accrued on account of the system software that might need to be changed during a design refresh activity. This problem has been addressed here. The objective of this thesis was to determine the impact of part obsolescence on system software for long field life electronic systems based on the

production plan, maintenance requirements and part obsolescence predictions. This impact was to be quantified in terms of acquisition, modification and support costs.

These costs were then added to the costs associated with design refresh and requalification to obtain a net cost. This net cost was to be used by MOCA in its existing cost analysis algorithms to schedule design refreshes during the life of the product in the field. The design refresh plan was to provide the number of design refresh activities and their respective calendar dates to minimize the life cycle sustainment cost of the product.

The approach to associating system software changes to the hardware obsolescence events, which precipitate them, is discussed in detail in Chapter 2. Chapter 2 also documents the degree to which the steps in the solution have been implemented in this work. The MOCA tool is discussed in Chapter 3. The various interfaces are explained. The cost model used is discussed in detail therein. Chapter 4 contains a case study. The output from the analysis performed on the case study example is compared with some real world data. The refined insights into the problem at hand yielded by this comparison are discussed. Chapter 5 contains a discussion of the contributions made by this thesis, the existing shortcomings in the present model and the future work that needs to be done.

## **Chapter 2– Solution Architectures**

### 2.1 Hardware Obsolescence Precipitated Change in System Software

As discussed in Chapter 1, cost analysis and careful planning in the initial stages of system design can help mitigate component obsolescence related costs in long field life systems. The studies carried out in the University of Maryland have hitherto concentrated on hardware costs alone that arise from component obsolescence. However, for many sophisticated systems, functionality is software driven. Therefore, there is a link between the system software, which "thinks" and the system hardware which "acts". At a hardware component obsolescence event, the linkage between hardware and software may result in a need to change portions of the system software. Software changes can be categorized into three types [Wong, 1996]:

- a) Adaptive changes,

- b) Perfective changes, and

- c) Corrective changes.

Adaptive changes accommodate technological improvements/changes. Perfective changes seek to make future evolution somehow better, more manageable and less costly. Corrective changes focus on detecting, tracking, and diagnosing defects and their root causes. The effective management and execution of these changes is critical and defines a significant portion of the system's life cycle cost. The software changes being dealt with in this thesis are primarily of the "adaptive" type. At a hardware obsolescence event the impact of this change has to be quantified and factored into the existing cost analysis. Two approaches for doing so will be discussed in this chapter (Sections 2.2 and 2.3).

# 2.2 Software Design Refresh by Quantifying Change in the Number of Source Lines of Code (SLOC) Due to a Hardware Part Obsolescence Event

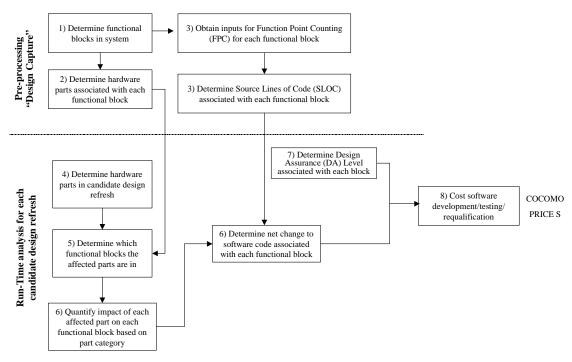

Figure 2.1: Software design refresh by Fault tree based analysis of functional blocks. (Note: The numbers in the boxes correspond to the sequence in which the respective steps have been explained below)

There are certain characteristics of a software functional block (explained below) that influence software development costs. These characteristics are modified at the time of a design refresh activity depending on how the hardware parts participating in it are modified. The software redesign approach illustrated in this section works by capturing all the characteristics of the system (of the Hardware parts as well as the functional blocks), gauging how these are modified during design refresh and then using the modified values, in conjunction with commercial software cost estimating tools such as

PRICE S or COCOMO, to calculate software development costs. The block diagram for this approach is shown in Figure 2.1 and is described below.

#### Pre-processing "Design Capture":

1) Determine functional blocks in the system and their attributes - Determining functional blocks involves understanding what the major functions performed by the system software are. The system is partitioned into functional blocks such that each of these blocks can be thought of as performing one particular function. These blocks are not necessarily physical partitions. A functional block might, and in most cases will, include hardware parts that are physically remote from each other. Partitioning the system into functional blocks seems logical in light of the fact that system software is modular in nature, i.e., it contains modules - each of which performs a different function. Each functional block can be thought of as a mapping onto a software module that has some fixed attributes.

Two of these attributes are implementation language (C++, ADA, etc.) and Source Lines of Code (SLOC)<sup>1</sup>. They are used in the quantitative analysis as discussed in Chapter 3. Another set of fixed attributes (Inputs, Outputs, Logical Files, Interface files and Inquires) is used for function point counting. These will be explained in Appendix A. "SLOC modifier" is an attribute that varies during run-time and gives a measure of how much SLOC associated with a functional block needs to be changed at an obsolescence event. It does this by quantifying the impact of the parts that participate in the block, which have gone obsolete.

-

<sup>&</sup>lt;sup>1</sup> Code refers to the symbolic arrangement of data or instructions in a computer program. It is a series of statements written in some human readable computer programming language. SLOC is a metric that is used to measure the number of such statements in a software program.

As mentioned above, the final software cost estimation is performed using tools such as PRICE S or COCOMO. This requires that certain other inputs pertaining to the functional blocks, needed by the cost estimating models employed by these tools, be acquired as well. These inputs, which will be explained in Chapter 3, are entered at this stage.

- 2) Determine hardware parts associated with each functional block In this step, information about participation of a hardware part in a functional block is extracted from the parts list (described in Chapter 3). Information extracted includes, among other things:

- a) Which block(s) the hardware part participates in, and

- b) The level of participation (characterized by "High", "Medium", "Low" or "None") and the number of instances of this hardware part in the functional block(s) in question.

Consider, as an example, a computer. It uses a monitor as an output device for display purposes. The Operating System (OS) contains a software module dedicated to manage the "display" functionality. We treat the "display" function as one functional block and the monitor as one of the hardware parts involved in realizing this functionality. If a significant amount of code in the software module is dedicated to "driving" the monitor; then, in the event that this particular monitor becomes obsolete, a large amount of software code may have to be re-written. This necessitates that, in order to capture this large degree of dependence, it be recorded, during pre-processing, the fact that the hardware part (monitor) participates in the functional block (display) and *also* that the

level of participation of the former in the latter is "High". This step can be thought of as one that determines the mapping between the hardware parts of the system and the functional blocks.

3) Determine Function/Feature Point Count inputs for the functional blocks and hence the SLOC associated with each block - In order to understand the methodology of "software design refresh by quantifying the change in the Number of Source Lines of Code (SLOC)", it is important to grasp the concept of Function/Feature Point Counting.

Function/Feature Point Counting is a technique by which, based on certain characteristics specific to the functionality of a software module (in the context of this thesis – the functionality of a functional block), the metric Function Point Count is generated – which in turn lends itself to an estimation of the size of the module, i.e., number of lines of code needed to implement the desired functionality, depending, of course, on the language used for coding (e.g., C++, JAVA).

A Function Point Count is a metric used to measure the functionality, and, from it the size of a software system. It can be used in the early stages of development. Function Point Counting begins by identifying the components of the system as seen by the enduser. These components are the inputs, outputs, inquiries, interfaces to other systems, and logical internal files. There may be several instances of each component. The components are then classified as simple, average, or complex. Numerical values are assigned to each component type depending on the number of instances of it in the system and the classification (simple, average or complex) of each of these instances. These values are then added and the resulting total is called "Unadjusted Function Point total (UFP)".

Complexity factors described by 14 general systems characteristics, such as reusability, performance, and complexity of processing are scored on a scale of 0 - not present, 1 - minor influence, to 5 - strong influence. The sum of scores of all the complexity factors is multiplied by the UFP to get the net function point count. This count can then be related by empirical factors to system size.

One might question, "Why go through this software sizing procedure when the number of lines of code for each functional block is available upfront?" The reason for this is that when a hardware part is redesigned, and some *new* code is to be developed as a result of that, it is not always possible to directly estimate how many lines of code will be needed. It is better to estimate the impact that the redesigned part will have on the functionality of the functional block(s), which it participates in. This changed functionality can, in turn, be used to calculate the change in function point count and from this the number of new lines of code can be estimated. This estimate is more realistic.

The details of Function Point Analysis can be found in Appendix A. The discussion therein contains an introduction to the history of Function/Feature Point counting, pertinent definitions, the factors used in this technique and a detailed explanation of the technique itself, i.e., the procedure to obtain the "counts" and size software code using them.

At this point, it is important to keep in mind that as per the solution architecture developed in this thesis, the system designer supplies the quantitative inputs required for function point analysis for all the functional blocks; using which the SLOC (and also the

*change* in SLOC at any point during the system's lifetime) associated with each one of them can be calculated.

Steps 1, 2 and 3, i.e., determining the functional blocks in the system, acquisition of data on how the hardware parts to relate to these blocks, and the function point analysis inputs for the functional blocks together constitute "Design Capture" of the system.

#### Run-time Analysis for each candidate design refresh

- 4) Determine hardware parts affected in candidate design refresh plan As mentioned in Chapter 1, the starting point for the implementation of the methodology<sup>2</sup> developed in this thesis is the design refresh plan generated by MOCA. This design refresh plan contains, among other things, a list of parts that have to be changed/modified at a particular date during the system's lifetime. This list of affected parts is imported for the purpose of software redesign analysis.

- 5) Determine which functional blocks the affected parts are in This information is obtained from the mapping developed in Step 2 during the pre-processing phase. It should be noted that a particular hardware part might belong to more than one functional block. For example, a microprocessor in a computer will participate in several functions to be performed by the system. In a case like that an analysis of the impact on each functional block has to be carried out separately.

At this stage, all the information obtained in the abovementioned steps is sorted to obtain, for each functional block, a list of affected hardware parts that participate in it.

\_

<sup>&</sup>lt;sup>2</sup> Hereafter referred to as the software redesign analysis

6) Quantify impact of each affected part on each functional block based on part category and hence SLOC change for the latter- Each of these affected parts belongs to a certain part category [Singh, 2001]. This input indicates the type of part being used. Several part categories are available in MOCA. These are: Microcircuit, Diode, Transistor, Integrated circuit, Semiconductor, Assorted and Custom Defined. The "Assorted" part type is used to represent an aggregate of parts and their instances. All the parts, which do not have any obsolescence or maintenance issues (e.g., most passives and mechanical devices), are lumped together into a single part to reduce computation time. A "Custom Defined" part is a part type for which no single standard part type could be used. When a new part is synthesized as a result of a design refresh, the obsolescence date is reset based on a default and a lifetime is obtained based on the part category of the modified part.

Software redesign analysis is carried out for every functional block. Based on the category that each of the affected parts belongs to and the number of instances of that part in the functional block being considered, a value is obtained for "SLOC modifier" (for that particular hardware part), which is a measure of how much SLOC associated with a functional block needs to be changed during design refresh on account of the hardware part in question. The rationale for this step is that a complex part (such as a microprocessor) going obsolete will result in a larger code change than a simple part (such as a resistor) going obsolete.

The appropriate function point inputs for each functional block can be recalculated using the "SLOC modifier" values for all the affected parts that participate in it. Using these modified function point inputs the amount of new SLOC to be generated, i.e., the net change in SLOC ( $\Delta KSLOC$ ), can be calculated for each functional block.

7) Determine Design Assurance (DA) level associated with each block - These levels are a measure of the criticality and complexity of the function performed by each of these blocks. They have a strong bearing on the re-qualification costs of the system. DA levels 'A' through 'E' correspond to failure condition classifications catastrophic, hazardous, major, minor, and no effect, respectively. During the analysis a Design Assurance (DA) level associated with the affected functional blocks is calculated. For each functional block the DA level is identified based on system Functional Hazard Assessment [Beland, 2000]. Prior to the start of the analysis, an assessment of complexity is made for each functional block. Typically, software code dealing with Math functions or String manipulation is assigned a lower DA level (i.e., E), while functional blocks that deal with functions such as Real time command and control operations are assigned higher DA levels.

8) Cost software development and testing – The final costing is done using either the PRICE S model or COCOMO. For this purpose, all the requisite parameters (acquired during "design capture"), including the ones with modified values (on account of the above steps) are sent to one of these tools<sup>3</sup>. Cost values for new software development for

-

<sup>&</sup>lt;sup>3</sup> In the case of PRICE S, the communication between it and MOCA takes place via a dynamic link library (DLL) included in MOCA. DLLs are a collection of small programs, which can be called upon when needed by the executable program (exe) that is running. The DLL lets the executable communicate with some other program and contains source code to do particular functions.

all the affected functional blocks are summed up and the total is added to the life cycle cost.

These steps are repeated for all the candidate design refreshes. Prior to the introduction of software redesign analysis, MOCA would rank different design refresh plans (each plan containing one or more design refreshes – the total for each plan being the sum of costs entailed on account of all the design refreshes contained in it) based on total cost. The same thing is done now – with the difference that the totals contain a "software redesign cost" as well – which may change the rankings.

## 2.3 Software Design Refresh by Fault Tree Based Analysis of Functional Blocks

This approach is similar in many regards to the one outlined in Section 2.2. Functional blocks and Function Point analysis are used in this approach too. "Design Capture" as explained in the previous section is a portion of this approach as well. The difference lies in the fact that this methodology attempts to make use of, if available, the fault tree for the system software.

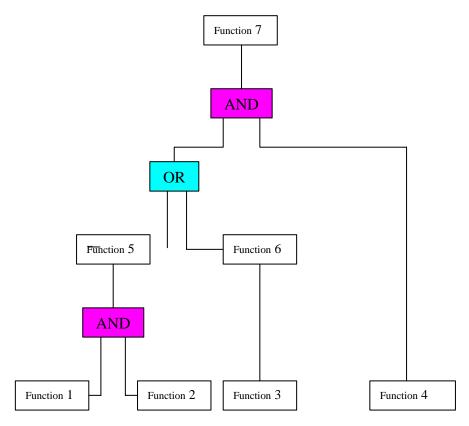

A Software Fault Tree is a graphical technique for identifying and documenting the combinations of lower level software events that allow a top-level event to occur [Leveson, 1995]. Software Fault Tree Analysis (SFTA) is a deductive, top-down method used to analyze system functionality. An example of a fault tree based functional description of a software system is shown in Figure 2.2. In this three-tier fault tree, Function 1, Function 2, Function 3 and Function 4 are bottom events; Function 5 and Function 6 are intermediate events and Function 7 is the top event. An OR gate signifies that a function is implemented if *any* of the functions below it are realized while an AND gate signifies that a function is implemented only if *all* the functions below it are realized.

The example of Figure 2.2 is a very simple one. An actual system is likely to have more tiers with several other intermediate events of different types with more complex relationships denoted by the various logic gates.

Figure 2.2: Fault Tree for a hypothetical system

For the purpose of the methodology discussed in this section, a fault tree can allow automation of the procedure to determine criticality levels of the functional blocks (analogous to DA level in the previous approach). This is because "criticality" values can be assigned to functional blocks based on where they exist in the hierarchy of the tree – with higher values assigned to blocks at the top of the tree.

Another advantage is that a fault tree gives a better idea about the interdependencies between the different functional blocks – something that was not taken into account by the previous method. This can have a significant bearing on qualification costs because if one functional block is redesigned then all the functional blocks connected to and above it on the tree may have to be qualified as well.

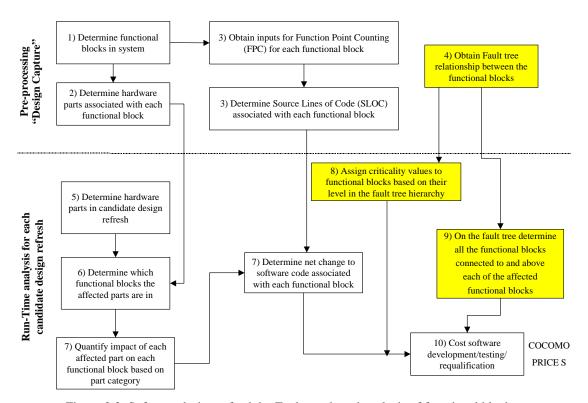

The block diagram for using fault-tree based analysis for software redesign approach is shown in Figure 2.3.

Figure 2.3: Software design refresh by Fault tree based analysis of functional blocks. (Note: The numbers in the boxes correspond to the sequence in which the respective steps have been explained below)

It should be noted that some of the steps are the same as in the previous approach. Table 2.1 lists all the steps that are common to the two approaches. Their explanation is the same as in the previous section. The new steps in this approach, indicated by the shaded boxes in the block diagram, will be explained below.

Table 2.1: Enumeration of steps common to the two approaches for software design refresh explained in Sections 2.1 and 2.2

| Step Number in Section 2.2 | Step Number in Section 2.3 | Remarks                                                                                                                                                                                        |

|----------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                          | 1                          | Determine functional blocks in system                                                                                                                                                          |

| 2                          | 2                          | Determine hardware parts associated with each functional block                                                                                                                                 |

| 3                          | 3                          | <ul> <li>Obtain inputs for Function Point Counting (FPC) for each functional block</li> <li>Determine Source Lines of Code (SLOC) associated with each functional block</li> </ul>             |

| 4                          | 5                          | Determine hardware parts in candidate design refresh                                                                                                                                           |

| 5                          | 6                          | Determine which functional blocks the affected parts are in                                                                                                                                    |

| 6                          | 7                          | <ul> <li>Quantify impact of each affected part on each functional block based on part category</li> <li>Determine net change to software code associated with each functional block</li> </ul> |

| 8                          | 10                         | Cost software development/testing/requalification                                                                                                                                              |

As mentioned above, for Steps 1-3 refer to Section 2.2

4) Obtain Fault tree relationship between the functional blocks – This requires an understanding of how the functional blocks are connected to each other. The system designer should have an appropriate blueprint for the software architecture of the system.

This blueprint can be specified in the form of a tabular arrangement. For the fault tree

shown in Figure 2.2, disregarding the logic gates for the moment, this tabular arrangement is shown in Table 2.2

| Parent     | Child      | Remarks  | Tier   |

|------------|------------|----------|--------|

| Function 7 | Function 5 | Top_Node | Tier 3 |

| Function 7 | Function 6 | Top_Node | Tier 3 |

| Function 7 | Function 4 | Top_Node | Tier 3 |

| Function 6 | Function 3 |          | Tier 2 |

| Function 5 | Function 2 |          | Tier 2 |

| Function 5 | Function 1 |          | Tier 2 |

| Function 4 |            |          | Tier 1 |

| Function 3 |            |          | Tier 1 |

| Function 2 |            |          | Tier 1 |

| Function 1 |            |          | Tier 1 |

This tabular arrangement can be stored in the form a Text file that can then be read and converted into a Fault tree. This can be done by using the following two-part algorithm starting with the above table in the form of a text file:

```

Find_ Top _Node (file)

Step 1 Scan "Remarks" column for Top _Node

Step 2 For each row with Top _Node found do

Step 2.1 function = function listed in "Parent" column

Step 2.2 Create node in tree for function and call it Top_Node

Step 2.3 Set function_tier = entry in "Tier" column

Step 2.4 Fault_Tree_Create (function, file)

```

```

Fault_Tree_Create (function, file)

Step 1 Scan "Parent" column for function

Step 2 For each row with function found do

Step 2.1 child = Function listed in "Child" column

Step 2.2 Connect child to function

Step 2.3 Set child_tier = entry in "Tier" column

Step 2.4 child = Fault_Tree_Create (child, file)

```

After the fault tree has been created, a relationship analysis along the lines of Software Failure Modes, Effects and Criticality Analysis (SFMECA) can be carried out [Dehlinger, 2004] to determine the appropriate inclusion of Logic Gates between the different functional blocks.

Steps 1, 2, 3 and 4, i.e., determining the functional blocks in the system, acquisition of data on how the hardware parts to relate to these blocks and the function point analysis inputs for the functional blocks, and "reading" the software fault tree together constitute "Design Capture" of the system.

Steps 5, 6 and 7 correspond to the Steps 4, 5 and 6 in Section 2.2 respectively.

- 8) Assign criticality values to functional blocks based on their level in the hierarchy of the fault tree- These values are a measure of the criticality and complexity of the function performed by each of these blocks. They have a strong bearing on the requalification costs of the system. These values can be assigned on the basis of the following information extracted from the fault tree:

- a) The tier at which the functional block exists. A higher tier function should be assigned a greater weight than a lower tier one.

- b) Type of "Logical" connection to the function at the tier immediately above. A greater weight should be assigned if the connection is of the "AND" (because of

the indispensability of the lower tier function implied by an AND gate) type than if it is of the "OR" type.

The purpose of this weighting is to establish the significance and criticality of the individual functions in the overall scheme of things.

9) Determine all the functional blocks connected to and above each of the affected functional blocks – In this step we determine, for each affected functional block, i.e., one for which new code is being developed, which are the other blocks that need to be requalified. The rationale for this step is that in addition to an affected block, which has to go through the entire software development cycle that includes design, development and testing; all functional blocks dependent on it have to be requalified as well.

Information pertaining to the dependency can be extracted from the fault tree by locating all the functional blocks connected to and above it in the tree. This method has the inherent flexibility to take into account only those connected blocks that are a specified number of tiers above the affected functional block. Also, if the affected block is connected to a block in the tier above by an "OR" gate, requalification for the latter may not be so critical. Thus the analysis can be tweaked in tune with the user's specifications.

Step 10, i.e., to cost software development and testing is the same as Step 8 in Section 2.2.

#### 2.4 Remarks

The solution scheme of Section 2.2 alone has been implemented in this thesis. The other approach (Section 2.3) entails the problem of reading a fault tree with its logical connections into MOCA. It should be noted that this could not be performed

successfully and was an impediment in the implementation of the methodology being described in this section.

However, It must be mentioned that this approach continues to be a potential candidate method for mapping software to hardware, which, of course, lies at the heart of the software design refresh methodology.

# Chapter 3 - Software Redesign Analysis Applied to Design Refresh Planning

#### 3.1 Introduction

A methodology and its implementation (Mitigation of Obsolescence Cost Analysis - MOCA) has been developed at the University of Maryland [Singh and Sandborn, 2002] for determining the part obsolescence impact on life cycle sustainment costs for the long field life electronic systems based on future production projections, maintenance requirements and part obsolescence forecasts. Based on a detailed cost analysis model, the methodology determines the optimum design refresh plan during the life cycle (design, production, and operation and support) of the product. The design refresh plan consists of the number of design refresh activities, their respective calendar dates and content to minimize the life cycle sustainment cost of the product. The methodology supports user determined short- and long-term obsolescence mitigation approaches on a per part basis and allows for inputs to be specified as probability distributions that can vary with time. Outputs from this analysis are used as inputs to the PRICE System's PRICE H/L commercial software tools for predicting life cycle costs of systems. As mentioned in Chapter 2, this tool hitherto took into account the impact of hardware obsolescence on only the system hardware. This thesis introduces into MOCA the ability to account for the impact of hardware obsolescence on system software as well. In this chapter, the implementation of the software redesign analysis within MOCA is described.

Some of the commonly used terms in this chapter are:

- 1) System The entity for which the sustainment cost is being evaluated. A system may be composed of multiple boards.<sup>4</sup> The System represents the top node in the System-Board-Part hierarchy.

- 2) Board Subsystems that contain multiple parts. All parts that belong to the system must belong to at least one board. The system part list is obtained by accumulating the part list from each board.

- 3) Part A part represents a unique part number, name or identification number in the system. It is an entity that resides on the boards. Each board may have multiple identical instances of a single part. A single part may also appear within multiple boards.

- 4) Component A specific instance of a hardware part. Usually distinguished from other instances by the board it is in and its physical location on a board.

- 5) Functional Block A portion, or module, of system software dedicated to performing one specific function. Each functional block can be mapped onto a software module. These blocks do not necessarily correspond to physical partitions.

- 6) Event An occurrence that affects the system life cycle could be part obsolescence, design refresh (defined in Chapter 1) or a reorder<sup>5</sup>.

In Section 3.2, the overall MOCA methodology and the incorporation of the software redesign approach of Section 2.2 into it will be explained. Interfaces for collecting inputs

<sup>&</sup>lt;sup>4</sup> MOCA accommodates an arbitrary hierarchy of boards within boards. The system is the "container" for the entire board hierarchy.

<sup>&</sup>lt;sup>5</sup> An event that brings an additional number of instances of the system into existence. It can be due to planned production of units spread over the lifetime of the system or additional orders during the system's field support life.

pertinent to software redesign analysis will be described in Section 3.3. Wherever appropriate, these inputs will be discussed. Discussion of the cost models employed by the PRICE S and COCOMO tools is the subject of Section 3.4

# 3.2 Overall MOCA Methodology And The Incorporation Of Software Redesign Analysis

The MOCA tool is a JAVA application created at the University of Maryland [Singh and Sandborn, 2002]. MOCA, which is an acronym for Mitigation of Obsolescence based Cost Analysis, can be used during the design stage of the life cycle, to predict the cost of sustaining the system. Its primary use is to compare, in terms of sustainment cost, several life cycle management strategies for a design. From an overall system point of view, the model helps to focus designers on the specific parts/boards, the obsolescence of which may cause problems and escalate life cycle cost.

# 3.2.1 The Problem Addressed by MOCA

Suppliers of low-volume electronics products need to support their products over extended time periods. In many cases, the parts that are used in these products are obsolete prior to the end of the product's life. The system manufacturer (sustainer) is then faced with a series of alternatives. Often the decision boils down to whether to make a "last-time buy" of parts necessary to last until the next design refresh, a "lifetime buy" of parts necessary to last through the remaining predicted life cycle of the product, count on being able to purchase required parts from third parties (whether they are the original part, emulated, or a replacement part), or to initiate an immediate design refresh in order to design the part out of the product (i.e., by replacement or elimination). Design refresh is often very expensive, requiring extensive engineering, qualification testing, and

certification. Making the problem worse, revisions to software necessitated by the new parts can also involve significant engineering effort (and re-qualification), sometimes exceeding that required for hardware design and qualification.

On the one hand, system sustainers do not wish to pay increased prices for obsolete parts and do not wish to risk losing the ability to sustain a system, but on the other hand, too many design refreshes to avoid obsolescence issues may be extremely expensive. Somewhere between these extremes lies an optimum balance between non-design refresh obsolescence mitigation solutions and design refreshes. MOCA performs a tradeoff analysis to find this optimum point.

# 3.2.2 MOCA Analysis Algorithm

The algorithm employed by MOCA can be broken down into the following steps:

- Step 1: Determine system details relevant information pertaining to the system, constituent subsystems (boards), and individual parts is collected. This information includes forecasting part obsolescence.

- Step 2: Determine the order of known events the events (reorders, part obsolescence and redesigns) affecting the system are determined and arranged in an ordered list called an 'Event List'

- Step 3: Schedule design refresh activities at various stages in the life of the product based on the planned production schedule.

For each design refresh activity:

- Step 4: Calculate costs accrued by affected system hardware

- Step 5: Calculate costs accrued by affected system software

Step 6: Sum the costs due to events during the product's life for each design refresh plan generated in Step 4 and Step 5

Step 7: Rank the various design refresh plans

These steps have been elaborated on below.

### Step 1: Determine system details

Three categories of inputs are necessary to populate the model.

- a) Part inputs: Part costs, reliability data, part characterization data, functional block participation data and obsolescence data.

- b) Board (any subsystem containing parts) inputs: Board assembly, disassembly, test, qualification and total acquisition costs, and the list of parts assigned to each board. The overall part list for the system is obtained by combining the part lists of each board.

- c) System inputs: Dates for the beginning and end of the system's life

In addition to these, solution control inputs are used to control various parameters

used in computing the sustainment cost and planning the design refreshes.

Appendix B explains all the inputs mentioned above in detail.

# Step 2: Determine the order of known events

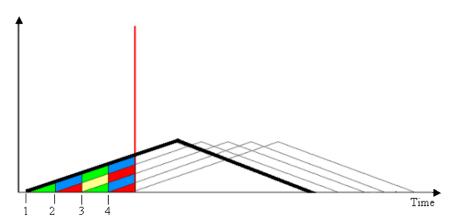

The events that a system undergoes in its lifetime include part obsolescence events, reorder events and design refresh events. All these events contribute to the sustainment cost. Figure 3.1 shows the simplified MOCA view of events that are relevant to design refresh optimization.

Figure 3.1: MOCA system timeline

a) Part obsolescence Events: A part is obsolete when the technology that defines the part is no longer implemented. Part obsolescence has been explained in Section 1.2. The obsolescence date of a part in MOCA is the date after which the part is no longer available from the original manufacturer (from which the part was procured for the current design).

Obsolescence can be handled in a variety of ways in MOCA:

- Purchase and store the obsolete part(s) (lifetime buy, in-store) and use whenever required

- Replace the obsolete part(s) with the same part(s) but with different procurement cost(s) (aftermarket source)

- Replace the obsolete part(s) with different part(s) with different or similar cost(s) but with same functionality (part substitution, emulation, reverse engineering)

- Design refresh of the system to eliminate the need of the obsolete part(s)

- b) Reorders (Planned Production): The reorder date represents the start of processing of an order request or start of a planned production. With every reorder, a new quantity of systems comes into existence. Each order will correspond to a different start date on the system timeline. A reorder can occur due to production spread over the lifetime of the product. The production can be for units, which were planned initially at the design stage, or additional orders during the product's field support life.

- c) Design Refresh: The design refresh date refers to the completion of all the design refresh activities carried on the product. In MOCA, a "Design Refresh" is equivalent to redefining the part set used in the system. "Design Refresh" has been defined in Section 1.4. Every time a design refresh event is specified, a new part set needs to be specified, and the new part set is used for all calculations beyond that point. Any future reorders made are manufactured on the basis of the new design.

Step 3: Scheduling "design refresh" activities

Figure 3.2: Associating design refreshes with reorders [Singh, 2001]

MOCA schedules design refreshes immediately before the reorder events. This is because scheduling it at any other time point before the reorder involves the risk of parts becoming obsolete between the design refresh and the reorder event. This step minimizes the time span between a design refresh and the next reorder, thereby eliminating the need to perform another design refresh because of any probable part obsolescence during that time period. Thus design refreshes can be thought of as being associated with reorders. This is depicted in Figure 3.2. For the case shown in Figure 3.2, a total of 15 design refresh plans are possible. These plans are enumerated in Table 3.1:

Table 3.1: Enumeration of possible design refresh schedules for the case depicted in Figure 3.2

| Point(s) on system timeline at which "design refresh" event is inserted | Remarks                                                  |  |  |  |  |

|-------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

| A                                                                       | Design refresh plan with ONE design refresh activity     |  |  |  |  |

| В                                                                       | Design refresh plan with ONE design refresh activity     |  |  |  |  |

| С                                                                       | Design refresh plan with ONE design refresh activity     |  |  |  |  |

| D                                                                       | Design refresh plan with ONE design refresh activity     |  |  |  |  |

| A+B                                                                     | Design refresh plan with TWO design refresh activities   |  |  |  |  |

| A+C                                                                     | Design refresh plan with TWO design refresh activities   |  |  |  |  |

| A+D                                                                     | Design refresh plan with TWO design refresh activities   |  |  |  |  |

| В+С                                                                     | Design refresh plan with TWO design refresh activities   |  |  |  |  |

| B+D                                                                     | Design refresh plan with TWO design refresh activities   |  |  |  |  |

| C+D                                                                     | Design refresh plan with TWO design refresh activities   |  |  |  |  |

| A+B+C                                                                   | Design refresh plan with THREE design refresh activities |  |  |  |  |

| A+B+D                                                                   | Design refresh plan with THREE design refresh activities |  |  |  |  |

| A+C+D                                                                   | Design refresh plan with THREE design refresh activities |  |  |  |  |

| B+C+D                                                                   | Design refresh plan with THREE design refresh activities |  |  |  |  |

| A+B+C+D                                                                 | Design refresh plan with FOUR design refresh activities  |  |  |  |  |

# Step 4: Calculate costs accrued by affected system hardware

- All the events are inserted into the system timeline in the order of their dates of occurrence.

- At a part obsolescence event, the part is treated according to its individual user-specified obsolescence mitigation strategy. The part's original cost is multiplied with an obsolescence mitigation factor that depends on the type of mitigation strategy adopted and the new cost is rolled up to the board level. This "rolling-up" reflects the fact that eventually a higher cost will be incurred to procure that board. The system cost is also modified to reflect the parts/board cost changes due to obsolescence events.

- At a reorder event the reorder cost is calculated based on the quantity of systems/boards reordered. At this stage the cost of the system reflects the contribution of all the events prior to the reorder event in question, which have resulted in an increase in the system cost.

- At a design refresh event all parts that have become obsolete prior to it are identified. MOCA also lets the user specify an input called "look-ahead time". This input signifies that whenever a design refresh takes place, MOCA looks-ahead for forecasted part obsolescence issues and proactively removes those part obsolescence problems at the current design refresh opportunity. There is a tradeoff involved over here. By having a large design refresh look-ahead time the number of design refreshes can be reduced. On the other hand by design refreshing parts that are not yet obsolete there is a risk of incurring extra cost for no improvement, i.e.,

there is a possibility that the obsolete part that was proactively design refreshed is never required in the future.

Thus parts that have become obsolete prior to the design refresh event and those that fall inside the "look-ahead" range from the date of the design refresh event are combined into a list of affected parts.

Based on the obsolescence mitigation strategies of the affected parts they can be either redesigned at the design refresh or left as they are for the system's support lifetime.

If they are to be redesigned, user-specified inputs pertaining to the complexity level of the parts and their associated design refresh effort are used to make required changes to the system at a design refresh event and also to determine the cost of the design refresh event itself. New parts without any immediate obsolescence problems are used to replace the obsolete parts. The obsolescence date for the new part is determined by a user input called TACTech lifecode and the average mean lifetime of the part category that the new part belongs to. All the data for the old part in the database is modified with the corresponding values of the new part.

# Step 5: Calculate costs accrued by affected system software

The solution architecture developed in Section 2.2 is applied here. The list of affected parts generated in Step 4 is an input to this step.

For each of the affected parts an assessment is made of its impact on all the functional blocks that it participates in. The cost value returned by PRICE S or COCOMO (which reflects the total effort to develop new code - for all the functional blocks - on

account of one particular type of affected part) is rolled up to the board level. It should be noted that a single type of part might be present on more than one board. Thus, for each board in the system, for rolling up the values to the board level, the PRICE S/COCOMO generated cost value is multiplied by a factor given by the following equation:

$$factor = \left(\frac{\text{Number of instances of the affected part on the board}}{\text{Number of instances of the affected part in the system}}\right)$$

The new cost of the boards, and hence of the system, reflects the cost increase of system software accounting for software redesign.

**Step 6**: Total costs accrued by the system in Step 4 and Step 5 are added up. This is done for each design refresh plan.

Step 7: The various design refresh plans are ranked on the basis on minimum life cycle cost.

# 3.3 MOCA Interfaces For Collecting Inputs Pertinent To Software Redesign Analysis [MOCA user's guide, 2003]

The MOCA tool is a JAVA application. It provides a Graphical User Interface to allow the user to enter various inputs required for solution processing. Some of these inputs have been mentioned briefly in the discussion above. A detailed explanation for all of the inputs is included in Appendix B. The user interfaces for collecting the inputs pertinent to Software Redesign Analysis will be depicted in this section. Clicking the appropriate buttons on the menu bar (shown in Figure 3.3) of the tool opens up these interfaces.

Figure 3.3: The MOCA tool (The Menu Bar is enclosed in the boxed region)

# 3.3.1 Board-Specific Parts List

For every board in the system, MOCA stores a list of parts that belong to that board. Included within the parts list information is<sup>6</sup>:

Part Category: This input indicates the type of part being used. Several part categories are available in MOCA. These are: Microcircuit, Diode, Transistor, Integrated circuit, Semiconductor, Assorted and Custom Defined. The "Assorted" part type is used to represent an aggregate of parts and their instances. All the parts, which do not have any obsolescence or maintenance issues (e.g., most passives and mechanical devices), are lumped together into a single part to reduce computation time. A "Custom Defined" part is a part type for which no single standard part type could be used. When a new part is synthesized as a result of a design refresh, the obsolescence date is reset based on a default and a lifetime is obtained based on the part category of the modified part.

<sup>6</sup> Only those part properties that are important for the software-costing problem have been discussed here.

A complete description of all the properties/units can be found in Appendix B.