ABSTRACT

Title of dissertation: CROSS-LAYER CUSTOMIZATION PLATFORM

FOR LOW-POWER AND REAL-TIME

EMBEDDED APPLICATIONS

Xiangrong Zhou, Doctor of Philosophy, 2008

Dissertation directed by: Professor Peter Petrov

Department of Electrical and Computer Engineering

Modern embedded applications have become increasingly complex and diverse in their functionalities and requirements. Data processing, communication and multimedia signal processing, real-time control and various other functionalities can often need to be implemented on the same System-on-Chip(SOC) platform. The significant power constraints and real-time guarantee requirements of these applications have become significant obstacles for the traditional embedded system design methodologies. The general-purpose computing microarchitectures of these platforms are designed to achieve good performance on average, which is far from optimal for any particular application. The system must always assume worst-case scenarios, which results in significant power inefficiencies and resource under-utilization.

This dissertation introduces a cross-layer application-customizable embedded platform, which dynamically exploits application information and fine-tunes system components at system software and hardware layers. This is achieved with the close cooperation and seamless integration of the compiler, the operating system, and the hardware architecture. The compiler is responsible for extracting application regularities through static and profile-based analysis. The relevant application knowledge is propagated and utilized at run-time across the system layers through the judiciously introduced reconfigurability at both OS and hardware layers. The introduced framework comprehensively covers the fundamental subsystems of memory management and multi-tasking execution control.

## CROSS-LAYER CUSTOMIZATION PLATFORM FOR LOW-POWER AND REAL-TIME EMBEDDED APPLICATIONS

by

## Xiangrong Zhou

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2008

Advisory Committee:

Professor Peter Petrov, Chair/Advisor

Professor Rajeev Barua

Professor Shuvra S. Bhattacharyya

Professor Bruce Jacob

Professor Chau-Wen Tseng

© Copyright by Xiangrong Zhou 2008

#### Acknowledgments

During the years of my Ph.D. study, so many dramatic changes have happened in the school, in the outside world and in myself. I owe my gratitude to all the people who have made it possible for me to complete this journey.

First and foremost I'd like to thank my advisor, Professor Peter Petrov for giving me an invaluable opportunity to work with him on such interesting projects. I really appreciate all his time, financial support and the advises he has given me. It has been my great pleasure to work with and learn from Professor Petrov through the years of study and research.

I would also like to thank Professor Jacob and Professor Barua for giving me suggestions on my proposal. Professor Jacob's advises on academic career and Professor Barua's suggestions on presentations are all helpful to me. I also own great gratitude to Professor Bhattacharyya, Professor Qu, and Professor Jacob for agreeing to serve on my dissertation committee and writing reference letters for my academic job applications. I also owe my great thanks to Professor Tseng for spending his valuable time to serve on my committee as dean's representative.

I would also like to thank the ECE department for supporting me with the Teaching Assistantship in the first two years, and the graduate school for supporting me with the dissertation fellowship. Thank Professor Leandros Tassiulas, Professor John Baras and Dr. Michael Hadjitheodosiou for giving me financial support in the first two summers and leading me into the early research activities. I specially thank Dr. Dan Balon, Dr. Tracy Chung, Maria Hoo and Vivian Lu at graduate office for

helping me handle all the departmental rules and forms.

I would also like to acknowledge help and supports from my fellow graduate student colleagues. The collaboration with Mr. Chenjie Yu and Ms. Alokika Dash is really helpful to me on the multi-processor project I participated. I also appreciate the helps and advises from many former ECE graduates: Mr. Chang Wang, Dr. Hongjun Li, Dr. Zhu Han, Dr. Xiaojiang Du, Dr. Hong Zhao and Dr. Zhanfeng Yue, Dr. Hui Li, Dr Yupeng Cui and Mr. Qigong Zheng. Their help had made my early days of graduate study much easier. I also thank my soccer buddies at Maryland for bringing me so much fun of playing pickup games and tournaments together. I will definitely miss this part of my life the most after I leave Maryland.

I owe my deepest thanks to my family - my mother and father who have always stood by me and guided me through my career, and have pulled me through against impossible odds at times. Words cannot express the gratitude I owe them. Thanks go to my brothers who had encouraged me and given their best support through all the years.

It is impossible to list all, and I apologize to those I have inadvertently left out.

# Table of Contents

| List of Figures |                                   |                                                             |                                                         |                                                                            |

|-----------------|-----------------------------------|-------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------|

| 1               | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | Hardw<br>Cross-                                             | ation                                                   | 1<br>3<br>6<br>9<br>13                                                     |

| 2               | Rela<br>2.1<br>2.2<br>2.3         | Memor                                                       | rk ower Design Techniques                               | 17<br>17<br>20<br>24                                                       |

| 3               | Cros 3.1                          | Direct<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5         | Customization for Memory Management Address Translation | 30<br>30<br>30<br>33<br>39<br>41<br>49<br>52<br>55<br>59<br>61<br>62<br>75 |

|                 |                                   | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7 | Introduction                                            | 75<br>78<br>84<br>87<br>91<br>94                                           |

|                 | 3.3                               | Addres 3.3.1 3.3.2 3.3.3 3.3.4 3.3.5                        | Introduction                                            | 110<br>112<br>116<br>120<br>122<br>122                                     |

|    |        | 3.3.6 Experimental Results                                  | 125 |

|----|--------|-------------------------------------------------------------|-----|

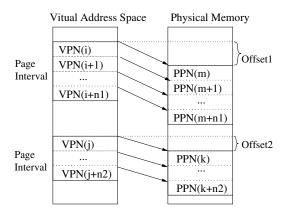

|    | 3.4    | Interval Page Table                                         | 131 |

|    |        | 3.4.1 Introduction                                          | 131 |

|    |        | 3.4.2 Motivation                                            | 133 |

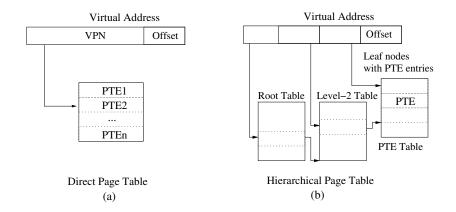

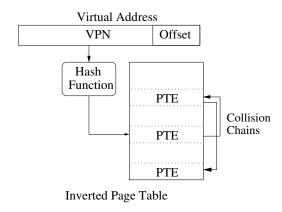

|    |        | 3.4.3 Page Tables Overview                                  | 137 |

|    |        | 3.4.4 The Interval Page Table                               | 140 |

|    |        | 3.4.4.1 IPT Organization                                    | 141 |

|    |        | 3.4.4.2 IPT Manipulation                                    | 143 |

|    |        | 3.4.4.3 IPT Lookup                                          | 146 |

|    |        | 3.4.5 Experimental Results                                  | 151 |

| 4  | Cros   | ss-Layer Customization for Multitasking Management          | 159 |

|    | 4.1    | Introduction                                                | 159 |

|    | 4.2    | Motivation                                                  |     |

|    | 4.3    | State Liveness and Preemption Deferral                      | 168 |

|    |        | 4.3.1 Register Liveness Analysis                            |     |

|    |        | 4.3.2 Switch-Points and Blocks                              |     |

|    |        | 4.3.3 Live State Preservation                               | 175 |

|    | 4.4    | Compiler-driven Context Switch (CCS)                        | 177 |

|    |        | 4.4.1 Compiler and OS Support                               |     |

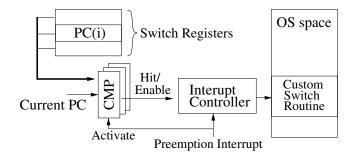

|    |        | 4.4.2 Hardware Support                                      | 182 |

|    | 4.5    | Register Mapped Context Switch (RMCS)                       |     |

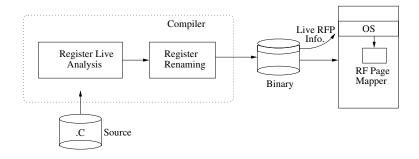

|    |        | 4.5.1 Compiler and OS support                               |     |

|    |        | 4.5.2 Hardware Support                                      |     |

|    | 4.6    | Experimental results                                        | 192 |

| 5  | Com    | piler-driven Register Re-Assignment for Temperature Control | 205 |

|    | 5.1    | Introduction                                                | 205 |

|    | 5.2    | Related Work                                                | 209 |

|    | 5.3    | Motivation for Temperature-Aware Register Re-Allocation     | 211 |

|    | 5.4    | Temperature-Aware Register Re-Allocation Fundamentals       | 215 |

|    |        | 5.4.1 Register Name Reassignment (RNR)                      |     |

|    |        | 5.4.2 Live Range Reassignment (LRR)                         |     |

|    | 5.5    | Register Re-Allocation Algorithms                           |     |

|    |        | 5.5.1 Set-Partition Heuristic for RNR                       |     |

|    |        | 5.5.2 Live Range Reassignment Algorithm                     |     |

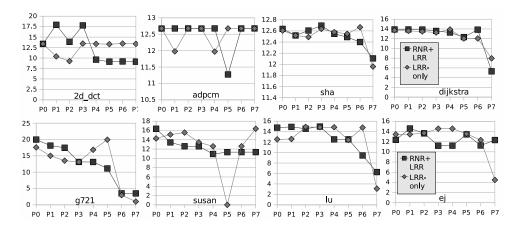

|    | 5.6    | Experimental results                                        |     |

| 6  | Con    | clusion                                                     | 241 |

| Bi | bliogr | raphy                                                       | 243 |

# List of Figures

| 1.1  | Moore's law                                                                                                           | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Feed-Back and Customization Design                                                                                    | 12 |

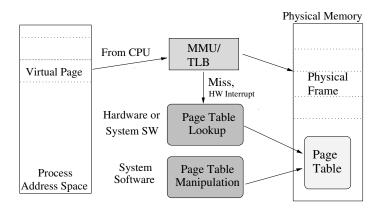

| 3.1  | TLB-based hardware address translation                                                                                | 33 |

| 3.2  | DTT: Software-controlled address translation                                                                          | 33 |

| 3.3  | Set of consecutive VPNs                                                                                               | 35 |

| 3.4  | Indexing SRAM table with LSBs                                                                                         | 35 |

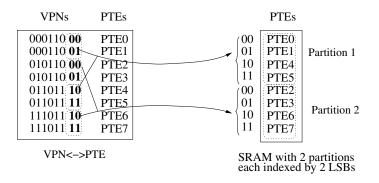

| 3.5  | Two VPN partitions, each indexed by 2 LSBs                                                                            | 36 |

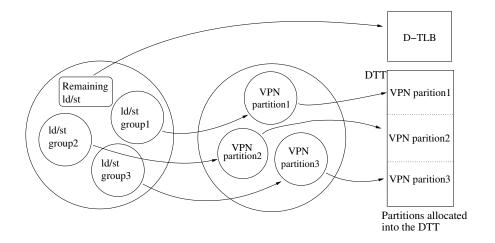

| 3.6  | Mapping VPN partitions to DTT segments                                                                                | 39 |

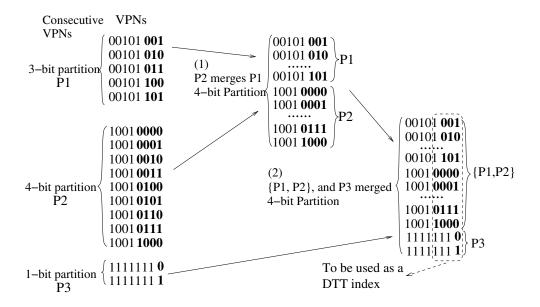

| 3.7  | VPN partition merging                                                                                                 | 43 |

| 3.8  | Pseudo-code of the VPN-partition formation algorithm                                                                  | 46 |

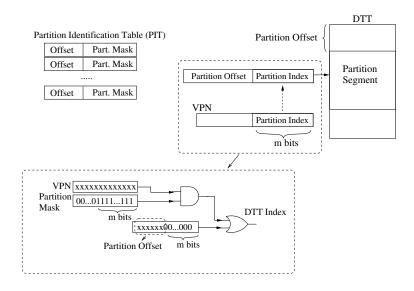

| 3.9  | DTT index computation and DTT access                                                                                  | 57 |

| 3.10 | Hardware architecture                                                                                                 | 58 |

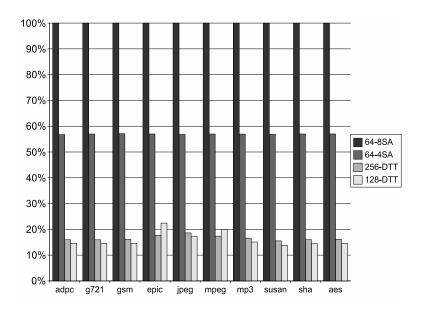

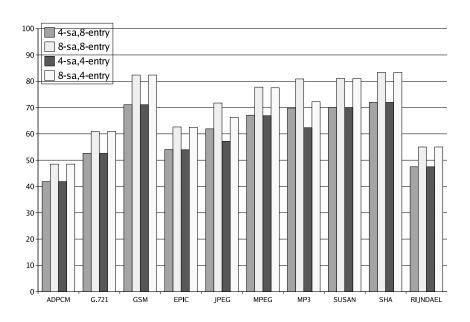

| 3.11 | Energy comparison (normalized) for set-associative organizations                                                      | 73 |

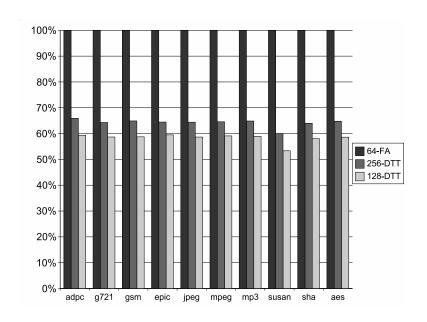

| 3.12 | Energy comparison (normalized) for fully associative organizations . $\ .$                                            | 74 |

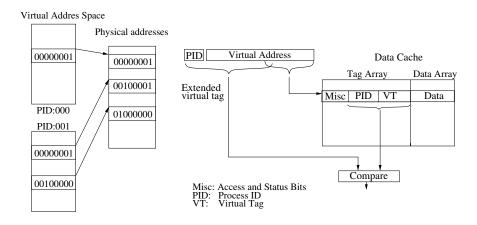

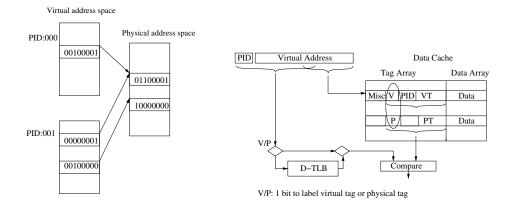

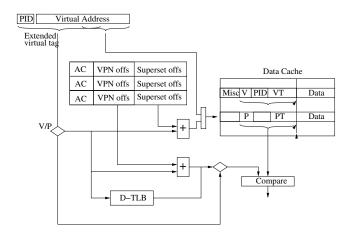

| 3.13 | Using PID to eliminate aliasing with virtually tagged caches                                                          | 79 |

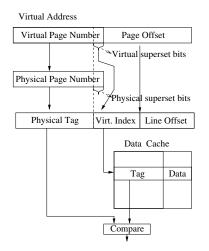

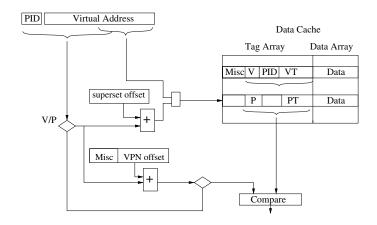

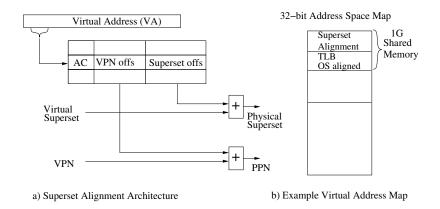

| 3.14 | Superset bits - overlap between virtual index and VPN                                                                 | 81 |

| 3.15 | Conflicting cache indices for the case of synonym groups exhibiting identical physical tags and virtual superset bits | 81 |

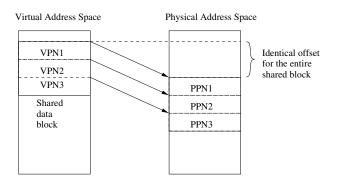

| 3.16 | Two processes sharing one data block; aligned virtual addresses                                                       | 83 |

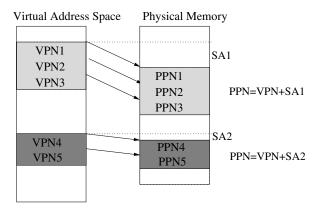

| 3.17 | Linear mapping from VPNs to PPNs                                                                                      | 90 |

| 3.18 | Two processes sharing one data block; non-aligned shared virtual addresses                                            | 92 |

| 3.19 | The Synonym Offset Table (SOT) and the adders for converting superset bits and VPNs                                   | 93 |

| 3.20 | Overall hardware organization                                      |

|------|--------------------------------------------------------------------|

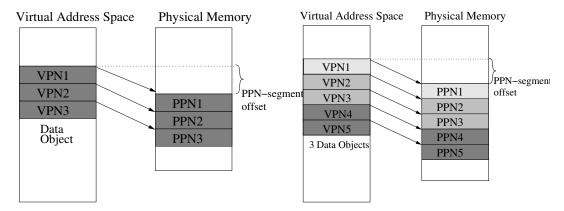

| 3.21 | A data object forming a VPN-segment                                |

| 3.22 | Multiple objects forming a VPN-segment                             |

| 3.23 | Multiple VPN-segments within a task                                |

| 3.24 | Compiler support and setup code insertion                          |

| 3.25 | Mapping load/store instructions to VPN-segments                    |

| 3.26 | SAT table with offsets for PPN computation                         |

| 3.27 | Address translation architecture                                   |

| 3.28 | Energy reduction comparison                                        |

| 3.29 | Virtual memory architecture                                        |

| 3.30 | Traditional hierarchical page table organizations                  |

| 3.31 | Traditional inverted page table organizations                      |

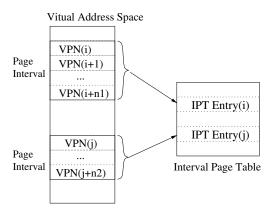

| 3.32 | Page interval example                                              |

| 3.33 | IPT: An entry per page interval                                    |

| 3.34 | Adding an IPT mapping                                              |

| 3.35 | Removing an IPT mapping                                            |

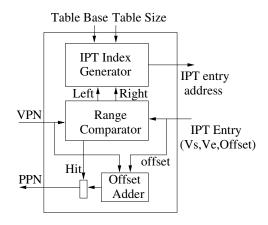

| 3.36 | Hardware for IPT traversal                                         |

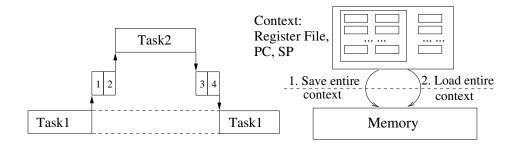

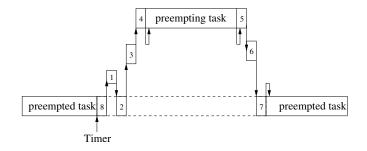

| 4.1  | Context-switch mechanism for preemptive multitasking               |

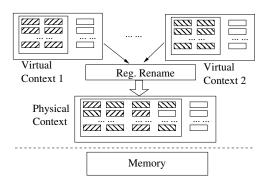

| 4.2  | Hardware register renaming                                         |

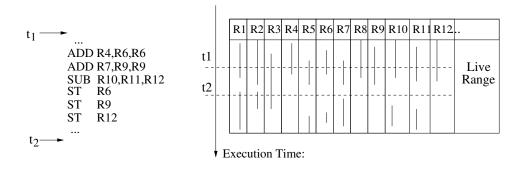

| 4.3  | Register live ranges and live state                                |

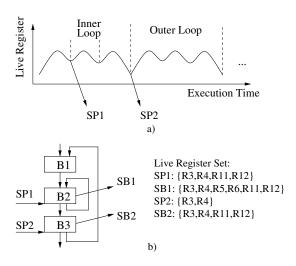

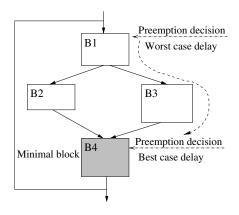

| 4.4  | Application "hotspot" with two <i>switch</i> points and blocks 172 |

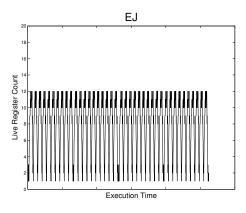

| 4.5  | Register liveness for EJ                                           |

| 4.6  | Register liveness for TRI                                          |

| 4.7  | Switch-points/blocks placement                                     |

| 4.8  | Structure of the CCS live state preservation                                 |

|------|------------------------------------------------------------------------------|

| 4.9  | CCS Hardware Support                                                         |

| 4.10 | RMCS methodology functional overview                                         |

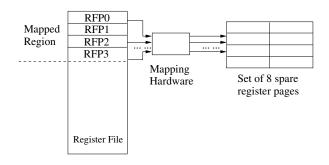

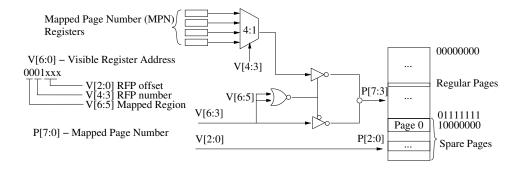

| 4.11 | Mapped register file organization                                            |

| 4.12 | Mapped register file architecture                                            |

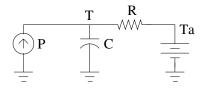

| 5.1  | Thermal RC model                                                             |

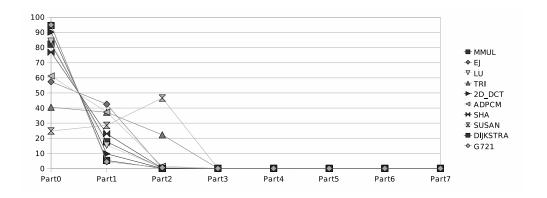

| 5.2  | Histogram of register accesses; Scalar compiler optimizations 211            |

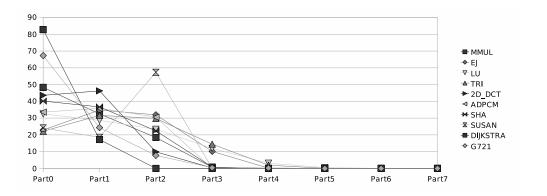

| 5.3  | Histogram of register accesses; Aggressive compiler optimizations 212        |

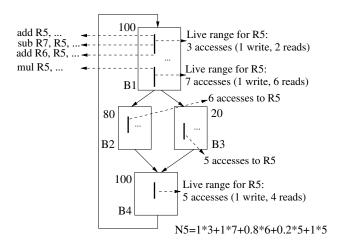

| 5.4  | A loop Control Flow Graph (CFG) and Register live ranges 215                 |

| 5.5  | Register name reassignment                                                   |

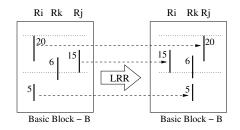

| 5.6  | Live range reassignment (LRR) procedure                                      |

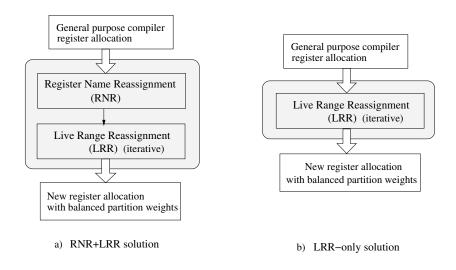

| 5.7  | Overall algorithms for temperature-aware register reallocation 223           |

| 5.8  | Pseudo-code for RNR set-partition heuristic                                  |

| 5.9  | Pseudo-code for live range reassignment (LRR) procedure                      |

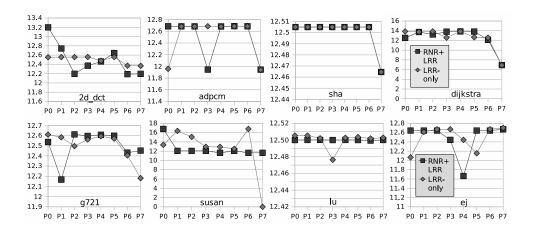

| 5.10 | Achieved register access distribution; Aggressive compiler optimizations 239 |

| 5.11 | Achieved register access distribution; Scalar compiler optimizations . 239   |

#### Chapter 1

#### Introduction

Embedded systems have been extensively used in various markets. These systems can be found in household electronics, office equipments, handhold and mobile devices, and industry control systems. It is estimated that the embedded processors occupy more than 90% of entire processor market, far more than their general-purpose counterparts.

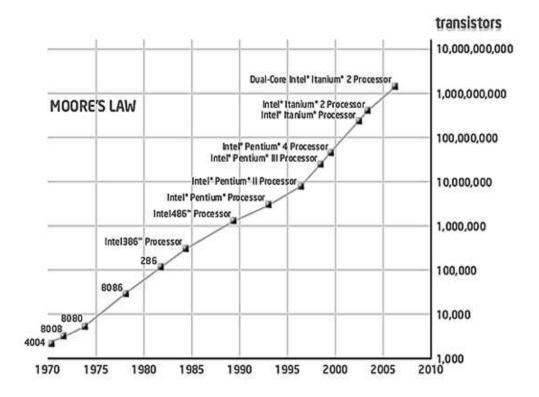

Moore's law, which states that the number of transistors integrated on a single chip doubles about every two years, has been holding true for the past forty years. As shown in Figure 1.1. Chips with billions of transistors are becoming into reality in the past two years. The previous board-level systems now are shrinking into chip-level systems, which are called System-On-a-Chip (SOC). The proliferation of nanometer technologies with ever decreasing geometry sizes has led to proportionally unprecedented levels of SOC integration. The large number of transistors and the high-speed clock frequency have provided powerful computation capability to the SOC platform.

As the direct result, more and more application tasks can be mapped into one SOC, which brings the system complexity to an unprecedented high level. The tasks include data computation, communication and signal processing, real-time control and various other types of applications, which show large diversity in terms of appli-

Figure 1.1: Moore's law

cation property and system requirements. The underlying hardware platforms are very difficult to be optimized for such diverse system requirements. In order to meet all the system performance specifications and efficiently utilize system resources, as well as fast time-to-market, lower design cost, and easier product maintenance, integration of multitude of embedded processor cores and other hardware accelerator blocks with hardware and software co-development have been adopted.

However, many embedded platforms still contain a large number of generalpurpose mechanisms in the microarchitecture, system software and their interactions. Such generalities typically result in excessive power consumption, low performance, and pool real-time guarantee compared to a full-customized design. A cross-layer system customization platform could dynamically integrate application information into system software and hardware platform, thus could fine tune the system to improve the performance and and resource utilization.

#### 1.1 Motivation

Due to the large diversity of embedded system applications, the embedded system designers have to trade off the advantages and disadvantages between hardware and software design approaches. Many of the board-level system designs are combinations of an microprocessor with memory and several hardware logic circuits or peripherals.

The reconfigurable hardware logics dated back to PAL (Programmable Array Logic), where a number of OR gates and AND planes are used to implemented different combinational logic circuit [1, 2]. With the advances of the VLSI technology advances, CPLD(Complex Programmable Logic Device) and FPGA (Field Programmable Gate Array) are used to implement more complex functions in the hardware. Application Specific IC (ASIC) are fully customized with optimal performance, low cost and small hardware area. In the past forty years, the academic research and industry development on electronic design automation (EDA) have revolutionized the design process and significantly increased the hardware design productivity. The rich set of EDA tools basically cover almost every step of the hardware design flow including circuit analysis and simulation, synthesis, place and routing, testing and verification, packaging, etc. The development of hardware

description languages such as Verilog and VHDL makes todays digital hardware development somehow similar to software programming although the knowledge regarding the underlying hardware platform is still necessary.

However, even with such abundant tools, hardware implementation processes are still very expensive with the large initial development cost. The rigorous verification and testing step makes the development cycle rather long compare to software programming. The pure ASIC designs are not flexible for future design modifications and upgrades. On the other side, a hardware design has tremendous advantages of better performance due to parallelism, and lower power overhead and unit cost, compared to pure software design. Thus it is usually used in large volume and commodity or relatively mature applications.

In pure software design approaches, applications are implemented by means of software programs running on microprocessor cores. This processor-based design model is adopted from general-purpose processor system design. The overall system includes several layers: the hardware layer includes processor microarchitecture, memory and I/O devices; the operating system layer includes system functions such as process scheduling and memory management. It also transparently supports all the hardware resource sharing and provides a virtual machine interface to the applications; the application layer includes application programs and libraries, and the corresponding compiler's support. The academic research and industry development on design of microprocessor architecture and embedded operating systems have been very success. Today, the embedded processor commercial products range from very low cost processors like Atmel's 8051, AVR[3], to low-power ARM processor[4], to

relatively high-end PowerPC processor[5]. Special purpose processors such as Digital Signal Processor (DSP) and graphic processor (GPU) have very high performance for certain applications. For embedded operating systems, several products such as VxWorks[6], embedded Linux[7], ThreadX[8], WinCE[9] and etc. have different advantages and are being adopted by the application developers.

The advantages of processor-based software implementation is obvious because of this vertical layered system design and software implementation of user application: application software could be reused across platform, system integration and test are easier than hardware approach, future upgrade and maintenance are more flexible. However, even though most embedded operating systems are designed and implemented with consideration of real-time performance and memory constraints, the application performance and system power consumptions are still less optimized than ASIC implementation.

In todays highly competitive market, embedded applications need to be designed with multi-dimensional requirements in mind. On the business side, the design cost and final product cost are the most influential issues in the market with very low profit margins. Rapid time to market is also very important for the product to lead the trend on both the business and the technical sides. The flexibility of the selected implementation platform could enable new features to be added and thus bring extra profits. It also reduces the design reuse cost. On the engineering side, system performance and throughput are the most important design criteria since many modern embedded applications such as wireless communication and multimedia processing require large computing performance. Power and energy efficiency are

also becoming extremely important, if not more than performance, not only to mobile and hand-held device where battery life directly affects the product acceptance, but also to office and household electronics because of today's high cost of energy. Real-time performance as well as system reliability and security are also very important system requirements, especially for critical applications such as automobile control systems. The SOC (System-On-a-Chip) platform, which integrates multiple processor cores and hardware function blocks, has been tremendously advantageous due to the highly reduced cost, fast time-to-market, low energy consumption, stronger performance, higher reliability, and easier product maintenance. On the SOC platform, the microprocessor cores are either integrated with ASIC blocks or FPGA blocks. The processor cores can be standard processor core such as ARM or PowerPC, or customized such as Application Specific Instruction Processor (ASIP). They can come in the form of either a hard-core or a soft-core implemented with FPGA logic or synthesized beforehand for the specific process technology.

## 1.2 Hardware/Software Co-design

The embedded system design complexity combined with a very tight time-tomarket requirements has revolutionized the embedded system design process. The concurrent design of hardware and software has displaced traditional sequential design. Furthermore, hardware and software design now begins before the system architecture (or even the specification) is finalized. System architects, customers, and marketing departments develop requirement definitions and system specifications together. System architects define a system architecture consisting of cooperating system functions that form the basis of concurrent hardware and software design.

Interface design requires the participation of both hardware and software developers.

The system integration and testing step consists of many individual steps. Reusing components taken from previous designs or acquired from outside the design group (Intellectual Property, or IP) is a main design goal to improve productivity and reduce design risk. A concurrent design starting with a partially incomplete specification requires close cooperation of all participants in the design process. Hardware and software designers and system architects must synchronize their work progress to optimize and debug a system in a joint effort.

Hardware/software co-design methodologies are critical in the design of such complex SOCs. The first challenge is modeling and partitioning system functionality between hardware and software. A major problem in the system partitioning process is synchronization and integration of hardware and software design. This requires permanent control of consistency and correctness. Hardware/software co-simulation is required to have different level of granularity since register-transfer-level (RTL) level hardware simulations are too slow for practical software simulation. The processor, memory and hardware modules must have different abstract execution models for the co-simulation.

The next challenge is hardware/software co-synthesis. Specialized architectures, such as DSP or micro-controllers, dominate the embedded processor market because of their cost and power efficiency. However, automatically generated software code is still not optimal compared to hardware solutions because of the large

overhead in the software implementation due to the microarchitecture complexity and the memory wall. Porting functions between hardware and software implementation is also very difficult. Many high level synthesize tools such as MATLAB or SystemC are developed and suitable for simple architectures and low performance requirements.

Hardware/software co-verification is even more cumbersome as the test space grows exponentially. The software and hardware modules impose different testing granularity and requirements. Automatic and reliable system level testing, especially testing the communication interface between hardware/software boundaries and processor/processor boundaries are still not mature enough for complex application cases.

In overall, hardware/software co-design has made considerable progress in the past few years. Co-simulation, co-synthesis, and co-verification for the SOC development have large advantages in terms of cost, performance, power consumption and reliability, compared the board-level system design with multiple discrete chips.

However, due to the heterogeneous application task and heterogeneous hardware component that are mapped to the SOC, the system level management of the software tasks and hardware component in the complex and dynamic run-time environment are even becoming challenging. The existing system resource management techniques are mostly inherited from general-purpose systems. Many of the system resource management schemes such as memory management, multitasking management are not optimized for these complex SOC platforms, and there exist large system level performance overhead and power over-consumption.

In the next generation of SOC platform, there is strong need to new system resource management techniques that could efficiently handle such complex and dynamic embedded systems. One way to achieve such intelligent management schemes is to dynamically fine-tune the system components to the application property and system requirement in the runtime, so that the overall system performance is improved and power consumption reduced with little system overhead, which motivate my research topic of the cross-layer system customization for low-power and real-time embedded applications.

## 1.3 Cross-Layer System Customizations

Fundamentally, a general-purpose processor architecture is a universal computation engine with a micro-architectural design targeted to achieve good performance and power characteristics on average across a large range of possible programs. While good on average, these micro-architectural components are far from the optimal performance and power points for any particular application. Furthermore, system softwares must always assume worst-case scenarios in terms of system-level information. For instance, to meet the real-time requirement, all tasks are scheduled assuming worst time execution time(WCET). For specific application, this over design under worst-case assumption would result in many waste utilization of system resources.

In embedded processors which adopt super-scalar micro-architecture, program

properties such as branches, data reuse are typically dynamically predicted by runtime traces. Due to limit hardware resource availability and program intrinsic complex logic, this prediction could result in poor estimation of the the real program parameters while adding substantial power consumption.

Certain domain specific processors in which the micro-architecture are designed to focus on certain domains of applications such as digital signal processing, networking switching. Such processors support many general-purpose type of instruction set with enhance of dedicated instruction and micro-architecture support optimized for the representative applications from this domain. For example, as audio/video compression standard typically utilized various DSP algorithm such as FIR/IIF filtering or FFT transformation, a DSP micro-architecture typically includes bit-reverse register addressing and circular buffer addressing mode to speedup the memory access. In high end DSP and graphic processor which utilize VLIW(Very Long Instruction Word) architecture, many Single Instruction Multiple Data (SIMD) instructions are included in the ISA and very complex complier techniques are designed to explicitly perform Instruction Set Parallel (ILP) to speed up the performance.

To further improve the performance for specific application, a type of Application Specific Processor (ASP) has been developed in the past few years. In typical implementation of an Application Specific Instruction Processors (ASIP), a baseline processor micro-architecture is used that can be automatically enhanced with customized instructions to significantly improve performance. Some FPGA-based ASPs have been proposed in [10], where the whole processor core can be reprogrammed

at any time for the target application requirements, including the instantiations of customized pipelines.

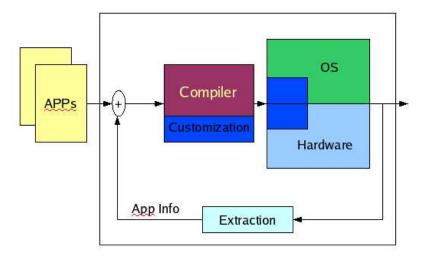

The lack of deterministic application knowledge within the pre-designed systems is the fundamental difficulty in such types of system optimizations. If such application specific information can been extracted and provided to the run-time system, the overall system performance and efficiency can be significantly improved. The compiler could utilize the application information to generate optimal code, the operating system can optimally schedule the tasks for execution and perform context switches efficiently. The micro-architecture can be designed and fine-tuned so that power efficiently is significantly improved. As shown in Figure 1.2, this customization includes the feed-back steps and the customization through all the systems layers including application, operating systems and hardware architecture. To fine-tune the system in the run-time, the feed-back path will extract specific application information either through profiling or run-time monitoring of system properties. The application information is analyzed and partitioned into customization module and distributed into each layer depending the targeting optimization objectives. This could be inserting certain probe code in the binary, or parameter tables to reconfigure the hardware blocks.

With the cooperation of complier, operation system, and hardware architecture, the proposed cross-layer application customizable platform dynamically exploits application information and fine tunes the system software and hardware platform. The compiler is responsible for extracting application regularities through static and dynamic analysis, especially within hot-spot regions which are the most

Figure 1.2: Feed-Back and Customization Design

frequently accessed parts of the application program and where computation is most intensive. A well known rule-of-thumb in computer architecture is that a program typically spend 90% of its execution cycles only in 10% of its code. Such hot-spots usually consist of frequent executed loops or functions, such as various algorithmic (numerical and signal processing) kernels. Because such hot-spot regions of code also potentially contain more regularity, an efficient customization of these hot-spots can significantly improve the performance and energy efficiency.

The system functions within the OS not only can be dynamically adjusted to application requirements, but also in their interaction with both the application and the hardware layers. At hardware architecture level, the right kind of reconfigurability has to be incorporated, since allowing complete FPGA-like reconfigurability would lead to a significant power and performance overheads. The right level of programmability must be identified so that all the relevant application properties

and regularities can be efficiently captured with minimal power, performance, and area impact. This can be efficiently achieved since most of the relevant application information regarding architectural components like caches and TLBs can be easily represented in a very regular way.

## 1.4 Contribution of the Dissertation

The objective of my Ph.D. research is to investigate application customization techniques and incorporate them into a system-level customization platform. The targeted sub-systems that we focused are mainly complex system management services, such as memory management and multitasking management, which typically require system-level information and could not be optimized by software or hardware alone. The substantial customization method will discussed and implemented in simulation tools. Then the overall experiment will by collected and evaluated in terms of performance improvement and power reduction.

Virtual memory has been adopted in general-purpose system for abstraction of memory management, which transparently provides services such as memory reallocation, data sharing and memory protection to application programs. The general-purpose design of virtual memory support requires the cooperation of system software which maintains page tables that hold all the translations mappings between each virtual address and its corresponding physical address, and a hardware cache(TLB, Translation Lookaside Buffer) which caches the most frequently used translation entry. However virtual memory would be beneficial to embedded

system, the non-deterministic TLB access time due to the frequent TLB misses or even page table lookup misses, as well as the excessive energy consumption overhead of TLB hardware accessed in every memory access, have been major obstacles for many embedded processors to support virtual memory in multitasking systems.

I have investigated several customization techniques to facilitate the adoption of virtual memory in low-power embedded systems. Similarly to scratchpad memory(SPM,on-chip SRAM) to replace cache for low-power processor, Direct Translation Table (DTT, a small on-chip SRAM) was proposed to replace TLB to provide deterministic and low-power translation access [11, 12]. Application address mapping information are collect and merged into compact partitions to share the DTT with high utilization. The application and OS work together on prefeteching and sharing partitions on the DTT. When the partitions of consecutive memory block such as large data array or task stacks are mapped consecutively in physical space, the physical page translation procedure is logically adding an offset to its corresponding virtual page number. For such special case, the table lookup can then be reduced to an simple parallel adder hardware to reduce power consumption [13, 14]. In general-purpose processor with cache, physical address translation is necessary for every memory access as virtual addressing could possible result in cache aliasing problem when same virtual address in different applications are mapped to different physical location, and cache synonym problem when different virtual addresses are mapped to the same physical address (caused by data sharing). Extending virtual address with process ID could resolve the former, we investigated the technique that embeds application sharing information in instructions and only translate physical address only for possible shared data with the help of hardware differentiating cache accesses [15, 16]. A special structured page table that compresses multiple translation entries of the same consecutive mapped segment into one wider entry was investigated for embedded systems where memory remapping are very rare cases [17].

To respond to frequently-triggered asynchronous events, preemption based multitasking systems are adopted in many real-time embedded systems. Each switch involves large number of memory accesses, as operating system will first save the context of current task (preempted task) and load the context of next highest-priority ready task (preempted task). The high frequency of context switches not only affect the throughput of system effective instruction, but also increase each task's response time. By analyzing the live register utilization through CFG(Control Flow Graph)'s paths and enabling switches at the point with minimal live sets, we effectively reduce necessary live context size. Deferring switches to nearest minimal point by customized hardware and preserving the minimal live set by customized OS callback functions enhance promptness of preemption, and increase the effective instruction throughput as useful application instruction are still being executed during deferral [18, 19]. To further reduce memory accesses of preserving contexts, a small pool of spare register pages are introduced to immediately remap live context [20]. The page level remapping is done through simple hardware structure, while the live registers are packed into small regular pages after the compiler's register allocation phase.

Temperature hot-spots have been known to cause severe reliability problems

and to significantly increase leakage power. Due to frequent access and relatively small area, the register file has been previously shown to exhibit the highest temperature in many modern high-end embedded processor, which makes it particularly susceptible to faults and elevated leakage power. We show that this is mostly due to the highly clustered register file accesses where a set of few registers physically placed close to each other are accessed with very high frequency. A compiler-based register assignment methodology, which purpose is to break such groups of registers and to uniformly distribute the accesses to the register file is investigated [22].

#### Chapter 2

## Related Work

## 2.1 Low Power Design Techniques

The overall chip power consumption as the sum of dynamic and static power can be expressed by the Equation 2.1 [23]:

$$\mathbf{P} = A \cdot C \cdot V^2 \cdot f + V \cdot I_{leak} \tag{2.1}$$

The first term is the dynamic power lost from charging and discharging the processors capacitive loads: A is the fraction of gates actively switching and C is the total capacitance load of all gates. The second term models the static power lost due to leakage current,  $I_{leak}$ . The power lost to the momentary short circuit at a gates output is ignored here since the loss is relatively small; it contributes to dynamic power loss, and the equations first term can absorb it, if necessary.

When dynamic power is the dominate the leakage power as it has been and as it remains today in many less aggressive fabrication technologies, Equation 2.1 can be approximated by the first term. Reducing the supply voltage with the factor of  $V_2$  is the most effective way to decrease power consumption. Scaling down the clock frequency, using low power transistors, and reducing switching activity will reduce f, C and V respectively so that the dynamic power can be reduced proportionally.

Leakage current, the source of static power consumption, is a combination of

sub-threshold and gate-oxide leakage:  $I_{leak} = I_{sub} + I_{ox}$ , where sub-threshold current and gate-oxide current can be expressed by Equation 2.2 and Equation 2.3:

$$I_{sub} = K_1 \cdot W \cdot e^{-V_{th}/nV_{\theta}} \cdot (1 - e^{-V/V_{\theta}})$$

(2.2)

where  $K_1$  and n are experimentally derived, W is the gate width, and  $V_{\theta}$  in the exponents is the thermal voltage. At room temperature,  $V_{\theta}$  is about 25 mV; it increases linearly as temperature increases. If  $I_{sub}$  grows enough to build up heat,  $V_{\theta}$  will also start to rise, further increasing  $I_{sub}$  and possibly causing thermal runaway. Turning off the supply voltage could sets V to zero so that the factor in parentheses also becomes zero. Increasing the threshold voltage can have a dramatic effect of reducing the sub-threshold current in even small increments.

$$I_{ox} = K_2 \cdot W \cdot (V/T_{ox})^2 \cdot e^{-\alpha T_{ox}/N}$$

(2.3)

where  $K_2$  and  $\alpha$  are experimentally derived.  $T_{ox}$  is oxide thickness. The research and development of community high-k dielectric gate insulators is to reduce this leakage current.

The direct method to reduce the power consumption is to target parameters at circuit level. In DVFS(Dynamic Voltage and Frequency Scaling) design, the supply voltage and the clock frequency are reduced to at minimum level when there is no critical task running. Various DVFS techniques have been both proposed in academia[24, 25] and developed in industry [26, 27]. Find appropriate transistor size [28] or redesign complex gate[29] will change the load capacity or reduce the

total number of transistor count, thus reduce the power consumption. Clock gating technique which pauses the clock input to the synchronous transistors when the function units and register files in the system are not active in the near future could significant reduce the power consumption [30].

Architecture level power reduction focus on larger granularity of power management. The power overheads of each part are analytical profiled to accurately estimated the power distribution in the system. Various power analysis and estimation techniques has been discuss in [31, 32]. The next step is to either replace that unit with alternative low power architecture design [33], [34]. Low power cache architectures have been proposed in [35], [36] as well.

Interconnect power reduction techniques focus on the reducing redundant power consumption in inter module communication activities in the SOC. Code compression techniques which compress the code before transit to bus and decompress after received from bus could significant reduce interconnect activity although there is some compression power overhead[37]. Bus encoding techniques in which the context of the data and frequency of each data is analyzed, the data transmitted on the bus is encoded to a power efficiently format and decoded at the other end of bus. Thus per activity cost is saved[38].

The software level or system-level power management techniques focusing the efficiency of utilizing the hardware components. For example, the compiler could analyzed the memory ambiguity and save the memory load/store activity[39]. The power-aware scheduling approach in [40] combined the DVS technique and OS scheduling algorithm to reduce the overall run-time power consumption. In [41],

the author applied the application memory access information to the compiler and the cache architecture to reduce the total cache access energy.

## 2.2 Memory Management

The memory subsystem has been known to be one of the major bottlenecks in terms of power and performance not only for general-purpose computing systems but also, and even more so, for the typically resource constrained embedded systems [42, 43].

Virtual memory [44, 45] has been well known as an elegant approach to abstract from the application the complexity of memory allocation, and code/data relocation and sharing, while efficiently providing memory protection between user applications and system software; all these being completely transparent to the application and controlled by the operating system (OS). Such features would tremendously benefit many embedded systems, if virtual memory is to be supported for them. In recent years many high-end embedded processors have started to employ a Memory Management Unit (MMU), such as Intel XScale [46], ARM720 [47], and ARM9 [48]. The MMU is a hardware structure responsible for translating addresses generated by the processor to physical memory addresses. General-purpose virtual memory, however, requires unacceptably high amounts of power and introduces execution time nondeterminism, thus rendering itself unusable for a large number of embedded applications with stringent power constraints and real-time requirements.

When virtual memory support is present, the program accesses a virtual ad-

dress space partitioned into pages, which are referred to as virtual pages and are identified by their Virtual Page Number (VPN) which constitutes a large fraction of the virtual address most significant bits. During each memory access a translation is needed to map the virtual address into a physical one. The translation is performed at a page granularity in order to control the complexity of the translating mechanism. The Translation Lookaside Buffer (TLB) is a hardware cache responsible for capturing the most recently used Page Table Entries (PTE) for dynamic virtual address translation with no intervention of the system software. The mapping between virtual and physical addresses is typically maintained by the OS and established by the OS loader, dynamic linker and memory manager. TLB misses typically result in trapping into the OS where the missing PTE is retrieved from the page table maintained by the kernel. As this process is complex and time consuming, the TLB is usually implemented as a highly associative cache structure so that misses are minimized, which, in turn, results in significant amount of power consumption. In [49] it has been demonstrated that the TLB power constitutes 20%-25% of the total cache power consumption, which in turn has been shown to comprise in some cases around 50% of the total chip power [50]. It has been shown through direct measurements [51, 52] that around 17% of the total on-chip power for the StrongARM and the Hitachi SH-3 is contributed by the TLB.

The need for energy costly address translation on each memory reference, as well as the introduced execution time uncertainty caused by the cache-like TLB lookups, have been the two major factors preventing the introduction of virtual memory and its benefits to low-power and real-time processors.

The importance of the TLB in terms of performance and power has been recognized in the microarchitecture industry and research communities. Consequently, techniques for minimizing the power and performance overhead of TLBs have constituted the focus of a number of research activities in the recent years. A low-power TLB organization for chip-multiprocessors has been proposed in [49]. By incorporating a special Page Sharing Table to the TLB and using virtual caches, the authors reduce the amount of TLB activities, at the same time eliminating a large number of snoop accesses. A similar work in the direction of employing virtual caches with specialized TLB support is presented in [53]. The authors propose replacing the TLB with the more scalable and power efficient Synonym Lookaside Buffer, as it stores only the current synonym instances. In [51], the authors evaluate the power consumption of a number of TLB organizations and propose a new cell implementation for low-power set-associative TLBs. A low-power and high-performance TLB architecture has been proposed in [54]. The result of each TLB lookup is latched and prior to accessing the TLB the previously latched address translation is first lookedup, thus eliminating the TLB access if that same virtual page has been accessed in the previous memory reference. The concept of synonymous translations has been introduced in [55]. Superscalar processors can execute multiple memory references per cycle, out of which many refer to identical virtual pages; such synonymous TLB accesses within a cycle and across cycles are identified and the TLB lookups are compacted to the minimum needed. In [56] the TLB and cache accesses are partitioned according to their semantic such as static, global, stack, and heap data. The unique behavior and locality of each reference partition is exploited and each stream redirected to its micro-TLB. A recent approach [57] proposes reconfigurable decoder structures for generating cache indices for direct-mapped cache structures. Cache line utilization is balanced and large number of conflicts eliminated thus approximating the functionality of highly associative caches yet at much lower power consumption. Another recently proposed approach for minimizing cache indexing conflicts was described in [58]. The cache index in this approach is computed by selecting a certain number of bit positions from the address. Which bits positions to select is determined during compile-time and a special hardware structure is configured prior to executing the program so that the cache index is formed by selecting the identified bit cluster. A TLB organization is proposed [59] that dynamically supports up to two pages per entry with a banked fully-associative structure. Such an organization benefits applications where larger pages can be used to minimize the translation overhead. In [60], the TLB accesses are redirected to a register file which holds a few recent TLB entries. Due to the small size of the register file compared to the VPN footprint, the compiler needs to reconstruct the code in order to minimize the overhead of replacing register entries at run time. Aspects of virtual memory have been modeled in software through a compiler inserted code in the application. Such an approach, where memory protection is implemented by the compiler is proposed in [61].

When virtual memory and caches coexist, techniques for power reduction and performance improvements for caches and TLBs together needed to considering the overall optimization. Cache conscious memory layouts have been explored for both code [62, 63] and data [64, 65]. In [66], the authors have proposed the *U-cache* archi-

tecture which maintains a reverse translation information of the cache blocks that belong to unaligned virtual pages only in order to handle the synonyms efficiently. A low-power physically-tagged cache has been proposed in [67]. A minimal set of tag bits is dynamically identified per hot-spot and used to access the cache instead of complete tags. In [52] the authors have proposed an instruction address translation architecture, which places the most recent I-TLB translation in a register, which is subsequently being reused until the instruction memory page is changed. For periods of time when instructions are fetched from the same memory page, the translation register is used to obtain the physical address instead of the I-TLB thus achieving faster and less power consuming instruction address translation. Compiler techniques have been presented in [68], which maximize the reuse of the softwarecontrolled translation registers. Methodologies which emulate the address translation process in software have been recently proposed in [69]. In these approaches the compiler introduces code for run-time checks in order to enable applications to share physical memory for their stacks and to prevent any out-of-boundary memory accesses.

## 2.3 Multitasking Management

Many modern embedded applications, such as personal organizers, cell phones, and various hand-held devices, constitute complex computing systems where multiple execution tasks cooperate in implementing the product specification. Due to market demands, a large number of capabilities need to be supported, such as

aggregated multimedia data processing (speech, audio, video), communication protocols (GSM/CDMA, VoIP, Bluetooth, CAN), security functions, user interfaces, and many others. The utilization of embedded processors for real-time and time-critical control applications have been growing rapidly. The modern automotive industry, for instance, has adopted the approach where tens to hundreds of such processors are used throughout a single automobile [70]. They are used for traction control, anti-lock brake systems, engine control, and many other control and time-critical tasks. Many real-time data acquisition and processing systems such as sensor nodes and networks, impose strict real-time constraints and response time in order to capture, process, and identify rapidly appearing objects and physical phenomena. At the same time, all this processing power needs to be achieved with extremely energy-efficient and low-cost embedded processors.

The inherent multi-tasking nature of these applications has led to implementations where multiple software tasks are mapped for execution on a high-performance embedded processor such as the Intel XScale [46] and the ARM9 [48], which offer multi-tasking support in the form of *MMUs* and *hardware timers*, and readily available operating systems (OS) which utilize this hardware to implement various forms of multi-tasking.

The two widely adopted schemes for task switch control are the *cooperative* and the *preemptive* multi-tasking. In cooperative multi-tasking, the task voluntarily releases the control of the CPU to the OS at certain points of its execution. This release typically occurs when the task finishes execution or when the task computation load is low and is waiting for a lengthy I/O operation. Such an approach is

followed in TinyOS [71] where tasks are executed in a manner of run-to-completion. In this approach, longer tasks need to be partitioned into shorter ones. As pointed out in [72], such run-to-completion scheme can cause problems with meeting real-time constraints, as it is not possible to partition many tasks, which can result into a situation where a single task occupies the CPU for a long time. The cooperative multitasking paradigm is further explored in [73], where the authors have proposed to integrate multiple threads into a single thread statically during compile time. The benefits of cooperative multitasking for networking applications have been analyzed in [74]. Even though these approaches have the advantage of avoiding nondeterministic context switch overheads, an extra limitation on the dynamic behavior is created as they require that all preemption points are known during compile time. The degraded responsiveness to asynchronous events has been the major disadvantage of cooperating multitasking.

In preemptive multi-tasking the OS can pause a low-priority task and assign the CPU to a higher priority task - an OS controlled event referred to as preemption. Preemptive multi-tasking relies on a timer to generate interrupts at regular time intervals. When such an interrupt occurs, the execution control is transferred to a kernel routine that determines whether a task switch needs to be performed and, subsequently, to perform the context-switch. As this approach has the distinctive advantage of better responsiveness and stability, most of real-time scheduling algorithms and OS multitasking support are based on it [75, 76]. However, the frequent preemptions interrupt the normal task execution and bring extra performance and power overheads in the form of cycles needed to preserve and then restore the task

context. The task context includes the entire register file and all the status registers such as the Program Counter (PC) and the Stack Pointer (SP); its size is by far dominated by the register file. As task preemption exhibits asynchronous behavior, the OS kernel must be conservative and preserve/restore the entire state.

Due to cost and power constraints the majority of modern embedded processors follow the RISC and VLIW paradigms. In these architectures, and even more so in VLIW, the register file is traditionally very large in order to enable aggressive compiler optimizations targeting instruction parallelism and execution throughput. A typical modern VLIW architecture [77] features a general-purpose register file of size from 64 to 256. It has been shown [78] that for some short tasks responsible to react and process data samples in sensor networks, the context switch overhead can be up to 30% of the total execution cycle.

Instead of having a distinct physical register file for each task, another hardware solution is to have a relatively small ISA-visible set of registers, while implementing a significantly larger physical register file. This organization is illustrated in Figure 4.2. At run-time, each virtual register is renamed to a free physical register. This approach is very popular in superscalar processors, such as Intel Pentium 4 [79] and Alpha 21264 [80]. Such hardware register renaming is mostly used to exploit the available ILP in the program. Context switches are fast as typically only a small part of the physical register file needs to be preserved in memory. However, due to its per-register granularity and the fact that the renaming hardware needs to be activated at every cycle, the approach suffers from excessive power consumption and as such is not applicable to embedded systems. With a similar objective, in [81]

the physical register file is implemented as a cache that captures a large number of virtual registers. Fast access to subroutine and multithread contexts is achieved with a non-trivial power overhead.

The notion of fast context switch point has been first introduced in [82]. Each instruction is marked with a special bit to indicate whether a fast context switch is possible at that point. A fast context switch point is defined as an instruction where all scratch registers are dead. Scratch registers are a subset of all the registers which are caller-saved across function call boundaries; the context switch mechanism saves and restores all the remaining non-scratch registers. Consequently, this is a "all-ornothing" approach targeting old architectures with rather small register files and no register windowing. VxWorks [6], on the other hand, provides a special hardware context for interrupt service code in order to avoid preserving the task context, and thus improving responsiveness to various system generated events. In [83], the authors have proposed a Simultaneous Multi-Threading platform with mini-thread execution. This approach, however, introduces a non-trivial hardware overhead. In [84], the authors have proposed to reduce the task context in the static OS by finding the live set of each task and merge the set by using the preemption priority information. The authors in [74] utilize and explore cooperative multi-threading instead of asynchronous preemption. Other research has shown that for some applications with known set of tasks and well known run-time characteristics and interactions, an efficient cooperative multitasking system can be synthesized through software thread integration [85, 86]. In a more dynamic system, however, with preemptive multitasking, the active task may have to be suspended at arbitrary point so that another task is placed for execution. Even though the task switch overhead is reduced, the system responsiveness is limited as the compiler must statically decide on the way tasks are interleaved.

### Chapter 3

### Cross-Layer Customization for Memory Management

Virtual memory [44, 45] has been well known as an elegant approach to abstract from the application the complexity of memory allocation, and code/data relocation and sharing, while efficiently providing memory protection between user applications and system software; all these being completely transparent to the application and controlled by the operating system (OS). Such features would tremendously benefit many embedded systems, if virtual memory is to be supported for them. In recent years many high-end embedded processors have started to employ a Memory Management Unit (MMU), such as Intel XScale [46], ARM720 [47], and ARM9 [48]. The MMU is a hardware structure responsible for translating addresses generated by the processor to physical memory addresses. General-purpose virtual memory, however, requires unacceptably high amounts of power and introduces execution time nondeterminism, thus rendering itself unusable for a large number of embedded applications with stringent power constraints and real-time requirements.

#### 3.1 Direct Address Translation

#### 3.1.1 Introduction

In general-purpose architecture designs, the assumption is that a large variety of programs are to be executed and that there is no program information

made available to the microarchitecture prior of its execution. It is also assumed that the program to be executed could come in a binary only form. Embedded processors and systems, however, have the distinctive advantage of complete application knowledge, as the embedded software is usually developed concurrently with the hardware design or is available in a source code format. The energy-efficient and time-deterministic address translation schemes outlined in this section are techniques that with the help of the compiler and the operating systems exploit dynamically such application-specific knowledge.

Through the utilization of application-specific information regarding the virtual memory footprint of the application, the set of VPNs accessed by the program is partitioned into groups so that by using only a small number of least significant VPN bits as an index into a special hardware translation table, a conflict-free, and thus tag-less lookup can be achieved. This not only results in very low-power address translation, but also to highly predictable execution times as the conflict free Direct Translation Table (DTT) access guarantees fast and time-deterministic address translation with no intervention of the OS for the majority of load/store instructions. This property is of great importance for real-time applications, where a worst-case execution time analysis of the program code is performed in order to guarantee the completion of certain computation within the pre-specified time deadlines.

The proposed methodology relies on the combined efforts of compiler, operating system, and hardware architecture to achieve both significant power reduction and deterministic address-translation times. It has been shown that any application program spends most of its execution times in a few relatively small parts of its code,

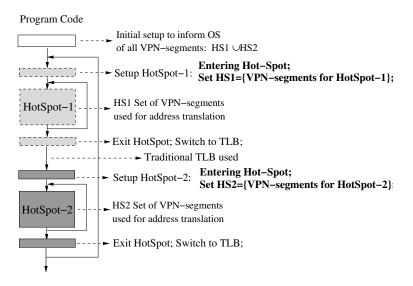

typically corresponding to loops or functions. Such parts of the code are usually referred to as phases of hot-spots [87, 88]. By targeting the application hotspots, practically all the benefits from the proposed technique can be achieved with only a low-cost hardware support needed to capture the information regarding the memory utilization. Consequently, the proposed techniques are applied on the application hot-spots, while for the rest of the infrequently executed part of the applications, the generic address translation mechanism is used. Upon entering or exiting a hot-spot, the compiler inserts a special setup code which stores certain information into special registers and tables implemented as a part of the specialized hardware support and, thus, informs the hardware that a hot-spot has just been entered.

The utilization of TLB for address translation is analogous to the cache utilization in embedded processor, where the tag operations introduce significant power consumption and non-deterministic access time due to possibility of conflicts. In many real-time systems, embedded processors with scratch-pad memory are rather used. Scratch-pad memories are SRAM memories mapped into the physical address space of the processor. Compared to caches scratch-pad memories provide for deterministic performance and energy efficiency. Various software controlled schemes for scratch-pad memory have been proposed and proved effective for data caching functionality [89, 90, 91, 92, 93], providing for fast and low-power data access. The large or difficult to allocate in scratch-pad data arrays can still utilize the services of hardware data cache. The mechanism replaces the majority of TLB cache-like accesses with software-managed direct-indexed SRAM table, thus offering energy-efficient TLB functionality with deterministic translation times. By effectively utilizing ap-

DataDataSoftwareAccessCacheMemoryAddressTLBProposedTransl.DTT

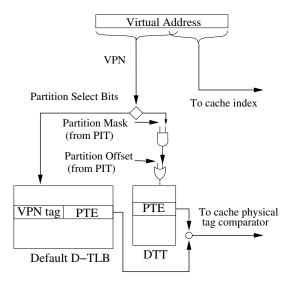

Figure 3.1: TLB-based hardware address translation

Figure 3.2: DTT: Software-controlled address translation

plication information regarding the virtual pages used in the address translation process, a direct table with no tag arrays is used to avoid the energy overheads and nondeterministic times caused by conflicts in the TLB. In contrast with the other approaches, the technique that we propose does not trade-off performance for power. On the contrary, the proposes technique as it eliminated accessed to the TLB for most of the VPN accesses, it drastically reduces the number of TLB misses and thus slightly improves performance and significantly improves the execution time predictability - a characteristic of great importance to any real-time embedded system.

## 3.1.2 Tagless Direct Address Translation

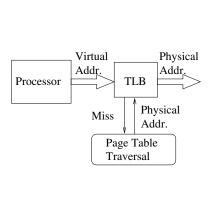

The role of the TLB is to cache the most frequently requested virtual to physical address translation. After a virtual address is generated by the processor, the

TLB is looked up in order to determine the physical address as shown in Figure 3.1. In the case of a TLB miss, a page table traversal procedure is activated in order to find the correct translation. The page table traversal can be implemented in either hardware or software. The TLB is a cache-like structure, which captures the most frequently requested page table entries. Because of its cache-like organization and possibility of conflicts, the TLB contains tag arrays which are read and compared against the accessed VPN to determine whether the TLB look-up is a hit or a miss. The possibility of conflicts and the existence of the tag arrays and tag operations are the reasons for the excessive power consumption and the difficulty in estimating prior to program execution whether a TLB access will hit or miss [94, 95]. Clearly, this situation is very similar to data caches and their high power consumption and difficulty in statically analyzing their behavior. To resolve these issues of data caches, scratchpad memories have been used when deterministic execution times are needed together with low-power requirements. The proposed DTT-based address translation scheme is somewhat analogous to scratchpad memories for data caching as illustrated in Figure 3.2. The DTT is software-controlled and the translation entries are allocated into it in a way, which enables direct indexing, hence provide for energy-efficient and time-deterministic address translation.

The set of virtual pages allocated to the application code and static data is available after compiling and linking the program. The starting virtual address of the stack data is available as well; if memory is dynamically allocated, the particular VPNs are determined and known to the OS memory manager. The proposed address translation scheme exploits this information available to the compiler/linker and to

Figure 3.3: Set of consecu

tive VPNs

table with LSBs

the operating system in order to judiciously allocate the translation entries into the DTT. The DTT is subsequently accessed in a manner similar to a scratchpad memory.

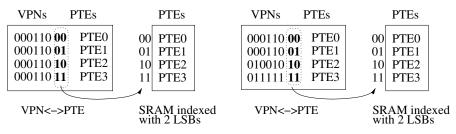

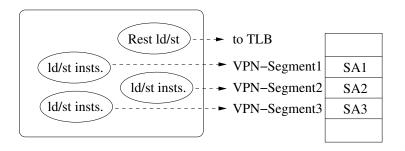

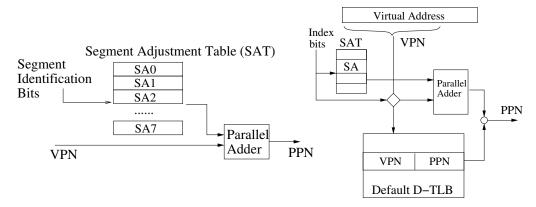

If the possibility of TLB conflicts can be avoided through a judicious analysis of the VPN set, then a direct indexing for finding the PPN, free of any tag operations, can be achieved. Figure 3.21 shows an example where the compiler/linker has identified that only four consecutive data virtual pages can be accessed throughout the subsequent program execution. It can easily be seen that among all the VPN bits, the two Least Significant Bits (LSBs) are enough to differentiate the four VPNs. Consequently, these two LSBs can be used as an index into a translation table, where the VPNs will be mapped into the table in a conflict-free manner. It is evident that for any set of n consecutive VPNs, the  $\lceil \log_2 n \rceil$  LSBs can be used as an unique identifier for any of the VPNs and as such they can be used as index to a table that stores information for any of the VPNs. A slightly more complex example is illustrated in Figure 3.22, in which four distinctive and not consecutive virtual pages are accessed. Although they are not consecutive, their two LSBs are still enough to uniquely distinguish them. Consequently, only these two bits of the

Figure 3.5: Two VPN partitions, each indexed by 2 LSBs

VPN can be used to form an index into a 4-entry memory block which holds the physical page addresses of these virtual pages, as shown in the figure. By avoiding the VPN tag look-up and using only these two bits as an index there would be no performance implications, while the overall reduction on the TLB power consumption is to be quite significant. All the power associated to the VPN tag arrays, the corresponding sense amplifiers, and the comparator cells is eliminated.

In the above examples not only is the power reduced but also the address translation timing for these VPNs becomes completely deterministic as by allocating the translation information for each VPN at the appropriate location in the table it can be guaranteed that the translation for these VPN will always complete within a cycle. This timing determinism is extremely important for real-time application where worst-case performance analysis need to be performed in order to guarantee that a certain processing is completed within a pre-specified time deadline.

The fundamental idea of the proposed approach is to identify such a conflictfree indexing scheme and to ensure a conflict-free allocation of the translation information in order to avoid the power consuming VPN tag operations and to provide for fast and deterministic address translation times. Given a set of n data VPNs, there exists the minimal number m of VPN LSBs that could differentiate these VPNs and thus be used as an index. Even more importantly, how efficiently will the introduced translation table be utilized after storing the translation entries of each VPN in such a  $2^m$  sized memory. The above examples show ideal situations where a minimal number of index bits are used and since the number of VPNs is a power of two, the entire index space is utilized. However, in many cases if no additional measures are taken then the utilization of the translation table could be quite low, or at worst it may even be impossible to capture all the translation entries because of the table limited size. Such an example is depicted in Figure 3.5. For these eight VPNs, seven LSBs are needed to differentiate them and use them as an index. Therefore, if the outlined above translation technique is to be used in the same manner, this set of VPNs would occupy a memory array with  $2^7$  entries, while only eight of them will actually be used.

The example outlined in Figure 3.5 therefor shows that a low memory utilization is possible with a large waste of memory and its associated power, if the set of VPNs accessed by the application is targeted as a whole. However, it can be seen that VPNs 0, 1, 4, 5 can be differentiated by two bits, while the VPNs 2, 3, 6, 7 can be differentiated by two bits as well. Consequently, if the initial set of eight VPNs is divided into two partitions, 0, 1, 4, 5 and 2, 3, 6, 7, then the two LSBs can still be used to form an index into two non-overlapping segments within a translation table as long as information regarding which partition is being used is known prior to access the table. Additionally, the two partitions need to be allocated into two

different four-entry sections of the translation table, so that VPNs across different partitions are guaranteed not to overlap. It can be observed that an alternative partitioning of the VPNs exists as well, which consists of two VPN partitions: 0, 1, 6, 7, and 2, 3, 4, 5. This alternative partitioning has the same cost as the aforementioned partition since both pair of partitions require two LSBs for VPN differentiation.

An important constraint for such a partitioning scheme to work properly is that if a load/store instruction can potentially access across multiple VPNs, all these VPNs must be allocated into the same partition. This constraint is needed since because of hardware cost considerations a VPN partition would be identified on a per load/store instruction basis, i.e. a load/store instruction would be mapped to one and only one VPN partition. This restriction guarantees that there is no ambiguity when accessing the DTT. As is shown later in the section, the algorithm forming the partitions is based on this constraint and efficiently finds large partitions with very high index space utilization. Any load/store instruction that cannot be ascertained to access VPNs from the same partition will be handled by a "default" traditional TLB.

The introduced approach involves the identification of partitions of VPNs which result in optimal indexing scheme maximizing the utilization inside each partition while reducing the overall number of partitions. Minimizing the number of partitions, while maintaining high utilization of the translation table is important to control the cost of hardware needed to identify partitions and to compute their translation table index.

After identifying the partitions, each partition is mapped to its own segment

Figure 3.6: Mapping VPN partitions to DTT segments

in the introduced *Direct Translation Table (DTT)*, as illustrated in Figure 3.6. In a manner analogous to scratchpad memories, the DTT is implemented as a small SRAM array, containing the translation entries for all VPNs, which have been determined to be part of VPN partitions. As each partition of VPNs is mapped to a distinct part of the DTT, a special indexing logic is need to form the final index. If the partitions is aligned inside the DTT on address boundaries proportional to their size, a very simple logic is needed to compute the DTT index; the DTT segment offset needs to be simply concatenated to the few VPN LSBs selected as a partition index.

# 3.1.3 Compiler and OS Support for DTT Management

The role of the compiler support is to determine an efficient VPN partitioning, which maximizes the DTT utilization, and to associate the load/store instructions to VPN partitions as explained in the previous section. The OS support required by

the proposed technique does not go beyond the traditional virtual memory support in terms of maintaining a page table that contains all the address translation entries for the application program. A small additional OS support is required to handle the context switch between tasks, which utilize the DTT. This support is outlined in subsection 3.1.3.3 the multitasking support for DTT management is discussed.