**ABSTRACT**

Title: 3D INTEGRATION, TEMPERATURE

EFFECTS, AND MODELING

Latise Anitrá Parker, Master of Science, 2005

Directed By: Professor Neil Goldsman, Department of

Electrical and Computer Engineering

Practical limits to device scaling are threatening the growth of integrated circuit (IC) technology. A breakthrough architecture is needed in order to realize the increased device density and circuit functionality that future high performance ICs demand. 3D integration is being considered as this breakthrough architecture. In this thesis, the limits to scaling are noted and the feasibility of overcoming these limits using 3D integration is presented. The challenges and considerations, most notably dangerously high chip temperatures, are provided. To address the temperature concern, a mixed-mode simulator that calculates temperature as a function of position on chip is detailed. The simulator captures the important link between individual device and full chip heating. Lastly, circuit simulations and lab experiments are performed to experimentally validate the claims that differences in device activity on chip leads to dangerously high local and overall chip temperatures.

## 3D INTEGRATION, TEMPERATURE EFFECTS, AND MODELING

By

## Latise Anitrá Parker

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science 2005

Advisory Committee: Professor Neil Goldsman, Chair Professor Martin Peckerar Professor Bruce Jacob © Copyright by Latise Anitrá Parker 2005

# Dedication

This work is dedicated to my mother, Sharon. Mom, you have always been there to support me academically and you have always encouraged me to stay tough and work through the rough times. Your support has brought me to this point.

# Acknowledgements

Two years of work can be contributed to one person—God. So first, I want to think Him for making me who I am and for bringing me to this point. Without His ever-present love, strength, and guidance, I would be nothing.

I want to thank my advisor, Dr. Neil Goldsman, for giving me the opportunity to perform my graduate study as a member of his research group. As a senior in undergraduate school, I had no idea what type of research I wanted to conduct. I only knew what I didn't want to do. But he took the time to show me the projects his group was working on and he welcomed me into his group. During stressful times, he was available to talk and offer support. I just want to say thank you for giving me the opportunity to be a part of your team.

To everyone in the lab, I extend my thanks for being the main source of help and support on a day to day basis. You helped with courses and with research. We all worked together to make this thesis possible. Akin, you are who I collaborated with the most. You were always patient and willing to discuss anything. You answered questions, sometimes the same one more then once, and you never seemed frustrated or too busy.

My thanks also go to Professor Tits, my undergraduate advisor, and everyone I worked with in the M.E.R.I.T. program. Each of you contributed to my decision to pursue a graduate degree in the first place. Your faith in my abilities encouraged me to believe that I could handle the combined BS/MS program.

I want to say thanks to my good friend Steve for being my study buddy in undergrad and my first 2 semesters of graduate courses. Theresa, after going from

kindergarten all the way through graduate school with you, I can honestly say that I am ever thankful for our friendship (and this crazy twist of fate that has pitted us together for so long). We have been classmates, roommates, and friends during all those years and your intelligence, thoughtfulness and insight has helped me in more ways then you will ever know. To all of my friends in the bowling center, thank you for your support and thank you for listening when I complained about homework, exams, and my 100-page thesis. There is only so much a person can take, and each of you tolerated more. Now we can have peaceful dinners at Bennigan's.

To the love of my life, Jeffrey, I want to say thank you for teaching me about balance. You showed me the importance of taking time to work and time to play. Without that lesson, I'm sure I would have gone crazy long before I reached this point. More then that, you probably heard the most about my ups and downs in graduate school and life in general. Through it all, you remained by my side. I love you for that—and so much more.

Finally, Mom, Gerryle, Brianna, Gerryle Jr., Angie, Grandma and Grandaddy: thank you for being a supportive family. You have each contributed to this work in your own way, perhaps with words of encouragement or by providing me with an outlet to balance school life with personal life.

To anyone I missed, you know you are important to me and you know there is a page in this thesis that I could not have wrote without you. My journey to this point has been helped along by a huge cast of characters, the names of which I cannot possibly mention without this acknowledgements section being as long as my thesis (it probably already is). God Bless you all.

# Table of Contents

| Dedication                                     | ii    |

|------------------------------------------------|-------|

| Acknowledgements                               | . iii |

| Table of Contents                              | v     |

| List of Tables                                 | vii   |

| List of Figures                                | viii  |

| Chapter 1: Introduction and Motivation         | 1     |

| Device Scaling Limitations                     | 2     |

| Interconnect Limitations                       | 3     |

| Thermal Limitations                            | 4     |

| Thesis Overview                                |       |

| Chapter 2: Integration in Three Dimensions     | 7     |

| Design Structure and Requirements              |       |

| Fabrication Using Silicon-on-insulator (SOI)   |       |

| Processed Wafer Bonding                        | 15    |

| Silicon Epitaxial Growth                       | 18    |

| Fabrication Using Polysilicon on Insulator     | 20    |

| Beam Recrystallization                         | 22    |

| Solid Phase Crystallization                    | 24    |

| Vertical Interconnects                         | 29    |

| Challenges and Considerations                  | 31    |

| Summary                                        | 33    |

| Chapter 3: 3D Full-Chip Temperature Simulation | 35    |

| 3D Heat Flow Model                             | 36    |

| 3D Thermal Network                             | 41    |

| Reduced 3D Thermal Network                     | 45    |

| Thermal Resistance in 3D Thermal Network       | 53    |

| Materials                                      | 54    |

| Architecture and Dimensions                    | 55    |

| Chip Packaging                                 | 57    |

| Full Chip Temperature Calculation              | 59    |

| 3D Chip Configuration and Activity Profile     | 61    |

| Device Performance Model                       |       |

| Thermal Network Solver                         |       |

| Complete Simulation Algorithm                  |       |

| Results and Analysis                           |       |

| 5-Layer Stacked Pentium III                    |       |

| Minimum and Maximum Temperature                |       |

| Alternate Chip Layout                          |       |

| Chapter 4: Temperature Experiments             | 80    |

| Effect of Temperature on Frequency             |       |

| Frequency versus Temperature Simulation        |       |

| Frequency Variations on Same Laver             | 83    |

| Frequency Variation on Different Layers                        | 84  |

|----------------------------------------------------------------|-----|

| Measuring Local Chip Temperature                               | 86  |

| Design of Temperature Sensor                                   | 86  |

| Design of Temperature Sensor Array                             | 88  |

| Fabrication of Chip #1: Temperature Sensing Chip               | 91  |

| Functionality Test                                             | 92  |

| Temperature Sensitivity Test                                   | 94  |

| Local Chip Heating and Temperature Measurement                 | 95  |

| Selective Heating Design                                       | 96  |

| Fabrication of Chip #2: Selective Heating and Measurement Chip |     |

| Functionality Tests                                            |     |

| Selective Heating and Temperature Measurement Test             | 100 |

| Further Heating and Measurement                                | 102 |

| Chapter 5: Conclusion                                          | 104 |

| References                                                     |     |

|                                                                |     |

# List of Tables

| Table 1: Thermal Conductivity at room temperature for materials used in 3-D chip                 |      |

|--------------------------------------------------------------------------------------------------|------|

| fabrication.                                                                                     | . 54 |

| Table 2: Material thicknesses for a 3D chip.                                                     | . 56 |

| Table 3: Thermal conductivity of common materials used to package integrated                     |      |

| circuits [38]                                                                                    | . 59 |

| Table 4: Activity profile of devices in various functional units.                                | . 64 |

| Table 5: Temperature for each unit on each layer of the 5-layer stacked 3D chip.                 |      |

| Devices within the unit operate at temperatures in the range [T- $\Delta$ T, T+ $\Delta$ T]. All | 11   |

| units are in Kelvins.                                                                            | . 74 |

# List of Figures

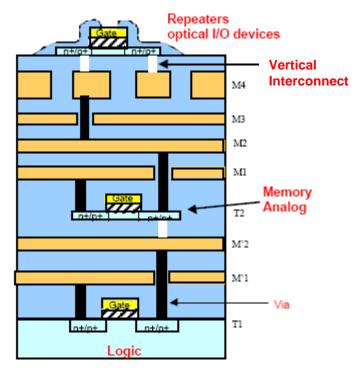

| Figure 1: 3D integrated circuit where each layer T is a block of devices. There are                         |

|-------------------------------------------------------------------------------------------------------------|

| separate metal layers for connections on the same layer and for different layers. 9                         |

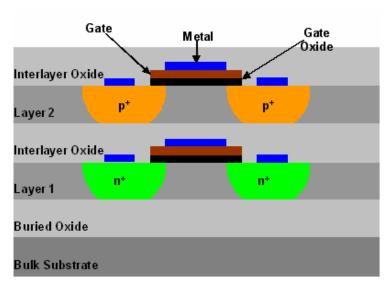

| Figure 2: 3D integrated circuit where each layer is a single type of devices                                |

| Figure 3: 3D systems-on-chip (SOC) consisting of logic, memory, analog, RF, and                             |

| optical components, each on a separate layer and integrated onto a single 3D                                |

| chip                                                                                                        |

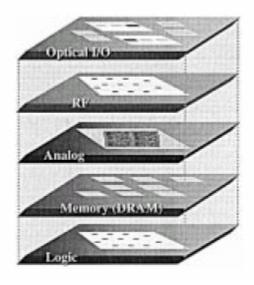

| Figure 4: CMOS transistors fabricated on (a) bulk silicon and (b) SOI                                       |

| Figure 5: Process steps for fabricating multiple layers of silicon using Silicon                            |

| Epitaxial Growth: (a) deposition, patterning, and insulation of islands, (b)                                |

| opening of seed window, (c) silicon growth and chemical mechanical polishing,                               |

| (d) deposition, patterning, and insulation of 2 <sup>nd</sup> layer islands, (e) opening of 2 <sup>nd</sup> |

| layer seed window, and (f) silicon growth and chemical mechanical polishing of                              |

| 2 <sup>nd</sup> layer islands                                                                               |

| Figure 6: Use of nickel or germanium seed to induce lateral crystallization to create a                     |

| single crystal region to comprise the channel of the device                                                 |

| Figure 7: Germanium seeded n-channel MOSFET with gate length of 100 nm: (a)                                 |

| transfer characteristics and (b) current output                                                             |

| Figure 8: Germanium seeded p-channel MOSFET with gate length of 100 nm: (a)                                 |

| transfer characteristics and (b) current output                                                             |

| Figure 9: Layout of a 3D inverter fabricated using MILC with nickel as the seeding                          |

| agent                                                                                                       |

| Figure 10: Inverter performance comparison for SOI, Large-grain Polysilicon SOI,                            |

| and conventional SOI inverters fabricated on the same wafer. The performance                                |

| of the 3D inverter fabricated using MILC is similar to the conventional SOI                                 |

| inverter29                                                                                                  |

| Figure 11: Representative 3D thermal network with each node representing a device:                          |

| (a) device nodes arranged uniformly and (b) a single device node with its 6                                 |

| thermal resistances, capacitive connection to ground, and heat source                                       |

| representing Joule heat generated by the device                                                             |

| Figure 12: 2D view of a group of device nodes grouped into a single subblock.                               |

| Additional lettered nodes are introduced half the resistance away from the                                  |

| boundary nodes. The 3D picture would show the 27 device nodes and additional                                |

| nodes E and F below and above, respectively                                                                 |

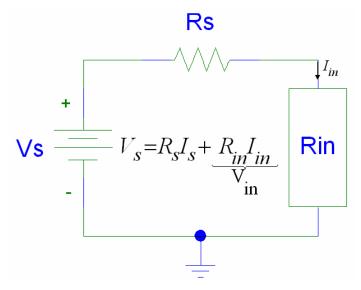

| Figure 13: The venin equivalent circuit with load resistance $R_{in}$                                       |

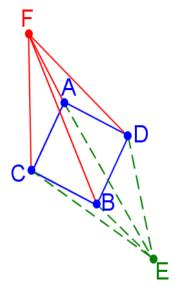

| Figure 14: Octahedron formed by the thermal connection of the 6 letter nodes.                               |

| Resistances are present between a given node and each of the other 5 nodes. For                             |

| clarity, the resistance between nodes AB, CD, and EF and the Joule heat source                              |

| that feeds each letter node is not shown                                                                    |

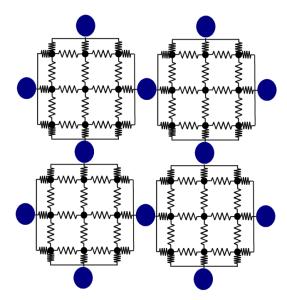

| Figure 15: 2D view of 108 devices grouped into 4 subblocks of 9 by 9 by 9. The 3D                           |

| view shows all 3 layers of device nodes and 4 additional nodes above and below                              |

| the subblocks51                                                                                             |

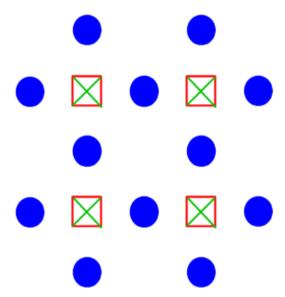

| Figure 16: Reduced network of octahedrons that represent 108 device nodes grouped                           |

| into 4 subblocks of 9 by 9 by 9. The blue nodes represent the 4 nodes in the                                |

| plane of the page. The red squares are the nodes in the –z direction and the green       |

|------------------------------------------------------------------------------------------|

| Xs are the nodes in the +z direction. Each octahedron has thermal resistances            |

| and Joule heat sources, not shown for clarity51                                          |

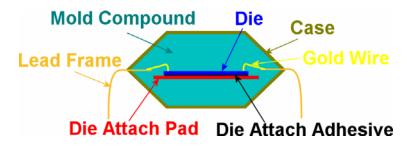

| Figure 17: Components of a basic packaging technology                                    |

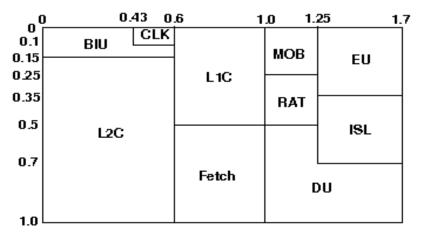

| Figure 18: Intel Flip Chip package (FCPGA2). The backside of the die is left exposed     |

| inside the processor package, which includes an integrated heat spreader. A heat         |

| sink is attached to the exposed die for better heat dissipation                          |

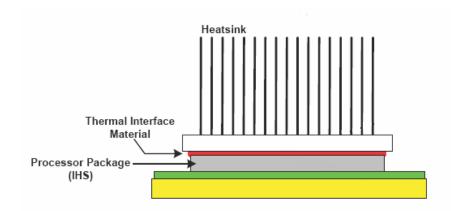

| Figure 19: Pentium III chip divided into functional blocks. The chip is stacked to       |

| form a 5-layer 3D chip for which local temperature is to be calculated                   |

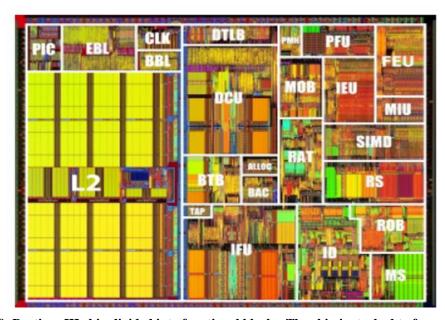

| Figure 20: Pentium III simplified functional units. Various units are combined           |

| according to application to reduce the number of units                                   |

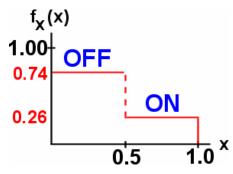

| Figure 21: Probability density function for a device in fetch unit. The device state (on |

|                                                                                          |

| or off) is represented by a number in [0, 1] and the probability of being in the         |

| state is given by the normalized power per unit area                                     |

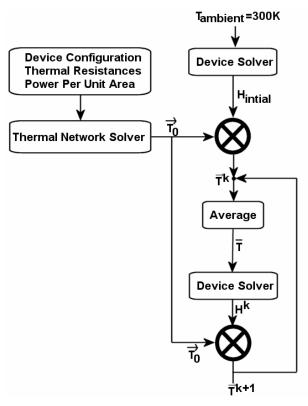

| Figure 22: Flowchart for complete temperature simulation algorithm                       |

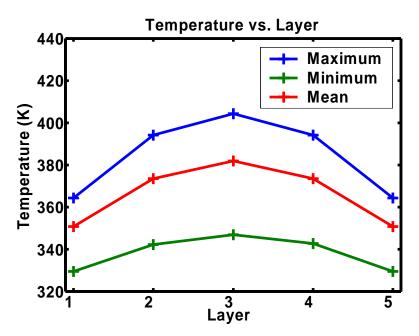

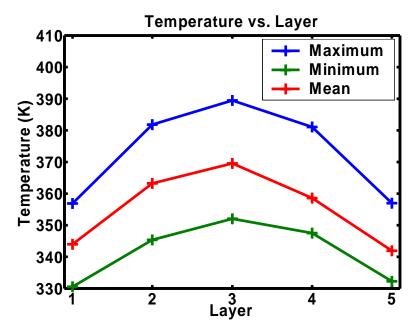

| Figure 23: Minimum, maximum, and mean layer temperature for 5-stack Pentium III          |

| 3D chip. The maximum temperatures occur in the clock and issue logic units               |

| while the minimum temperatures occur in the L2 cache                                     |

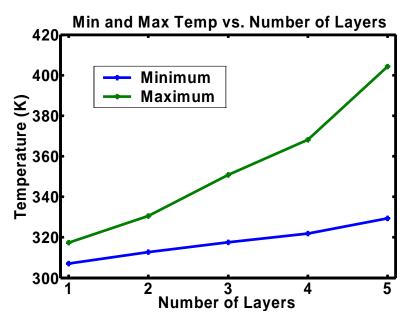

| Figure 24: Minimum and maximum chip temperature versus number of stacked                 |

| Pentium III layers on a 3D chip                                                          |

| Figure 25: Minimum, maximum, and mean layer temperatures for alternate 3D chip           |

| layout in which layers 4 and 5 are rotated 180 degrees from the original 5-layer         |

| chip78                                                                                   |

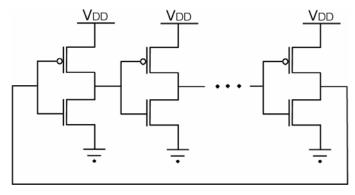

| Figure 26: A 31 stage ring oscillator                                                    |

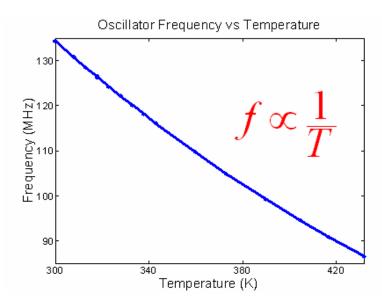

| Figure 27: Ring Oscillator frequency versus temperature. The results show an inverse     |

| relationship between frequency and temperature                                           |

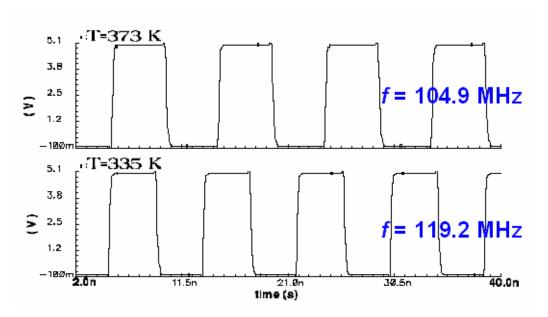

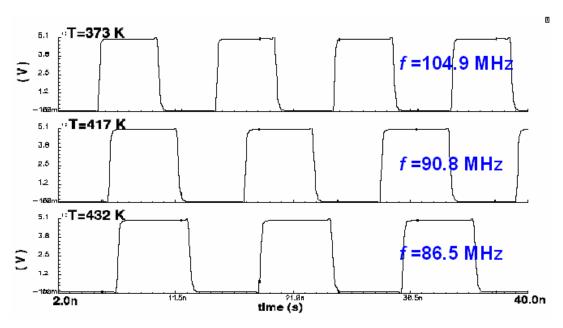

| Figure 28: Output voltage plot for a 31-stage ring oscillator. The representative        |

| temperatures are found in 2 different locations on the same layer of a 3D circuit.       |

| The plots show the expected result that oscillation frequency differs for an             |

| oscillator places on the same layer at 2 different locations                             |

| Figure 29: Output voltage plot for transient simulation of 31-stage ring oscillator. The |

| oscillator is placed at the same x-y location on each of the 5 layers of a 3D chip.      |

| Because the temperature on each layer is different at that same x-y location, the        |

| frequency is different. Temperatures on the upper layers are higher, resulting in        |

| lower oscillator frequency                                                               |

| Figure 30: Cadence layout of a diode temperature sensor fabricated through MOSIS.        |

| 88                                                                                       |

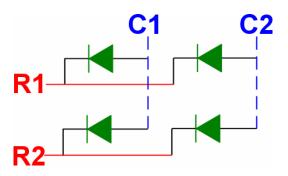

| Figure 31: Diode sensors arranged in a 2x2 array. The p-terminal of each device is       |

| connected to its corresponding column line and n-terminal of each device is              |

| connected to its corresponding row line                                                  |

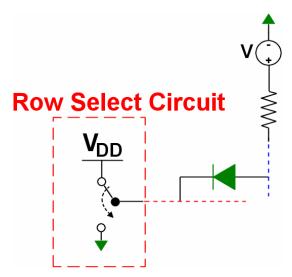

| Figure 32: Apparatus for measuring diode current for a particular sensor in the sensor   |

| array                                                                                    |

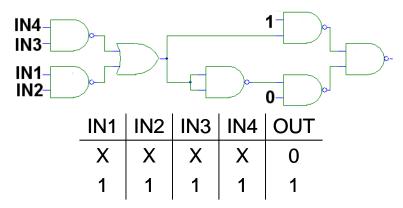

| Figure 33: Circuit schematic and truth table for the row select circuit placed at the    |

|                                                                                          |

| beginning of each row of the diode array                                                 |

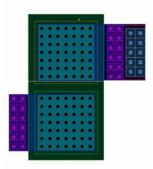

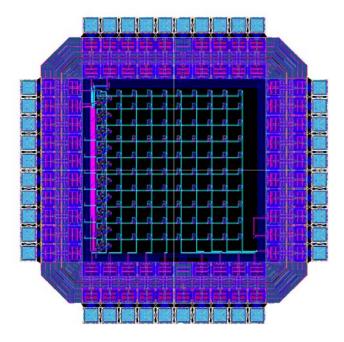

| Figure 34: Cadence layout of Chip #1: a 10x10 diode sensor array with control            |

| circuitry to select the desired diode                                                    |

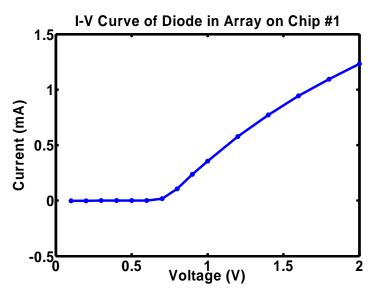

| Figure 35: <i>I-V</i> characteristic curve for a representative diode in the sensor array on   |

|------------------------------------------------------------------------------------------------|

| Chip #193                                                                                      |

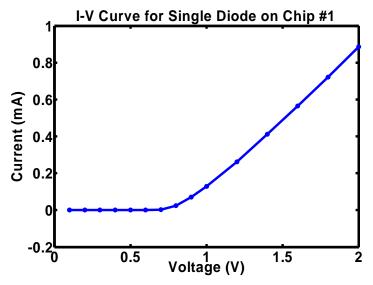

| Figure 36: <i>I-V</i> characteristic curve for a single diode fabricated outside of the sensor |

| array on Chip #1                                                                               |

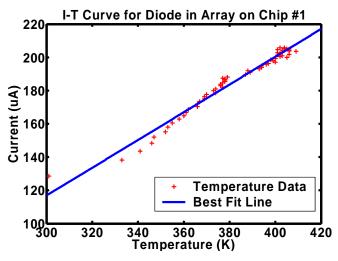

| Figure 37: Current vs. Temperature plot for representative diode in sensor array 95            |

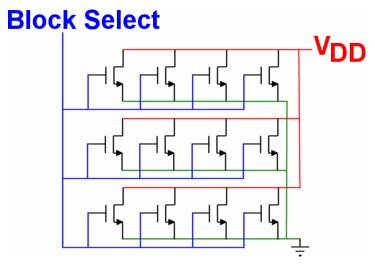

| Figure 38: Representative block of n-channel MOSFET devices. The entire block of               |

| devices is turned on when a voltage is applied to the block select line. The block             |

| facilitates local heating                                                                      |

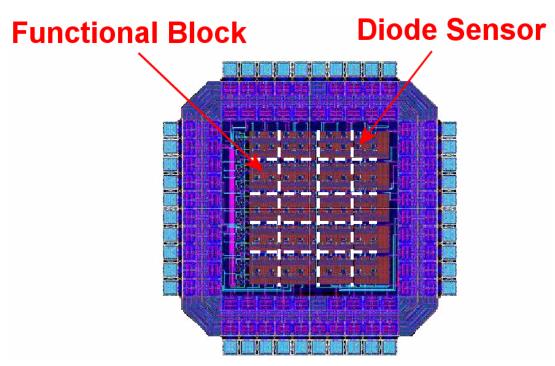

| Figure 39: Cadence layout of Chip #2: Selective Heating and Measurement Chip. The              |

| chip contains a 10x10 diode temperature sensor array spread across the chip and                |

| a 5x4 array of functional blocks. The white dashed lines show the functional                   |

| blocks98                                                                                       |

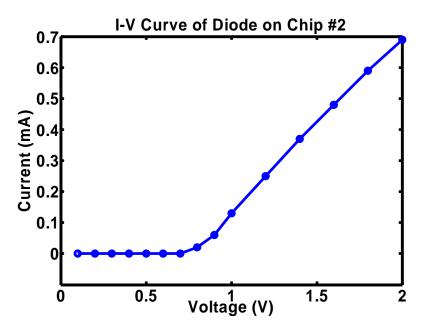

| Figure 40: <i>I-V</i> characteristic curve for sensor in the sensor array fabricated on Chip   |

| #2100                                                                                          |

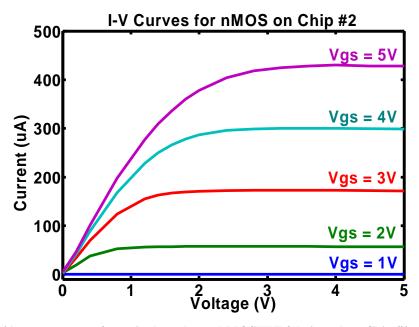

| Figure 41: $I_D$ - $V_{DS}$ curve for a single n-channel MOSFET fabricated on Chip #2,         |

| outside of the functional blocks and the diode sensor array 100                                |

| J                                                                                              |

## Chapter 1: Introduction and Motivation

Since the invention of the field effect transistor (FET), the electronics industry has seen unparalleled growth. Integrated circuits have evolved from large chips containing only a few transistors to chips with areas less then 100 square millimeters containing over 50 million transistors. These performance gains are possible because designers have found ways to increase the functionality of integrated circuits by realizing faster, smaller devices and by using more devices on a single chip. The performance advances have followed an exponential behavior known as Moore's Law, first observed by George Moore in 1965. The most recent projection of Moore's Law, the 2004 International Technology Roadmap for Semiconductors, predicts processors with device gate lengths down to 20 nm and device densities of over one billion transistors per chip by the year 2016 [1]. This projection is 70 nm smaller and a transistor count of almost twenty times greater then current manufactured technology. While the projections sound realistic given the pace of improvements to date, the reality is that fundamental physical limits may mean the end to Moore's Law. Current methods for realizing faster devices and packing more of them on chip are quickly reaching their limits. The motivation of this work is to present these limiting factors, to introduce three-dimensional integration as a new architecture to overcome these limits, and to present a method for calculating and controlling chip heating in a three dimensional circuit.

### **Device Scaling Limitations**

Device scaling is the shrinking of transistor characteristics to produce smaller, faster devices. Ideally, a transistor's characteristics are scaled up or down by a factor  $\alpha$  to maintain an electric field inside the device that is the same as the original device. This "constant field scaling" results in circuit speed increasing in proportion with  $\alpha$  and circuit density increasing as  $\alpha^2$  [2]. Unfortunately, ideal scaling theory is reaching its practical limits. As gate lengths become smaller, voltages, gate-oxide thicknesses, and device lengths can not be scaled ideally because of short channel effects, quantum effects, and application tolerance limitations [2].

When device lengths are small, quantum and short channel effects lead to random variations in gate length and other device parameters, leading to large differences in device characteristics. Physical dimensions are limited by leakage currents through various barriers. Voltage scaling is limited by the non-scalable bandgap of silicon and its effect on built-in junction voltages. Supply voltage scaling is limited by the need for sufficient gain for logic functionality. Finally, non-scaling of the subthreshold slope is the limiting factor for threshold voltage [2]. In all, the inability to continue ideal scaling of these parameters will lead (and in some cases, has already led) to a point where process tolerances and proper device behavior cannot be obtained at small feature sizes. The result is an inability produce smaller, faster devices and thus, a potential roadblock in the ability to pack more and more devices on chip.

#### Interconnect Limitations

The ever-growing demand for functionality and higher performance requires more transistors to be closely packed on a single chip. However, all of these devices must be connected together with interconnects that that do not inhibit the propagation of the signal. While scaling has had a positive effect of allowing designers to incorporate more devices on chip, the impact on interconnects has been just the opposite. Interconnect performance degrades with scaling due to smaller wire pitch and wire cross sections. Also, the increased device density and larger chip area creates the need for an increased number of interconnects that must traverse longer distances. All of these factors lead to an increase in wire resistance and capacitance, thereby increasing signal propagation delay. Also, increasing interconnect loading affects the power consumption in high performance chips, a drawback for low power systems [3].

Solutions to the interconnect problem have been investigated. Designers have tried widening interconnect lines as well as utilizing new materials to combat the increased delay times. At the 250 nm node, copper with low-*k* dielectric was successfully introduced. However, as device features continue to scale, interconnect delays will result in spite of the new materials, and it is believed that no new materials will be available to solve the problem [3]. While widening the metal lines is another solution, it also creates a need to add more metal layers to the fabrication process, which increases the complexity and cost of the process and can also degrade circuit reliability [4]. In all, there is an increasing need for a new architecture that will

allow designers to pack more and more devices on chip and connect these devices in an efficient manner.

#### Thermal Limitations

Ideally, power density remains unchanged when devices are scaled. However, because supply voltages can not be scaled ideally due to the scaling limits previously addressed, power density actually increases for the scaled device. Also, the demand for greater functionality and the presence of smaller devices allows for more devices to be used on a chip. The end result is a higher chip power density because of the use of individual devices drawing more power and more of these devices on chip. In addition, the packaging of many VLSI chips into compact packages, such as multichip modules, also creates higher then desired power densities for the packaged component [5]. The energy consumed as power is drawn is converted to heat and results in detrimentally high chip temperatures.

There are a number of potential problems that result from additional heat being generated. It has been stated that for every 10 °C increase in temperature, the failure rate of microelectronic devices doubles, leading to a serious long term reliability concern [5]. Typical thermally induced analog failures include input offset voltage and offset voltage drift in differential amplifiers, reference voltage shifts in regulators and data converters, and nonlinearities in multipliers [5]. In digital circuits, logic errors are the main concern. The source of these problems is not overall chip heating, but rather local heating. Since power dissipation is not uniform across the chip, localized heating occurs much faster then heating across the entire chip. The extra heat generated can lead to hot spots—areas where large temperature gradients

exist. Thus, there is a need for methods to calculate localized chip temperature in addition to overall chip temperature, and ways to cool hot spots before any timing errors occur or any physical damage is done. Finally, it signals an alert for future VLSI design: any new method employed to allow for the increased packaging of devices or systems should also be temperature considerate.

#### Thesis Overview

The purpose of this thesis is three-fold:

- 1. to present 3D integration as a way to group more devices in a single area as well as overcome the limitations of interconnect scaling.

- to present a methodology for calculating localized chip temperature for a 3D chip.

- 3. to present experimentation on the effect of device activity on chip temperature and extend these results for verification of the methodology mentioned in 2.

The following is an outline for the remainder of this thesis

- In chapter 2, integration in three dimensions is presented. Design structure, fabrication techniques, vertical interconnect technology, and challenges and considerations are presented.

- In chapter 3, a simulator that calculates chip temperature as a function of position on chip is presented. The specifics of heat theory and thermal networks are explained and the algorithm for the simulator is detailed. Results from simulations are provided.

- In chapter 4, validation of the claims stated in this thesis is presented.

Simulations of the effects of temperature on frequency are presented and designs for measuring local chip temperature and selectively heating areas of a chip are provided. Results of experiments conducted after fabrication of the designs are offered.

- In chapter 5, a summary of the findings of this thesis are given.

# Chapter 2: Integration in Three Dimensions

Vital to the continued growth of advanced integration is the ability to increase chip functionality. So far, designers have done this by scaling device features to increase the complexity of chip designs, resulting in an increase in the number of devices on chip and an increase in chip area. The fact that scaling not only allows for the use of more devices on chip, but also results in faster devices, is the other important factor in the performance gains to date. However, to continue to meet the demand for highly functional and faster integrated circuits, the limitations discussed previously must be overcome. A paradigm shift from present integrated circuit architecture is needed. The new architecture should meet the ever-growing demand for higher functionality and performance without increasing chip area, exceeding the limitations of interconnect technology, or creating dangerously high local or overall chip temperatures.

At present, integrated circuits are produced in a planar way. Devices are fabricated on a single layer of silicon and are interconnected to form complex circuits. The idea presented in this thesis is to branch out into the third dimension. The suggestion is to create multiple active layers of silicon for fabrication of devices not only laterally, but vertically as well. The devices are then connected using dense, vertical interconnects. The 3D architecture will lead to potentially smaller chip areas, shorter interconnect paths, higher transistor packing density, and flexibility in system design and placement.

The idea of utilizing the third dimension for integration is not a new one. The concept was demonstrated as early as 1979 with the presentation of silicon thin films

relief structures to induce crystallographic orientation in thin films [6]. The idea remained a concept though, with no real strides being made to actually produce working circuits on multiple layers of silicon. This is because of the overwhelming success of device scaling in bulk silicon CMOS technology. However, with the growing limitations to scaling and the menace of interconnect delays, researchers have turned to 3D integration as more of a necessity, rather than a concept, for maintaining chip performance well into the deep sub-nanometer range. Performance models have been developed to show the gains in chip area, performance, and interconnect delay that can be obtained using three-dimensional circuits [3], [7]-[8]. Furthermore, the actual fabrication and testing of devices fabricated on multiple layers of silicon and the implementation of vertical interconnects has been shown [9]-[18]. The idea of three-dimensional circuits has moved from an idea to a reality. The latest research shows the feasibility of the idea and the practicality of implementation.

## Design Structure and Requirements

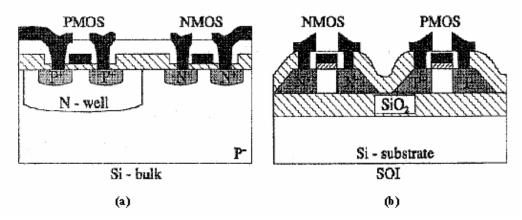

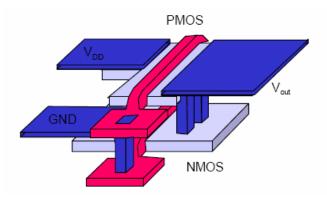

There are 2 approaches to designing a 3D circuit. The first is to divide the entire chip into blocks and place each block on a separate layer, as seen in Figure 1. Since each layer is stacked, the blocks are connected using vertical interconnects. The connections within blocks should be simple, eliminating the need for more then one or two layers of metal for each block layer. The second approach is to fabricate the same kind of device on each layer, for example only n-channel MOSFETs on one layer and only p-channel MOSFETs on another (Figure 2). The individual devices are then interconnected vertically to realize the desired element, such as an inverter. In

both cases, there is a significant reduction in chip area and interconnect length over the 2D configuration. However, each approach has other unique benefits.

Figure 1: 3D integrated circuit where each layer T is a block of devices. There are separate metal layers for connections on the same layer and for different layers.

Figure 2: 3D integrated circuit where each layer is a single type of devices.

For the block layer approach, the immediate benefit is flexibility in block placement and routing. Logic gates on a critical path are placed close together within a block and blocks on a critical path can be placed side by side or vertically for faster signal propagation due to shorter interconnect lines. Furthermore, the ability to build highly integrated systems is evident. Circuits with different voltage and performance requirements can be put on different layers for isolation. Analog and digital components in mixed-signals systems can be placed on different layers to achieve better noise performance due to lower electromagnetic interference [3]. Figure 3, from [3], shows an example of a 3D chip with logic, memory, analog, radio frequency, and optical circuits on separate layers, integrated into a single 3D chip.

Figure 3: 3D systems-on-chip (SOC) consisting of logic, memory, analog, RF, and optical components, each on a separate layer and integrated onto a single 3D chip.

For the device layer approach, the benefits lie in fabrication and routing. First, separate device layers reduce the process steps for each layer by almost half [8]. This is because there is no need to use wells for fabrication of n- and p-channel devices on the same substrate. Thus, there are no extra ion implants or long thermal anneals at

high temperatures. Instead, designers can just use the proper doping depending on the device being fabricated. This approach also allows for better routing capabilities because designers can take advantage of the typically one-third smaller area of n-channel devices over p-channel devices and use this area for routing and interconnects. Finally, single devices are more compact then blocks of devices, so the interconnections between devices are shorter and devices are closer together, allowing for better packing density.

There are basically two design requirements for a 3D circuit: proper device behavior and uniformity in behavior across all devices on all layers. These requirements are satisfied during both design and fabrication of the multiple layers of silicon. For both the device and block layer approaches, obtaining the multiple layers can follow either a sequential or parallel process flow. In a sequential process, each layer is constructed on top of the previous layer. This requires complete fabrication of the devices or blocks on one layer before the next layer is fabricated. This approach requires subjection of devices on previous layers to all of the process steps for fabricating the current layer. Thus, low temperature fabrication processes are required to ensure proper device behavior and uniformity, since subjecting completed layers to high temperatures can degrade the integrity of the previous layers. For a parallel process, each layer is fabricated individually and then all layers are combined together. This approach avoids repeatedly subjecting subsequent layers to process steps and also helps with device uniformity, since each layer is done separately using the same steps. However, this method introduces the problem of alignment. Proper

alignment insures good device and circuit behavior after interconnection, so care must be taken to ensure proper device and circuit function.

## Fabrication Using Silicon-on-insulator (SOI)

The foundation for 3D integration is the stacking of multiple active layers. One way of achieving multiple stacked active layers is through silicon-on-insulator (SOI). SOI is a layered structure of thin single-crystal silicon either on top of an insulating substrate, such as quartz or sapphire, or separated from a bulk silicon substrate by an insulating layer such as silicon dioxide [19]. The foundation of the SOI structure is a bulk silicon substrate. Above it is an insulating layer, called the buried oxide. On top is a film of silicon. Devices are fabricated on this film, rather then directly on the silicon substrate, as in conventional bulk silicon CMOS.

There are many advantages to utilizing SOI technology, namely increased reliability, faster circuit operation, and low-voltage low-power operation. The advantages are due to differences between SOI and bulk silicon technology. Figure 4 from [20], shows transistors on bulk silicon and silicon-on-insulator.

Figure 4: CMOS transistors fabricated on (a) bulk silicon and (b) SOI.

One benefit SOI offers is inherent device isolation, an advantage created by the buried oxide. The thin film of silicon above the buried oxide can be fabricated into "islands" that comprise each device. The buried oxide allows for vertical isolation of the islands so that devices will not share the same substrate, as in conventional CMOS. Thus, vertical isolation is achieved as a benefit of the process, rather then by the sophisticated schemes employed in conventional bulk technology. Separate device substrates eliminate the need for the deep wells that facilitate fabrication of n- and p- channel devices on the same substrate in conventional CMOS. This simplifies process steps by as much as 30 percent and overall circuit area by up to 60 percent [19].

Circuit reliability is also improved in SOI, mostly due to the innate isolation it offers. First, device malfunction due to latch-up is essentially nonexistent in SOI because there is no need for wells or deep trenches for isolation. Thus, there are no parasitic paths between highly doped areas, well, and substrate to cause latch-up. Second, soft errors due to radiation are reduced because the insulating layer in SOI limits the volume of the body of the device to only the thin silicon island, rather then a large bulk substrate. This is a volume reduction of 2 to 3 orders of magnitude [20]. Thus, there is less volume available for a radiated particle to induce ionization as well as less volume available for storing any ionized charge.

Another benefit of the SOI structure is decreased junction capacitance. From Figure 4, it is evident that the source and drain regions extend all the way down to the insulator so that only their lateral sides can serve as junctions. The result is a reduction in the area of overlap of the source and drain regions with the body, thereby

significantly reducing junction capacitance as compared to bulk technology. The reduction in the parasitic capacitance significantly improves circuit speed, allowing higher frequency circuits to be constructed.

Lastly, the SOI structure allows for low power and low voltage application. The smaller junctions of SOI films permit better performance over bulk circuits as supply voltages fall. The structure also produces devices with steeper subthreshold voltage slopes then bulk devices. The subthreshold slope determines the gate bias needed to assure an "off" condition in a device. Requirements for a specific on-off current ratio limit the minimum threshold voltage the device can have, which ultimately limits the required power supply voltage for the device [21]. Thus, in SOI the steeper subthreshold slopes allow for lower possible threshold voltages and thus lower supply voltages, all without loss of speed [19]. The effect is lower supply voltages and reduced leakage current, both leading to lower power consumption.

There are commercial options available for fabrication of single layer SOI wafers. One is Separation by Implanting Oxygen (SIMOX), a process in which the buried oxide is formed by internal oxidation of the silicon substrate during a high energy oxygen implantation. A subsequent high temperature anneal is necessary to recover the crystalline quality of the thin silicon film [20]. Wafer bonding, another method, involves fusing together two oxidized wafers (or one oxidized and one bare wafer) at room temperature. After annealing to increase the bonding strength, one of the two wafers is thinned to the proper thickness by grinding, polishing, and etching. The technique provides undamaged crystal quality and a wide range of thickness for both the buried oxide and SOI film [20].

While the single layer methods are sufficient for creating one SOI active layer, the subsequent active layers for the 3D chip must still be fabricated. Each active layer must contain high quality single crystal silicon and the process steps for obtaining the silicon layer must not change the characteristics of the active layer beneath it. SIMOX and wafer bonding processes prove unsuitable for creating multiple layers because of the high temperatures they require. Thus, while designers can use the single layer SOI techniques aforementioned for first layer devices, they must employ other techniques for creating the subsequent layers. Another alternative is to develop a completely new approach to SOI that, while requiring fabrication from bulk rather than utilizing SOI wafers for the first layer, is more suitable for repetition for 3D integration.

There are at present 2 methods suitable for creating multiple layers using SOI: processed wafer bonding and silicon epitaxial growth. The first is a parallel process while the second is a sequential one. The choice of method employed will depend on the requirements of the system, since performance is strongly influenced by the electrical characteristics of the devices fabricated as well as on the manufacturability of the process. The specifics of these two methods are described in the subsections that follow.

#### **Processed Wafer Bonding**

Processed wafer bonding is an appealing approach for creating 3D circuits that involves fusing together two or more fully processed wafers. The wafers, usually single layer SOI type, are processed individually to create working 2D circuits complete with planar interconnects. The individual wafers are bonded, face to face or

back to back, either directly or indirectly. Direct bonding methods exploit the intermolecular attractive forces that exist between two smooth surfaces brought into intimately close contact. Indirect bonding involves the deposition of an intermediate layer of bonding agent followed by a combination of temperature and force processes to secure the bond. For either method, interlayer vias can be etched before or after the bonding process for vertical interconnections between layers.

One requirement of wafer bonding processes is strong and secure bonds. For direct bonding, in order to achieve sufficient bonding energy at low temperatures, bonding surfaces must be smoothed, flattened, and cleaned. Achieving a smooth surface free of contaminants is critical for maximizing the density of bonding species on the mating surfaces. Defects on the surface reduce reactivity and lower the bond energy [22]. For indirect bonding, bond strength can be optimized by adjusting the bond process parameters, including ambient temperature, pressure, bond temperature, and surface treatments.

Another requirement of wafer bonding processes is preservation of the electrical integrity of the bonded layers. This requirement demands the use of processes that work at low temperature and minimize mechanical stress. High temperature is detrimental to metal layers used for interconnects, as it can lead to undesired metal diffusion through barrier layers. Also, unwanted dopant activation in the active areas of devices can occur at high temperatures. There are reports of direct and indirect bonding processes that are successful at temperatures below 400 °C [22]. Mechanical stress is reduced by proper preparation of the surfaces for easier bonding and also by embracing low temperature, low pressure techniques.

Perhaps the biggest demand on wafer processes for 3D integration is adequate alignment. Proper alignment is critical for good electrical connections. Each layer must be sufficiently aligned to the layer beneath it if a good vertical interconnect is to be fabricated. One method is transparent alignment, which involves transferring a device layer from its bulk silicon substrate onto a transparent glass "handle" substrate. The new wafer is then inverted and bonded to the layer beneath, using the transparent glass substrate on top for visual alignment. The temporary glass substrate is then removed by laser ablation. This bonding method has been shown to preserve the electrical integrity of long and short channel devices after transfer [12]. Also, alignment can be done using infrared cameras that align through the silicon substrate. Another alternative is flip-chip bonding, a method that achieves alignment in the x-and y- directions using optics. The misalignment is reportedly less then 1  $\mu$ m and can be done at a temperature of 400 °C [3].

In all, wafer bonding proves to be a promising method for 3D integration, provided limitations in alignment can be overcome. It is suitable for creating multiple layers in parallel, all with similar electrical properties. Also, it imposes no temperature limitation on device fabrication, since each layer of devices is fabricated separately. Only bond temperature is limited, and this has already proven to be surmountable. The feasibility of integrating 3D ring oscillators and coupling optical signals generated in n<sup>+</sup>p diodes on one layer to CMOS circuits on another layer has already been shown [13]. As stated before, wafer bonding using a temporary glass substrate has also been demonstrated. Measurements after layer transfer yielded less then 10 percent degradation in drain current and threshold voltage for 65 nm n-

channel MOSFETs and only a slight increase in stage delay of ring oscillator circuits composed of 55 nm CMOS inverters [12]. However, to achieve the state of the art performance enabled by deep nanometer devices, the reported best case alignment of  $\pm 2 \mu m$  in [3] must be improved.

### Silicon Epitaxial Growth

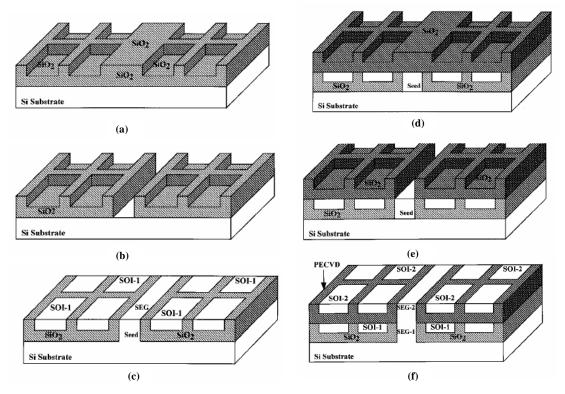

Silicon epitaxial growth (SEG) is a sequential technique for creating multiple active layers of silicon that uses a hole etched in the insulating layer to grow single crystal silicon seeded from the substrate. The SEG process, shown in Figure 5 from [17], typically takes place in a low pressure chemical vapor deposition reactor. The carrier gas is hydrogen, dichlorosilane supplies the silicon, and hydrochloric acid prevents the formation of polysilicon on the insulator [23]. A thermal oxide is deposited on a bulk silicon substrate and etched to create islands where the silicon will selectively grow. A thin oxide is then deposited in the islands to provide insulation for the island and the substrate beneath. Next, a seed window is opened adjacent to the oxide wells. Silicon is grown first vertically through the seed window and then laterally over the oxide. Device quality material is produced when temperature is between 860 °C and 1000 °C at a pressure of 50 to 150 Torr [23]. The excess silicon grown outside of the islands is removed using chemical mechanical planarization. Thus, silicon islands are obtained selectively within the oxide wells. Subsequent layers are formed the same way.

Figure 5: Process steps for fabricating multiple layers of silicon using Silicon Epitaxial Growth: (a) deposition, patterning, and insulation of islands, (b) opening of seed window, (c) silicon growth and chemical mechanical polishing, (d) deposition, patterning, and insulation of 2<sup>nd</sup> layer islands, (e) opening of 2<sup>nd</sup> layer seed window, and (f) silicon growth and chemical mechanical polishing of 2<sup>nd</sup> layer islands.

The ability to create single crystal silicon as pure as the underlying substrate is one advantage SEG affords. Provided few faults occur in the growth process, devices should behave the same since they are all fabricated on the same silicon seed.

Furthermore, the growth of the silicon is not overly complicated and is compatible with CMOS fabrication processes. Some methods for creating multiple layers of silicon do not offer the ease of process like SEG does, nor do they offer the same crystal quality.

However, SEG is not without its disadvantages, the biggest being thermal budget. While other techniques have much lower process temperatures, SEG relies on temperatures as high as 1000 °C for silicon growth. As previously stated, temperature

this high can be very straining on devices fabricated on lower levels. If SEG is to be used to fabricate state of the art devices with small gate lengths, process temperature will need to be lowered significantly to ensure good device performance.

There has been success in forming multiple layers of silicon and even submicrometer devices using SEG. These advances demonstrate the feasibility of 3D integration using SEG. First, there are reports of good crystalline quality SEG at temperatures as low as 750 °C in ultra-high vacuum epitaxy systems [14].

Furthermore, silicon islands as small as 150×150 nm have been developed on 2 layers [17]. At this size, it is possible to accomplish terascale integration (10<sup>15</sup> devices per die) with devices with gate lengths of 25 nm. Furthermore, fully depleted p-channel MOSFET with gate lengths of less then 100 nm were fabricated on both layers to show the quality of the silicon. The fabricators report normal current-voltage characteristics as well as decent on-off, threshold voltage, and subthreshold slope values. The findings show that good quality silicon can be obtained using SEG and with improvements, the technology could potentially be used for high performance circuits integrated in three dimensions.

#### Fabrication Using Polysilicon on Insulator

Polysilicon on insulator is a very popular method of creating a second active layer of silicon. As in SOI, an insulating layer is deposited on a substrate. However, polycrystalline or amorphous silicon instead of pure single crystal silicon is deposited on the insulator. In SOI, obtaining single crystal silicon on an insulator at a temperature suitable for 3D applications is difficult. However, obtaining polycrystalline silicon is not as difficult, since there are fabrication steps already

available to deposit the poly layer onto the insulator. One commonly used method is low pressure chemical vapor deposition. After the film is deposited, methods to crystallize certain regions are employed in an effort to control grain size and orientation. Thin film transistors fabricated on polysilicon layers have been widely used in active matrix displays for years. The ease of fabrication demands a look at ways of improving device characteristics in order to produce devices that could one day be used in 3D circuits.

The problem with polysilicon thin film transistors is performance. Polysilicon thin film transistors suffer low mobility and high threshold voltages because of grain boundaries. Grain boundaries create trap states due to bonds left dangling because of the change in crystal orientation. These defects can trap electrons at the boundary, inhibiting current flow and degrading device performance. This phenomenon distinguishes thin film transistors from bulk silicon and SOI MOSFETs, which do not suffer from such degradation because the silicon used is pure, single crystal silicon free of defects.

The other problem with thin film transistors on polysilicon is device uniformity, an important requirement for high performance 3D integration. A strategy for modeling variations in device performance due to grain size was developed [24]. It predicts that as grain size and device size converge, variation in device characteristics increases because of variations in grain size, location of grain boundaries, and the number of grains in a single device. This is very important considering high performance devices have nanometer gate lengths. The model also predicts there would be no variation in device performance if grain size and grain

boundary can be precisely controlled. Thus, uniformity among devices is a huge concern to be addressed if polysilicon thin film transistors are to be used for 3D circuits. Methods need to be employed to eliminate—or at least control—grain boundaries so that devices can be fabricated away from such locations for better performance and uniformity.

It is believed that the requirement of having single crystal silicon can be relaxed as long as the channel region of the MOSFET lies on a single grain [10]. This belief has prompted many to try and improve thin film transistor performance for use in 3D circuits by obtaining localized regions of single crystal silicon within the amorphous or polycrystalline silicon. If a device could be made to lie on a single grain, then theoretically, it should perform identically to a device formed in highly pure single crystal bulk silicon. Thus, the challenge for polysilicon on insulator for 3D applications is obtaining large single crystal grains of silicon within the polycrystalline layer. Devices fabricated would offer device performance similar to bulk technology. There are at present 2 methods being explored to produce such devices: beam recrystallization and solid phase crystallization. The specifics of these two processes are explained in the following subsections.

### Beam Recrystallization

Beam recrystallization is a method commonly used for creating an active layer of silicon atop an existing substrate. Polysilicon or amorphous silicon is deposited on an insulating oxide layer and an intense laser or electron beam is used to induce crystallization. The beam can be focused entirely on one area and used to heat only

that area, without much heat being spread through the underlying insulator. Thus, protection of underlying layers is obtained.

Work was done in the early nineties to produce devices and working 3D circuits using beam recrystallization. Mobility and subthreshold slope comparable to bulk silicon technologies were achieved for some devices [25]. However, the leakage current for such devices was unacceptably high. Also, a four-layer 3D device with a primitive function of parallel image signal processing was realized [16], but the techniques used do not appear to be useful for highly scaled circuits due to the high temperature processes employed for interconnections. Lastly, a four layer chip containing a programmable logic array, CMOS gate array, and a CMOS synchronized random access memory was fabricated [18]. The performance was limited by large variations in threshold voltage due to unintentionally doped impurity concentration from vertical isolation layers. It was also limited by fluctuations in gate insulator thickness and carrier mobility due to variation in silicon orientation.

Recently, interest has been renewed in the use of beam recrystallization for thin film transistors. High performance polysilicon thin film transistors using laser beam recrystallization along with low temperature processing have been fabricated [26]. However, it is still difficult to control variations in grain size and grain boundary size. Thus, beam recrystallization will not emerge as a leading technology for 3D integration of high performance devices unless the grain variations can be controlled. This will require obtaining larger single crystal grains that have fewer defects. A beam crystallization method employing sequential lateral solidification to produce

single crystal silicon has been preliminarily presented, but further improvements must still be made [27].

#### Solid Phase Crystallization

Solid phase crystallization (SPC) is another method for fabricating thin film transistors on polysilicon layers. Amorphous silicon is deposited on an oxidized silicon wafer using low-pressure chemical vapor deposition in a silane atmosphere at a temperature of 550 °C. The silicon is then crystallized in the solid phase by thermal annealing in an inert gas such as N<sub>2</sub> or Ar. Low anneal temperatures in the range of 550 °C to 650 °C are selected to hinder the randomness of crystallization. The process, because of its low temperatures, is easily implemented to create multiple layers of polysilicon without thermally damaging devices on lower layers. The drawback: in conventional SPC, there is still no real control over the location of the grain boundaries [28]. Therefore, newer SPC methods have been developed that employ seeding to induce lateral crystallization and allow greater control over grain location [28]-[33].

The process of crystallization begins with nucleation: the formation of single grains of a specific orientation that form and enlarge as the material is heated. The time it takes for nucleation to begin is the incubation time, while the rate at which the grains enlarge is the grain growth. In solid phase crystallization, designers exploit the fact that the amount of nucleation relative to grain growth decreases with decreasing temperature [29]. This means that at lower temperatures, grains will have more time to enlarge before nucleation of another grain. This allows designers to produce larger grains and thus have some control over grain size. The disadvantage to the process is

that crystallization may take several hours because a fraction of the time is spent in the incubation period [29].

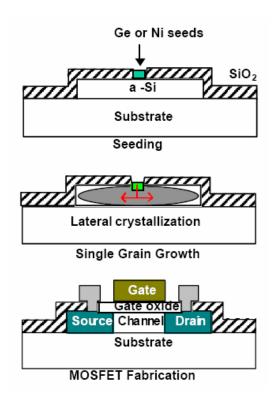

While grain size can be controlled somewhat by utilizing lower anneal temperatures, there is still a need for better control over grain size, location, and boundaries. To achieve this control, the use of seeding agents has been investigated. An illustration of the seeding process is shown in Figure 6 from [28]. After depositing amorphous silicon, extra process steps are added to selectively deposit seeding agents to induce lateral crystallization with minimal self nucleation. A sacrificial oxide is deposited and etched to expose seed windows where the seeding agents will be deposited. The crystallization by annealing is then performed. The seeds stimulate lateral crystallization and the grains are grow from the specified locations defined by the windows. The deposited seeding agent and the sacrificial oxide are then removed. Another anneal is employed to enlarge the grains even further. Finally, thin film transistors are fabricated on the grain a safe distance away from the seeds. Theoretically, the transistors are fabricated on a single grain with no boundaries within the channel of the device. Thus, greater control over device variations as well as better device performance is attained.

One seeding agent that has been used in SPC is germanium. Germanium deposited on silicon bonds to form a SiGe alloy. This alloy crystallizes faster then pure silicon, allowing for a reduction in the incubation time and thus the anneal time. Also, germanium does not diffuse fast in silicon, and the amount of germanium needed to induce nucleation is small [30]. These two facts allow for easier removal of

the germanium after crystallization because the alloy is confined only to the interface between silicon and germanium. Typically, grain sizes of 1-2 µm can be obtained.

Figure 6: Use of nickel or germanium seed to induce lateral crystallization to create a single crystal region to comprise the channel of the device.

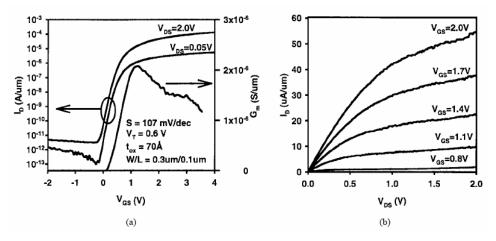

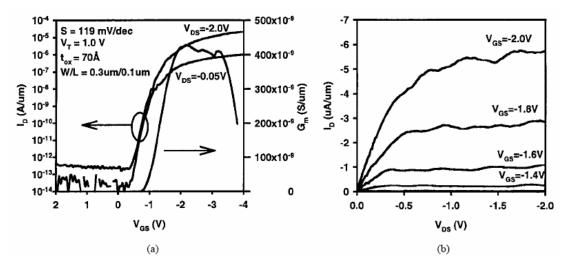

Germanium seeding has been used to fabricate polysilicon thin film transistors with gate lengths of 100 nm [30]. Since the length of the device is smaller then the grain size, the channel lies on single grain silicon. The devices exhibit excellent onoff ratio and off-state performance. Transfer and output characteristics, from [30], are shown in Figure 7 and Figure 8. Seed window sizes have been scaled to dimensions smaller then 1 μm, indicating that seed size is not a limiting factor on scaling the technology for smaller length devices [30]. While there are still no reported 3D circuits constructed using this technology, the method seems promising for achieving vertical integration of high performance circuits with deep submicrometer devices because of its low thermal budget and ability to accommodate small feature sizes.

Figure 7: Germanium seeded n-channel MOSFET with gate length of 100 nm: (a) transfer characteristics and (b) current output.

Figure 8: Germanium seeded p-channel MOSFET with gate length of 100 nm: (a) transfer characteristics and (b) current output.

Another seeding agent that has been investigated is nickel. Nickel is used to increase grain size beyond the roughly 1-2 µm obtained using germanium, allowing for fabrication of wider devices. The technique of using a metal such as nickel has been termed Metal Induced Lateral Crystallization (MILC). Nickel deposited on silicon through the etched seed windows bonds to form NiSi<sub>2</sub> and acts as a nucleus for crystallization, just as with germanium [10]. The grains grow elongated with major axis aligned perpendicular to the seed strip. After completion of crystallization

and removal of the remaining Ni and sacrificial oxide, another anneal is performed to enlarge the grain size in the MILC region. The result is grains with major and minor axis lengths as large as  $80~\mu m$  and  $10~\mu m$ , respectively [31]. In addition, the additional anneal can also act as a dopant activation step [28], thereby combining two process steps into one.

There has been considerable success in utilizing nickel seeding for 2D integration. Just as with Germanium seeding, 100 nm high performance thin film transistors have been fabricated using MILC with nickel as the seed agent [33]. The maximum process temperature employed was 500 °C, and the dopant was fully activated during the crystallization process. The process is compatible with CMOS technology, and device layers can be fabricated on top of metal lines because of the low thermal budget. With improvements to device performance, this approach seems very likely to succeed with 3D integration of high performance technology.

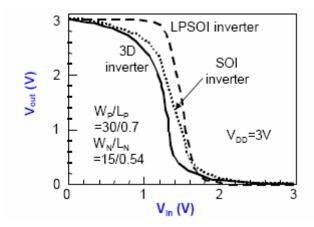

There has also been success in accomplishing 3D integration using MILC with nickel as the seed [9]-[10]. Inverters integrated in three dimensions, shown in Figure 9, were fabricated using MILC with maximum process temperature of 900 °C [10]. The n- and p-channel MOSFETs have gate lengths of 0.5 µm and 0.4 µm, respectively. The inverter performance approaches that of an SOI inverter, as shown in Figure 10 from [10]. Ring oscillators were also constructed to show the uniformity and repeatability of the device performance. While these 3D circuits have been constructed, they are still far from exhibiting the high performance seen in bulk technology 2D devices. Furthermore, low thermal budget and small feature size, as in [33], were not achieved. The point is that 3D devices have been suggested and

fabricated. With further improvements, especially in utilizing the advances in [33] to create 3D structures with low a thermal budget and small feature size, MILC may definitely emerge as a possibility for 3D integration of high performance circuits.

Figure 9: Layout of a 3D inverter fabricated using MILC with nickel as the seeding agent.

Figure 10: Inverter performance comparison for SOI, Large-grain Polysilicon SOI, and conventional SOI inverters fabricated on the same wafer. The performance of the 3D inverter fabricated using MILC is similar to the conventional SOI inverter.

#### Vertical Interconnects

In 3D circuits, vertical interconnects will be responsible for connecting active layers. Instead of having long global interconnects, blocks on critical paths are placed close to each on separate levels and connected with vertical interconnects. The proposed structure consists of the various active levels. Each silicon layer will have its own conventional 2D interconnects, but then between each layer there will be a

metal layer solely used for vertical interconnects. Dense 3D vias will connect these metal layers.

The nice thing about incorporating vertical interconnects into 3D integration is that current metallization techniques are easily expanded to three dimensions. Copper technology currently being used for 2D interconnects as well current via technology can be used for vertical interconnects without modifications [3]. Thus, no new technologies need to be implemented, only expansion of current techniques.

Furthermore, there are only a few extra process steps for creating the vertical interconnects. In a sequential fabrication process, after the formation of devices or blocks on the level being processed, contacts are made for both vertical and horizontal interconnects. Then, where vertical interconnects are to be defined, dense vias are patterned and filled using conventional techniques. After completion of the next layer, the connections are complete and the vertical interconnect is realized. In a parallel process, the extra steps are even less. All interconnects within a layer are fabricated. The vertical interconnects can either be patterned before or after bonding the layers. If done prior to bonding, vias are etched and can be used as alignment markers for bonding. After bonding, vias are filled in during the metallization process. For after-bonding techniques, etching is used to create the 3D vias for the metallization process. Either way, the additional process steps are few.

Many believe that the huge performance increase that will result from 3D integration is due to the shortening of interconnect lines by using vertical interconnects. In the 3D work that has been done, most of the speed enhancements have been attributed to the vertical interconnects. For example, in [10], the 3D

inverter exhibited a delay of 1.4 ns, a delay smaller then an inverter formed completely on a large grain polysilicon area on one level and an SOI 2D inverter. The speed increase is attributed to the reduced length of the interconnect forming the inverter.

The main concern with vertical interconnects continues to be device fabrication process. Subjecting metal layers to high temperature can cause considerable metal diffusion and leakage through barrier layers. The potential for metal contamination or poor interconnections due to diffusion is large and threatening. For true high performance integration, process temperatures will need to be kept below 500 °C for copper technology to protect the reliability of interconnects and to prevent copper diffusion [3]. In short, the 3D interconnect is one of the main reasons for performance gains from 3D integration. As such, its performance will need to be protected throughout the fabrication process.

## Challenges and Considerations

While three-dimensional integration appears to be a highly desirable innovation for continuing the trend of Moore's Law, there are still many roadblocks. As stated previously, low process temperature and good device performance are the main requirements for a 3D technology. Obtaining quality silicon islands for device fabrication at a suitable temperature to fabricate uniform devices is a serious challenge. However, in addition to this fabrication challenge, there are still other challenges to be faced once the challenges of fabrication are overcome.

One consideration is temperature. In 3D integrated circuits, the thermal heat generated is even more important then in two dimensions. As stated previously, high

temperature gradients can cause local as well as global chip failure. The same factors that lead to better performance gains in 3D circuits will also lead to higher temperatures. On a 3D integrated circuit, there are even more transistors enclosed in a given area, resulting in an overall increase in heat generated on chip. Furthermore, the SOI structure and the insulating layers, while providing device isolation, have thermal conductivity values generally two orders of magnitude smaller then silicon, thus providing poor thermal insulation. Also, 3D chips will offer systems-on-chip capabilities. This increased functionality of electrical, optical, RF, and other types of signals demand greater surface area for input and output of the signals, thereby reducing the surface area available for heat removal [34].

Thermal packaging will be the biggest factor in keeping 3D chips cool. It has already been stated that thermal packaging technologies with thermal resistance below 0.5 K/W will be necessary to maintain reasonable chip temperature. In [3], it is suggested that providing heat sinks for each active layer can significantly alleviate the thermal problem. No matter what, in order for the 3D chips of the future to operate at maximum performance limits, advancement in cooling and packaging technology will be necessary.

There are also reliability concerns in 3D circuits. As already stated, thermal effects pose a serious reliability risk. In addition, heterogeneous integration and systems-on-chip create the need for a better understanding of the mechanical and thermal behavior of new material interfaces. The use of different fabrication process will create a need for a new and better understanding of bonding interfaces and materials used, as these new processes may lead to new ways for devices to fail.

Furthermore, these new processes may influence existing reliability hazards such as electromigration. There are questions of yield and cost that will have to be dealt with as well. Careful tradeoffs will have to be made between system performance, cost, and 3D manufacturing.

Another area of concern is routing and placement along with computer assisted design. In two dimensions, there are numerous design tools available to figure out the best placements of different blocks on a chip. There are also computer programs available for layout; there are design rules in place for fabrication. The same thing will have to happen in three dimensions. There will be a need for computer assisted programs for 3D chip layout and simulators for 3D circuit behavior. Device models will need to be obtained. The road to 3D integration is a long one, and the research to date has not even begun to scratch the surface.

# **Summary**

Integration in three dimensions is a highly practical and highly logical step for the integration industry. It follows naturally to utilize the third dimension to continue the success of 2D integration brought on by scaling. The ability to pack more transistors, reduce interconnect length, and incorporate different technologies onto a single chip will transform the semiconductor field.

Work has been done to achieve multiple layers of silicon and fabricate devices on these layers. The techniques of wafer bonding, silicon epitaxial growth, beam recrystallization, and solid phase recrystallization are 4 methods currently being researched for potential 3D integration. Each of the processes offer advantages and disadvantages and each still needs a lot of improvement before the world will see 3D

integration of today's high performance, ultra small devices using any of these processes. Based on the work done, high performance 3D integration is still a long way off, considering most of the work presented thus far has only touched the surface by either achieving rudimental 3D structures or simply achieving working devices on multiple levels. 3D integration is still an idea and a research concept, but most believe with serious attention to the possibility, 3D integration will be the saving grace for the future of integration.

# Chapter 3: 3D Full-Chip Temperature Simulation

As stated previously, chip temperature is a big concern in current VLSI technology. In addition, it will be a major concern in the future for 3D integrated circuits. As more devices are packed onto chips and as devices are scaled, the overall power density on chip is increasing, resulting in overall increase in chip temperature. The increases, however, are not just global increases for overall temperature, but local increases as well. A potentially big problem with temperature increase is the dangerously high temperature gradients that exist locally. These local gradients result in "hot spots" on chip—areas of detrimentally high temperature. These hot spots can cause local logic errors and even physical damage. In 3D circuits, heat is generated on each layer and a coupling exists between layers, resulting in even higher local temperatures. Thus, in 3D circuits, hot spots may be an even bigger concern. What is needed is a methodology for locating hot spots, calculating the temperature at these locations, and figuring out ways to eliminate such spots.

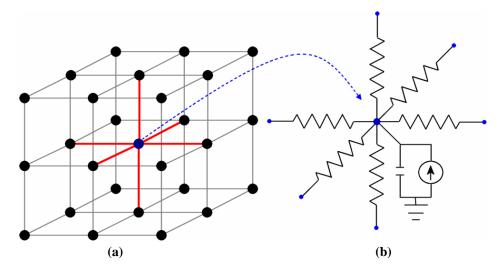

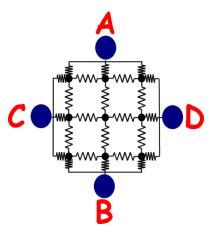

This chapter presents a model for heat flow in a 3D circuit and an algorithm that uses this model, in conjunction with a device simulator, to calculate chip temperature as a function of position. The model builds on work presented in [35]. While previous work has been done in estimating chip temperature [3], [36], there is a need for a simulator that connects individual device heating with full chip temperature. The methodology presented in this work takes into account the individual contributions of each device on each layer to the local and full chip temperature. It employs spatial dependent device operation as well.

#### 3D Heat Flow Model

To calculate chip temperature as a function of position, it is necessary to understand how heat is generated in an integrated circuit and the methods that allow the spread of the heat. Of course, individual devices on a chip generate heat as they are operated. In a 3D circuit, there are multiple layers of devices generating heat. This heat spreads laterally as well as vertically to other layers. The chip package is used to safely dissipate heat to the ambient. This takes place as heat is conducted through the substrate, through a heat spreader, and finally through a heat sink. To calculate temperature, it is necessary to use equations derived from basic heat theory along with the architectural knowledge of a chip and its packaging.

To calculate the localized temperatures for a chip, start with the general heat flow equation given in equation (3.1). The first term is recognized as the heat stored by a device while the second term can be noted as the net flux. The final term is the heat sourced in the device,  $(J_n + J_p)\nabla \varphi$ , and consists predominately of Joule heating. The goal is to transform the differential equation into a lumped heat flow equation to reduce the number of mesh points required because of the order of magnitude difference in the scales of a single device and the entire chip.

$$C\frac{\partial T}{\partial t} = \nabla \cdot (\kappa \nabla T) + H \tag{3.1}$$

The first step in transforming the differential equation is to eliminate the temperature dependency of thermal conductivity  $\kappa$  in order to make the equation linear using Kirchoff's transformation presented in [5] and shown in equation (3.2).

$$\overline{T} = T_o + \frac{1}{\kappa(T_o)} \int_{T_o}^{T} \kappa(\tau) d\tau$$

(3.2)

The linearization begins by taking the gradient of transformed temperature  $\overline{T}$ . Note that  $T_0$  is the ambient temperature and is constant so that  $\nabla T_0 = 0$ . The final gradient of transformed temperature is given in equation (3.3).

$$\nabla \overline{T} = \nabla T_0 + \frac{1}{\kappa(T_0)} \nabla \int_{T_0}^T \kappa(\tau) d\tau$$

$$\nabla \overline{T} = \frac{1}{\kappa(T_0)} \left[ \kappa(T) \nabla T - \kappa(T_0) \nabla T_0 \right]$$

$$\nabla \overline{T} = \frac{1}{\kappa(T_0)} \kappa(T) \nabla T$$

(3.3)

The gradient equation allows substitution of  $\kappa(T_o)\nabla \overline{T}$  for  $\kappa\nabla T$  in the general heat flow equation (3.1) to eliminate the temperature dependency of thermal conductivity  $\kappa$ . The resulting differential heat flow equation is a linear equation in terms of T and  $\overline{T}$ , as seen in equation (3.4).

$$C\frac{\partial T}{\partial t} = \nabla \cdot \kappa (T_o) \nabla \overline{T} + H$$

$$C\frac{\partial T}{\partial t} = \kappa (T_o) \nabla \cdot \nabla \overline{T} + H$$

$$C\frac{\partial T}{\partial t} = \kappa (T_o) \nabla^2 \overline{T} + H$$

(3.4)