#### ABSTRACT

Title of dissertation: Using Locality and Interleaving Information

to Improve Shared Cache Performance

Wanli Liu, Doctor of Philosophy, 2009

Dissertation directed by: Professor Donald Yeung

Department of Electrical and Computer Engineering

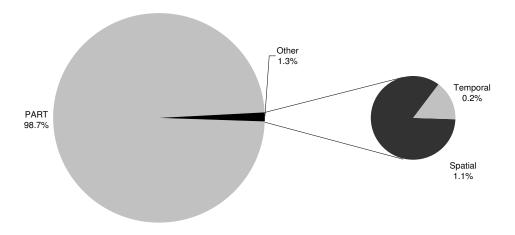

The cache interference is found to play a critical role in optimizing cache allocation among concurrent threads for shared cache. Conventional LRU policy usually works well for low interference workloads, while high cache interference among threads demands explicit allocation regulation, such as cache partitioning. Cache interference is shown to be tied to inter-thread memory reference interleaving granularity: high interference is caused by fine-grain interleaving while low interference is caused coarse-grain interleaving. Profiling of real multi-program workloads shows that cache set mapping and temporal phase result in the variation of interleaving granularity. When memory references from different threads map to disjoint cache sets, or they occur in distinct time windows, they tend to cause little interference due to coarse-grain interleaving. The interleaving granularity measured by runlength in workloads is found to correlate with the preference of cache management policy: fine-grain interleaving workloads perform better with cache partitioning, and coarse-grain interleaving workloads perform better with LRU.

Most existing shared cache management techniques are based on working set

locality analysis. This dissertation studies the shared cache performance by taking both locality and interleaving information into consideration. Oracle algorithm which provides theoretical best performance is investigated to provide insight into how to design a better practical policy. Profiling and analysis of Oracle algorithm lead to the proposal of probabilistic replacement (PR), a novel cache allocation policy. With aggressor threads information learned on-line, PR evicts the bad locality blocks of aggressor threads probabilistically while preserving good locality blocks of non-aggressor threads. PR is shown to be able to adapt to the different interleaving granularities in different sets over time. Its flexibility in tuning eviction probability also improves fairness among thread performance. Evaluation indicates that PR outperforms LRU, UCP, and ideal cache partitioning at moderate hardware cost.

For single program cache management, this dissertation also proposes a novel technique: reuse distance last touch predictor (RD-LTP). RD-LTP is able to capture reuse distance information, which represents the intrinsic memory reference pattern. Based on this improved LT predictor, an MRU LT eviction policy is developed to select the right victim at the presence of incorrect LT prediction. In addition to LT predictor, another predictor: reuse distance predictors (RDPs) is proposed, which is able to predict actual reuse distance values. Compared to various existing cache management techniques, these two novel predictors deliver higher cache performance with higher prediction coverage and accuracy at moderate hardware cost.

## Using Locality and Interleaving Information to Improve Shared Cache Performance

by

## Wanli Liu

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2009

Advisory Committee:

Professor Donald Yeung, Chair/Advisor

Professor Bruce Jacob

Professor Rajeev Barua

Professor Manoj Franklin

Professor Alan Sussman

Professor Steven Tretter

© Copyright by Wanli Liu 2009

## Acknowledgments

I owe my gratitude to all the people who make this thesis possible. I couldn't imagine how I would go through my graduate years without you. First and foremost I'd like to thank my advisor, Professor Donald Yeung for giving me invaluable encouragement and strong support over the past years. He has always made himself available for help and inspiration. It has been a pleasure to work with and learn from such an extraordinary individual.

I would also like to thank Professor Bruce Jacob, Professor Rajeev Barua, Professor Manoj Franklin, Professor Steven Tretter, and Professor Alan Sussman for agreeing to serve on my thesis committee and for sparing their invaluable time reviewing the manuscript.

My colleagues at the System Computer Architecture laboratory have enriched my graduate life in many ways and deserve a special mention. Dongkeun, Seungryul, Gautham, Deepak, Sumit and Hameed helped me jump start my research in the group. Xuanhua, Priyanka, Meng-Ju, Inseok, and Xu gave me wonderful help and discussion. Collaboration and communication with Aamer, Sumesh, Brinda, Zahran, Kursad, David, Sada, Ohm, and other friends are highly appreciated.

My experiences at MIT CSAIL were unforgettable with Michael, David, Ian, Saman, and Anant. Stephen, Janice, Dong-In, Jinwoo, and Karan from ISI east also gave me exceptional help.

Finally, I would like to thank my family. My dear wife Zhongqin has been unconditionally supporting me through my graduate years. I owe my deep thanks

to our parents, whose help is just indispensable. Eric makes my life complete and my study happy and meaningful.

## Table of Contents

| Lis | st of I                             | Figures                                                      | vi |  |  |  |  |

|-----|-------------------------------------|--------------------------------------------------------------|----|--|--|--|--|

| 1   | Intro                               | oduction                                                     | 1  |  |  |  |  |

|     | 1.1                                 | Motivation                                                   | 1  |  |  |  |  |

|     |                                     | 1.1.1 Chip Multi-Processor                                   | 1  |  |  |  |  |

|     |                                     | 1.1.2 CMP Resource Sharing                                   | 2  |  |  |  |  |

|     |                                     | 1.1.3 CMP Shared Resource Management                         | 4  |  |  |  |  |

|     | 1.2                                 | Improving Shared Cache Policy                                | 6  |  |  |  |  |

|     |                                     | 1.2.1 Optimal Shared Cache Management                        | 6  |  |  |  |  |

|     |                                     | 1.2.2 Probability Replacement Policy                         | 8  |  |  |  |  |

|     | 1.3                                 | Contributions                                                | 9  |  |  |  |  |

|     | 1.4                                 | Road Map                                                     | 11 |  |  |  |  |

|     |                                     |                                                              | 1  |  |  |  |  |

| 2   | Rela                                | ated Work                                                    | 13 |  |  |  |  |

|     | 2.1                                 | Memory Locality Characterization and Application             |    |  |  |  |  |

|     | 2.2                                 | Shared Cache in Multithreaded Workloads                      | 17 |  |  |  |  |

| 3   | Bacl                                | kground and Methodology                                      | 22 |  |  |  |  |

|     | 3.1                                 | y .                                                          |    |  |  |  |  |

|     | 3.2                                 | Interleaving                                                 |    |  |  |  |  |

|     |                                     | 3.2.1 Interleaving Granularity                               | 26 |  |  |  |  |

|     |                                     | 3.2.2 Sensitivity of Interleaving Granularity                | 29 |  |  |  |  |

|     |                                     | 3.2.3 Impact of Interleaving on Performance                  | 30 |  |  |  |  |

|     | 3.3                                 | Characterizing Multithreaded Workloads                       | 32 |  |  |  |  |

|     |                                     | 3.3.1 Case Study                                             | 33 |  |  |  |  |

|     | 3.4                                 | Methodology                                                  | 35 |  |  |  |  |

| 4   | Shared Cache Performance Analysis 4 |                                                              |    |  |  |  |  |

|     | 4.1                                 | Oracle Management Policy                                     | 40 |  |  |  |  |

|     |                                     | 4.1.1 Oracle Management Performance                          | 42 |  |  |  |  |

|     |                                     | 4.1.2 Comparing LRU with the Oracle Algorithm                | 43 |  |  |  |  |

|     |                                     | 4.1.3 Comparing PART with Oracle Algorithm                   | 45 |  |  |  |  |

|     | 4.2                                 | Characterizing Oracle Algorithm Behavior                     | 51 |  |  |  |  |

|     |                                     | 4.2.1 Advantages of Oracle Algorithm Behavior                | 51 |  |  |  |  |

|     |                                     | 4.2.2 Quantitative Profiling of Oracle Algorithm Behavior    | 52 |  |  |  |  |

|     |                                     | 4.2.3 Aggressor Eviction Bias in Oracle Algorithm            | 57 |  |  |  |  |

| 5   | Agg                                 | ressor Eviction Algorithm                                    | 60 |  |  |  |  |

|     | 5.1                                 | Using Aggressor Information in Victim Selection              | 60 |  |  |  |  |

|     | 5.2                                 | General Aggressor-Eviction Algorithm                         | 63 |  |  |  |  |

|     | 5.3                                 | Comparing Aggressor-Eviction Algorithm to Cache Partitioning | 64 |  |  |  |  |

|     | 5.4                                 | Aggressor-Eviction Algorithm Analysis with Interleaving      | 66 |  |  |  |  |

|     |                                     |                                                              | _  |  |  |  |  |

| 6  | Prol                                             | oabilisti                                             | ic Replacement Policy               | 70  |  |  |  |  |  |

|----|--------------------------------------------------|-------------------------------------------------------|-------------------------------------|-----|--|--|--|--|--|

|    | 6.1                                              | Proba                                                 | bility Replacement Ratios           | 71  |  |  |  |  |  |

|    | 6.2                                              | Online Sampling and Learning of Aggressor Information |                                     |     |  |  |  |  |  |

|    | 6.3                                              | B Hardware Cost                                       |                                     |     |  |  |  |  |  |

|    | 6.4                                              | Perfor                                                | mance Evaluation                    | 80  |  |  |  |  |  |

| 7  | Reuse Distance Based LTP-Driven Cache Management |                                                       |                                     |     |  |  |  |  |  |

|    | 7.1                                              | 1 Introduction of Last Touch Prediction               |                                     |     |  |  |  |  |  |

|    | 7.2                                              | Relate                                                | ed Work                             | 89  |  |  |  |  |  |

|    | 7.3                                              | Predic                                                | eting Last Touch References         | 92  |  |  |  |  |  |

|    |                                                  | 7.3.1                                                 | Global Reuse Distance History       | 93  |  |  |  |  |  |

|    |                                                  | 7.3.2                                                 | Motivating Example                  | 94  |  |  |  |  |  |

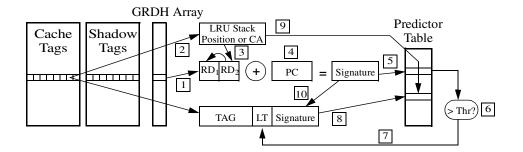

|    |                                                  | 7.3.3                                                 | Predictor Hardware                  | 97  |  |  |  |  |  |

|    |                                                  | 7.3.4                                                 | LNO vs OPT Last Touches             | 99  |  |  |  |  |  |

|    | 7.4                                              | Experimental Methodology                              |                                     |     |  |  |  |  |  |

|    | 7.5                                              | .5 Last Touch Prediction Results                      |                                     |     |  |  |  |  |  |

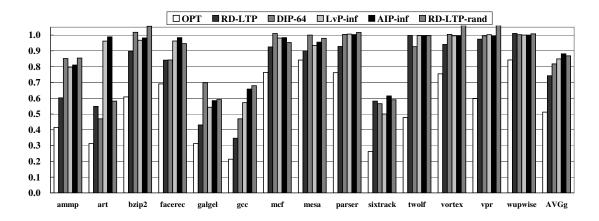

|    |                                                  | 7.5.1                                                 | LTP and Insertion Policy Evaluation | 105 |  |  |  |  |  |

|    |                                                  | 7.5.2                                                 | Cache Organization Evaluation       | 107 |  |  |  |  |  |

|    |                                                  | 7.5.3                                                 | Prediction Rate                     |     |  |  |  |  |  |

|    |                                                  | 7.5.4                                                 | Victim Selection                    |     |  |  |  |  |  |

|    | 7.6                                              | Reuse                                                 | Distance Prediction Results         | 116 |  |  |  |  |  |

| 8  | Con                                              | clusion                                               |                                     | 119 |  |  |  |  |  |

|    | 8.1                                              | Summ                                                  | nary                                | 119 |  |  |  |  |  |

|    | 8.2                                              | Future Directions                                     |                                     |     |  |  |  |  |  |

| Bi | bliogi                                           | raphy                                                 |                                     | 122 |  |  |  |  |  |

# List of Figures

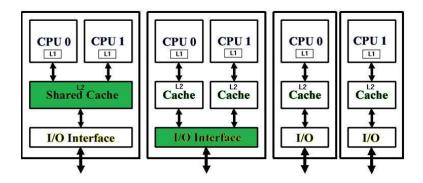

| 1.1  | Resource sharing in multi-threaded architectures                                                                                                      | 3  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

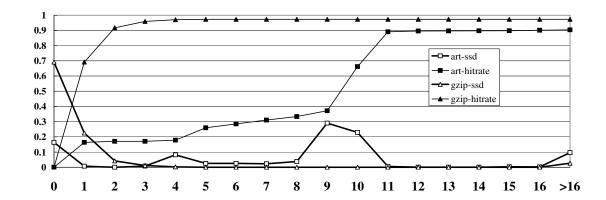

| 3.1  | Singlethreaded stack distance distribution, and cache hit rate as a function of cache associativity                                                   | 25 |

| 3.2  | Fine-grain and Coarse-grain interleaving                                                                                                              | 27 |

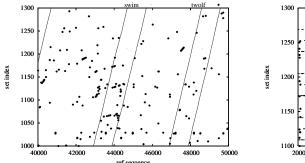

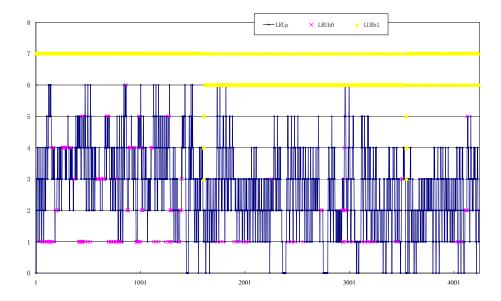

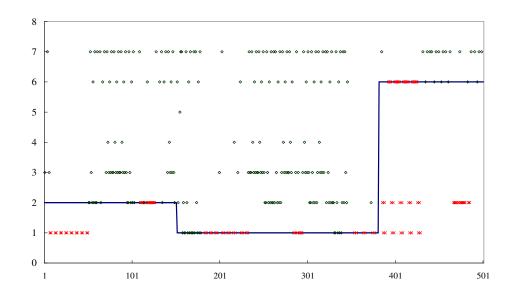

| 3.3  | Fine-grain interleaving pattern for the swim-twolf workload                                                                                           | 28 |

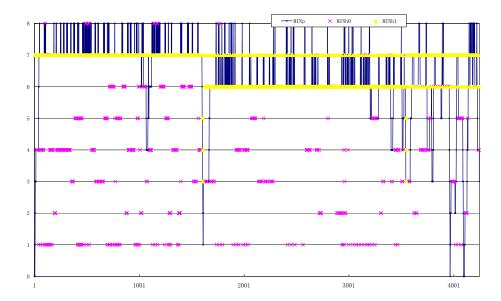

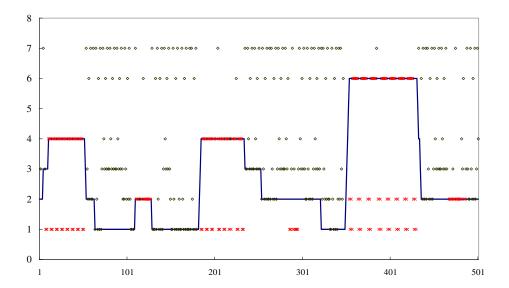

| 3.4  | Coarse-grain interleaving pattern for the apsi-gcc workload                                                                                           | 28 |

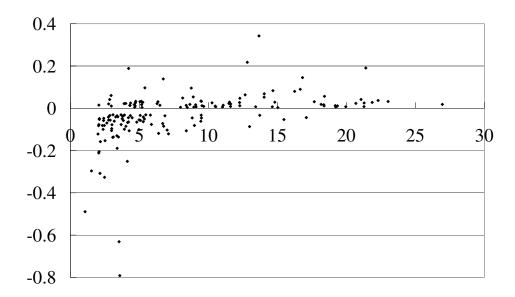

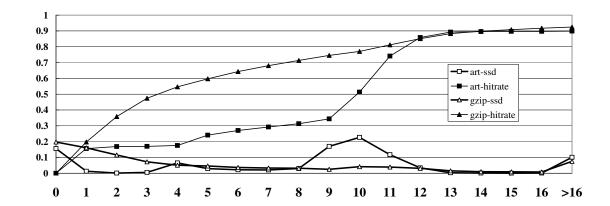

| 3.5  | Cache performance comparison of LRU and iPART over different interleaving granularities (average runlength)                                           | 31 |

| 3.6  | Multithreaded stack distance distribution, and cache hit rate as a function of cache associativity                                                    | 34 |

| 4.1  | Oracle management policy for multiple threads                                                                                                         | 41 |

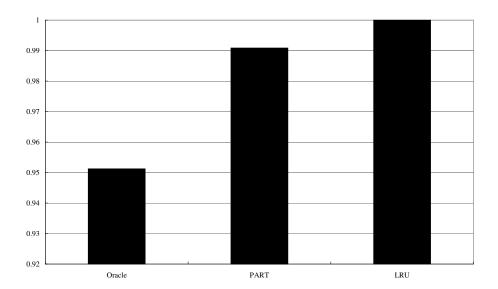

| 4.2  | Average miss rates achieved by the Oracle management policy, PART, and LRU                                                                            | 42 |

| 4.3  | Cache partitioning with exhaustive searching                                                                                                          | 43 |

| 4.4  | LRU policy behavior in ammp-swim workload: line (cache capacity division), crosses (hits of ammp), triangles (hits of swim)                           | 45 |

| 4.5  | The Oracle algorithm behavior in ammp-swim workload: line (cache capacity division), crosses (hits of ammp), triangles (hits of swim)                 | 46 |

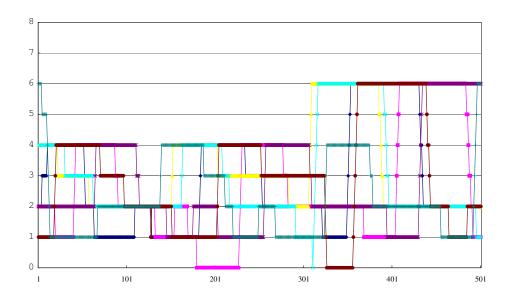

| 4.6  | Cache division lines for 7 different sets in apsi-gcc workload                                                                                        | 47 |

| 4.7  | Cache performance breakdown between PART and Oracle algorithms                                                                                        | 48 |

| 4.8  | UMON partitioning behavior in apsi-gcc workload: line (cache capacity division), crosses (hits of apsi), diamonds (hits of gcc)                       | 50 |

| 4.9  | The Oracle algorithm behavior in apsi-gcc workload: line (cache capacity division), crosses (hits of apsi), diamonds (hits of gcc)                    | 50 |

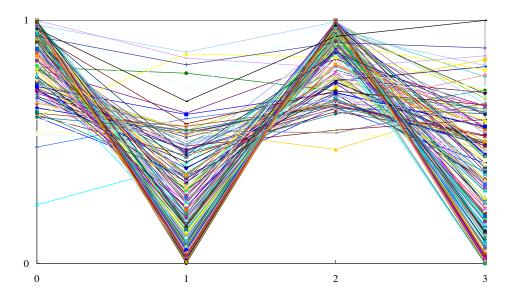

| 4.10 | The percentage of LRU victim choice matching the Oracle victim choice for 4 event categories (0: $E_{00}$ ; 1: $E_{01}$ ; 2: $E_{10}$ ; 3: $E_{11}$ ) | 56 |

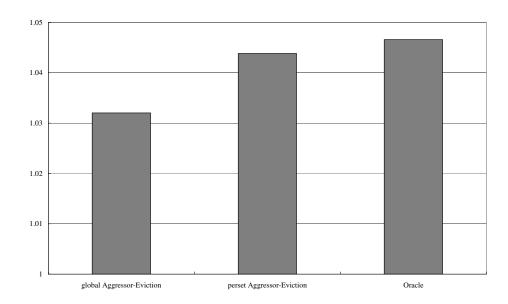

| 5.1 | eviction with the Oracle algorithm (normalized to LRU hit rate)                                                                                                                                                                                                                                                                          | 63 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

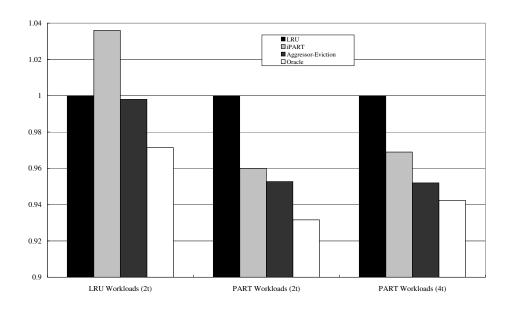

| 5.2 | Cache performance (miss rate) comparison for LRU, iPART and the Oracle in workloads preferring LRU or partitioning (normalized to LRU miss rate)                                                                                                                                                                                         | 65 |

| 5.3 | Cache performance (hit rate) comparison for LRU, iPART and the Aggressor-Eviction in workloads preferring LRU or partitioning (normalized to Oracle hit rate)                                                                                                                                                                            | 67 |

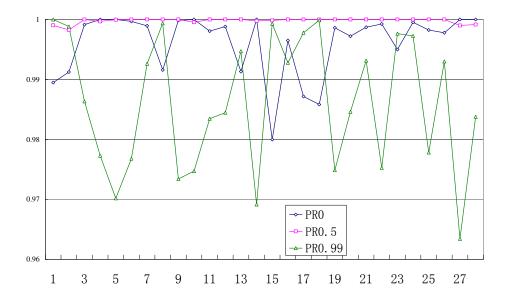

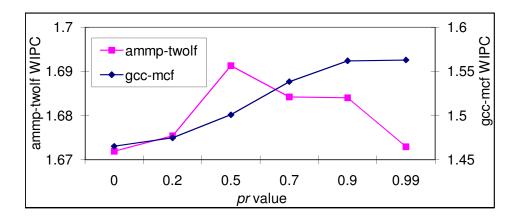

| 6.1 | Performance (weighted IPC) per epoch comparison of different Probability Ratios in ammp-twolf workload (normalized to the highest performance for each epoch)                                                                                                                                                                            | 72 |

| 6.2 | Performance (WIPC) as function of different $pr$ values for two typical workloads                                                                                                                                                                                                                                                        | 73 |

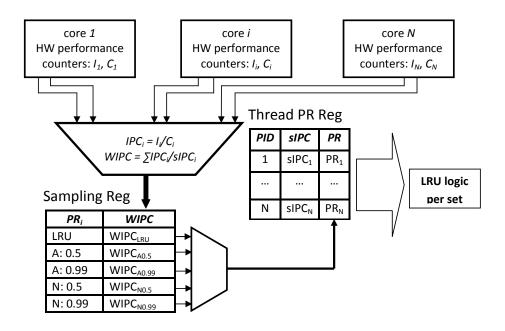

| 6.3 | Online sampling algorithm for detecting aggressor threads and testing $pr$ value for each thread                                                                                                                                                                                                                                         | 76 |

| 6.4 | PR central control hardware                                                                                                                                                                                                                                                                                                              | 79 |

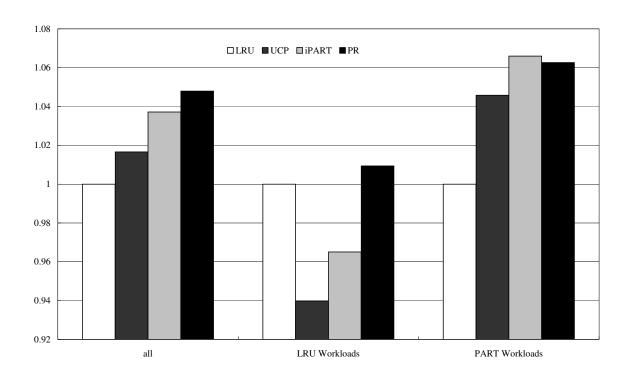

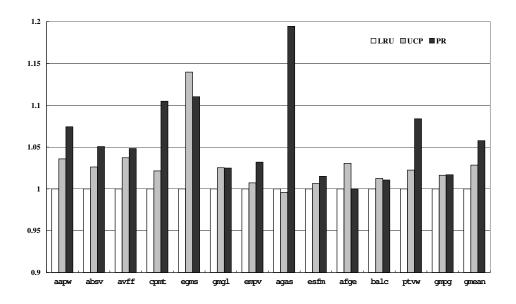

| 6.5 | Comparison of PR and iPART on 2-program workloads                                                                                                                                                                                                                                                                                        | 81 |

| 6.6 | Comparison of PR, UCP and iPART on our 2-program workloads (normalized to LRU performance)                                                                                                                                                                                                                                               | 82 |

| 6.7 | Comparison of PR, UCP and iPART on 4-program workloads (normalized to LRU performance)                                                                                                                                                                                                                                                   | 84 |

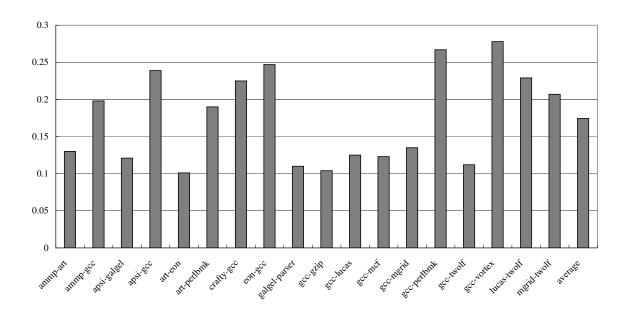

| 6.8 | PR's performance advantage over UCP on 2-program workloads (with larger than $10\%$ performance advantage)                                                                                                                                                                                                                               | 86 |

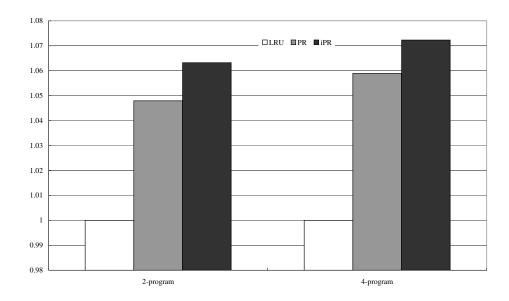

| 6.9 | Comparison of PR and iPR on 2-program and 4-program workloads (normalized to LRU performance)                                                                                                                                                                                                                                            | 87 |

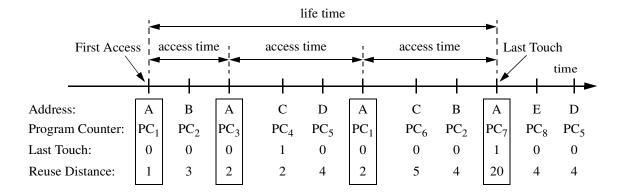

| 7.1 | A memory address trace, and various information associated with the trace used to predict last touch and/or reuse distance. Information includes memory addresses, memory reference program counters, last touch history, and reuse distance. Access and live times are indicated for a sequence of references to the memory address $A$ | 91 |

| 7.2 | Memory reference pattern from the ART benchmark                                                                                                                                                                                                                                                                                          | 94 |

| 7.3  | Reuse distance last touch predictor organization and actions. Steps 1–7 perform a prediction. Steps 8–10 update the predictor 97                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

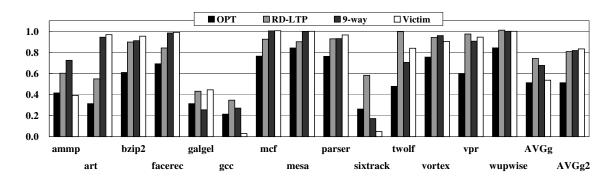

| 7.4  | Cache miss rates for the high potential benchmarks achieved by OPT, RD-LTP, DIP, LvP, AIP, and RD-LTP-Rand. All of the miss rates are normalized to the LRU miss rate                            |

| 7.5  | Cache miss rates for the high potential benchmarks achieved by OPT, RD-LTP, 9-way cache, and victim cache. All of the miss rates are normalized to the LRU miss rate                             |

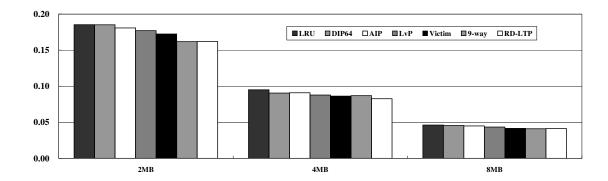

| 7.6  | Average cache miss rates for different cache sizes achieved by LRU, 9-way, victim cache, LvP, AIP, DIP, and RD-LTP. All of the miss rates are normalized to the LRU miss rate for 1 MB cache 109 |

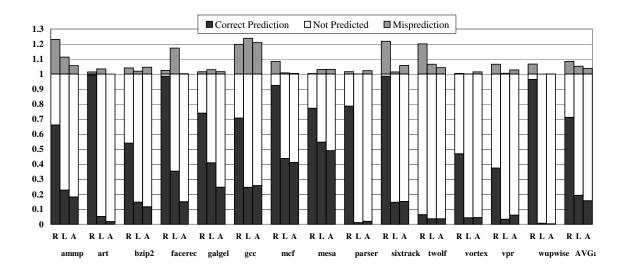

| 7.7  | Prediction accuracy of RD-LTP, LvP, and AIP                                                                                                                                                      |

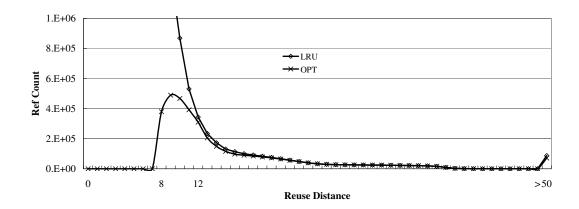

| 7.8  | Last touch reference histograms under LRU and OPT cache management for the AMMP benchmark. $CRD=12.\ldots 113$                                                                                   |

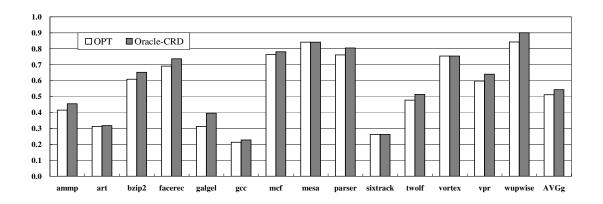

| 7.9  | Cache misses under the OPT and Oracle-CRD policies                                                                                                                                               |

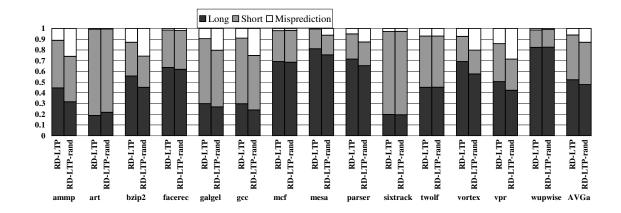

| 7.10 | Breakdown of the evictions performed by the RD-LTP and RD-LTP-Rand techniques                                                                                                                    |

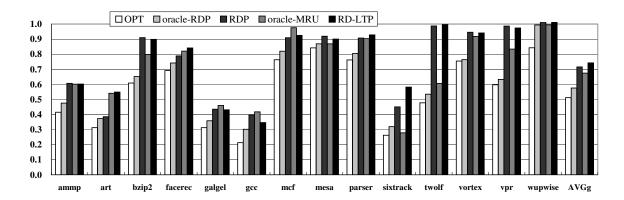

| 7.11 | Cache miss rates achieved by OPT, Oracle-RDP, RDP, Oracle-MRU, and RD-LTP for the high potential benchmarks                                                                                      |

## Chapter 1

#### Introduction

#### 1.1 Motivation

## 1.1.1 Chip Multi-Processor

While the industry continues to improve the performance of both processor and memory systems, the *processor-memory gap*, a disparity between processor and memory speed, keeps increasing, and is now one of the main obstacles to high performance. Hennessy and Patterson [1] predict the gap will grow wider in the future, which is also shown by the state-of-the-art industry products.

Recent commercial architectures rely on a memory hierarchy to alleviate the memory bottleneck. A modern memory system consists of register files, multiple levels of cache, main memory and disk. The first level L1 cache is usually built on chip, in the closest location to the processor pipeline among all levels of cache. Since the access time for L1 cache is only a couple of CPU cycles, this latency can be effectively hidden through out-of-order execution and lock-up free caches. The second level L2 cache has larger capacity but longer latency than L1 cache. More recent processors choose to build the L2 cache on chip to minimize access time, and have an off-chip L3 cache to buffer data between the on-chip processor and main memory. Since the behavior of the memory hierarchy below L1 cache is less affected

by pipeline design, the DRAM latency in the range of hundreds of cycles cannot be totally tolerated. Previous research shows that a significant amount of CPU stall time is spent on L2 cache misses [2].

On the other hand, Moore's law remains valid as industry projects to integrate 10Billion transistors by 2010<sup>1</sup>. Both industry (DEC Piranha, Sun Niagara, IBM Cell, Intel 80-core processor) and academia (MIT Raw, Univ. of Texas Trips, Univ. of Washington WaveScalar) are actively looking for solutions for translating higher integration density to higher microprocessor performance. In addition to traditional superscalar architecture, two alternatives have been proposed: simultaneous multithreading (SMT) [3] and chip multiprocessor (CMP) [4]. Single thread in superscalar architecture can only offer diminishing returns due to limited parallelism which can only be extracted with prohibitive complexity and power cost. Unlike the superscalar architecture which only exploits instruction-level parallelism, SMT and CMP can also take advantage of thread-level parallelism and process-level parallelism, which are exposed by compiler and OS scheduler.

## 1.1.2 CMP Resource Sharing

Multithreaded architectures, such SMT and CMP, permit sharing of hardware resources, including the memory hierarchy. In particular, how threads share the memory system affects the processor-memory gap. The SMT architecture permits the greatest degree of sharing by allowing all threads to have access to the processor pipeline, and memory hierarchy. This design usually results in more efficient utiliza-

<sup>&</sup>lt;sup>1</sup>http://www.intel.com/technology/mooreslaw

Figure 1.1: Resource sharing in multi-threaded architectures.

tion of processor resources when single thread can be allocated most of the shared resources while the remaining concurrent threads demand little shared resources [5]. However, due to layout and implementation complexity suffered by the wide-issue SMT processor, CMPs are expected to deliver higher throughput with better scalability [6]. Therefore, this dissertation will focus on CMP architectures although some of the techniques presented may also be applicable for SMT architectures.

In CMPs, individual cores usually share some portion of the memory system which are often lower levels of the memory hierarchy (there exists some exceptional design, such as the MIT Raw architecture [7] which provides register-level communication channels between cores). Figure 1.1 shows three sharing strategies for CMP architectures.

The first sharing architecture allows individual cores to have their own private L1 caches which are located close to the cores and provide fast access. These private L1 caches are connected to a globally shared L2 cache (or L3 cache which is the last level of on-chip cache) through a fast on-chip interconnect. The private L1 caches also share the underlying I/O interface. Many commercially available products, for example the Intel Duo Core, are built around such a design.

In the second sharing architecture, individual cores have both private L1 and private L2 caches. Such processors as the AMD Athlon Dual-Core takes advantage of fast on-chip inter-core communication and relies on shared high-speed I/O bandwidth to provide memory access to the threads. Compared to the previous shared cache architecture, the private L1 and L2 cache architecture provides less flexibility in sharing the important on-chip cache capacity among cores.

The third sharing architecture is adopted in traditional SMP's (symmetric multiprocessing) which rely on off-chip network and memory to connect individual single-cores with private L1 and L2 caches. The communication in such processors occurs completely off-chip and therefore suffers from high communication latency. This architecture also suffers from the zero-cache-sharing problem since the L1 and L2 caches are private.

Among the three types of sharing architectures, the first and second designs are more popular since they provide faster on-chip inter-core communication which is the key to better performance for multi-threaded applications. The shared L2 cache design is more appealing than the private L2 cache design due to more flexibility in sharing the highly critical L2 cache capacity. This dissertation will study the shared on-chip L2 cache for CMP architectures.

## 1.1.3 CMP Shared Resource Management

Although sharing cache capacity among cores enables higher utilization of resources, multiple threads sharing the memory system may sometimes have negative consequences for the following reasons. First, parallel architectures implementing high performance through multiple levels of parallelism also put more pressure on memory latency and capacity. The total working set of multiple threads scales up with the number of threads. This requires larger caches, wider buses and higher bandwidth of both on-chip and off-chip communication, and results in high miss rate, long average access time, high hardware complexity and power consumption. Second, stretched memory systems limit the ability of multithreaded architectures to maximize the total overall IPC because more cycles will be wasted waiting for cache misses. Third, multiple concurrent threads compete for the limited shared cache capacity, and when the total available resources cannot satisfy all the competing threads, there will be winners and losers, which suffer differently from unfair allocation. Therefore, in multithreaded execution, more parallelism is exposed but may not be exploited effectively due to the memory system, and sensible management schemes are necessary to improve both utilization and fairness of cache sharing.

Several policies to manage the shared cache among threads have been studied. The simplest policy is LRU sharing, allowing all threads to compete for shared cache freely. Many policies directly manage the number of cache blocks to be allocated to individual threads by partitioning the whole cache along different dimensions [8].

Most of these techniques try to allocate cache capacity to individual threads based on their working set sizes by assigning ways or sets to a particular thread. While these techniques have had success in managing shared cache, one common problem is that the allocation decision is mostly based on the measurement of individual thread's locality without taking into consideration the fine grain interaction

among references from all threads. As shown by the analysis of interaction among threads, various interleaving granularities across sets often lead to non-uniform optimal capacity allocation in different sets. Therefore locality information of individual threads alone results in conservative cache management policies because the interleaving information is not considered in the cache management.

## 1.2 Improving Shared Cache Policy

## 1.2.1 Optimal Shared Cache Management

Researchers have been successful in analyzing reference trace to study cache management policies for one thread. A particularly insightful exercise is to study optimally managing cache resources with oracle information [9]. Other realistic online policies can also be evaluated using traces since the intra-thread reference sequence is maintained under various policies. However, it is more complicated to study cache shared by multiple threads than single thread cache, because the inter-thread order of references is subject to the cache management policy applied. Different policies have varied impacts on single thread performance, hence the relative progress variation of individual threads will change the hashing of references from those threads.

Nevertheless, a trace analysis with oracle information is still desired to provide insight into how a better online management policy should behave and how much improvement is possible to achieve over existing policies. To enable such analysis, an important assumption is proposed in this dissertation that the inter-thread reference order is maintained under any management policy in question. With this assumption, various shared cache management ideas can be tested and compared with one another based on common traces.

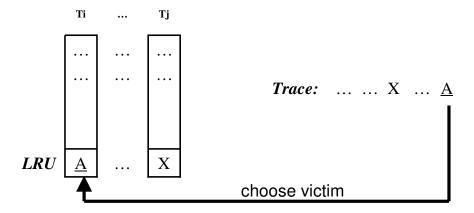

The first policy studied with this assumption is called Optimal Management Policy for Multi-threading (OPTm). Since the goal of this research is to propose a realistic policy, the OPTm algorithm tries to manage the inter-thread conflict with future information while maintaining realistic policy (basic policy) for managing intra-thread references. The basic policy is LRU in this research, since it is a popular policy selection in both academic and industry communities. OPTm policy looks at all the victim candidates of the lists of cache blocks from all the threads in the cache, and uses future information to select the victim candidate with the furthest reuse for replacement. The critical part of OPTm algorithm is to compare the future reuse distances of victim candidates from different threads. The future reuse distance of a reference in a multi-threaded trace is determined by two factors: its intra-thread reuse distance, and interleaved references from other threads. The evaluation of OPTm algorithm shows that there is still room for improvement, which provides motivation for this research.

The success of OPTm algorithm results from two major reasons. One apparent reason is the knowledge of future information. The second one is the consideration of both locality and interleaving. This reason is rather important because it sheds light on the key to further improvement. Existing cache allocation policies base their management decisions on locality information for individual threads. Interleaving information is ignored in such policies. Although some policies [10, 8] try to provide more flexibility into rigid cache capacity allocation, the full potential for improve-

ment cannot be fulfilled without explicitly taking thread interleaving into account. In this dissertation, a new technique called Probability Replacement (PR) is proposed to take advantage of some key observations made in analyzing the behavior of OPTm algorithm,

#### 1.2.2 Probability Replacement Policy

The analysis of OPTm algorithm reveals that it is possible to improve shared cache management by taking thread interleaving into consideration. To take advantage of the potential made possible by considering thread interleaving, some key observations from OPTm algorithm must be understood. The first observation is that in OPTm algorithm, for each set, the boundaries between threads are fluid. In other words, the allocation-based policies enforce unnecessary rigid boundary, which prevents threads from benefiting from transient locality variation. The second observation is that OPTm algorithm looks at victim candidates from all the sharing threads, and selects the one with furthest reuse. Profiling the behavior of the OPTm algorithm indicates that in many cases OPTm has strong bias in selecting optimal candidate based on thread ID of missing thread and the primary candidate (the block at global LRU position). The third observation is that OPTm algorithm often behaves like LRU when the interleaving is coarse-grained.

Based on these observations, a new shared cache management technique, *Probability Replacement*(PR), is proposed in this dissertation. PR is an LRU-style policy, with additional rate control knobs to manage the rate of replacements in shared

cache. The rate control knob is a probability by which the policy determines which victim block to evict based on the ID's of missing thread and victim candidate blocks. The values of the knob probability are learned from sampling epochs and applied till different phase is detected. This online learning algorithm enables the hardware to adapt to the phase variation of multi-threaded workload. The evaluation of this technique shows that it is capable of managing shared cache more efficiently than previously proposed techniques.

#### 1.3 Contributions

This dissertation makes the following contributions.

Studying Shared Cache Management Problem as a Locality-Interleaving Problem

The reference trace in multi-threaded workload is the aftermath of interleaved traces from individual threads. Due to the chaotic nature of program behavior, the interleaving is highly irregular and random, hence hard to study. Previous research try to eliminate the effect of interleaving by focusing on locality per-thread. However, this approach cannot achieve high utilization of shared resources. This dissertation suggests that the interleaving factor is equally important and provides opportunities for further improvement.

Development of Trace Analysis Tool to Study both Thread Locality and Thread

Interleaving

The high irregularity and randomness of thread interleaving prevents researchers

from thoroughly studying the multi-threaded workload. The conventional approach is to separate interleaving from locality information, and use locality per-thread only to manage shared resources. This dissertation proposes to analyze interleaved traces with the awareness that locality interacts with interleaving. Instead of isolating locality from interleaving, new analysis methodology treats interleaved trace in its entirety, which minimizes loss of valuable information as for how multiple threads interact with one another.

Qualitative and Quantitative Analysis of OPTm Algorithm Behavior to Explore

Design and Performance Space for Multi-threaded Cache

The assumption that the interleaved trace remains the same under different management policies enables feasible analysis framework to evaluate different policies on the same trace. Although accuracy is sacrificed, the benefit of ease and key observations makes it a desirable approach to study multi-threaded workloads. Experiments based on this assumption shows its effectiveness and validity in revealing insights into how multiple threads interact with one another and directing the design of realistic online management techniques.

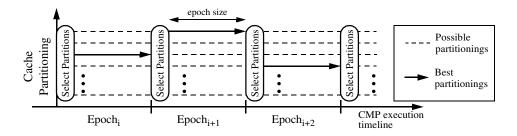

Design of Probabilistic Replacement Policy

Based on the knowledge acquired through multi-thread trace, a novel shared cache management policy is proposed. This policy is able to adapt to the dynamic interleaving of threads with different locality. An important portion of the PR policy is the epoch-based online learning of best control ratios, which tracks the phase variation of program behavior and feeds back to control logic. The implementation uses global control ratios to manage threads in all sets, minimizing hardware cost.

Evaluation of Probabilistic Replacement Policy and Comparison with Other Techniques

A faithful evaluation of the performance of probabilistic replacement policy is conducted across a large number of two-program workloads and a number of four-program workloads as well. A group of other allocation based techniques are also evaluated and compared against PR policy qualitatively and quantitatively. The experiment results show that PR policy outperforms LRU and UCP, a recent cache partitioning technique, by about 5% and 3%, respectively.

Design and Evaluation of Reuse Distance based Last Touch Predictor

In addition to the topic on the shared cache for multi-program workloads, the cache management for single-program is also studied. A reuse-distance based last touch predictor is proposed to improve cache performance for single programs. The reuse-distance information is employed to increase both prediction coverage and accuracy, resulting in lower miss rate at cheaper hardware cost, compared to other existing last touch predictors.

## 1.4 Road Map

The remainder of this proposal is organized as follows. Chapter 2 discusses related work, followed by background and methodology in Chapter 3. Chapter 4 profiles and analyzes the run-time behavior of multi-threaded cache with various management techniques, particularly the Oracle management algorithm. Based on this analysis, Chapter 5 proposes new cache management algorithm: victim eviction.

Probabilistic replacement, a practical online management technique is developed based on victim eviction in Chapter 6, and it is evaluated and compared to other existing techniques. Chapter 7 reports reuse distance information based last touch predictor for single program cache management. Finally, Chapter 8 concludes the dissertation and suggests future directions.

## Chapter 2

#### Related Work

This chapter surveys background material and related work on memory systems. First, it introduces some historical work on the general locality and cache study. It then focuses on some research work on cache management policies and their application in multithreaded execution. Much attention is paid to recent developments in multithreaded cache, such as cache partitioning, locality optimization, capacity allocation, etc.

## 2.1 Memory Locality Characterization and Application

#### Characterizing Locality

As the speed gap between the processor and memory system widens, caches became an important component of computing system in mid 60's, 20th century [11]. The cache organization parameters: capacity, associativity and block size, and their impact on cache performance are studied by Smith [12]. Three cache miss categories are defined by Hill [13] as compulsory misses, capacity misses, and conflict misses. Puzak [14] conducted analysis on cache replacement policies to improve cache utilization with shadow tags.

Another aspect of memory study has been driven by workload characterization, such as control flow, instruction level parallelism, memory locality, and basic block behavior. Characterizing the intrinsic quality of application motivates new architectural features and provides insight for explaining performance measurement/simulations. As one important form of program characterization, locality analysis has been the focus of memory research. Early efforts sought to manage page storage and transfer to improve virtual memory system performance [15]. In [9], the theoretical optimum OPT algorithm was proposed to set up the upper bound limit for replacement policy, and concluded LRU (least recently used) replacement is practically a good choice. Denning [16] proposed working set model and defined working set as the set of pages used during a fixed-length sampling window in the past, and suggested working set be measured by monitoring page footprint. Later Denning [17] defined locality using virtual time distance, and suggested three meanings of distance: temporal, spatial and cost.

Some researchers [18] proposed representations of locality in terms of probability density, which can be used to predict and tune cache performance. Instead of using probabilistic model, other researchers [19, 20, 21] used analytical cache modeling to capture locality based on cache models specified with parameters.

Improve Memory Performance with Locality

The principle of locality has wide application in virtual memory, cache, I/O buffer, network interface, video processing, web caching, and search engine. The scope of this literature survey will be focused on cache management. To solve the widening processor-memory gap, many researchers work to improve cache performance through hardware, software, or hybrid solutions.

Hardware solutions have the advantage of exploiting runtime information to

improve hit rate and save power consumption.

Column-associative caches [22] improve direct-mapped cache performance by placing conflicting cache blocks through rehashing. Hardware called *locality pre*diction table is proposed in [23] to detect different types of locality. The victim cache [24] stores replaced data in a small fully-associative buffer to convert some references with reuse distances slightly larger than what the main cache can allow into additional cache hits. A small fully associative cache is proposed in [25] to bypass references with bad temporal locality and prevent them from polluting cache. Johnson, Merten, and Hwu [26] use Spatial Locality Detection Table to capture the spatial locality variation and dynamically adjust cache block sizes to reduce both capacity and conflict misses. This proposal is particularly indebted to the work of run-time cache bypassing [27] for motivation of using bypassing techniques to optimize locality quality. Line distillation [28] also detects low spatial locality of the less recent part of the LRU stack and retains the used words while evicting the unused words. Hardware history tables for last touch prediction are employed by Lai and Falsafi [29, 30] for self-invalidating dead block in advance for distributed shared memory coherence protocol, as well as for improving cache prefetching. Locality in the form of generational behavior can help to reduce cache leakage power by turning off dead cache lines [31].

Cache replacement policy is a heavily investigated topic. Some researchers try to bring access frequency into replacement policies [32, 33, 34]. Guo and Solihin [35] use an analytical model to explain the performance variation of different replacement policies. In [36], locality is approximated by the combination of access frequency and

block age to choose victim to evict. Wong and Baer [37] propose both profile-based scheme and on-line locality table to detect temporal locality and direct replacement policy to retain those cache lines exhibiting strong temporal locality. The v-way cache [38] observes the non-uniform distribution of access frequencies across cache sets and vary associativity on a per-set basis to match the different locality levels in different sets. With replacement policy divided into victim selection and insertion policy, adaptive insertion policies [39] places the incoming line in the LRU position to avoid thrashing in cyclic reference pattern. Cache replacement policies based on last touch prediction [40, 41, 42] provide hardware tables to track reference behavior and predict last touches to enable early eviction replacement.

Since memory locality is an intrinsic property of programs, compiler and operating system can be particularly helpful in detecting locality at source code level and managing cache organization in more flexible way at small or little hardware overhead. Hallnor and Reinhardt [43] use software to manage a fully associative L2 cache, which is called indirect index cache (IIC) with generational replacement policy. This software replacement policy outperforms a set-associative cache using LRU policy by exploiting the ability of fully associative cache to take advantage of temporal locality. Compiler [44] can also play an important role in locality analysis at source code level providing victim selection hints to hardware replacement.

Pretching has been proven to be an effective technique to reduce cache misses. Special hardwares are proposed to facilitate cache prefetching [45, 46, 47, 48, 49]. Compiler can also analyze the program access pattern and predict the block addresses before their real references. As a result, prefetching instructions can be

inserted into program by compiler [50, 51]. A similar technique taking advantage of memory level parallelism to improve cache efficience is runahead execution [52], which can be supported in both hardware [53] and compiler [54].

More detail about related work on locality optimization can be found in Section 7.2.

#### 2.2 Shared Cache in Multithreaded Workloads

#### Multithreaded Workloads

When SMT and CMP became the focus of architectural research, people started to study memory behavior in parallel execution by characterizing access pattern [55, 56, 57] and developing analytic model [58]. The benchmarks under study include SPEC2000 suite [59], server workloads [60], bioinformatics benchmarks [61], SPEC OMP suite [62], and SPECjbb [10]. Single-threaded benchmarks are usually grouped together to compose multi-program workload, in which there is zero overlap among the working sets of individual programs. Parallel programs, on the other hand, represent more complicated situations because different thread working sets have both private portion and shared portion. This dissertation is focused on the multi-program workloads.

Evaluation Metric, Performance Target and Management Policy

In [60], shared cache management is described in some important aspects: evaluation metrics, performance targets and management policies. Evaluation matrix are some measurement methods to quantify the performance of multiple threads

based on IPC or miss rate. Compared to measuring performance based on miss rate, IPC based evaluation is more frequently adopted in research because it is closely connected with execution time. Three IPC-based metrics are proposed: average IPC, average weighted IPC [63], and harmonic mean of weighted IPC [64].  $IPC_i$  is the IPC of single thread when N threads are executed simultaneously, while  $SingleIPC_i$  is the IPC of that thread when it is executed without sharing the cache capacity with other threads.

$$AverageIPC = \frac{\sum_{1}^{N} IPC_{i}}{N}$$

(2.1)

$$AverageWeightedIPC = \frac{\sum_{1}^{N} \frac{IPC_{i}}{SingleIPC_{i}}}{N}$$

(2.2)

$$HarmonicMeanWeightedIPC = \frac{N}{\sum_{1}^{N} \frac{SingleIPC_{i}}{IPC_{i}}}$$

(2.3)

Among the three metrics, average weighted IPC and harmonic mean of weighted IPC reveal more about system-level performance by considering relative performance variation due to sharing resources. This relative effect on individual thread performance is quantified as fairness [64, 65], and employed as an important target for optimization of overall throughput. With equal priority set for each individual thread, average weighted IPC has been a popular metric used by many researchers. In this dissertation, the optimization target is to maximize average weighted IPC for multi-program workloads.

The specific technique to reach the optimization target is called the man-

agement policy. A simple solution is to inherit cache policies from conventional single-threaded cache, such as LRU. This policy treats all references as if they are from the same program. Unfortunately, this simplest approach does not work well, and researchers found that some regulation is necessary when competition happens and results in unfair allocation among threads. To better manage the competition for shared resources, a number of management techniques are developed.

Static and Dynamic Cache Partitioning Policies

In an early study [66], an optimal static partitioning algorithm of shared memory for multiple programs with miss rate variation outperforms LRU policy. Profiling information determines the static splitting of L2 cache in [62], which outperforms both private L2 and address-interleaved shared L2 caches.

Since programs exhibit phase behavior during their execution, static partitioning cannot adjust to the variation of multiple competing programs. Suh et al. [59, 67] employ on-line miss rate characterization and dynamic variation of partition size to improve overall hit-rate of L2 cache. Chiou et al. [68] use software to dynamically partition cache with the awareness of constructive and destructive interference, which lead to better overall performance. Qureshi et al. [69] define the utility function of program and optimize global miss rate with online utility monitoring technique, and they use this UMON mechanism to implement utility-based cache partitioning (UCP). This technique is selected as a typical practical cache partitioning technique to compare in this dissertation. Improving overall performance alone does not completely solve the problem of fairness, which is addressed by [70] with the notion of fair cache sharing and partitioning. Jaleel et al. [71] change the

insertion policy to adaptively control the portions of individual thread working sets to be resident in cache.

Conventional cache partitioning algorithms assign allocations in sets, while Srikantaiah et al. [8] propose partitioning among sets for parallel programs. For parallel programs with inter-thread data reuse, compiler [72] can reorganize the loop iterations of each processor to maximize inter-thread locality. Operating system can also manage shared cache through architectural features [10] to optimize fairness of miss-rate or performance.

Hybrid of Private and Shared Caches

Compared with private cache, shared cache has disadvantage of slow access time and small capacity due to higher complexity. Hybrid of private and shared architectures [73] can provide high global capacity and fast local access through non-uniform accesses and sharing private cache among processors to allow expanding private data. Victim replication [74] replicates local primary cache victims within local L2 cache to minimize local L2 cache hit latency and maximize utilization of effective shared capacity. Cooperative caching [75] uses private caches and aggregate cache to exploit local and global levels of locality. Hardware-managed coherent caches and software-managed streaming memory are compared in [76] to evaluate these two basic models for CMP memory systems. In [77], the separation of L1 and L2 caches are overcome by allowing direct access to remote L1 cache to provide immediate access to data once produced.

Service Quality Management

Shared cache also challenges the Quality of Service (QoS) in CMP systems due

to less effective share of resources allocated to a particular application. CQoS [78] is a priority-based QoS scheme for shared cache, in which the priority is enforced by selective cache allocation, set partitioning, and heterogeneous cache regions. In Virtual Private Machines (VPM), Virtual Private Caches (VPCs) [79] provide minimum guarantees of bandwidth and capacity for cache QoS through arbiter and capacity manager.

## Chapter 3

## Background and Methodology

As discussed in Chapter 1, the memory behavior of shared cache in CMP is an outcome resulting from locality and interleaving. This chapter describes the definitions for locality and interleaving, and how they interact with each other. The experiment setup and methodology are also described in this chapter.

## 3.1 Locality

To use locality to characterize multithreaded working sets, some quantitative representation methods have been developed. One commonly-used definition of locality of a reference at time T is as follows [80]:

$$Locality = \frac{1}{(T_{next} - T)} \tag{3.1}$$

where  $T_{next}$  is the time of the next access to the same address.

Since we assume the data unit for communication in the memory system is a block, temporal locality is a special case of spatial locality. According to this definition, we can say a memory reference has high locality if the time of the next access to the same block is far in the future, and low locality if the next access time is near in the future.

In practice, T is expensive to measure and susceptible to program volatility.

| Time Index      | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|-----------------|---|---|---|---|---|---|---|---|

| Block Address   | X | Y | Z | Y | X | Z | Z | Y |

| Complete FRD    | 2 | 1 | 2 | 2 | * | 0 | * | * |

| Complete FRL    | 3 | 1 | 2 | 3 | * | 0 | * | * |

| Complete BRD    | * | * | * | 1 | 2 | 2 | 0 | 2 |

| Residual FRD(X) | 2 | 2 | 1 | 0 | * | 0 | * | * |

| Residual FRD(Y) | 0 | 1 | 0 | 3 | 1 | 1 | 0 | * |

| Residual FRD(Z) | 1 | 0 | 2 | 1 | 0 | 0 | * | * |

Table 3.1: Illustration of the reuse distance concept. (\*: the values cannot be computed without the information beyond the trace shown in the table)

The concept of *stack distance* [81] and *reuse distance* [82] are introduced to describe locality using abstract time (the number of accesses) instead of real time. For the convenience of discussion, the most commonly used definition is adopted as follows:

• reuse distance (stack distance)  $RD(A_m \prec A_n) =$ the number of unique memory accesses between two consecutive accesses ( $A_m$  preceding  $A_n$ ) to the same cache block A.

Some researchers [83] chose to use reuse distance to count all intermediate memory accesses. Since the total number of all intermediate memory accesses is also a very important concept in the following discussion, reuse length(stack length) is proposed to define it.

Table 3.1 illustrates the concepts defined above, where processor accesses block address X at abstract time 0, then accesses two other cache blocks (Y and Z in the figure) before accessing X again at time 4. Thus, the reuse distance for the first reference to X at time 0 is 2, while its reuse length is 3 because Y is accessed twice between the references to X.

In the following discussion it is sometimes necessary to distinguish between the distances from a cache block reference (Y at time 3) to its immediately previous reference (Y at time 1) and to its immediately next reference (Y at time 7).  $RD(Y_3 \prec Y_7)$  is called *forward* reuse distance of  $Y_3$ , and  $RD(Y_1 \prec Y_3)$  is called *backward* reuse distance of  $Y_3$ .

Reuse distance can sometimes be a runtime measurement of how far in the future a block is reused at the reference time of another block. For this purpose,  $RD(E_m \prec F_n)$  is called residual reuse distance of block  $F_n$  at reference time of block  $E_m$ , ie, the number of unique memory accesses between reference  $E_m$  and reference  $F_n$  (including other possible references to block address E between  $E_m$  and  $F_n$ ). On the contrary,  $RD(A_m \prec A_n)$  is called complete reuse distance of block A.

Before studying multithreaded locality, let us first look at singlethreaded program behavior since it provides a basis for discussing the multithreaded cases. A common way to profile singlethreaded program locality is to look at how miss rate varies over various cache configurations with different levels of capacity, associativity, and replacement policy. Instead of treating every cache miss equally in computing overall miss rate, some studies [84] also try to identify each cache miss as either a conflict miss or a capacity miss. Since LRU is a widely used cache replacement

Figure 3.1: Singlethreaded stack distance distribution, and cache hit rate as a function of cache associativity

policy, stack distance (reuse distance) profile [85] has been proposed to reveal more detail in characterizing locality under LRU policy.

Figure 3.1 presents the cache profile of two SPEC2000 benchmarks: art and gzip, under a set-associative LRU L2 cache. Since the stack distance distribution varies with the number of sets in the cache, the number of sets is set up as 2048 in the experiment. The points labeled "art-ssd" stand for the percentage of references exhibiting a particular stack distance value (X-axis label) among all references in the art benchmark trace. Under LRU replacement policy, all references with future reuse distance smaller than the associativity will cause the next reference to the same block to hit in cache, otherwise a miss will occur. Thus the miss rate for a particular associativity AS is equal to the sum of the percentages of all references with stack distances smaller than AS, ie, Hitrate(AS) =  $\sum_{d=0}^{AS-1} ssd(d)$ . Assuming 64-byte cache block size, the cache capacity can be computed as 2048\*64\*AS bytes.

From the stack distance distribution in Figure 3.1, it is evident that different benchmarks have various locality characteristics. Benchmark qzip has high locality

since most of its stack distances are concentrated in the range from 0 to 2, thus high associativity (high capacity) has very limited benefit when associativity increases beyond 2. In contrast, benchmark *art* shows low locality, with its stack distances widely spread from 0 to 16. Hence it takes a cache larger than 1.4MB to reach 90% hit rate.

#### 3.2 Interleaving

When multiple threads are sharing memory system, interference is inevitable due to interleaving. Concurrent threads compete for the limited shared resources. However, depending on the programs, different workloads react differently to interference. Therefore, it is important to study how their references are interleaved in the shared resource, in terms of how frequently each thread is accessing memory and how they are ordered in time.

# 3.2.1 Interleaving Granularity

Interleaving is interesting yet important to study because it is the cause of memory interference, and as shown in later chapters, it also provides some possibilities to improve memory system performance. One important question is how interleaving happens, and one answer could be *Interleaving Granularity*. Figure 3.2 shows two cases for different interleaving granularities. In fine-grain interleaving, references from different threads are shuffled with each at small distance, while coarse-grain interleaving tends to have references from the same thread cluster to-

Figure 3.2: Fine-grain and Coarse-grain interleaving

gether. Run Length is defined as the number of the references from the same thread without any reference from other thread, and average runlength is the average of all the runlength from the same thread in the multi-threaded trace. For example, thread 0 of fine-grain interleaving in Figure 3.2 has different runlengthes, namely 1, 1, 2, and 2. The runlengthes for thread 0 in coarse-grain interleaving are 3, 2 and 1. Thus, thread 0 has different average runlengthes in these two cases, 1.5 for fine-grain interleaving and 2 for coarse-grain interleaving.

The interleaving granularity is workload dependent. Fine-grain interleaving happens to workloads whose concurrent programs access to the same set very close in time, as illustrated by the example workload *swim-twolf* in Figure 3.3. In this Figure, program swim (light dots) is sweeping through all the sets shown, while program twolf (heavy dots) is also accessing almost all the sets in a less regular

Figure 3.3: Fine-grain interleaving pattern for the swim-twolf workload

Figure 3.4: Coarse-grain interleaving pattern for the apsi-gcc work-load

pattern. Nevertheless, in many sets, there are a few references from twolf between two consecutive references from swim. There is not much clustering occurring for either program. Hence this workload exhibits small runlengthes and small average runlength for both programs. For most workloads to have fine-grain interleaving, concurrent programs usually have a considerable working set spanning most sets and both access cache very frequently.

Figure 3.4 shows a coarse-grain interleaving workload: apsi-gcc. Program gcc (heavy dots) still spans most sets, showing the same access pattern of program twolf. Program apsi (light dots) shows a very different access pattern: its references hit a small number of sets with heavy accessing, while avoiding accessing many other sets. In the time window shown in this figure, the access patterns of apsi and gcc show spatial isolation. It is possible that in the later profiling windows program apsi will come back to access the sets it does not in the currently shown time window. When that happens, the later references from apsi are said to have temporal isolation with

| App  | applu | mgrid | apsi | sixtrack | bzip2 | swim | art   | wupwise | perlbmk | crafty | mesa |

|------|-------|-------|------|----------|-------|------|-------|---------|---------|--------|------|

| Skip | 1.5B  | 3.4B  | 3.3B | 8.5B     | 2.3B  | 5.7B | 18.3B | 3.4B    | 1.7B    | 5.2B   | 2.1B |

Table 3.2: Different simulation start points for interleaving sensitivity study (B = Billion)

the references from gcc in the time window shown in the figure. It is worthwhile to note that normally in a particular workload, the interleaving granularity varies across sets over time, therefore there is a distribution of different runlengthes, and the shape of the distribution will have important impact on the shared cache performance.

## 3.2.2 Sensitivity of Interleaving Granularity

In individual programs there are multiple phases with different memory accessing frequencies, working sets, and set mappings. If a program is executed concurrently with different program phases of other program, the interleaving will change because of varied accessing frequency and set mapping. To study the sensitivity of interleaving granularity to program phases, some traces are created by running programs from different starting points. Then the average runlength is measured in these new traces, and compared with the original traces.

Start points for the original traces are shown in Table 3.5. Out of 26 SPEC CPU2000 benchmarks, 11 benchmarks are selected to start from different start points as shown in Table 3.2. 100 new traces are created by simulating workloads which are made of one program with original start point and another program with new start point. The average runlength of the new trace of a particular workload is compared with that of the original trace of the same workload with programs

starting from the original start points. Then the percentage of average runlength variation is computed for each workload, and the average variation over the 100 new traces compared to the original traces is within 3%. Although some programs start from very different code regions due to different start points, interleaving granularity remains stable for most workloads. Different execution regions of the same program may have impact on memory access behavior, however, the variation is not significant enough to change the relative interleaving of the memory references from different threads.

### 3.2.3 Impact of Interleaving on Performance

In order to reveal the impact of interleaving on performance, a large number of two-program workloads (to be introduced in later chapters) are simulated to gain some statistical insights. Shared L2 cache traces are collected from these workloads' dynamic executions and are fed to a set-associative 1MB cache trace simulator with associativity of 8. This simulator is capable of enforcing a number of management policies, including oracle policy, LRU, and some other policies to be mentioned later in this dissertation. Once the simulation completes, the simulator reports miss rate, runlength, locality and other detailed information both per-set and per-cache.

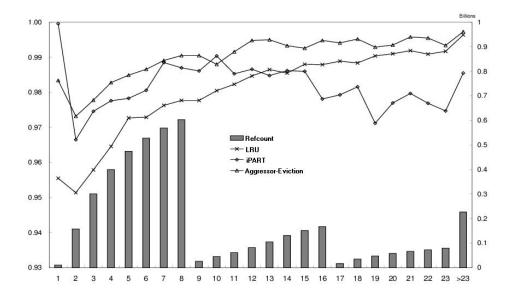

The results show that different workloads react differently to various cache policies because of the interaction of program locality and interleaving. If the interleaving granularity is measured using *average runlength*, the trace miss rate simulations show that certain interleaving correlates with the r elative performance

Figure 3.5: Cache performance comparison of LRU and iPART over different interleaving granularities (average runlength)

of cache policies. In Figure 3.5, the cache performance (measured in overall miss rate) is shown across all the 2-program workloads composed in the experiment. The points above 0 are workloads with better performance under LRU policy than under an ideal cache partitioning policy (to be introduced in later chapter), and the points below 0 are workloads with better performance under this ideal cache partitioning policy. This figure shows that cache partitioning usually works better in workloads with finer interleaving, and LRU works better in workloads with coarser interleaving, as well as some workloads with fine interleaving. Another important observation is that there are various levels of granularity across all the workloads, and more workloads with fine interleaving than coarse interleaving. Although cache partitioning seems to work better in the majority of the workloads (67.5%), there are still many workloads preferring the LRU policy.

### 3.3 Characterizing Multithreaded Workloads

After analyzing the single thread locality of programs and their interleaving, let us look at the interaction of multiple working sets. When multiple threads are running simultaneously, assuming there is no sharing of data among threads (which is true for multi-program workload), the resulting stack distances are incremented due to the interleaving references from other threads. Several models are proposed in [85] to predict inter-thread cache contention, with the conclusion that it is necessary to consider three factors: hit(reuse) frequency, miss frequency, and stack distance distribution.

Based on the definition of stack distance (reuse distance) under singlethreaded working set, multithreaded stack distance (reuse distance) with interleaving can be defined as  $SD_m(s) = s + incr(s)$ , where incr(s) is the incremental part of  $SD_m(s)$  caused by interleaving from other threads. Note that s is the same as stack distance in singlethreaded working set, since interleaving threads has no effect on the internal order of references within a single thread.

Further analysis of incr(s) helps understand what factors contribute to the incremental part of multithreaded stack distance. By definition, incr(s) is the number of unique memory accesses from other threads during the reuse stack of distance s. Thus incr(s) can be represented as distance(intv(s)), where intv(s) is the total number of memory accesses during the reuse stack of distance s, and function distance(s) counts the number of unique memory accesses. There are 2 factors which determine intv(s): the stack length sl(s) corresponding to stack distance s, and the

ratio r(s) of the frequencies of all the other threads over local thread. In summary, incr(s) = distance(sl(s) \* r(s)), and r(s) is a key measurement of the degree of intervention caused by interleaving.

### 3.3.1 Case Study

Now let us look at the same workload composed of two SPEC2000 benchmarks art and gzip. Figure 3.6 shows that cache hit rate variation when art and gzip are simultaneously running with a shared 1MB L2 cache. Compared with Figure 3.1, it is evident that the distributions of stack distances of different benchmarks are expanded towards larger values at different rate. Compared to the singlethreaded case, the stack distance distribution of art experiences small variation, with stable high concentrations at stack distance values of 0, 4, 9 and 10 in both figures. At the same time, gzip expands its stack distance concentration from the range of  $0 \sim 2$  in singlethreaded case to  $0 \sim 12$  in multithreaded case, and shows poorer locality than in singlethreaded case (gzip hit rate climbs above 90% only at stack distance beyond 14). This observation indicates that art loses little locality while gzip loses much of its locality due to the competition for limited cache capacity.

Table 3.3 compares the miss rates of art and gzip under singlethreaded and multithreaded executions. The comparison between singlethreaded 0.5MB and doublethreaded 1MB shows how much benefit a benchmark receives by sharing doubled-capacity cache with another benchmark, while the comparison between singlethreaded 1MB and doublethreaded 1MB shows how much penalty a benchmark suffers by

Figure 3.6: Multithreaded stack distance distribution, and cache hit rate as a function of cache associativity

| Threads       | Sing  | Double |       |

|---------------|-------|--------|-------|

| Cache Size    | 0.5MB | 1MB    | 1MB   |

| art missrate  | 0.822 | 0.666  | 0.686 |

| gzip missrate | 0.029 | 0.027  | 0.286 |

Table 3.3: Comparison of miss rates of singlethreaded and multithreaded cache miss rates of art and gzip, with frequency ratio art:gzip = 0.88:0.12

sharing the same cache with another benchmark. Benchmark gzip suffers almost 10X miss rate increase due to contention from art. On the other hand, art benefits (4.6% miss rate reduction) from sharing 2X capacity with gzip while suffering only 18% extra miss rate by sharing 1MB cache. The disparity of miss rate variation of art and gzip can be explained by their ratio of frequency (art:gzip=0.88:12). Such high r(s)  $(art_{freq}/gzip_{freq})$  for gzip produces high incr(s) and moves the whole stack distribution towards higher locations. For art, very small r(s)  $(gzip_{freq}/art_{freq})$  makes little difference to its stack distance distribution, hence the locality suffers slightly.

This analysis of multithreaded cache performance indicates some key factors in improving performance, which will be discussed in Chapter 4.

### 3.4 Methodology

M5 [86], a cycle-accurate event-driven simulator, is employed to quantify the performance of different cache allocation policies. M5 is configured to model both a dual-core and quad-core system. The cores are single-threaded 4-way out-of-order issue processors. Each core also employs its own hybrid gshare/bimodal branch predictor. The on-chip memory hierarchy consists of private L1 caches split between instructions and data, each 32-Kbyte in size and 2-way set associative; the L1 caches are connected to a shared L2 cache that is 1-Mbyte (2-Mbytes) in size and 8-way (16-way) set associative for the dual-core (quad-core) system. The latency to the L1s, L2, and main memory is 2, 10, and 200 cycles, respectively. Table 3.4 lists the detailed simulator parameters.

Cache partitioning techniques under study are applied to the shared L2 cache architectures. To model UCP, M5 is modified to implement the UMON-global profiler for acquiring SDPs, as well as the analysis to determine the partitioning from the SDPs. In each epoch, all possible allocations of the 8 ways in shared L2 cache to different threads are simulated. While 2-program workloads only require trying 7 allocations (each program is allocated at least 1 cache way), simulations become prohibitively time-consuming for larger workloads (there are 455 different allocations per epoch for 4 threads). Due to the combinatorial number of allocations,

| Processor Parameters |                                                                    |  |  |  |  |

|----------------------|--------------------------------------------------------------------|--|--|--|--|

| Bandwidth            | 4-Fetch, 4-Issue, 4-Commit                                         |  |  |  |  |

| Queue size           | 32-IFQ, 80-Int IQ, 80-FP IQ, 256-LSQ                               |  |  |  |  |

| Rename reg / ROB     | 256-Int, 256-FP / 128 entry                                        |  |  |  |  |

| Functional unit      | 6-Int Add, 3-Int Mul/Div, 4-Mem Port, 3-FP Add, 3-FP Mul/Div       |  |  |  |  |

|                      | Memory Parameters                                                  |  |  |  |  |

| IL1                  | 32KB, 64B block, 2 way, 2 cycles                                   |  |  |  |  |

| UL2-2core            | 1MB, 64B block, 8 way, 10 cycles 2MB, 64B block, 16 way, 10 cycles |  |  |  |  |

| UL2-4core            |                                                                    |  |  |  |  |

| Memory               | 200 cycles (6 cycle bw)                                            |  |  |  |  |

| Branch Predictor     |                                                                    |  |  |  |  |

| Branch predictor     | Hybrid 8192-entry gshare/2048-entry Bimod                          |  |  |  |  |

| Meta table           | 8192                                                               |  |  |  |  |

| BTB/RAS              | 2048 4-way / 64                                                    |  |  |  |  |

Table 3.4: Simulator parameters  $\,$

| App      | Type | Skip   | App     | Type | Skip   | App     | Type | Skip   |

|----------|------|--------|---------|------|--------|---------|------|--------|

| applu    | FP   | 187.3B | mgrid   | FP   | 135.2B | apsi    | FP   | 279.2B |

| sixtrack | FP   | 299.1B | bzip2   | Int  | 67.9B  | swim    | FP   | 20.2B  |

| art      | FP   | 14B    | twolf   | Int  | 30.8B  | equake  | FP   | 26.3B  |

| wupwise  | FP   | 272.1B | facerec | FP   | 111.8B | vpr     | Int  | 60.0B  |

| fma3d    | FP   | 40.0B  | eon     | Int  | 7.8B   | galgel  | FP   | 14B    |

| gzip     | Int  | 4.2B   | gap     | Int  | 8.3B   | perlbmk | Int  | 35.2B  |