ABSTRACT

Title of Dissertation: MESOSCALE MICROSTRUCTURE

EVOLUTION, RELIABILITY AND FAILURE ANALYSIS OF HIGH

TEMPERATURE TRANSIENT LIQUID

PHASE SINTERING JOINTS

Seyed Ali Moeini, Doctor of Philosophy, 2017

Dissertation directed by: Professor F. P. McCluskey, Department of

Mechanical Engineering

The continuous increase in application temperature of power electronic devices, due to the growing power density, miniaturization, and functionality in military and commercial applications, requires new packaging technologies with high temperature and reliability capabilities. Currently, the traditional maximum allowable temperature of power electronics (125°C) is a limiting factor for high temperature applications, such as space exploration, drilling, avionics, and electronic vehicles. Substitution of Silicon devices with wide bandgap (e.g., SiC) devices has extended the maximum allowable temperatures to 475°C. However, this created the need for robust high temperature packaging materials, especially interconnects and attachments. High temperature solders are often too expensive, too brittle, or environmentally toxic to be used, leading to increased study of low temperature joining techniques, such as solid phase sintering

and Transient Liquid Phase Sintering (TLPS), for producing high temperature stable attachments. TLPS is an emerging electronic interconnect technology enabling the formation of high temperature robust joints between metallic surfaces at low temperatures by the consumption of a transient, low temperature, liquid phase to form high temperature stable intermetallic compounds (IMCs).

The performance and durability of these materials strongly depend on their microstructure, which is determined by their processing. The complicated process of IMC formation through eutectic solidification and the extensive number of parameters affecting the final microstructure make it impractical to experimentally study the effect of each factor. In this work, phase field modeling of the microstructure of TLPS materials fabricated by different processing methods will be conducted. Phase-field modeling (PFM) is a powerful thermodynamic consistent method in mesoscale modeling that simulates the evolution of intermetallic compounds during the solidification process, providing insight into the final microstructure. Application of this method facilitates the optimization of influential processing factors. Efforts will also be conducted to identify failure modes and mechanisms experimentally under dynamic, power and thermal cycling loads as a function of critical microstructural features, facilitating the optimization of joining parameters to obtain higher durability TLPS interconnections.

The objective of this dissertation is to provide an insight into the processing of a reliable high temperature TLPS and facilitate their application in power electronic industries.

# MESOSCALE MICROSTRUCTURE EVOLUTION, RELIABILITY AND FAILURE ANALYSIS OF HIGH TEMPERATURE TRANSIENT LIQUID PHASE SINTERING JOINTS

by

Seyed Ali Moeini

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2017

Advisory Committee:

Professor F.P. McCluskey, Chair

Professor A. Dasgupta

Professor H. Bruck

Professor A. Christou

Professor. L. Hu, Dean's representative

© Copyright by Seyed Ali Moeini 2017

# Dedicated

To my wonderful family

Ata, Azar, Azita, Rozita, Reza

and the love of my life,

Mahshid

# Acknowledgement

I would like to thank my advisor and mentor, Professor Patrick McCluskey, for his excellent guidance, support, feedback, and for always encouraging me to push my boundaries. I could never imagine having a better advisor than him, and I will always be grateful for that. This dissertation wouldn't be possible without all our discussions. I would like to thank my committee members, Profs. Bruck, Christou, Dasgupta, and Hu, for serving on this dissertation committee. I am deeply grateful to my mentors, Dr. Nie, and Profs. Hu, Baz, Dasgupta, Trinkle for their unconditional help and support. I'd like to thank my friends, Amirhossein, Mohammad, Mehdi, Mahnaz, Armin, Hannes, Subramani, Jennifa, Chandra, David, Shaheen, Pouya, Alborz, Alireza, Ladan, Niloofar, Aryan, Farhad, Mahyar, Bahar, Navid, Elham, Hadi, Hamidreza, Elnaz, Nickan, Danny, Moein, Faryaneh, Mostafa, Marjan, Lei, Jay, Jingshi, and Ahmad, who made my life fun and meaningful. I, also, would like to thank Majid Aroom for his help and access to the Machine Shop resources.

I would like to thank my parents, my twin sisters, my genius brother, their children and spouses for their lifetime support, endless kindness, and for always being there for me and encouraging me to follow my dreams.

I would like to say my thanks to my wonderful wife, love, and best friend, Mahshid. I'm indebted to her for her endless patience, help, and support in every moment of my graduate school, and making our house a place of happiness and peace. I'm so lucky to have her in my life.

Ali Moeini, Sep 2017

# **Table of Contents**

| Acknowledgement                                                                | iii |

|--------------------------------------------------------------------------------|-----|

| Table of Contents                                                              | iv  |

| List of Figures                                                                | vi  |

| Chapter 1: High temperature interconnections                                   | 1   |

| Lead-free solders                                                              | 2   |

| Sn-based alloys                                                                |     |

| Au based alloys                                                                | 7   |

| Zn-based alloys                                                                |     |

| Bi-based                                                                       |     |

| Epoxy adhesives                                                                |     |

| Sintering technologies                                                         |     |

| Research gap and problem statement                                             |     |

| Outline                                                                        |     |

| Chapter 2: Sintered joints, fundamentals, processing and development           |     |

| Introduction                                                                   |     |

| Solid-state Sintering                                                          |     |

| Microscale Silver Sintering                                                    |     |

| Nanoscale Silver Sintering                                                     |     |

| Liquid Sintering                                                               |     |

| Paste Constituents and Preparation                                             |     |

| Organic Vehicle                                                                |     |

| Metal Particles                                                                |     |

| Paste Placement                                                                |     |

| Solid-state sintering                                                          |     |

| Liquid phase sintering                                                         |     |

| Sintering Process                                                              |     |

| Pressure                                                                       |     |

| Temperature                                                                    |     |

| Ambient                                                                        |     |

| Shrinkage and Weight Loss                                                      |     |

| Pre-drying                                                                     |     |

| Surface Metallization                                                          | 39  |

| Experiment:                                                                    | 40  |

| One-step processing                                                            |     |

| Large-area interconnections                                                    |     |

| Tertiary elements:                                                             |     |

| Conclusion                                                                     |     |

| Chapter 3: Microstructure evolution modeling during transient liquid phase sin | _   |

|                                                                                |     |

| Introduction                                                                   |     |

| Classical Sharp-interface model                                                |     |

| Phase field method                                                             |     |

| Thermodynamics treatment                                                       | 67  |

| Isothermal phase transitions in binary alloys                       | 69  |

|---------------------------------------------------------------------|-----|

| Multiphase field models                                             |     |

| Multiphase field modeling of Cu-Sn transient liquid phase sintering | 83  |

| Modified phase-field model                                          |     |

| Experiment procedure                                                | 89  |

| Cu-Sn Microstructure evolution modeling:                            |     |

| IMC growth around a single particle:                                | 95  |

| Two-step processing joint formation                                 |     |

| One-step processing joint formation                                 | 100 |

| Conclusions                                                         | 102 |

| Chapter 4 : Experimental process                                    | 104 |

| Introduction                                                        | 104 |

| Quality metric                                                      | 105 |

| Screening                                                           | 106 |

| Composition classification                                          | 111 |

| Composition evolution                                               | 113 |

| Reliability and failure analysis                                    | 114 |

| Dynamic loading (drop-shock test)                                   |     |

| Sample preparation and test procedure                               |     |

| Results and discussion                                              | 118 |

| Dynamic loading (drop-shock test) after aging                       | 121 |

| Sample preparation and test procedure                               | 121 |

| Results and discussion                                              |     |

| Power cycling                                                       | 135 |

| Sample preparation                                                  |     |

| Experimental setup                                                  | 141 |

| Test procedure                                                      | 146 |

| Results and discussion                                              | 146 |

| Thermal cycling                                                     | 150 |

| Sample preparation and test procedure                               |     |

| Results and discussion                                              |     |

| Conclusion                                                          | 157 |

| Chapter 5 Wood carbon Cu-Sn high temperature die-attach technology  | 160 |

| Introduction                                                        |     |

| Methods:                                                            | 164 |

| Shear test results:                                                 | 174 |

| Conclusion:                                                         | 176 |

| Chapter 6 Contributions and future works                            | 177 |

| Future works                                                        |     |

| Appendix I                                                          |     |

| Au-In SLID Joints                                                   |     |

| Ag-In SLID Joints                                                   |     |

| Au-Sn and Ag-Sn SLID Joints                                         |     |

| Ni-Sn SLID Joints                                                   |     |

| Other Materials                                                     | 188 |

| References                                                          | 190 |

# **List of Figures**

| Figure 1-1: Ag-Sn phase diagram [12]                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Left) The market share of different lead-free solders; Right) Survey of the market share of different types of SAC alloys [16]                                                                                                                                                        |

| Figure 1-3: Au-Sn phase diagram [12]                                                                                                                                                                                                                                                              |

| Figure 1-4: Silver-bismuth phase diagram [12]                                                                                                                                                                                                                                                     |

| Figure 2-1: Solid-state sintering stages 20                                                                                                                                                                                                                                                       |

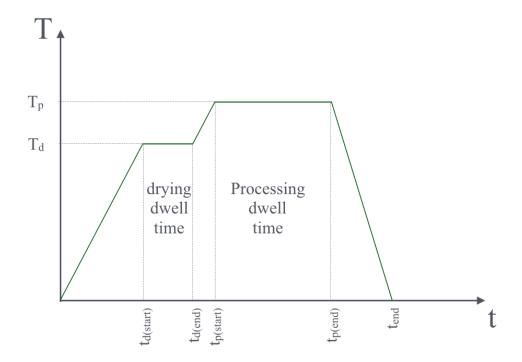

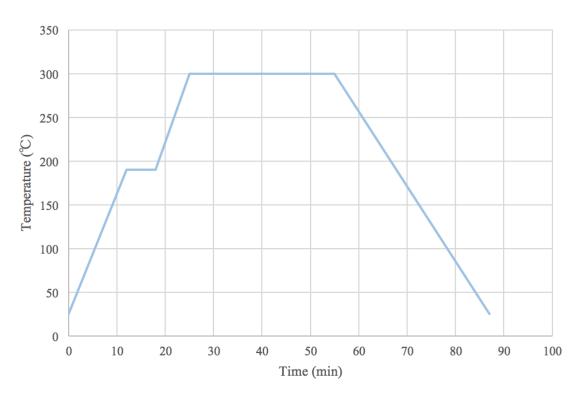

| Figure 2-2: Processing thermal profile                                                                                                                                                                                                                                                            |

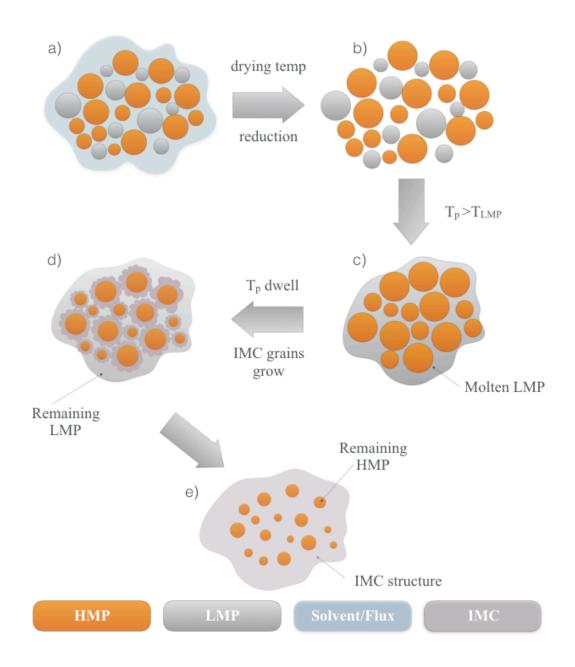

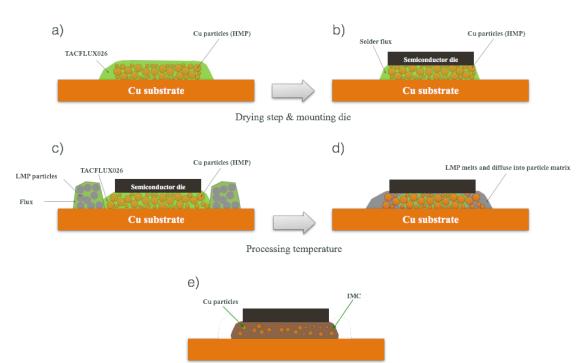

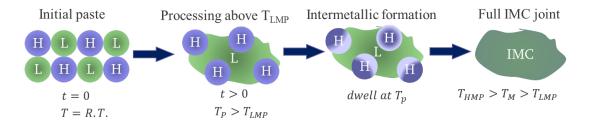

| Figure 2-3: TLPS processing stages: a) HMP and LMP particles mixed in binder, b) Reduced particles at drying temperature, c) LMP phase melts and diffuse into HMP phase matrix, d) IMC grains start growing on HMP particles, e) An IMC matrix forms around the remaining unreacted HMP particles |

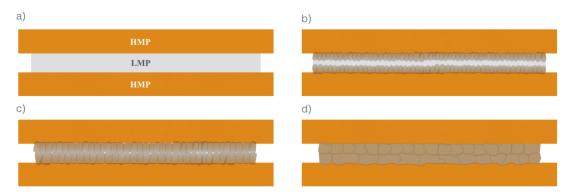

| Figure 2-4: Layer-based TLPS processing a) Material placement, b) IMCs start growing c) Small amount of unreacted LMP phase d) Full IMC joint                                                                                                                                                     |

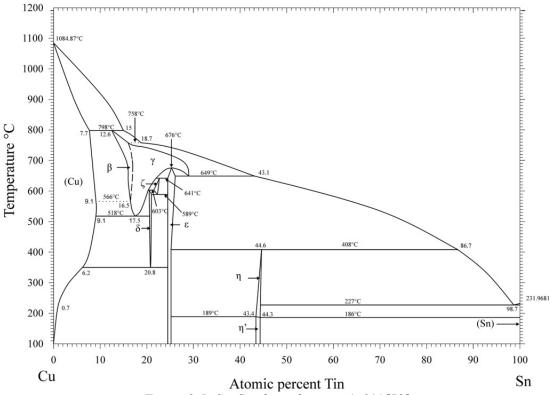

| Figure 2-5: Sn-Cu phase diagram (at%)[78]                                                                                                                                                                                                                                                         |

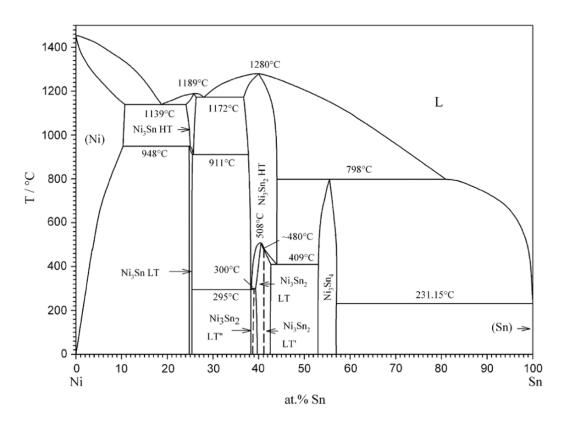

| Figure 2-6: Ni-Sn phase diagram (at%) [79]                                                                                                                                                                                                                                                        |

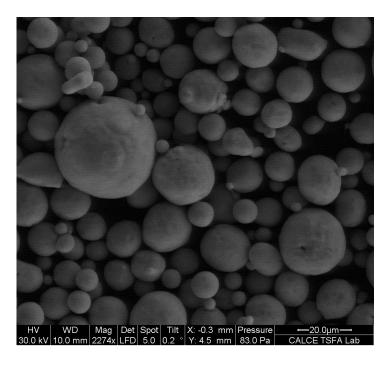

| Figure 2-7: Cu particles after ultrasonic cleaning at room temperature                                                                                                                                                                                                                            |

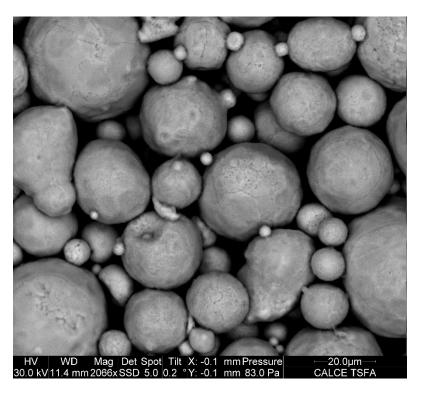

| Figure 2-8: Cu particles after drying at 500°C                                                                                                                                                                                                                                                    |

| Figure 2-9: Two-step processing: a) HMP paste was stencil-printed on the substrate, b) Semiconductor die was mounted on the paste, c) LMP phase was injected around the assembly d) At processing temperature, the LMP phase melts and diffuses through the interconnection region                |

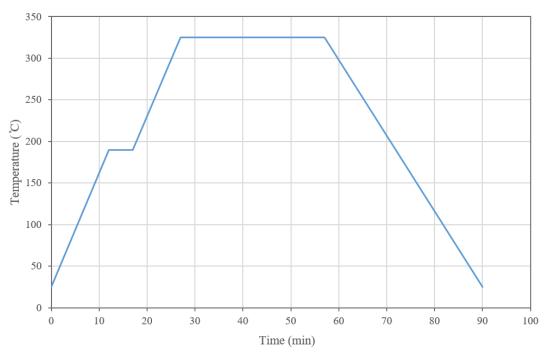

| Figure 2-10: Cu-Sn two-step sintering thermal profile                                                                                                                                                                                                                                             |

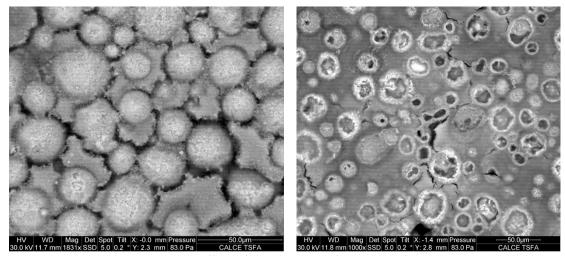

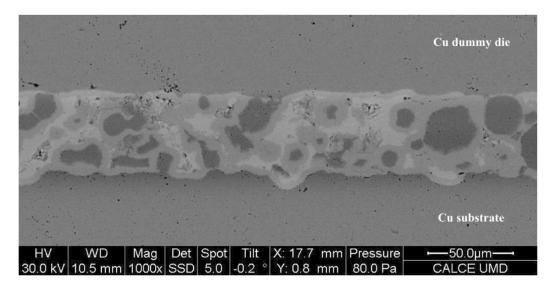

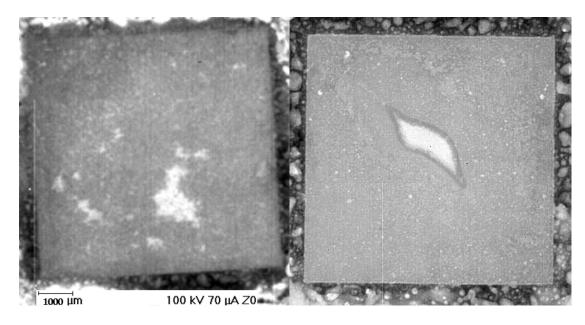

| Figure 2-11: Considering the effect of dwell time on formation of TLPS joints: dwell for 2 minutes (left image), and 5 minutes (right image) at 325°C                                                                                                                                             |

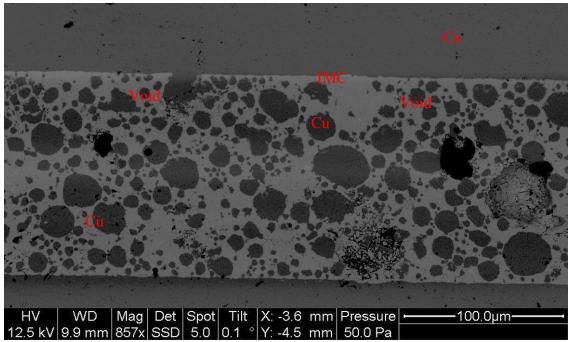

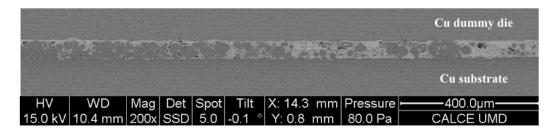

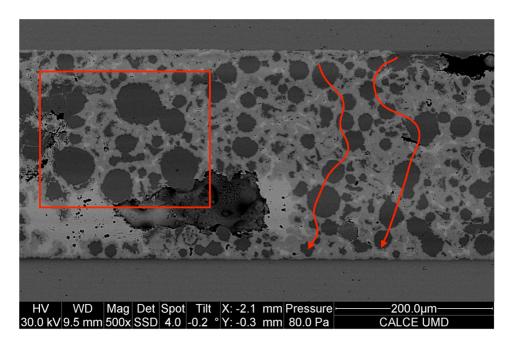

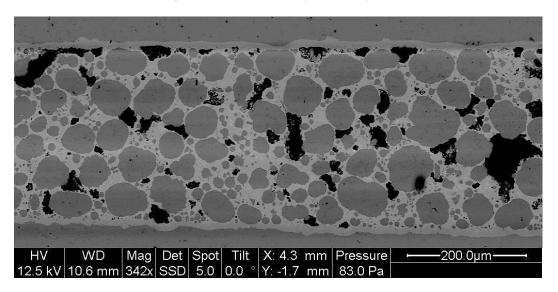

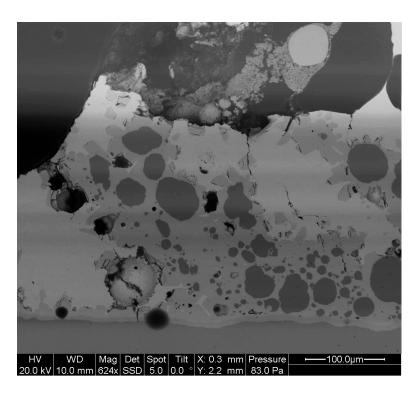

| Figure 2-12: Cross section of a fully processed Cu-Sn TLPS joint                                                                                                                                                                                                                                  |

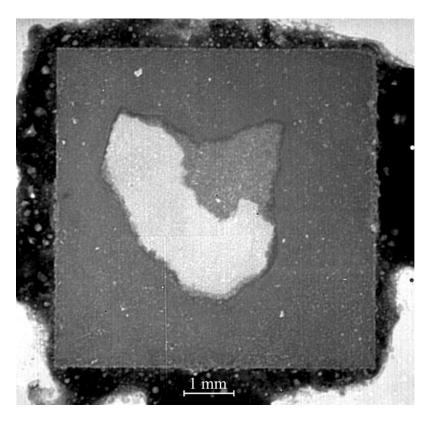

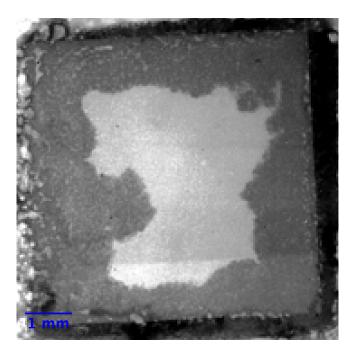

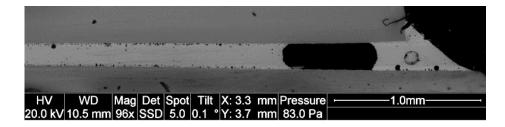

| Figure 2-13: X-ray of a TLPS joint without enough LMP material from the top view; huge un-wetted area observed at the center of the joint                                                                                                                                                         |

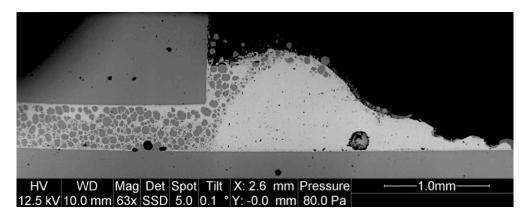

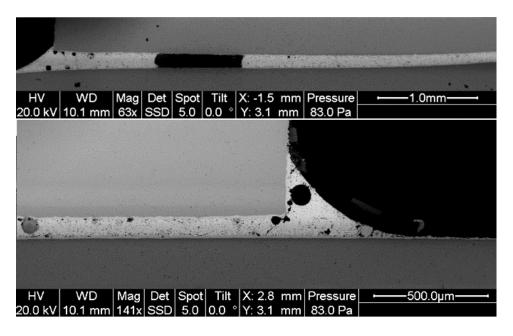

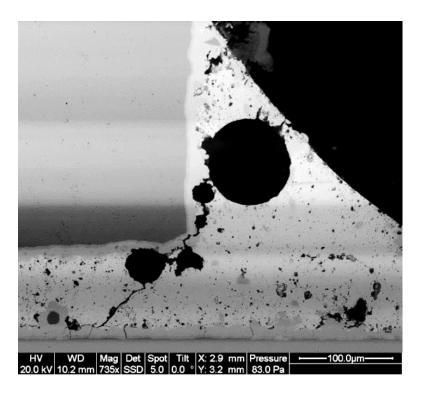

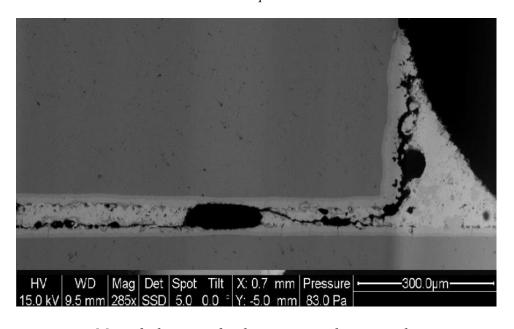

| Figure 2-14: ESEM image of TLPS joint with too much LMP phase at the edges of assembly; unreacted LMP phase remained at the edge after processing                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

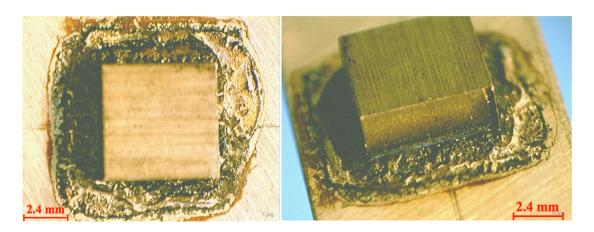

| Figure 2-15: Extra LMP residues around the interconnection                                                                                                                                                                                                                            |

| Figure 2-16: The LMP phase and migrated HMP phase moved to top of the die 51                                                                                                                                                                                                          |

| Figure 2-17: Cu-Sn one-step sintering thermal profile                                                                                                                                                                                                                                 |

| Figure 2-18: Cu-Sn interconnection exterior appearance using one-step sintering process                                                                                                                                                                                               |

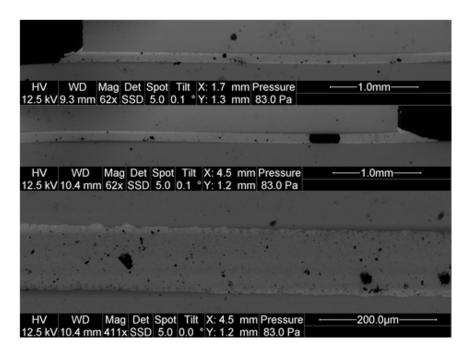

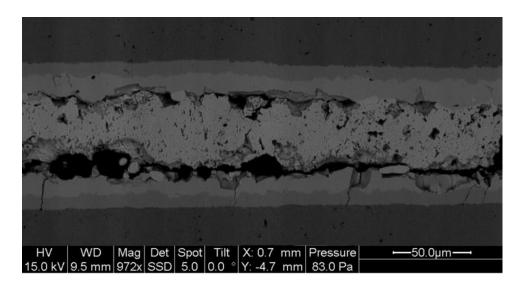

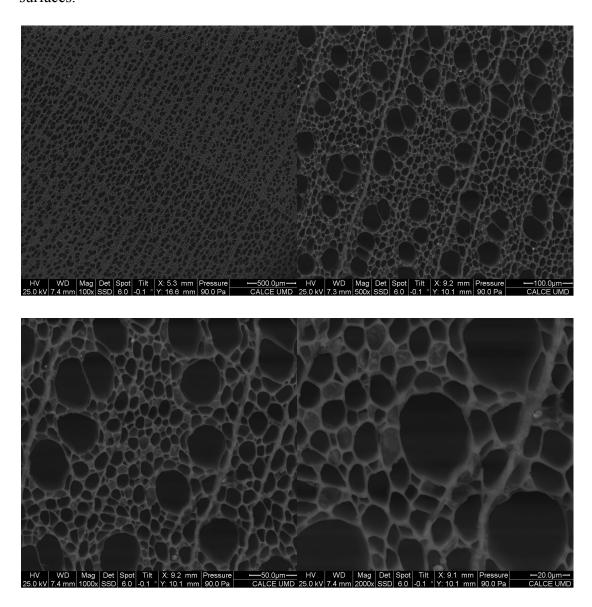

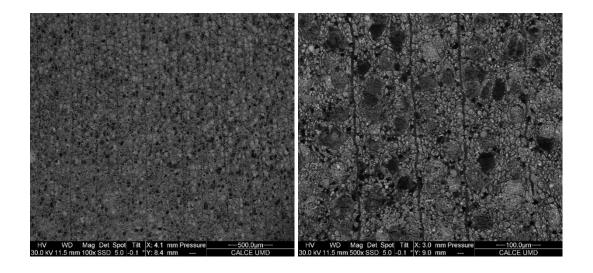

| Figure 2-19: ESEM image of Cu-Sn TLPS joint (one-step processing)                                                                                                                                                                                                                     |

| Figure 2-20: Higher magnification ESEM image of Cu-Sn TLPS joint (one-step processing)                                                                                                                                                                                                |

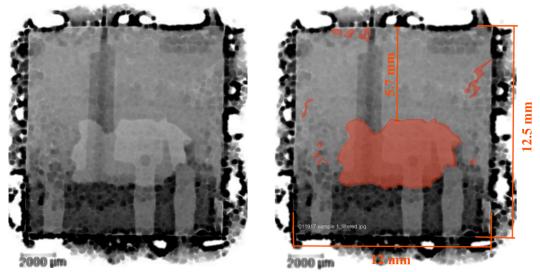

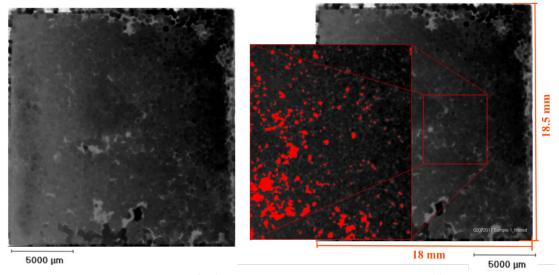

| Figure 2-21: Top-view x-ray of a large-area interconnection processed by two-step Cu-Sn TLPS processing; the light-red regions define the un-wetted regions                                                                                                                           |

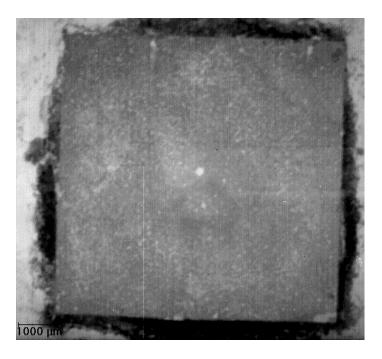

| Figure 2-22: Top-view x-ray of a large-area interconnection processed by one-step Cu-Sn TLPS processing; the red regions define the pores regions                                                                                                                                     |

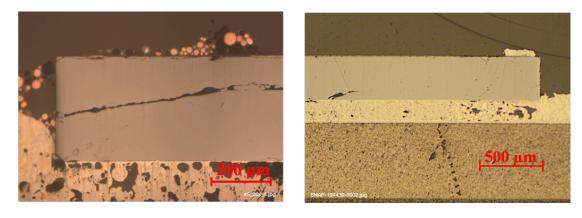

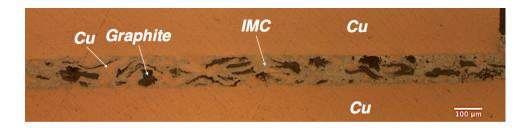

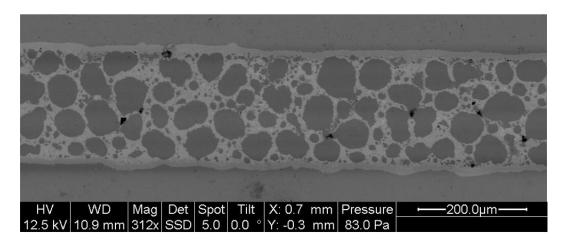

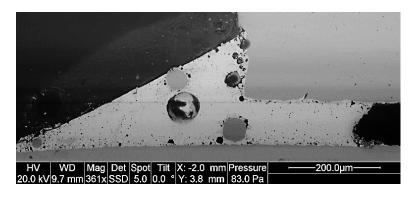

| Figure 2-23: Cross-section image of a section of large-area interconnection processed by one-step Cu-Sn TLPS processing under optical microscope                                                                                                                                      |

| Figure 2-24: Cu-Sn TLPS with silver-plated graphite under optical microscopy 56                                                                                                                                                                                                       |

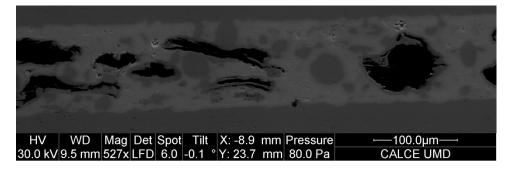

| Figure 2-25: Cu-Sn TLPS with silver-plated graphite under ESEM                                                                                                                                                                                                                        |

| Figure 2-26:Cu-Sn TLPS with silver-plated graphite under optical microscopy 57                                                                                                                                                                                                        |

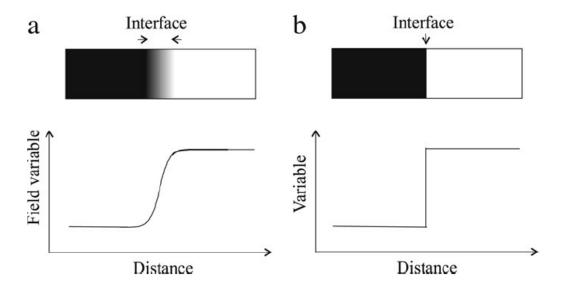

| Figure 3-1: (a) Diffuse interface: properties evolve continuously between their equilibrium values in the neighboring phases. (b) Sharp interface: properties are discontinuous at the interface. [86]                                                                                |

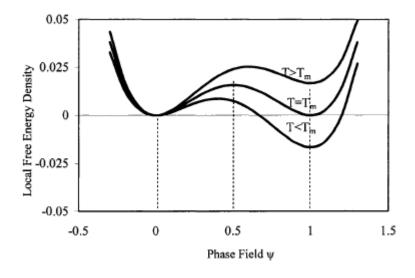

| Figure 3-2: The free-energy density $f(\phi,T)$ , employed in WBM model, displayed as a function of $\phi$ for three values of the temperature near the melting temperature $T_M$ : for $T < T_M$ ( $\beta = -0.2$ ), $T = T_M$ ( $\beta = 0$ ), and $T > T_M$ ( $\beta = 0.2$ ) [90] |

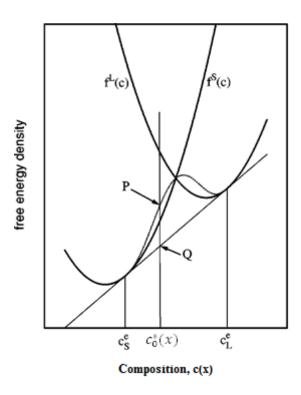

| Figure 3-3: Free energy density curves of solid and liquid phases with respect to composition [91]                                                                                                                                                                                    |

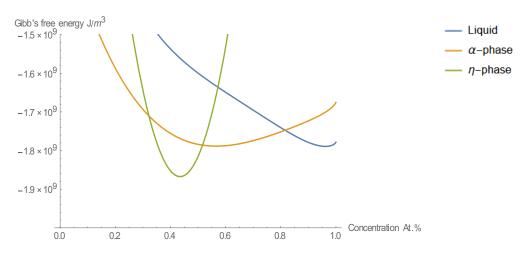

| Figure 3-4: Gibb's free energy of Cu-Sn interface at 324°C consists of: 1. Sn (liquid phase) 2. α-phase (Solid) 3. η-phase (Cu <sub>6</sub> Sn <sub>5</sub> IMC)                                                                                                                      |

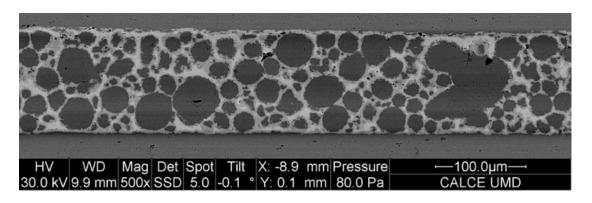

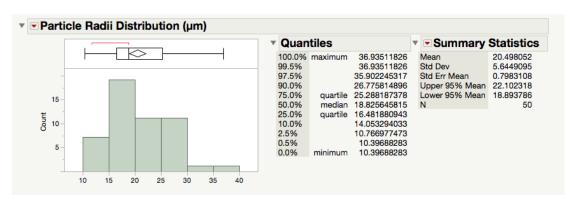

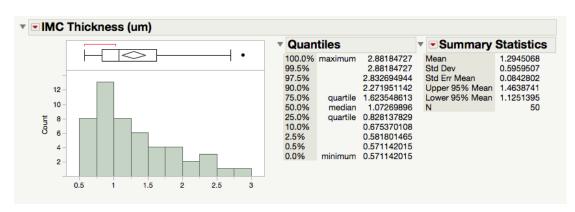

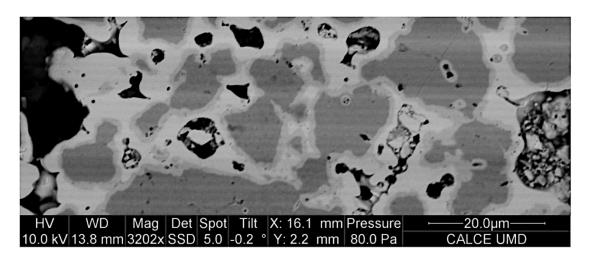

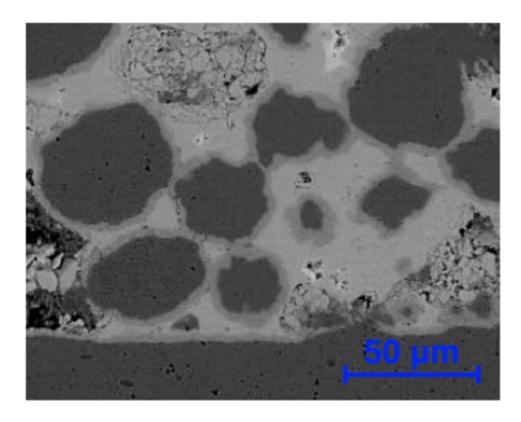

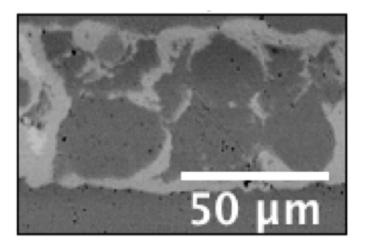

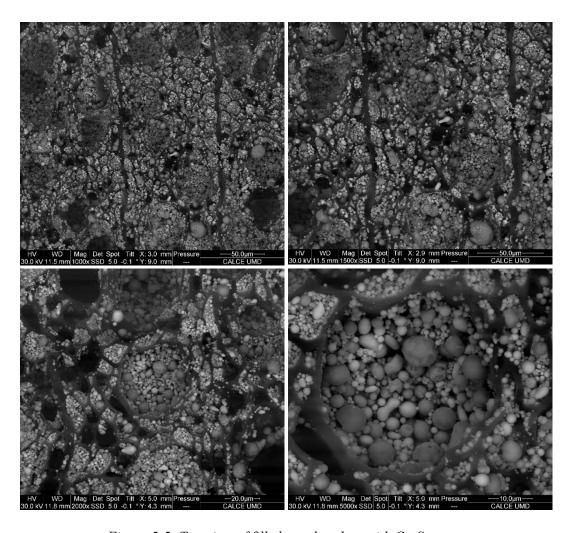

| Figure 3-5: ESEM image of Cu-Sn TLPS sintered for 30s                                                                                                                                                                                                                                 |

| Figure 3-6: Particle radii distribution for particles with radius>10µm shown in Figure 3-5 (sample size: 50 particles)                      |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-7: Average IMC thickness around the particles shown in Figure 3-5 (sample size: 50 particles)                                      |

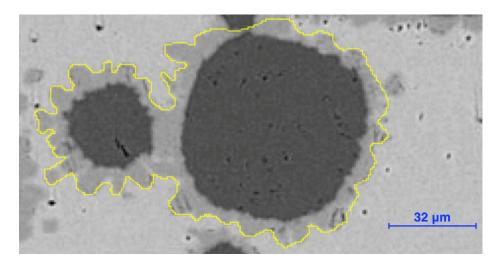

| Figure 3-8: Higher magnification image of a copper particle in Cu-Sn TLPS interconnection processed for 30s at the high temperature (300°C) |

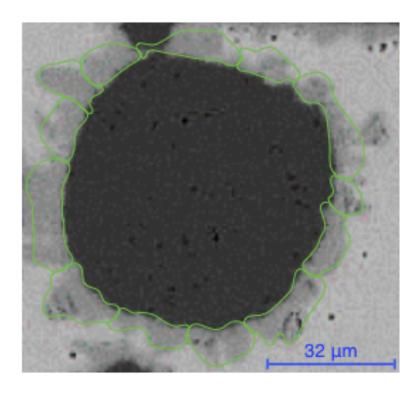

| Figure 3-9: IMC growth around copper particles after 2 minutes sintering at 300°C[99]                                                       |

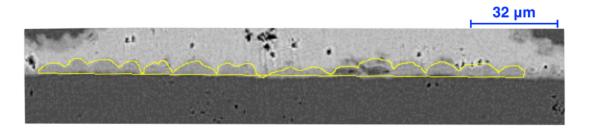

| Figure 3-10: IMC growth on copper flat surface after 2 minutes sintering at 300°C. 92                                                       |

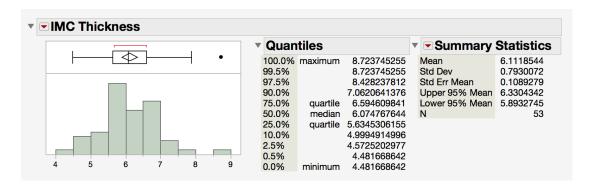

| Figure 3-11: Average IMC thickness around the particles after 2 minutes of sintering at 300°C (sample size: 53 particles)                   |

| Figure 3-12: ESEM image of Cu-Sn TLPS sintered for 4 minutes at 300°C                                                                       |

| Figure 3-13: ESEM image of Cu-Sn TLPS sintered for 30 minutes at 300°C 94                                                                   |

| Figure 3-14: Grains formed around a copper particle after 2 minutes of sintering at 300°C                                                   |

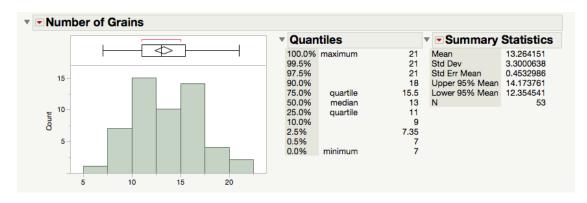

| Figure 3-15: Average number of IMC grains around the particles after 2 minutes of sintering at 300°C (sample size: 53 particles)            |

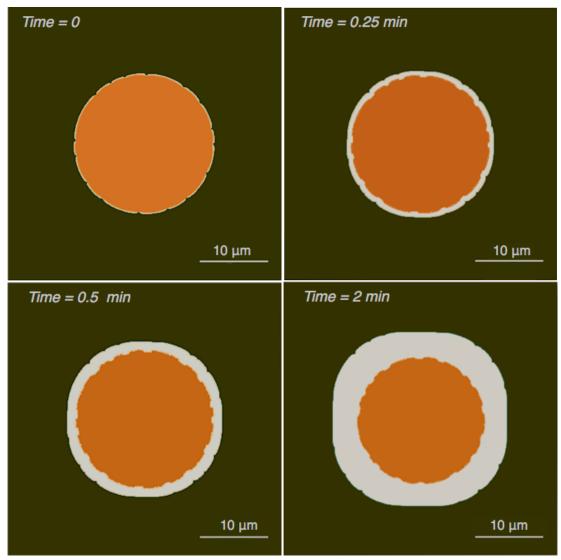

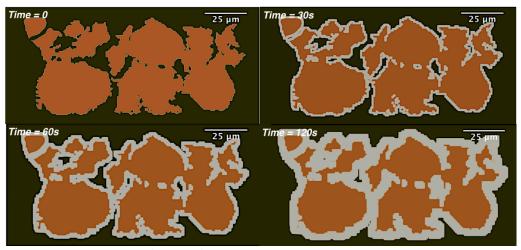

| Figure 3-16: <i>Cu6Sn</i> 5 growth during TLPS after a) 0, b) 0.25, c) 0.5, d) and 2 minutes processing at 300°C                            |

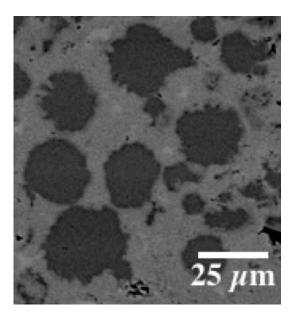

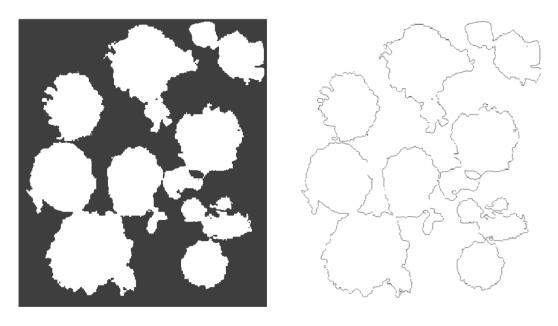

| Figure 3-17: Copper particles in a two-step TLPS joint                                                                                      |

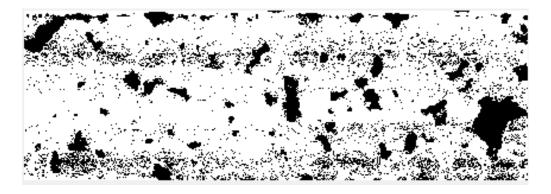

| Figure 3-18: Image processing of Figure 3-17: left image shows copper phase, and right image shows the interface of copper and tin          |

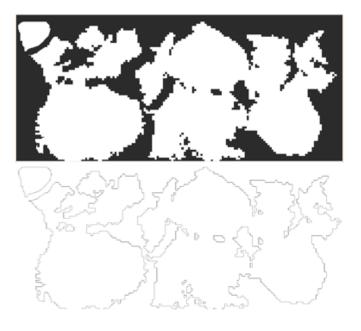

| Figure 3-19: IMC growth around copper particles in one-step TLPS processing at 300°C                                                        |

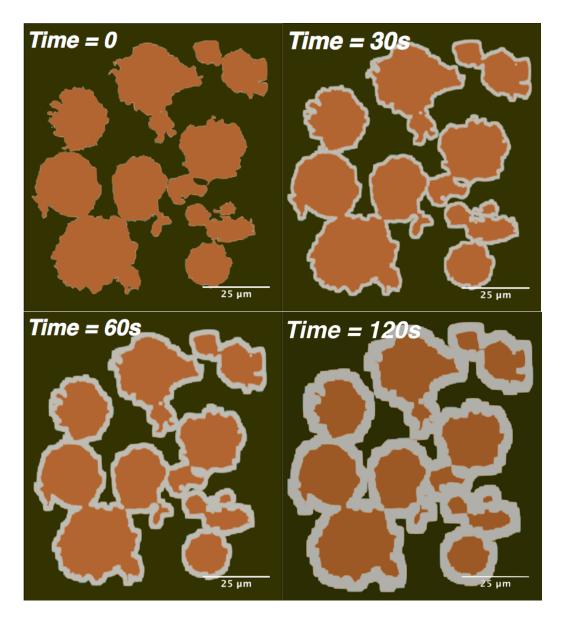

| Figure 3-20: Solid-state sintered copper particles in a one-step TLPS joint 101                                                             |

| Figure 3-21: Image processing of Figure 3-20: top image shows copper phase, and bottom image shows the interface of copper and tin          |

| Figure 3-22: IMC growth around copper matrix in one-step TLPS processing at 300°C                                                           |

| Figure 4-1: Cross section of a fully processed Cu-Sn TLPS joint                                                                             |

| Figure 4-2: A low quality joint rejected in X-ray screening                                                                                 |

| Figure 4-3: A high quality joint; passed the X-ray screening                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-4: Joints passed the X-ray screening with wetting (~96%)                                                                                                                                                         |

| Figure 4-5: Almost void-free TLPS joint                                                                                                                                                                                   |

| Figure 4-6: Voided TLPS joint that passed X-ray screening                                                                                                                                                                 |

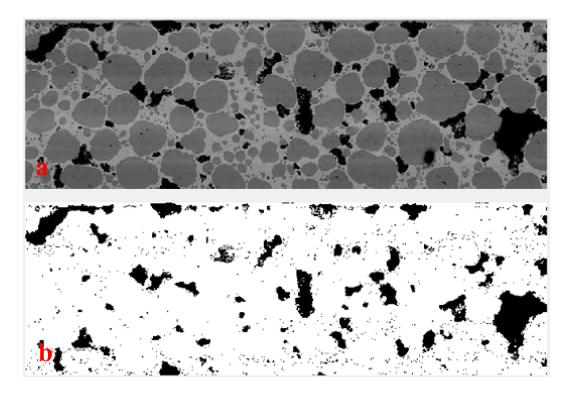

| Figure 4-7: a) Joint image (MATLAB code input), b) Processed image with threshold=80, 87.7% joint density                                                                                                                 |

| Figure 4-8: Processed image with threshold=90, 79.5% joint density                                                                                                                                                        |

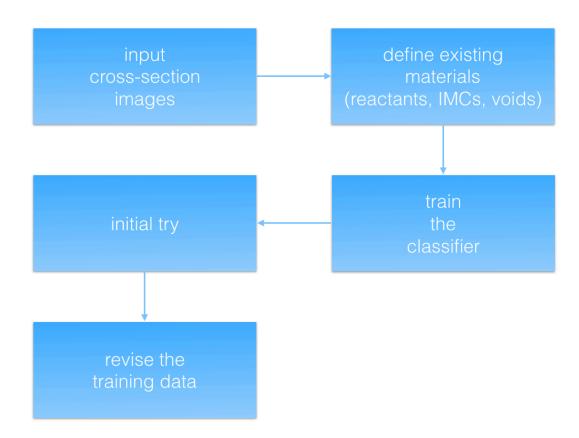

| Figure 4-9: Machin-learning composition classification approach                                                                                                                                                           |

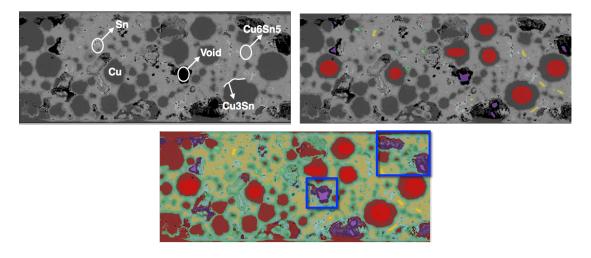

| Figure 4-10: a) Input ESEM image, b) Defined material classes: copper particles (red), unreacted tin (cyan), <i>Cu6Sn5</i> (yellow), <i>Cu3Sn</i> (green), and voids (purple), and c) First try results with low accuracy |

| Figure 4-11: Composition classification results after finalizing training step 113                                                                                                                                        |

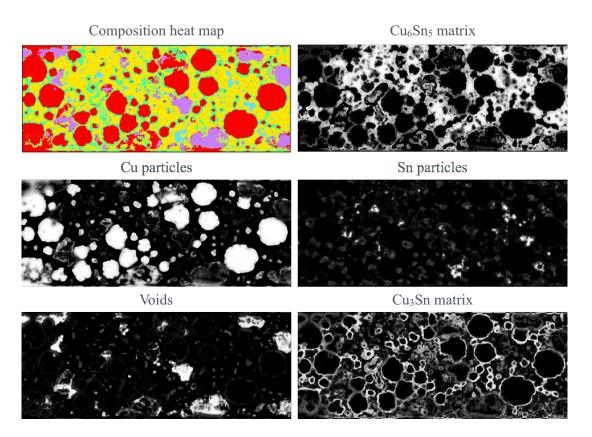

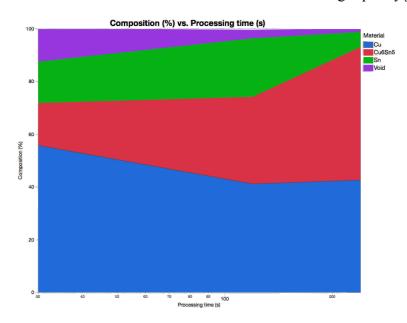

| Figure 4-12: Composition evolution with respect to processing time for TLPS at 300C                                                                                                                                       |

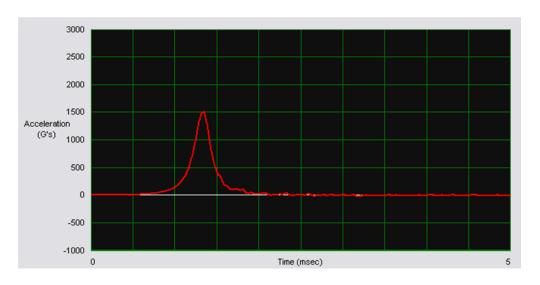

| Figure 4-13: Drop shock test acceleration over time                                                                                                                                                                       |

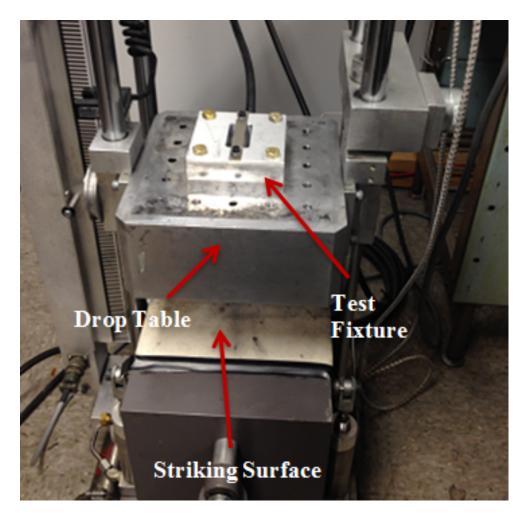

| Figure 4-14: Sample fixture mounted on drop tower                                                                                                                                                                         |

| Figure 4-15: Ni-Sn TLPS drop test sample                                                                                                                                                                                  |

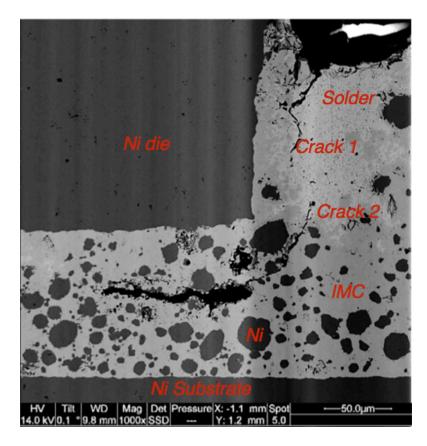

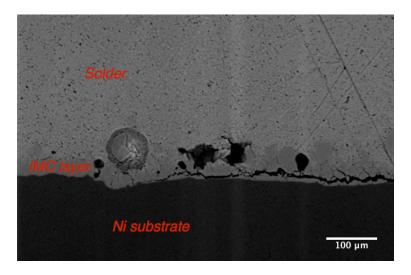

| Figure 4-16: ESEM image of Ni-Sn sinter joint between Ni-die and Ni-stripe) after drop tests; magnification x1000                                                                                                         |

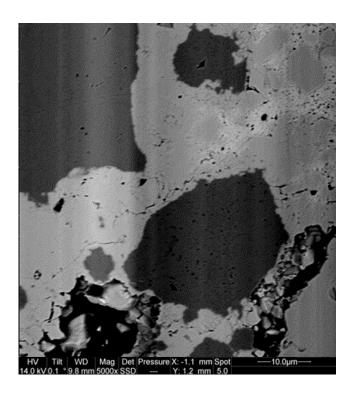

| Figure 4-17: ESEM image of Ni-Sn sinter joint between Ni-die and Ni-stripe) after drop tests; magnification x5000                                                                                                         |

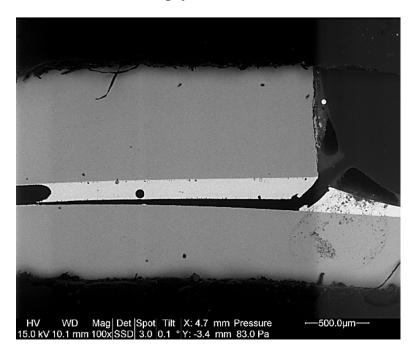

| Figure 4-18: ESEM image of Sn3.5Ag solder joint between Ni-die and Ni-stripe) after drop tests; magnification x1000                                                                                                       |

| Figure 4-19: Magnified ESEM image of crack propagation in IMC layer between Sn3.5Ag solder Ni-stripe) after drop tests; magnification x3500                                                                               |

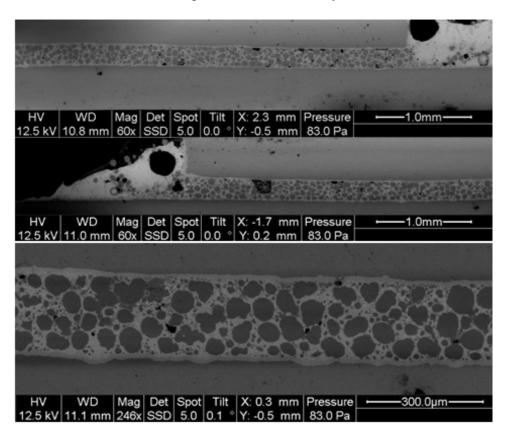

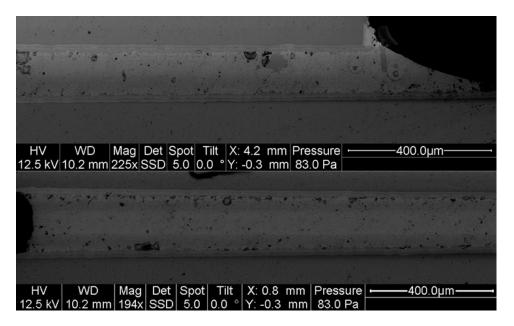

| Figure 4-20: ESEM image of TLPS joint (no isothermal aging)                                                                                                                                                               |

| Figure 4-21: ESEM image of TLPS joint after 100 hours isothermal aging at 185°C                                                                                                                                           |

| Figure 4-22: ESEM image of TLPS joint after 500 hours isothermal aging at 185°C                                                                                                                                           |

| Figure 4-23: ESEM image of Sn3.5Ag solder joint (no isothermal aging)                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-24: ESEM image of Sn3.5Ag solder joint after 100 hours isothermal aging at 185°C                                                 |

| Figure 4-25: ESEM image of Sn3.5Ag solder joint after 500 hours isothermal aging at 185°C                                                 |

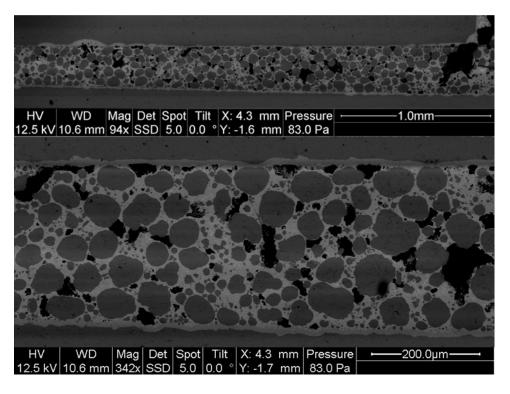

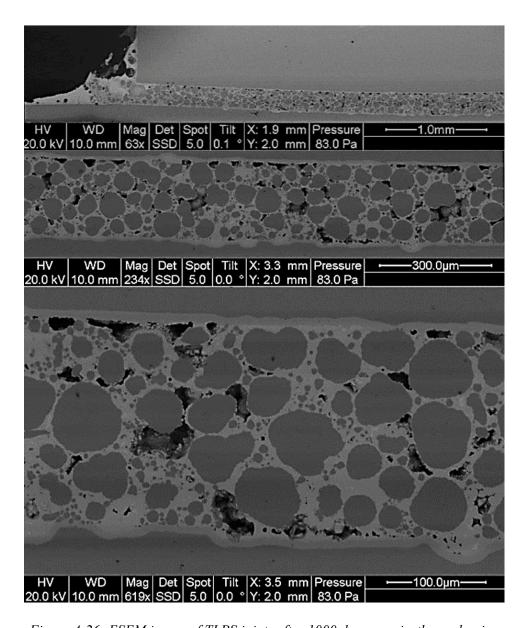

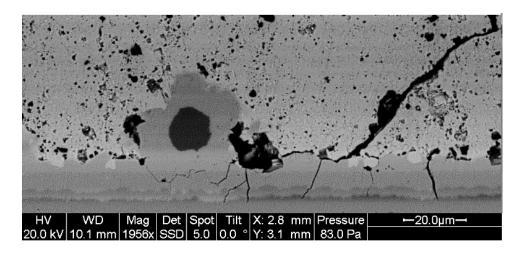

| Figure 4-26: ESEM image of TLPS joint; after 1000 drops, no isothermal aging 126                                                          |

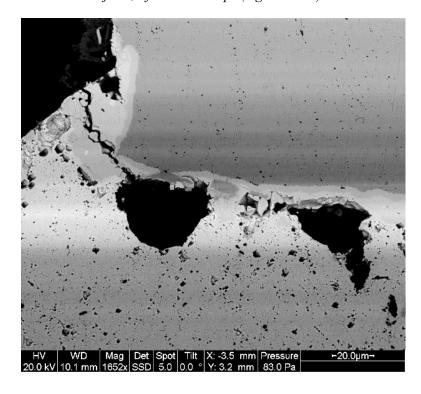

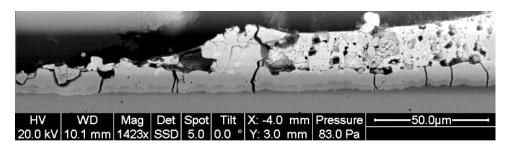

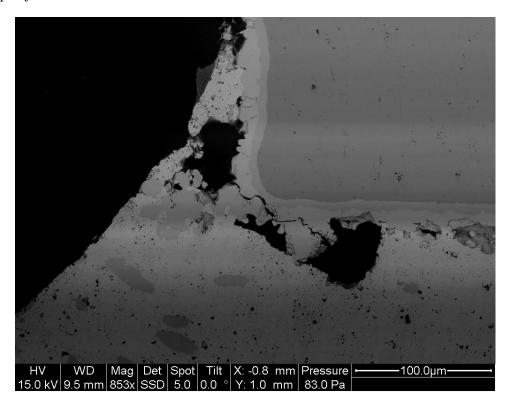

| Figure 4-27: Cracks observed at the corner of TLPS joint; after 1000 drops (no isothermal aging)                                          |

| Figure 4-28: ESEM image of Sn3.5Ag solder joint; after 1000 drops, no isothermal aging                                                    |

| Figure 4-29: ESEM image of crack in Sn3.5Ag solder joint; after 1000 drops, no isothermal aging                                           |

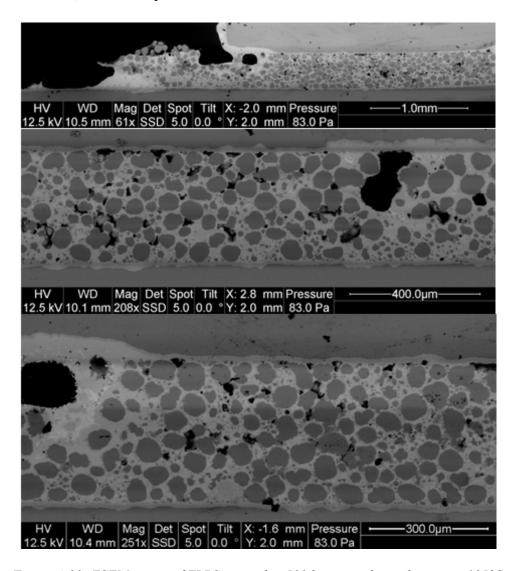

| Figure 4-30: ESEM image of 100 hours isothermally aged TLPS joint; after 1000 drops                                                       |

| Figure 4-31: ESEM image of 100 hours isothermally aged Sn3.5Ag solder joint; after 1000 drops                                             |

| Figure 4-32: Magnified ESEM image of crack in 100 hours isothermally aged Sn3.5Ag solder joint; after 1000 drops (right corner)           |

| Figure 4-33: Magnified ESEM image of crack in 100 hours isothermally aged Sn3.5Ag solder joint; after 1000 drops (left corner)            |

| Figure 4-34: Magnified ESEM image of vertical cracks in 100 hours isothermally aged Sn3.5Ag solder joint; after 1000 drops (right corner) |

| Figure 4-35: Magnified ESEM image of vertical cracks in 100 hours isothermally aged Sn3.5Ag solder joint; after 1000 drops (left corner)  |

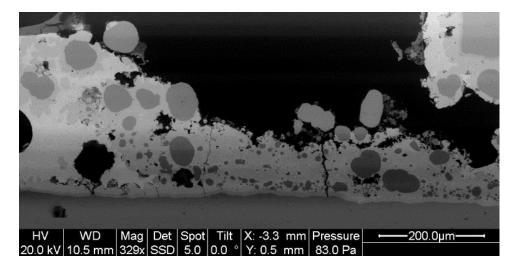

| Figure 4-36: ESEM image of 500 hours isothermally aged TLPS joint; after 1000 drops                                                       |

| Figure 4-37: Magnified ESEM image of vertical crack in 500 hours isothermally aged TLPS joint; after 1000 drops (left corner)             |

| Figure 4-38: ESEM image of 500 hours isothermally aged Sn3.5Ag solder joint; after 1000 drops                                             |

| Figure 4-39: Magnified image of right corner crack presented in Figure 4-38 133                                                           |

| Figure 4-40:Fracture behavior of the Sn3.5Ag solder joint aged for 500 hours after 1000 drops of 1500G acceleration                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-41: Smaller crack propagating from the left side of the Sn3.5Ag specimen after ageing for 500 hours and 1000 drops                                                                                                                                                                                                                                                              |

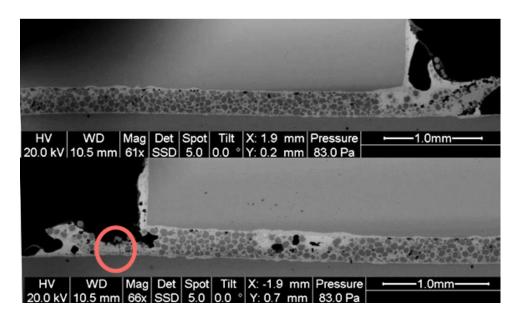

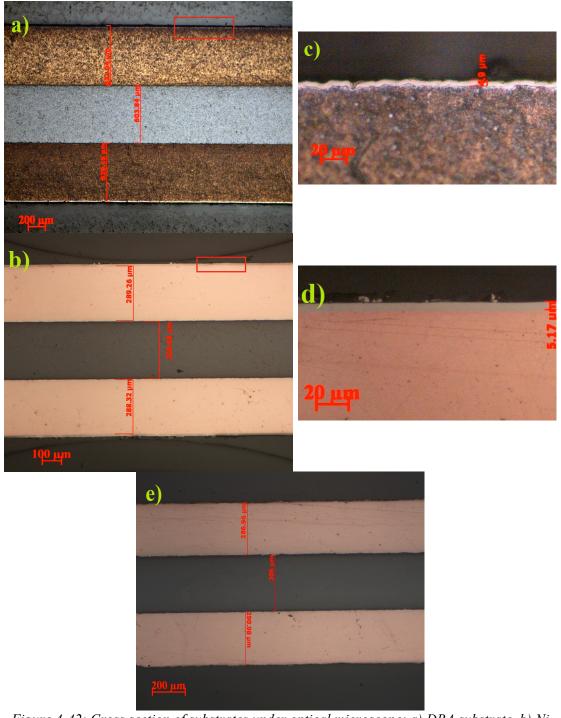

| Figure 4-42: Cross section of substrates under optical microscope: a) DBA substrate, b) Ni plate DBC substrate, c) Nickel plating on the surface of DBA substrate; magnified image of the red-square area shown in image a, d) Nickel plating on the surface of DBC+Ni plated substrate; magnified image of the red-square area shown in image b, e) DBC substrate (without any plating) |

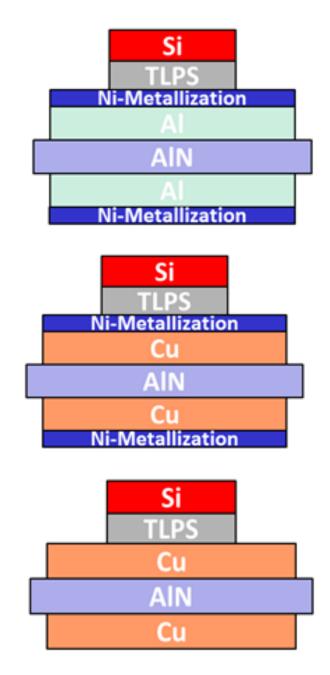

| Figure 4-43: Schematic view of packages designed for the power cycling test 138                                                                                                                                                                                                                                                                                                          |

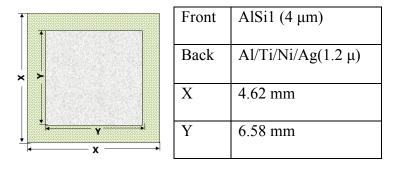

| Figure 4-44: Diodes' dimensions and metallization                                                                                                                                                                                                                                                                                                                                        |

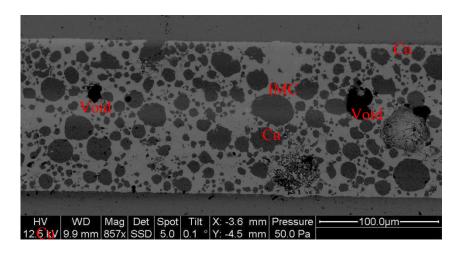

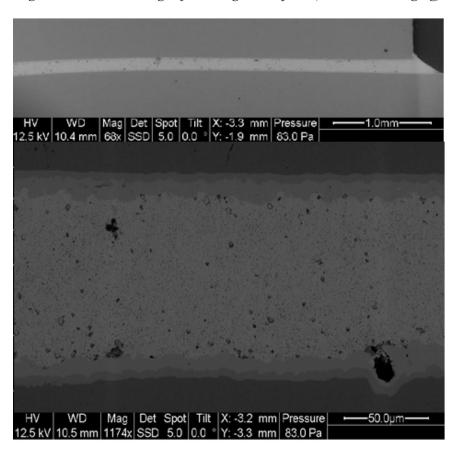

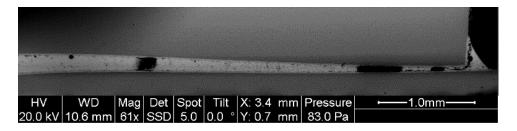

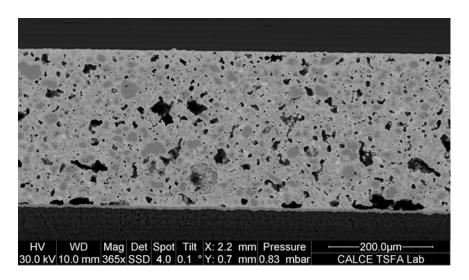

| Figure 4-45: ESEM image of TLPS joint prepared between a DBA substrate and power diode                                                                                                                                                                                                                                                                                                   |

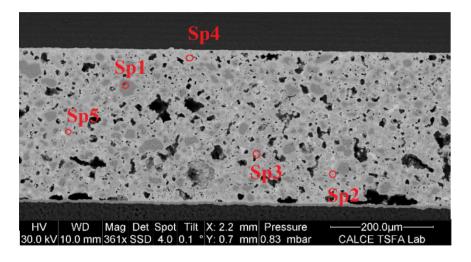

| Figure 4-46: Location of five spectrums analyzed under EDS                                                                                                                                                                                                                                                                                                                               |

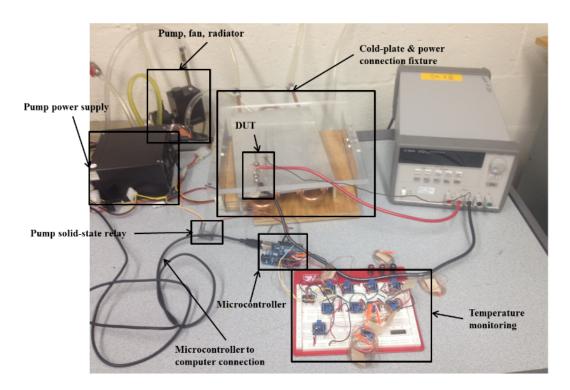

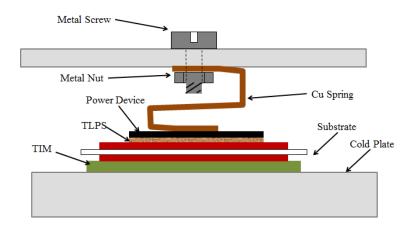

| Figure 4-47: Overall view of the power cycling test setup prepared for testing UUT without wire-bonds                                                                                                                                                                                                                                                                                    |

| Figure 4-48: Schematic of Cu spring connection used instead of wire-bonding 143                                                                                                                                                                                                                                                                                                          |

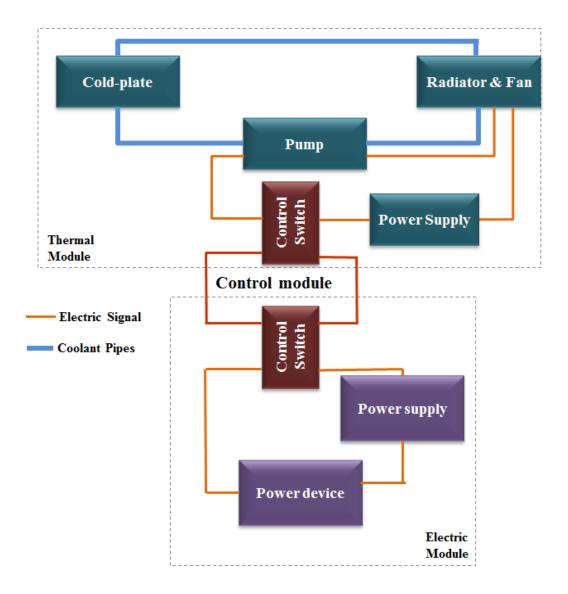

| Figure 4-49: Schematic diagram of three modules considered in power cycling setup                                                                                                                                                                                                                                                                                                        |

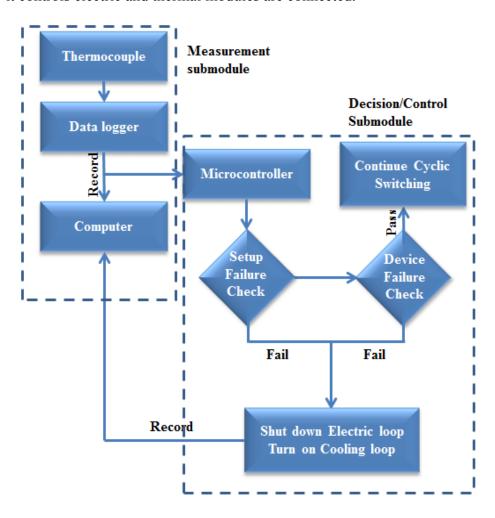

| Figure 4-50: Schematic diagram of logic used in the submodules of the control module and their connection                                                                                                                                                                                                                                                                                |

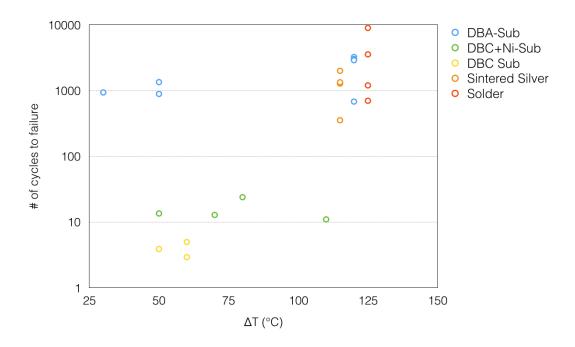

| Figure 4-51: Number of cycles to failure with respect to temperature swing 147                                                                                                                                                                                                                                                                                                           |

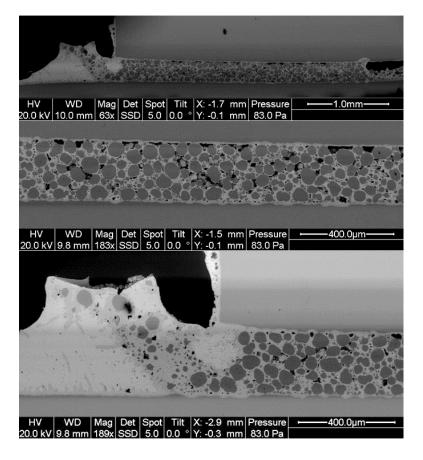

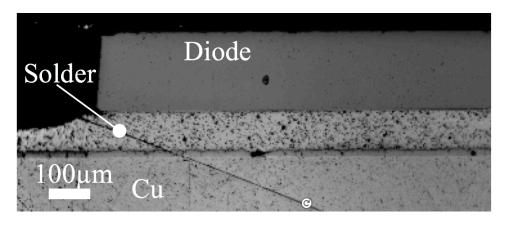

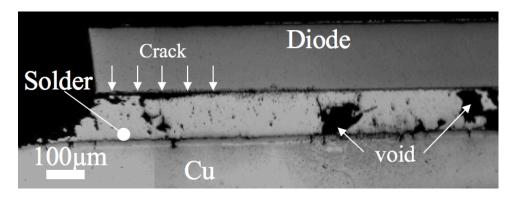

| Figure 4-52: Vertical crack in TLPS joint that induced diode fracture (DBA) 148                                                                                                                                                                                                                                                                                                          |

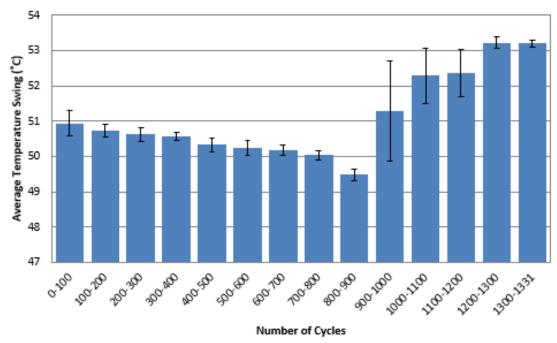

| Figure 4-53: Mean and standard deviation of temperatures measured over 100 cycles period until failure for a DBA package                                                                                                                                                                                                                                                                 |

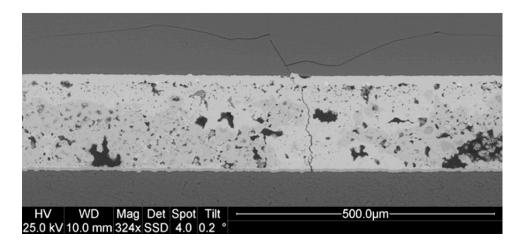

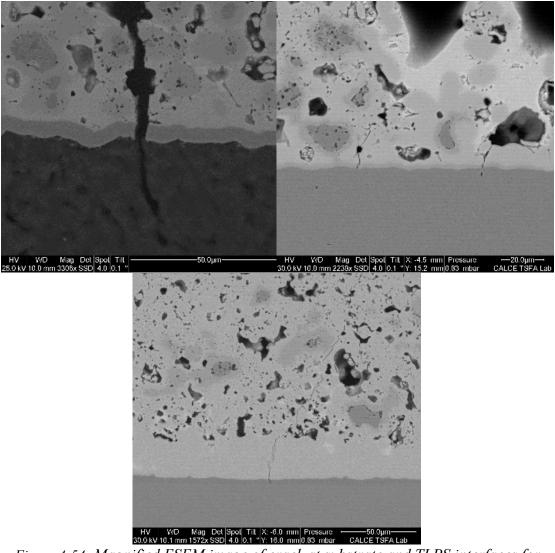

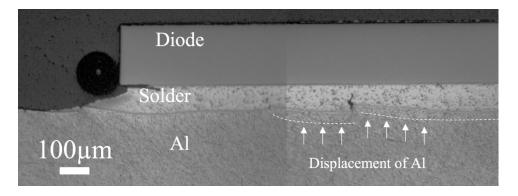

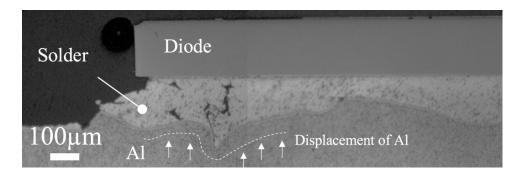

| Figure 4-54: Magnified ESEM image of crack at substrate and TLPS interfaces for three types of substrates (DBA: top left, Ni plated DBC: top right, DBC: bottom). 150                                                                                                                                                                                                                    |

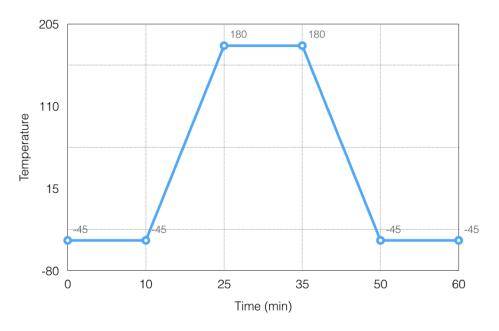

| Figure 4-55: Thermal cycling profile                                                                                                                                                                                                                                                                                                                                                     |

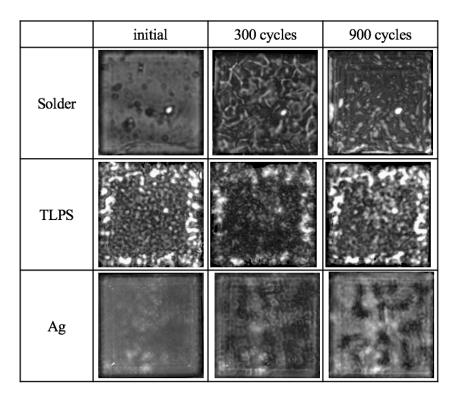

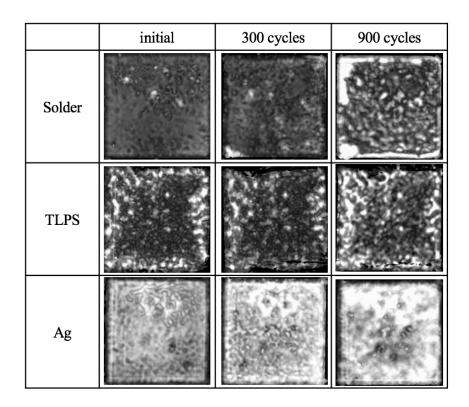

| Figure 4-56: CSAM inspection of under each die-attach technology on DBA substrates                                                                                                                                                                                                                                                                                                       |

| Figure 4-57: CSAM inspection of under each die-attach technology on DBC substrates                                                                                                                                                                                                                                                                                                       |

| Figure 4-58: Cross-section image of the solder die-attach on DBC substrates after 3 cycles |     |

|--------------------------------------------------------------------------------------------|-----|

| Figure 4-59: Cross-section image of the solder die-attach on DBC substrates after 9 cycles |     |

| Figure 4-60: Cross-section image of the solder die-attach on DBA substrates after 3 cycles |     |

| Figure 4-61: Cross-section image of the solder die-attach on DBA substrates after 9 cycles |     |

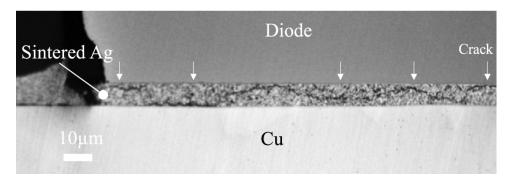

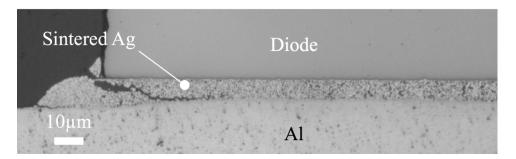

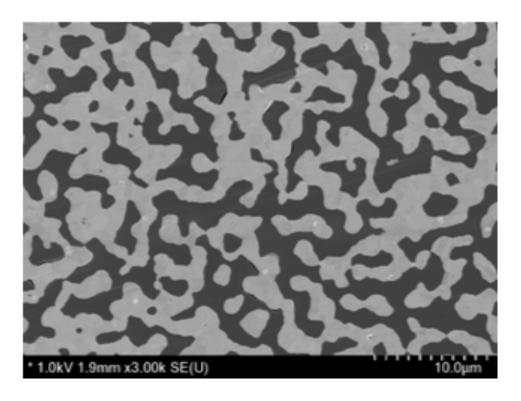

| Figure 4-62: Cross-section image of the sintered-Ag on DBC substrates after 900 cyc        |     |

| Figure 4-63: Cross-section image of the sintered-Ag on DBA substrates after cycles         |     |

| Figure 4-64: Sintered silver high magnification structure                                  | 156 |

| Figure 4-65: Cross-section image of the sintered-Ag on DBC substrates after 900 cyc        |     |

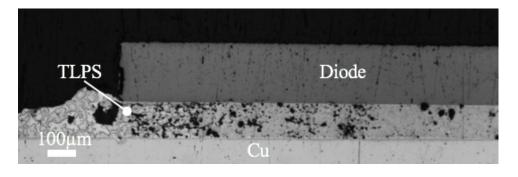

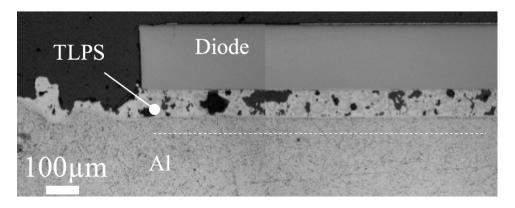

| Figure 4-66: Cross-section image of the Cu-Sn TLP on DBC substrates after 900 cyc          |     |

| Figure 5-1: Layer-wise TLPS processing                                                     | 163 |

| Figure 5-2: Particle based TLPS processing                                                 | 163 |

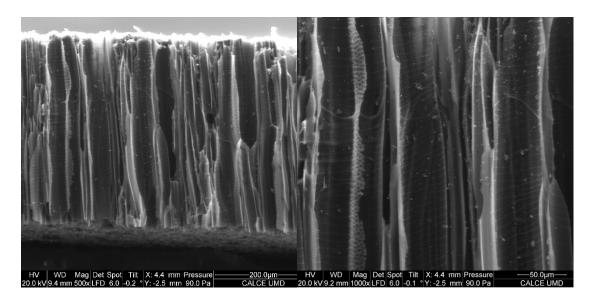

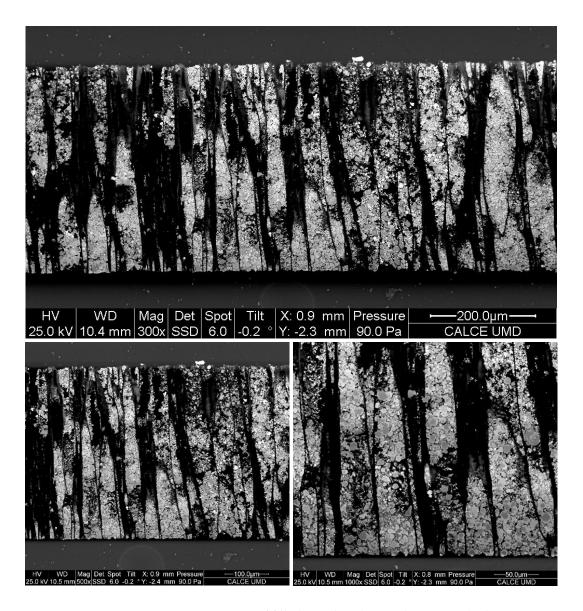

| Figure 5-3: Environmental scanning electron microscopy of wood carbon after grind          | _   |

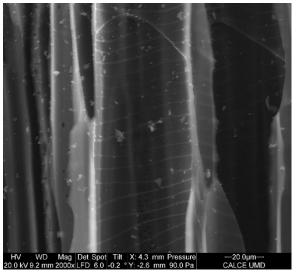

| Figure 5-4: Cross-section of wood carbon channels                                          | 166 |

| Figure 5-5: Top view of filled wood carbon with Cu-Sn paste                                | 168 |

| Figure 5-6: Cross-section view of filled wood carbon with 400 μm thickness 1               | 169 |

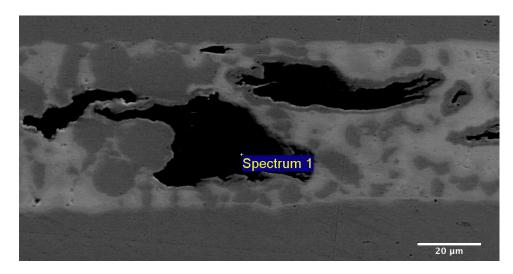

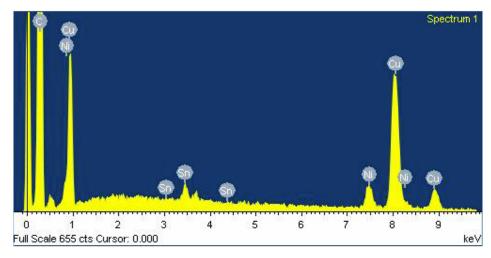

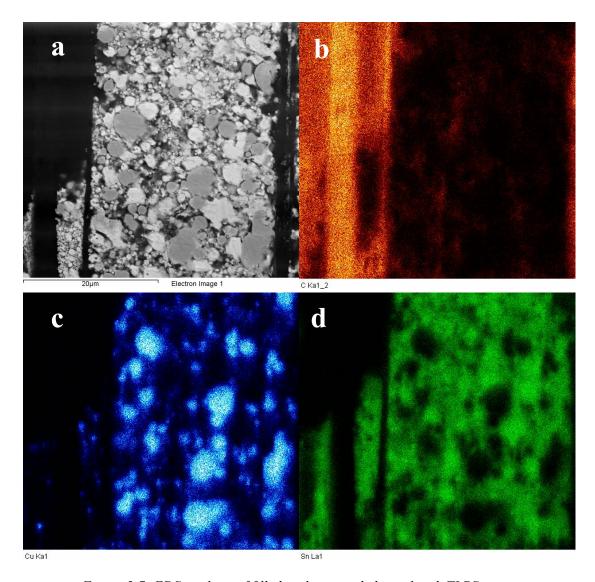

| Figure 5-7: EDS analysis of filled carbon-wood channel with TLPS paste                     | 170 |

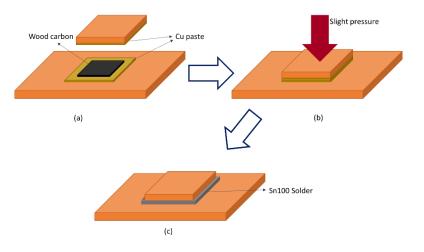

| Figure 5-8: Wood carbon Cu-Sn TLPS sample preparation                                      | 171 |

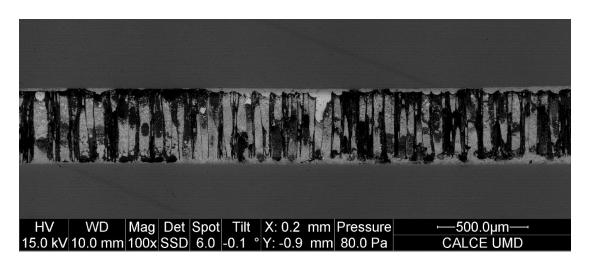

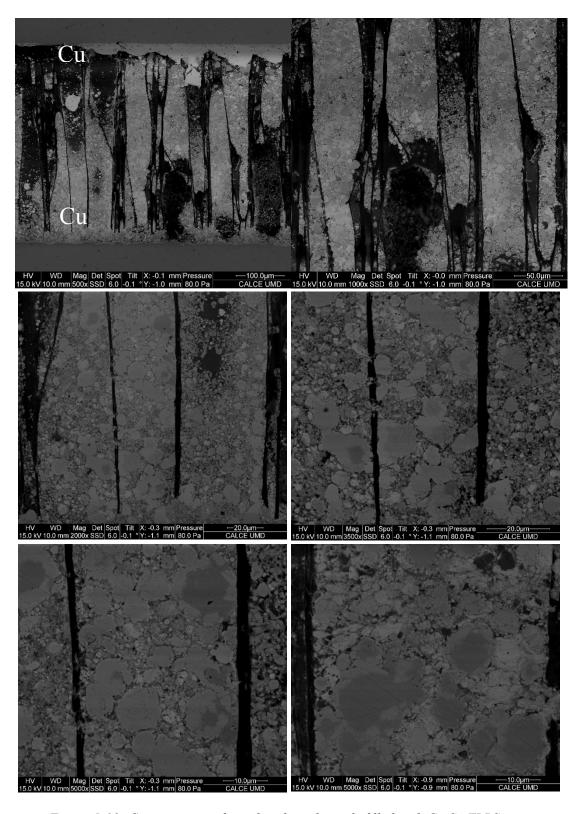

| Figure 5-9: Cross-section of wood carbon Cu-Sn TLPS joint                                  | 172 |

| Figure 5-10: Cross-section of wood carbon channels filled with Cu-Sn TLPS joint 1          | 173 |

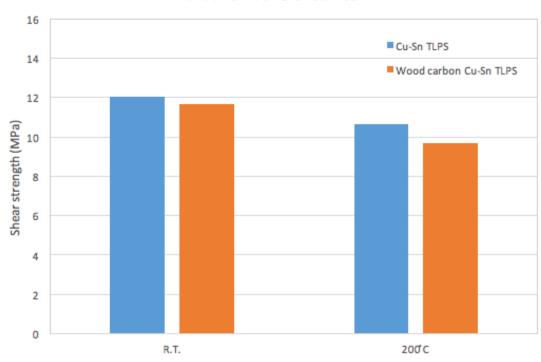

| Figure 5-11: Shear test specimen 1                                                         | 174 |

| Figure 5-12: Test setup                                  | 175 |

|----------------------------------------------------------|-----|

| Figure 5-13: Shear test at room temperature and at 200°C | 175 |

# Chapter 1: High temperature interconnections

The maximum application temperature of power electronic packages is continuously growing due to the increase in their power density, miniaturization and functionality. This is motivated and driven by industrial and commercial applications, such as avionics, space exploration, drilling, and electric vehicles. The traditional application temperature of 125°C [1], [2] for current power electronic devices is a barrier to progress of the aforementioned applications. Thus, new components and technologies with higher application and threshold temperatures are required to produce future generations of power electronics. In recent decades, the move from traditional silicon semiconductor devices with application temperature below 175°C to wide bandgap (WBG) devices increased the limits on the semiconductor device to 475°C [3], [4]. Similar trends are observed for other packaging components, such as substrates and interconnections. New types of power substrates made of AlN and Si<sub>3</sub>N<sub>4</sub> are proposed to improve the reliability of power packages at high temperature applications [5]. The need for high temperature interconnection materials in power packages resulted in a sharp increase in application of high lead containing solders with melting temperatures above 186°C. However, the search for an alternative is essential due to the expanding ban on the application of lead containing materials in electronics because of their hazardous effects on human health.

Currently, some regulations, such as the Restriction of Hazardous Substances (ROHS) 2002/95/EC, End of Life Vehicle (ELV), and Waste Electrical and Electronic Equipment (WEEE) 2002/96/EC restrict the use of lead containing materials in electronic applications aimed at eventually prohibiting their use completely [6]. Power

electronics which use high lead solders are currently exempted due to the lack of a reliable non-hazardous replacement. Different alternatives, such as lead-free tin/gold based solders and sintering based interconnections, were proposed to replace the lead containing solders and deliver a similar performance. A review of the state of the art high temperature interconnection technologies and materials proposed as alternative replacement is provided in the following sections to introduce their potentials and defects for power electronic applications. The rest of this dissertation is focused on developing, processing, screening, and qualifying TLPS for high temperature applications.

#### **Lead-free solders**

High operating temperature is the first factor in the selection of a material for high temperature applications. Eutectic tin-lead alloy as the predominant solder material in classical electronic devices has a melting temperature of  $183^{\circ}$ C. This melting temperature can increase to higher values by increasing the fraction of lead in the solder composition, to even  $312^{\circ}$ C, for extreme temperature application [7]. High melting temperature for a solder has a twofold effect: first, it increases the allowable operating temperature of the package; second, it improves the mechanical properties of the interconnection by decreasing the homologous temperature,  $T_h$  (the ratio of operating temperature over the melting temperature, both expressed in Kelvin). Higher values of this ratio result in poor mechanical properties, such as creep resistance of the solder during performance. For high temperature applications, homologous temperatures lesser than 0.67 are favorable; however, values around 0.85 are not uncommon. Contrary to favorable effects of high melting temperature is the increase in process

temperature. It may damage the other packaging components or result in higher residual stresses due to large temperature differences. Generally, die-attach materials with a processing temperature lower than 300°C are more favorable.

The above factors are considered as parts of the broad category of attach manufacturability. Furthermore, performance/reliability issues are the other essential factors in the selection of interconnection materials. Table 1 shows the properties related to manufacturing and reliability/performance of the solder alloys. Material composition is a major element in defining these properties. The base materials for most of the lead-free solders are Sn, Au, or Bi. Other alloying components are In, Zn, Ag, Sb, Cu, and Mg. Properties of some of the solders made of these materials are presented in the following sections.

Table 1 Properties relevant to manufacturing and reliability/performance of the solder materials [8]

| Manufacturing                             | Reliability and performance        |

|-------------------------------------------|------------------------------------|

| Melting/liquidus temperature              | Electrical conductivity            |

| Wettability (of copper)                   | Thermal conductivity               |

| Cost                                      | Coefficient of thermal expansion   |

| Environmental friendliness                | Shear properties                   |

| Availability and number of suppliers      | Tensile properties                 |

| Manufacturability using current processes | Creep resistance                   |

| Ability to be made into balls             | Fatigue properties                 |

| Copper pick-up rate                       | Corrosion and oxidation resistance |

| Recyclability                             | Intermetallic compound formation   |

| Ability to be made into paste             | _                                  |

## Sn-based alloys

Tin is the base material for a relatively large number of lead-free interconnections. A combination of different properties makes tin an attractive candidate for high temperature applications. The melting temperature of tin is 231°C which is above the

current maximum allowable temperature of power electronic devices and low enough to facilitate the manufacturing process. The ability of tin in wetting different substrates is another advantageous parameter in its application for joint technologies. However, the disadvantageous factors, such as tin pest and tin whiskers, should be considered in application of Sn-based alloys.

Tin pest occurs when a tin crystal structure transforms from one thermodynamically stable condition ( $\beta$ -phase) to the other ( $\alpha$ -phase) with respect to temperature change. Tin has two different crystal structures in the solid state: white tin ( $\beta$ -phase) which has a body-centered tetragonal (BCT) structure and gray tin ( $\alpha$ -phase) which has a diamond cubic crystal structure. The BCT structure is stable at room temperature while the other is thermodynamically stable below 13°C. Therefore, when the temperature falls below the transition temperature the  $\beta$ -phase transforms to lower density  $\alpha$ -phase. This results in large increases in the volume which can result in cracking the structure [8]. The addition of alloy agents showed an effective influence in preventing this phase transformation and its undesirable consequences.

Another limitation is the possibility of whisker growth in the high content tin compositions. Single crystal whiskers can grow, similar to fine wires, up to 0.64 mm high (more rapidly ~51°C). Whiskers do not deteriorate tin solderability. However, they can cause electrical shorts in circuits. Lead has a substantial effect in suppressing tin whisker growth [9]. Here some of the common Sn-based lead-free solders are introduced and their properties discussed.

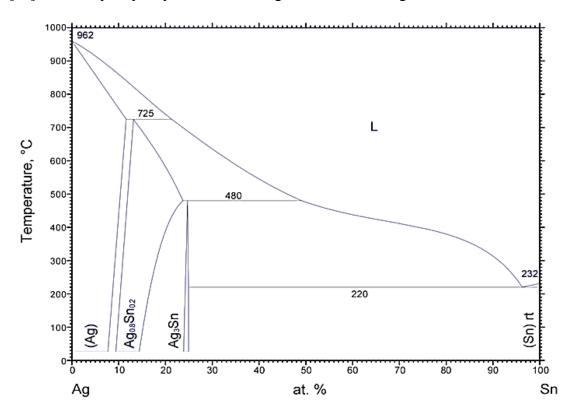

#### Sn-Ag

The phase diagram for the Sn-Ag system has a eutectic point of 221°C at Sn3.5Ag composition, Figure 1-1. This temperature is in appropriate range for the manufacturing purposes of high temperature packages; however, it does not increase the maximum allowable and homologous temperatures significantly. The microstructure of joints prepared from eutectic solidification of Sn3.5Ag is described as dispersed  $Ag_3Sn$  percipitates within  $\beta$ -phase tin matrix [10]. Addition of 1% Zn improves the microstructure by introduction of a finer two phase distribution throughout the joint [11]. This alloy may be prone to whisker growth due to its high tin content.

Figure 1-1: Ag-Sn phase diagram [12]

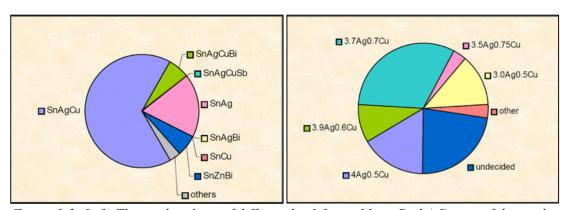

#### Sn-Ag-Cu

The Sn-Ag-Cu (SAC) alloys are the most widely accepted type of lead-free solders. Near eutectic SAC alloy (with 3-4% Ag and 0.5-1.0% Cu) is the most popular type of these alloys, Figure 1-2. Its melting point is 217°C which is close to binary Sn3.5Ag alloy. The addition of Cu improved the wettability and reduced the melting point of near eutectic alloy [13]. The microstructure properties of SAC alloys are affected by the formation of IMC between three constituents. The possible IMC compositions are:  $Ag_3Sn$ ,  $Cu_6Sn_5$ , and  $Cu_3Sn$ . The reaction between Ag and Cu only results in Ag-rich  $\alpha$ -phase and Cu-rich  $\beta$ -phase and without formation of any IMCs [14]. The fine IMCs can strengthen the alloy and improve the fatigue life of the solders. Fatigue life of 3-4 times higher than Pb-Sn eutectic solders are reported for SAC solders [15].

Figure 1-2: Left) The market share of different lead-free solders; Right) Survey of the market share of different types of SAC alloys [16]

The low melting temperature of some of the other Sn-based alloys, such as Sn-Bi (139°C) and Sn-In (117°C), makes them incompatible for high temperature applications. Therefore, they are not considered in this section.

## Au based alloys

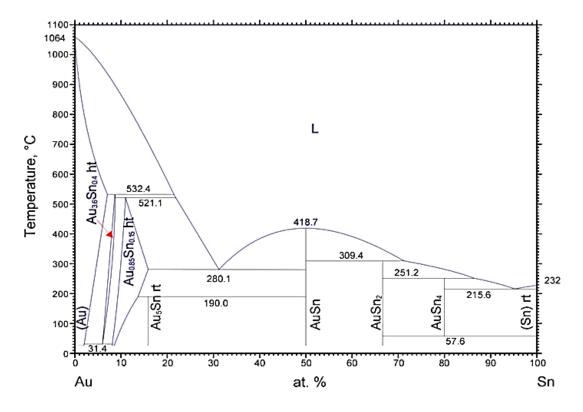

#### Au-Sn

There are several binary eutectic points in the Au-Sn phase diagram, Figure 1-3. Different types of stable IMCs form during the soldering process. The Au-rich solder (Au20wt%Sn) has a eutectic temperature of 280°C which is compatible for high temperature processing requirements. Also, the fluxless bonding process in addition to high fatigue and creep resistance makes this solder a superior choice for electronic and optoelectronic packages [17]. There are two application limitations: first, high cost of gold; second, the transformation in IMCs phases near 190°C which can induce cracks and decrease joint reliability [18]. Au-rich solders are considered as hard solders due to the existence of the brittle  $Au_5Sn$  IMCs [5].

Figure 1-3: Au-Sn phase diagram [12]

#### Off-eutectic Au-Sn

The off-eutectic Au-Sn alloy has a high melting temperature of 400°C and shows excellent performance at high temperature, corrosion resistance, and high electrical and thermal conductivities. Also, the fluxless bonding process makes it an excellent choice for optoelectronic, biomedical and micro-electro-mechanical systems (MEMS) applications. On the other hand, the processing temperature for this type of interconnection is very high and requires specific considerations during manufacturing [19].

#### Au-Ge

Au-Ge similar to the Pb-Sn system has no IMC phases. The eutectic (Au28at%Ge) melting temperature of 360°C and decent ductility makes this material an excellent dieattach material for very high temperature applications. The high ductility solder material makes it an excellent choice for die-attach applications due to its great ability to relax under high thermomechanical stresses. The addition of Sb to this solder decreases the melting temperature and increases the ductility considerably which makes it more appropriate for manufacturing processes [17]. Like all other Au-based solders, the high cost of raw materials is a huge hindrance in its widespread industrial applications.

#### *Zn-based alloys*

#### Zn-Al

Zn6wt%Al has a eutectic melting point of 381°C. The eutectic solidification does not create any IMCs throughout the microstructure. The advantage of using Zn-Al eutectic alloy is the low cost of raw material. In contrast, the corrosive behavior of Zn and poor

wettability of Al and Zn, due to their high oxygen affinity, are the drawbacks of using Zn-Al alloys. Also, this alloy is considered as a hard alloy compared to high lead solders [5].

#### Zn-Sn

Different alloys of Zn-Sn were proposed as high temperature solders (Zn20wt%Sn, Zn30wt%Sn, and Zn40wt%Sn). They have several desirable properties, such as: decent melting temperature (199°C), no IMCs at the equilibrium state, good ductility, excellent electrical properties, superior thermal conductivity (100-106 W/m-K) and oxidation resistance [20], [21]. On Cu substrates, the Zn forms  $CuZn_5$  and  $Cu_5Zn_8$  IMCs with Cu. This results in increased hardness of Zn-Sn alloy which provides higher strength at high temperatures. The main drawback of this alloy, like Zn-Al, is its low corrosion resistance.

#### Bi-based

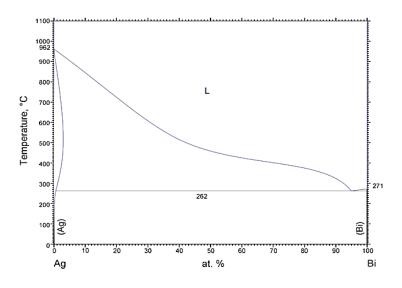

Bismuth has a melting temperature of 270°C which makes it a potential candidate for high temperature applications. Meanwhile, the brittle nature of its microstructure, and its poor bonding strength makes it less attractive for high reliability applications. Alloying bismuth with other elements, such as Ag, Al, Mn, and Cu is considered to improve its performance. Here, Bi-Ag and Bi-Cu-Al-Mn systems are considered and discussed to elaborate their advantages and defects for high temperature power electronic applications.

#### Bi-Ag

The favorable eutectic melting temperature (shown in Figure 1-4) and good workability of the Bi2.6Ag alloy makes it a decent candidate for high temperature applications.

However, its poor thermal conductivity and wetting behavior on Cu substrates are shortcomings of this material [22]. Bi-(11-12)Ag is another system considered to improve some of the shortcomings of Bi-2.6Ag. The higher amount of silver slightly improves the thermal conductivity, seen in Table 2, and the electrical resistance considerably decreases from 116.5  $\mu\Omega$ . cm for Bi-2.5Ag to 86.5  $\mu\Omega$ . cm for Bi-11Ag [23]. Also, the higher content of silver makes strain localization and crack growth harder in the Bi-11Ag systems [24]. Development of this solder system is still in progress to improve the inferior workability, thermal conductivity, and electrical conductivity. Currently, the addition of rare earth metals is considered as a method to improve the wettability and shear strength of the solders [25].

Figure 1-4: Silver-bismuth phase diagram [12]

Table 2: Thermal conductivity of solder systems [22]

| Alloy        | Thermal conductivity (W/m-K) |

|--------------|------------------------------|

| Sn-25Ag-10Sb | 55                           |

| Bi-2.6Ag     | 7                            |

| Bi-12Ag      | 11                           |

| Pb-2Sn-2.5Ag | 53                           |

Up to this point some of the high temperature lead-free solders which can be used as die-attach interconnections in power electronic packages were introduced. In the following sections, some of the materials and interconnection technologies specifically designed as die-attach materials will be discussed.

#### Epoxy adhesives

Epoxy adhesives is the general term for die-attach materials prepared by the suspension of metal particles or flakes in an epoxy carrier. The metal content provides electrical and thermal paths in the component while the epoxy matrix creates a strong bonding between the components. There are two challenges in the application of adhesive components: first, the maximum allowable temperature with respect to melting temperature of the conductive adhesive; and second, poor thermal and electrical conductivity due to poor connections between metal particles or flakes. Thermal and mechanical properties of some commercial epoxy adhesives are listed in Table 3. Silver filled adhesives are high temperature die-attach materials with a decent ability to lower stress concentrations on the die. The main concern in the application of these types of adhesives is the dispersion of silver fillers in the epoxy and inability of the dieattach to provide appropriate thermal and electrical paths for the high temperature applications [25]. Also, the reliability issues, such as die-attach delamination and "popcorn" cracking, become more serious with increasing chip sizes [26]. The popcorn cracking occurs when the moisture absorbed in the polymer evaporates during the surface mounting process and cracks the plastic package or the semiconductor die. Efforts are underway to improve the polymers used in the manufacturing of epoxy adhesives to assure high performance and reliability during high temperature applications.

*Table 3: Thermal and mechanical properties of selected die-attach materials [27]*

| Material             | $T_{m(^{\circ}C)}$ | $T_{\text{max (°C)}}$ | K(W/mK) | CTE (10-6/°C) | G (GPa) |

|----------------------|--------------------|-----------------------|---------|---------------|---------|

| P-1011 <sup>1</sup>  | -                  | 350                   | 1.29    | 37            | -       |

| H20E-HC <sup>1</sup> | -                  | 300                   | 3.5     | 26            | -       |

| H20E-HC <sup>1</sup> | -                  | 200                   | 9.96    | 53            | -       |

| $QMI-3555R^2$        | ~400               | 300                   | 80      | 16            | 11.5    |

| FO-3,                | 450                | 200                   | 60      | 25            |         |

| FO-13 <sup>3</sup>   | 450                | 300                   | ~60     | 25            | -       |

| Tap 3M <sup>4</sup>  | -                  | 250                   | -       | -             | 0.1     |

#### Sintering technologies

The sintering process is densification and growth of the initial grains by application of thermal energy. The driving force for this process is reduction of interfacial energies [28]. Different classifications based on the state of the constituents or process parameters can be considered for categorizing the sintering processes, such as pressureless and pressure-assisted processes or solid-state sintering and liquid phase sintering. The latter is the most common type for dividing sintering processes and indicates the state of the constituent during the sintering process.

In solid-state sintering, all the components are in solid state. This method is mostly used in power metallurgy in which the metal particles/flakes are mixed and processed under temperature and pressure. In solid-state sintering, the process temperature is lower than the melting temperature of all the paste constituents.

<sup>&</sup>lt;sup>1</sup> Adhesive made by Epoxy Technology

<sup>&</sup>lt;sup>2</sup> Silver filled glass made by Loctite <sup>3</sup> Silver filled glass made by ITME, Poland.

<sup>&</sup>lt;sup>4</sup> Thermally conductive tape made by 3M

In liquid phase sintering, at least one of the components melts during the sintering. The processing temperature for liquid phase sintering is above the melting temperature of at least one of the paste ingredients. There are different types of liquid sintering, such as viscous flow sintering and transient liquid phase sintering. The viscous flow sintering occurs when the volume of the liquid phase is large enough to completely mix with solid particles. During this process, the shape of the grains does not change. In the transient liquid phase sintering process, the liquid phase only exists in the early stages of sintering and the sintering completes by solid-state sintering [28].

The low process temperature of sintering technology in contrast with the high application temperature makes them a potential candidate for high temperature applications. For example, the solid-state sintered silver joints can be processed at low temperatures near or less than 300°C and they are stable up to 960°C, which is the melting temperature of silver. Different aspects of utilization of sintering technologies in power electronic applications and the important parameters in their preparation, such as binder, and particle sizes, in addition to process parameters, such as temperature and pressure are discussed in the following chapters.

# Research gap and problem statement

There is a growing demand for power electronics with higher application temperature due to continuous increase in power density, functionality, and miniaturization. This has inspired more advanced and new packaging technologies. Additionally, the expanding ban on application of lead-containing solders, as the conventional high-temperature power electronics die-attach material, necessitates a new nonhazardous alternative.

In this chapter, the current state of the art interconnection materials and their processing conditions have been introduced. The options can be classified into three broad categories: lead-free solders, epoxy adhesives, and sintered joints. The first group can be used either as solder or die-attach material; however, the other two are specifically designed for die-attach applications. The advantages of different options from processing, and mechanical, electrical, and thermal features, in addition to their shortcomings, which prevented them from completely replacing lead-containing solders were discussed.

One of the introduced technologies with considerable potential for industrial applications is sintering. Sintering provides the feasibility of processing high melting temperature materials at alternatively low processing temperature<sup>1</sup>. Also, it is possible to use different types of sintering methods based on the processing requirement. Sintering can be done fully in solid-state or solid-liquid interaction. Also, it is possible to have only a single material or a combination of different materials. These features provide great controllability over processing and final properties; however, the inadequate reliability information, complicated processing procedure, and poor modeling approaches limit their potential. The main goal of this dissertation is to provide improvement in processing, modeling, and reliability testing of TLPS joints through experimental, analytical, and simulation approaches. Therefore, the following objectives were considered:

1) Creating a simple and repeatable TLPS processing approach which does not require specific operator training or any specific environment

\_

<sup>&</sup>lt;sup>1</sup> The processing temperature is considerably lower than melting temperature of sintered interconnection

- 2) Creating an accurate joint screening and composition monitoring approaches to evaluate the quality of processed interconnections

- 3) Increasing the application of TLPS joints to large size areas

- 4) Introducing a new phase field modeling method to simulate microstructure evolution during TLPS processes

- 5) Comparing different processing methods by phase filed modeling (PFM) simulation to find the one with better potential for industrial applications

- 6) Evaluating performance of TLPS joints under dynamic loads (drop-shock) and compare with competition

- 7) Evaluating performance of TLPS joints under power and thermal cycling loads and compare with other interconnection technologies

- 8) Introducing an innovative and novel approach to improve conventional TLPS interconnections

Based on these objectives the following outline is considered for this dissertation:

### **Outline**

In Chapter 2, different aspects of solid-state and liquid-state sintering from the fabrication and processing point of view are introduced and analyzed. The effects of different factors in paste preparation, such as paste ingredients, and processing factors, like temperature and sintering environment, are evaluated. Then, common processing methods used in the literature are introduced and their shortcomings in becoming an industrial prevalent method are discussed. Finally, a new one-step TLPS processing method is introduced. The one-step TLPS processing procedure does not require extensive operator training or special sintering environment or chamber and creates high quality joints. Furthermore, unlike conventional methods, it can create low voiding large area joints. Additionally, tertiary elements can be integrated in the joint without any change in processing.

Chapter 3 introduces common solutions to solid-liquid interaction problems. Two methods of sharp-interface problem and PFM are introduced. PFM has great potential for application, such as eutectic solidification and TLPS. The fundamentals of this method are presented and a new approach is introduced by the author to improve its application to TLPS modeling. Finally, copper-tin joints which are processed with two-step and one-step processing methods are modeled with PFM and the microstructure evolution results are presented. This provides significant insight in process completion and selection of appropriate processing methods.

Chapter 4 includes screening and reliability testing methods specifically designed for die-attach interconnections. First, a joint quality screening method using image processing is introduced and later, this is extended to application of machine-learning methods to accurately define joint material composition. Then, different reliability tests, such drop-shock, and power and thermal cycling are considered for evaluating the performance of TLPS interconnections. For each test, a specific procedure is designed and applied. The samples are cross-sectioned and examined at the end of the process to define failure mechanism and its root cause.

Chapter 5 introduces a novel TLPS interconnection method and material involving copper and tin micro-particles embedded in wood carbon channels. This provides a high-conductivity material with comparable mechanical properties to common TLPS joints. The processing method is explained comprehensively and the mechanical integrity is tested by shear strength test at room and high temperature.

Finally, Chapter 6 summarizes the contributions and findings of this dissertation. Also, potential future works to further improve the current state of the art based on the results of this dissertation are discussed.

Chapter 2: Sintered joints, fundamentals, processing and development

#### Introduction

The advent of wide band-gap devices (GaN, SiC) has made high operating temperatures more achievable in power electronic components. This creates the opportunity to have higher power densities, better functionality and miniaturization. However, this demands compatible packaging components which work efficiently under the new conditions. In the case of interconnections, the expanding ban on the application of high-lead solders, which are the conventional high-temperature interconnection in power electronic applications, have increased the priority of finding a reliable and environmentally friendly high temperature interconnects.

In the previous chapter, the current state-of-the-art alternatives for high-lead solders were introduced. The options were categorized into three classes of lead-free solders, epoxy adhesives and sintering technologies [29], [30]. These are still in the development and qualification research phases to potentially fully substitute high-lead solders and even grow the application limits beyond current power electronics. In this chapter, the focus will be on sintering technologies. First, the two major types of sintering, solid-state and liquid-solid inter-diffusion sintering will be introduced and then, the paste constituents, processing factors, and their effect on the joint quality will be discussed.

Finally, a novel method of processing will be introduced to fabricate high quality transient liquid phased sintered joints. The method is designed based on two factors:

simplicity and repeatability. A major issue with most sintering systems is the complicated processing which requires detailed attention to many factors. A minor change in one of these factors results in an unacceptable decrease in the quality of joint microstructure. This generally depicts an increase in pore content of the joint or high amount of reactants in the final products. The main objective is to design a simple processing, like solders that creates repeatable results. Also, this method provides the potential to involve a more diverse range of reactants or passive elements.

#### **Solid-state Sintering**

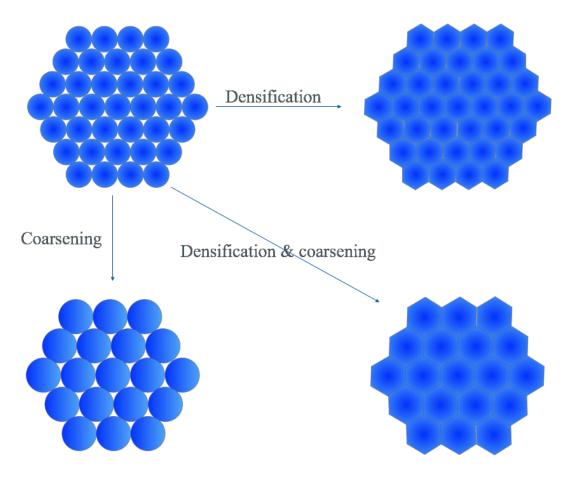

Reduction in interfacial energy is the main driving force behind a sintering process [28]. Solid particles, generally from one phase, start forming solid bonds when heated. The sintering temperature is below the melting point of the reactant material. The final product will have a melting temperature equal to the reactant. For the case of silver sintering, the melting temperature is 960°C while the sintering temperature is ~300°C. The process includes two simultaneous steps of densification and coarsening as shown in Figure 2-1. Densification is the process of increasing joint density by reducing the pores. Coarsening or grain growth is the process of increasing average grain size by boundary motion or Oswald ripening. Smaller size particles and application of pressure during processing expedites these processes and decreases the required heat. Most of the sintering studies were performed on ceramic, but in recent decades silver (and copper) sintering became of interest for interconnection applications.

Figure 2-1: Solid-state sintering stages

Silver solid-state sintering methods developed a long time ago, but due to the advent of nanoparticles they became more and more of interest for electronic applications. In the following sections the evolution of solid-state sintering and its application in electronics packaging is analyzed. Many concepts, such as paste preparation, and effective factors can be easily applied to solid-liquid sintering.

# Microscale Silver Sintering

In the late 1980s, a die-bonding technique based on solid diffusion of metals was introduced for fabrication of power electronic components [31]. This method was initially termed the Low Temperature Joining Technology (LTJT). In this method, microscale metal (silver) flakes are sintered under uniaxial or hydrostatic pressure at

temperature levels generally lower than 300°C. The application of this method in attachment of Molybdenum disks to silicon wafers was first introduced by Schwarzbauer and Kuhnert [32], [33] as a four-step process. First, the joining paste was prepared through the dispersal of silver flakes (20-30 um) in an organic binder. Second, the produced paste was screen or stencil printed on the molybdenum disk surface. Third, the paste was dried in open air at 250°C. Lastly, the silicon wafer was mounted on the dried paste and sintered under 10-40MPa at 200-250°C until bonding had occurred. The fabricated joints showed acceptable mechanical stability and shear strength up to 100 MPa. It is demonstrated that thermomechanical stresses between the molybdenum disk and the Silicon wafer could be avoided by controlling the process temperature. This minimizes the bowing in the final product [34].

Successful application of silver flakes in the fabrication of power components inspired the utilization of LTJT in the attachment of power electronic devices. Various advantages were mentioned in the literature [35] for sintered joints in power electronic applications, such as:

- 1. Acceptable wetting

- 2. Movement control of chips (no swimming)

- 3. High thermal-conductivity

- 4. High reliability

- 5. Low microscopic void content

Properties of microscale sintered joints were evaluated and compared with *Sn63Pb37* from thermal, mechanical, and electrical aspects. The results showed promising properties and potential for industrial applications [36]. In a study, the two main failure mechanisms of interconnections, joint detachment and wire-bond lift off were studied

in single- and double-sided sintered diode chips [37]. In the double-sided case, two 1 mm silver bands with 100 µm thickness replaced the Al wire bond. The results indicate that bond-wire lift-off and aluminum reconstruction are the main failure mechanisms of single-sided sintered assemblies under power cycling conditions. The life of double-sided LTJT assemblies is reported to be nearly double that of single-sided assemblies; however, the main failure mechanism of the double-sided assemblies is not addressed by the authors. The high caliber mechanical and thermal performance of LTJT joints showed potential for high temperature electronic applications. Numerous research projects were conducted to improve the manufacturability and reliability of LTJT joints. A major improvement was shown with the application of nanoscale silver particles mixed with or applied instead of microscale silver particles.

## Nanoscale Silver Sintering

The advent of nanoscale silver particles boosted solid-state sintering and their application in power electronics industry. The use of nanoscale silver particles in LTJT significantly improves the sintering conditions required to process a high-quality joint. Decreasing particle sizes creates an opportunity to revise other influential factors, such as processing pressure and temperature. In a case study, Lu et al. [38] assessed the dependency of joint density on influential factors, such as pressure and kinetic factors. Two types of sintering strategies were considered: first, microscale (1-3µm) silver particles were sintered at a low temperature (240°C) under 40 MPa; and second, processing nanoscale (10-30 nm) silver particles at 280°C without pressure. Both joints showed acceptable density and high thermal-conductivity. They concluded that utilization of smaller particles results in similar density with lower or no pressure

during processing. Extensive research in processing and optimization of sintered joints is ongoing; recently, several sintering pastes have been commercialized [39].

The following sections concentrate on silver sintering, its requirements, and properties; however, alternative materials (such as Cu) are discussed separately at the end of this section to evaluate the progress in their manufacturability, as well as their relative advantages and disadvantages over silver particles. The "sintering" described in the first part of this article indicates "silver sintering" unless otherwise mentioned.

### Liquid Sintering