#### **ABSTRACT**

Title of dissertation: MODELING AND MAPPING OF OPTIMIZED

SCHEDULES FOR EMBEDDED SIGNAL PROCESSING SYSTEMS

Hsiang-Huang Wu, Doctor of Philosophy, 2013

Dissertation directed by: Professor Shuvra S. Bhattacharyya

Department of Electrical and Computer Engineering,

and Institute for Advanced Computer Studies

The demand for Digital Signal Processing (DSP) in embedded systems has been increasing rapidly due to the proliferation of multimedia- and communication-intensive devices such as pervasive tablets and smart phones. Efficient implementation of embedded DSP systems requires integration of diverse hardware and software components, as well as dynamic workload distribution across heterogeneous computational resources. The former implies increased complexity of application modeling and analysis, but also brings enhanced potential for achieving improved energy consumption, cost or performance. The latter results from the increased use of dynamic behavior in embedded DSP applications. Furthermore, parallel programming is highly relevant in many embedded DSP areas due to the development and use of Multiprocessor System-On-Chip (MPSoC) technology. The need for efficient cooperation among different devices supporting diverse parallel embedded computations motivates high-level modeling that expresses dynamic signal processing behaviors and supports efficient task scheduling and hardware mapping.

Starting with dynamic modeling, this thesis develops a systematic design methodology that supports functional simulation and hardware mapping of dynamic reconfiguration based on Parameterized Synchronous Dataflow (PSDF) graphs. By building on the DIF (Dataflow Interchange Format), which is a design language and associated software package for developing and experimenting with dataflow-based design techniques for signal processing systems, we have developed a novel tool for functional simulation of PSDF specifications. This simulation tool allows designers to model applications in PSDF and simulate their functionality, including use of the dynamic parameter reconfiguration capabilities offered by PSDF. With the help of this simulation tool, our design methodology helps to map PSDF specifications into efficient implementations on field programmable gate arrays (FPGAs). Furthermore, valid schedules can be derived from the PSDF models at runtime to adapt hardware configurations based on changing data characteristics or operational requirements. Under certain conditions, efficient quasi-static schedules can be applied to reduce overhead and enhance predictability in the scheduling process.

Motivated by the fact that scheduling is critical to performance and to efficient use of dynamic reconfiguration, we have focused on a methodology for schedule design, which complements the emphasis on automated schedule construction in the existing literature on dataflow-based design and implementation. In particular, we have proposed a dataflow-based schedule design framework called the dataflow schedule graph (DSG), which provides a graphical framework for schedule construction based on dataflow semantics, and can also be used as an intermediate representation target for automated schedule generation. Our approach to applying the DSG in this thesis emphasizes schedule construction as a design process rather than an outcome of the synthesis process. Our

approach employs dataflow graphs for representing both application models and schedules that are derived from them. By providing a dataflow-integrated framework for unambiguously representing, analyzing, manipulating, and interchanging schedules, the DSG facilitates effective codesign of dataflow-based application models and schedules for execution of these models.

As multicore processors are deployed in an increasing variety of embedded image processing systems, effective utilization of resources such as multiprocessor system-on-chip (MPSoC) devices, and effective handling of implementation concerns such as memory management and I/O become critical to developing efficient embedded implementations. However, the diversity and complexity of applications and architectures in embedded image processing systems make the mapping of applications onto MPSoCs difficult. We help to address this challenge through a structured design methodology that is built upon the DSG modeling framework. We refer to this methodology as the DEIPS methodology (DSG-based design and implementation of Embedded Image Processing Systems). The DEIPS methodology provides a unified framework for joint consideration of DSG structures and the application graphs from which they are derived, which allows designers to integrate considerations of parallelization and resource constraints together with the application modeling process. We demonstrate the DEIPS methodology through cases studies on practical embedded image processing systems.

# MODELING AND MAPPING OF OPTIMIZED SCHEDULES FOR EMBEDDED SIGNAL PROCESSING SYSTEMS

by

#### Hsiang-Huang Wu

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2013

Advisory Committee: Professor Shuvra S. Bhattacharyya, Chair/Advisor Professor Manoj Franklin Professor Andrew Harris Professor Jeffery Hollingsworth Professor Alan Sussman, Dean's Representative © Copyright by Hsiang-Huang Wu 2013

#### Dedication

This thesis is dedicated to my parents and sister, who support me to pursuit the Ph.D. degree. It is also dedicated to Jie Ni, who has accompanied me to get through all the hard time.

## Table of Contents

| Li | st of F                                  | igures                                                                                                                                                                                                                                                             | V                                                                          |

|----|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 1  | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | duction  Key Problems in the Design and Implementation of Embedded Systems  Dataflow Models  Scheduling for Dataflow Models  Design Techniques for Multiprocessor Systems-on-Chip  Contributions of this Thesis                                                    | 1<br>4<br>7<br>8<br>13                                                     |

| 2  | -                                        | d Prototyping for Digital Signal Processing Systems using Parameterized hronous Dataflow Graphs  PSDF Operational Semantics                                                                                                                                        | 16<br>16<br>20<br>21<br>23<br>26                                           |

| 3  | Grap 3.1 3.2 3.3 3.4 3.5 3.6 3.7 3.8 3.9 | Adaptive Dataflow Schedule Graphs Concurrent Dataflow Schedule Graphs Adaptive Dataflow Schedule Graphs Experimental Results 3.9.1 Simulation Time Improvement 3.9.2 Hardware Architecture Mapping from a DSG Steleule Dataflow Software Implementation Extensions | 32<br>32<br>34<br>35<br>36<br>40<br>41<br>44<br>51<br>52<br>55<br>58<br>62 |

| 4  | Multi plica 4.1 4.2 4.3 4.4              | Introduction and Related Work                                                                                                                                                                                                                                      | 666<br>669<br>70<br>72<br>74                                               |

|    | 4.5    | Comparison to Other Dataflow-Based Modeling Techniques for Image           |    |

|----|--------|----------------------------------------------------------------------------|----|

|    |        | Processing                                                                 | 9  |

|    | 4.6    | Case Study: Background Subtraction on a Multicore Digital Signal Pro-      |    |

|    |        | cessor                                                                     | 30 |

|    |        | 4.6.1 Application Modeling                                                 | 32 |

|    |        | 4.6.2 Macro-Pipeline Mapping Structure                                     | 34 |

|    |        | 4.6.3 Fork-Join Mapping Structure                                          | 37 |

|    |        | 4.6.4 Combination of Macro-Pipelined Execution and Fork-Join Paral-        |    |

|    |        | lelism                                                                     | 39 |

|    | 4.7    | Case Study: Image Registration on a Multicore Digital Signal Processor . 9 | 0  |

|    | 4.8    | Summary                                                                    | 2  |

| 5  | Con    | lusion and Future Work 10                                                  | )2 |

| Bi | bliogi | phy 10                                                                     | )6 |

# List of Figures

| 1.1  | Shared memory model                                                                                                                            | 9          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2  | An example of the parallel programming patterns <i>map</i> and <i>reduce</i>                                                                   | 10         |

| 1.3  | An example of dataflow modeling                                                                                                                | 11         |

| 1.4  | Fork-join model                                                                                                                                | 12         |

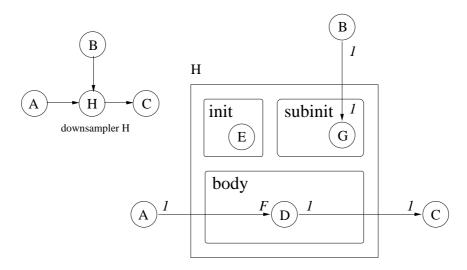

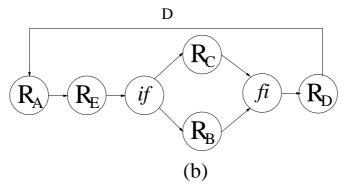

| 2.1  | A PSDF Downsampler                                                                                                                             | 19         |

| 2.2  | An illustration of parameter propagation in PSDFsim                                                                                            | 21         |

| 2.3  | FPGA/ASIC design flow overview                                                                                                                 | 23         |

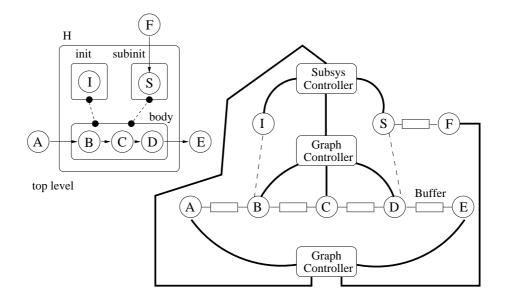

| 2.4  | Interface and control architecture for a circuit block                                                                                         | 26         |

| 2.5  | An illustration of subsystem-level hardware mapping                                                                                            | 27         |

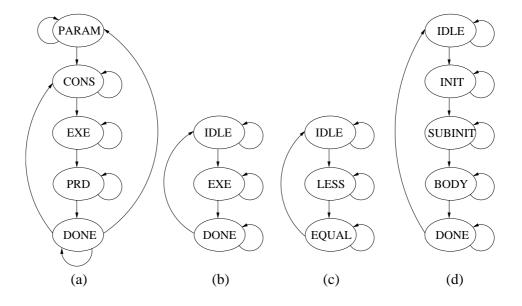

| 2.6  | Finite state machines for (a) a circuit block, (b) a graph controller, (c) consumption and production circuits, and (d) a subsystem controller | 28         |

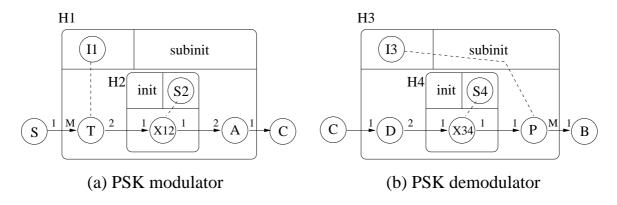

| 2.7  | PSDF-based model of PSK modulator and demodulator                                                                                              | 28         |

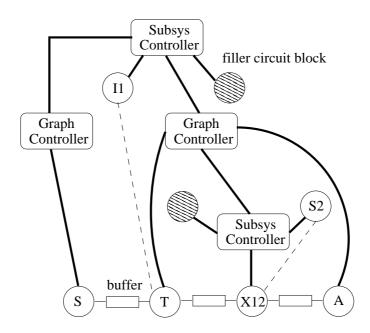

| 2.8  | Hardware mapping for modulator                                                                                                                 | 30         |

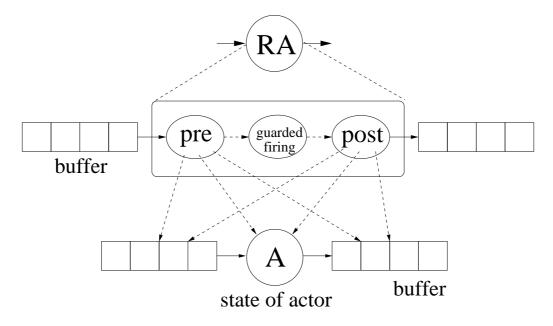

| 3.1  | The internal structure of an RA                                                                                                                | 37         |

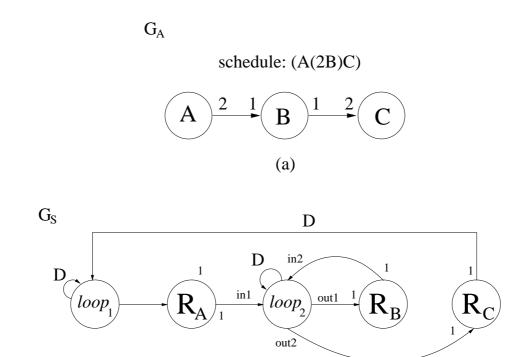

| 3.2  | (a) An SDF graph (b) A design example of an SDSG for the single ap-                                                                            |            |

|      | pearance schedule $(A(2B)C)$                                                                                                                   | 45         |

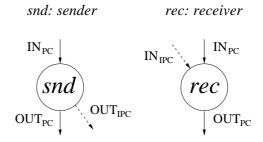

| 3.3  | The snd and rec actors                                                                                                                         | 46         |

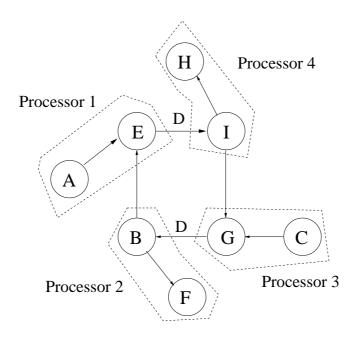

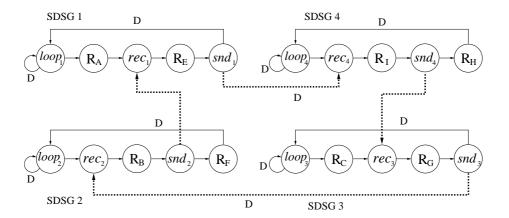

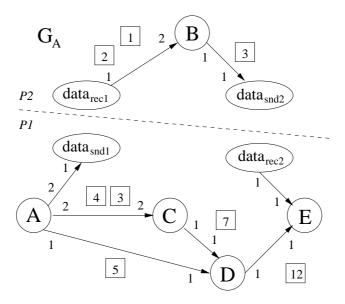

| 3.4  | An application graph and a partitioning of the graph across four processors.                                                                   | 48         |

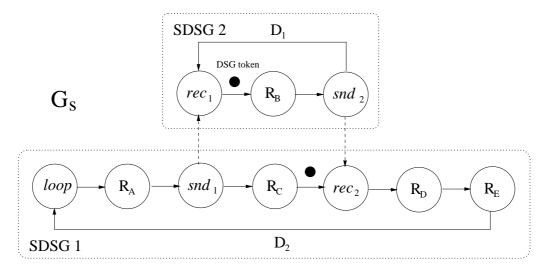

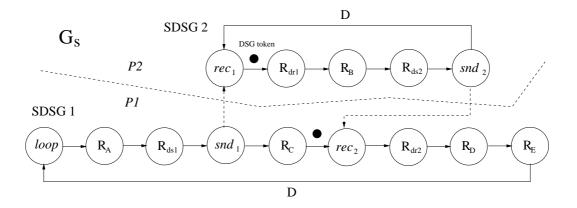

| 3.5  | A CDSG representation of a multiprocessor schedule that corresponds to                                                                         | 4.0        |

|      | the partitioning result shown in Figure 3.4                                                                                                    | 49         |

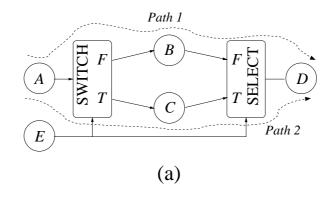

| 3.6  | (a) A dataflow-based if-then-else construct. (b) An adaptive DSG                                                                               | <b>-</b> 0 |

| 2.7  | for this construct.                                                                                                                            | 50         |

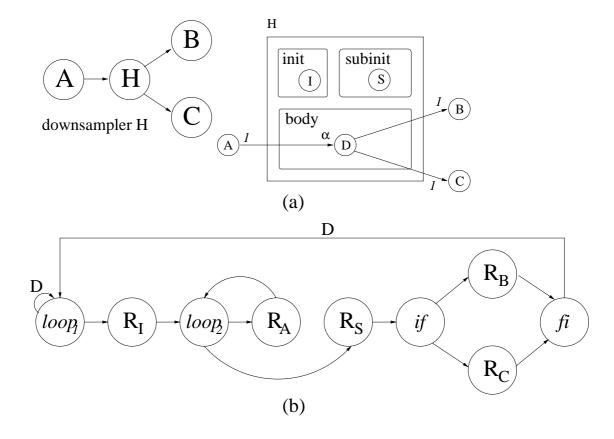

| 3.7  | (a) A PSDF model for a reconfigurable phase shift keying application; (b)                                                                      | - 1        |

| 2.0  | an ADSG representation for implementing this application                                                                                       | 54         |

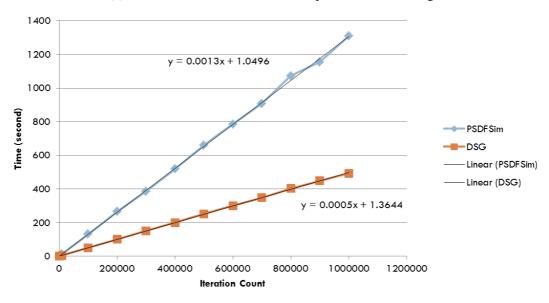

| 3.8  | Performance comparison between DSG-based quasi-static scheduling, and                                                                          | - (        |

| 2.0  | dynamic scheduling                                                                                                                             | 56         |

| 3.9  | RPSK modulator                                                                                                                                 | 57         |

|      | Hardware architecture mapping for a DSG                                                                                                        | 59<br>61   |

|      | RPSK system and alternative DSGs                                                                                                               | 01         |

| 3.12 | ure 3.11(c)                                                                                                                                    | 64         |

|      | ule 5.11(c)                                                                                                                                    | 04         |

| 4.1  |                                                                                                                                                | 73         |

| 4.2  | CDSG for Figure 1.3                                                                                                                            | 75         |

| 4.3  | Illustration of synchronization for the partitioned dataflow graph of Fig-                                                                     |            |

|      | ure 1.3                                                                                                                                        | 76         |

| 4.4  | The Concurrent Dataflow Schedule Graph (CDSG) for Figure 4.3                                                                                   | 77         |

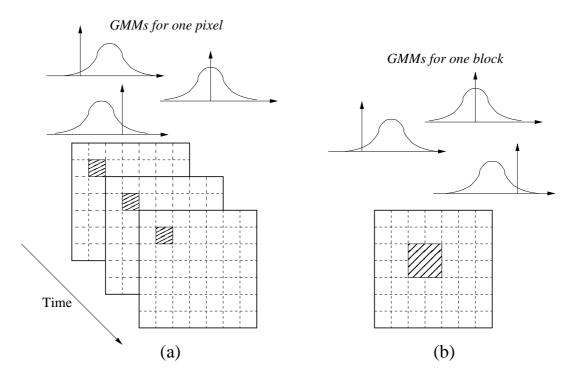

| 4.5  | (a)Temporal GMMs; (b)Spatial GMMs                                                                                                              | 81         |

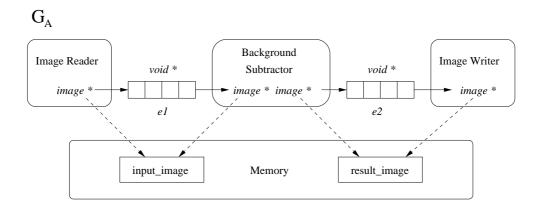

| 4.6  | LiDE-based application model for macro-pipelined background subtraction.                                                                       | 84         |

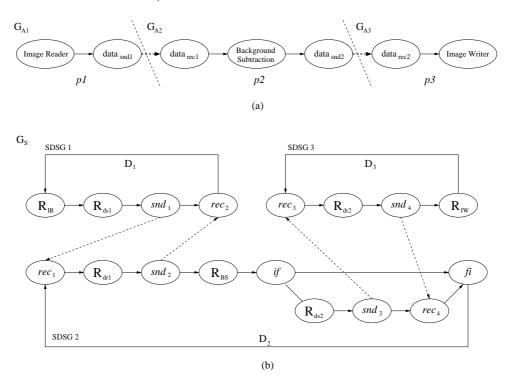

| 4.7  | (a)Macro-pipelined version of Figure 4.6; (b)the corresponding CDSG                                                                            | 85         |

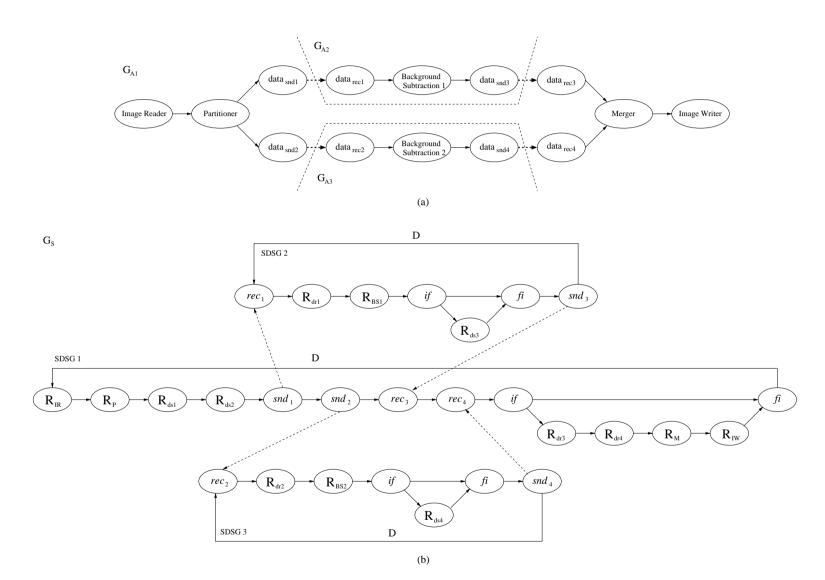

| 4.8  | (a)Fork-join version of Figure 4.6; (b) a corresponding CDSG represen-      |     |

|------|-----------------------------------------------------------------------------|-----|

|      | tation                                                                      | 95  |

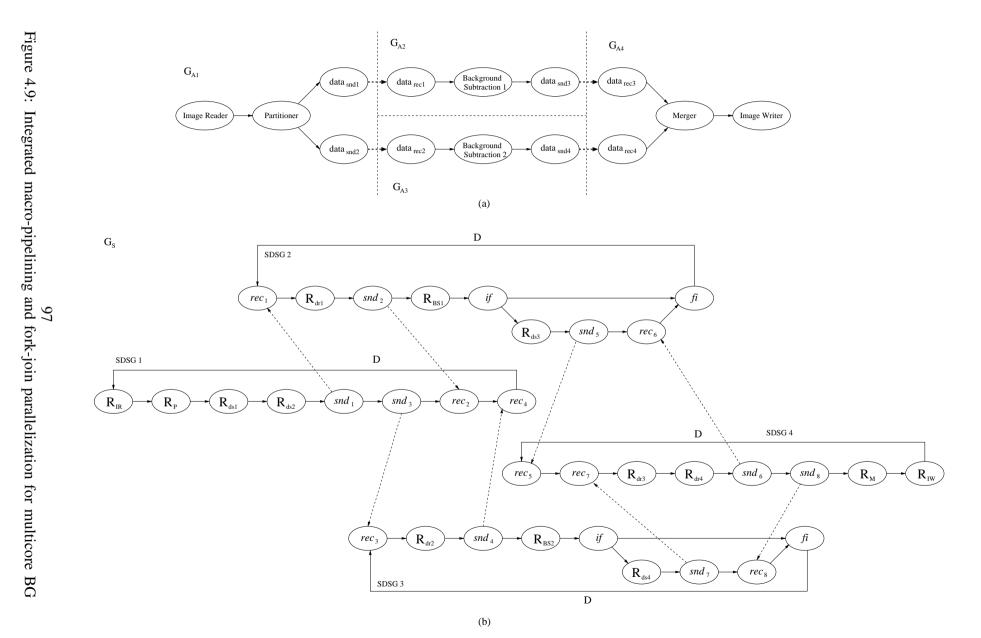

| 4.9  | Integrated macro-pipelining and fork-join parallelization for multicore     |     |

|      | BG subtraction                                                              | 97  |

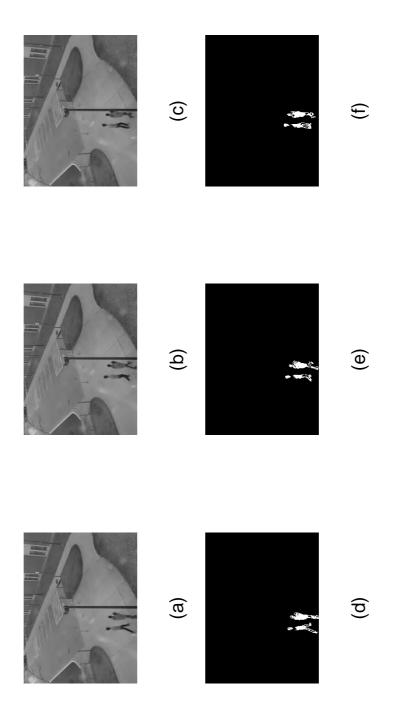

| 4.10 | Experimental results for multicore BG subtraction: (a)–(c) show the input   |     |

|      | frames; (d)–(f) show the corresponding background subtraction results       | 98  |

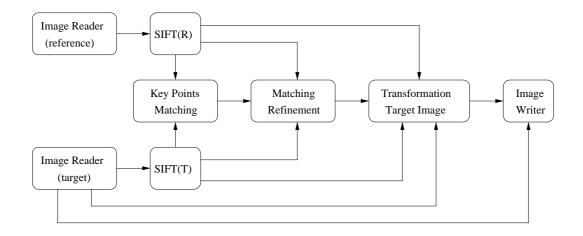

| 4.11 | A dataflow graph model of Scale-Invariant Feature Transform (SIFT)-         |     |

|      | based image registration                                                    | 99  |

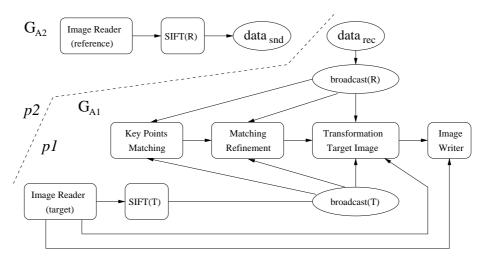

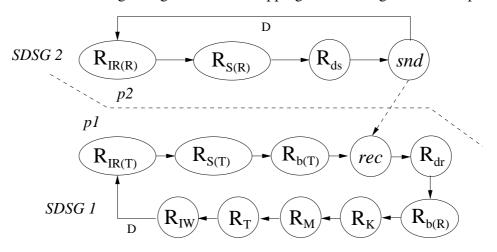

| 4.12 | Partitioning of Figure 4.11 for mapping onto the target multicore platform. | 99  |

| 4.13 | The CDSG derived for Figure 4.12                                            | 99  |

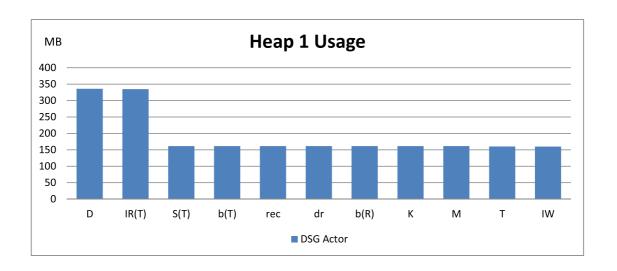

| 4.14 | Heap usage measurements for SDSG 1                                          | 100 |

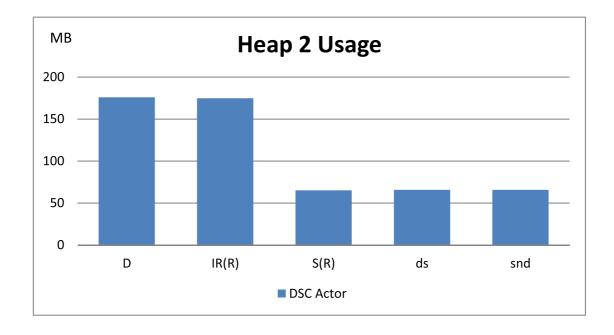

| 4.15 | Heap usage measurements for SDSG 2                                          | 100 |

#### Chapter 1

#### Introduction

1.1 Key Problems in the Design and Implementation of Embedded Systems

Widely used in many different application areas, embedded systems are usually dedicated to specialized purposes, and need to satisfy diverse constraints. In recent years, as tablets and smart phones have emerged and spread around the world, an increasing variety of applications are developed for such devices, and as such applications evolve, they often require higher and higher levels of performance.

Such a trend towards higher performance embedded processing makes Multiprocessor System-On-Chip (MPSoC) technology increasingly attractive across many embedded system domains. At the same time, the rapid evolution of tablet and smart phone technology accelerates the product cycle in associated embedded systems. The need to manage such change with high productivity and low cost makes designers turn to abstract models for design process management and application development. Because embedded processing technology and sensor technologies are evolving rapidly, such abstract models need to be independent of the underlying hardware. Furthermore, the increasing levels of adaptivity and reactivity required in embedded applications call for embedded system implementations that can efficiently achieve dynamic reconfiguration, and associated

scheduling and parallelization of application programs.

Due to time-to-market pressures and standards (e.g., standards for media formats or data communication) that evolve concurrently with product evolution, ASIC cannot provide the design agility, turnaround time, and flexibility required for many embedded application areas. In such scenarios, reconfigurable devices, such as FPGA, can be used as for prototyping and experimentation because of their regular structure with lower price [58]. Furthermore, as the technology for such reconfigurable devices advances, it can provide solutions beyond the needs of the prototyping and experimental stages, and can be competitive, for certain application areas, in terms of the requirements of final implementations [51]. Software-Defined Radio (SDR) is an example of an application area where FPGA are employed extensively [7].

Dynamic reconfiguration allows for reconfiguration of processing structures at runtime, while an application is executing. Through support for dynamic reconfiguration, embedded systems allow customization of hardware structures both statically and at runtime, thus allowing streamlining of processing configurations in response to application requirements or data characteristics that are not known at design time. In addition to allowing for dynamic changes in system functionality, dynamic reconfiguration, when carried out effectively, can enhance performance, resource utilization, and energy efficiency (e.g., see [25]).

Dynamic reconfiguration in embedded systems provides valuable flexibility and opportunities for enhanced efficiency, but also leads to increased complexity in terms of design analysis and optimization. Existing approaches focus primarily on either abstract models with the capability of expressing dynamic reconfiguration at a high level or

techniques for low-level, platform-specific implementation. While both of these areas of advancement are important, there is an increasing need to bridge the gap between them in order to better realize the potential of dynamic reconfiguration technology.

Scheduling is of critical importance to embedded systems, and effects key metrics, including latency, throughput, memory management efficiency, and power consumption. Furthermore, scheduling disparate applications running on limited resources is very challenging. Past research has focused extensively on static scheduling, and has provided a variety of efficient solutions for different kinds of requirements or constraints (e.g., see [51]). However, research on dynamic scheduling, particularly in the context of efficient embedded system implementation, is relatively less mature.

Scheduling has been studied extensively in the context of dataflow-based modeling of DSP systems. Dataflow graph scheduling involves assigning actors to processors, and sequencing subsets of actors that share common processing resources. For dataflow scheduling of DSP systems, a "processor" in this context is typically taken to be a hardware resource on which execution is time-multiplexed by actors that are assigned to it. In addition to ensuring that dataflow graph dependencies are respected, scheduling is often geared towards exploiting parallelism (performance improvement) and efficient memory utilization (buffer management). Given the fundamental role of scheduling in dataflow-based design flows, and its heavy impact on key implementation metrics, a wide variety of techniques has evolved over the years and continues to evolve for scheduling DSP dataflow graphs. Such techniques target objectives such as buffer optimization [2], joint code and data minimization [8], quasi-static scheduling [20], adaptive scheduling [6, 55], and throughput optimization [18].

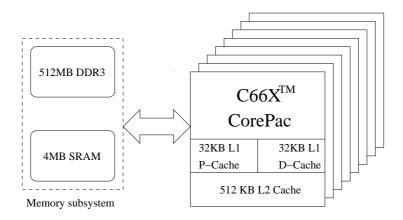

As multicore processors are deployed in an increasing variety of embedded systems, effective utilization of multiprocessor system-on-chip (MPSoC) technology becomes critical to developing effective embedded implementations. Besides the challenges of parallelizing embedded system applications, the exploitation of parallelism also increases the complexity of resource management. Characteristic of embedded systems, limited resources become a major bottleneck of performance improvement and of the management of overall design constraints, especially in computationally-intensive application areas, such as multidimensional signal processing. To help designers expose and exploit parallelism in tightly resource-constrained design scenarios, systematic methods are needed for integrated modeling and exploration of associated implementation trade-offs.

#### 1.2 Dataflow Models

Dataflow modeling is widely used in the design and implementation of DSP systems (e.g., see [7]). A dataflow graph is composed of actors (nodes) and edges, which represent computational tasks and data dependencies, respectively. The complexity of computations represented as dataflow actors can have arbitrary granularity — e.g., ranging from a few lines of code in a high level language to hundreds or thousands of lines.

As a distributed model of computation, dataflow involves local control through the "firings" (discrete units of execution) of individual actors. An actor starts a firing when an enclosing scheduler or hardware controller dispatches it for execution, and sufficient data is available at its input ports. Such an asynchronous, concurrent model of computation allows naturally for simultaneous execution of multiple actors if sufficient input data and

sufficient resources are available [40].

As the complexity of DSP systems increases, we see a steadily increasing demand for more powerful dataflow models and associated techniques for analysis and optimization. Synchronous Dataflow (SDF), proposed in [35], is the first dataflow-based model of computation to gain broad acceptance in DSP design tools, and many useful techniques, such as efficient scheduling and buffer size optimization, have been developed in the context of SDF (e.g., see [8]).

Although an important class of useful DSP applications can be modeled effectively in SDF, the expressive power of SDF is restricted since SDF imposes a restriction of *static* communication behavior, which actors must adhere to. In particular, for any given input port  $p_i$  of an SDF actor, the number of data values (tokens) consumed from  $p_i$  is constant across all firings of the actor, and similarly, the number of tokens produced by the actor on each of its output ports is constant. In other words, SDF actors cannot produce and consume varying amounts of tokens on their output and input ports.

As the need to model dynamic communication behavior has increased, due to the increasing levels of flexibility and dynamics in signal processing applications, many extensions or alternatives to the SDF model have been proposed. In general, an important objective for these models is to accommodate a broader range of applications while maintaining a significant part of the compile-time predictability that is offered by SDF.

Cyclo-static dataflow [9], scenario-aware dataflow [55], and Enable-Invoke Dataflow (EIDF) [46] are examples signal processing oriented dataflow models of computation that have been designed for increased expressive power. An extensive survey of such modeling techniques and their associated trade-offs is provided in [51]. In this thesis, we

target a specific form of dataflow modeling referred to as Parameterized Synchronous Dataflow (PSDF), which offers valuable properties in terms of modeling systems with dynamic parameters, supporting efficient scheduling techniques, and natural integration with popular SDF modeling techniques [5].

PSDF can represent cyclo-static dataflow by making dataflow-related parameter variations occur according to periodic patterns. Compared to EIDF, PSDF has lower expressive power overall, but is equipped with streamlined scheduling techniques for the subclass of application models that are amenable to PSDF semantics. Compared to scenario-aware dataflow, PSDF can be viewed as having a more strict separation between data and parameters, which facilitates symbolic scheduling techniques based on parameterized looped schedules.

PSDF is based on *parameterized dataflow*, which is a meta-modeling technique that can significantly improve the expressive power of an arbitrary dataflow model that possesses a well-defined concept of a *graph iteration* [6]. Parameterized dataflow provides a method to systematically integrate dynamic parameter reconfiguration into such models, while preserving many of the original properties and intuitive characteristics of the original models.

The integration of the parameterized dataflow meta-model with SDF provides the model of computation that we refer to as PSDF. Efficient *quasi-static scheduling* techniques have been demonstrated previously for PSDF specifications [5]. Here, by quasi-static scheduling, we refer to a general approach to scheduling in which significant portions of schedule structure are fixed at compile time, while some amount of run-time schedule adjustment can be made in response to input data or changes in operational

requirements.

Functional DIF is a functional simulation environment, with useful applications to rapid prototyping, for DSP-oriented dataflow models of computation [46]. Functional DIF is based on the EIDF model of computation, which is Turing complete. Functional DIF allows actors whose internals are programmed in Java to be integrated with EIDF-based dataflow graphs that are specified using Dataflow Interchange Format (DIF). DIF is a textual language for specifying dataflow graphs in terms of arbitrary dataflow models of computation [22].

#### 1.3 Scheduling for Dataflow Models

In DSP-oriented dataflow models of computation, applications are modeled as directed graphs, where actors represent computational modules for executing tasks, and edges represent first-in-first-out channels for storing tokens, and imposing data dependencies between actors. Whenever an actor fires, it consumes and produces tokens from its input and output edges, respectively. As discussed previously, scheduling is a fundamental process that must be addressed carefully to derive efficient implementations from dataflow graphs.

As the range of dataflow graph scheduling techniques continues to expand, based on the heterogeneity of application modeling styles and implementation objectives, and the increasing degree of dynamics in applications, it becomes increasingly important to develop a common representation for modeling and working with dataflow schedules. Such a representation is desirable to enable systematic reuse of design tool code, anal-

ysis techniques, and back-end implementation methodologies across various scheduling strategies. Furthermore, a formal representation helps to integrate different scheduling techniques so that they can be mixed and matched across different subsystems of a design based on characteristics and objectives associated with those subsystems.

#### 1.4 Design Techniques for Multiprocessor Systems-on-Chip

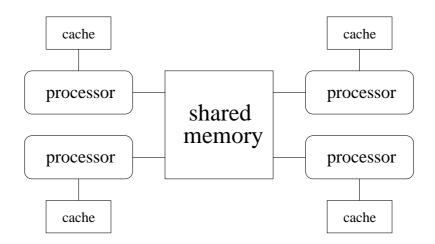

The *shared memory* model, illustrated in Figure 1.1, is a popular parallel programming model. The shared memory model is widely used in small scale parallel computers, such as desktop personal computers and laptops. Parallel computing platforms that are based on the shared memory model are called SMP. In SMP, processors (threads) are given flexible access to shared memory, while writing conflicts (i.e., consistency problems) need to be resolved by programmers based on the available architectural support. For example, a write-through cache can update shared memory data as soon as possible, whereas a write-back cache generally takes longer to do so, thereby requiring additional considerations to handle consistency [53]. One of the most popular multiprocessors for embedded system, the ARM Cortex-A9 MPCore, is based on the shared memory model.

Instead of using a centralized concept of memory, the *message passing* programming model assumes that each processor has its own local memory and communicates with other processors through communication packets (messages). Message passing is suitable for large scale parallel computers due to better scalability compared to the shared memory model. However, memory references across different local memories can be difficult to resolve. This makes the approach error prone, and requires more effort in

Figure 1.1: Shared memory model.

code maintenance. To support message passing, a library called Message Passing Interface (MPI) has been developed for C- and Fortran-based parallel programming. Furthermore, the implementation of message passing is not restricted to distributed memory systems. That is, message passing can be realized in shared memory systems as well.

In contrast to imperative programming, *skeleton programming* (also called structured programming) provides a different flavor for expressing parallelism [14]. Skeleton programming involves the use of skeleton codes, which can be viewed as generic and reusable functions (patterns) that are derived from functional programming languages [19]. Patterns for skeleton programming are discussed in [38].

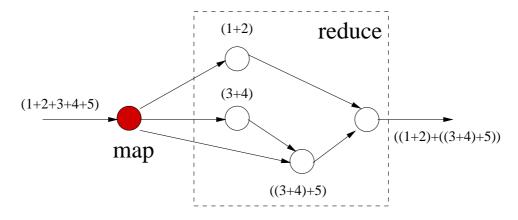

Figure 1.2 demonstrates an example of the parallel patterns map and reduce. The function sum, which takes two operands, computes (1+2+3+4+5) in parallel by creating four sub-summations sum (1,2), sum (3,4), sum (sum(3,4),5) and sum (sum(3,4),5) for short. The sub-summation sum (1,2) and sum (3,4) can

be executed concurrently.

Algorithmic skeleton frameworks have been integrated with object oriented programming languages, such as Java and C++. *MapReduce*, along with its implementation developed by Google [15], is one well known programming model of this kind.

Figure 1.2: An example of the parallel programming patterns *map* and *reduce*.

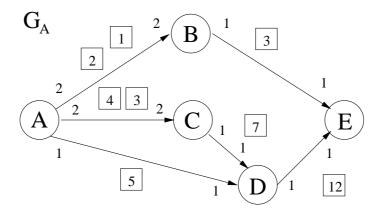

Dataflow models of computation, as the name suggests, emphasize data and its flow more than computation. They are also considered as first order functional programming models. The function sum in Figure 1.2 modeled in terms of SDF semantics is illustrated in Figure 1.3. Here, actor A produces five tokens containing the data values 1, 2, 3, 4 and 5 on its three outgoing edges. Consuming two tokens from its input edges, actor B(C) produces one token, which encapsulates the sum (1+2)((3+4)). Actor E consumes the tokens produced from actors E and E to obtain the result of the overall computation. To exploit parallelism from this dataflow graph, actors E and E can be executed simultaneously.

Conforming to the shared memory model, *portable operating system interface* (POSIX) threads, also known as *Pthreads*, is a widely used library that supports SMPs [11].

Figure 1.3: An example of dataflow modeling.

Based on sequential programming languages, such as C and Fortran, Pthreads helps to realize the potential performance gains of parallel computing by providing programmers with an extensive library of APIs for thread management and thread synchronization. In this context, threads can be viewed as subtasks of procedures that have their own program counters and function-call stacks. Thus, threads can execute concurrently and share resources.

Some programming languages, such as Java and C#, incorporate support for threads into their associated development frameworks. In such frameworks, parallelism can be expressed through constructs in the programming language, instead of through use of libraries. Although thread programming is a popular way to achieve performance gains from parallel computing, the approach is fraught with problems in terms of understandability, predictability, and determinism, which are the essential and appealing properties of sequential computing [34].

To help simplify parallel programming, OpenMP (Open Multi-Processing) adopts a concept of *incremental parallelization*, where the compiler undertakes the parallelization

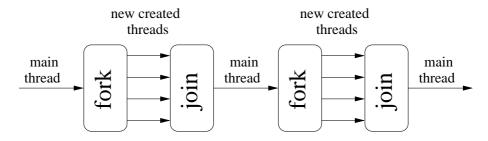

of sequential codes based on programmer-specified *directives*. Parallelization is realized through a fork-join model [16], which creates multiple threads at selected instants during execution (fork), and collects threads created by fork operations when they are completed (join). Figure 1.4 illustrates the operation of fork and join operations in OpenMP.

Using OpenMP, programmers start with sequential codes, and insert OpenMP directives (pragmas) to specify which regions of the sequential codes are to be parallelized and synchronized. Such an approach allows programmers to parallelize their sequential codes incrementally, increasing the amount of parallelism exploited as they gain confidence in their evolving implementations.

Figure 1.4: Fork-join model.

The execution of a parallel program can be categorized into two styles according to whether or not the number of parallel activities (e.g., threads) is constant at runtime. Fork-join operations spawn parallel activities at some time and then, terminate them at another time. Therefore, the number of parallel activities is not fixed. In this thesis, we are generally concerned with dataflow graph scheduling strategies that involve dynamically determined numbers of parallel activities, although not limited to a fork-join style of parallelism.

In many areas of embedded signal processing, utilizing the underlying memory sys-

tem efficiently has an major effect on important metrics, including real-time performance, cost, and energy consumption. In [44], the authors present an overview of how the memory architectures of embedded systems can be customized to enhance performance.

Additionally, input/output (I/O) interfacing is an important part of embedded system design, and needs to be considered carefully to derive efficient implementations. Various studies have investigated the streamlining of I/O. For example, to improve the latency of file I/O, stream-enabled file I/O is proposed in [30]. This approach allows applications to access files concurrently while they are being transferred.

#### 1.5 Contributions of this Thesis

In this thesis, we present a number of contributions to help improve the mapping of dataflow graphs for DSP applications into efficient parallel implementations. First, we present a novel simulation tool that integrates the Java-based actor programming capability of Functional DIF with PSDF-based graph specification in the DIF language in Chapter 2. This provides the first implementation of a comprehensive simulation environment for PSDF. Such an environment is useful for exploring the capabilities of dynamically reconfigurable SDF modeling and quasi-static scheduling offered by PSDF, and for applying these methods more deeply into design flows for FPGA and digital system implementation.

Building on our newly developed PSDF simulator, which we refer to as *PSDFsim*, we propose a comprehensive PSDF-based design methodology that covers modeling of the target application, simulation of functionality, and hardware architecture mapping.

PSDFsim is applied as a core part of this methodology to help validate the high-level PSDF modeling architecture before committing to lower-level implementation decisions, and later on, to help validate derived hardware description language (HDL) implementations.

To support the scheduling of dynamic reconfiguration, we address the problem of schedule design by introducing a formal framework, called the Dataflow Schedule Graph (DSG) for precisely representing, analyzing, manipulating, and interchanging schedules in Chapter 3. We have designed the DSG representation with two major objectives — 1) it should be rooted in formal dataflow semantics, and 2) it should accommodate a wide range of schedule classes, including static, quasi-static, and dynamic schedules, as well as both sequential and parallel schedule formats. Furthermore, because they are based on the same dataflow semantic framework as the application representations from which the schedules are derived, DSG can naturally represent structures in which schedules are adapted dynamically (e.g., in response to changes in input data characteristics).

As motivated above, resource-constrained implementation of embedded systems requires careful attention to a variety of design aspects, including parallelizing computations, memory management, efficient I/O interfacing, and efficient and fair management of limited resources. Embedded image processing is a domain of signal processing where the challenges in such a multi-faceted implementation process are especially difficult, due to the large volumes of data involved, and the stringent real-time performance constraints. To help address these challenges, we present in Chapter 4, a new design methodology, called the DEIPS (DSG-based design and implementation of Embedded Image Processing Systems) methodology. The DEIPS methodology builds on the DSG model to provide

a structured framework for design and implementation of embedded image processing applications. The DEIPS methodology provides an integrated methodology for addressing the issues that include parallelization of signal processing operations, memory management, I/O interfacing, and efficient management of multidimensional (e.g., image- or block-oriented) dataflow behavior. We demonstrate the DEIPS methodology through two detailed case studies that involve mapping different image processing applications onto a state-of-the-art multicore digital signal processor platform.

#### Chapter 2

Rapid Prototyping for Digital Signal Processing Systems using

#### Parameterized Synchronous Dataflow Graphs

In this chapter, we present a comprehensive simulation environment for signal processing systems that are modeled as parameterized synchronous dataflow (PSDF) graphs. PSDF was introduced in [6] as a model of computation that augments synchronous dataflow (SDF) semantics with structured methods to dynamically configure dataflow graph parameters, including but not limited to parameters that affect token production and consumption rates of actors. Our proposed new PSDF simulation environment is useful for exploring the capabilities of dynamically reconfigurable SDF modeling and quasi-static scheduling offered by PSDF, and for applying these methods more deeply into the design and implementation for signal processing systems.

#### 2.1 PSDF Operational Semantics

The PSDF operational semantics allows subsystem behavior to be controlled by sets of parameters that can be configured dynamically. Some basic concepts and terminology associated with PSDF modeling and semantics are described as follows. For more details, we refer the reader to [5].

1. A *PSDF specification* is composed of three cooperating PSDF graphs, which are referred to as the *init*, *subinit*, and *body* graphs of the specification. Actors and

- edges in PSDF graphs can be parameterized with arbitrary parameters that can be changed at run-time. For any fixed setting of parameters, the PSDF graph yields an SDF graph.

- 2. A PSDF specification can be nested within a higher level PSDF graph. Such nesting is achieved by encapsulating the specification as a hierarchical PSDF actor in the higher level graph.

- 3. Parameters of actors and edges in a PSDF graph can only change between *iterations* of the graph. The precise boundaries between iterations can in general be user-defined; typically, in PSDF they correspond to boundaries between *periodic schedules* of the underlying SDF graph. A periodic schedule of an SDF graph is a sequence of actor firings that executes each actor at least once, and returns the graph to its initial state (the initial set of token populations on the edges) [35].

- 4. The *interface dataflow behavior (IDB)* of a nested PSDF subsystem (i.e., the numbers of tokens produced or consumed at input and ports of the subsystem) can only be changed by the init graph of the subsystem. The init graph executes once during each iteration of the parent (hierarchically enclosing graph). In general, the init graph is allowed to configure (change parameters in) the corresponding subinit and body graphs. Such parameter changes are achieved by mapping the associated parameters to appropriate actor output ports in the init graph.

- 5. The subinit graph executes once during each execution of the corresponding PSDF subsystem (each firing of the enclosing PSDF actor if the subsystem is nested).

During such an execution, the subinit graph executes; new parameter values com-

puted at outputs of the subinit graph are propagated to corresponding parameters in the body graph; and then the body graph executes based on the updated set of parameters.

- 6. Parameter changes that are computed by the subinit graph cannot modify the IDB of the body graph or enclosing PSDF actor. This ensures that any parent graph has a consistent view of the subsystem throughout an iteration of the parent graph. Such a consistent view facilitates efficient quasi-static scheduling and associated analysis [5, 41].

- 7. Based on 4, 5 and 6, parameter changes produced by the subinit graph can generally be viewed as more frequent, but more restricted compared to those computed by the init graph.

We use the downsampler example shown in Figure 2.1 to illustrate these concepts. Here, actor H is a hierarchical PSDF actor that encapsulates a PSDF representation (subsystem) of a dynamically reconfigurable downsampler. Actor D in the body graph of the subsystem represents the core downsampling functionality. This actor is parameterized by the *factor* and *phase* parameters, which represent, respectively, the downsampling ratio F and the phase P of the downsampler (P < F). In each firing, D consumes F tokens from its input edge, and produces a single token, which is a copy of the (P+1)th token consumed during the firing.

Since the input of D is connected as input of the enclosing subsystem, changes to the factor parameter in general affect the consumption rate of the subsystem and therefore its IDB. Thus, the factor parameter can be configured by the init graph, but *not* the subinit

graph. On the other other hand the phase parameter does not affect the IDB, and therefore, this parameter can be configured by either the init graph, the subinit graph, or both.

Actors A, B, and C in Figure 2.1 represent SDF actors. The production rates of A and B and the consumption rate of C are statically fixed at unity. These actors represent data sources and a data sink, respectively, which can be used, for example, to drive the subsystem with test data and collect the corresponding test output for subsequent validation.

As part of the init graph, actor E executes once before each iteration of the parent graph of the PSDF subsystem corresponding to H. Thus, E can be used to perform initialization of the factor parameter, as well as to perform periodic updates to this parameter.

For a more elaborate tutorial discussion of PSDF semantics, we refer the reader to [5].

Figure 2.1: A PSDF Downsampler.

#### 2.2 PSDFsim

In this section, we introduce *PSDFsim*, which to our knowledge is the first comprehensive functional simulator for PSDF-based application modeling and design. PS-DFsim generates the schedule (simulation sequence) whenever the init graph determines the dataflow behavior that it controls, and then simulation starts. Using PSDFsim, one can validate and test the PSDF modeling architecture at a high level of abstraction before committing to lower-level design decisions, such as detailed hardware-level modeling for the actor internals. Such a two-phase approach to PSDF-based implementation helps to separate the high-level (inter-actor) dataflow architecture design (in terms of PSDF semantics) from the fine grained control and dataflow structures involved in the individual actor implementations, and to allow the former to be applied systematically as a testbench for the latter. More details on this PSDF-based implementation approach are described in Section 2.3.

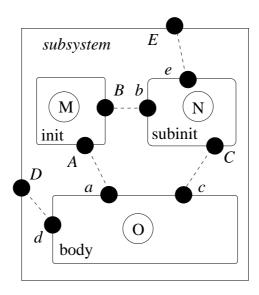

PSDFsim supports two different forms of parameter propagation — *internal* and *hierarchical* propagation — for dynamic parameter changes to actors and edges. For example, consider Figure 2.2. Each dashed edge in this figure represents a parameter propagation path. Edges (A,a), (B,b), and (C,c) correspond to internal propagation paths, which are explained further in Section 2.1. On the other hand, edges (D,d) and (E,e) in Figure 2.2 represent paths for hierarchical parameter propagation. Such hierarchical propagation paths provide channels to update parameters based on new parameter values that are computed from higher level subsystems. Based on properties derived from PSDF semantics, updates through hierarchical propagation override any corresponding

configurations that have been made through internal propagation.

These two forms of parameter propagation facilitate code reuse by allowing arbitrary actors to be applied and adapted in different kinds of contexts through different forms parameter initialization and reconfiguration structures.

Figure 2.2: An illustration of parameter propagation in PSDFsim.

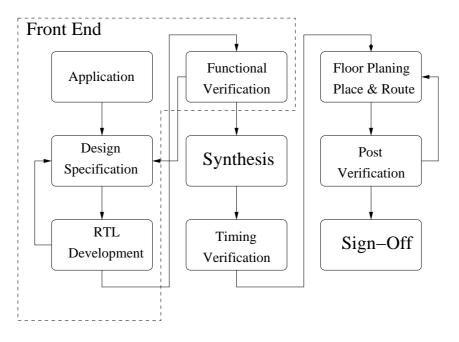

### 2.3 PSDF-based Design Methodology

PSDF-semantics can be applied for model-based design in the front end of the FPGA/ASIC design flow shown in Figure 2.3. Such an approach can provide a structured framework to control dynamic functionality and make corresponding adaptations to scheduling strategies and resource allocations. Such a PSDF-based approach involves two phases — high level modeling and validation (*modeling*) and hardware architecture mapping (*mapping*). These two phases can in general be applied iteratively to implement dataflow based parallel processing structures for FPGA- or ASIC-based signal processing

systems.

The modeling phase ensures correct application functionality as well as the correct formulation of the functionality in terms of dataflow and PSDF principles. Through its direct connection to the concurrency modeling capabilities of dataflow, this phase helps provide a framework for efficient implementation even though the focus on this phase is on functional validation rather than detailed hardware mapping. In this phase, procedural software is used to specify the internal functionality of the actors, while a dataflow language is used to specify the high-level (inter-actor) application model. In PSDFsim the Java and DIF languages are used for these purposes of intra-actor and inter-actor, modeling-phase specification, respectively.

In the mapping phase, the designer applies the individual actor models as functional references to derive corresponding hardware implementations using a hardware description language (HDL). The functionality of these "hardware actors" can be validated using the same testbenches as those used in the modeling phase. Similarly, edges in the DIF-based application (application graph) model are mapped into corresponding FIFO implementations using the targeted HDL and associated design library.

By developing the actors based on PSDF principles, and connecting them through standard FIFO semantics, functional correctness of the overall, application-level hardware implementation follows directly from correctness of the original PSDF application model, and correct mappings of the individual actor models into hardware. Additionally, the application level model from the modeling phase can be used as a testbench to begin application-level testing of the hardware, where both functional and timing constraints must be taken into account. Insight from timing analysis of the hardware implementation

can then be used to optimize the hardware actors and possibly to iterate back to the modeling phase to explore refinements or alternatives to the high level dataflow architecture.

Figure 2.3: FPGA/ASIC design flow overview.

#### 2.4 Hardware Architecture Mapping

In this section, we present details on the mapping phase of our proposed design methodology, including the steps involved in hardware architecture mapping of PSDF actors, graphs, and specifications. Previous work on mapping dataflow structures into hardware include the work on VLSI dataflow arrays [31], SystemC [21], and multidimensional arrayed dataflow [37]. The methods developed in this thesis are different from these approaches in their support for parameterized dataflow modeling, and the novel features of dynamic parameter reconfiguration and reconfigurable dataflow modeling that are provided by PSDF semantics [5]. Due to the potential for applying parameterized dataflow

semantics with arbitrary dataflow models of computation (subject to suitable definitions of graph iterations, as described in Chapter 1), the integration of the techniques presented in this thesis with the models used in the aforementioned works is an interesting direction for further study.

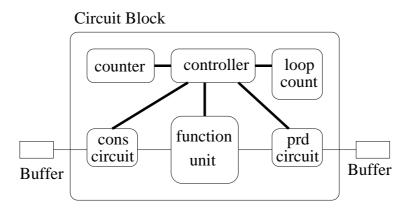

PSDF and PSDFsim modeling constructs — in particular, PSDF actors, edges, schedules, parameter propagation paths, and operational semantics — map naturally into corresponding hardware structures. The buffer sizes can be determined by the schedule used in the hardware, and other hardware components are generic and reusable (not application-specific). Table 2.1 summarizes this mapping.

Table 2.1: Mapping PSDF constructs to hardware.

| PSDF Model                 | Hardware Components  |

|----------------------------|----------------------|

| actor                      | circuit block        |

| edge                       | buffer (e.g., FIFO)  |

| schedule                   | graph controller     |

| parameter propagation path | wire                 |

| operational semantics      | subsystem controller |

Although the complexity of circuit blocks can vary widely, the top-down application of PSDF principles provides a standardized design style for the interaction between different circuit blocks and for the interaction between circuit blocks and the associated PSDF control for scheduling and parameter management for the blocks. This allows for significant reuse of parameterized HDL "glue code", as well as corresponding streamlin-

ing of verification effort.

We employ self-timed scheduling and control of dataflow actors, where actors can fire as soon as they have sufficient data on their input buffers; sufficient empty spaces on their output buffers; and up-to-date values available for their parameters, as determined by the associated subinit and init graphs. Such self-timed hardware mapping is natural for signal processing oriented dataflow models of computation, and avoids bottlenecks and scheduling restrictions due to the alternative of fully static (globally clocked) scheduling (e.g., see [51]).

Figure 2.4 illustrates the architecture of a standard wrapper for PSDF-based interfacing of actor circuit blocks. Here, the blocks labeled *counter*, *controller*, and *loop count* handle control and iteration management within the functional unit of the actor, which can be of arbitrary complexity. The blocks labeled *cons circuit* and *prd circuit* handle input and output interfacing of the actor based on dataflow rates that may be parameterized and dynamically configured.

The structure of hardware mapping at the PSDF subsystem level is illustrated in Figure 2.5. The dashed lines indicate wires for parameter configuration, and the circuit blocks B and D are parameterized by the init and subinit graph, respectively. The controllers associated with the structures of Figure 2.4 and Figure 2.5 are illustrated in Figure 2.6.

The circuit block control, illustrated in Figure 2.6(a), is a key part of self-timed, PSDF hardware implementation. At the beginning of a control iteration (the state labeled *PARAM*), the circuit block configures any dynamically managed parameters based on the current settings and tries to consume data from the buffer (*CONS* state). The controller

will block in the CONS state until all data has arrived from the corresponding producer actor, and has been consumed for processing by the circuit block. Then the controller enters the *EXE* state and activates the function unit to process the input data and generate any output values. When the output data is ready, the prd circuit pushes it onto the corresponding output edges during the *PRD* state. Finally, after all output data has been written, the controller enters the *DONE* state. In the DONE state, if the firing count within the current loop execution matches the loop count, then the controller goes back to the PARAM state and waits for another circuit block iteration before proceeding; otherwise, the controller goes to the CONS state to consume tokens for the next firing.

Figure 2.4: Interface and control architecture for a circuit block.

#### 2.5 Case Study: Phase-Shift Keying

In this section, we demonstrate our PSDF-based design methodology using a reconfigurable *phase-shift keying (PSK)* application that can be configured as binary PSK (BPSK), quadrature PSK (QPSK) or 8PSK. We construct PSDF models of the modulator and demodulator for this system, and develop Java-based functional DIF code to specify

Figure 2.5: An illustration of subsystem-level hardware mapping.

the internal functionality of each actor. The resulting PSDF program is then simulated and tested using PSDFsim, and then hardware mapping is applied to the modulator to derive a Verilog implementation. HDL simulation and synthesis is then applied to validate the evaluate the derived hardware.

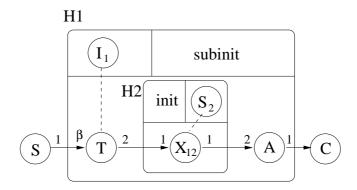

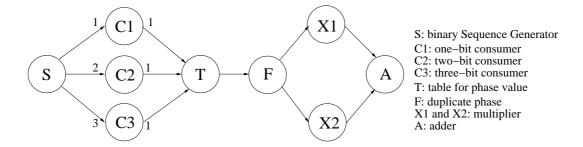

Figure 2.7 illustrates our PSDF model of the targeted system for reconfigurable PSK. Here, D represents an input interface that injects samples from the incoming data stream into the dataflow graph; T and P are parameterized lookup tables; I1 is an actor that configures the consumption rate (based on M) of T; S2 and S4 provide trigonometric functions that are selected based on a dynamic parameter setting; I3 configures the production rate of P; A is an adder; X12 and X34 are constant multipliers whose associated constants (scaling factors) are managed as dynamic parameters; and B is an output interface for the storing or further processing of the resulting binary sequence. The input interface D makes two copies of each input token on its output since two separate

Figure 2.6: Finite state machines for (a) a circuit block, (b) a graph controller, (c) consumption and production circuits, and (d) a subsystem controller.

multiplications are required for each input sample.

Figure 2.7: PSDF-based model of PSK modulator and demodulator.

Our PSDF model involves a parameter M, which determines which form of PSK to employ. For M=1,2,3, an SDF graph associated with BPSK, QPSK and 8PSK, respectively, is effectively activated. After the system model is constructed, we use a

PSDFsim to simulate the system and validate the functionality for the different values of M. This initial simulation is performed assuming no distortion of data in the channel.

Since channel quality is critical to the choice of PSK, we can modify actor C to model the noise in the channel and analyze the simulation results under different PSK configurations. PSDFsim enables such multi-mode application simulation to be executed in an integrated manner — i.e., as a single simulation that includes all PSK configurations along with simulation control functionality that dynamically changes the configuration.

Our hardware mapping of the modulator is illustrated in Figure 2.8. Here, the *filler* block represents an actor that is inserted to help maintain PSDF operational semantics. Since the init and subinit graphs here both contain one node each, their associated graph controllers can be removed. Note also that the circuit blocks associated with blocks T and X12 are parameterized and receive parameter value updates from circuit blocks I1 and I1 and I1 are parameterized and receive parameter value updates from circuit blocks I1 and I1 and I1 are parameterized and receive parameter value updates from circuit blocks I1 and I1 and I1 are parameterized easily in future designs.

A comparison of the simulation time for the PSK modulator between PSDFsim and ModelSim SE 6.5 is shown in Table 2.2. The time required by PSDFsim to compute the dataflow graph schedule is not included in the time reported here for PSDFsim. This is because this schedule computation is not specific to a single simulation — the schedule can be reused across multiple simulations for the same dataflow graph. The derived schedule is also an important part of the hardware mapping process, and is used (without any recomputation effort) by the lower level, ModelSim simulation. The time taken by PSDFsim in our experiments to compute the schedule for the PSK system is 125 ms.

The improvements in simulation time using PSDFsim help to demonstrate the utility

Figure 2.8: Hardware mapping for modulator.

of using PSDF for rapid prototyping and early-stage design. In particular, PSDF allows for faster simulation and design exploration early in the design phase when the high level dataflow architecture is being developed, and detailed HDL simulation (e.g., that provided by ModelSim) is not needed.

Note that these experiments are based on an initial Java-based implementation of PSDFsim that has not been optimized for speed. We expect that with optimization for speed, the simulation time speedup achieved using PSDFsim can be improved significantly.

To provide an area comparison, we instantiate three separate PSK circuits that support BPSK, QPSK and 8PSK individually using SDF-based models. We compare this pure-SDF-based implementation with our PSDF implementation that is derived using PSDFsim and our proposed design methodology. Synthesis results generated by the Cadence

Encounter RTL Compiler are shown in Table 2.2. Although there is some area overhead in the PSDF implementation due to the controllers and auxiliary circuits used for the init and subinit graphs, this overhead is more than compensated for by the hardware reuse that is facilitated by the flexible, dynamic parameterization capabilities of PSDF.

Table 2.2: Comparisons for PSK modulator system.

| Simulation time of PSDFsim and ModelSim      |               |                |  |  |  |

|----------------------------------------------|---------------|----------------|--|--|--|

| PSDFsim (ms)                                 | ModelSim (ms) | Speedup        |  |  |  |

| 47                                           | 93            | 1.98X          |  |  |  |

| Area of PSDF design and SDF design (100 MHz) |               |                |  |  |  |

| PSDF (cell)                                  | SDF (cell)    | Reduction      |  |  |  |

| 20004                                        | 33602         | 44.67% (1.68X) |  |  |  |

#### Chapter 3

A Model-based Schedule Representation for Heterogeneous Mapping of Dataflow Graphs

In this chapter, we introduce a formal framework, called the *dataflow schedule graph* (*DSG*), for precisely representing, analyzing, manipulating, and interchanging schedules that are associated with high-level dataflow specifications of signal processing systems. We have designed the DSG representation with two major objectives — 1) it should be rooted in formal dataflow semantics, and 2) it should accommodate a wide range of schedule classes, including static, quasi-static, and dynamic schedules, as well as both sequential and parallel schedule formats. Furthermore, because they are based on the same dataflow semantic framework as the application representations from which the schedules are derived, DSG can naturally represent structures in which schedules are adapted dynamically.

#### 3.1 Related Work

A number of dataflow schedule representations have been explored previously. The *generalized schedule tree* (*GST*) representation provides a tree-based representation of arbitrary looped schedules [29]. A novel schedule format based on dynamic loop counts that is geared towards SDF buffer memory minimization is developed in [43]. The *interprocessor communication graph* and *synchronization graph* models provide dataflow-based

schedule representations for parallel schedules of homogeneous SDF (HSDF) graphs [51]. HSDF is a restricted form of SDF in which the dataflow rate on each input and output port is always equal to 1 [35].

A distinguishing characteristic of our proposed DSG representation is that it is both dataflow based, and capable of handling dynamic schedule structures as well as dynamic dataflow application models. This is in contrast to execution-sequence based representations, which can usually be characterized formally but lack dataflow semantics and are often restricted to static schedules.

The most closely related modeling technique is the synchronization graph model. In this model, self-timed multiprocessor schedules are represented as interacting dataflow graph cycles, where each cycle corresponds to the periodic execution of the actors that are assigned to a given processor [51]. A significant body of theory and algorithms has been developed for this model. We are therefore motivated to generalize the synchronization graph concept beyond self-timed schedules, and HSDF graphs.

The DSG can be viewed as such a generalization. The DSG model can represent dynamic schedules, which can be applied to static or dynamic application models to improve flexibility (e.g., load balancing robustness or data dependent control structures). Furthermore, the model is fully based on dataflow principles, which together with its accommodation of dynamic dataflow semantics, allows for integration with dynamic parameter control methods for dataflow graphs, such as those provided by parameterized dataflow [6] and scenario-aware dataflow [55].

The DSG representation can be used in conjunction with existing task graph scheduling techniques, such as those developed in [17, 27, 32, 50, 57]. For example, the DSG can

be used to model the sequencing structures derived by the scheduling techniques (e.g., as a standard interface for code generation) or to bridge subsystems that are scheduled using different techniques. Indeed, exploring the optimized integration of DSG based schedule control with new and existing task graph scheduling techniques is an interesting direction for further investigation, and one that is especially relevant in the area of heterogeneous computing systems.

## 3.2 Core Functional Dataflow

For concreteness, we develop the DSG in the context of a specific form of dataflow — the *core functional dataflow (CFDF)* model of computation, which can be viewed as a deterministic sub-class of *enable-invoke dataflow graphs* [46]. CFDF is a highly expressive (Turing complete), dynamic dataflow model. In Section 3.10, we discuss how the DSG model can be adapted to other forms of dataflow (beyond CFDF).

In CFDF, actors are specified as sets of *modes*, where each mode has a fixed production and consumption rate associated with each input and output port, respectively. Each actor has an associated *current mode*, which is maintained as part of its state. When an actor is invoked, it executes its current mode, produces and consumes data (as in other dataflow models), and updates its current mode. Since different modes of an actor can have different production and consumption rates, dynamic dataflow can be modeled flexibly in CFDF.

A distinguishing aspect of CFDF (and the non-deterministic superset EIDF) is that *separation* of enable and invoke functionality for actors is defined as a first class charac-

teristic of the model. Specifically, each actor has an associated *enable* function, which can be called at any time between firings (e.g., by a run-time scheduler), and returns a Boolean value indicating whether or not there is sufficient data available on the actor input ports to fire (invoke) the actor in its current mode. Since such an isolated enable check is available, the invoke function of an actor assumes that sufficient data is present, and reads its input data without blocking reads.

In the implementation of dataflow tools, functionalities corresponding to the enable and invoke methods are often interleaved — for example, an actor firing may have computations that are interleaved with blocking reads of data that provide successive inputs to those computations. In contrast, there is a clean separation of enable and invoke capabilities in EIDF. This separation helps to improve the predictability of an actor invocation (since availability of the required data can be guaranteed in advance by the enable method), and in prototyping efficient scheduling and synthesis techniques (since enable and invoke functionality can be called separately by the scheduler). This separation also leads naturally to a concept of *guarded execution*, whereby an actor firing is conditionally executed depending on whether or not it is enabled.

### 3.3 The Dataflow Schedule Graph Representation

Given a CFDF representation  $G_A$  of an application, a dataflow schedule graph (DSG) is a dataflow graph that satisfies certain technical constraints (described later in this section), and represents the time-multiplexed execution of  $G_A$  across a set of hardware resources. Here, a hardware resource represents an arbitrary computational resource,

such as a processor core, dedicated accelerator or FPGA subsystem, that executes actors sequentially. Constraints imposed on the DSG ensure that each hardware resource can execute at most one actor from  $G_A$  at any given time. Tokens that flow along edges of the DSG serve to enable actors for execution (as it becomes their turn to execute). DSG tokens can also contain values that are manipulated and queried during execution of the DSG to achieve various forms of data- or parameter-dependent schedule control.

In DSGs, special actors, called *schedule control actors* (*SCAs*) and *reference actors* (*RAs*), are selected or developed as an integral part of the schedule modeling framework. In contrast to conventional dataflow actors, which represent functional components from the original application specification (*application actors*), *SCAs* are dataflow actors that are dedicated to coordinating control flow in derived schedules. On the other hand, *RAs* can be viewed as "pointers" to application actors. These pointers are equipped with optional auxiliary computations. Intuitively, an RA represents a scheduling "wrapper" that specifies the computation that is executed when the corresponding actor is "visited" during schedule execution. The simplest form of RA is one that simply performs a guarded execution of the actor that it points to. However, more capabilities can be incorporated into RAs using the optional auxiliary computations mentioned above.

#### 3.4 Reference Actors

An RA has a single input port and a single output port. An RA is a homogeneous synchronous dataflow actor in the enclosing DSG — that is, it consumes a single token on each firing from its input, and produces a single token on its output.

Given an RA A, we represent the application graph actor pointed to by A with the symbol ref(A), and we refer to ref(A) as the *referenced actor* of A.

As illustrated in Figure 3.1, an RA A consists of two functions  $pre_A$  and  $post_A$ , which are executed, respectively, before and after the *guarded execution* phase of A. This guarded execution phase, represented by the block labeled "guarded firing" in Figure 3.1, represents the guarded execution of A in terms of CFDF semantics (see Section 3.2).

Figure 3.1: The internal structure of an RA.

We refer to the functions  $pre_A$  and  $post_A$  as *subfunctions* of the enclosing RA. Intuitively, the RA subfunctions provide a mechanism to process and manipulate data that is used throughout the graph to control execution of actors (e.g., to facilitate conditional execution or data dependent iteration in various parts of the graph). The data manipulated by RA subfunctions is encapsulated within the DSG tokens that are produced and consumed by the enclosing RA.

To clarify the operational structure of DSGs, it is useful to emphasize that the tokens flowing on a DSG are strictly for schedule control purposes. Furthermore, because actors in the application graph are allowed to execute only when they have sufficient data (as specified by the CFDF enabling conditions), and CFDF is a deterministic dataflow model, schedule control by DSGs does not violate determinacy — such control only dictates how actors are time multiplexed when they are mapped to the same hardware resource.

RAs can contain internal state. Such local (actor-specific) state is widely known to be compatible with dataflow representations since in dataflow graphs, state can be modeled as self loops with delays (initial tokens) [35, 28]. Thus, the use of state in RAs does not violate our ability to interpret DSGs as genuine dataflow representations.

The following categories of data can be used as inputs in RA subfunctions:

- The value represented by the current DSG token i.e., the DSG token that is consumed by the enclosing RA firing ( $pre_A$  only). This value can be of any type. The type is a design issue of the particular DSG control structure that is being developed for a specific schedule or the particular class of control structures that is being targeted by a particular scheduling tool.

- The state of the enclosing RA.

- The state of the referenced actor.

The following categories of data serve as outputs for (i.e., can be modified by) RA subfunctions:

• The state of the enclosing RA.

• The value of the token that is produced by the RA ( $post_A$  only).

Firing of an RA involves the following sequence of steps:

- 1. The RA consumes a token from its input edge. This token is passed as input to  $pre_A$ , which executes, and updates the state of RA.

- 2. A guarded execution of  $ref_A$  is carried out. That is,  $ref_A$  is fired once if it is enabled.

- 3. An execution of  $post_A$  is carried out. This execution operates on the state of the RA. The output value from this execution is produced as the output of the RA firing.

The general purpose of  $pre_A$  and  $post_A$  is to manipulate DSG tokens. The values of DSG tokens, in conjunction with SCAs, contribute to overall schedule control. Computations in  $pre_A$  and  $post_A$  are optional. For example, an RA can simply execute the referenced actor unconditionally, maintain no internal (RA) state, and pass input DSG values from input to output without modification. Such "lightweight" RAs are typical in the construction of static scheduling structures, as well as in dynamic structures where dynamic schedule control is managed by SCAs. When code is generated from DSGs, such lightweight RAs can easily be detected and "optimized away" so that they do not result in run-time overhead.

An example of a non-lightweight RA is one that updates DSG tokens with estimates of the amount of energy or execution time taken by the associated firings. Such information can then be used by the enclosing DSG to adapt overall schedule control —

e.g., when the DSG is embedded within a parameterized dataflow system or other kind of reconfigurable dataflow graph framework (e.g., see [6, 55]).

#### 3.5 Schedule Control Actors

To model dynamic scheduling structures, SCAs generally play an important role in conjunction with RAs. An SCA is an actor that can have any positive number of input ports and any positive number of output ports. In other words, an SCA must have at least one input port and output port, and may have any number of additional input or output ports. The dataflow behavior of an SCA exhibits the following *lumped homogeneous* synchronous dataflow (LHSDF) condition: for every firing f of an SCA C, we have that  $n_c = n_p = 1$ , where  $n_c$  represents the total number of tokens consumed by C across all input ports during f, and  $n_p$  represents the total number of tokens produced across all output ports during f.

Note that an SCA C can have internal state, and if we model that state as a self-loop edge for C, then this edge is treated independently of the LHSDF condition — i.e., such a self-loop edge is a standard HSDF edge whose dataflow does not "count towards" the values of  $n_c$  and  $n_p$ .

A token in a DSG can be interpreted loosely as an "actor level program counter" for a given target processor. The LHSDF condition for SCAs along with the HSDF semantics of RAs guarantee that there is only one such program counter (thread of control) that is "demanded of" each target processor. This ensures that the schedule execution modeled by the DSG conforms to the assumption that individual target processors execute actors

sequentially.

Note that while our proposed DSG model is used to model schedules for CFDF graphs, SCAs and hence DSGs do not necessarily conform to CFDF semantics. The primary requirement for SCAs in the context of the associated actor level program counter concept is most naturally captured by LHSDF semantics as opposed to CFDF.

We introduce several types of SCA actors that will be used in this thesis. Table 3.1 summarizes properties of these actors. The *loop* actor has two pairs of inputs and outputs. One pair is used to perform computations within the loop repeatedly, while the other pair is used for conditionally branching into and exiting the loop based on certain control conditions. Since there is only one DSG token, execution always proceeds unambiguously either inside or outside the loop.

SCA actors can be paired with other SCA actors to provide special control functions that involve their coordination. For example, if and fi provide DSGs with the capability of selecting computations conditionally. The number of outputs for a given if actor must match the number of inputs to the corresponding fi actor to provide conditional selection of the computations that are enclosed by the matching if and fi pair.

The pair *snd* and *rec* is used for interprocessor communication and synchronization in concurrent DSGs (CDSGs), which are discussed further in Section 3.7.

# 3.6 Sequential Dataflow Schedule Graphs

A DSG for a single-processor schedule represents the time-multiplexed (sequential) execution of a set of actors on a single processing resource. Execution of the DSG

Table 3.1: Examples of SCAs.

| SCA  | # of inputs | # of outputs |  |  |

|------|-------------|--------------|--|--|

| loop | 2           | 2            |  |  |

| if   | 1           | ≥ 2          |  |  |

| fi   | ≥2          | 1            |  |  |

| snd  | 1           | 2            |  |  |

| rec  | 2           | 1            |  |  |

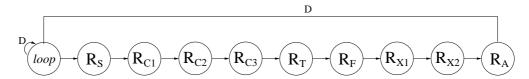

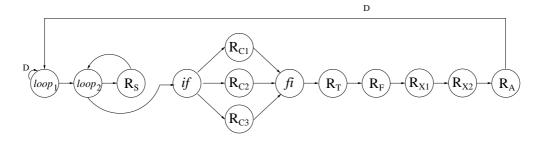

models the evolution of actor firings in the associated sequential schedule. To preserve this sequential execution property, a *sequential DSG* (SDSG) imposes the restriction that *at most one token* can be present in the entire DSG at any given time. This requirement formally captures the interpretation of DSG tokens as actor level program counters in the context of single-processor schedules. Just as the program counter in a conventional processor "points to" a single instruction at any given time, the unique SDSG token points to a single SDSG actor, which is the next actor to execute.

For example, consider the class of single appearance schedules for SDF graphs [8]. These schedules are represented in terms of *looped schedules* such that each actor appears exactly once, implying, for example, minimal code size under inline implementation. For example, the looped schedule (3(2ab)c), involving 3 actors a, b, c, and 2 loops represented by the two nested, parenthesized terms, represents the firing sequence ababcababcababc.

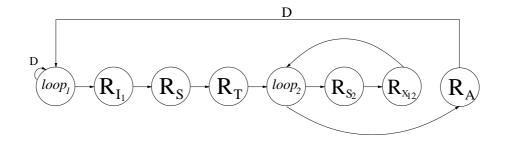

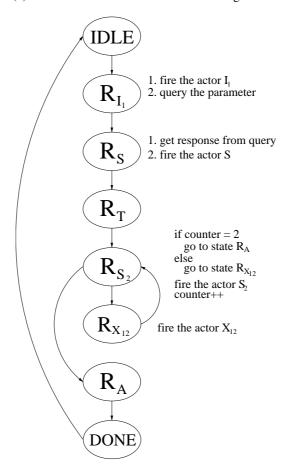

To demonstrate SDSGs for single appearance schedules, we apply the loop SCA