**ABSTRACT**

Title of Document: AUTOMATIC CRITICAL SECTION

DISCOVERY USING MEMORY USAGE

PATTERNS.

Lisa Marie Stechschulte, M.S., 2012

Directed By: Professor Donald Yeung

Department of Electrical and Computer

Engineering

Parallel programming introduces new types of bugs that are notoriously difficult to find. As a result researchers have put a significant amount of effort into creating tools and techniques to discover parallel bugs. One of these bugs is the violation of the assumption of **atomicity**— the assumption that a region of code, called a **critical section**, executes without interruption from an outside operation.

In this thesis, we introduce a new heuristic to infer critical sections using the temporal and spatial locality of critical sections and provide empirical results showing that the heuristic can infer critical sections in shared memory programs. Real critical sections in benchmark programs are completely covered by inferred critical sections up to 75% to 80% of the time. A programmer can use the reported critical sections to inform his addition of locks into the program.

# AUTOMATIC CRITICAL SECTION DISCOVERY USING MEMORY USAGE PATTERNS

By

Lisa Marie Stechschulte

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master or Science

2012

Advisory Committee: Professor Donald Yeung, Chair Professor Rajeev Barua Professor Steve Tretter © Copyright by Lisa Marie Stechschulte 2012

## Acknowledgements

To Dr. Yeung, thank you for your creative ideas, challenging questions, and patient teaching. I learned something new from you in every discussion. Thank you.

To my committee, thank you for your flexibility and willingness to help me.

To my colleagues, thank you for supporting me through this writing process and covering for me while I was away working on my graduate studies.

To Adam, thank you for the support, encouragement, love, and home-cooked meals. I could not have done this without you... and I owe you dinner.

I dedicate my thesis to my parents. You have always believed in me and told me I could do anything I set my mind to do. Thank you.

# Table of Contents

| Acknowledgements                                                    | ii |

|---------------------------------------------------------------------|----|

| Table of Contents                                                   |    |

| List of Tables                                                      | iv |

| List of Figures                                                     | V  |

| Chapter 1: Introduction                                             |    |

| Parallel Computing Background                                       | 2  |

| Processing Element Organization                                     |    |

| Memory Organization                                                 |    |

| POSIX Threads – The Parallel Implementation Studied                 | 5  |

| Common Parallel Programming Bugs                                    | 7  |

| Deadlock                                                            | 8  |

| Data Race                                                           | 9  |

| Atomicity Violation                                                 | 10 |

| Order Violation                                                     | 11 |

| Motivation and Goals                                                | 12 |

| Contributions                                                       |    |

| Chapter 2: Related Work                                             | 15 |

| Transactional Memory                                                | 15 |

| Atomicity Violation Detection and Prevention                        | 19 |

| Chapter 3: Inferring Critical Sections                              | 26 |

| Inferring Objects                                                   | 27 |

| Inferring Critical Sections                                         | 30 |

| Chapter 4: Results                                                  | 34 |

| Benchmarks                                                          |    |

| How suitable is the tool for these benchmarks?                      | 36 |

| Measuring Success                                                   | 41 |

| Real Critical Section Coverage                                      | 43 |

| Inferred Critical Section Accuracy                                  | 50 |

| Overall Performance                                                 | 54 |

| Examples                                                            | 62 |

| Example: Covered Real Critical Section with Excess                  |    |

| Example: Uncovered Real Critical Section Covered with Island Method | 65 |

| Example: Real Critical Section in a Loop                            | 67 |

| Chapter 5: Discussion                                               |    |

| Improving the Results                                               | 70 |

| Potential Uses                                                      |    |

| Chapter 6: Future Work                                              |    |

| Analyzing New Benchmarks                                            |    |

| Improving Object and Critical Section Inference                     |    |

| Creating a Completely Automated Tool                                |    |

| Appendices                                                          |    |

| Glossary                                                            |    |

| Bibliography                                                        | 80 |

# List of Tables

| 37 |

|----|

| 13 |

|    |

|    |

|    |

| 51 |

|    |

|    |

| 54 |

|    |

# List of Figures

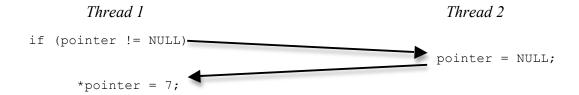

| Figure 1: Atomicity bug example.                                                   | 10     |

|------------------------------------------------------------------------------------|--------|

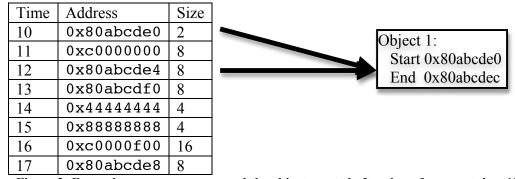

| Figure 2: Example memory accesses and the object created after the reference at t  | time   |

| 12. Here the time threshold is 4 and the address distance threshold is 8 bytes     |        |

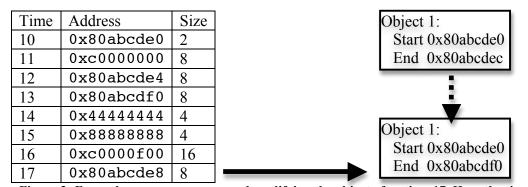

| Figure 3: Example memory accesses and modifying the object after time 17. Here     | e the  |

| time threshold is 4 and the address distance threshold is 8 bytes.                 | 28     |

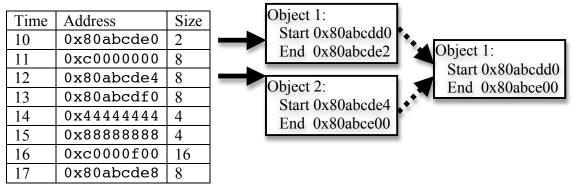

| Figure 4: Example memory accesses and merging after time 12 when both addres       | ses    |

| are in objects. Here the time threshold is 4 and the address distance threshold    | d is 8 |

| bytes.                                                                             | 29     |

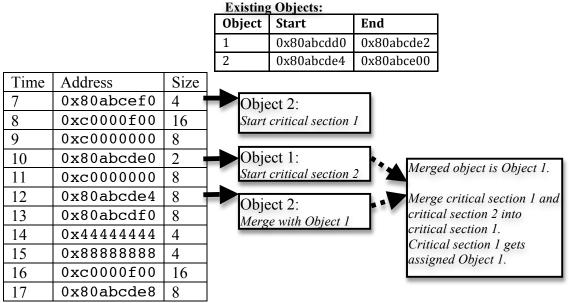

| Figure 5: Merging active critical sections from when related objects are merged.   |        |

| Here the object creation time threshold is 4 and the distance threshold is 8 by    |        |

| The critical section non-object accesses threshold is 50                           |        |

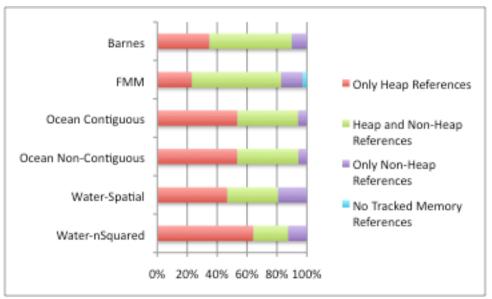

| Figure 6: Percentage of real critical sections that reference only heap memory, on | -      |

| non-heap memory, some of both, and no tracked memory references                    |        |

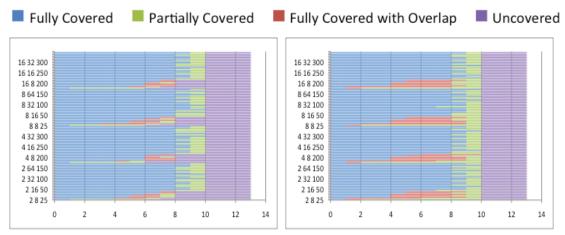

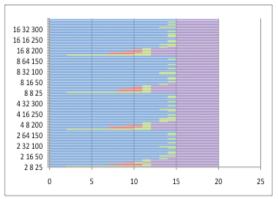

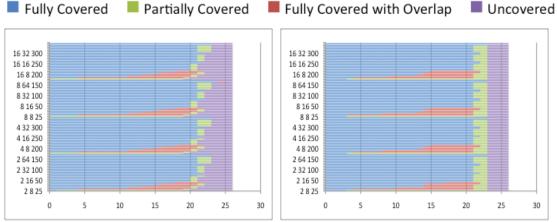

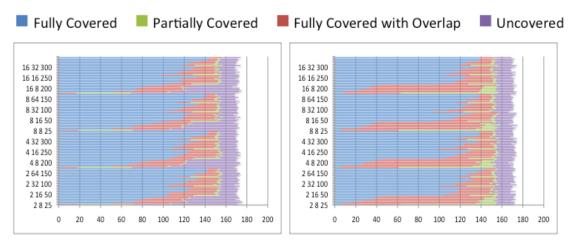

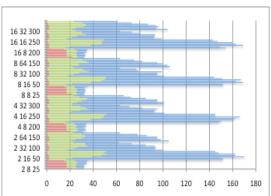

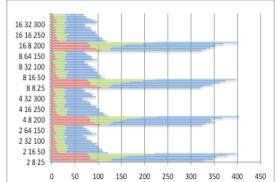

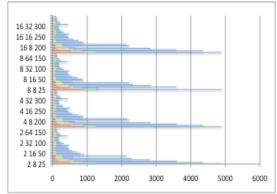

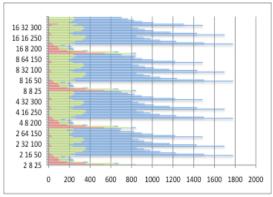

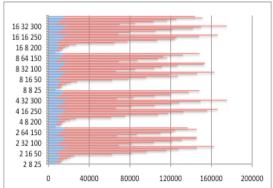

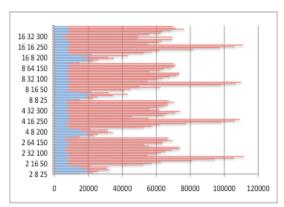

| Figure 7: Static critical section coverage for Ocean Contiguous using Islands      |        |

| Figure 8: Static critical section coverage for Ocean Contiguous                    |        |

| Figure 9: Static critical section coverage for FMM using Islands.                  |        |

| Figure 10: Static critical section coverage for FMM.                               |        |

| Figure 11: Static critical section coverage for Barnes using Islands.              |        |

| Figure 12: Static real critical section coverage for Barnes.                       |        |

| Figure 13: Static critical section coverage Ocean Non-contiguous.                  |        |

| Figure 14: Static critical section coverage Ocean Non-contiguous using Islands     |        |

| Figure 15: Static critical section coverage for Water-nSquared using Islands       |        |

| Figure 16: Static critical section coverage for Water-nSquared                     |        |

| Figure 17: Static critical section coverage for Water-Spatial using Islands        |        |

| Figure 18: Static critical section coverage for Water-Spatial.                     |        |

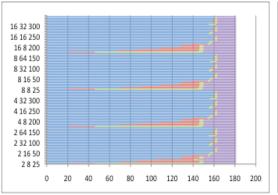

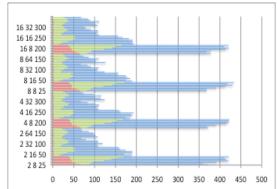

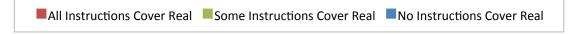

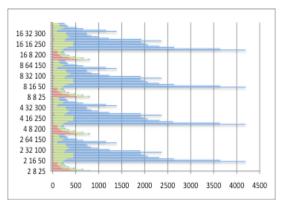

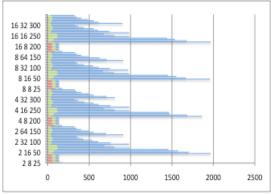

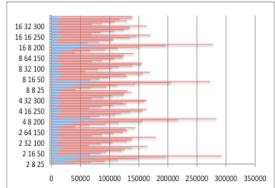

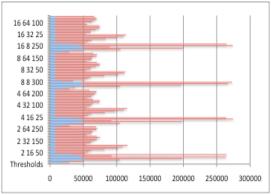

| Figure 19: Dynamic critical section coverage for Ocean Contiguous using Islands    |        |

| Figure 20: Dynamic critical section coverage for Ocean Contiguous.                 |        |

| Figure 21: Dynamic critical section coverage for FMM using Islands.                |        |

| Figure 22: Dynamic critical section coverage for FMM.                              |        |

| Figure 23: Dynamic critical section coverage for Barnes using Islands              |        |

| Figure 24: Dynamic critical section coverage for Barnes.                           |        |

| Figure 25: Dynamic critical section coverage for Water-nSquared using Islands      |        |

| Figure 26: Dynamic critical section coverage for Water-nSquared                    |        |

| Figure 27: Dynamic critical section coverage for Water Spatial using Islands       |        |

| Figure 28: Dynamic critical section coverage for Water Spatial.                    | 49     |

| Figure 29: Dynamic critical section coverage for Ocean Non-contiguous using        | 49     |

| Islands. Figure 30: Dynamic critical section coverage for Ocean Non-contiguous     |        |

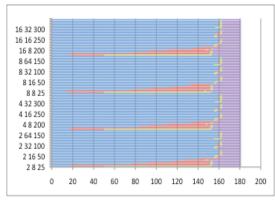

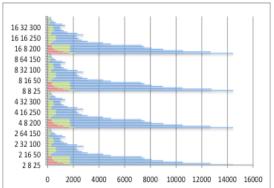

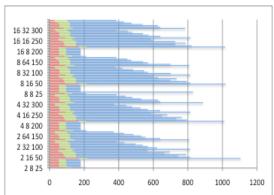

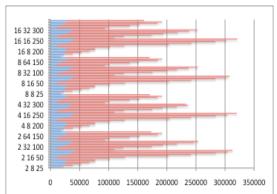

| Figure 31: Static inferred critical section accuracy for FMM using Islands.        |        |

| Figure 32: Static inferred critical section accuracy for FMM.                      |        |

| Figure 32: Static inferred critical section accuracy for Ocean Contiguous using    | 50     |

| Islands                                                                            | 56     |

| Figure 34: Static inferred critical section accuracy for Ocean Contiguous          |        |

| Figure 35: Static inferred critical section accuracy for Barnes using Islands                        | 56         |

|------------------------------------------------------------------------------------------------------|------------|

| Figure 36: Static inferred critical section accuracy for Barnes.                                     | 56         |

| Figure 37: Static inferred critical section accuracy for Water-nSquared using Islan                  | nds.<br>57 |

| Figure 38: Static inferred critical section accuracy for Water-nSquared                              | 57         |

| Figure 39: Static inferred critical section accuracy for Water Spatial using Islands                 |            |

| Figure 40: Static inferred critical section accuracy for Water Spatial                               |            |

| Figure 41: Static inferred critical section accuracy for Ocean Non-contiguous using                  |            |

| Islands.                                                                                             | 57         |

| Figure 42: Static inferred critical section accuracy for Ocean Non-contiguous                        |            |

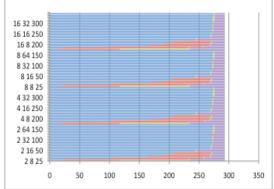

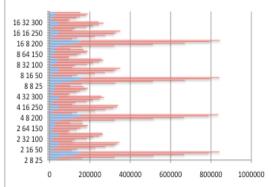

| Figure 43: Dynamic inferred critical section accuracy for Ocean Contiguous using                     |            |

| Islands.                                                                                             | 58         |

| Figure 44: Dynamic inferred critical section accuracy for Ocean Contiguous                           | 58         |

| Figure 45: Dynamic inferred critical section accuracy for FMM using Islands                          |            |

| Figure 46: Dynamic inferred critical section accuracy for FMM.                                       | 58         |

| Figure 47: Dynamic inferred critical section accuracy for Barnes using Islands                       | 58         |

| Figure 48: Dynamic inferred critical section accuracy for Barnes.                                    | 58         |

| Figure 49: Dynamic inferred critical section accuracy for Water-nSquared using                       |            |

| Islands                                                                                              | 59         |

| Figure 50: Dynamic inferred critical section accuracy for Water-nSquared                             | 59         |

| Figure 51: Dynamic inferred critical section accuracy for Water Spatial using Isla                   | ınds.      |

|                                                                                                      | 59         |

| Figure 52: Dynamic inferred critical section accuracy for Water Spatial                              | 59         |

| Figure 53: Dynamic inferred critical section accuracy for Ocean Non-contiguous                       |            |

| using Islands.                                                                                       | 59         |

| Figure 54: Dynamic inferred critical section accuracy for Ocean Non-contiguous.                      | 59         |

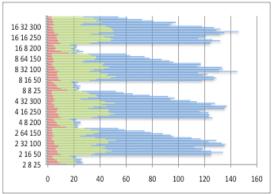

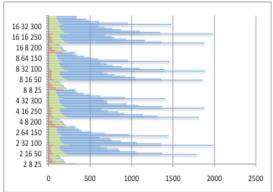

| Figure 55: Inferred critical sections' instructions by real overlap for Ocean                        |            |

| Contiguous.                                                                                          | 60         |

| Figure 56: Inferred critical sections' instructions by real overlap for Ocean                        |            |

| Contiguous using Islands.                                                                            | 60         |

| Figure 57: Inferred critical sections' instructions by real overlap for FMM using                    |            |

| Islands.                                                                                             | 60         |

| Figure 58: Inferred critical sections' instructions by real overlap for FMM                          |            |

| Figure 59: Inferred critical sections' instructions by real overlap for Barnes                       |            |

| Figure 60: Inferred critical sections' instructions by real overlap for Barnes using                 |            |

| Islands.                                                                                             |            |

| Figure 61: Inferred critical sections' instructions by real overlap for Water-nSquare                |            |

| using Islands.                                                                                       |            |

| Figure 62: Inferred critical sections' instructions by real overlap for Water-nSquare                |            |

| Figure 62: Informed spitial gestional instructions by real eventon for Weter Spatial                 | 61         |

| Figure 63: Inferred critical sections' instructions by real overlap for Water Spatial using Islands. |            |

| Figure 64: Inferred critical sections' instructions by real overlap for Water Spatial                |            |

| Figure 65: Inferred critical sections' instructions by real overlap for Ocean Non-                   | 01         |

| contiguous using Islands                                                                             | 61         |

| configuous using islands                                                                             | 01         |

| Figure 66: Inferred critical sections' instructions by real overlap for Ocean Non- |    |

|------------------------------------------------------------------------------------|----|

| contiguous                                                                         | 61 |

# List of Code Segments

| Code Segment 1: Water-Spatial <i>mdmain.c</i> printing critical section            | 38      |

|------------------------------------------------------------------------------------|---------|

| Code Segment 2: FMM CreateParticleList malloc critical section                     | 39      |

| Code Segment 3: FMM InsertBoxInGrid critical section                               | 40      |

| Code Segment 4: Assembly code for FMM InsertBoxInGrid critical section             | 40      |

| Code Segment 5: Critical section in mdmain.c lines 114 to 166, which is the res    | sult of |

| expanding a BARRIER macro in mdmain.C line 47.                                     | 63      |

| Code Segment 6: Structure start: the object that associated with the inferred cri  | tical   |

| sections that fully cover the real critical section in mdmain.c lines 114 to 1     | 66. 64  |

| Code Segment 7: Real critical section in lines 160 to 162 of interf.c (correspond  | ding to |

| lines 145-147 of interf.C)                                                         | 65      |

| Code Segment 8: Real critical section in kineti.c lines 47 to 60 (kineti.C lines 3 |         |

| 45)                                                                                | 67      |

## Chapter 1: Introduction

To provide high performance, applications running on our home computers, web servers, data centers, and scientific computing clusters have embraced techniques to run many tasks at once. This move from serial to parallel processing allows a scientific application to run a complex computation faster, a web server to serve many clients at once, and our home computers to seamlessly offer high performance to multiple services at the same time.

However, writing an application that runs in parallel is difficult and prone to error. Programmers are trained to think of their code as running sequentially—one instruction follows the next and nothing is executed between them—but in a parallel program, two or more sections of the code that run simultaneously could interfere with each other. When that happens, a program could crash, hang eternally, or produce an incorrect answer.

Parallel programming bugs are notoriously difficult to find. It is not uncommon for a bug to manifest itself only with particular inputs and a specific interleaving of the simultaneously running sections of code. Researchers have put a significant amount of effort into creating tools and techniques to discover bugs in static and dynamic code and building systems that attempt to mask the effects of parallel bugs.

In this thesis, we present evidence for a new way to discover a type of parallel programming bug called an **atomicity violation**, which occurs when a programmer expects that a region of code will be executed without interference from other

simultaneously executing code regions—that is it must execute **atomically**. A region of code that must execute atomically is called an **atomic section** or **critical section**. Existing research uses two primary methods to find atomicity violations. In one method, tools determine if code regions executing in parallel could be executed in some serial order and get the same result—in other words, determining if a parallel execution is **serializable**. If a parallel execution cannot be serialized, the tools assert that an atomicity violation may have occurred. The other method heuristically assumes that critical sections have temporal locality and that atomically executing large groups of consecutive memory accesses can prevent atomicity violations.

Our heuristic is quite different. We intuit that programmers want accesses to related variables to execute atomically. Thus, our tool forms **objects** composed of related variables and builds critical sections to protect accesses to these objects. In this study, we explain how we form objects and their related critical sections.

### Parallel Computing Background

To begin, we define **parallel computing** as performing two or more computations simultaneously. Each computation is performed by a **processing element**—a generic term to describe any unit that can perform a computation.

### **Processing Element Organization**

In his 1972 paper "Some Computer Organizations and their Effectiveness," Flynn classifies processing element organizations into four categories by how many instruction and data streams are used simultaneously by all processing elements. The simplest organization is Single Instruction-Single Data (SISD)—this is a sequential

element at a time. When multiple processing elements execute the same instruction at the same time but operate on different data, they are using the Single Instruction-Multiple Data (SIMD) organization. A vector or array processor, where multiple processing units share a program counter but operate on independent data, is an example of SIMD organization. It is important to note that SIMD enforces processing elements to operate instructions in lockstep. The third organization, Multiple Instruction-Single Data (MISD), is not used frequently. In this organization, each processing element executes a different instruction on the same data. In the final organization, Multiple Instruction-Multiple Data (MIMD), each processing element executes a different set of data [9].

In later years, specific MIMD organizations were defined to include the Single Program-Multiple Data (**SPMD**) organization. In this organization, processing elements execute the same program, but do not operate in lockstep like the SIMD processing elements (each processing element has its own program counter). Data is divided among the programs [5].

## **Memory Organization**

In any Multiple Data organization, data can be distributed or shared among processing elements.

In the shared memory model, multiple processing elements have access to the same memory and can access the memory of every other processing element [6].

This is especially useful for communication among processing elements. In hardware, shared memory can be accomplished by having multiple processors on a

single chip each with its own cache; all caches are then linked to a shared main memory. Cache coherence protocols keep each cache up to date with main memory and with the caches of the other processors as necessary. In software, the shared-memory model can be implemented using a multi-threading library like the *pthreads* library, for example. The library offers functions for the program to create a thread—a stream of instructions that can run independently of the main process but is also still sub-process of the main process. It also offers functions to synchronize the execution of the threads and provide threads with exclusive access to regions of memory through structures called *locks*.

In the distributed memory model, individual processing elements access only their own data and do not have access to the data of other processing elements.

Processing elements can be sure that if they perform an operation on data, the data is current and has not been modified by any other processor. Communication between processing elements can be complicated in this model because it must take place in a separate network outside of memory. One communication solution is to use a message passing library like the Message Passing Interface (MPI) for communication between processing elements. To use MPI, the programmer writes a single program that runs on every machine in a cluster or every processing core of a single machine. MPI offers functions to send and receive messages and a barrier function, which stops processing on a core until a certain condition—for example, all cores have reported their results—is met. The programmer synchronizes the cores and communicates between them by using these send, receive, and barrier functions. All communication

between cores in the message passing model is explicit, so the data on which one core is operating cannot be modified unexpectedly by another core [7].

### **POSIX Threads** – The Parallel Implementation Studied

For this study, we analyzed programs that used the POSIX Threads, or *pthreads*, C library to implement programs running the shared memory SPMD model. As the library's name indicates, threads are the fundamental tools used in this library to parallelize code. A thread is an independent stream of instructions that exists within a process. The thread uses some basic resources of its parent process, but the resources it uses are basic enough that the operating system can scheduled it independent of the parent process. While all threads have access to the program's global data, each thread maintains its own stack, registers (including an instruction pointer), and private data [18].

The *pthreads* library offers the function *pthread\_create* for the main process or threads inside the main process to create new threads. When a thread is created, it is given a function to execute. This organization follows the SPMD model since every thread's code is part of a single program, but threads can execute different parts of the program simultaneously.

A thread can be terminated by the main process, another thread, or itself. The thread terminates itself when it returns normally from the function it was given at creation or when it calls the function *pthread\_exit*. A thread can call *pthread\_cancel* to terminated another thread. If the whole process is terminated or if *main* returns, all threads are terminated [18]. When a thread is terminated, its stack and private data are discarded.

Since all threads can read and modify the process's global data, the programmer must enforce that these accesses are appropriately synchronized. As an example, say a process has two threads that have finished their computations storing the results in *local result* and now must add their result to the global variable *total*. Thread 1 finishes, reads total, locally performs the addition local total = local result + total, then stores local total into total. Thread 2 will do the same tasks. If Thread 2 finishes just slightly after Thread 1 so that Thread 2 reads total after Thread 1 read total but before Thread 1 updated total, then the final result will not be total plus both variables *local result*, but instead, will be *total* plus the *local result* that updates *total* last. Access to total needs to be protected so that this cannot happen. This region of code is called a **critical section**, because it accesses a shared resource (total) and must execute atomically. Atomic execution means that all computations occur together without other threads interrupting. As Netzer and Miller put it, "Atomic execution means that the final state of variables read and written in the section depends only upon their initial state at the start of the section and upon the operations performed by the code (and not operations performed by another process)" [21].

The *pthreads* library provides the data structures and functions to synchronize access to global data and resources. The structure is called a **mutex**, which stands for "mutual exclusion." When a region of code must have mutually exclusive access to data or a resource, the programmer can guarantee this by insisting that before executing that region, the thread must **lock** the mutex using the function *pthread\_mutex\_lock*. Only one thread can hold a lock on a mutex at once. When mutually exclusive access to the data or resource is no longer needed, the mutex is

**unlocked** using *pthread\_mutex\_unlock*. It is then available for other threads to lock and access memory regions exclusively [18].

Threads can synchronize with each other using *pthreads* library's *barrier* function and condition variables and functions. The *barrier* function forces each thread to stop executing until all threads reach the barrier. A condition variable works with a mutex to signal events to other threads. As an example, Thread 1 recalculates a value *result* every time the global variable *total* is updated while other threads can update *total*. Thread 1 could continuously poll *total* waiting for a change and recalculating *result* when it notices *total* has changed; or when other threads update *total* from within a critical section (while a mutex is locked), they could notify Thread 1 via the condition variable that *total* has changed, awakening Thread 1 and causing Thread 1 to start its computation. The condition functions that we find in our analysis include *pthread\_cond\_wait*, which blocks a thread and releases the mutex until the condition variable changes, and *pthread\_cond\_broadcast*, which broadcasts a signal to all threads that the condition variable has changed [18].

## Common Parallel Programming Bugs

While performing multiple computations at once provides performance gains, it also introduces a new set of potential programming bugs. In the paper "Learning from Mistakes – A Comprehensive Study on Real World Concurrency Bug Characteristics," the authors noted four types of bugs found in concurrent (i.e., parallel) programs [15]. Each of these bugs is discussed separately below.

The authors studied 105 randomly selected concurrency bug reports from the open-source software applications MySQL, Apache, Mozilla, and Open Office.

MySQL (a database application) and Apache (a web server) are both server applications; Mozilla (a web browser) and Open Office (a suite of word processing, spreadsheet, and other office applications) are both client applications. They examined everything included in the bug reports (source code, patches, programmer comments) to determine the type of bug and how it was fixed. From this, they developed an understanding of what types of bugs exist in the real world, under what conditions they appear, and how they are fixed [15].

#### Deadlock

Deadlock occurs when two or more processing elements cannot proceed because they are waiting on each other to release access to a resource [15]. For example, Thread 1 must lock mutex A and then mutex B; meanwhile, Thread 2 locks mutex B and then mutex A. If simultaneously Thread 1 locks mutex A and Thread 2 locks mutex B, then neither will be able to proceed with their next lock and they will wait indefinitely.

It might seem that deadlock cannot occur when a program has only one gatekeeper guarding exclusive access to resources; however, in the "Learning from Mistakes" study, the authors found that 22% of deadlock bugs occurred because one thread tried to acquire a resource that it already had. They also found that 97% of the deadlock bugs were the result of "two threads circularly waiting for at most *two resources*" [15]. Despite the fact that increasing the number of exclusively accessed resources provides more opportunity for deadlock, very few of the deadlock bugs involved more than two resources.

#### **Data Race**

A data race occurs when two or more processing elements access a shared variable without synchronizing [15]. The example that begins on page 5 where two threads add their results to a global variable *total* is an example of a data race. Here, the two threads race to update *total*, with the thread that updates *total* last overwriting the update made to *total* by the thread that updated *total* first.

Data races are not always errors. Sometimes programmers use data races as an efficient method of raising a flag to all processing elements that a condition has been met. For example, multiple processing elements are tasked with answering the question, "Is *x* in my data set? If so, where is *x*?" All processing elements share a global variable *found*, which is initially set to zero. Each processing elements checks *found* to see if it is non-zero indicating *x* has been found. If so, the processing element quits. If not, the processing element continues looking. If a processing element finds *x*, it updates *found* to the location of *x* without locking *found*. Because processing elements do not lock *found*, it is possible that two processing elements could simultaneously race to overwrite *found* with different locations; however, both locations are valid locations of *x*, so either location correctly answers the problem.

Because data races are not always bugs, the authors of "Learning from Mistakes" did not include them in the bug patterns they studied. Still many researchers have studied the area of data race detection and prevention, and we will discuss some of these studies in Chapter 2. It is important to note that a data-race free program may have other concurrency bugs.

### **Atomicity Violation**

As explained in the section above on *POSIX Threads*, atomic execution means that only the initial state of variables and data on a processing element and the instructions that processing element executes affect the final state of the variables and data [21]. The region of code that should execute atomically is called a **critical section**. If another processing element influences the final state of a critical section, then an atomicity violation has occurred. This occurs because the programmer incorrectly assumes that a section of code will execute atomically and does not protect the region from outside access.

As an example, consider a program in which the operations of Figure 1 on the global variable *pointer* occur on two different threads without any protection from outside accesses. In the code for Thread 1, the programmer incorrectly assumes that checking that *pointer* is initialized and dereferencing *pointer* will occur atomically. Instead, Thread 2 interferes with these two operations and resets *pointer* to NULL causing Thread 1 to crash when it tries to dereference *pointer*. The programmer could have fixed this bug by surrounding each block of code—each critical section—with a lock and unlock to a common mutex.

Figure 1: Atomicity bug example.

In the "Learning from Mistakes" study, 51 out of 74 non-deadlock concurrency bugs studied (nearly 69%) were atomicity violations [15].

#### **Order Violation**

The authors of "Learning from Mistakes" found that order violations constituted 32% of the non-deadlock concurrency bugs examined. Unlike the three bug types discussed already, very little research has been done on detecting order violations [15].

An order violation occurs when the programmer assumes an order between blocks of code in different threads but does not enforce this order between the threads [15]. For example, the first thread initializes a variable and the second thread uses the variable. If the programmer does not force the initialization to occur before the second thread starts to use the variable, then an order violation occurs. In a server application where the main thread creates a new thread to handle each new client connection, this type of order violation could occur if the programmer starts the new thread before initializing a structure containing the client's data.

A variety of fixes are available for this order violation. The programmer could insert a barrier function at the beginning of the second thread and after the initialization in the first thread; this requires that the second thread wait for the first to finish before continuing. The programmer could initialize the variable prior to creating the second thread, so that the second thread can proceed immediately once it is created. The second thread could poll the variable to see if it has been initialized and proceed as soon as the variable is initialized.

Note that only one of these solutions, the barrier solution, uses any sort of synchronization function. One finding of the "Learning from Mistakes" study was that 73% of non-deadlock concurrency bugs (of all types, not just order violations)

were fixed without using locks [15]. While locks can fix this type of bug, they also can hurt performance making other fixes more efficient.

#### Motivation and Goals

The "Learning from Mistakes" study showed that 69% of non-deadlock concurrency bugs examined were atomicity violations. Given that atomicity violations are so common, our goal was to determine if the memory access pattern of a dynamically executing program could suggest related variables that must be accessed atomically and where the critical sections for accessing these related variables were in the program's static code. If in fact the memory access pattern correctly discovered critical sections, this information could be used to build a tool that suggested potential critical sections to the programmer or a tool that automatically locked down critical sections. By automatically adding locks to critical sections, we could address the 27% of non-deadlock concurrency bugs in the "Learning from Mistakes" study that were fixed by adding or changing locks [15].

Of all non-deadlock concurrency bugs (atomicity violations, order violations, and other bugs) examined in the "Learning from Mistakes" study, 34% of them involved accesses to multiple (often related) variables (the remaining 66% involved only one variable); however, few concurrency bug detection tools look for bugs caused by accessing multiple variables [15]. Rather than using program variables to find the shared resources of critical sections, we aimed to address the multiple-variable nature of concurrency bugs by analyzing shared resources at the level of the memory layout. We formed **objects**, contiguous blocks of memory, by merging nearby memory addresses that are accessed close together in time; consequently, if

access to multiple variables causes a concurrency bug and these variables are accessed nearby in space and time, they will form an object and can be detected as needing protection in a critical section.

#### **Contributions**

Tools that detect and avoid atomicity violations are an important part of atomicity research. While all the tools address the problem slightly differently, they also use similar techniques. In Chapter 2: Related Work, we discuss several of these tools: AVIO [16], MUVI [14], Atom-Aid [17], and AtomTracker [20].

The major contribution of this study is the addition of a novel heuristic for determining critical sections. The heuristic is based on the idea that programmers assume that accesses to related variables happen atomically. We develop a method using the temporal and spatial locality of memory accesses to group related variables into memory objects and from those objects produce a set of static code critical sections inferred during a single run of a program.

This study gives empirical results showing that the novel heuristic can infer objects and critical sections in shared memory programs. A comparison with the real critical sections in analyzed programs shows real critical sections are covered by inferred critical sections up to 75% to 80% of the time. A programmer can use the reported critical sections to inform his addition of locks, or a new tool could be developed to automatically insert locks into the program for future runs.

Critical sections in this tool are inferred on the fly eliminating the need to collect massive memory traces required by AVIO and AtomTracker.

Programmers do not need to annotate code in any way in order for the tool to discover critical sections. In fact, the tool can run on a program that has no synchronization or locking implemented. Additionally, the code never needs to run correctly for the tool to infer critical sections. This is a prerequisite for AVIO and AtomTracker.

Like MUVI, our tool can detect critical sections that arise from using multiple variables. AVIO and Atom-Aid cannot do this.

The tool is implemented as a C++ Pintool (see Chapter 3: Inferring Critical Sections). This allows it to run on any program using X86 assembly language.

Otherwise, the underlying hardware is irrelevant to the tool, unlike Atom-Aid, which must be run on top of an *implicit atomicity* system.

Perhaps the most important difference between this tool and AVIO, MUVI, Atom-Aid, and AtomTracker is that the only inter-processor information that our tool must know is whether a memory object is shared, in other words whether it is accessed by more than one processor. All the other tools require significant information about memory access interleavings. As a result, our tool can operate without significant inter-process communication.

## Chapter 2: Related Work

In this chapter, we review the current state of atomicity research. We begin by discussing transactional memory, an increasingly popular way of implementing critical sections without locks. Transactional memory grew out of the concept of database transactions and is used in parallel processing to avoid atomicity violations; we discuss several transactional memory studies below. Then we cover a series of studies that aim to automatically detect and correct atomicity violations.

## Transactional Memory

In the section *POSIX Threads* – The Parallel Implementation Studied, we introduced a lock-based system for implementing parallelism. However, another important shared-memory model for parallelism uses the concept of a **transaction**, which was developed in the study of databases. A transaction is a group of operations that optimistically execute atomically, meaning that the transaction will execute but before modifying the state of the shared memory or database will check to ensure that its own atomicity has not been violated by other transactions. If its atomicity has been violated, it aborts; otherwise, it commits its changes making them visible to the whole system [12]. In databases, the state of the system is allowed to be inconsistent while a transaction is executing, but must return to a consistent state once the transaction completes [8].

An example of a transaction is transferring money between bank accounts; here the constraint for the consistent state is that the amount of money stays constant. During the transaction, one bank account will be debited before the other is credited

15

violating the constraint that the amount of money in the system is constant; however, at the end of the transaction, both bank accounts have been modified and the total amount of money is unchanged [8].

Transactions also must be **serializable**, meaning that even though transactions execute simultaneously, one can always get the same result by executing the transactions serially in some order—transaction operations cannot interleave [12]. As Eswaran et al. note, the serializability property is different from determinism—a set of transactions can be serialized without producing the same state in every execution of those transactions. In their paper "The Notions of Consistency and Predicate Locks in a Database System," they provide an excellent example of serializable transactions: consider an airplane reservation system where a transaction is assigning a seat for a reservation; the seats may be assigned differently depending on the serializable order of the transactions, but a consistent seating assignment will always be produced (no seat will be assigned more than once) [8].

In their 1993 paper "Transactional Memory: Architectural Support for Lock-Free Data Structures," Herlihy and Moss building on the database concept of transactions present the concept of transactional memory. Transactional memory relies on the concept of lock-free shared data structures, a data structure that does not require operations on it to be mutually exclusive. A lock-free data structure allows other processors to operate on it even if the first processor to operate on it gets interrupted during operation; in lock-based systems, this first processor would continue to hold the lock on the structure while it handles the interruption preventing all other processors from operating on it—this is called *convoying* [12]. In addition to

preventing convoying, transactional memory has two other major advantages over lock-based models: transactional memory avoids the problem of *priority inversion* where a lower-priority process holds a lock needed by a higher-priority process preventing the higher-priority process from progressing. And, transactional memory cannot *deadlock* (see Deadlock above).

While others built software implementations of lock-free shared data structures, Herlihy and Moss created a new multiprocessor architecture to handle lock-free data structures. They added operations to the cache-coherence protocols to accommodate a set of new memory instructions that allow the programmer to specify that reads and writes to memory are included in a transaction and a set of instructions to change the transaction's state. The hardware to support transactions required two caches—a regular cache to handle non-transactional operations and a transactional cache to handle transactional operations. The transactional cache did not propagate writes to main memory unless a transaction successfully committed [12].

Herlihy and Moss compared their architecture with two software and two hardware methods for atomically updating memory. The two software methods and one hardware method were lock-based. The other hardware method used the LOAD\_LINKED/STORE\_COND operations from the MIPS II architecture, in which the LOAD\_LINKED operation makes a local copy of a shared variable and only stores it back using STORE\_COND if the shared variable has not changed since it was first read; essentially, this is a transaction with a single variable. The transactional memory architecture outperformed all four competitors.

In Herlihy and Moss's transactional memory architecture, the programmer is responsible for annotating transactions at the level of individual loads and stores. In the 2004 paper "Transactional Memory Coherence and Consistency," Hammond et al. eliminate the need for the programmer to annotate individual loads and stores by insisting that "transactions are always the basic unit of parallel work, communication, memory coherence, and memory reference consistency" allowing the programmer to insert only transaction boundaries [10]. They call their shared-memory model *Transactional Memory Coherence and Consistency* (TCC) and developed a hardware-based TCC that requires a central authority to regulate commits for the whole system and relies on broadcast communication of transaction commit packets. Like Herlihy and Moss's transactional memory hardware, TCC requires changes to the caches and cache coherence protocol to maintain transactions.

Programming for the TCC model requires first dividing the code into transactions, carefully ensuring not to break up critical sections. The hardware ensures that transactions are executed atomically, so the programmer does not need to worry about transaction independence. Optionally, the programmer may specify the order in which transactions should execute by giving transactions phase numbers. All transactions with the same phase number will be permitted to execute simultaneously, but TCC will not progress to the next largest phase number until all transactions at the current phase have committed.

In performance tests, TCC performed well, but required a high broadcast bandwidth for broadcasting commit packets. Because broadcast is central to TCC, TCC has limited scalability.

### Atomicity Violation Detection and Prevention

Transactional memory systems like lock-based systems are subject to atomicity violations. In the transactional memory systems described above, the programmer is responsible for correctly annotating transactions so that no critical section is split between two transactions. Likewise, in systems that use *POSIX* Threads, avoiding atomicity violations relies on the programmer's ability to recognize and protect critical sections. The following set of papers address detecting and preventing atomicity violations and identifying critical sections for the programmer.

Up until Lu et al.'s 2006 paper on "AVIO: Detecting Atomicity Violations via Access Interleaving Invariants," most concurrency bug detection research had focused on data race detection. As Lu et al. note, transactional memory models are not immune to atomicity violations, and the growing research in that field made addressing atomicity violations even more pertinent. Two years later their evaluation of the importance of detecting atomicity violations was reinforced by the "Learning from Mistakes" paper (which shared two co-authors with the AVIO paper) that showed atomicity violations constituted 67% of all examined non-deadlock concurrency bugs [15].

AVIO makes three contributions to atomicity violation detections. First, it uses "Access Interleaving (AI) Invariant based detection." Access Interleaving Invariant holds for an instruction if during all correct runs, there is no unserializable access between this instruction and the previous instruction that accessed the same shared variable. In a large number of correct runs, many possible correct interleavings will appear; if the Access Interleaving Invariant holds across all correct

19

runs, then AVIO concludes that the programmer assumed these accesses would be atomic [16].

The authors' second contribution was building and analyzing both software and hardware versions of AVIO. They built the hardware version by extending the cache coherence protocol with the intention of using it to detecting atomicity violation during "production runs." The software version, which had more overhead than the hardware version, was intended for use as a debugging tool allowing a programmer to find a bug that has already occurred [16].

The final contribution was testing AVIO on six real atomicity violation bugs from server applications. They found that AVIO could detect a wider variety of bugs than previously tools. It did not report benign data races (see the section Data Race for a discussion of benign data races). It found only 3-5 static false positives compared with 80 or more false positives from other tools. It did not require the programmer use a specific parallel programming model or to annotate the program in any way. It did not require a large body of training data. The overhead created by AVIO for both the hardware version and the software version was smaller than that for other concurrency bug detection tools [16].

While AVIO only detects Access Interleaving Invariants for single variable accesses, MUVI suggests improvements on AVIO that would discover multi-variable accesses atomicity violations. MUVI uses static program analysis and data-mining techniques to determine correlated variables within large programs. In MUVI, correlated variables must be accessed with a common lock to avoid data races.

Detecting atomicity violations is much harder. With the set of correlated variables

provided by MUVI, AVIO can check the Access Interleaving Invariant between correlated variables. Checking for serializability is much more complicated with two or more variables and the authors of "MUVI: Automatically Inferring Multi-Variable Access Correlations and Detecting Related Semantic and Concurrency Bugs" do not provide detail [14].

In 2008, Lucia et al. presented the first paper on surviving atomicity violations: "Atom-Aid: Detecting and Surviving Atomicity Violations." Their paper begins with analyzing *implicit atomicity* systems—those in which the processors form arbitrary chunks of dynamic instructions and execute them atomically. This means that individual memory instructions within a chunk are never interleaved individually with instructions on other processors; instead, chunks are interleaved. Because chunks are updated atomically, an individual processor can reorder the instructions inside a chunk without influencing other processors. Examples of implicit atomicity systems include [2], [25], and [26]. Lucia et al. studied the effect of changing the chunk size on hiding atomicity violations. They found that while a larger the chunk size does correspond with a higher probability of hiding atomicity violations, the relationship is nearly logarithmic—while large probability gains are reported from increasing the size of chunks from 0 to 2000 instructions for atomicity violations with fewer than 750 instructions, larger chunks barely improve the probability of hiding the violation [17].

The authors sought to improve these probabilities by creating "smart" chunks rather than arbitrary chunks. Atom-Aid, which can be implemented in any implicit atomicity system, was the result. On the fly, Atom-Aid creates smart chunks by

finding potential atomicity violations and inserting chunk boundaries at the beginning of the potential violations. It detects atomicity violations by looking for two accesses to the same variable a within a chunk on one thread with a recent access to a in a different thread from a committing chunk. If these accesses may be unserializable, then Atom-Aid watches for a, and when it appears again, Atom-Aid may insert a chunk boundary before the access to a. We use "may insert a chunk boundary" instead of "will insert a chunk boundary" because if Atom-Aid always broke a chunk at an instance a, it could actually expose the atomicity violation. Instead, Atom-Aid insists that a chunk will be broken at most once and the new chunk will be the default chunk size, and that if a new address is added to Atom-Aid's watch set, that it cannot break the current chunk, only later chunks [17].

Note that Atom-Aid requires knowledge of not only the current memory accesses from the local chunk, but also the memory accesses from the previous local chunk and the memory accesses from chunks committing elsewhere in the system. By bounding the stored memory accesses by chunks, Atom-Aid is able to reduce the amount of data it must manage and analyze. The cost of the boundary is that Atom-Aid cannot detect atomicity violations that are larger than two chunks; on the other hand, no implicit atomicity system can hide an atomicity violation that is larger than a single chunk [17].

Additionally, Atom-Aid is capable of starting a new chunk only after it has identified a variable as part of a potentially unserializable group of accesses [17]. This means that the first potentially unserializable group of accesses could form an atomicity violation that Atom-Aid cannot hide.

In testing, Atom-Aid performed well, hiding almost 100% of the atomicity violations in bug kernels and MySQL, Apache, and XMMS applications. However, for some applications, Atom-Aid created too many unnecessary chunks; for four of the nine bug kernels, the between 46% and 79% of the smart chunks created did not hide atomicity violations [17].

While Atom-Aid and AVIO sought to find and prevent atomicity violations, AtomTracker was built to discover generic atomic regions within programs without requiring any programmer annotation and then detect atomicity violations of these atomic regions. AtomTracker is split into two programs: AtomTracker-I that infers atomic regions and AtomTracker-D that tests for atomicity violations using these regions.

AtomTracker-I takes correct dynamic memory traces of a program and processes them one thread at a time greedily joining together consecutive memory accesses to form atomic regions. At the end, it outputs the entry and exit points of all atomic regions [20].

The algorithm works on a single thread at a time, looping through all threads for a single trace file first before proceeding to the next trace file. For Thread 1, AtomTracker-I begins by trying to merge the first two instructions into a single atomic region. For example, the first two accesses on Thread 1 are  $I_0$ , which reads x, and  $I_1$ , which writes y. If there are no conflicting accesses on any of the other threads, then  $I_0$  and  $I_1$  are merged into an atomic region. If  $J_0$  from Thread 2 writes x and happens between  $I_0$  and  $I_1$ , then  $I_0$  and  $I_1$  can be merged only if  $I_1$  is brought up to  $I_0$  and both happen before  $I_0$ ;  $I_0$  cannot happen after  $I_0$  or else  $I_0$  would not read the

correct value of x. If instead  $J_0$  from Thread 2 reads y, then  $I_0$  can happen after  $J_0$ , but  $I_1$  cannot happen before  $J_0$  or else  $J_0$  would read the wrong value of y. AtomTracker-I must perform this check of merging I0 and I1 into the same atomic region on every thread in the trace. Then it proceeds with the remaining instructions in Thread 1 [20].

Once AtomTracker-I has finished processing a single trace file, it then checks the atomic regions it created against the next trace file. If any are inconsistent, they will be split into smaller atomic regions. Once all trace files are processed, AtomTracker-I reports the resulting atomic regions [20].

Muzahid et al. note that atomic regions rarely cross loop iteration boundaries unless the full loop is included in the atomic region. Therefore, AtomTracker–I discovers loop boundaries and looks for conflicting accesses within the loop boundaries. If there are none, then it treats the entire loop as a unit incorporating either the whole loop or none of it into atomic regions. If there are conflicts within the loop boundaries, then AtomTracker-I ensures that if a loop iteration is included in any atomic region that the atomic region ends at the boundary of a loop iteration [20].

Finally, AtomTracker-I adds the atomic region boundaries it found to the static code of the program. Muzahid et al. point out that this can be particularly difficult when traces follow different control paths, so they supplement the exit points with their corresponding entry points to ensure that the correct exit is followed during a dynamic run using AtomTracker-D [20].

In addition to the inference tool, AtomTracker-D detects atomicity violations on the fly by running the program code modified by AtomTracker-I to contain the atomic regions. The tool works by determining if two concurrently running atomic

regions can be serialized. If they cannot be serialized, then the program notes an atomicity violation [20].

Muzahid et al. implemented AtomTracker by building a C++ Pin tool (see Chapter 3: Inferring Critical Sections) and compared its performance with AVIO [16], MUVI [14], and PSet. The authors do not compare the atomic regions found by AtomTracker-I and the true atomic regions of a correct program; instead, they only report the atomicity violations discovered and the number of false positive atomicity violations discovered. AtomTracker successfully found eight atomicity violation bugs in the MySQL, Apache, and Mozilla, whereas AVIO found three, MUVI found four, and PSet found 2. The false positive rate ranged from 1.6 from the software implementation to 16.4 for a hardware implementation of AtomTracker-D.

## Chapter 3: Inferring Critical Sections

Determining memory objects that must be protected and code regions of a parallel benchmark program that should be treated as critical sections required the ability to dynamically analyze the benchmark's memory usage. While several tools can analyze a program's memory usage, we choose to use Pin because it provides an extensive API to dynamically instrument parallel Linux or Windows executables running on IA-32, IA-64, or Intel® 64 [22].

Instrumentation programs used with Pin, called Pintools, define insertion points and the actions that should be performed at those insertion points. Pin provides the API to insert instrumentation at different levels of a program including images, routines, basic blocks, and instructions. Actions at insertion points can include modifying the program's behavior by inserting C or C++ code or analysis that does not modify the program's behavior, such as saving every address accessed in memory for a memory trace.

For this study, we created a C++ Pintool that captured all non-stack and non-instruction memory operations (both reads and writes) to determine simultaneously if the address should be part of an object and, if it was part of an object, if the address should be included in a critical section. The benchmarks we analyzed used the *pthread* libraries for locking, so the Pintool also captured the *pthread\_mutex\_lock* and *pthread\_mutex\_unlock* functions to define the boundaries of the benchmark's real critical sections. The tool also discarded memory instructions that occurred during a call to *pthread\_mutex\_lock* to prevent analysis on locking-specific code; we wanted the tool to do the same for *pthread\_mutex\_unlock*, however, Pin could not identify

the end of this function, so it was not possible to discard accurately all memory instructions that occurred during this call<sup>1</sup>. Once the program finished running, the Pintool computed statistics on how well the inferred critical sections covered the real critical sections and how many instructions were locked unnecessarily.

## **Inferring Objects**

Every critical section has two components: a memory object and a region of code; the region of code must access the object atomically. Therefore, the Pintool must determine where the objects are before it can find any critical sections.

We define an object as a contiguous region of memory. If within a threshold amount of time (time threshold) a single thread of the benchmark accesses two memory addresses that fall within a threshold number of bytes (address distance threshold), the Pintool groups the two addresses into the same object. For example, consider the following memory accesses with a time threshold of 4 and an address distance threshold of 8 bytes:

Figure 2: Example memory accesses and the object created after the reference at time 12. Here the time threshold is 4 and the address distance threshold is 8 bytes.

<sup>&</sup>lt;sup>1</sup> Pin instruments calls to return to find the end of functions and does not guarantee success. Several other *pthread* functions are called by the benchmarks. These were not discarded in the Pintool's analysis.

Addresses 0x80abcde0 and 0x80abcde4 will be merged together since their time distance is 2 and their byte distance is 4. This will create a new object, *Object 1*, that starts at 0x80abcde0 and ends at 0x80abcdec (note that the end address is an exclusive upper bound on the object). Address 0x80abcdf0 will not be merged into this object since the byte distance to 0x80abcde0 is 16 and the byte distance to 0x80abcde4 is 12; note that this is still true after the *Object 1* is created.

The number of bytes accessed with an address is not considered in determining the distance between two addresses. In our example, address 0x80abcde4 with size 8 accessed at time 12 and address 0x80abcdf0 with size 8 accessed at time 13 will not be merged into an object even though the distance between the last byte accessed at time 12 (0x80abcdeb) and the first byte accessed at time 13 (0x80abcdf0) is only 5 bytes.

Once an object is formed, if an address inside of the object is accessed with a size that extends beyond the end of the object, the object's size will be increased to include all the bytes referenced by this access. Continuing our example from Figure 2, in Figure 3 we see the access at time 17 to address 0x80abcde8 is inside *Object 1*. The size of *Object 1* will be increased so the new end address is 0x80abcdf0.

Figure 3: Example memory accesses and modifying the object after time 17. Here the time threshold is 4 and the address distance threshold is 8 bytes.

As we saw above when two addresses without objects are merged, they form a new object, and when one address that is in an object is merged with another that is not, the object containing the first address subsumes the second. If two addresses are already in separate objects are merged, their corresponding objects are also merged. For example, if the address accessed at time 10 was part of an object that started at 0x80abcdd0 and ended at 0x80abcde2 and the address accessed at time 12 was part of an object that started at 0x80abcde4 and ended at 0x80abce00, then the result of merging the addresses at time 10 and time 12 would be a single object that starts at 0x80abcdd0 and ends at 0x80abce00.

Figure 4: Example memory accesses and merging after time 12 when both addresses are in objects. Here the time threshold is 4 and the address distance threshold is 8 bytes.

Note that in this method of determining objects, a single address with no nearby accesses in space or time will never become an object. This "island" address may still need to be locked. Therefore, we developed a second method for creating objects termed the **island method**. In the island method, the first time a region of memory is accessed it becomes its own object; the starting address is the accessed address and the size of the object is the referenced size. After that, the merging process from the original method takes place.

Merging addresses into objects happens independently for each thread of the benchmark; however, once an object is created, it is maintained in a globally accessible bank of objects. This allows us to log whether an object is exclusive to the thread that created it or shared among multiple threads. An object that is never shared does not need to be locked.

Merging objects and maintaining the global bank is computationally intensive. As a result, we limited the memory operations used to create objects to those that accessed heap memory. Heap memory was determined by instrumenting all calls to *malloc* to capture the start address and the size of the allocated block. As discussed in Chapter 4: Results, nearly all of the benchmarks' real critical sections access heap memory, so narrowing the addresses we consider should not drastically impact our results.

## **Inferring Critical Sections**

At the same time the Pintool builds objects from the benchmark's memory accesses, it also infers critical sections. Although the Pintool only uses heap memory addresses to build objects, it examines all non-stack and non-instruction memory accesses while building critical sections. Critical sections are built by each thread independently and maintained independently until the benchmark finishes running.

A critical section should begin when a thread first accesses an object and end when it last accesses that object before going on to do other tasks. Detecting the beginning of an inferred critical section is easy for the Pintool; if it accesses an object for which it is not currently creating a critical section, then that access begins a new inferred critical section for the object.

Detecting the end of a critical section is much harder. How does the Pintool know that a particular access to an object is the last to that object?<sup>2</sup> It cannot know; however, if it waits long enough and has seen no other accesses, it can guess that the critical section should have ended at the last reference. This is our strategy. The Pintool has a threshold for the number of memory accesses since it last saw the object accessed (non-object accesses threshold), and as soon as that many accesses have passed, it decides the critical section must have ended. The end of the critical section is the last reference to the object.

Inferred critical sections have two states in the Pintool. They are either active or finalized. An active critical section is one for which the Pintool has found a start, but has not yet found the end. Once the end is determined, the critical section is finalized.

A single thread can have multiple critical sections active simultaneously. This would not cause any confusion if the objects were statically determined prior to inferring critical sections, but objects can change while critical sections are active. If two objects are merged together while the Pintool has active critical sections for both of them, the two critical sections are merged also: the critical section that started first gets assigned to the new object; the critical section that started last is discarded. As an example, consider the sequence of memory references below. Two objects, *Object I* that encompasses the access at time 10 and *Object 2* that encompasses the accesses at time 7 and time 12, have already been created:

31

<sup>&</sup>lt;sup>2</sup> This question is similar to the concept of last-touch prediction for caches, and our solution is an algorithm similar to the Least-Recently Used algorithm for cache eviction.

Figure 5: Merging active critical sections from when related objects are merged. Here the object creation time threshold is 4 and the distance threshold is 8 bytes. The critical section non-object accesses threshold is 50.

Object 1 and Object 2 are merged together into Object 1. Since both have active critical sections, the two critical sections are also merged and assigned to Object 1; Critical Section 2 is then discarded. Due to the complexity of bookkeeping, finalized critical sections are not modified even if their corresponding objects get merged with new addresses or other objects.

Multiple threads can create critical sections for the same object at the same time. We allow this to ensure that the Pintool would catch all critical sections if a program had atomicity bugs.

When a thread finishes, the Pintool displays all critical sections that the thread found dynamically and whether the object for which the critical section was created was shared or exclusive to that thread. If the thread repeated execution of a particular region of code where it found a critical section once, it is possible that it found the critical section multiple times, and that critical section will get reported multiple

times. Once all threads are finished, a complete list of critical sections found dynamically in all threads is created.

From this list, the Pintool weeds out critical sections that were found multiple times to determine the static critical sections. Static critical sections are the set of critical sections with unique start and end instruction pairs. If any dynamic instance of a critical section was built from a shared object, the static critical section is considered to reference shared objects also even if some dynamic instances of the critical section were referencing objects accessed exclusively by a single thread.

## Chapter 4: Results

While the method of inferring objects and critical sections may seem simple, applying it to real programs can lead to complex results. In this chapter, we discuss the benchmarks we tested, how we evaluated the tool's performance, the overall results for real critical section coverage and inferred critical section accuracy, and finally some specific examples of real critical sections that the tool did or did not find.

#### **Benchmarks**

To test how well we could infer critical sections using a program's memory usage pattern, we ran the Pintool described above on six benchmarks from the SPLASH-2 benchmark library: Barnes, FMM, Ocean Contiguous Partition, Ocean Non-Contiguous Partition, Water-nSquared, and Water-Spatial. The SPLASH-2 benchmarks are all parallel applications designed for shared memory systems. The six implementations we tested all perform scientific computations, so these results may not transfer to non-scientific programs.

The SPLASH-2 benchmarks are written in C and use macros to define parallel constructs (locks, unlocks, barriers, etc.). For our study, we used the file c.m4.null.POSIX provided on the Modified SPLASH-2 Home Page to replace macros with the original POSIX Thread standard functions [18]. LOCK macros are replaced with a call to *pthread\_mutex\_lock* and UNLOCK macros are replaced with a call to *pthread\_mutex\_unlock*. The original POSIX Thread standard did not implement any barrier function, so instead barriers in c.m4.null.POSIX start with

pthread\_mutex\_lock and check condition variables to determine if all threads have reached the barrier; finally, they end with pthread mutex unlock [18].

Of the six benchmark applications, there are three categories of computation. Barnes and FMM (Fast Multipole Method)—both categorized as N-body problems—do similar calculations to evaluate the interaction of bodies like particles or galaxies over time. For both, data are arranged in a tree structure, but Barnes traverses the tree once per body, and FMM traverses the tree once per time step [24]. Ocean Contiguous and Ocean Non-Contiguous both simulate ocean movements (eddies, currents) by partitioning data into grids. In Ocean Contiguous the grid is represented with three-dimensional arrays so that data are partitioned contiguously; in Ocean Non-Contiguous the grid is represented by two-dimensional arrays, which do not allow representing data contiguously [1]. Like Barnes and FMM, Water-nSquared and Water-Spatial are N-body problems. They both simulate the forces on a system of water molecules over time, but Water-Spatial uses an O(n) algorithm while Water-nSquared uses an  $O(n^2)$  algorithm [24].

The benchmarks have been thoroughly tested and in use for many years, so we assumed that they were bug free; thus the only critical sections in the benchmarks are those explicitly marked by *pthread\_mutex\_lock* and *pthread\_mutex\_unlock* functions.

Because of the computational complexity of the Pintool, in order to perform the analysis we had to use the smallest possible input data size. Reducing the data size to train an algorithm is common. The end results can still be used on a larger data set. The Appendix contains the input data for each benchmark. One input

parameter for each benchmark is the number of threads the benchmark should use; this was set to four for all trials.

### How suitable is the tool for these benchmarks?

As mentioned in Chapter 3, the computations needed to infer objects and critical sections were too complex to run on all memory references. Therefore, we reduced the number of memory references used for both object and critical section inferences by ignoring all stack-relative and IP-relative references. For the object inference, we had to further reduce the set of memory references to only heap references. If a program's real critical sections do not lock heap memory accesses, then the tool will never catch them.

To determine how suitable the benchmarks were to analysis under these restrictions, we created a small memory profiling Pintool. It caught all calls to *malloc* to determine the boundaries of heap memory. The boundaries of real critical sections were defined by calls to *pthread\_mutex\_lock* and *pthread\_mutex\_unlock*; the tool also logged the first and last memory accesses inside the lock to determine if the calls locked user code or library code. Finally, the Pintool calculated the number of heap and non-heap references in critical sections excluding IP-relative and stack-relative references. All results were reported for dynamic critical sections.

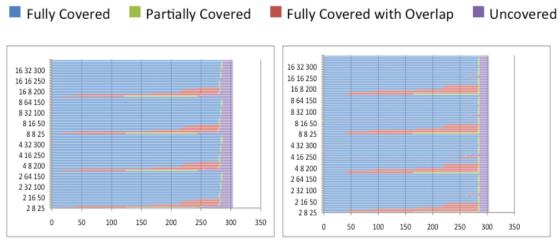

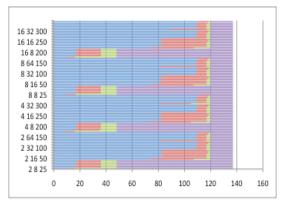

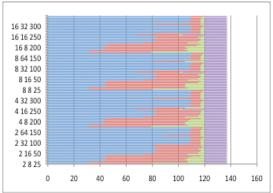

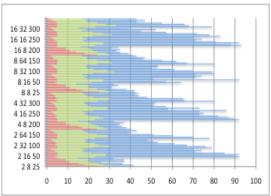

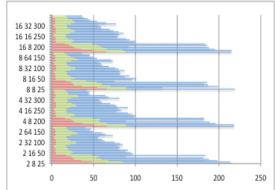

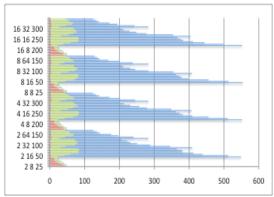

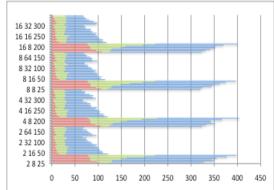

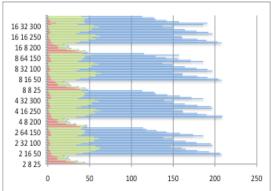

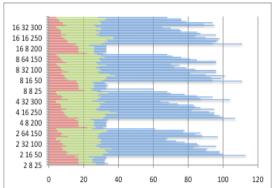

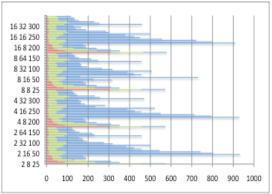

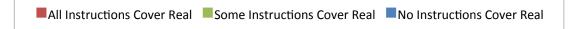

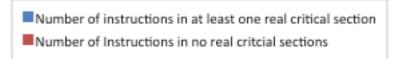

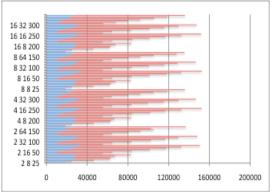

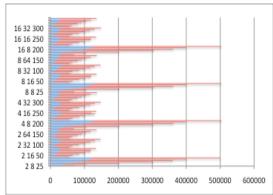

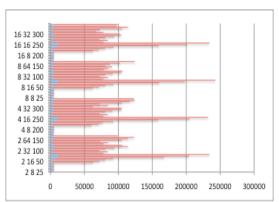

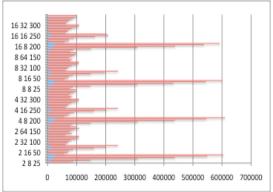

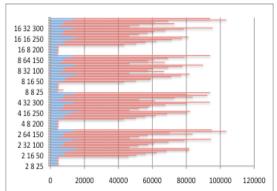

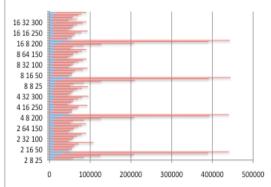

As Figure 6 shows, at least 80% of real critical sections in all benchmarks touch some element of heap memory. In fact, between 25% and 65% of real critical sections reference only heap memory.

36

Figure 6: Percentage of real critical sections that reference only heap memory, only non-heap memory, some of both, and no tracked memory references.

Of the critical sections that do not reference any heap memory, we were able to use the first and last memory accesses inside the lock to determine if user or library code was being locked. Table 1 shows that every benchmark had 17 dynamic critical sections in library code that referenced non-heap memory exclusively. For every benchmark, 16 of these were in the *ld-linux-x86-64.so.2* library's procedure \_*dl\_fini* and the last one was in a *libc.so.6*'s procedure \_*dl\_addr*. These library functions are used to initialize and end a program or thread. For four of the six benchmarks (Water-nSquared, Ocean Non-Contiguous, Ocean Contiguous, and Barnes), these library critical sections were the only ones that referenced only non-heap memory.

Table 1: Number of dynamic real critical sections that only referenced non-heap memory by code region.

|         | Barnes | FMM | Ocean<br>Contiguous | Ocean<br>Non-<br>Contiguous | Water<br>Spatial | Water-<br>nSquared |

|---------|--------|-----|---------------------|-----------------------------|------------------|--------------------|

| Library |        |     |                     |                             |                  |                    |

| code    | 17     | 17  | 17                  | 17                          | 17               | 17                 |

| User    |        |     |                     |                             |                  |                    |

| code    | 0      | 9   | 0                   | 0                           | 1                | 0                  |

Of the remaining two benchmarks, Water-Spatial had one large critical section from user code that referenced non-heap memory exclusively. It had 2919 references to non-heap memory and 0 to heap memory and is located in mdmain.C lines 172 to 177. When it is translated to use *pthread\_mutex\_lock* and *pthread\_mutex\_unlock* this segment of code is as follows:

#### Code Segment 1: Water-Spatial mdmain.c printing critical section.

This critical section grabs the input and output lock to prevent any other thread from printing results between its calls to *fprintf* and *fflush*. The value *six* is a globally declared *FILE* pointer set to *stdout* at the beginning of the program. The remaining variables that are printed during this critical section (TEN, POTA, POTR, POTRF, etc.) are stack variables. Since none of the variables referenced here are dynamically allocated, our Pintool cannot capture this critical section.

FMM has nine dynamic user code critical sections that do not reference heap memory; of these, there are three static critical sections. One static critical section is in a function called *LockedPrint*, which behaves like the critical section in Water-Spatial above; this function locks the input and output lock, flushes *stdout*, prints the input arguments to *stdout*, and flushes *stdout* again. It does not reference heap

memory, because the input arguments to the function are passed by value and not by reference.