ABSTRACT

Title of dissertation: VARIABILITY-AWARE VLSI DESIGN

AUTOMATION FOR

NANOSCALE TECHNOLOGIES

Vishal Khandelwal, Ph.D., 2007

Dissertation directed by: Professor Ankur Srivastava

large scale integrated systems.

Department of Electrical and

Computer Engineering

As technology scaling enters the nanometer regime, design of large scale ICs gets more challenging due to shrinking feature sizes and increasing design complexity. Aggressive scaling causes significant degradation in reliability, increased susceptibility to fabrication and environmental randomness and increased dynamic and leakage power dissipation. In this work, we investigate these scaling issues in

This dissertation proposes to develop variability-aware design methodologies by proposing design analysis, design-time optimization, post-silicon tunability and runtime-adaptivity based optimization techniques for handling variability. We discuss our research in the area of variability-aware analysis, specifically focusing on the problem of statistical timing analysis. The first technique presents the concept of error budgeting that achieves significant runtime speedups during statistical timing analysis. The second work presents a general framework for non-linear non-Gaussian statistical timing analysis considering correlations.

Further, we present our work on design-time optimization schemes that are applicable during physical synthesis. Firstly, we present a buffer insertion technique that considers wire-length uncertainty and proposes algorithms to perform probabilistic buffer insertion. Secondly, we present a stochastic optimization framework based on Monte-Carlo technique considering fabrication variability. This optimization framework can be applied to problems that can be modeled as linear programs without without imposing any assumptions on the nature of the variability.

Subsequently, we present our work on post-silicon tunability based design optimization. This work presents a design management framework that can be used to balance the effort spent on pre-silicon (through gate sizing) and post-silicon optimization (through tunable clock-tree buffers) while maximizing the yield gains. Lastly, we present our work on variability-aware runtime optimization techniques. We look at the problem of runtime supply voltage scaling for dynamic power optimization, and propose a framework to consider the impact of variability on the reliability of such designs. We propose a probabilistic design synthesis technique where reliability of the design is a primary optimization metric.

# VARIABILITY-AWARE VLSI DESIGN AUTOMATION FOR NANOSCALE TECHNOLOGIES

by

### Vishal Khandelwal

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2007

Advisory Committee:

Professor Ankur Srivastava, Chair/Advisor

Professor Joseph JaJa

Professor Samir Khuller

Professor Shuvra S. Bhattacharyya

Professor Kazuo Nakajima

Professor Gang Qu

© Copyright by Vishal Khandelwal 2007

# DEDICATION

This dissertation is dedicated to my parents for their love, support and encouragement.

### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my advisor, Prof. Ankur Srivastava for his guidance and help through my PhD. His advice and support has been crucial in the completion of this dissertation and other research projects that I have successfully completed at University of Maryland.

I also want to thank Professor Joseph JaJa, Professor Samir Khuller, Professor Shuvra Bhattacharyya, Professor Kazuo Nakajima and Professor Gang Qu for serving on the dissertation committee. Their advice and support in completing this dissertation is greatly appreciated.

I would also like to thank my uncle and aunt Dr. Basant and Rita Khandelwal for their constant support and encouragement in the years that I have been at Maryland.

I owe my gratitude to a lot of colleagues and friends with whom I have had very fruitful discussions about my research. Specifically, I want to thank my colleague Azadeh Davoodi and Ashish Dobhal for their help in several research projects. Lastly, I want to thank all my friends, specifically Amit Agrawal, Manish Shukla, Rahul Ratan, Ravi Tandon, Anuj Rawat, Abhishek Kashyap, Amrit Bandyopadhyay for various discussions and their unwavering support through my PhD.

### TABLE OF CONTENTS

| Lis | st of | Tables                                                            | vi |

|-----|-------|-------------------------------------------------------------------|----|

| Lis | st of | Figures                                                           | ii |

| 1   |       | noscale VLSI Design Automation                                    | 1  |

|     | 1.1   | Introduction                                                      |    |

|     |       | 1.1.1 Fabrication Variability: Sources and Issues                 |    |

|     |       | 1.1.2 Environmental Variability: Sources and Issues               |    |

|     | 1.0   | 1.1.3 Estimation/Modeling Variability: Sources and Issues         |    |

|     | 1.2   | New Design Methodology Paradigm                                   |    |

|     |       | 1.2.1 Predictable/Robust Designs                                  |    |

|     |       | 1.2.2 Parametric Yield Optimization                               |    |

|     | 1.3   | Current Approaches to Variability Driven Design                   |    |

|     |       | 1.3.1 Deterministic Techniques                                    |    |

|     |       | 1.3.2 Probabilistic Analysis/Optimization                         |    |

|     | 1.4   | Variability-Aware Design Methodology                              |    |

|     |       | 1.4.1 The Basic Idea                                              |    |

|     |       | 1.4.2 Key Advantages                                              |    |

|     |       | 1.4.3 Key Challenges                                              |    |

|     | 1.5   | Techniques for Handling Randomness due to Variability             |    |

|     |       | 1.5.1 Reduce the Sources of Variations                            |    |

|     |       | 1.5.2 Design-Time Optimization                                    |    |

|     |       | 1.5.3 Post-Silicon Design Tunability                              |    |

|     |       | 1.5.4 Runtime Adaptivity                                          |    |

|     | 1.6   | Organization                                                      | 24 |

| 2   | Var   | v                                                                 | 27 |

|     | 2.1   | Statistical Timing Analysis                                       | 28 |

|     | 2.2   | Current Approaches in STA                                         |    |

|     |       | 2.2.1 Modeling Arrival-Time and Gate Delays                       |    |

|     |       | 2.2.2 Block-Based STA Versus Path-Based STA                       |    |

|     | 2.3   | Key Challenges in STA and Our Research Contributions              | 35 |

|     | 2.4   | Efficient Statistical Timing Analysis Through Error Budgeting     | 39 |

|     |       | 2.4.1 Motivation and STA Framework                                | 40 |

|     |       | 2.4.2 Error Budgeting                                             | 45 |

|     |       | 2.4.3 Linear and Quadratic Approximation Schemes                  | 55 |

|     |       | 2.4.4 Experimental Results                                        | 60 |

|     | 2.5   | A General Framework for Accurate Statistical Timing Analysis Con- |    |

|     |       | sidering Correlations                                             | 65 |

|     |       | 2.5.1 Modeling Parameter Variations and Spatial Correlations      | 67 |

|     |       | 2.5.2 Statistical Timing Analysis Framework                       | 72 |

|     |       | 2.5.3 Reducing Complexity in Quadratic Regression                 | 82 |

|     |       | 2.5.4 Experimental Results                                        |    |

| 3 | Var | iability | y-Aware Design Optimization: Design Time Techniques                                                                                                                                                                                                                                                                                                                       | 99                                        |

|---|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|   | 3.1 | A Pro    | babilistic Approach to Buffer Insertion                                                                                                                                                                                                                                                                                                                                   | 103                                       |

|   |     | 3.1.1    | Motivation                                                                                                                                                                                                                                                                                                                                                                |                                           |

|   |     | 3.1.2    | Probabilistic Buffer Insertion: Metrics                                                                                                                                                                                                                                                                                                                                   | . 114                                     |

|   |     | 3.1.3    | Probabilistic Buffer Insertion: Algorithms                                                                                                                                                                                                                                                                                                                                | 116                                       |

|   |     | 3.1.4    | Experimental Results                                                                                                                                                                                                                                                                                                                                                      | 129                                       |

|   |     | 3.1.5    | Appendix                                                                                                                                                                                                                                                                                                                                                                  |                                           |

|   | 3.2 | Monte    | e-Carlo Driven Stochastic Optimization Framework for Han-                                                                                                                                                                                                                                                                                                                 |                                           |

|   |     |          | Fabrication Variability                                                                                                                                                                                                                                                                                                                                                   | . 148                                     |

|   |     | 3.2.1    | Binning Yield Loss                                                                                                                                                                                                                                                                                                                                                        |                                           |

|   |     | 3.2.2    | Motivational Example: Linear-Programming Based Optimiza-                                                                                                                                                                                                                                                                                                                  |                                           |

|   |     |          | tion                                                                                                                                                                                                                                                                                                                                                                      | . 154                                     |

|   |     | 3.2.3    | Stochastic Programming                                                                                                                                                                                                                                                                                                                                                    |                                           |

|   |     | 3.2.4    | SLP and Fabrication Variability                                                                                                                                                                                                                                                                                                                                           |                                           |

|   |     | 3.2.5    | Statistical Approximations: Successive Sample Mean Opti-                                                                                                                                                                                                                                                                                                                  |                                           |

|   |     |          | mization                                                                                                                                                                                                                                                                                                                                                                  | . 166                                     |

|   |     | 3.2.6    | The Cutting Plane Method                                                                                                                                                                                                                                                                                                                                                  |                                           |

|   |     | 3.2.7    | Stochastic Decomposition                                                                                                                                                                                                                                                                                                                                                  |                                           |

|   |     | 3.2.8    | SLP Applied to VLSI CAD                                                                                                                                                                                                                                                                                                                                                   |                                           |

|   |     | 3.2.9    | Experimental Results and Comparisons                                                                                                                                                                                                                                                                                                                                      |                                           |

| 4 | 4.1 | Varial   | y-Aware Design Optimization: Post-Silicon Tunability bility-Driven Formulation for Simultaneous Gate Sizing and Post- Tunability Allocation Introduction Background and Definitions Simultaneous Gate Sizing and PST Buffer Range Determina- tion for Minimizing BYL and TC Shortest Path Delay Constraints Solving the Two-Stage Stochastic Program Experimental Results | . 197<br>. 200<br>. 208<br>. 219<br>. 222 |

| 5 | Var | iability | y-Aware Design Optimization: Runtime Techniques                                                                                                                                                                                                                                                                                                                           | 234                                       |

|   | 5.1 | -        | taneous Resource Binding and Dual-Vdd Allocation for Power                                                                                                                                                                                                                                                                                                                |                                           |

|   |     |          | nization with Probabilistic Reliability Guarantee                                                                                                                                                                                                                                                                                                                         | 235                                       |

|   |     | 5.1.1    | Fabrication and Environmental Variability: Impact and Mod-                                                                                                                                                                                                                                                                                                                |                                           |

|   |     |          | eling                                                                                                                                                                                                                                                                                                                                                                     | 238                                       |

|   |     | 5.1.2    | Reliability Guarantee: Definition and Understanding                                                                                                                                                                                                                                                                                                                       |                                           |

|   |     | 5.1.3    | Simultaneous Resource Binding and Dual-Vdd Allocation With                                                                                                                                                                                                                                                                                                                |                                           |

|   |     |          | Reliability Guarantees                                                                                                                                                                                                                                                                                                                                                    | 246                                       |

|   |     | 5.1.4    | Architectural Issues                                                                                                                                                                                                                                                                                                                                                      |                                           |

|   |     | 5.1.5    | Determination of the Optimal $Vdd_l$                                                                                                                                                                                                                                                                                                                                      |                                           |

|   |     | 5.1.6    | Rescheduling the DFG through local perturbation                                                                                                                                                                                                                                                                                                                           |                                           |

|   |     | 5.1.7    | Consideration of Leakage Power and Soft Errors                                                                                                                                                                                                                                                                                                                            |                                           |

|   |     | 5.1.8    | Experimental Results                                                                                                                                                                                                                                                                                                                                                      |                                           |

| 6   | Con    | clusion | and Future Work                                            | 266 |

|-----|--------|---------|------------------------------------------------------------|-----|

|     | 6.1    | Future  | Work                                                       | 268 |

|     |        | 6.1.1   | Microscopic View: Single Integrated/Embedded System        | 269 |

|     |        | 6.1.2   | Macroscopic View: Distributed Integrated and Embedded Sys- |     |

|     |        |         | tems                                                       | 271 |

| Bib | liogra | aphy    |                                                            | 273 |

## LIST OF TABLES

| 1.1 | Technology Parameters                                                                      |

|-----|--------------------------------------------------------------------------------------------|

| 1.2 | Percentage Delay Variability Imposed by Within-Die Variations 7                            |

| 2.1 | Runtime and Error Comparison                                                               |

| 2.2 | Runtime Comparison wrt Monte Carlo (Global Parameters have a Uniform Distribution)         |

| 2.3 | RMS Error Comparison wrt Monte Carlo CDFs (Global Parameters have a Uniform Distribution)  |

| 2.4 | Runtime Comparison wrt Monte Carlo (Global Parameters have a Gaussian Distribution)        |

| 2.5 | RMS Error Comparison wrt Monte Carlo CDFs (Global Parameters have a Gaussian Distribution) |

| 3.1 | Results from Experiments                                                                   |

| 3.2 | Runtime Comparison Between the Three Criteria                                              |

| 3.3 | Result for 2 Terminal Nets                                                                 |

| 3.4 | Post Routing Delay Results: Deterministic vs Probabilistic 137                             |

| 3.5 | Result: Delay Constraint Violation and Average Leakage Current 186                         |

| 3.6 | Result: Runtime in cpu cycles                                                              |

| 4.1 | Comparison of Binning Yield-Loss, Area and Total PST Buffer Range in (psec)                |

| 4.2 | Comparison of Yield-Loss                                                                   |

| 4.3 | Comparison of Total Run-Time (min) and Number of Iterations 232                            |

| 4.4 | Contribution of Monte-Carlo Based STA time to Iteration Time (sec) 233                     |

| 5.1 | Power and Reliability Results Obtained From [30]                                           |

| 5.2 | Experimental Results: Power, Optimal $Vdd_l$ and Reliability 261                           |

## LIST OF FIGURES

| 1.1  | Typical VLSI Design Flow                                             | 2  |

|------|----------------------------------------------------------------------|----|

| 1.2  | Technology Parameter Variations                                      | 8  |

| 1.3  | Predictable/Robust Solution                                          | 12 |

| 1.4  | High Parametric Yield Solution                                       | 13 |

| 1.5  | Probabilistic Optimization Framework                                 | 19 |

| 2.1  | Statistical timer: block diagram & sample slack distribution $\dots$ | 28 |

| 2.2  | Static versus Statistical Timing Analysis                            | 30 |

| 2.3  | Gate with x and y input pins and output o                            | 31 |

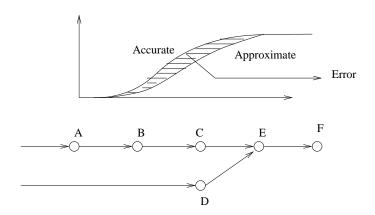

| 2.4  | Distributions and their Linear Approximations                        | 41 |

| 2.5  | Gate with x and y input pins and output o                            | 42 |

| 2.6  | Error Budgeting                                                      | 43 |

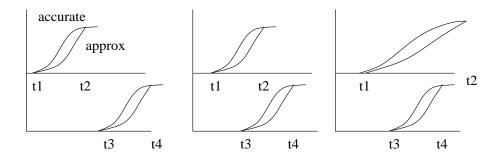

| 2.7  | Error in SUM                                                         | 46 |

| 2.8  | Error in MAX                                                         | 48 |

| 2.9  | Error Bound in MAX                                                   | 50 |

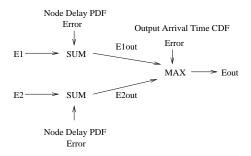

| 2.10 | Error Injection in a Gate                                            | 53 |

| 2.11 | Decomposing CDF and PDF into sum of ramps                            | 56 |

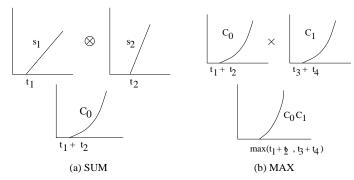

| 2.12 | SUM and MAX                                                          | 57 |

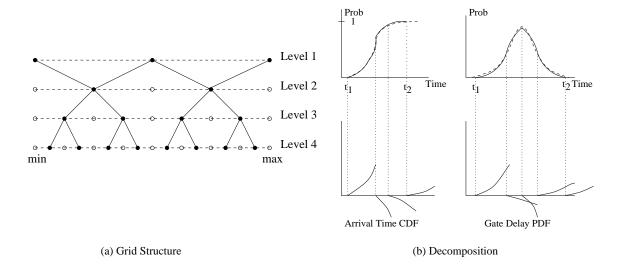

| 2.13 | Grid Structure and Quadratic Decomposition                           | 59 |

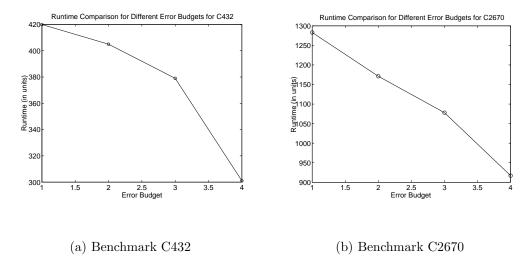

| 2.14 | Runtime Results                                                      | 61 |

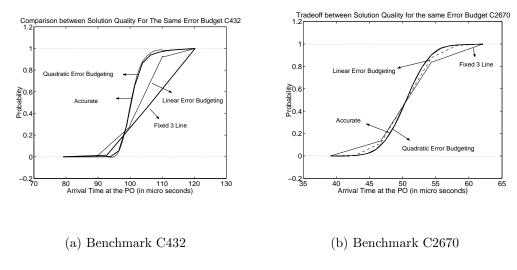

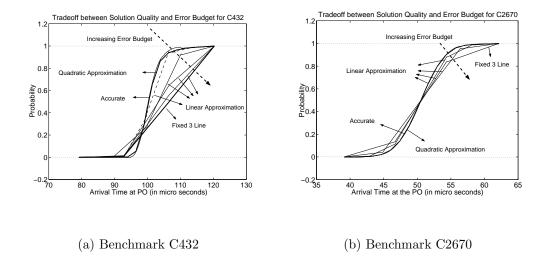

| 2.15 | STA Results                                                          | 62 |

| 2.16 | Error Budgeting Tradeoff                                             | 63 |

| 2.17 | Grid-Based Spatial Correlation Model                                 | 69 |

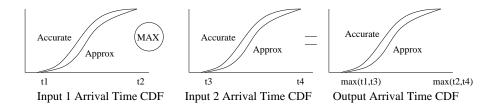

| 2.18 | SUM and MAX Computation                                              | 73 |

| 2.19 | STA technique at Gate G                                                                   |

|------|-------------------------------------------------------------------------------------------|

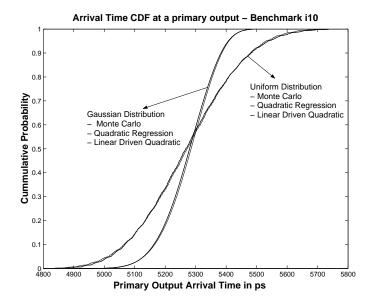

| 2.20 | CDF Result for i10 at a primary output                                                    |

| 2.21 | CDF Result for i10 at a primary output                                                    |

| 3.1  | RC Tree Network                                                                           |

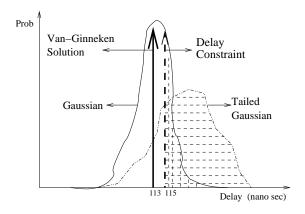

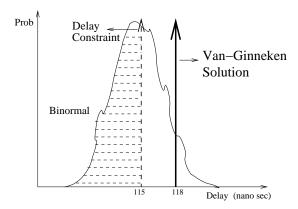

| 3.2  | Mean Value vs. Actual Delay Distribution                                                  |

| 3.3  | Worst Case Length Estimate                                                                |

| 3.4  | Spread in Distribution                                                                    |

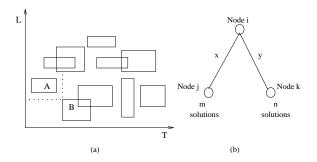

| 3.5  | Distribution of Potential Solutions at a node                                             |

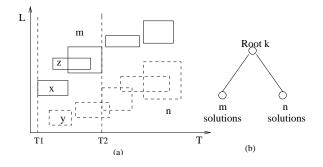

| 3.6  | Generate Solutions at a Node from its Fanout Nodes                                        |

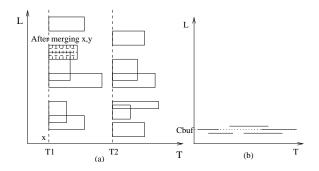

| 3.7  | Total $m \cdot n$ Solutions After Merging                                                 |

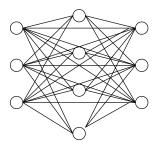

| 3.8  | Complete R-Partite Max Cost Clique                                                        |

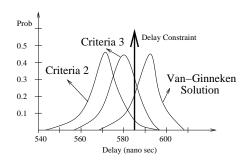

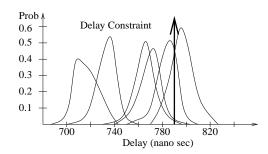

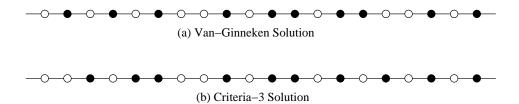

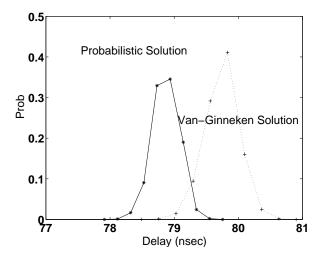

| 3.9  | Comparison of Solutions for a Benchmark                                                   |

| 3.10 | Delay Distribution of Solutions Satisfying a Delay Constraint 130                         |

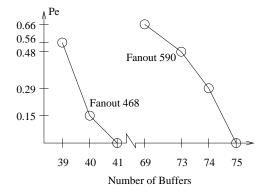

| 3.11 | Trade-off Between Number of Buffers and Probability of Error 130                          |

| 3.12 | Buffered Solution for a 2 Terminal Net with 20 Potential Locations . 133                  |

| 3.13 | Delay Distribution of Buffered Solutions for a 2 Terminal Net with 20 Potential Locations |

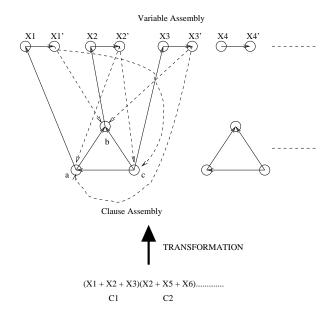

| 3.14 | Transforming UNIPHASE-ONE-IN-3SAT to Directed-Cover 139                                   |

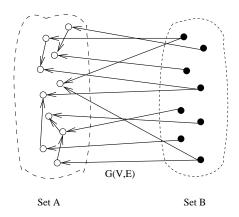

| 3.15 | Transforming Directed-Cover to Directed Maximal Independent Set . 142                     |

| 3.16 | Transforming 3SAT to Complete R-Partite Max Cost Clique 145                               |

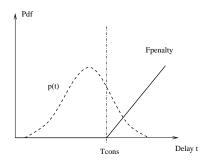

| 3.17 | Binning Yield Loss with a Linear Penalty Function                                         |

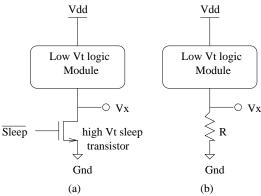

| 3.18 | Sleep Transistor in MTCMOS Circuits                                                       |

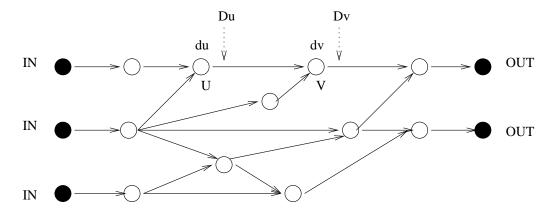

| 3.19 | DAG representation                                                                        |

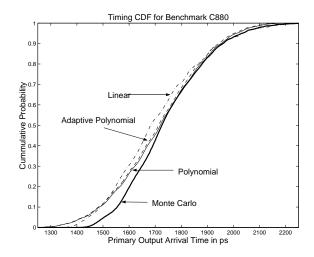

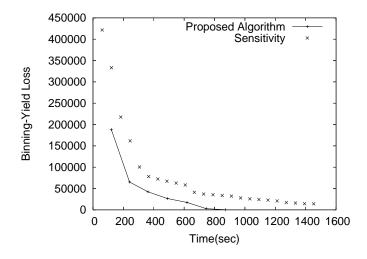

| 3.20 | Timing Result for C880                                                                    |

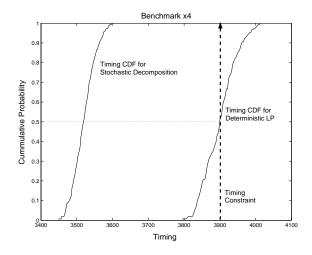

| 3.21 | Timing Result for x4                                                                      |

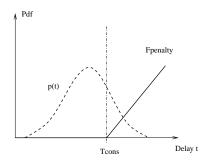

| 4.1 | Binning Yield Loss with a Convex Penalty Function                                                                                       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

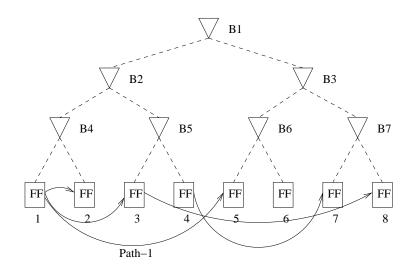

| 4.2 | Sequential Design with a PST Clock Tree [72]                                                                                            |

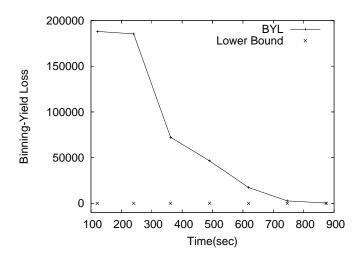

| 4.3 | Convergence of BYL to its lower bound with time for s344 230                                                                            |

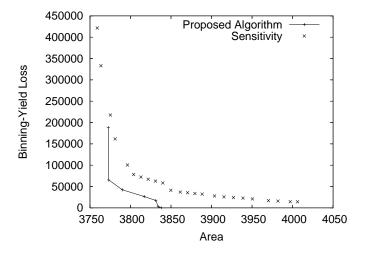

| 4.4 | BYL vs. Area Generated at Different Iterations of Kelley's and Sensitivity-Based Algorithms                                             |

| 4.5 | BYL vs. Time Generated at Different Iterations of Kelley's and Sensitivity-Based Algorithm                                              |

| 5.1 | Reliability in a Scheduled and Bound DFG                                                                                                |

| 5.2 | Example: Computing $P_f^{ij}$                                                                                                           |

| 5.3 | Example: Computing $D_{crit}^{ij}$                                                                                                      |

| 5.4 | Example: (a) DFG (b) Extended Operations (c) Comparability Graph for DFG in a (d) Comparability Graph for DFG in b (e) Network Graph246 |

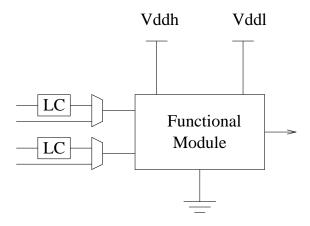

| 5.5 | Architectural Considerations for Dual-Vdd Scheme                                                                                        |

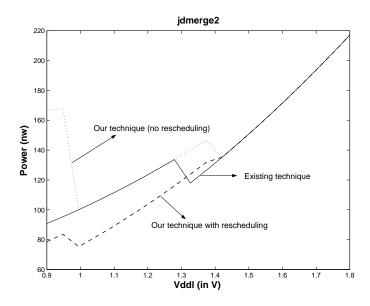

| 5.6 | Power Versus $Vdd_l$ Trade-Off For $jdmerge2 \dots 264$                                                                                 |

#### Chapter 1

#### Nanoscale VLSI Design Automation

#### 1.1 Introduction

The technological advances in the last decade have enabled the emergence of the deep sub-micron (sub 250nm) and nanometer (sub 90nm) eras in VLSI Design. High performance and low cost ICs are a direct result of this growth. In 1965, Gordan Moore predicted that the number of transistors per IC would double every two years. In the last three decades, we have more than kept up with the famous *Moore's Law*. Intel, one of the key players in the IC/Microprocessor design field has scaled the number of transistors on an IC with each generation of its product keeping in pace with Moore's prediction. The Intel-286 series developed in 1982 had about a 130,000 transistors, which scaled to about 7,000,000 transistors in 1997 for the Intel Pentium II series, then scaled to about 300,000,000 transistors in 2003 for the Intel Itanium 2 Processor and is projected to hit the 1 billion transistor mark for its ongoing 64 bit microprocessor designs in the coming years.

This brings to light the increasing complexity in designing such ICs, that are faster, smaller and more powerful that their previous generations. The existing CAD tools need to adapt themselves to these new rising challenges posed in design automation. Design of high performance digital ICs has become an extremely challenging task. Shrinking device dimensions, increasing manufacturing and envi-

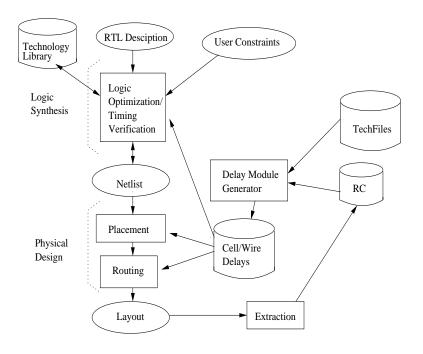

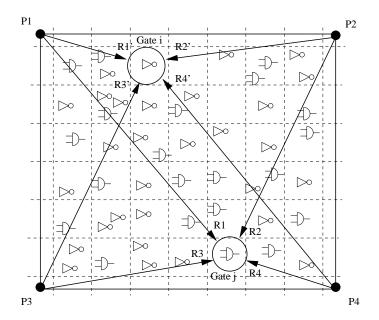

Figure 1.1: Typical VLSI Design Flow

ronmental variations has made fast design closure and high yield difficult.

The traditional design automation (DA) flow is rapidly having to adapt itself to these changes in Deep Sub-Micron (DSM) VLSI design. A typical VLSI design flow can be stated as in figure 1.1. As shown in the figure, the design specifications are defined using a hardware description language like VHDL or Verilog. This can be a behavioral level or a block level description of the design. Each design is associated with a technology library containing pre-characterized standard-cells that will be used for the design. The library contains standard information about cells like the timing, area and power specifications. Logic synthesis performs optimization on the high-level design specifications to generate a netlist for the design. Some of the optimization steps involved here are logic minimization, scheduling, binding, structuring, technology mapping, gate sizing, buffer insertion etc. [100]. We perform

timing verification at each step of optimization to ensure that the design meets the required timing constraints. The optimized netlist then undergoes physical synthesis that comprises of floor-planning, placement and routing (global and detailed) [81]. There are several detailed optimizations that are involved in each stage of the VLSI design flow. Essentially, physical design takes a netlist and generates a lower-level representation of it on silicon that is ready to be sent for fabrication. The technology information ensures that the physical design is compatible with the fabrication process. The location of the pins/pads, clock and power supply distribution etc. are characterized according to the technology specifications.

The new challenges in DSM technology has changed this rather sequential looking VLSI design flow into a more unified design flow. Logic and physical synthesis are no longer two sequential steps. Logic synthesis required estimation of design parameters that are available only after physical design. Hence, the design flow needs to have an interaction between logic synthesis and physical design to enable faster design closure. As seen in the figure, we can see that circuit parameters are extracted after physical synthesis and are then processed during the next iteration of logic synthesis. The current design methodologies are making this iterative flow more unified so as to achieve faster design closure. The quick turn-around time demanded by this market does not allow the designer to keep iterating on his design to meet specifications. In presence of fabrication and environmental variability, efficient design closure becomes an even bigger challenge. There is a need for more accurate models and estimation techniques to bridge the gap between logic and physical synthesis. An even bigger challenge is to consider the fabrication and

environmental variations into the VLSI design flow to enable quicker design closure and a higher fabrication yield.

The traditional optimization and analysis techniques often lead to sub-optimal or invalid (violates design constraints) solutions in the presence of fabrication variabilities. These variabilities make it extremely difficult to accurately estimate parameters even at lower levels of design flow. This fabrication and environmental variabilities cause the performance of the chip to deviate from the specifications leading to a dramatic reduction in the yield after fabrication. Also, it is not possible to consider these variations in the traditional design flow (which would perform several iterations of the design flow to generate a valid solution) due to design time constraints. The time to market window has shrunk significantly and these business aspects are also creeping into the way ICs need to be designed.

As a result of shrinking dimensions, secondary effects are becoming significant. For instance, until recently it was acceptable to perform timing analysis by considering only gate delays and ignoring wire delays. But in the deep sub-micron technology wire-delays are becoming more critical as compared to gate/device delays. It has been predicted [113] that for deep sub-micron technologies, almost 80% of the delay in critical paths will be the interconnect delays. The entire timing optimization/analysis paradigm has shifted to consider interconnect delays in the current technology.

In this work, we have tried to address the variability problem in DSM/Nanoscale VLSI design automation. We will introduce the problem of variability and discuss its sources. We will also discuss how design automation is adapting to these po-

tential problems by adopting a variability-aware design analysis and optimization methodology. We will look at some techniques for design analysis and optimization that explicitly consider the impact of variability on design performance.

We can categorize the sources of variability in DSM VLSI design [111] into three broad categories:

- 1. Fabrication/Manufacturing Variability

- 2. Environmental Variability

- 3. Estimation/Modeling Variability

#### 1.1.1 Fabrication Variability: Sources and Issues

The current DSM technologies have extremely high costs and therefore require a rapid turn-around time to generate revenue to meet the financial constraints. There is tremendous pressure on the designers to create more complex and more powerful designs under small time-to-market windows. *Performance* and *yield* are both limited by the existence of fabrication variability effects in DSM designs. Fabrication process induced parameter variations cause performance fluctuations and have become important considerations in DSM ICs. Until now it was sufficient to consider die-die variations which were handled typically using a worst-case design methodology. In DSM there are significant within-die variations in terms of device and interconnect parameters [111]. Furthermore, these within-die variations are dependent not only on the fabrication process but also on the implementation

(physical design) of the IC. Hence, these sources of variability are caused by both the design-flow as well as the fabrication process.

The fabrication variability can be divided into two categories:

- 1. Die-Die variations: These are variations which are imposed on the design by the fabrication process. Within the same die, there is no variability in parameters. Such cases can be analyzed using the classic Monte-Carlo or worst-case techniques. The fabrication process can characterize the variability as a distribution for such an analysis. Though the increasing number of sources contributing to die-die variations is making it increasingly hard to accurately counter the impact of these variations on design analysis and performance.

- 2. Within-Die variations: These variations are both fabrication as well as design dependent. Firstly, there can be a large number of parameters which are varying making it harder to perform any form of analysis. The variations can be both spatially correlated or independent (random variations). We do not have accurate modeling as well as analysis techniques to handle these withindie variations. There variations can be in device parameters (like  $V_{th}$ , W,  $T_{ox}$  etc.) or in interconnect parameters (like sheet resistance  $R_s$ ,  $L_{max}$  etc.)

Some trends in device and interconnect parameter trends have been given in the SIA technology roadmap [113]. Typical parameter values for each generation of technology node (between 250nm to 70nm) are given in table 3.5. In [111], the corresponding delay variability imposed by these technology parameter (within-die) variations are given in table 3.6. It is interesting to note that both device and

| Parameter               | 1997 | 1999 | 2002 | 2005 | 2006 |

|-------------------------|------|------|------|------|------|

| $L_{eff}$ (nm)          | 250  | 180  | 130  | 100  | 70   |

| $T_{ox}$ (nm)           | 5    | 4.5  | 4    | 3.5  | 3    |

| $V_{dd}$ (V)            | 2.5  | 1.8  | 1.5  | 1.2  | 0.9  |

| $V_T$ (V)               | 0.5  | 0.45 | 0.4  | 0.35 | 0.3  |

| $W(\mu)$                | 0.8  | 0.65 | 0.5  | 0.4  | 0.3  |

| $H(\mu)$                | 1.2  | 1.0  | 0.9  | 0.8  | 0.7  |

| $\rho \ (m\Omega/\Box)$ | 45   | 50   | 55   | 60   | 75   |

Table 1.1: Technology Parameters

| Parameter | 1997         | 1999 | 2002 | 2005 | 2006 |

|-----------|--------------|------|------|------|------|

| $V_{dd}$  | 9.5          | 10.8 | 10.0 | 1.2  | 0.9  |

|           | Device       |      |      |      |      |

| $L_{eff}$ | 32.4         | 28.3 | 25.5 | 24.6 | 23.8 |

| $T_{ox}$  | 1.3          | 2.5  | 3.2  | 3.9  | 4.9  |

| $V_T$     | 3.8          | 5.3  | 5.5  | 6.5  | 7.2  |

|           | Interconnect |      |      |      |      |

| W         | 13.3         | 12.0 | 11.7 | 11.4 | 10.5 |

| H         | 7.8          | 8.0  | 8.1  | 8.3  | 7.1  |

| ρ         | 16.0         | 16.6 | 17.9 | 18.4 | 20.1 |

Table 1.2: Percentage Delay Variability Imposed by Within-Die Variations

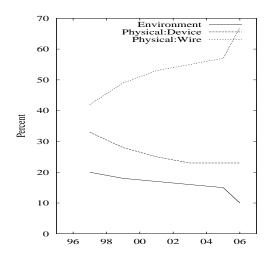

Figure 1.2: Technology Parameter Variations

interconnect variability are causing significant variations in delay.

The authors in [112] performed experiments on the above device parameters to study the variations induced by fabrication variability on the design. In figure 1.2, they present the technology parameter variation trends across five generations of technology node. We note that though the device variations  $(T_{ox}, V_T)$  somewhat stabilize with newer technology nodes, the interconnect variations keep increasing. This clearly highlights the importance of considering interconnect variations as well as device variations in any form of VLSI design optimization. The current deterministic models for estimating variability are not able to predict these variabilities with reasonable accuracy. In [25], the authors point out that:

- Technology scaling is continuously reducing physical dimensions and the effect

of variabilities is such geometries is making the current estimating models very

inaccurate.

- It was assumed earlier that the variations in devices was strongly correlated

thereby reducing the number of sources of variability. However, DSM technologies show large number of sources of variabilities which are correlated as well as independent. This increasing number of independent sources of variability is making analysis very difficult.

#### 1.1.2 Environmental Variability: Sources and Issues

There is variability in design due to various environmental uncertainties. These include variations in power supply voltage  $V_{dd}$ , coupling noise, temperature variations, soft errors, electro-migration issues etc. These variations have been characterized as probability distributions and have been analyzed at the intra-die level using worst-case or Monte-Carlo techniques. But as we enter the nanoscale regime, these variations are starting to pose a bigger challenge and cannot be handled through the traditional techniques. As the number of source of these variations increase, using deterministic techniques to estimate such variations is becoming increasingly pessimistic leading to large overheads in performance while trying to counter of these variations. There is a growing need to consider environmental variations probabilistically/statistically during the design flow similar to fabrication variability.

### 1.1.3 Estimation/Modeling Variability: Sources and Issues

The estimation variability comes into design flow primarily due to design abstraction and the lack of accurate estimation techniques. Early in the design flow, the specifications are only at a very high level of abstraction and therefore interaction with lower-level (physical design) can only be estimated [112]. It is very hard to make accurate predictions at such a high-level without knowing any information for the physical design since there is a certain amount of design uncertainty that is not concretely specified.

Additionally, we need to have accurate models that can be used to predict design parameters with reasonable accuracy. Often such accurate models either do not exist or are computationally expensive to be used in the design flow. Both logic synthesis and physical design suffer from insufficient parameter estimations. This has led to an increasing requirement for logic synthesis and physical design to be more unified so that information can be efficiently exchanged between the two steps. As shown in figure 1.1, the design parameters (like capacitance, parasitics etc.) is extracted after physical design (layout) and fed back to the logic synthesis stage to provide a more accurate estimation of wire delays and capacitances in the next iterations of design cycle. But this can still lead to potentially many iterations of the design cycle which is not acceptable due to tight design-time windows. In [35] the authors have shown that in DSM micron designs, the current interconnect delay models are not accurate when interconnect delay forms a large part of the critical path delay (which is true for DSM designs). Furthermore, they show that the iterative feedback in design flow to better estimate design parameters may not sufficient to allow for incremental optimization capabilities. This form of estimation variability can be countered by using better modeling techniques. There is a need to shift from the traditional deterministic models and adopt a probabilistic modeling framework for better estimation/prediction of device parameters.

These sources of variations have a big impact on design performance. Critical issues like timing and power inaccurately estimated leading to very poor design solutions.

#### 1.2 New Design Methodology Paradigm

In the presence of variability, we need to redefine our design objectives. Correspondingly, we need to focus on different design methodology paradigms. We want to create designs that are robust and predictable. Robustness adds an inherent immunity towards the existing variabilities in the systems as is a desirable characteristic in any design. Additionally, we could also focus towards getting a higher parametric yield from our design methodology. Let us now understand how these two different paradigms come into the picture in DSM designs in presence of variability.

# 1.2.1 Predictable/Robust Designs

Robustness is an extremely desirable property from any design because it inherently implies stability towards variations. Predictability in design automation has been defined as a quantified form of accuracy/certainty [14]. Each step of VLSI design flow requires estimates to drive the optimization. If these estimates are more accurate, we end up with a more predictable design after optimization. The idea is to get an accurate estimate of the cost function being optimized, so that the final design is more robust. The goal of a predictability-driven objective function is to

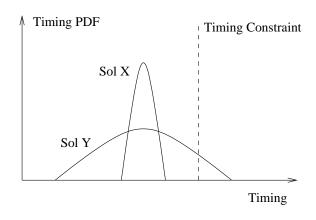

Figure 1.3: Predictable/Robust Solution

choose the most accurate solution.

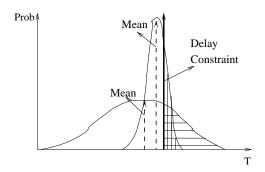

A predictable estimate of an objective function does not vary much in presence of uncertainty and provides robustness in design. [18] defines a design to be robust if its performance is not influenced by factors like coupling noise, temperature or other variations. This essentially means that the design is more tolerant towards perturbations while still performing within acceptable limits. The authors point out that in order to achieve such a design methodology, the effects and interactions of these factors with design performance need to be investigated. The modeling of the optimization problem should identify and include these variations within the design framework. However, a robust/predictable solution hence obtained may not be the optimal solution and is also not guaranteed to meet the design constraints. As shown in figure 1.3, let us suppose that we generate two solutions X and Y. We can impose the variability on both these solutions and generate their timing PDFs. As shown in the figure, we can see that solution X is more predictable/robust as compared to solution Y because it has lesser uncertainty in value.

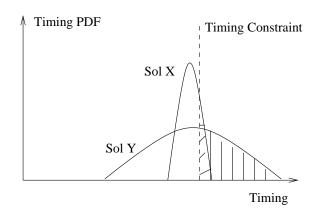

Figure 1.4: High Parametric Yield Solution

#### 1.2.2 Parametric Yield Optimization

Yield from fabrication of ICs is a very important aspect of large scale production. This directly determines the cost of production and hence, we need to ensure that a high yield is achieved. Typically, the yield is calculated by binning the ICs according to their design performance (operating frequency, total power consumption etc.). ICs that do not meet the requirements are rejected. There can be catastrophic defects that lead to ICs that do not work at all. Defects caused due to dirt particles or photo defects are categorized under catastrophic (or non-recoverable) defects. Parametric yield is basically caused by fabrication variations and other disturbances in the environment. Essentially this results in sub-optimal performance of the ICs in terms of timing and can also be referred to as timing yield.

Improvement of timing yield in presence of process variations has caught a lot of attention lately [106, 89, 51, 11]. The objective in parametric yield maximization is to obtain a solution that is likely to meet the constraints with the highest prob-

ability after fabrication. As shown in figure 1.4, let us suppose that we generate two solutions X and Y. We can impose the variability on both these solutions and generate their timing PDFs. As shown in the figure, we can see that solution X is a better solution from a parametric yield perspective as compared to solution Y because it has a higher probability of meeting the timing constraints.

#### 1.3 Current Approaches to Variability Driven Design

There are a few existing design paradigms that try to capture variability during design automation. The goal is to obtain fast design closure satisfying all constraints while ensuring that the IC meets the performance requirements after fabrication. There are both deterministic and probabilistic approaches in this context.

### 1.3.1 Deterministic Techniques

These techniques perform optimization based on a fixed (deterministic) estimate of the parameters. As soon as variability is introduced into the framework, it is hard for such technique to accurately capture the nature of the variability. There are worst-case approaches, sensitivity-based approaches and slack management based deterministic approaches that try to capture variability in a deterministic perspective.

### Worst-case Analysis/Monte-Carlo

This is the traditional form of analysis. However, in presence of fabrication variations this approach tends to be very pessimistic. This is a corner-based approach that tries to identify the design corners in the solution space to ensure that the performance of the design is acceptable within the extreme boundaries. In a variability perspective, firstly there are a lot more design corners making this approach very inefficient. Additionally, there are design corners that exist with a virtually zero probability for all practical purposed and this approach tries to optimize the design around such points as well. As a result, the final design is very sub-optimal. Since all variations are not perfectly correlated, the worst-case scenario does not imply a worst-case occurrence of all parameters [78]. There are local independent random variations that also need to be considered. It is very pessimistic to assume that the worst-case occurs when absolutely every parameter is at its worst-case value.

Another possible approach is to generate upper and lower bounds on the solution. It is generally a hard task to obtain tight bounds on the potential solution. In [2], the authors proposed statistical bounds in a timing analysis framework. Intra-die variations have been analyzed deterministically using Monte-Carlo based simulations with reasonable efficiency. Certain within-die interconnect variations have also been modeled using worst-case deterministic approaches [120].

#### Sensitivity-Based Analysis

Sensitivity based optimization/analysis is generally performed to get a more robust design. The idea is to try to get a design that is less sensitive to variations in parameters. It is in general hard to identify the relevant sources of variability at each step in the optimization, so as to optimize the objective function to be less sensitive to these parameters. We note that the goal here is not to obtain an optimal performance from the design, but to obtain a robust performance from the design. In [110], the authors have shown that a stable/robust solution is not necessarily close to being an optimal one. Although this technique is very well suited towards a predictable/robust design methodology paradigm.

### Constraint Relaxation Techniques / Slack Management

These techniques rely on inducing flexibility in the design constraints by relaxing some of them during the design flow. At higher-levels of design flow, this flexibility allows the later optimization steps to handle variability and other issues better. In [16], the authors introduce the concept of delay relaxation parameter as a property to reach design closure. The paper talks about scheduling in high-level synthesis. The timing constraints of functional resources are relaxed without violating the data-flow constraints. Future optimizations in logic and physical synthesis tend to benefit from this extra flexibility and increased the chances of design closure in presence of variability.

Slack in different paths of a circuit can be efficiently distributed to gain maxi-

mum benefits from optimization. In [24], the authors perform gate sizing to consider delay uncertainty. In [124], the authors have tried to implement the slack management paradigm in the probabilistic framework.

#### 1.3.2 Probabilistic Analysis/Optimization

Probabilistic techniques have gained a lot of attention recently. Variability in DSM technologies have let to the failure of existing deterministic optimization paradigms that are not able to effectively capture the variations. A lot of work has been done in the area of timing analysis under variability from a probabilistic perspective [42, 105, 79, 2, 39, 10, 118, 27, 119, 1, 96, 43].

Probabilistic technique represent each parameter variation as a distribution and tries to maximize the distribution of the objective function during optimization. Accurate models representing parameter dependencies are required for such an approach. In [9] and [68], the authors try to model wire-length variability as a distribution in the post-placement pre-routing stage of VLSI design.

From a robustness perspective we try to find a solution that has minimum variance in its distribution in presence of variability. From a parametric yield perspective, we try to find a solution that has the least chances of violating the design constraints. Essentially, the designer is taking a probabilistic risk of not satisfying the constraints (in presence of variability). Voltage scheduling through such a risk-management paradigm for higher parametric yields has been proposed in [6]. In [115], the authors present a technique to perform buffer insertion to maximize the

parametric yield under wire-length variability.

#### 1.4 Variability-Aware Design Methodology

#### 1.4.1 The Basic Idea

As mentioned in the previous sections, variability-aware approaches can be both deterministic as well as probabilistic. There is an inherent limitation in the deterministic approach to capture the variations effectively. Recently, there has been a shift in focus towards probabilistic design methodologies that are better able to capture fabrication variabilities. It is very hard to model the design parameters as fixed quantities. The variability in their values makes it easier for us to capture their nature by modeling them as random variables. This allows us to generate a distribution (PDF/CDF) for each parameter (modeled as a random variable). The objective function can also be represented as a distribution. From a robustness/predictability perspective, we are looking to minimize the variance in the final solution but from a timing yield perspective, we are trying to maximize the chances of meeting the design constraints.

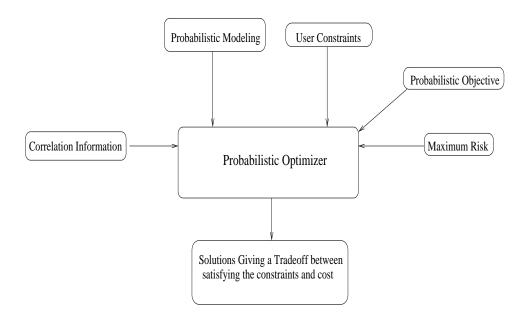

A probabilistic optimization framework could be represented as shown in figure 1.5. The central block of the framework is a probabilistic optimizer that takes in the design constraints (user constraints), the probabilistic optimization objective and the probabilistic risk that the designer is willing to take of violating the design constraints. Additionally, we require accurate models to capture the variability to represent it as distributions and accurate ways to capture the correlation informa-

Figure 1.5: Probabilistic Optimization Framework

tion between these distributions. The final solutions from the optimizer are those that satisfy the constraints within the user defined risk limits. The one which has minimum cost (from a robustness or parametric yield perspective) is chosen as the final solution.

# 1.4.2 Key Advantages

There are several advantages of using such a probabilistic optimization framework in presence of variability.

• Handling fabrication variability in design flow: Since we can probabilistically model all design parameters, we can capture the variability in the design effectively. Each parameter variation can be estimated as a distribution and given to the probabilistic optimizer. This statistical information is assumed to be given to the optimizer.

- Faster design closure: Since we can consider variability issues concurrently while performing design optimization, we are able to reach a design satisfying all constraint faster. We do not need to iteratively try to refine the design to cover all process-corners in the solutions space.

- Risk management: The probabilistic framework allows the designer to decide the amount of risk he is willing to take in his design. A higher acceptable risk typically results in solutions with lower costs as a trade-off. The quality of solution versus the cost of the solution is presented an an interesting trade-off to the designer.

#### 1.4.3 Key Challenges

Though there are several advantages in using a probabilistic optimization framework, there are several key challenges to developing such a methodology:

- Probabilistic modeling: It is important to be able to generate accurate probabilistic models of all design parameters. This requires the processing of statistical data on the parameter combined with its deterministic information. In general this poses a tough challenge to the designers. Also, the cost of evaluating/using such a model should not be very high (computational complexity) in order for it to be a practical solution.

- Correlation Modeling: It has been shown that correlations are very significant in parameter variations. From a timing perspective, most global variations induced due to fabrication variability are spatially correlated. We need to

be able to accurately capture these correlations during optimization. Additionally, not all source of variations are correlated, so we must also have the flexibility to capture independent correlations. Since all gates on a chip are manufactured through the same process, there are global correlations between them. Additionally, there can be variations in characteristic based on their spatial locations, i.e. gates that are placed in close physical proximity are more likely to see similar variations. It is hard to model these correlations such that they can be computed accurately and efficiently.

• Run-time complexity: Probabilistic optimization technique is general require

a lot more computation than their deterministic counterparts. The reason for

this is obvious since they try to process more information in each step (everything is a distribution as compared to a fixed value in deterministic framework). As compared to deterministic technique, probabilistic technique have

significantly higher run-time complexity. We need fast technique to compute

probabilistic data without sacrificing the accuracy of capturing correlations.

On the flip-side, it is perhaps better to run one iteration of a slow probabilistic framework to get a good solution as compared to many runs of the

deterministic algorithm (which occurs when variabilities get higher).

# 1.5 Techniques for Handling Randomness due to Variability

Variability due to fabrication and environmental randomness poses severe performance, yield and reliability issues in nanoscale designs. There are several philosophies that can be applied to counter the impact of these randomness.

#### 1.5.1 Reduce the Sources of Variations

One of the most promising ways to counter fabrication variability are to develop newer fabrication techniques where we have more control over the actually fabrication process. Such advances will allow us to reduce the manifestation of variations thereby avoiding the problem of randomness due to variability. A key requirement of this is to develop fabrication techniques that are firstly compatible with the existing fabrication flow as well as have a low cost overhead. Without these two qualities, it is extremely difficult for mainstream ASIC designs to adopt these newer fabrication techniques that can reduce the sources of variations.

#### 1.5.2 Design-Time Optimization

In this approach, one can try to explicitly model and consider the impact of variability during the design flow. We appropriately modify our design analysis and optimization techniques to ensure that we can use both deterministic and probabilistic algorithms to consider the performance spread that occurs due to variations. Such an approach allows us to gauge and limit the performance band of the design to ensure that we get the desired yield and reliability without paying any extra overhead in design cost and design time. Key issues for such an approach are:

- 1. Accurate and compact modeling of the variability data

- 2. Analysis techniques that can use the modeling information to predict the im-

pact of variability on design performance through variability-aware analysis. In recent years, statistical timing analysis [42, 105, 79, 2, 39, 10, 118, 27, 119, 1, 96, 43] has emerged as one such effective analysis scheme that uses variability-aware modeling for timing analysis considering the impact of fabrication variability.

3. Design optimization techniques that are driven by the variability-aware analysis to probabilistically/statistically optimize the design performance considering variability. A lot of work has been done considering state of the art design optimization techniques like buffer insertion [115, 7, 69], gate sizing [117, 8, 73, 67, 80, 32] and leakage optimization [97, 89, 77, 73, 83].

#### 1.5.3 Post-Silicon Design Tunability

This approach presents a powerful solution to the fabrication and environmental variability problem. Using this design philosophy, we can build in tuning knobs into the design which can be used to selectively alter design parameters once the chip has been manufactured. After fabrication, through external or on-chip testing, we can gauge the real manifestation of randomness due to fabrication variability and then appropriately tune the chip to counter the impact of variability and improve design yield and performance significantly. Tunability in designs can be provided through adaptive body-biasing, supply voltage scaling and through post-silicon tunable clock-tree buffers [117, 72, 114, 82, 36].

#### 1.5.4 Runtime Adaptivity

Runtime adaptivity based techniques are effective in being able to counter the impact of runtime environmental variations. The design is such that it has the capability of sense the occurance of variations and adapts the design performance to counter the variation while still trying to meet the overall performance constraints on the design. Self-correcting designs and architectural modifications can be made by using techniques like reconfigurable logic and redundant path based designs to counter the impact of variability during runtime. Furthermore, another interesting possibility is to use larger blocks of asynchronous logic which is inherently immune to variations.

#### 1.6 Organization

This dissertation is organized as follows:

Chapter 2 discusses our research contributions to the area of variability-aware analysis, specifically looking at the problem of statistical timing analysis. We present the basic background behind statistical timing analysis, discuss the current literature and present our research contributions in the area. We specifically present two works, one of which presents a framework for non-linear, non-Gaussian statistical timing analysis considering correlations [119]. The second work presents an interesting technique to control the trade-off between runtime and error induced during statistical timing analysis. This technique allows us to get significant run-

time speedups compared to traditional statistical timing analysis using the concept of *error budgeting*.

Chapter 3 discusses our research contributions to the area of variability-aware design optimization. We first present the existing literature in this area and then discuss two specific works in this area. Firstly, we talk about a probabilistic buffer insertion technique [115]. This work was one of the first to consider buffer insertion in presence of wirelength uncertainty and proposed technique to perform probabilistic design optimization using buffer insertion. Secondly, we present our work on a general optimization framework based on Monte-Carlo technique considering fabrication variability. In this work, we look at stochastic programming based technique in a linear programming framework. Such techniques can be applied to several VLSI-CAD problems without making any assumptions of the nature of the distributions of the variability data or the correlations between them.

Chapter 4 presents our work on design optimization through post-silicon tunability. The work titled variability-driven simultaneous gate sizing and post-silicon tunability allocation [117] presents a design management framework that can be used to balance the effort spent on pre-silicon (through gate sizing) and post-silicon optimization (through tunable clock-tree buffers) while maximing the yield gains.

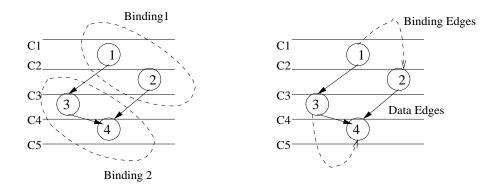

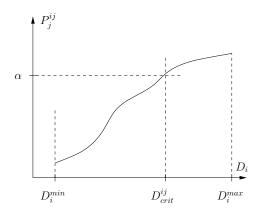

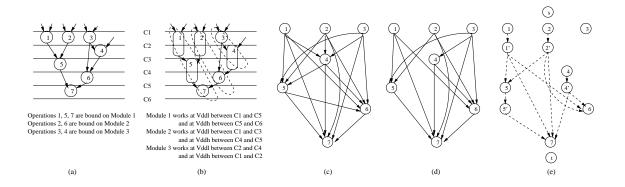

Chapter 5 presents our work on runtime dynamic power optimization technique considering variability. We talk about probabilistic design synthesis and runtime optimization as a means to get reliable and robust designs. This work titled Simultaneous Resource Binding and Dual-Vdd Allocation for Power Optimization with Probabilistic Reliability Guarantee, introduces the concept of probabilistic re-

liability guarantee as a metric of optimization considering the impact of fabrication and environmental uncertainty at system-level design stage. We propose a framework that presents a design technique for runtime optimization of dynamic power through supply voltage scaling.

Chapter 6 concludes this dissertation and presents some interesting directions for future work in variability-aware design methodology for nanoscale technologies. Further, we present some directions to extend these ideas to distributed integrated and embedded systems as well focusing on the key challenges of performance, reliability and yield.

## Chapter 2

#### Variability-Aware Timing Analysis

Static Timing Analysis is one of the most critical steps in VLSI design. It is used both during optimization as well as verification. In high performance design, it is absolutely imperative for the design to meet the required timing constraints. This brings out the need for fast, accurate and incremental timing analysis methodologies.

In the past static timing techniques [84, 88] have provided a reliable and efficient method for timing analysis during design sign-off or verification. These techniques were enhanced to accommodate for the DSM effects like coupling noise, RC and RLC interconnect modeling, simultaneous switching and other variations. The die-die and within-die variations were also handled typically by performing case analysis. As pointed out in [25], this paradigm is breaking down due to the increasing DSM effects. It is very hard for conventional static timing analysis to account for the variability accurately. These schemes are deterministic in nature and it is very hard to capture the nature of the distributions of the variability using such techniques. Performing a case-based or corner-based analysis required a large number of static timing runs as the number of independent sources of variability are increasing. Furthermore, at the design corner a worst-cast assumption is made which is pessimistic, while it is very hard to analyze all possible design corners. Missing one such critical design corner could lead to failure which are detected after the IC is

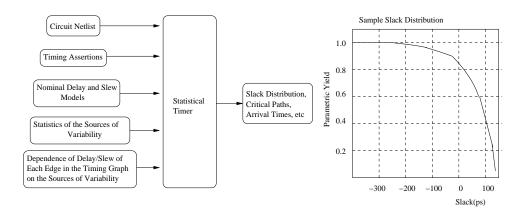

Figure 2.1: Statistical timer: block diagram & sample slack distribution manufactured.

This brings the need to develop *Statistical Timing Analysis* (STA) techniques, that will allow the designer to aim for high-performance while giving a quantitative risk-management against the effects of fabrication variability. Let us now understand the basics about a typical statistical timing framework.

# 2.1 Statistical Timing Analysis

A conventional static timer takes the circuit as an input and builds a timing graph from it. Delay models are used to provide the timing information (delay, slew etc.) about each gate. The analysis computes the timing slack in the circuit from which the highest frequency of operation can be determined. Additionally, it can produce a list of failed timing tests, arrival times at gates, slack at gates, critical paths or any other timing information that may be useful.

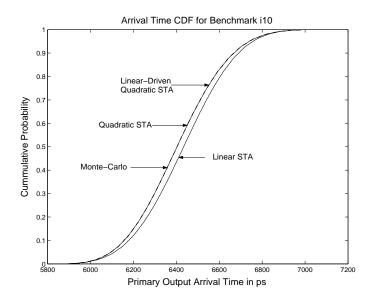

As shown in figure 2.1, we can see that a statistical timer takes in additional information about the nature of the sources of variations. We can generated accurate

modeling of the fabrication variability to calculate the distribution of these variations and the correlation information. The statistical timer has the capability to link these sources of variability to their effect on timing values. The main output from the timer is a probability distribution of the slack. As shown in figure 2.1, we can see that the parametric yield of the circuit is almost 100 % at a slack of -300ps while it sharply drops down as the slack increases. Additional information like arrival times at each gate, slack at each gate, slew, critical paths etc. are also reported by the timer which can be used for later optimization.

A statistical timer needs to be able to model the correlations that exist between different parameter variabilities. In general most within-die variations are correlated although there is some independent randomness that exists in the die. Correlations can be path-based (reconvergent fanout) which essentially occur because two paths can share a sub-path between them. Correlation also exist between gates that share the same voltage islands ( $V_{dd}$  fluctuations). There is global correlation due to diedie variations (fabrication variability) as well as spatial correlations for within-die variations. Additional effects that thermal heating etc. also induce correlations into the gate behavior. And lastly, there is also some uncorrelated independent variations (doping concentration,  $T_{ox}$  etc.) that exist on the chip as well. A good statistical timer needs to be able to model these variations along with the correlation information.

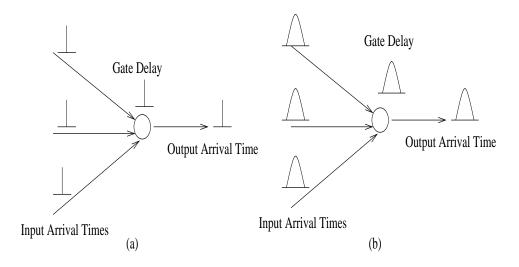

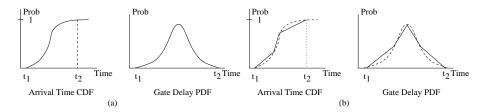

Figure 2.2: Static versus Statistical Timing Analysis

### 2.2 Current Approaches in STA

Let us now try to understand the working of a statistical timing analysis technique in more detail. Essentially, the idea is to try to capture the variability in design parameters by modeling them as distributions (PDFs/CDFs) or even as random variables (with a corresponding distribution). This essentially implies that in the STA modeling framework, each arrival time as well as gate delay becomes a distribution (represented as a PDF/CDF or a function of random variables). As shown in figure 2.2(a), a typical static timing framework represents each arrival time as well as gate delay by a deterministic value which can be easily propagated through the circuit generating the required timing information. In STA, as shown in figure 2.2(b), each arrival time/gate delay is modeled as a distribution and we now need to propagate the distribution through the circuit to generate the required timing information. Additionally, as mentioned earlier, the variations in the parameters are correlated globally as well as spatially. There can also be independent random

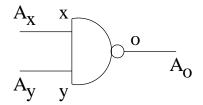

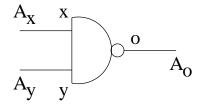

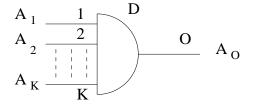

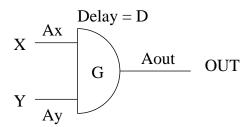

Figure 2.3: Gate with x and y input pins and output o

variations due to fabrication variability as well. The STA framework needs to be able to model as well as propagate these correlations accurately.

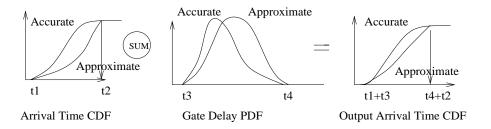

Timing Analysis involves the computation of two main operations on the timing variables. As shown in figure 2.3, let us assume that we are given a gate g with two input pins x and y and an output pin o. The arrival time  $A_o$  at the output pin o can be calculated given the arrival times at the input pins  $(A_x, A_y)$  and the gate delay  $(G_D)$ . Mathematically, this operation can be represented as given by equation 2.1:

$$A_o = MAX(SUM(A_x + G_D), SUM(A_y + G_D))$$

(2.1)

Hence, we first need to perform a SUM operation and then perform a MAX operation on the timing variables to calculate the distribution of the arrival time variables. While the SUM operation is computationally tractable, calculating the exact arrival time after the MAX operation is very difficult. The main problem here is that it is very hard to accurately compute the MAX of two timing PDFs/CDFs or functions of random variables efficiently. This has been a primary bottleneck in STA techniques and has prompted most researchers to model the distributions as Gaussian and enforce a Gaussian assumption on the timing distribution after the

MAX computation in order to exploit the various mathematical results that exist on Gaussian Random Variables. We will discuss this issue in greater detail later in this chapter.

#### 2.2.1 Modeling Arrival-Time and Gate Delays

There are two basic ways in which the timing variables can be modeled in STA:

- In [10, 118], the authors have modeled the arrival times and gate delay distributions as PDFs and CDFs. The key problem with both these approaches is the assumption of independence in the timing variables (no correlation information being captured), which is the central assumption in the computational efficiency proposed by these schemes. In [2], the authors present a way to compute bounds on the exact PDF of the timing values in the circuit considering within-die parameter variations.

- Most of the recent work on STA [42, 105, 79, 27, 119, 1, 96, 43, 60] models arrival time and gate delays as a function of random variables. Each parameter that has variability is modeled as an independent random variable. The parameters that are globally or spatially correlated are shared between all gates in the circuit while the independent randomness at each gate is modeled as a separate independent random variable. Initially, this modeling was done such that the gate delay/arrival times were modeled as a linear function of random variables, but lately due to the increasing non-linear effects of variability on

timing, the recent works tries to extend this to a non-linear gate delay model framework [119, 43]. The main reason for modeling timing variables as random variables is to provide an efficient way of capturing correlations between different gates (by using the same random variables for each gate to represent global parameters). Also, there is a vast amount of mathematical framework that exists in random variable theory. In particular Gaussian Random variables are well-studied and have results that are extremely useful in computing the MAX operations. This is the primary reason why most of the existing work in STA modeled timing information as Gaussian Random Variables.

#### 2.2.2 Block-Based STA Versus Path-Based STA