#### ABSTRACT

Title of dissertation: AUTOMATIC PARALLELIZATION OF AFFINE

LOOPS USING DEPENDENCE AND CACHE

ANALYSIS IN A BINARY REWRITER

Aparna Kotha, Doctor of Philosophy, 2013

Dissertation directed by: Professor Rajeev Barua

Department of Electrical and Computer Engineering

Today, nearly all general-purpose computers are parallel, but nearly all software running on them is serial. Bridging this disconnect by manually rewriting source code in parallel is prohibitively expensive. Automatic parallelization technology is therefore an attractive alternative.

We present a method to perform automatic parallelization in a binary rewriter. The input to the binary rewriter is the serial binary executable program and the output is a parallel binary executable. The advantages of parallelization in a binary rewriter versus a compiler include (i) compatibility with all compilers and languages; (ii) high economic feasibility from avoiding repeated compiler implementation; (iii) applicability to legacy binaries; and (iv) applicability to assembly-language programs.

Adapting existing parallelizing compiler methods that work on source code to work on binary programs instead is a significant challenge. This is primarily because symbolic and array index information used in existing compiler parallelizers is not

available in a binary. We show how to adapt existing parallelization methods to achieve equivalent parallelization from a binary without such information. We have also designed a affine cache reuse model that works inside a binary rewriter building on the parallelization techniques. It quantifies cache reuse in terms of the number of cache lines that will be required when a loop dimension is considered for the innermost position in a loop nest. This cache metric can be used to reason about affine code that results when affine code is transformed using affine transformations. Hence, it can be used to evaluate candidate transformation sequences to improve run-time directly from a binary.

Results using our x86 binary rewriter called SecondWrite on a suite of densematrix regular programs from *Polybench* suite of benchmarks shows an geomean speedup of 6.81X from binary and 8.9X from source with 8 threads compared to the input serial binary on a x86 Xeon E5530 machine; and 8.31X from binary and 9.86X from source with 24 threads compared to the input serial binary on a x86 E7450 machine. Such regular loops are an important component of scientific and multimedia workloads, and are even present to a limited extent in otherwise non-regular programs.

Further in this thesis we present a novel algorithm that enhances the past techniques significantly for loops with unknown loop bounds by guessing the loop bounds using only the memory expressions present in a loop. It then inserts run-time checks to see if these guesses were indeed correct and if correct executes the parallel version of the loop, else the serial version executes. These techniques are applied to the large affine benchmarks in SPEC2006 and OMP2001 and unlike previous

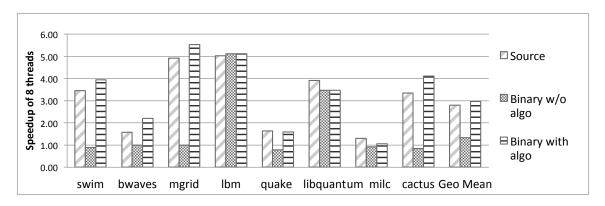

methods the speedups from binary are as good as from source. We also present results on the number of loops parallelized directly from a binary with and without this algorithm. Among the 8 affine benchmarks among these suites, the best existing binary parallelization method achieves an geomean speedup of 1.33X, whereas our method achieves a speedup of 2.96X. This is close to the speedup from source code of 2.8X.

# AUTOMATIC PARALLELIZATION OF AFFINE LOOPS USING DEPENDENCE AND CACHE ANALYSIS IN A BINARY REWRITER

by

# Aparna Kotha

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2013

Advisory Committee:

Professor Rajeev Barua, Chair/Advisor

Professor Gang Qu

Professor Shuvra Bhattacharya

Professor Donald Yeung

Professor Alan Sussman, Deans Representative

© Copyright by Aparna Kotha 2013

# Dedication

# Dedicated to my family

To my father for the inspiration to begin

To my mother for the motivation to continue

To my sister for the long chats to keep me going

To my husband for lots of love and stability to finish

#### Acknowledgments

I owe my gratitude to all the people who have made this thesis possible and because of whom my graduate experience has been one that I will cherish forever.

First and foremost I'd like to thank my advisor, Dr. Rajeev Barua for giving me an invaluable opportunity to work on challenging and extremely interesting projects over the past six years. In times when I felt lost, he was always there to give me a fresh perspective and look at the problem. His words have inspired me in many ways.

I would also like to thank my committee members, Dr. Gang Qu, Dr. Shuvra Bhattacharyya, Dr. Donald Yeung and Dr. Alan Sussmann for agreeing to be on my committee. Your feedback during my proposal and dissertation talks is invaluable.

My labmates through the years at the SCAL lab, University of Maryland, College Park have taught me many things related to academics and many a times otherwise. I would specially like to thank Kapil Anand, Khaled ElWazeer, Timothy Creech, Matthew Smithson, Greeshma Yellareddy, Mincy Mathew, Kyungjin Yoo, Fady Ghanim and many more. Thank you for all the time we spent together and for everything you taught me.

I would also like to acknowledge the help and support from some of the staff members at the ECE department. Melanie Prange, Carrie Hilmer, Kristie Little, Maria Hoo and everyone at the helpdesk and ECE graduate office for being there to solve my non-thesis related problems that arose during the jouney, hence making it a more enjoyable journey.

I owe my deepest thanks to my parents - my mother and father who have always stood by me and supported me all along my career. They have always encouraged me to live my dreams. Their love for me is unparalleled.

I'd like to express my gratitude to my housemates through the years Suma Babu, Purva Ghate, Sarah Khurian, Aparajita Bal and Khushboo Maheshwari for their friendship and support.

Lastly the journey would not have been any fun without my friends. Thanks all of you for all the crazy and fun times: Kapil Anand, Nitesh Shroff, Shalabh Jain, Kaustubh Jain, Harita Tenneti, Rashi Jain, Srikanth Vishnubhotla, Jishnu Keshavan, Surabhi Chouhan, Ishwar Bhati, Raghuraman Gopalan, Satish C Reddy, Silpa Billa, Anshu Sarje and many others. Special thanks goes out to my friends Vijayalakshmi Ethirajulu, Ashwin Rishinaramangalam, Ashwin Pejaver and Sreekanth Annapureddy from IITM days with whom a vacation a year was compulsary and those times are part of my best memories in the last few years.

It is impossible to remember all, and I apologize to those I've inadvertently left out.

Lastly, thank you all and thank God!

# Table of Contents

| Lis | st of T                    | $\Gamma$ ables                                                                                                            | viii                                   |

|-----|----------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Lis | st of I                    | Figures                                                                                                                   | ix                                     |

| 1   | Intro<br>1.1<br>1.2<br>1.3 | Oduction Introduction                                                                                                     | 1<br>1<br>7<br>8                       |

| 2   | Auto 2.1                   | Traditional methods                                                                                                       | 10<br>10<br>11<br>12<br>14<br>14       |

|     | 2.3                        | 2.2.1 Representation of Dependence information2.2.2 Decision algorithm to transform loops2.2.3 Code GenerationConclusions | 15<br>16<br>17<br>17                   |

| 3   | Depe 3.1 3.2               | endence Analysis Calculating dependence vectors                                                                           | 19<br>19<br>19<br>21<br>32             |

| 4   | Run<br>4.1<br>4.2          | time dependent loop bounds  Examples                                                                                      |                                        |

| 5   | Cach<br>5.1                | Characterizing cache reuse  5.1.1 From source                                                                             | 67<br>69<br>71<br>72<br>73<br>74<br>74 |

|   |       | 5.1.2.2 Calculating LoopCost(1) in terms of cache lines                |     |

|---|-------|------------------------------------------------------------------------|-----|

|   | 5.2   | Using Loop Cost in McKinley's Algorithm                                |     |

|   |       | 5.2.1 McKinley's Algorithm                                             |     |

|   |       | 5.2.1.1 Determining the Ideal Loop Order                               |     |

|   |       | 5.2.1.2 Determining the Optimal Loop Order                             |     |

|   |       | 5.2.1.3 Strip-mining and Interchanging for blocking                    |     |

|   |       | 5.2.1.4 Running Example                                                |     |

|   | 5.3   | Handling Imperfect Nests                                               | 85  |

| 6 | Infra | astructure                                                             | 88  |

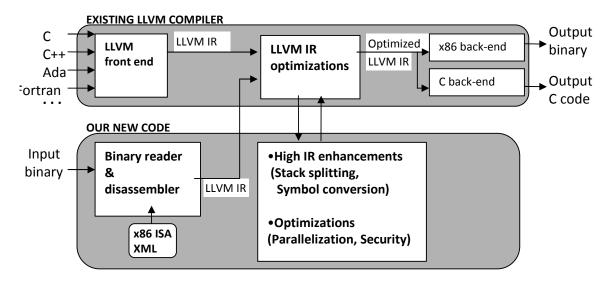

|   | 6.1   | Implementation-SecondWrite                                             | 89  |

|   |       | 6.1.1 Innovations in SecondWrite                                       |     |

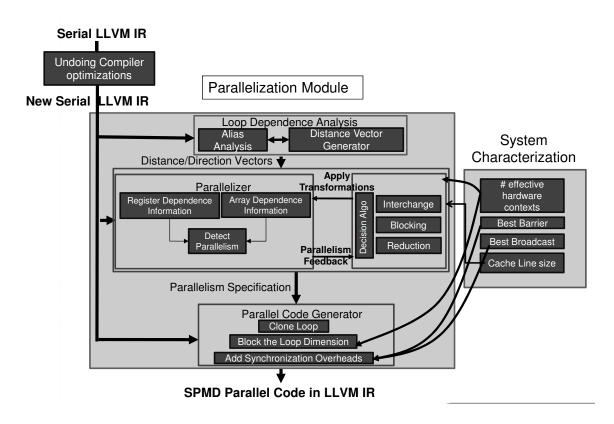

|   | 6.2   | Affine Automatic Parallelizers                                         | 96  |

|   |       | 6.2.1 Undoing Compiler Optimizations in a Binary Rewriter              | 99  |

|   |       | 6.2.1.1 Undoing LICM                                                   | 96  |

|   |       | 6.2.1.2 Undoing Complex Control flow                                   | 101 |

|   |       | 6.2.1.3 Discovering induction variables                                | 102 |

|   |       | 6.2.2 Register dependencies                                            | 103 |

|   |       | 6.2.2.1 Special case of scalar dependence: Reduction                   | 106 |

|   |       | 6.2.2.2 Special case of scalar dependence: Values carried              |     |

|   |       | across loop                                                            |     |

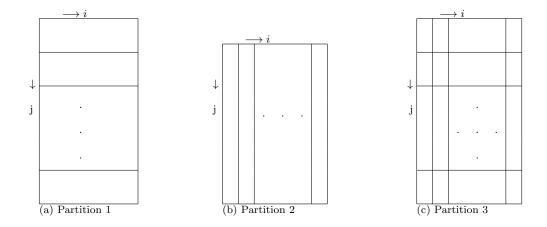

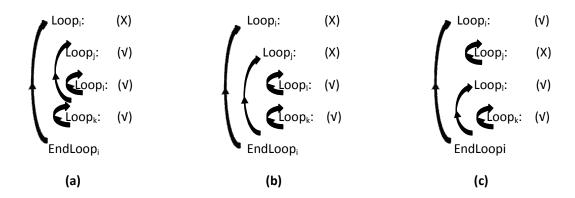

|   |       | 6.2.3 Deciding Partitions                                              | 108 |

|   |       | 6.2.4 Code Generation                                                  | 111 |

|   |       | 6.2.5 Using LLVM for Implementation                                    |     |

|   | 6.3   | Source Parallelizer: AESOP                                             | 115 |

|   | 6.4   | Implementation in the Polyhedral model                                 | 117 |

| 7 | Resi  | ults                                                                   | 121 |

|   | 7.1   | Results for Dependence Analysis                                        | 121 |

|   | 7.2   | Results for cache reuse metric                                         |     |

|   | 7.3   | Results for algorithm for guessing loop bounds                         |     |

| 8 | Rela  | ted Work                                                               | 148 |

|   | 8.1   | Static binary rewriters and their applications                         | 148 |

|   | 8.2   | Affine based automatic parallelizers from source                       | 150 |

|   | 8.3   | Linear algebriac methods to calculate distance and direction vectors . | 151 |

|   | 8.4   | Dynamic binary automatic parallelization methods                       | 152 |

|   | 8.5   | Static affine automatic parallelization of binaries                    | 153 |

|   | 8.6   | Automatic vectorization of binaries                                    | 154 |

|   | 8.7   | Array delinearization techniques                                       |     |

|   | 8.8   | Cache optimizations using binary rewriting                             |     |

|   | 8.9   | Cache analysis and optimizations in source affine parallelizers        |     |

| 9 | Con   | clusions and Future Work                                               | 159 |

|   | 0.1   | Conclusions and Future Work                                            | 150 |

Bibliography 161

# List of Tables

| 5.1 | LoopCost(1) for the loop in genver                                    |

|-----|-----------------------------------------------------------------------|

| 7.1 | Test machines to test dependence analysis                             |

| 7.2 | Test machines used for testing the cache reuse model                  |

| 7.3 | L1 cache miss rate after applying modified McKinley algorithm 134     |

| 7.4 | Loop nest transformation from input to output using modified McKin-   |

|     | ley's algorithm                                                       |

| 7.5 | Description of the affine benchmarks from the SPEC 2006 and OMP       |

|     | 2001 benchmark suites                                                 |

| 7.6 | Number of loops parallelized for the affine benchmarks with and with- |

|     | out the run time loops algorithm                                      |

| 7.7 | Description of the non-affine benchmarks from the SPEC 2006 and       |

|     | OMP 2001 benchmark suites                                             |

| 7.8 | Number of loops parallelized by our binary parallelizer for the non-  |

|     | affine benchmarks in SPEC 2006 and OMP 2001 benchmark suites 146      |

# List of Figures

| $3.1 \\ 3.2$      | Loop-Carried Dependencies in Source Code                                                                                      |       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.1               | Code Example to motivate the algorithm to guess loop bounds for loops with run-time dependent loop bounds                     | . 37  |

| 4.2<br>4.3        | Example 1 & 2 to illustrate the algorithm to guess loop bounds Example 3 & 4 to illustrate the algorithm to guess loop bounds | . 41  |

| 5.1               | Example Loop to illustrate Cache Reuse Algorithm                                                                              |       |

| 5.2<br>5.3<br>5.4 | Algorithm to obtain Optimal Order from Ideal Order                                                                            | . 84  |

| 6.1               | SecondWrite                                                                                                                   |       |

| 6.2<br>6.3<br>6.4 | Detailed diagram of the Affine Parallelizer                                                                                   |       |

|                   | by compiler optimizations                                                                                                     | . 103 |

| 6.5               | Example Loop to illustrate introducing induction variables                                                                    |       |

| 6.6               | Example of a loop that carries a scalar dependence                                                                            |       |

| 6.7<br>6.8        | Example of a loop that carries a reduction dependence Example loop showing a scalar value defined before a loop and used      |       |

| 6.9               | after it                                                                                                                      |       |

| 6.10              | Arbitrarily nested affine loops to illustrate which loops will be parallelized by our decision algorithm                      |       |

| 7.1               | Speedup on x86 DASH for source and binary using dependence analysis techniques                                                | . 123 |

| 7.2               | Speedup on x86 BUZZ for source and binary using dependence anal-                                                              |       |

| 7.3               | ysis techniques                                                                                                               | . 124 |

|                   | ysis techniques                                                                                                               | . 125 |

| 7.4               | Number of loops parallelized from source and binary using dependence analysis techniques                                      | 127   |

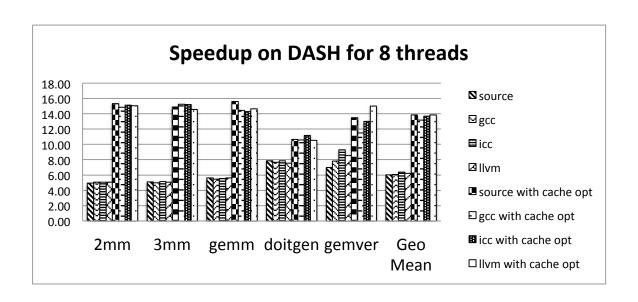

| 7.5               | Speedup on DASH using the cache resuse metric for 8 threads                                                                   |       |

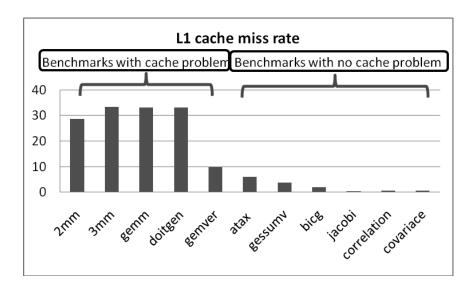

| 7.6               | Cache miss rate for the original benchmarks                                                                                   |       |

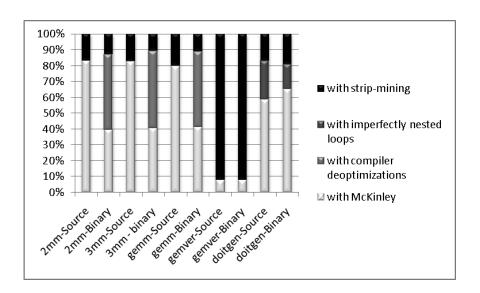

| 7.7               | Breakup of the speedup on x86 DASH from different steps of the                                                                |       |

|                   | decision algorithm                                                                                                            |       |

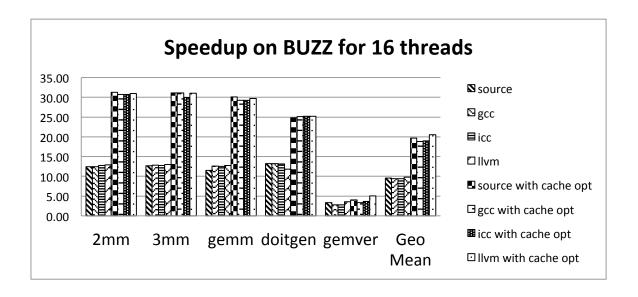

| 7.8<br>7.9        | Speedup on BUZZ using cache reuse metric for 24 threads Speedup on x86 DASH for benchmarks compiled from GCC, ICC and         | . 133 |

|                   | LLVM                                                                                                                          | . 135 |

| 7.10              | Speedup on x86 BUZZ for benchmarks compilers from GCC, ICC and LLVM                                                           | . 135 |

|                   | 1/1/1/1/10                                                                                                                    | . 155 |

| 7.11 | Speedup of the affine benchmarks from SPEC 2006 and OMP 2001 |     |

|------|--------------------------------------------------------------|-----|

|      | benchmark suites for 8 threads                               | 140 |

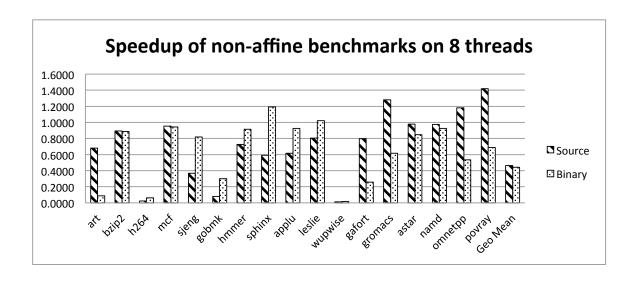

| 7.12 | Speedup of the non-affine benchmarks from SPEC 2006 and OMP  |     |

|      | 2001 benchmark suites                                        | 143 |

| List | of Algorithms                                                      |   |

|------|--------------------------------------------------------------------|---|

| 1    | Step 1: Algorithm to divide accesses into DGs 4                    | 9 |

| 2    | Step 3.1: Guesses for induction variables using one access 5       | 0 |

| 3    | Step 3.2: Guesses for induction variables using pair of accesses 5 | 2 |

| 4    | Step 5: Algorithm for Inter-group constraints 6                    | 1 |

| 5    | Algorithm to decide which loop dimensions to parallelize 10        | 9 |

# Chapter 1

#### Introduction

#### 1.1 Introduction

Since about 2004, semiconductor trends show that the astonishing improvements in clock speeds over the last few decades have come to end. However improvements in silicon area, as per Moore's law, are still being realized. As a natural consequence of these trends, microprocessor vendors have turned to multi-core processors to remain competitive. For e.g., Intel Corporation has replaced its Pentium line of uniprocessors with the Intel Core processor family, virtually all of which have multiple cores. AMD Corporation offers the Athlon Dual-core and Phenom Quad-core processors. By the end of 2009, multi-cores accounted for 100% of all new desktop and notebook processors [1]. The CPU road maps of both Intel and AMD show trends towards further multiple cores. Today even handheld devices such as mobile phones and tablets have multiple cores in them. Embedded system processors are being realized with multiple cores in them.

With the advent of multi-core hardware in every sphere it is essential to have parallel software to run on them. There are three methods to obtain parallel software:

• The first way to obtain parallel software is to use parallel language directives such as OpenMP [2, 3] to implicitly specify parallelism using comments in

high-level language programs.

- The second way to obtain parallel software is to write programs in an explicitly parallel manner. This is done using a set of APIs, such as MPI [4], posix complaint *pthreads* or Intel's TBB, to extend existing languages such as C, C++ and Fortran.

- The third way to obtain parallel software is to use an automatic parallelizing compiler. This is a tool that takes as input serial code and produces as output parallel code

The first two methods need human intervention whereas the third method is an automatic tool. Although the use of explicitly parallel programming using the first two methods is increasing, their adoption has been slowed by the following factors:

- Huge amounts of serial code represent most of the world's programs.

- Rewriting code manually in parallel is time consuming and expensive.

- Dearth of engineers trained in parallel programming and algorithms.

- Parallel programming productivity per line of code is lower than for serial [5].

For this reason, except for the most performance-critical code, it is not likely that most of the world's existing serial code will be rewritten in parallel.

The third way to obtain parallel software using an automatically parallelizer overcomes the above-mentioned drawbacks of explicitly parallel code. Indeed, since

the introduction of parallel machines in the early 1970s, many strides have been made in parallelizing compiler technology. Most efforts to date have focused on parallelism in loops, primarily in regular, dense-matrix codes. In particular, techniques have been developed for parallelizing loops with array accesses whose indices are affine (linear) functions of enclosing loop induction variables [6]. This work is particularly interesting as most scientific and multi-media codes are affine and the maximum run time is spent in these loops. Hence parallelizing these loops can result in significant speedups. The advantages of automatic parallelization over explicit parallel programming are:

- No need of human intervention; hence large amounts of programs can be parallelized

- Less prone to error since manual intervention is not there

- Can be integrated within an compiler framework since it can be constructed to work on compiler IR

In this thesis we present methods to implement automatic parallelization inside a binary rewriter, instead of a compiler. A binary rewriter is a software tool that takes a binary executable program as input, and outputs an improved executable as output. In our case, the input code will be serial, and the output will be parallel code. As far as we know, there are no existing methods for automatic parallelization in a static binary rewriter. Further, there are no existing binary automatic parallelization tools (static or dynamic) that perform affine-based parallelization. Parallelization in a binary rewriter has several advantages over parallelization in a compiler:

- Works for all compilers and languages A parallelizer in a binary rewriter

works for all binaries produced using any compiler from any source language.

This compatibility is a huge practical advantage versus a compiler implementation.

- No need to change software tool chains A binary rewriter is a simple add-on to any existing software development tool chain. Developers and their companies, typically very resistant to changing the tool chains they are most familiar with, will not have to. This is important since many existing compilers do not perform automatic parallelization.

- **High economic feasibility** A parallelizer in a binary rewriter needs to be implemented only once for an instruction set, rather than repeatedly for each compiler.

- Applies to legacy code Legacy binaries for which no source is available, either because the developer is out of business, or the code is lost can be parallelized using a binary rewriter. No compiler can do this.

- Works for assembly-language programs A binary rewriter, unlike a compiler can parallelize assembly code, regardless of whether it is part of the program with inlined assembly or all of it. Assembly code is used sometimes to write device drivers, code for multi-media extensions, memory-mapped I/O, and time-critical code portions.

- Can perform platform-specific tuning Since a binary rewriter can tune

the output program for the particular platform it is executing on, it is possible to tune the same input executable differently for different platforms which share the same ISA, but may have widely different runtime costs. For example, we already choose the best barrier and broadcast mechanism for the end-user platform, and are investigating specific optimizations for the instruction set enhancements and instruction latencies of that platform.

• Can be used by end user of software Unlike compiler-provided parallelization which can only be done by the software developer, parallelization in a binary rewriter can be done by the end user of the system depending upon his or her specific needs, constraints and environment.

The above advantages argue that it is useful to provide automatic parallelization in a binary rewriter, despite compiler implementation being possible. By allowing automatic parallelization to be done on arbitrary binaries from any source,

we hope to make this technology universal, accessible, portable, customizable to the

end-user's platform, and usable by any computer user, not just developers. In this

vision, our hope is that the parallelizing rewriter will be a transparent utility that

is automatically triggered for all programs at install-time.

Our approach to automatic parallelization is **not** to invent entirely new parallelization methods, but to investigate how best to adopt ideas from existing compiler methods to a binary rewriter. This adoption is not trivial, since binary rewriters pose challenges not present in a compiler, including primarily, the lack of high-level information in binaries. Parallelizing compilers rely on symbolic information, for

identifying arrays, affine function indices, and induction variables; for renaming to eliminate anti and output dependencies; and for pointer analysis to prove that memory references cannot alias, allowing their parallel execution. Binaries lack symbolic information, making all these tasks more difficult. A central contribution of this proposal is parallelization methods in a binary rewriter that can work effectively without using any symbolic or array index information.

On the flip side, binary rewriters also enjoy an advantage compared to a compiler: they have access to the entire program including library code. The need for separate compilation – an important practical requirement – has meant that commercial compilers typically have access to only one file at a time. For large programs with many files, this represents a tiny sliver of the total code. Whole-program parallelization is important since parallelization in one procedure may inhibit parallelization at containing or contained procedures, and moreover, parallel code blocks may be in different files. Currently we look at loop-level parallelism as most execution time is spent in loops.

Of course, we recognize that parallelizing affine programs is only one step towards the goal of parallelizing all programs, albeit an important one. Many programs have non-affine parallelism, and others have little or no parallelism. Our techniques can be effectively combined with non-affine techniques to parallelize a larger set of programs. This work should be seen as what it is: a first successful attempt to parallelize binaries using affine analysis, rather than the last word. We hope to open up a new field of research with this significant step.

#### 1.2 Contributions

The main contribution of this thesis is to present an affine automatic parallelizing tool inside a static binary rewriter. The main contribution of this work can be divided into three major parts:

- The first contribution of this work is to present how dependence analysis can be performed directly on binary code without the presence of any symbolic information. Traditionally all automatic parallelizing compilers from source rely on symbolic information to know the size and dimensions of arrays, the array indices etc. However, no such information is present in a compiled binary. We present methods to still recover dependences using only binary code. This is done by recovering array address variables in the form of linearized multi-dimensional expressions from binary code and then solving them using dependence tests within the loop bound regions.

- The second contribution of this thesis is to parallelize affine loops from binaries even when loop bounds are run-time dependent. Using the techniques developed in the first contribution, the parallelization of such loops is highly limited since solving linearized multi-dimensional expressions in the infinite region generates more dependencies limiting parallelization. Hence, we have developed techniques to guess bounds for the loop within which it is parallel. We then insert run-time checks to see that the actual loop bound is lower than or equal to the one we guessed before executing the parallel version of the loop. In this way we increase the scope of affine loops parallelized. In our

results we show that we can effectively parallelize the affine benchmarks from SPEC 2006 and OMP 2001 using this techniques.

• The third contribution of this thesis is a technique by which the cache reuse of affine loops can be calculated directly from binaries using the linearized multi-dimensional expressions for address variables obtained directly from binary code. Using the cache reuse metric we can reason about the loop ordering in a loop nest and transform it to maximize cache reuse and increase coarse-grain parallelization.

# 1.3 Organization of Dissertation

This thesis is further organized as follows:

In chapter 2 we introduce automatic parallelization by presenting the past literature in both the traditional and polyhedral schools of study. Chapter 3 presents a method to parallelize affine loops directly from binary code by recovering address expressions for the affine access followed by a method to parallelize loops when their bounds are run-time dependent in chapter 4. In chapter 5 we present a method to calculate the *cache reuse metric* directly from binary and use it to transform the loop. The implementation details of our automatic parallelizer are presented in chapter 6 followed by results in chapter 7 and related work in chapter 8. Conclusions of the work and suggested future directions are presented in chapter 9.

# Chapter 2

#### Automatic Parallelization

In this chapter we briefly describe the background of automatic parallelization as has been described in the vast literature in this area.

An automatic parallelizer is a tool that takes as input serial code and produces as output parallel code. Traditionally such tools have been designed for source code with affine loops in them. Affine loops are loops that contain array indices that are a linear combination of the induction variables of the loop nest *i.e.*loops containing A[i][j], A[i+3j+5][4i+2j+10], A[i][i] are all affine whereas loops containing A[i/2] or  $A[i^2]$  are not.

Existing methods in affine analysis and parallelization can be categorized into two broad classes: traditional methods and those based on the polyhedral model.

#### 2.1 Traditional methods

Traditional methods [7] [8] [9] [10] [11] [6] [12] are those which are based on modeling loops as the units of consideration, where matrices are used to model most concepts including affine indices, iteration vectors, dependence vectors and loop transformations. Methods have been proposed for deciding what order of transformations should be applied and in what order.

The traditional methods are divided into three steps: representation of the

dependencies; decision algorithms to transform loop nests and then methods to generate target code. Further we present these three steps briefly describing the methods that have been proposed for each of them in the past. These have been presented to describe the techniques used in parallelizing compilers that are built on the traditional model.

#### 2.1.1 Representation of dependence information

In this section we describe how dependence information is represented in the traditional methods.

Traditional models predominantly represent the dependence information either as distance or direction vectors [13] [7] [8]. Distance vectors for every loop contain an entry for each loop nest where each entry is the step of the loop dependence in that induction variable.

The formal definition of the distance vector from [6] is:

Suppose that there is a dependence from statement  $S_1$  on iteration i of a loop nest of n loops to statement  $S_2$  on iteration j, then the dependence distance vector d(i,j) is defined as a vector of length n such that  $d(i,j)_k = j_k - i_k$  where:

- i and j are both iteration vectors of n elements

- Distance vector measures the difference between i and j in the iteration space

Direction vectors represent the same information as the distance vector when less precision is required or available. The formal definition of dependence direction vectors from [6] is:

Suppose there is a dependence from statement  $S_1$  on iteration i of a loop nest of n loops to statement  $S_2$  on iteration j, with a distance vector d(i, j), then the dependence direction vector D(i, j) is defined as a vector of length n such that

$$\begin{split} D(\mathtt{i},\mathtt{j})_{\mathtt{k}} &= \text{``} < \text{``} \text{ if } d(\mathtt{i},\mathtt{j})_{\mathtt{k}} > 0 \\ \\ &= \text{``} &= \text{``} \text{ if } d(\mathtt{i},\mathtt{j})_{\mathtt{k}} = 0 \\ \\ &= \text{``} > \text{``} \text{ if } d(\mathtt{i},\mathtt{j})_{\mathtt{k}} < 0 \end{split} \tag{2.1}$$

Distance/Direction vectors are calculated using standard linear algebraic methods described in literature. These include the Greatest Common Divisor (GCD) test [14, 15], Banerjee's inequalities [15], Single Index and Multiple Index Tests [13, 7], multidimensional GCD [15], the delta test [16] and the omega test [17].

Every loop nest has a set of distance or direction vectors associated with it that represent the dependencies present in the loop nest.

# 2.1.2 Decision algorithms to transform loops

Most affine transformations, their legality conditions, and code generation methods have been known for many years. However the problem of finding an optimal order of transformations is very challenging. In this section we present some of the decision algorithms that have been presented in traditional literature in the past.

Most work in traditional methods, for example by M.J Wolfe [7] describes the affine transformations independently, but does not provide a decision algorithm for deciding when to apply which transformations, and in what order.

Studies from the University of Illinois from the Polaris group include [9] [18] [19] [20]; The Polaris group extends Kap, an automatic parallelizer, and then use it to parallelize the Perfect Benchmarks. Their target architecture is Cedar, a shared-memory parallel machine with cluster memory and vector processors. Their work focuses on detecting parallelism via array and scalar analysis. Their inter-procedural analysis results de facto from inlining or is performed by hand.

Wolf & Lam's research in Unimodular transformations [21] [8] and later work by Kathyrn McKinley [12] describe how transformations can be traded in a traditional model. Wolf & Lam present a method to correctly model and apply multiple unimodular transformations to affine code to discover coarse grain parallelism minimizing communication. Unimodular transformations unify loop interchange, loop skewing and loop reversal. A unimodular matrix has three important properties. First, it is a square, meaning that it maps an n-dimensional space to an n-dimensional space. Second, it has all integral components, so it maps integer vectors to integer vectors. Third, the absolute value of its determinant is one. Due to these properties, the product of two unimodular transforms is unimodular and the inverse of a unimodular matrix is unimodular. The work by Wolf and Lam looks at transformations in isolation, and does not present a decision algorithm by which multiple transformations may be applied. Later work by SUIF [22] [23] includes interprocedural transformations. McKinley's work [12] builds on some ideas from the unimodular transformation algorithms. This work discovers coarsest grain parallelism and preserves data locality. McKinley's algorithm can take advantage of known loop bounds to more precisely compute locality and granularity of parallelism, and is very efficient. McKinleys work uses a simple cache model to model the reuse in a loop, whereas most earlier work do not have this. The reuse is calculated once and then the algorithm tries to achieve it. This work integrates loop fusion, loop fission and loop tiling.

#### 2.1.3 Code Generation

In traditional model code generation is an immediate effect of the loop transformations applied to every loop. Using any of the decision algorithm described above, the transformation order is decided; then the loop transformations are applied to the loop in the same order generating the final code.

## 2.2 Polyhedral methods

Polyhedral methods [24] [25] [26] [27] [28] [29] are the second class used for affine analysis and automatic parallelization. They represent each statement in an affine loop separately as a point in an iteration domain. After this is done decisions to transform the loop are taken and parallel code is generated for the same.

Polyhedral methods have the following three advantages over traditional methods:

- First, polyhedral models handle imperfectly nested loops seamlessly in their model.

- Second, they are able to model dependence between every dynamic instance in the loop.

Third, complex affine transformations can be modeled as scheduling functions, which in a few instances, can discover multiple traditional transformations in one step;

Traditional methods have the following advantages over the polyhedral methods:

- Their worst-case complexity is in the order of polynomial complexity against the exponential complexity of polyhedral methods.

- Their implementation complexity is also lower than the polyhedral methods.

- These methods are scalable to large programs running into millions of lines of code.

Similar to the traditional model, the polyhedral model has three steps: representation of the program in the polyhedral model; decision algorithms to transform the loop; and then generate target code.

# 2.2.1 Representation of Dependence information

Dependence information is represented differently in the polyhedral and traditional models. In this section we present the techniques used for representing dependence information in the polyhedral methods.

In the polyhedral model, each statement in an affine loop is separately represented as a point in an iteration domain [30]. This is different from traditional affine analysis where the loop iterations are generally considered indivisible in most

scenarios. The points in the iteration domain are defined by constraints arising from loop bounds, and represented mathematically. Polyhedral model represents this information for every dynamic instance of every statement in the loop. They represent dependencies over the iteration space in a dependence polyhedron [29] [28] in a d-dimensional space, where d is the nesting depth of the loop in question.

## 2.2.2 Decision algorithm to transform loops

In this section we present decision algorithms of polyhedral methods.

In this step, the program represented mathematically in the polyhedral model is transformed. In the polyhedral framework, a transformation is a set of affine scheduling functions each of which maps each run-time statement instance to a logical execution date [28] [27] [26] [25] [24]. Transformations are applied to satisfy some optimization need such as improved cache locality or coarser granularity of threads, which can be added on via heuristic or other methods.

The decision algorithms in polyhedral methods are very complex in terms of implementation and computational complexity. The computational complexity of the decision algorithms present in polyhedral models is exponential in the order of the number of statements present in the loop body. Further, this algorithm are memory intensive and combined with their worst-case run-time, suffer from scalability problems.

# 2.2.3 Code Generation

Finally code transformations map the program representation along with the scheduling functions to output code for the target machine. Code generation relies upon syntax tree construction schemes that consist of a recursive application of domain projections and separations [31] [28]. The final code is deduced from the set of constraints describing the polyhedra attached to each node in the tree.

#### 2.3 Conclusions

In balance we decided to implement our technologies in the traditional model. However, they can be adapted to the polyhedral model, as we will present in section 6.4 of chapter 6.

# Chapter 3

# Dependence Analysis

# 3.1 Calculating dependence vectors

The first challenge in parallelizing binaries is in calculating distance/direction vectors. In chapter 2 we have defined distance/direction vectors. In this chapter we first show how these are calculated from source code, and then present our method to calculate the same directly from binary code without any source level information.

#### 3.1.1 From source

In this we section overview the strategy to calculate dependence vectors in the form of distance or direction vectors from affine loops (source-code loops containing array accesses whose indices are affine (linear) functions of enclosing loop induction variables). For example, if i and j are loop induction variables, then array accesses A[i] and A[2i+j+3][i-3j+7] are affine, whereas A[i/2] is not. We will present the techniques first from the source and then we will adapt it from a binary in section 3.1.2. The source-level techniques reviewed in this section are well documented in the literature of affine loop parallelism. These are presented in chapter 8.

To understand how parallelization can be done for affine-based loops; consider that dependencies between the instructions limit the parallelism that we can extract in code. For loops, loop-carried dependencies are the major inhibitors of parallelism,

```

for i from lb_i to ub_i for i from lb_i to ub_i for i from lb_i to ub_i

for j from lb_j to ub_j for j from lb_j to ub_j for j from lb_j to ub_j

A[i+1,j] += A[i,j] + 1 A[i,j] += A[i,j+2] + 1

A[i,j] = \dots

A[i-2,j] = \dots

end for

end for

end for

end for

end for

end for

(a) True-loop carried

(b) Anti-loop carried

(c) Output-loop carried

dependence

dependence

dependence

```

Figure 3.1: Loop-Carried Dependencies in Source Code

and occur when the next loop iteration cannot be initiated before some previous set of loop iterations has completed. Just like scalar dependencies, loop-carried dependencies can be classified into three types: true, anti, and output loop-carried dependencies. Figure 3.1 shows an example of each type.

As in existing work, based on the formulation in [15], a dependence vector  $(\vec{D})$  for loops is defined as an n-dimensional vector, where n is the nesting depth of the loop. The most common formulation of a dependence vector is a distance vector, where each entry is the step of the loop dependence in that induction variable. For example, for the code in figure 3.1(a) the distance vector is calculated by looking for iterations  $(i_1, j_1)$  and  $(i_2, j_2)$  such that the two array accesses in the loop A[i + 1, j] and A[i, j] access the same memory location, then their difference  $(i_2 - i_1, j_2 - j_1)$  is the distance vector. The memory address that A[i + 1, j] accesses in iteration  $(i_1, j_1)$  is  $A[i_1 + 1, j_1]$  and the memory address that A[i, j] accesses in iteration  $(i_2, j_2)$  is  $A[i_1, j_1]$ . If both the array expressions access the same memory location,

then  $i_1 + 1 = i_2$  and  $j_1 = j_2$ . Rearranging the terms:

$$i_2 - i_1 = 1$$

$$j_2 - j_1 = 0$$

(3.1)

Hence, the distance vector for the loop in figure 3.1(a) is (1,0) indicating that there is a dependence in steps of 1 along i, whereas there is no dependence along j. Similarly, for the loop in figure 3.1(c) the distance vector is  $\vec{D} = (2,0)$ , indicating that there is a dependence in steps of 2 along i, whereas there is no dependence along induction variable j. Further, for the loop in figure 3.1(b) the distance vector is  $\vec{D} = (0,2)$ , indicating that there is a dependence in steps of 2 along induction variable j, and no dependence along induction variable i.

Linear systems of equation solvers are used to calculate distance vectors in literature. These include the GCD and Single Index Variable (SIV) test [15]. As shown above, the linear system of equations is obtained from the symbolic array index expressions and array declarations present in source code. Further when the distance cannot be found or is not deterministic, we can represent the dependence in loops by direction vectors [7] [6], a less precise formulation of distance vectors. Dependence vectors are vectors of loop nesting depth each entry of which are one of  $\{=,<,>,*\}$ .

# 3.1.2 From Binary

In this section we present our method for calculating dependence analysis from low-level code obtained from binary code, which does not contain any symbolic information or affine expressions. The analysis will be successful when the underlying access patterns are affine, even when the array indices needed for traditional dependence analysis for parallelization are absent, such as in binary code.

A source-code fragment and one of its possible binaries is shown in figure 3.2. The binary is shown in pseudo-code for comprehensibility, but actually represents machine code. Other binaries are also possible, but we will be able to illustrate the general principles of our method with this example. The binary code assumes that the array is laid out in row-major form, with the address of A[i, j] being computed as:

$$\&\mathtt{A}[\mathtt{i},\mathtt{j}] = \mathtt{A} + \mathtt{i} \times \mathtt{size\_j} + \mathtt{j} \times \mathtt{elem\_size} \tag{3.2}$$

where elem\_size is the size of an individual array element, and size\_j is the size of the second array dimension, both in bytes. We assume row-major accesses to understand our techniques, but in no way are these techniques going to be effected if the code was arranged in a column-major format. If the code is arranged in a column-major format then the address computed in binary code will be of the form:

$$\&A[i,j] = A + i \times elem\_size + j \times size\_i$$

(3.3)

Though our theory presently assumes row-major, it is correct for column-major codes as well.

To see how we parallelize the binary code, the following intuition is helpful: it is a simple proof to show that for any affine array access, its address variable is

#### Source Code

```

\texttt{j}' \leftarrow \texttt{lb}_\texttt{j} * \texttt{elem\_size}

for i from lb_i to ub_i

addr\_reg \leftarrow Base + i' + j' --(B)

for j from lb<sub>j</sub> to ub<sub>j</sub>

\texttt{reg\_ub\_addr} \leftarrow \texttt{Base} + \texttt{i}' + \texttt{ub}_\texttt{j} * \texttt{elem\_size}

A[i,j] = A[i,j] + 1

10 loopj:load reg ← [addr_reg]

end for

end for

11

\texttt{reg} \leftarrow \texttt{reg} + \texttt{1}

Binary Code

12

\texttt{store [addr\_reg]} \leftarrow \texttt{reg}

addr\_reg \leftarrow addr\_reg + elem\_size --(A)

reg_lb_i \leftarrow lb_i

13

CMP addr_reg \leq reg_ub_addr --(C)

2

\texttt{reg\_ub}_\texttt{i} \leftarrow \texttt{ub}_\texttt{j}

14

\mathtt{i}' \leftarrow \mathtt{lb_i} * \mathtt{size\_j}

--(E)

15

Branch if true to loopj

\texttt{reg\_ub}_i' \leftarrow \texttt{ub}_i * \texttt{size\_j}

\mathtt{i}' \leftarrow \mathtt{i}' + \mathtt{size}_{\mathtt{-}}\mathtt{j}

16

--(D)

\texttt{CMP} \ \mathtt{i'} \leq \texttt{reg\_ub'_i}

--(F)

\texttt{5 loopi:reg\_lb}_j \leftarrow \texttt{lb}_j

17

6

\texttt{reg\_ub}_j \leftarrow \texttt{lb}_j

Branch if true to loopi

18

```

Figure 3.2: Example showing source code and it's binary code

provably always an induction variable in it's immediately enclosing loop. Of course, it is a derived induction variable [32], derived from the basic induction variables like i and j in source<sup>1</sup>.

Analyzing the control flow graph that we obtain from a binary can help us recognize loops in a binary. Every back edge in the control flow graph defines a loop [32]. We know that the address of every affine access in the body of the loop is a derived induction variable. In the binary code in figure 3.2, addr\_reg is the address register, which must be an induction variable since it came from an affine access in source. It would not be an induction variable if it was not an affine access in source. We must first check that all memory accesses in the loop are induction variables, for this loop to have been an affine loop in source. Starting from this address induction variable addr\_reg, we can define the following six special statements in the binary ((A) to (F)) for every address variable in a loop that is an induction variable. These six statements will help us parallelize the binary, regardless of the exact binary code:

- (A) Address variable increment: The rewriter searches for the increment of the address induction variable in the loop, and names it (A). See the example binary in figure 3.2 to find (A) to (F).

- (B) Address variable lower bound: The incoming value of the address induction variable (addr\_reg in the example) is its lower bound; it is marked

(B).

<sup>&</sup>lt;sup>1</sup>Basic induction variables are those, which are incremented by a constant every loop iteration. A derived induction variable d is of the form  $d = c_1 \times i + c_2$ , where i is a basic or derived induction variable with step s; hence d too is an induction variable with step  $c_1 \times s$ .

- (C) Address variable upper bound: The upper bound comparison of the address variable for the loop-ending branch identifies the upper bound of the address variable. It is searched for and marked (C).

- (D) Outer loop induction variable increment: We check if statement

(B)'s right-hand side value contains another induction variable. If it does, it is

distinguished as the induction variable of the next-outer loop. In the example

it is i'. The increment which reveals this induction variable is marked (D).

- (E) Outer loop induction variable lower bound: The incoming value

of the outer loop induction variable (i' in the example) is its lower bound; it

is marked (E).

- (F) Outer loop induction variable upper bound: The upper bound comparison of the outer loop induction variable for the loop-ending branch identifies the upper bound of the address variable. It is searched for and marked (F).

Statements (A) to (C) are for the inner loop; and (D) to (F) are for the outer loop, if present. For loops nested to depth three or more, additional statements can be identified (e.g. (G) to (I) and so on). These special statements can be identified from almost any binary compiled from affine accesses, regardless of its exact form. Recognizing statements (A) to (F) in the binary relies primarily on effective induction variable analysis, which is easy for registers in binaries. By the definition of an induction variable, once it is recognized, its increment (or set of

increments) reveal the statements (A) and (D). The incoming values ((B) and (E)) immediately follow, as well as the exit conditions ((C) and (F)).

Our recognizer will recognize not only virtually all affine accesses written as such, but also affine accesses through pointers, since the pointers themselves will be induction variables. The only non-recognized case is when the constant increment of the induction variable is hidden by layers of indirection, e.g. when the constant is in a memory location, or when the induction variable is not virtual-register-allocated in the binary rewriter's intermediate representation, but we have found such cases to be extraordinarily rare.

Let us now describe our procedure to derive address variable equations directly from a binary.

For a two-dimensional loop, consider an affine memory reference in a binary loop inside loop dimension 2, where loop dimensions are counted from outermost (1) to innermost (2). Let addr\_reg be the address variable of this memory reference, which must be an induction variable for an affine access. From the binary code shown in figure 3.2 we can define the address variable's lower bound value (RHS of (B)) as Initial\_addr\_reg. Since, this is the lower bound to the induction variable in the innermost loop, it will be a loop-invariant quantity in the innermost loop. If the access was indeed affine in the original source code (which we do not have access to), then from applying row-major ordering to the access, it must be the case that:

$$Initial\_addr\_reg = Base + i \times size\_j + lb_j \times elem\_size$$

(3.4)

In the binary, however, the above formula is not necessarily evident. What we do know is that for induction variable addr\_reg, from the definition of an induction variable with loop-entry value Initial\_addr\_reg, we get:

$$addr_reg = Initial_addr_reg + num_j \times step_i$$

(3.5)

where num\_j is the number of iteration of the j loop executed so far, and step<sub>j</sub> is the step of the induction variable. Substituting eq.(3.4) into eq.(3.5) we get:

$$addr\_reg = Base + i \times size\_j + lb_j \times elem\_size + num\_j \times step_j$$

(3.6)

We know that the number of iterations  $num_i = i - 1b_i$ . Hence,  $i = num_i + 1b_i$ . Substituting this in eq.(3.6) we get:

$$\texttt{addr\_reg} = \texttt{Base} + \texttt{lb_i} \times \texttt{size\_j} + \texttt{lb_j} \times \texttt{elem\_size} + \texttt{num\_i} \times \texttt{size\_j} + \texttt{num\_j} \times \texttt{step_j}$$

$$(3.7)$$

Since the first three terms of the RHS are constants, we rename their sum as Base<sub>outer</sub> since they are the loop-entry value of outer loop address variable. Hence:

$$\texttt{addr\_reg} = \texttt{Base}_{\texttt{outer}} + \texttt{num\_i} \times \texttt{size\_j} + \texttt{num\_j} \times \texttt{step_j} \tag{3.8}$$

Comparing eq.(3.5) with eq.(3.8), we can now back out the value of Initial\_addr\_reg in the binary:

$$Initial\_addr\_reg = Base_{outer} + num\_i \times size\_j$$

(3.9)

We will now prove that  $Initial_addr_reg$  is an induction variable in the outer i loop. To do so, we prove that the value of  $Initial_addr_reg$  for  $num_i vs (num_i + 1)$  is a constant value, which is the characteristic of an induction variable. Substituting  $(num_i + 1)$  in eq.(3.9), we get:

$$Initial\_addr\_reg_{num\_i+1} = Base_{outer} + (num\_i + 1) \times size\_j$$

(3.10)

subtracting eq.(3.10) - eq.(3.9) yields:

$$step_{i} = size_{-j} \tag{3.11}$$

since by definition  $step_i = Initial_addr_reg_{num_i+1} - Initial_addr_reg_{num_i}$ . Substituting eq.(3.11) in eq.(3.8) yields:

$$addr\_reg = Base_{outer} + num\_i \times step_i + num\_j \times step_j$$

(3.12)

Generalizing this to an n-dimensional loop yields:

$$\mathtt{addr\_reg} = \mathtt{Base_{outer}} + \sum_{k=1}^{n} \mathtt{num\_k} \times \mathtt{step_k} \tag{3.13}$$

This is an important equation since it will help us derive dependence vectors next. An equation of the form eq.(3.13) is constructed by our binary rewriter for every memory reference for which special statements (such as (A) to (F) in the two-dimensional loop case) can be identified. In particular, the Base<sub>outer</sub> value is constructed from statement (E), whereas the step values of the inner and outer loop are found from statements (A) and (D), respectively. Memory references for which such special statements cannot be found are assumed to be non-affine, and are not analyzed further.

Deriving dependence vectors Next we aim to define the dependence vector between pairs of array accesses in the loop. To do so, we consider any two derived induction variable references in a loop (not necessarily the two in the code example above) with addresses addr\_reg1 and addr\_reg2. Their expressions would be the following:

$$\mathtt{addr\_reg_1} = \mathtt{Base_{outer1}} + \sum_{k=1}^{n} \mathtt{num\_k} \times \mathtt{step_{1k}} \tag{3.14}$$

$$addr\_reg_2 = Base_{outer2} + \sum_{k=1}^{n} num\_k' \times step_{2k}$$

(3.15)

After deriving these equations, the next step is to calculate the distance vector (d1, d2, ..., dn) associated with these accesses. Say that (num\_1, num\_2, ..., num\_n) and (num\_1', num\_2', ..., num\_n') are the iterations where add\_reg\_1 and addr\_reg\_2 alias to the same memory location, then by definition (num\_1 - num\_1', ... num\_n - num\_n') is the distance vector associated with these accesses <sup>2</sup>. Hence, to calculate this distance vector we need to equate the R.H.S of eq.(3.14) and eq.(3.15). The unknowns in the equation are num\_1, num\_2, ..., num\_n, num\_1', num\_2', ... and num\_n'. We now have 2n unknowns and one equation. But we also have the following bounds for these unknowns, as they are the number of iterations of loop dimensions.

$$0 \leq \text{num\_k}, \text{num\_k}' \leq \lfloor \frac{ub_k - 1b_k}{\text{step}_{1k}} \rfloor \quad \forall k \in [1:n] \tag{3.16}$$

We derive these bounds from the special induction variable statements in the binary (statements (B), (C), (E), (F) in the two-dimensional loop case.). For loops nested with higher depths there will be statements (H), (I), ... to determine the bounds. We now solve for the distance vectors using the equation and bound conditions. One of the following four conditions may happen:

There is no solution to this equation in the given space. This means that the

two addresses do not alias with one another. We add a distance vector of (0,

0, . . .) to this loop.

<sup>&</sup>lt;sup>2</sup>Distance vectors need to be lexicographically positive, hence if  $(num_1 - num_1')$  is negative then the distance vector is  $(num_1' - num_1, num_2' - num_2, ..., num_n' - num_n)$

- There is a deterministic solution (d1, d2, . . ., dn). Then we add this to the distance vectors of the loop.

- There are multiple deterministic solutions to this equation. Then we add all the deterministic solutions to the distance vectors of this loop.

- In all other cases, when there are uncountable many solutions or when we are unable to determine the solution, the direction vector added has elements per loop dimension that are a combination of < , > , = and \* [7]depending on the dimension that is uncountable and the direction in which it is uncountable.

Traditional affine theory defines the (Greatest Common Divisor) GCD test [14, 15], Banerjee test [13], Delta Array tests [16] and the Single Index Variable (SIV) and Multiple Index Variable (MIV) tests [13] [6] to solve the linear equations that we derive from source. We use the same techniques to solve the equations from low-level code. Multiple tests have been defined as the techniques evolved to more precise solutions in increasing order of complexity.

If the bounds of the loop are unknown we can still say something about these equations in the infinite space. But of course this is not always true. Hence, we have developed techniques specific to a binary in case of unknown bounds and these are presented in chapter 4.

The techniques presented in this section are different from source in the following way:

• The equations to be solved are directly derived from the binary as against the

symbolic array index expressions readily available from source but absent in binaries.

• From source we derive the distance vectors by solving each dimension separately, where as from binary we derive the equations equivalent to linearizing the array. We do this since there is no symbolic information in the binary to determine array bounds and dimensions. We have found that these techniques are nearly as powerful as source techniques on the Polybench benchmark suite. We have been able to discover the same dependence vectors from source as well as the corresponding binaries. In extremely rare cases, the dependence vectors from binaries are less precise than from source, but still conservative and correct. This impact is measured in chapter 7.

# 3.2 Examples

In this section we briefly apply the theory described in section 3.1 to four code examples to show how their loops will be parallelized from a binary without any symbolic information.

int A[20,50]

int B[20,50]

int A[20,50]

int A[20,50]

for  $i = 0 \rightarrow 19$  step 1

for  $j = 0 \rightarrow 49$  step 1 B[i,j] = A[i,j] + 10for  $j = 0 \rightarrow 47$  step 1 A[i,j] = A[i,j+2] + 10(a) Example 1

(b) Example 2

Example 1: The memory address expressions that we recover from the binary above will be of the form  $Base_A + 200i + 4j$  and  $Base_B + 200i + 4j$  (Assuming that the size of an integer is 4.).  $Base_A$  and  $Base_B$  will at least differ by 4000, since the size of each array is 4000 bytes. Without loss of generality lets assume we recover the following equations from the binary 100 + 200i + 4j and 4100 + 200i + 4j.

When the code above is compiled to a stripped binary, symbolic information is lost. Hence we no know longer the location or dimension sizes (20, 50) of array A. However, we can also infer from binary code that the bounds of loop i is [0,19] and the bounds of loop j is [0,49].

Next, we apply the standard dependence tests to the set of equations we recovered 100 + 200i + 4j and 4100 + 200i + 4j within the ranges  $0 \le i \le 19$  and  $0 \le j \le 49$ . The dependence tests reveal that both these memory expressions will accesses different memory locations in the iteration space, *i.e.* in other words no two iterations ever access the same location. Hence, the distance vector for this loop is (0,0) directly from binary code. We can now parallelize any dimension of the loop nest. We decide to parallelize the outer most loop dimension *i.e.* loop i.

Example 2: The memory address expression that we recover from the binary will be of the form  $Base_A + 400i + 4j$  and  $Base_A + 8 + 400i + 4j$ . Without loss of generality, lets assume that  $Base_A$  is 200, then the expressions that we recover from the binary will be 200 + 400i + 4j and 208 + 400i + 4j (assuming that the element size is 4). The ranges we discover for i is [0,19] and j is [0,47].

Next, we apply the dependence tests to this set of equations within the ranges discovered from the binary. Note that these were discovered directly from the binary without using any symbolic information that a source compiler would use. The dependence tests reveal that every two iteration of j accesses the same memory location as two iterations before this one *i.e.* the distance vector for this loop is (0,2). The distance vector reveals that the outer loop is parallel, hence we parallelize the outer loop i of the loop nest.

Example 3: The equations we will recover from the binary will be  $Base_A + 4i$  and  $Base_A + 200 + 4i$ . Without loss of generality lets assume that  $Base_A$  is 1000, then the expressions for memory that we recover directly form the binary will be 1000 + 4i and 1200 + 4i. The range for i that is discovered from the binary is [0,49]. Using the dependence tests we discover that both these address expressions do not accesses the same memory location in any two iterations in the given iteration space. Hence, the distance vector associated with this loop is (0). After we have calculated the distance vector we parallelize the i loop of the loop nest.

Example 4: The equations we will recover from the binary will be  $Base_A + 8i$  and  $Base_A + 4 + 8i$ . Without loss of generality lets assume that  $Base_A$  is 100, then the expressions that are recovered from the binary are 100 + 8i and 104 + 8i and the range for i is [0,49]. Using the dependence tests we discover that no two iterations

every access the same memory location again. Hence, the distance vector associated with this loop is (0). After we have calculated the distance vector we infer that loop i does not carry a dependence and hence can be parallelized.

### Chapter 4

### Run time dependent loop bounds

In this chapter we first describe the best-known methods for obtaining distance vectors from source code for affine loops with run-time determined loop bounds. We then present the limitations of the binary method presented in chapter 3 for the same and then describe our algorithm.

int A[20,50]

for  $i = 0 \rightarrow ub_i$  step 1

for  $j = 0 \rightarrow ub_j$  step 1

A[i,j] = A[i,j] + 10

The code shows a normalized loop, i.e.a loop with a lower bound of zero and a step of one. Loops can be normalized using existing methods such as the normalization pass in LLVM.

Figure 4.1: Code Example to motivate the algorithm to guess loop bounds for loops with run-time dependent loop bounds

Distance vectors from source code for the loop in figure 4.1 are calculated as follows. From source, existing methods make the assumption that row and column accesses are within the bounds of the array's dimensions. They solve for two iterations that refer to the same memory location within bounds for an infinite range of iteration values. If no solution exists, like in this example, we can conclude that no two iterations ever access the same memory. This implies that iterations of the j loop can execute in parallel (i.e., the component of the distance vector for this loop

is zero.) Such an analysis individually proves that the loop i is parallel.

To obtain distance vectors from binary for this code we cannot use the above source method since it relies on known affine expressions for array indexes in terms of induction variables, which are not apparent from the binary. Instead we start with the method for binaries in chapter 3. We showed that we can recover linearized expressions for memory accesses from a binary, and solving these multidimensional expressions gives us dependence vectors. In the presence of loop bounds the solutions from binaries are very powerful, and can handle most linear algebraic kernels as presented in chapter 3. However, when loop bounds are run-time dependent, we need to solve these multi-dimensional expressions in the infinite space (since we need to assume that the loop bounds can take any value at run-time). This greatly reduces the precision of the analysis.

For e.g., let us apply the binary method from chapter 3 to the loop in figure 4.1. From the binary for the code above we will recover a memory expression of the form  $Base_A + 200i + 4j$  which corresponds to the A[i, j] access (assuming the element size is 4). The "200" in 200i is because the size of a row is 50 elements, each of 4 bytes. We need to reason about this access in the infinite space for i and j since the loop bounds are unknown. In the infinite space, iterations (2,0), (1, 50) and (0, 100) refer to the same memory location. All of these iterations except (2,0) are not possible because the legal range of j is [0,49] and if it is greater than 49 the code accesses columns out of bounds, and thus wrapping into rows. Source code methods assume that such iterations are not possible; hence proving the loop is parallel. However, unlike source methods, the binary method in chapter 3 cannot make any

assumptions about iterations remaining within array bounds, since differentiated array bounds are not known from binary code. As a result, without loop bounds, the binary method from chapter 3 fails to prove the loop is parallel because of the false loop-carried dependences that appear.

In this chapter we present a method to statically guess the most likely upper bounds of loops with unknown loop bounds. We then check the loop bounds at run-time, and run the parallel version of the loop if the loop bounds were indeed with in the ranges that we guessed. For e.g. for the loop shown in figure 4.1, using the theory presented in chapter 3 we discover the memory expression for the A[i][j] access to be  $Base_A + 200i + 4j$ . We then look at the coefficients multiplying the induction variables in this memory expression that we recover from the binary and guess the likely limit of the induction variable with the smallest coefficient (i.e. j in this example, since its coefficient 4 is smaller than the coefficient of i 200) as the immediately higher coefficient divided by the coefficient of this induction variable; *i.e.* in this example we guess the limit on j as (Coefficient of i/Coefficient of j)  $(i.e.\frac{200}{4} = 50)$ . By guessing that j is less than 50 no two iterations will access the same memory because now j has been prevented to run into i and we can parallelize the loop. At run-time we check if j indeed does not exceed 50 and this run-time check will always succeed and we will always execute the parallel version of the loop.

In the following section 4.1 we present more examples and briefly describe how our algorithm would guess loop bounds for them followed by the detailed algorithm in section 4.2. Within these bounds for the induction variables the loop is parallel in most cases. We insert run-time checks to check that these guesses were indeed correct before executing the parallel version of the loop; else, we execute the serial version of the loop. The run-time check is necessary for binary code since our guesses may be incorrect in some cases. We show one such example in section 4.1. However, this does not hurt us since that loop was actually serial in the original source code and the loop bounds we guess represent the parallel region.

#### 4.1 Examples

In this section we first briefly describe the steps of the algorithm described in section 4.2 and then apply it to four code examples to show how their loops can be parallelized from a binary even though the loop bounds are run-time dependent.

First, we state the algorithm that we use to guess the upper loop bounds for a loop directly from a binary. Only the steps are outlined here, details in section 4.2.

**Step 1:** Divide memory accesses (both reads and writes) in a loop into De- $pendence\ Groups\ (DGs)$ . Intuitively, a DG is a subset of memory addresses in the

loop that are sufficiently close to one another.

- $\mbox{\bf Step 2:} \ \mbox{Arrange all DGs in ascending order of their base addresses, from $DG_1$ } \\ \mbox{to $DG_T$}.$

- **Step 3:** For all the DGs that have writes in them make best guesses for the possible range for induction variables. These guesses are called intra-group constraints, since they are obtained by working on one DG at a time.

- **Step 4:** Initiate a worklist by all DGs with constraints remaining after step 3.

**Step 5:** Work on each  $DG_i$  in the worklist and solve for the values of induction variables such that the accesses in  $DG_i$  do not overlap with those in  $DG_{(i+1)}$ . This generates further guesses on the induction variables. Merge these new constraints with existing constraints for the same induction variable by choosing the minimum. These guesses are called inter-group constraints because they are obtained by constraining  $DG_i$  to not overlap  $DG_{(i+1)}$ .

Figure 4.2: Example 1 & 2 to illustrate the algorithm to guess loop bounds

Example 1: The memory address expressions that we recover from the binary above will be of the form  $Base_A + 200i + 4j$  and  $Base_B + 200i + 4j$  (Assuming that the size of an integer is 4.).  $Base_A$  and  $Base_B$  will at least differ by 4000, since the size of each array is 4000 bytes. Without loss of generality lets assume we recover the following equations from the binary 100 + 200i + 4j and 4100 + 200i + 4j.

When the code above is compiled to a stripped binary, symbolic information is lost. Hence we no know longer the location or dimension sizes (20, 50) of array A. Hence we can no longer infer (as we implicitly do from source) that  $\mathtt{ub_i}$ ; 20 and  $\mathtt{ub_j}$ ; 50. Instead maximum values of these bounds of the loops must be inferred.

We now show briefly how our algorithm is applied to these accesses to guess the bounds on i and j. In Step 1, we check to see if the accesses belong to different DGs. The heuristic we use is that the difference of the bases is greater than a factor (5 for our experiments) of the highest coefficient; i.e.  $Base_B - Base_A > 5 \times 200$  $i.e.(4100-100) > 5 \times 200$ . As this is true both the accesses will belong to different DGs. In Step 2, we arrange the DGs in ascending order of their bases.  $100+200 \mathtt{i}+4\mathtt{j}$  belongs to  $\mathtt{DG_1}$  because its base is lower than the second access which belongs to DG<sub>2</sub>. In Step 3, we solve for intra-group constraints in DG<sub>2</sub> since it contains a write. We guess the bound on j by dividing the co-efficient multiplying i (the just higher co-efficient in the linearized equation) by the co-efficient of j  $i.e.(\frac{200}{4})$ = 50). Hence, we guess that j must belong to [0, 49]. In step 4, we create a worklist with all DGs that have constraints remaining. In this example both the DGs have constraints remaining on i; hence both of them will belong to the worklist. In step 5, we guess the bound on i by solving that  $DG_1$  i.e. 100 + 200i + 4j does not overlap with  $DG_2$  *i.e.* 4100 + 200i + 4j given the highest possible value for j is 49; i.e.100 + 200i + 4 \* 49 < 4100. Hence, i must be less than 19.02 or in the range [0, 19]. Since DG<sub>2</sub> is the highest DG we do not solve for it overlapping with any other DG.

After we have applied our algorithm to this loop, our guess for i is [0,19] and j is [0,49]. We now solve for dependencies within this range for the loop and discover that the loop can be parallelized. We also add lightweight run-time checks before the parallel version of the loop (which will always succeed for this loop).

Example 2: The memory address expression that we recover from the binary will

be of the form  $\mathtt{Base_A} + 400\mathtt{i} + 4\mathtt{j}$ . Since there is only one access, step 1 and 2 will result in placing it in  $\mathtt{DG_1}$ . In step 3, we guess that the bound of  $\mathtt{j}$  is  $(\frac{400}{4} = 100)$  or the range of j is guessed to be [0, 99]. There would be no step 4 and 5 for this loop since there is only one  $\mathtt{DG}$ .

Next we calculate dependencies assuming the range of j is [0,99] and i can take any value and discover that the loop can be parallelized. In reality however the range of j will not exceed [0, 49]. But our larger discovered bounds work well since even if they did exceed 49 and be below 99 this loop can still be parallelized. i.e if the programmer decided to access two rows using a column increment (which most programmers do not do) it is still a parallel loop. From the binary this means that we see a A[20, 50] array as a A[10, 100] array. However, this is fine as we reason about the dependencies in the correct way and parallelize the loop only when our run-time checks succeed.

Figure 4.3: Example 3 & 4 to illustrate the algorithm to guess loop bounds

Example 3: The equations we will recover from the binary will be  $Base_A + 4i$  and  $Base_A + 200 + 4i$ . After step 1, we will place them in different DGs since the difference between the bases (200) is greater than 5 times the highest co-efficient 4. After

arranging the DGs in ascending order in step 2,  $Base_A + 4i$  will belong to  $DG_1$  and  $Base_A + 200 + 4i$  will belong to  $DG_2$ . No intra-group guesses are calculated in step 3 since the recovered equations are single dimensional. After step 4, the worklist is populated with both the DGs since both contain i for which there is no guess as yet. In step 5, we solve for inter-group guesses such that  $DG_1$  does not overlap with  $DG_2$ , i.e.4i < 200 or i < 50. Hence, the range we guess for i is [0,49] which is also the actual limit on i from source. The run-time check will always succeed in binary code and we will execute the parallel version of this loop. This is correct because, regardless of the value of  $ub_i$ , the two array references access non-intersecting portions of the array. Our method correctly treats these non-intersecting portions as different DGs.