### ABSTRACT

| Title of dissertation:    | Symbiotic Subordinate Threading (SST)                               |

|---------------------------|---------------------------------------------------------------------|

|                           | Rania Mameesh, Doctor of Philosophy, 2007                           |

| Dissertation directed by: | Dr Manoj Franklin<br>Electrical and Computer Engineering Department |

Integration of multiple processor cores on a single die, relatively constant die sizes, increasing memory latencies, and emerging new applications create new challenges and opportunities for processor architects. How to build a multi-core processor that provides high single-thread performance while enabling high throughput through multi-programming? Conventional approaches for high single-thread performance use a large instruction window for memory latency tolerance, which requires large and complex cores. However, to be able to integrate more cores on the same die for high throughput, cores must be simpler and smaller.

We present an architecture that obtains high performance for single-threaded applications in a multi-core environment, while using simpler cores to meet the high throughput requirement. Our scheme, called Symbiotic Subordinate Threading (SST), achieves the benefits of a large instruction window by utilizing otherwise idle cores to run dynamically constructed subordinate threads (a.k.a. *helper threads*) for the individual threads running on the active cores.

In our proposed execution paradigm, the subordinate thread fetches and pre-

processes instruction streams and retires processed instructions into a buffer for the main thread to consume. The subordinate thread executes a smaller version of the program executed by the main thread. As a result, it runs far ahead to warm up the data caches and fix branch miss-predictions for the main thread. In-flight instructions are present in the subordinate thread, the buffer, and the main thread, forming a very large effective instruction window for single-thread out-of-order execution. Moreover, using a simple technique of identifying the subordinate thread non-speculative results, the main thread can integrate the subordinate thread's nonspeculative results directly into its state without having to execute their corresponding instructions. In this way, the main thread is sped up because it also executes a smaller version of the program, and the total number of instructions executed is minimized, thereby achieving an efficient utilization of the hardware resources. The proposed SST architecture does not require large register files, issue queues, load/store queues, or reorder buffers. In addition, it incurs only minor hardware additions/changes. Experimental results show remarkable latency-hiding capabilities of the proposed SST architecture, outperforming existing architectures that share similar high-level microarchitecture.

We performed two extensions of our SST scheme, and came up with two additional microarchitectures. In the first extension, we developed a simple way to allow the subordinate thread be aware of its own speculation. A speculative-aware subordinate thread is capable of identifying instructions that are more likely to produce invalid values, and so may skip their execution. In the second extension, we allow a subordinate thread to have its own subordinate thread. The main thread and multiple subordinate threads are arranged in a hierarchy based on the degree of their speculation, with the most speculative subordinate thread at the bottom of the hierarchy and the least speculative thread (the main thread) at the top of the hierarchy. This new microarchitecture, named Hierarchical Symbiotic Subordinate Threading, combines the benefit of the speed of highly speculative subordinate threads with the accuracy of not-too-speculative subordinate threads.

# Symbiotic Subordinate Threading (SST)

by

Rania Mameesh

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2007

Advisory Committee:

Dr Manoj Franklin, Chair/Advisor Dr Amr Baz Dr Charles Silio Dr Donald Yeung Dr Peter Petrov © Copyright by Rania Mameesh 2007

# ACKNOWLEDGMENTS

I owe my gratitude to all the people who have made this thesis possible and because of whom my graduate experience has been one that I will cherish forever.

First and foremost I'd like to thank my advisor, Professor Manoj Franklin for giving me an invaluable opportunity to work on challenging and extremely interesting projects over the past five years.

I would also like to thank my committee members, Dr Amr Baz, Dr Charles Silio, Dr Donald Yeung, and Dr Peter Petrov for agreeing to serve on my thesis committee and for sparing their invaluable time reviewing the manuscript.

I owe my deepest thanks to my family - my parents and brother who have always stood by me and guided me through my career, and have pulled me through against impossible odds at times. Words cannot express the gratitude I owe them.

It is impossible to remember all, and I apologize to those I've inadvertently left out.

Lastly, thank you all and thank God!

# TABLE OF CONTENTS

| Li | st of                                                     | ables                                                                                                                                                                                                                                                                                                                                                                                                                               | vi                                              |

|----|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Li | st of                                                     | igures                                                                                                                                                                                                                                                                                                                                                                                                                              | vii                                             |

| 1  | <b>Int</b><br>1.1<br>1.2<br>1.3                           | duction<br>Motivation                                                                                                                                                                                                                                                                                                                                                                                                               | <b>1</b><br>1<br>4<br>7                         |

| 2  | <ul><li>Bac</li><li>2.1</li><li>2.2</li><li>2.3</li></ul> | 2.1.1       Motivation for Building Single-Chip Multiprocessors                                                                                                                                                                                                                                                                                                                                                                     | 8<br>9<br>11<br>14<br>15<br>16<br>17<br>19      |

| 3  |                                                           | A Simple Methodology for Distilling The Subordinate Thread2A Simple and Efficient Way of Pruning The Main Thread23.2.1 Basic Idea23.2.2 Skipping Non-Memory Instructions23.2.3 Skipping Memory Accesses (Only LOAD Instructions)23.2.4 An Example2Communicating Subordinate Thread Results and Decoded Information to the Main Thread2Putting it All Together: The SST Microarchitecture23.4.1 Basic Operation23.4.2 Memory System2 | 25 $29$ $29$ $30$ $32$ $34$ $41$ $43$ $44$ $45$ |

| 4  | <b>Exp</b> 4.1                                            | <ul> <li>Performance Evaluation of SST Against Slipstream Processor 4</li> <li>4.1.1 Average IPC Improvement of SST</li></ul>                                                                                                                                                                                                                                                                                                       | <b>47</b><br>49<br>50<br>52<br>54<br>56<br>57   |

|   |      | 4.1.6 Improvement in the Main Thread L1 DCache Miss Rate         | 59       |

|---|------|------------------------------------------------------------------|----------|

|   | 4.0  | 4.1.7 Reduction in the Main Thread Branch Miss-predictions       | 60       |

|   | 4.2  | Performance Evaluation of SST Against DCE                        | 63       |

|   |      | 4.2.1 IPC Improvement of SST without Memory Symbiosis (100       |          |

|   |      | Cycles for Main Memory Access)                                   | 64       |

|   |      | 4.2.2 IPC Improvement of SST with Memory Symbiosis (100 Cycles   | <b></b>  |

|   |      | for Main Memory Access)                                          | 65       |

|   |      | 4.2.3 IPC Improvement of SST with Memory Symbiosis (300 Cycles   | 00       |

|   |      | for Main Memory Access)                                          | 66<br>60 |

|   |      | 4.2.4 Reduction in the Subordinate Thread L2 Cache Miss Rate     | 68       |

| 5 | An   | Optimized Implementation of SST                                  | 70       |

|   | 5.1  | A Partially Speculative-Aware Subordinate Thread                 | 71       |

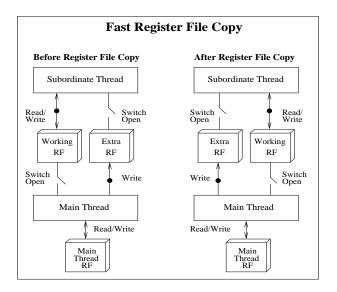

|   | 5.2  | The Subordinate Thread Recovers from Miss-Speculation By Switch- |          |

|   |      | ing Roles with the Main Thread                                   | 75       |

|   | 5.3  | New SST Microarchitecture                                        | 79       |

|   | 5.4  | Experimental Results                                             | 79       |

|   |      | 5.4.1 IPC Improvement                                            | 82       |

|   |      | 5.4.2 Branch Miss-predictions in The Main Thread                 | 84       |

|   |      | 5.4.3 Branch Miss-predictions in the Subordinate Thread          | 85       |

|   |      | 5.4.4 L2 Cache Miss Rate                                         |          |

|   |      | 5.4.5 Reduction in the Total Number of Executed Instructions     | 88       |

| 6 | HSS  | $\overline{v}$ $\overline{0}$                                    | 91       |

|   | 6.1  | 0 1                                                              |          |

|   | 6.2  | Implementation Details of HSST                                   |          |

|   |      | 6.2.1 Spawning Subordinate Threads                               |          |

|   |      | 6.2.2 Distilling the Subordinate Thread                          |          |

|   |      | 6.2.3 Result Integration                                         |          |

|   |      | 6.2.4 Recovering the Subordinate Thread Corrupted State 1        |          |

|   | 6.3  | Experimental Results                                             |          |

|   |      | 6.3.1 Performance Improvement                                    |          |

|   |      | 6.3.2 Advantages of Result Integration                           |          |

|   |      | 6.3.3 Improvement in L2 Cache Miss Ratio                         |          |

|   |      | 6.3.4 Experimenting with More than Two Subordinate Threads 1     | 115      |

| 7 | Rela | ated Work 1                                                      | .17      |

|   | 7.1  | SST and Run-ahead execution                                      | 117      |

|   | 7.2  | SST and Leader/Follower Architectures                            | 120      |

|   | 7.3  | SST and Result Reuse                                             | 125      |

|   | 7.4  | SST and Clustered Architecutures                                 | 126      |

| 8 | Fut  | ure Work 1                                                       | .27      |

|   | 8.1  | Making the Fastest Thread the Leader                             | 197      |

|   | 0.1  | Making the Pastest Thread the Leader                             | 121      |

|   | 8.2  | Hybrid HSST Processor                                            |          |

|                 | 8.3 | Exploiting Program Behavior Changes Using Dual Thread Execution |

|-----------------|-----|-----------------------------------------------------------------|

|                 |     | Models                                                          |

|                 | 8.4 | Division of Work                                                |

|                 | 8.5 | Power Studies                                                   |

|                 | 8.6 | Simulation Work                                                 |

| 9               | Sun | mary and Conclusions 133                                        |

| Bibliography 13 |     |                                                                 |

# LIST OF TABLES

| 4.1 | Microarchitectural Simulation Parameters For Smaller Cores 48 |

|-----|---------------------------------------------------------------|

| 4.2 | Microarchitectural Parameters with Larger Cores               |

| 5.1 | Microarchitectural Simulation Parameters for Old & New SST 81 |

| 6.1 | HSST Microarchitectural Parameters                            |

| 6.2 | Superscalar Microarchitectural Parameters                     |

# LIST OF FIGURES

| 3.1 | SST top level design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Identifying the backward slice of a branch instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |

| 3.3 | RSB update scenarios.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

| 3.4 | MSB addressing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 |

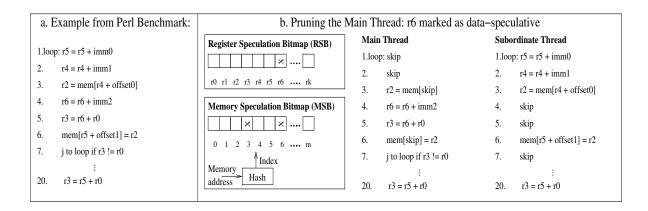

| 3.5 | (a) Loop example from benchmark <i>perl</i> ; (b) Example of reducing the number of executed instructions by the main thread.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

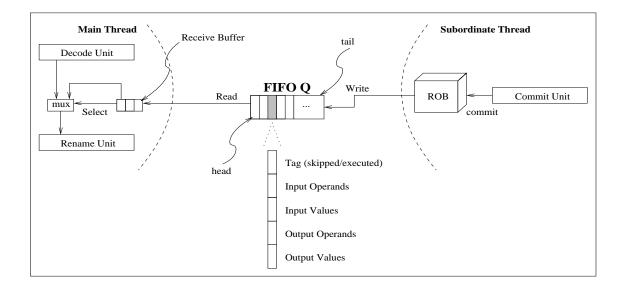

| 3.6 | FIFO queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38 |

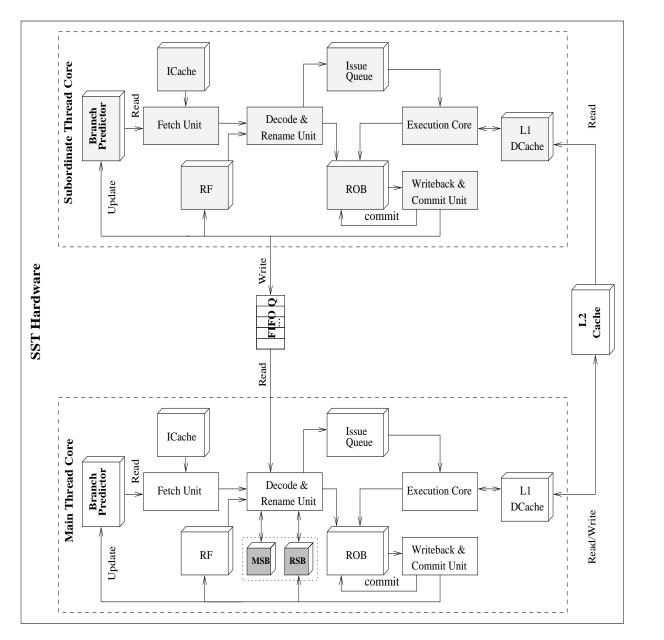

| 3.7 | SST microarchitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

| 3.8 | Fast recovery of the subordinate thread state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

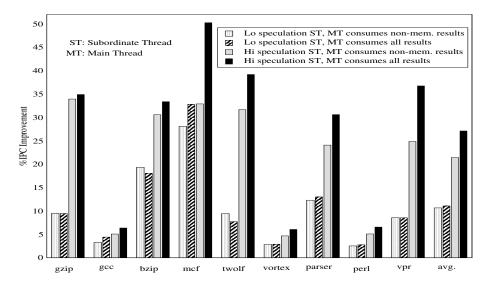

| 4.1 | % IPC improvement achieved with symbiotic subordinate threading (SST) over the slipstream processor (main thread does not skip in-<br>structions). (a) SST with low speculation subordinate thread, and<br>main thread does not skip load instructions; (b) SST with low spec-<br>ulation subordinate thread, and main thread skips load instructions;<br>(c) SST with high speculation subordinate thread, and main thread<br>does not skip load instructions; (d) SST with high speculation sub-<br>ordinate thread, and main thread skips load instructions sub-<br>ordinate thread, and main thread skips load instructions | 51 |

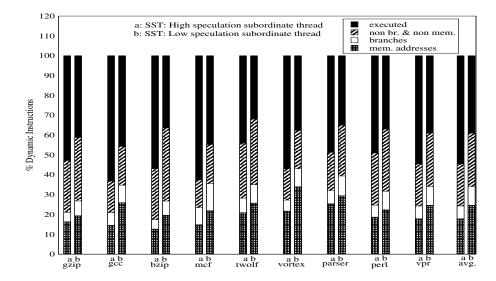

| 4.2 | Instruction distribution in main thread for two schemes: (a) SST with high speculative subordinate thread; (b) SST with not too speculative subordinate thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54 |

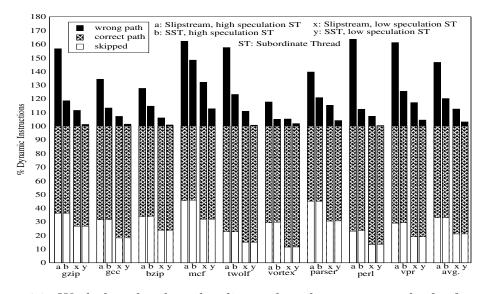

| 4.3 | Work done by the subordinate thread on wrong paths for four schemes:<br>(a) Slipstream with a highly speculative subordinate thread; (b) SST with a highly speculative subordinate thread; (c) Slipstream with a not too speculative subordinate thread; (d) SST with a not too speculative subordinate thread.                                                                                                                                                                                                                                                                                                                 | 55 |

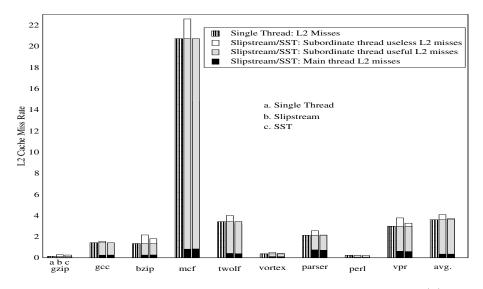

| 4.4 | Distribution of average L2 cache misses obtained with: (a) Single thread; (b) Slipstream processor; and (c) SST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58 |

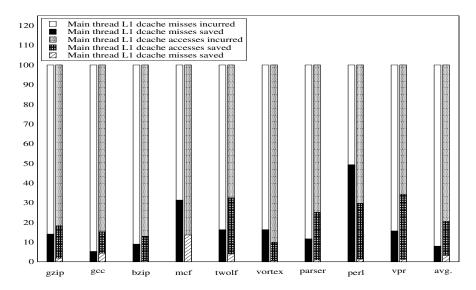

| 4.5 | Main thread L1 dcache: (a) misses incurred and saved with SST when memory symbiosis is applied; and (b) accesses incurred and saved with SST when memory symbiosis is applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60 |

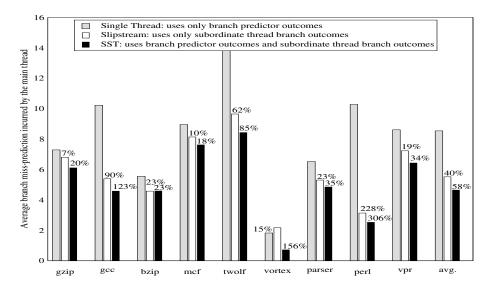

| 4.6  | Main thread % of branch miss-predictions incurred when using: (a) The branch predictions obtained from a branch predictor for all branch instructions (single thread); (b) The branch predictions obtained from the subordinate thread for all branch instructions (slipstream); (c) The non-data-speculative branch outcomes of the subordinate thread, and the predictions obtained from the branch predictor for all other branch instructions (SST). | 62 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

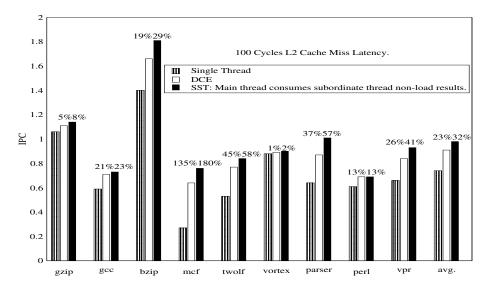

| 4.7  | IPC obtained with memory latency 100 cycles for: (a) Single thread scheme; (b) DCE scheme; and (c) SST scheme (main thread consumes the results of the subordinate thread for only non-memory instructions.                                                                                                                                                                                                                                              | 65 |

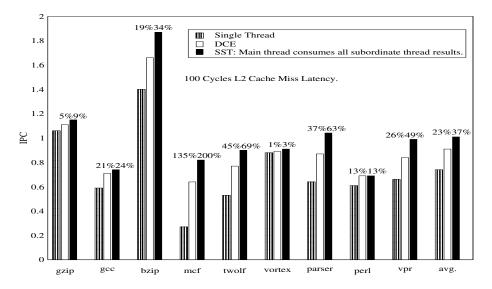

| 4.8  | IPC obtained with memory latency 100 cycles for: (a) Single thread scheme; (b) DCE scheme; and (c) SST scheme (main thread consumes the results of the subordinate thread for all types of instructions).                                                                                                                                                                                                                                                | 66 |

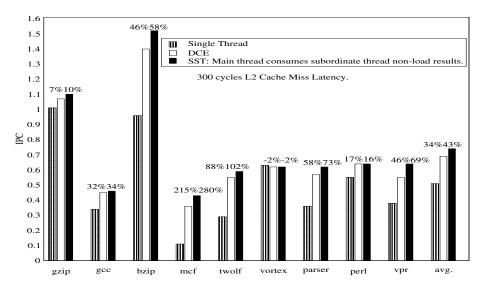

| 4.9  | IPC obtained with memory latency 300 cycles for: (a) Single thread scheme; (b) DCE scheme; and (c) SST scheme (main thread consumes the results of the subordinate thread for only non-memory instructions.                                                                                                                                                                                                                                              | 67 |

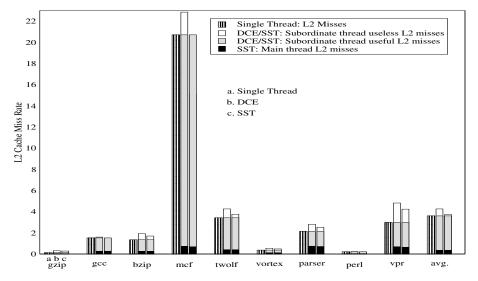

| 4.10 | Distribution of average L2 cache misses obtained with memory la-<br>tency 300 cycles for: (a) Single thread scheme; (b) DCE scheme; and<br>(c) SST scheme (main thread consumes the results of the subordinate<br>thread for only non-memory instructions)                                                                                                                                                                                               | 67 |

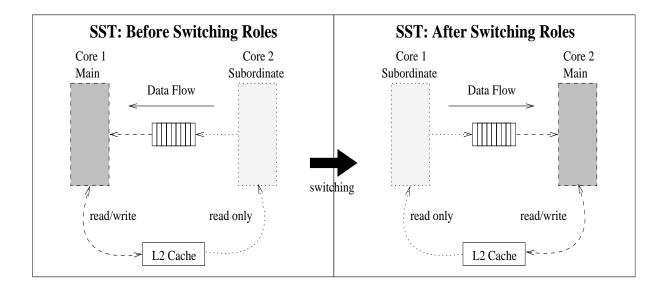

| 5.1  | Subordinate thread and main thread switch roles after recovery of the subordinate thread from miss-speculation                                                                                                                                                                                                                                                                                                                                           | 76 |

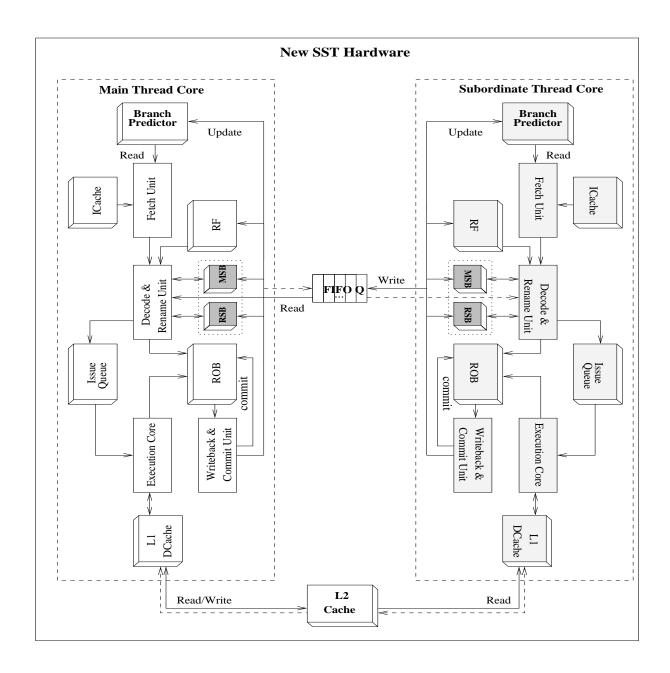

| 5.2  | New SST Microarchitecture.                                                                                                                                                                                                                                                                                                                                                                                                                               | 78 |

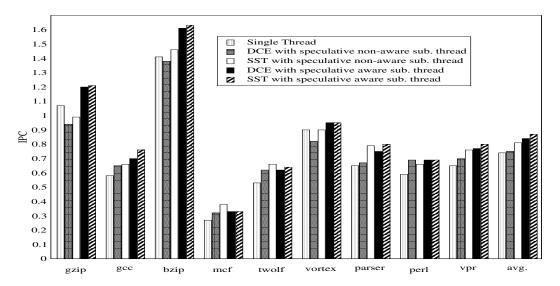

| 5.3  | IPC for 5 schemes: (a) Single thread (a superscalar that combines two cores in one); (b) DCE with speculative unaware subordinate thread; (c) SST with speculative unaware subordinate thread; (d) DCE with speculative-aware subordinate thread; (e) SST with speculative-aware subordinate thread.                                                                                                                                                     | 82 |

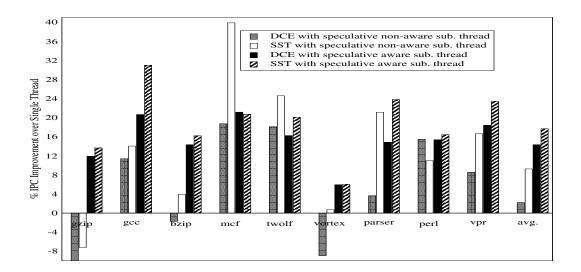

| 5.4  | Percentage IPC improvement over a single thread (a superscalar that combines two cores in one) for four schemes: (a) DCE with speculative unaware subordinate thread; (b) SST with speculative unaware subordinate thread; (c) DCE with speculative-aware subordinate thread                                                                                                                                                                             | 84 |

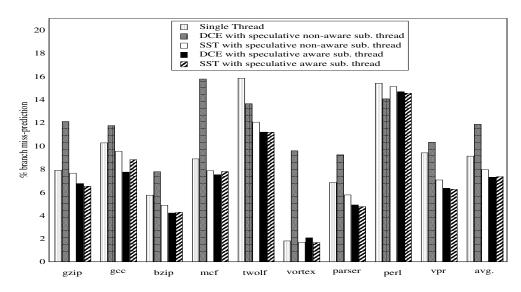

| 5.5 | Percentage branch miss-predictions incurred by the main thread for<br>five schemes: (a) Single thread (a superscalar that combines two<br>cores in one); (b) DCE with speculative-unaware subordinate thread;<br>(c) SST with speculative-unaware subordinate thread; (d) DCE with<br>speculative-aware subordinate thread; (e) SST with speculative-aware<br>subordinate thread | . 86  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

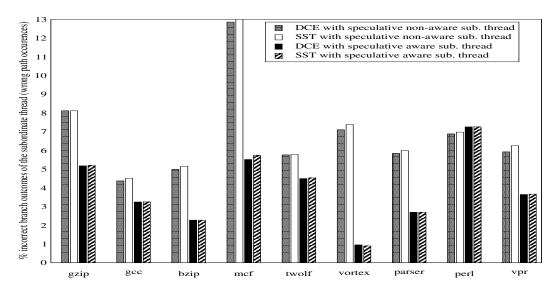

| 5.6 | Percentage of incorrect branch outcomes of the subordinate thread for<br>four schemes: (a) DCE with speculative-unaware subordinate thread;<br>(b) SST with speculative-unaware subordinate thread; (c) DCE with<br>speculative-aware subordinate thread; (d) SST with speculative-aware<br>subordinate thread                                                                   | . 87  |

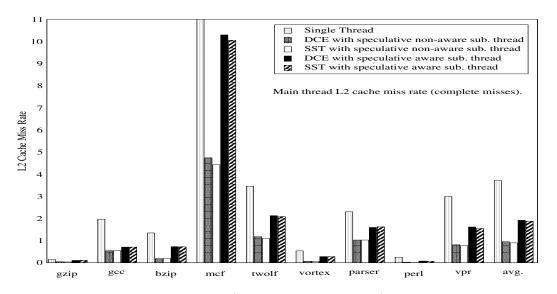

| 5.7 | L2 cache miss rate (only complete misses) in the main thread for<br>five schemes: (a) Single thread (a superscalar that combines two<br>cores in one); (b) DCE with speculative-unaware subordinate thread;<br>(c) SST with speculative-unaware subordinate thread; (d) DCE with<br>speculative-aware subordinate thread; (e) SST with speculative-aware<br>subordinate thread   | . 88  |

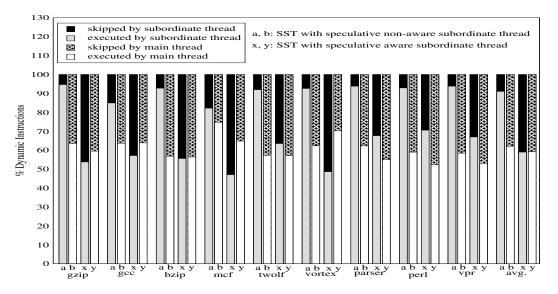

| 5.8 | Distribution of skipped and executed instructions in the main thread<br>and the subordinate thread for two schemes: (a) SST with speculative-<br>unaware subordinate thread; (b) SST with speculative-aware subor-<br>dinate thread                                                                                                                                              | . 89  |

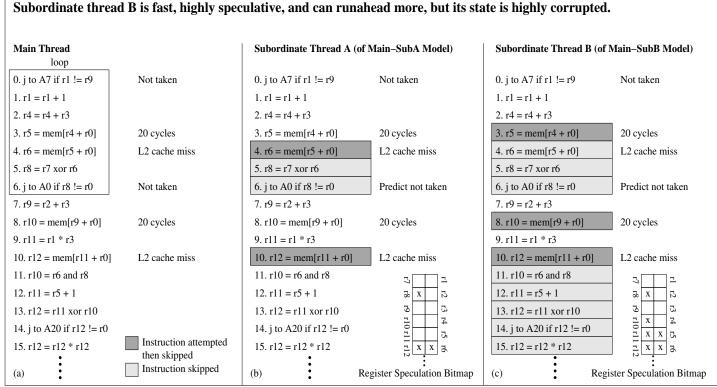

| 6.1 | Example from benchmark <i>perl</i> showing the code snippet for: (a) Main thread; (b) Subordinate thread of main-subA model; and (c) Subordinate thread of main-subB model.                                                                                                                                                                                                      | . 93  |

| 6.2 | Pros and cons of high and low speculation subordinate threads                                                                                                                                                                                                                                                                                                                    | . 95  |

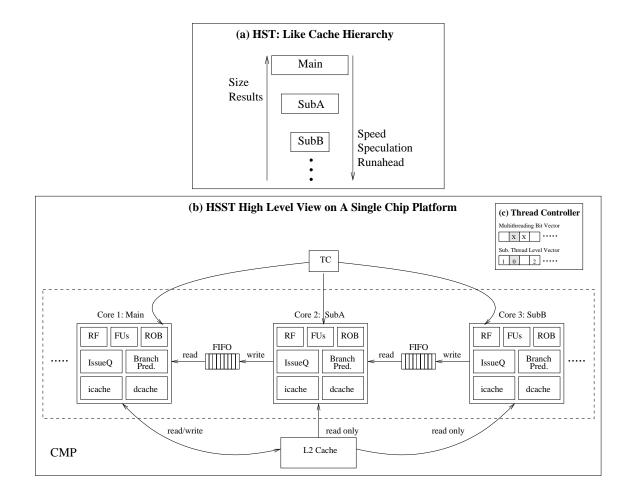

| 6.3 | HSST High Level Microarchitecture: (a) HSST similar to a cache hierarchy; (b) HSST block diagram; and (c) Components of Thread Controller (TC).                                                                                                                                                                                                                                  | . 97  |

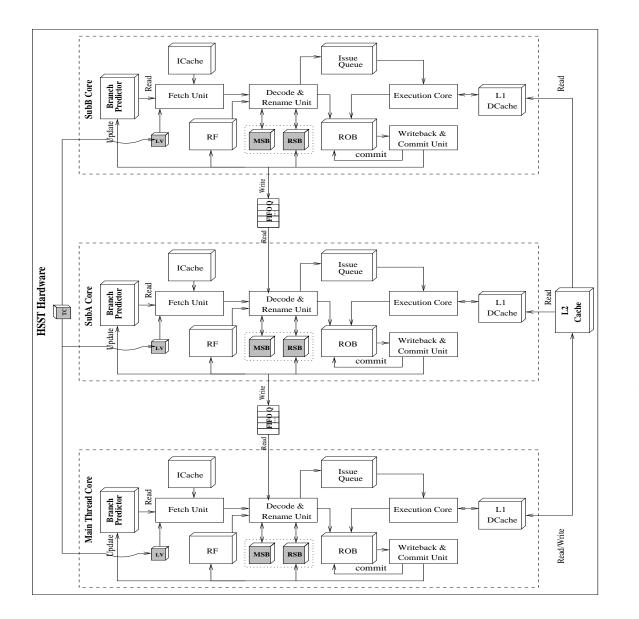

| 6.4 | HSST detailed microarchitecture design.                                                                                                                                                                                                                                                                                                                                          | . 99  |

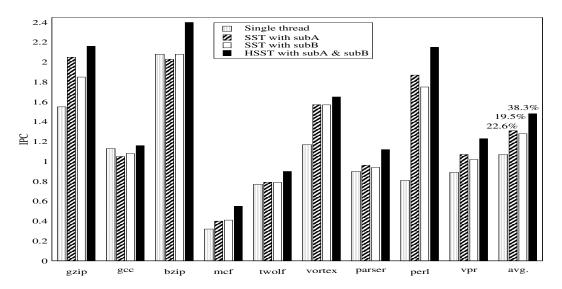

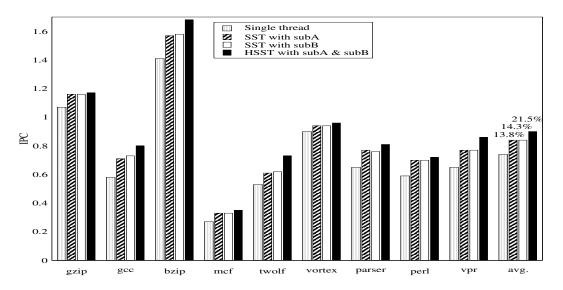

| 6.5 | IPC obtained for four schemes: (a) Single thread (superscalar); (b)<br>SST with subA (main-subA); (c) SST with subB (main-subB); and<br>(d) HSST with both subA and subB                                                                                                                                                                                                         | . 107 |

| 6.6 | IPC obtained for four schemes: (a) Single thread (superscalar); (b)<br>SST with subA (main-subA); (c) SST with subB (main-subB); and<br>(d) HSST with both subA and subB                                                                                                                                                                                                         | . 107 |

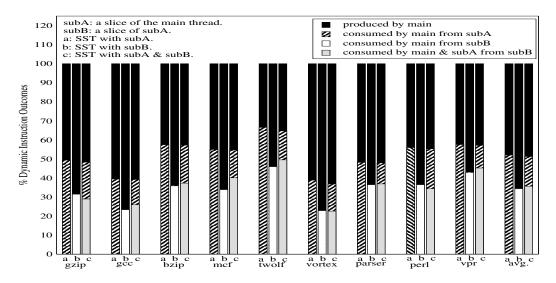

| 6.7  | Distribution of instruction outcomes in main thread for three schemes:<br>(a) SST with subA (main-subA); (b) SST with subB (main-subB);<br>and (c) HSST with subA and subB                                                                                                                                                     | . 108 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

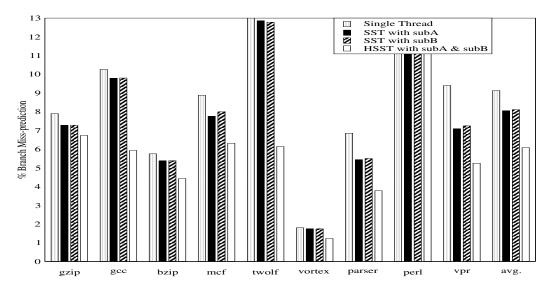

| 6.8  | Average branch miss-predictions in main thread for four schemes: (a) Single thread (superscalar); (b) SST with subA (main-subA); (c) SST with subB (main-subB); and (d) HSST with both subA and subB.                                                                                                                          | . 110 |

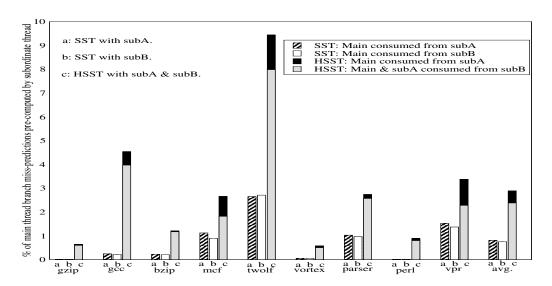

| 6.9  | Percentage of branch instructions that were a miss-prediction and the main thread obtained their correct outcomes from the subordinate thread, for three schemes: (a) SST with subA (main-subA); (b) SST with subB (main-subB); and (c) HSST with both subA and subB.                                                          | . 110 |

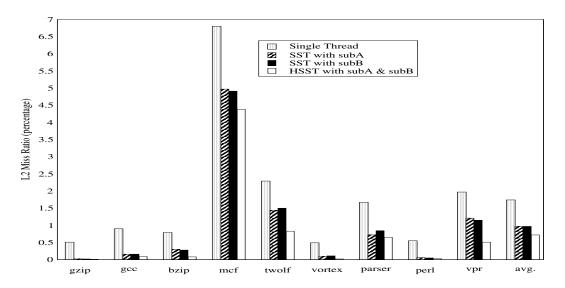

| 6.10 | L2 cache miss ratio in main thread for four schemes: (a) Single thread;<br>(b) SST with subA (main-subA); (c) SST with subB (main-subB);<br>and (d) HSST with both subA and subB                                                                                                                                               | . 112 |

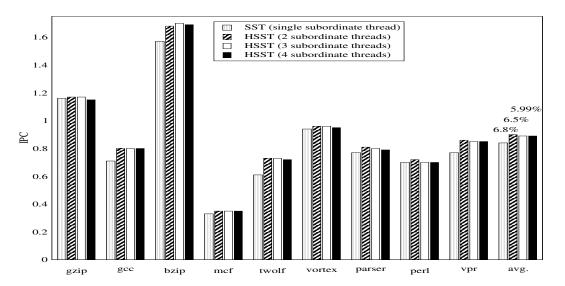

| 6.11 | IPC obtained for four schemes: (a) SST with a single subordinate thread; (b) HSST with two subordinate threads; (c) HSST with three subordinate threads; and (d) HSST with four subordinate threads                                                                                                                            | . 113 |

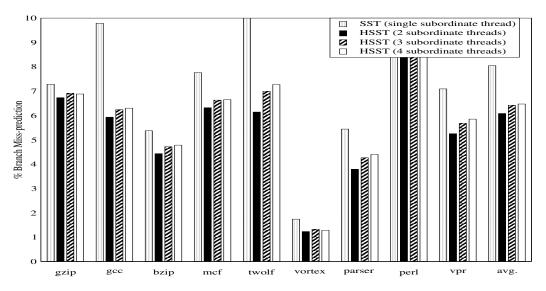

| 6.12 | Average branch miss-predictions in main thread for four schemes: (a) SST with a single subordinate thread; (b) HSST with two subordinate threads; (c) HSST with three subordinate threads; and (d) HSST with four subordinate threads.                                                                                         | . 113 |

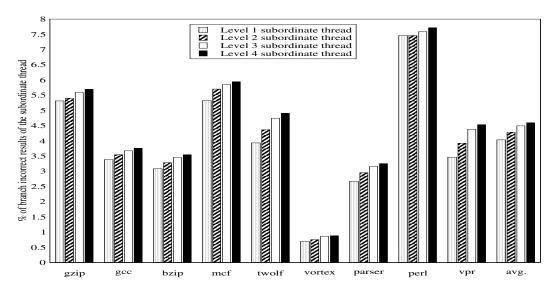

| 6.13 | Average incorrect branch results of four subordinate threads with different levels of speculation: (a) Subordinate thread at speculation level 1 (subA); (b) Subordinate thread at speculation level 2 (subB); (c) Subordinate thread at speculation level 3 (subC); and (d) Subordinate thread at speculation level 4 (subD). | . 114 |

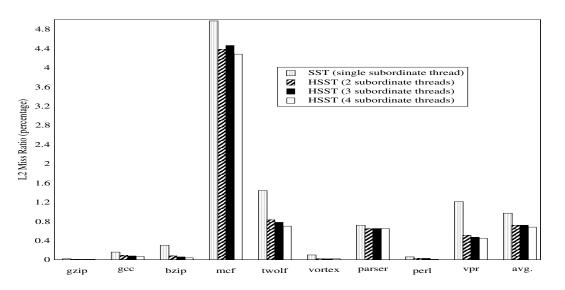

| 6.14 | L2 cache miss ratio in main thread for four schemes: (a) SST with a single subordinate thread; (b) HSST with two subordinate threads; (c) HSST with three subordinate threads; and (d) HSST with four subordinate threads.                                                                                                     | . 114 |

### Chapter 1

### Introduction

#### 1.1 Motivation

Recent trends in microarchitecture reveal a move towards multi-core architectures that can efficiently leverage the billion transistor chips promised by future technologies. All major high-performance microprocessor vendors have announced or are already selling chips with two to nine cores. Future generations of these processors will undoubtedly include more cores on a single chip multiprocessor (CMP) [1, 2]. In 2001, IBM introduced the dual-core POWER-4 [47] processor, and in 2004 it introduced the POWER-5 processor, in which each core supports 2-way simultaneous multithreading (SMT) [48]. In 2005 IBM introduced the Cell Broadband Engine Architecture known as Cell processor [72], which combined eight synergistic processor elements with a dual-issue POWER processor element. In 2004 Sun announced the Niagara processor [49], which included eight cores, each of which is a four-way SMT. AMD, Fujitsu, and Intel have also released their dual-core chip multiprocessors [50, 51, 52].

Multiprogrammed environments as well as parallel applications benefit the most out of multiple cores. However, the performance of individual serial programs does not improve and may even suffer a penalty because of increased contention for shared resources such as caches in a multi-core environment. Moreover, the cost and complexity of software increases if applications are manually parallelized to obtain a benefit from multiple cores. Finally, many general purpose applications, that are easy to parallelize, exhibit limited scalability. Therefore, they may not be able to take advantage of additional cores beyond a certain point.

Improving the performance of single threads in a multi-core environment has proven to be difficult for several reasons. First, multi-core architectures favor simpler and smaller cores to address the application needs for parallelization and the power budget, which limits the opportunity to exploit the available ILP with wide-issue cores. Also, achieving high single-thread performance in the presence of relatively increasing memory latencies has traditionally required large and complex cores to sustain a large number of instructions in flight while waiting for memory. On the other hand, special-purpose hardware accelerators that are located outside the core can improve a thread's performance by eliminating control and memory bottlenecks (e.g. advanced branch predictors and data prefetchers), but they often result in significant chip area additions and additional complexity. In light of these trends, architectural techniques that allow the use of additional cores to speed up single threads are becoming an attractive alternative [31].

Subordinate threading is one such technique that utilizes multi-core architectures for single-thread performance because of its ability to overcome the hurdles imposed by unpredictable branches and long-latency memory accesses. The basic idea is to spawn *subordinate threads* (also called *helper threads*), which are shorter versions of the main thread that execute in parallel with the main thread. Because they are shorter, they advance faster than the main thread, and perform many useful actions on behalf of the main thread, thereby speeding up the main thread computation. Useful actions performed by the subordinate thread include instruction and data pre-fetching to reduce cache misses [3, 4, 6, 7, 32, 8, 9, 10, 11, 12], and precomputing the outcome of hard-to-predict branches [27, 28, 29]. Moreover, it has been shown that the main thread can also benefit significantly from directly consuming subordinate thread results that are guaranteed to be correct [4, 35].

This dissertation describes and evaluates a new hardware-based architectural framework, named Symbiotic Subordinate Threading (SST), that allows otherwise idle cores in a CMP to function as helper engines for the individual threads running on the active cores. Our model exploits various sources of subordinate threading benefits: cache pre-fetching, branch pre-computation, and result reuse. The subordinate thread runs ahead of the main thread, performing cache pre-fetches and resolving branch miss-predictions ahead of the main thread demand and forwarding all of its results to the main thread. The main thread consumes the subordinate thread results that are guaranteed to be correctly executed by the subordinate thread without executing their corresponding instructions. Speeding up the main thread in this manner has several advantages. First, the overall speed of the processor increases, because it is dependent on how fast the main thread moves forward. Second, a faster main thread detects the subordinate thread's miss-speculations earlier, thereby cutting down the amount of time spent by the subordinate thread on wrong-path or wrong-data instructions. Third, both threads are making efficient use of the resources, by executing a relatively less overlapping portions of the program in parallel. Finally, because of the provision for early detection of violations, the subordinate thread is now free to do more aggressive speculations. This symbiotic relationship between the two threads speeds up both of them, resulting in significant improvements in performance.

#### 1.2 Contributions

This dissertation makes five major contributions, outlined below:

1. Symbiotic Subordinate Threading (SST): A key contribution of this dissertation is the development of a minimal dual-core SST model on a CMP platform that achieves significant performance benefits. The model uses simple hardware structures to facilitate forwarding of results from the subordinate thread to the main thread as well as determining if those results can be consumed by the main thread without executing their corresponding instructions. At the heart of our SST model is the formation of the subordinate thread dynamically. We provide a simple and efficient way of distilling the subordinate thread dynamically with minimum hardware requirements. Recovering the subordinate thread from the wrong path is another major concern and is addressed with minimum overhead. Our scheme is purely at the hardware level so it does not require any compiler intervention. (Chapters 3,4 and 5).

2. Understanding SST: Insight is provided regarding the sources of symbiotic subordinate threading performance. This focuses exploration of the architecture and leads to the following key results: (a) Significant performance improvement is

achieved with symbiotic subordinate threading, up to 27% improvement in speed. (b) A significant improvement in L2 cache misses is achieved in the subordinate thread. Also, a significant improvement in L1 dcache misses is achieved in the main thread. (c) The number of branch miss-predictions incurred by the main thread are reduced with SST. (d) Increased cooperation of the main thread and the subordinate thread is evident. First, the number of instructions executed by the main thread is reduced, up to 40%. Second, the subordinate thread wrong-path work is reduced significantly (Chapter 4).

4. Comparison between SST and other schemes: We perform comparisons between SST scheme and other already existing schemes that share the same high level implementation as SST. Those schemes are the slipstream processor, and dualcore execution model (DCE) [18, 36]. Both the slipstream processor and the DCE scheme are pure hardware mechanisms for speeding up single thread performance just like SST. They provide the same means as SST for forwarding results of the subordinate thread to the main thread but do not provide the means to identify the correct results of the subordinate thread as SST does. Hence, the main thread in slipstream and in DCE consumes the subordinate thread results as value and control predictions and so must validate them by executing all instructions. However, in SST the main thread consumes the correct results of the subordinate thread without executing their corresponding instructions. We show that SST, outperforms those techniques with a relatively simpler hardware additions. The average performance improvement of SST is 27% and 14% over the Slipstream processor and the DCE scheme, respectively (Chapter 4).

3. An optimized implementation of SST: We provide another implementation of SST in which the subordinate thread is aware of its own speculation. By letting the subordinate thread know which registers and memory locations are speculative, it can avoid executing instructions that uses data-speculative input values. In that sense, the subordinate thread distills itself and only executes instructions that will yield correct results. This is especially useful in reducing the number of times the subordinate thread miss-speculates and goes on the wrong path. It also provides the benefit of reducing the total number of instructions executed by both the main thread and the subordinate thread (Chapter 5).

5. Hierarchical Symbiotic Subordinate Threading (HSST): This is another key contribution of this dissertation, extending the SST scheme to include more than one subordinate thread. Our HSST execution paradigm allows a subordinate thread to have its own subordinate thread. Collectively, the main thread and the subordinate threads form a hierarchy, with the main thread at the top of the hierarchy. As we traverse the hierarchy downwards the subordinate thread speed and speculation increase because it executes fewer instructions, and so, its ability to explore more instructions than its instruction window allows, increases. Results generated by a thread are consumed by its parent thread just like in SST with a single subordinate thread. We explored HSST with two subordinate threads, three subordinate threads and four subordinate threads. Our results yield that as we add more subordinate threads, the penalties associated with squashing and recovering the subordinate threads increase such that they offset the benefits when we go beyond two subordinate threads. With two subordinate threads we achieved an average performance improvement of 15% over an SST scheme that uses a single subordinate thread (best of the two) (Chapter 6).

# 1.3 Roadmap

Background material is covered in Chapter 2. In Chapter 3, we describe how the main thread is pruned in order to be faster. This introductory Chapter provide insight into the implementation details of symbiotic subordinate threading (first and second contributions respectively). The sources of performance improvement achieved with symbiotic subordinate threading are discussed in Chapter 4 as well as comparing its performance against already existing schemes (second and third contributions). An optimized implementation of symbiotic subordinate threading is presented in Chapter 5 (fourth contribution) in which the subordinate thread is speculative aware. Hierarchical symbiotic subordinate threading is discussed in Chapter 6 (fifth contribution). Chapter 7 describes the related work. We propose the future work in Chapter 8. Chapter 9 concludes the dissertation.

#### Chapter 2

#### Background

This chapter provides the necessary background to better understand this dissertation. First we discuss single-chip multi-core processors, which is the current trend for maintaining microprocessor performance growth by providing significant benefits for both parallel and throughput oriented computing. We then discuss multithreading as a way to boost processor throughput by dividing the program workload into multiple threads that run simultaneously on the multiple cores available on the chip, thereby making efficient use of processor resources and boosting performance through exploiting thread level parallelism (TLP). Finally, we discuss subordinate threading and their benefits towards improving single-thread performance. Subordinate threading techniques utilize otherwise idle cores on a singlechip to run subordinate threads that perform some useful actions on behalf of the main thread.

### 2.1 Single-Chip Multi-core Processors

Execution models that can support multiple threads on a single-chip such as simultaneous multithreading (SMT), chip multiprocessing (CMP), and chip multithreading (CMT) [30, 1, 2], have received much attention from the research community in the computer architecture field. On the multiple processing elements (cores) available in a modern processor, one can run multiple programs in parallel, or multiple threads from the same program in parallel to overlap useful computations, or subordinate threads to assist the execution of the main computation thread. In this section we discuss the technological constraints that lead to single-chip multi-core processors, mainly, the superscalar's diminishing returns and the demand for a decentralized microarchitecture, in addition to the low power budget constraint, and the demand for low inter-processor communication latency. We then discuss the existing single-chip multi-core processor architectures.

## 2.1.1 Motivation for Building Single-Chip Multiprocessors

Earlier in 1996, Olukotun et. al [1] showed that a better use of silicon area is a multiprocessor constructed from simpler processors and that building a complex wide issue superscalar CPU is not the best use of silicon resources. We list some of the motivating reasons for building a single-chip multi-core processor.

Diminishing Performance of the Wide-Issue Superscalar Model: The superscalar processor yields diminishing returns in performance as the issue width increases, due to the increased complexity of the issue queue and limitations in instruction level parallelism. The net effect of all the comparison logic and encoding associated with a wide instruction issue queue is that it takes a large amount of die area to implement. Moving to the circuit level, a wide instruction issue queue requires longer wires that span the length of the structure, resulting in longer delays. Farkas et. al. found that an eight-issue machine only performs 20% better than a four-issue machine when the effect of cycle-time is included in the performance estimates [53]. This leads to the need for a microarchitecture constructed from simpler processors to maintain the performance growth of microprocessors.

**Application Demand:** From the applications perspective, the microarchitecture that works best depends on the amount and characteristics of parallelism present in the applications. Applications fall into two categories. The first category consists of applications with low to moderate amounts of parallelism (under 40 instructions per cycle), most of which are integer applications. The second category consists of applications with large amounts of parallelism, greater than 40 instructions per cycle. The floating point applications fall into the second category and most of the parallelism is in the form of loop-level parallelism. These two categories require different execution models. Integer applications work best on a moderately superscalar processor with very high clock rates because there is little parallelism to exploit. On the other hand, a decentralized multiprocessor paradigm best suites the floating point programs because it exploits the vast amount of parallelism present in those programs. Multi-core microarchitectures will work well on integer programs because each individual processor is a simple superscalar processor with very high clock rates. Also, multi-core microarchitectures can exploit the parallelism of the floating point applications by running multiple threads in parallel from the same program on the available cores.

Low Power Budget Requirement: Finally, power considerations also favor simpler processors but with low frequency. For workloads with adequate thread level parallelism (TLP), doubling the number of cores and halving the frequency delivers roughly equivalent performance, while reducing power consumption by a factor of four [2]. However, for applications with limited TLP, speculative parallelism or subordinate threading have to be exploited for obtaining good single-thread performance under a low-power budget; otherwise single-thread performance will be negatively affected due to low frequency.

Low Communication Latencies Requirement: In multiprogramming and conventional parallel processing environments, communication between threads is through shared memory and has latencies typically in the hundreds of CPU cycles [1]. Because of the high inter-thread communication latencies, threads are constructed such that they rarely have to communicate, and this implies that fine-grain parallelism cannot be exploited. The addition of low-latency inter-processor communication between processors on the same chip allows the multi-core processor to better exploit the available parallelism in applications.

### 2.1.2 Single-Chip Multi-core Architecture Models

The most common use for CMP and CMT is to execute multiple threads in parallel to increase throughput. The widespread use of visualization and multimedia applications tend to increase the number of active processes or independent threads on a desktop or a server in a particular point of time. One way to increase throughput is to execute threads simultaneously from multiple applications. Another way is to execute multiple threads in parallel that come from a single application, such as transaction processing. Multi-core processors can also be used to accelerate the execution of a single thread of control. We next discuss the trade-offs between CMP and CMT in what they can offer regarding throughput and single-thread performance.

**CMP:** Each core on a CMP processor runs only a single-thread. To increase throughput, cores are made simpler and smaller to accommodate more threads. Hence, layout efficiency increases, resulting in more functional units within the same silicon area plus faster clock rates. The problem with CMP is that the hardware partitioning of on-chip processors restricts performance. The hardware partition results in smaller resources since the level-1 caches, TLBs, branch predictors, and functional units are divided among the multiple processors. Hence, single-threaded programs cannot use resources from the other processor cores and the smaller level-1 resources per core cause increased miss rates [54].

**CMT:** CMT processors provide support for many simultaneous hardware threads of execution in various ways, including SMT and CMP. Recall that, in an SMT processor, the physical processor core appears to the operating system as if it is a symmetric multiprocessor containing several logical processors. Hence, the physical processor core executes instructions from more than one instruction stream (thread). This increases throughput through thread-level parallelism and tolerates processor and memory latencies to increase processor efficiency. The problem with SMT is that complexity and circuit delays grow faster with issue width. In addition, multiple threads on a single core share the same level-1 cache, TLB, and branch predictor units, which causes contention. The resulting increase in cache misses and branch miss-prediction rates limits performance. Merging CMP and SMT combines the advantages of both the individual techniques. CMT has the CMP advantages of more functional units and a faster clock than a wide-issue processor. Also, the addition of SMT increases the efficiency of the underlying CMT, because there is no hardware partitioning of processor resources, which allows a number of instructions from multiple threads to access the functional units, hence increasing the functional unit utilization.

**Trade-offs:** More smaller cores makes the throughput of CMPs higher than that of SMTs; however, a wide-issue SMT delivers higher single-thread performance. Given the significant area cost associated with high-performance cores, for a fixed area and power budget, the CMT design choice is between small number of high performance (high frequency, aggressive out-of-order, large issue width) cores or multiple simple (low frequency, inorder, limited issue width) cores. For workloads with sufficient TLP, the simpler core solution may deliver superior chip-wide performance at the fraction of the power. However, the simpler core solution will not work well for applications with limited TLP, unless other means for parallelization are used. In this dissertation, we realize the low area and low power budget, so we believe that future CMTs will use simpler cores. Hence, we focus in this dissertation on subordinate

threading to speed up the performance of a single thread that lacks sufficient TLP.

# 2.2 Multithreading

Multithreading boosts the processor throughput and improves single-program performance, through exploiting thread-level parallelism that resides in programs. It has been studied extensively in both academia and industry [63, 42, 64]. To make use of the available transistor budget, processor manufacturers such as IBM, Intel, and AMD started integrating more cores and/or threads on a single chip to support multithreading. Many studies in academia have been carried out to examine the potential of using multithreading processors such as SMT and CMP. We expect that multithreading will continue to benefit single-program performance as well as processor throughput, as long as the transistor count on a chip continues to grow. Below, we discuss some of the multithreading execution paradigms mainly multiprogramming and parallel processing. We also, discuss how each of them exploits the available thread-level parallelism in programs.

# 2.2.1 Multiprogramming

Multiprogramming utilizes multiprocessor systems and increases the overall processor throughput by running multiple independent programs simultaneously. Also, in a multiprogramming environment, communication or synchronization between threads is not frequent, thereby, thread-level parallelism can be easily extracted from programs. The parallelism exploited by multiprogramming is from different programs. However, because multiprocessor systems serve a large number of threads that often share critical hardware resources, those critical hardware resources are often saturated with so many threads. This results in diminishing throughput as more threads are fed into the system. Moreover, some times, we are interested in speeding up a single program and not only achieving high throughput. However, multiprogramming often sacrifices single-program performance in order to achieve higher throughput.

## 2.2.2 Parallel Processing

In parallel processing, the program is divided into subprograms, which all run in parallel on a multiprocessor system. In this way, single-program performance is boosted. One way to improve the performance of a single program is We discuss two different parallel processing paradigms. The first one is conventional parallel processing and the other is thread-level data speculation technique.

In conventional multiprocessor systems, when a program is partitioned into multiple subprograms, each subprogram usually runs almost independently, thereby exploiting thread-level parallelism in a single program. In such a system, the threads are completely non-speculative and overlap useful computations, which improves the processor throughput. The partitioning is done by a compiler or a programmer such that the threads are independent. The programmer or compiler, also takes care of handling the synchronization among the different threads.

In thread-level speculation, the program is partitioned into multiple threads

speculatively. Thread-level speculation exploits thread-level parallelism by running the multiple threads in parallel. When, partitioning the threads, it is assumed that there are no memory dependences between threads. Each thread commits its results sequentially in the original program order, and this ensures correct program execution. Dependence violations are detected by a special hardware, which recovers the threads from any memory dependence violations. This hardware, also holds intermediate results until a thread commits. True dependencies between store and load operations prevent the threads from running and exploiting thread-level parallelism. In thread-level speculation a finder-grain thread synchronization is needed and is supported by the hardware, as in a chip multiprocessor.

In thread-level speculation, complicated dependence structures often limit successful exploitation of thread-level parallelism. This leads to subordinate threading, as a means of boosting single-thread performance when thread-level parallelism is scarce and partitioning a program into speculative threads is difficult due to complicated dependence structures present in the program.

### 2.3 Subordinate Threading

With integrating more processor cores on a single-chip multiprocessor, communication delays have been reduced considerably. In subordinate threading, one or more subordinate (helper) threads run in parallel with the main thread to help its execution. We identify two unique characteristics of subordinate threading. First, subordinate threads help speed up the execution of the main computation thread. However, they do not affect the processor throughput. Subordinate threads help the main thread execution by running far ahead of the main thread, such that they do work on its behalf. Second, the execution of subordinate threads are decoupled from that of the main thread and their code does not have to be extracted from the original program code. Subordinate threads open up a lot of opportunities for exploiting otherwise idle cores on a chip-multiprocessor for single-program performance as we will show in this dissertation. Below, we present some of the previously proposed uses of subordinate threading to assist the execution of a single program. We then describe some of the tradeoffs of constructing effective subordinate threads.

### 2.3.1 Uses of Subordinate Threading

Tolerating Long-Latencies on Behalf of the Main Thread: Subordinate threads improve the performance of the main computation thread by hiding the latencies of critical instructions such as load instructions that miss in the cache or miss-predicted branch instructions. Subordinate threads help the main computation thread by executing a slice of the main computation thread. Because they execute fewer instructions than the main thread, they are able to run ahead of it and trigger long-latency events much earlier. They also overlap those latencies with useful computations. Some examples include data pre-fetching [7, 32, 33, 34, 8, 3, 4, 10, 12], instruction pre-fetching [6, 14], branch outcome pre-computation [27], and virtual function call target prediction [5]. Some subordinate threads only trigger cachemisses but they never completely service it, instead they run ahead to find other

independent cache-misses and trigger them [59, 19, 11]. For the subordinate threads to be effective they have to accomplish their task in a timely fashion. If they are too slow, the main thread will not benefit and if they are too fast, they may throw pages out of the cache that are needed by the main thread.

# Executing the Exception Handler Code in Parallel with the Main Thread:

Subordinate threads can also be used to run the exception handler code of faulting instructions. This relieves the main thread from executing this code, and so it can continue to execute in parallel other instructions that are independent from the one that caused the exception [65]. If the code being executed does not contain many exceptions, or if there is not enough independent instructions from the faulting instruction to overlap with the exception handler code, then performance may not improve much.

Used as an Accurate Value and Branch Predictor to the Main Thread: Subordinate threads that are distilled such that they execute hard-to-predict branch instructions and their backward slices, or critical load instructions that miss in the cache and their backward slices, produce near accurate results. Those results can serve as near perfect predictions in the main thread, thereby allowing the main thread to do progress in the event of a cache miss and reducing the number of branch miss-predictions in the main thread [36, 18, 45]. However, because the subordinate thread may execute instructions speculatively, it may introduce incorrect branch predictions that otherwise would not occur if the main thread followed the prediction obtained from the branch predictor.

**Incorporating Fault Tolerance:** Subordinate threads can also be used to improve fault tolerance. They are a redundant copy of the main computation thread that runs on another core, thereby helping in detection and recovery from faults that occur during the program execution [66, 67]. This type of subordinate thread executes the same code as the main thread, and so it is totally redundant, and therefore it does not contribute to the processor performance. However, in the slipstream processor, the subordinate thread, called A-stream in slipstream terms, is used for both performance improvement as well as fault tolerance [15].

Implementing Hardware Structures and Algorithms in Software: Using subordinate threading, one can implement complicated hardware structures or algorithms in software, such as a cache pre-fetcher algorithm [46], and run them as helper threads on spare cores. In this way, the hardware complexity of the processor for supporting those new complicated structures is vastly reduced. Hence, reducing the testing and validation cost of the processor hardware. In this case, the subordinate thread code is not derived from the original program, rather it is general purpose and serves any of the individual threads running on the active cores.

# 2.3.2 Subordinate Thread Construction Techniques

One of the important issues in subordinate threading is generating subordinate threads that perform their required task effectively. In this dissertation we focus on those subordinate threads that enhance single-thread performance. That means, constructing subordinate threads must take into consideration that the subordinate thread has to produce accurate results at the right time. There are several ways for constructing subordinate threads. One way, is constructing subordinate threads manually by the programmer [3]. The disadvantage of manual construction, is that it is labor intensive and is error-prone. Hence, automating the construction is more fruitful.

Kim [73] classifies the various approaches of constructing effective subordinate threads automatically based on how and when in the program's lifetime subordinate threads are constructed. There are four possible approaches to extracting subordinate threads. First, in *compiler-based extraction* the compiler analyzes the program code and generates subordinate threads at the source-level [32]. The second approach is *linker-based extraction*, which generates subordinate threads using binary analysis [8, 29]. The third approach is *dynamic optimizer-based extraction*. In this approach, binary-level code is analyzed and extracted similar to linker-based extraction. However, the extraction of binary-level code occurs at runtime using dynamic optimization techniques. Finally, the fourth approach is *hardware-based extraction* [7, 10, 18]. In this approach, subordinate threads are extracted at runtime from instruction traces. This requires, runtime analysis of retired instructions using special hardware structures.

Each of the four approaches makes use of different analysis techniques in different phases of a program's lifetime, to generate effective subordinate threads. Therefore, each approach exhibits very different characteristics. Below, we describe some of the tradeoffs between the main two approaches to extracting subordinate threads, compiler-based extraction and hardware-based extraction; a more detailed treatment is available in [73]. We also discuss the operating system intervention with compiler-based subordinate threads versus hardware-based subordinate threads.

Run-time Versus Compile-time Information: In hardware-based extraction, the runtime information is used to accurately identify long-latency events (cache misses and hard-to-predict branches) in a program. However, the size of the hardware structure responsible for detecting dependences among instructions to help in extracting independent subordinate thread code is not sufficiently large, resulting in a limited scope of analysis. The runtime information, however, cannot be utilized in compiler-based approaches. They need to collect off-line profiles instead for identifying long-latency events. Compiler-based approaches operate in the earlier phases of the program lifetime, and so they utilize the high-level information of the program.

**Dependence on the Machine Platform:** When the subordinate thread is generated at runtime (hardware-based extraction), it becomes dependent on the hardware platform, i.e., the machine implementation. This is because, hardware-based extraction requires a special hardware structure for analyzing retired instruction traces. Therefore, this special hardware structure must be redesigned for every new processor design. On the other hand, compiler-based approaches generate a source code that can be compiled for any processor design. Therefore, compiler-based extraction is completely independent of the platform, thereby generating code that is portable.

Effect on Transparency to the User: Runtime extraction is transparent to the user, hence, hardware-based approaches are completely transparent to the user. In hardware-based approaches, all the necessary hardware for runtime analysis and generation of subordinate threads is implemented within the processor. On the other hand, the compiler-based approach is less transparent for several reasons. First, it requires additional compilation steps such as code analysis and off-line profiling. Second, it requires the program source code, which is sometimes unavailable. Third, it requires changes to the instruction set architecture (ISA).

Effect on Hardware Complexity: In compiler-based extraction, the subordinate threads are generated using software, thereby reducing the hardware complexity. Compiler-based approaches require some hardware support though for supporting multithreading. On the other hand, hardware-based approaches generate subordinate threads using hardware, hence increasing the hardware complexity. Adding new hardware, has the disadvantage of increasing the the testing and validation cost of the hardware. However, this depends on how much special hardware is required for hardware-based extraction.

**Operating System Independence:** The operating system is the one that schedules the compiler-based subordinate threads to begin executing on the hardware. It may take a thread up to 50 thousand cycles to begin executing on hardware since

the time it got scheduled by the operating system due to context switching. Recall that, subordinate threads must accomplish their task at a time suitable to the main thread. If they are too slow, they will not be able to hide the latency associated with memory or branch miss-predictions. If they are too fast, they may throw out of the cache blocks that are needed by the main thread. Because subordinate threads must be timely, the operating system must schedule them at the same time as the main thread. On the other hand, pure hardware-based subordinate threads are launched independent from the operating system. They are triggered on spare idle cores by the hardware, and begin execution with no delay once they are triggered. That makes hardware-based subordinate threads more flexible and more event-driven, so they are launched only when needed.

From the above discussion, we can conclude that each approach (compilerbased and hardware-based) exhibits its own advantages and disadvantages. In this dissertation, however, we focus on the hardware-based generation of subordinate threads due to the following reasons. First of all, while compiler-based approaches have been evaluated previously in many research proposals, hardware-based construction of subordinate threads is relatively new and has not been fully investigated. Also, we believe that it is possible to support hardware-based extraction of subordinate threads with moderate additions/changes to the hardware of existing multithreading processors, as we will show in this dissertation. Third, while compilerbased extraction utilizes high-level program information of the earlier phases of the program lifetime, by supporting hardware-based extraction we are also utilizing the runtime information to construct subordinate threads for improving single-thread performance. Fourth, with so many cores integrated on a single chip, there is more opportunity to use otherwise idle cores to improve the performance of the active cores. Finally, it is much faster to switch the mode of a core to act as a subordinate engine for another active core than to make the operating system launch a subordinate thread.

We discuss in the following chapters our proposed subordinate threading model, named, Symbiotic Subordinate Threading, which is a hardware-based approach of subordinate threading.

## Chapter 3

# Symbiotic Subordinate Threading (SST) — The Concepts and Implementation Details

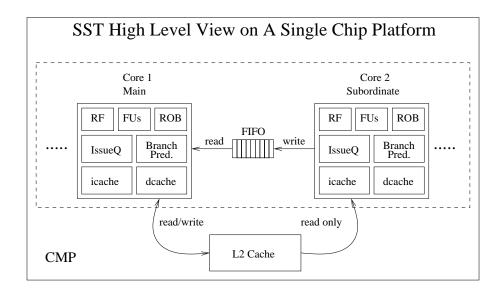

In this chapter we describe our proposed SST scheme. The basic SST is a dual-core subordinate threading scheme in which one core is the main thread and the other core acts as the helper engine (subordinate thread) for the main thread. The high level view of SST is shown in Figure 3.1. Each thread, main or subordinate, runs on a separate core on a chip multiprocessing platform (CMP) [1]. Each core has its own data cache (dcache), instruction cache (icache), functional units (FUs), issue queue, reorder buffer (ROB), branch predictor, and register file (RF). Both threads share a unified L2 cache, which is updated only by the main thread. The subordinate thread forwards all of its outcomes to the main thread via a first-infirst-out (FIFO) queue. The mechanisms for distilling the subordinate thread and the main thread as well as the means for communicating the subordinate thread outcomes to the main thread will be described shortly, followed by the detailed design of SST.

## 3.1 A Simple Methodology for Distilling The Subordinate Thread

In order for the subordinate thread to run ahead of the main thread, it must speculate more often and skip instructions. There have been several techniques

Figure 3.1: SST top level design.

for distilling the subordinate thread, and they can be divided into dynamic (at run time) and static (by the compiler). In our implementation of the subordinate thread we distill it dynamically using the hardware, to utilize the runtime information about the program and the data. Also, our hardware mechanism does not require caching recurring code regions of the subordinate thread as conventional hardware mechanisms require.

The subordinate thread we use skips highly predictable branches and their backward slices. This allows it to concentrate on the hard-to-predict branch instructions. It also identifies critical memory instructions and retires them early from the pipeline similar to runahead execution [19], so that they do not block the pipeline. The criticality of a memory instruction is determined by the number of cycles it spends at the head of the ROB, waiting for main memory.

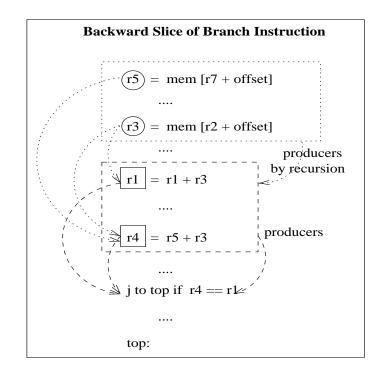

Figure 3.2: Identifying the backward slice of a branch instruction.

Identifying highly predictable branches: We use a simple methodology for identifying highly predictable (non-critical) branch instructions and distill them out of the subordinate thread along with their backward slices. We use a branch predictor to identify highly predictable branches. Branch instructions that are critical usually have low prediction confidence in the branch predictor, and the highly predictable ones usually have high prediction confidence in the branch predictor. When the subordinate thread skips a highly predictable branch instruction, it follows the predicted outcome and direction of the highly predictable branch at the fetch stage and marks all pipeline instructions in front of the highly predictable branch and its backward slice. The algorithm for identifying the backward slice of a branch instruction begins by identifying the producer instructions of each input operand of the branch instruction (those producer instructions are shown with a square at their output operand in Figure 3.2). Next, by recursion, the algorithm is applied on the producer instructions to identify the instructions that produce their input operands (shown with a circle at their output operand in Figure 3.2), and so on.

Identifying long latency memory instructions: Our subordinate thread also does not wait for long latency memory instructions to complete. When a memory instruction reaches the head of the ROB, a counter is reset and is incremented every cycle the memory instruction spends at the head of the ROB. When that counter reaches a specific maximum value, the subordinate thread concludes that this memory instruction is critical (long latency). It marks all subsequent instructions in the pipeline that are dependent on its outcome. It then supplies a speculative value (most likely an invalid value) for the output operand of the memory instruction and retires it.

Handling Instructions Marked to Be Skipped: The backward slices of highly predictable branches, as well as long latency memory instructions and their dependency chains free all the resources they hold. Hence they do not finish executing and pass into the pipeline as no-ops. Once they reach the head of the ROB, their ROB entry is reclaimed and their decoded information is written onto the FIFO queue. Because they pass into the pipeline as no-ops, they leave the pipeline much earlier, and so, more instructions can be brought into the pipeline, resulting in a wider instruction window for the subordinate thread.

Note that the subordinate thread passes every instruction onto the FIFO queue, even if it did not execute it. In case of skipped branches, it also passes the predicted branch outcome that it followed. This is essential information that is passed to the main thread to help it monitor the subordinate thread path, as will be discussed later.

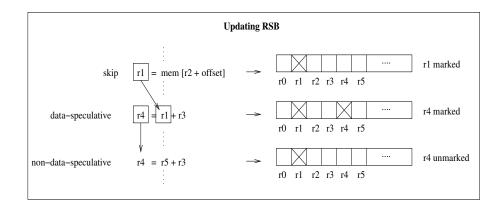

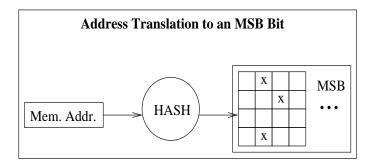

## 3.2 A Simple and Efficient Way of Pruning The Main Thread

In this section we introduce an algorithm that helps the main thread consume the results that were correctly produced by the subordinate thread without having to execute their corresponding instructions. This involves recording the subordinate thread speculative state (registers or memory addresses that contain speculative values in the subordinate thread), to aid in identifying outcomes of the subordinate thread that were computed using speculative input values from those that did not involve any speculative input values. We will show that our technique for pruning the main thread is independent from the subordinate thread type. A working example is presented at the end of this section for clarification.

### 3.2.1 Basic Idea

In order for the subordinate thread to run ahead of the main thread, it skips instructions. The output registers of those skipped instructions contain dataspeculative values. Some of the instructions the subordinate thread executes are dependent on the ones it skipped. The outcomes of those dependent instructions are speculative in nature (which could be correct or incorrect). We categorize the instructions executed by the subordinate thread into two classes: those producing *data-speculative* outcomes and those producing *non-data-speculative* outcomes.