#### ABSTRACT

| Title of Dissertation:    | STUDY OF FINE-GRAINED, IRREGULAR<br>PARALLEL APPLICATIONS ON A<br>MANY-CORE PROCESSOR                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | James Alexander Edwards<br>Doctor of Philosophy, 2020                                                                                               |

| Dissertation Directed by: | Professor Uzi Vishkin<br>University of Maryland Institute for Advanced<br>Computer Studies and Department of<br>Electrical and Computer Engineering |

This dissertation demonstrates the possibility of obtaining strong speedups for a variety of parallel applications versus the best serial and parallel implementations on commodity platforms. These results were obtained using the PRAM-inspired Explicit Multi-Threading (XMT) many-core computing platform, which is designed to efficiently support execution of both serial and parallel code and switching between the two.

*Biconnectivity:* For finding the biconnected components of a graph, we demonstrate speedups of 9x to 33x on XMT relative to the best serial algorithm using a relatively modest silicon budget. Further evidence suggests that speedups of 21x to 48x are possible. For graph connectivity, we demonstrate that XMT outperforms two contemporary NVIDIA GPUs of similar or greater silicon area. Prior studies of parallel biconnectivity algorithms achieved at most a 4x speedup, but we could not find biconnectivity code for GPUs to compare biconnectivity against them. *Triconnectivity:* We present a parallel solution to the problem of determining the triconnected components of an undirected graph. We obtain significant speedups on XMT over the only published optimal (linear-time) serial implementation of a triconnected components algorithm running on a modern CPU. To our knowledge, no other parallel implementation of a triconnected components algorithm has been published for any platform.

*Burrows-Wheeler compression:* We present novel work-optimal parallel algorithms for Burrows-Wheeler compression and decompression of strings over a constant alphabet and their empirical evaluation. To validate these theoretical algorithms, we implement them on XMT and show speedups of up to 25x for compression, and 13x for decompression, versus bzip2, the de facto standard implementation of Burrows-Wheeler compression.

Fast Fourier transform (FFT): Using FFT as an example, we examine the impact that adoption of some enabling technologies, including silicon photonics, would have on the performance of a many-core architecture. The results show that a single-chip many-core processor could potentially outperform a large high-performance computing cluster.

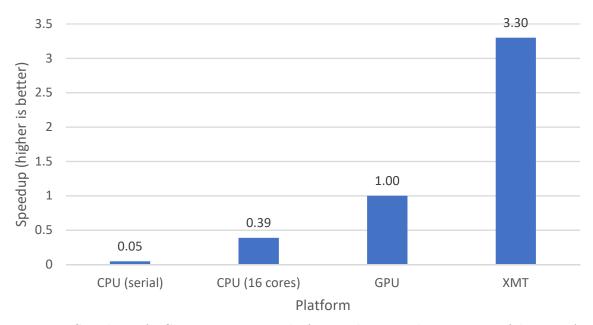

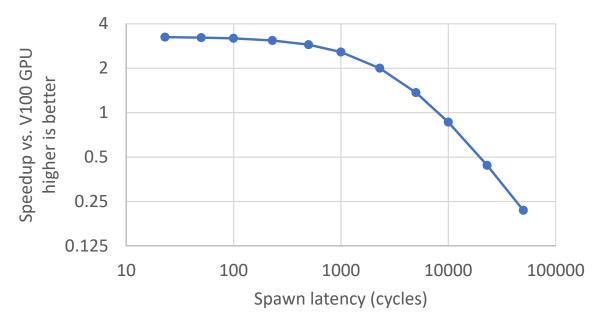

Boosted decision trees: This chapter focuses on the hybrid memory architecture of the XMT computer platform, a key part of which is a flexible all-to-all interconnection network that connects processors to shared memory modules. First, to understand some recent advances in GPU memory architecture and how they relate to this hybrid memory architecture, we use microbenchmarks including list ranking. Then, we contrast the scalability of applications with that of routines. In particular, regardless of the scalability needs of full applications, some routines may involve smaller problem sizes, and in particular smaller levels of parallelism, perhaps even serial. To see how a hybrid memory architecture can benefit such applications, we simulate a computer with such an architecture and demonstrate the potential for a speedup of 3.3X over NVIDIA's most powerful GPU to date for XGBoost, an implementation of boosted decision trees, a timely machine learning approach.

Boolean satisfiability (SAT): SAT is an important performance-hungry problem with applications in many problem domains. However, most work on parallelizing SAT solvers has focused on coarse-grained, mostly embarrassing parallelism. Here, we study fine-grained parallelism that can speed up existing sequential SAT solvers. We show the potential for speedups of up to 382X across a variety of problem instances. We hope that these results will stimulate future research.

# STUDY OF FINE-GRAINED, IRREGULAR PARALLEL APPLICATIONS ON A MANY-CORE PROCESSOR

by

#### James Alexander Edwards

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2020

Advisory Committee: Professor Uzi Vishkin, Chair/Advisor Professor Rajeev Barua Professor Joseph JaJa Professor Alan Sussman Associate Professor Behtash Babadi Doctor Bogdan Kosanovic © Copyright by James Alexander Edwards 2020

#### Acknowledgments

I would like to thank my advisor, Prof. Uzi Vishkin, for his patient guidance. Throughout my academic career, he was always more than willing to listen to my (often convoluted) explanations of my work, provide insightful comments, and help me ask the right questions about my work.

I appreciate the time and effort spent by the dissertation committee members, Prof. Rajeev Barua, Prof. Joseph JaJa, Prof. Alan Sussman, Assoc. Prof. Behtash Babadi, and Dr. Bogdan Kosanovic, especially given the unusual circumstances this year. I would like to thank Prof. Barua in particular for helping me to sharpen the main contributions of this dissertation.

I would like to thank former and current members of the XMT team for their help in making this work possible. George Caragea, Fuat Keceli, Alexandros Tzannes, and Xingzhi Wen not only provided the XMT toolchain but took the time to help me understand how the tools worked and how to upgrade them. The research done by Fady Ghanim and Sean O'Brien helped to validate my own work.

I am grateful to my father for sparking my interest in computers, and my mother and sister for cheering me on and always being there for me whenever I needed them.

And, last but most importantly, I would like to thank God for guiding and uplifting me through this stage of my life.

#### Specific acknowledgments

We would like to thank the authors of [149] for providing us with the CUDA code for graph connectivity tested in Chapter 2.

We gratefully acknowledge comments provided by Prof. Rina Dechter related to putting prior work on SAT solvers in proper perspective in Chapter 7.

## Table of Contents

| Ac | know  | ledgements                                                                          |

|----|-------|-------------------------------------------------------------------------------------|

| Ta | ble o | f Contents                                                                          |

| 1. | Intro | pduction                                                                            |

| 2. | Gra   | oh biconnectivity                                                                   |

|    | 2.1   | Introduction                                                                        |

|    |       | 2.1.1 Related Work                                                                  |

|    | 2.2   | Evaluated Algorithms                                                                |

|    |       | 2.2.1 Input and Output                                                              |

|    |       | 2.2.2 Parallel Depth-First Search (pDFS)                                            |

|    |       | 2.2.3 Tarjan-Vishkin (TV)                                                           |

|    |       | 2.2.4 Tarjan-Vishkin with a BFS Spanning Tree (TV-BFS) 20                           |

|    | 2.3   | Evaluated Platforms                                                                 |

|    |       | 2.3.1 GPUs                                                                          |

|    |       | 2.3.2 XMT                                                                           |

|    |       | 2.3.3 Evaluated configurations                                                      |

|    | 2.4   | Experimental Evaluation                                                             |

|    |       | 2.4.1 Tested Graphs                                                                 |

|    |       | 2.4.2 Results for comparing GPUs and XMT                                            |

|    |       | 2.4.3 Biconnectivity Algorithms: Overall Speedups and Compari-<br>son of Algorithms |

|    | 2.5   | Discussion                                                                          |

|    | 2.6   | Conclusion                                                                          |

| 3. | Graj  | oh triconnectivity                                                                  |

|    | 3.1   | Introduction                                                                        |

|    | 3.2   | Triconnectivity Algorithms                                                          |

|    | 3.3   | The XMT Many-Core Platform                                                          |

|    | 3.4   | Experimental Results                                                                |

|    | 3.5   | Future Work                                                                         |

|    | 3.6   | Conclusion                                                                          |

| 4. | Burr | $rows$ -Wheeler (BW) compression $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 51  |

|----|------|----------------------------------------------------------------------------------------------------------|-----|

|    | 4.1  | Introduction                                                                                             | 51  |

|    |      | 4.1.1 Related Work                                                                                       | 53  |

|    | 4.2  | Serial Algorithm                                                                                         | 55  |

|    |      | 4.2.1 Compression                                                                                        | 56  |

|    |      | 4.2.2 Decompression                                                                                      | 62  |

|    | 4.3  | Parallel Algorithm                                                                                       | 62  |

|    |      | 4.3.1 Compression                                                                                        | 63  |

|    |      | 4.3.2 Decompression                                                                                      | 67  |

|    | 4.4  | Experimental Validation                                                                                  | 71  |

|    |      | 4.4.1 The XMT Platform                                                                                   | 71  |

|    |      | 4.4.2 Evaluated Configurations                                                                           | 72  |

|    |      | 4.4.3 Data Sets                                                                                          | 74  |

|    |      | 4.4.4 Implementation Details                                                                             | 75  |

|    | 4.5  | Results                                                                                                  | 77  |

|    | 1.0  | 4.5.1 Comparison with bzip2                                                                              | 77  |

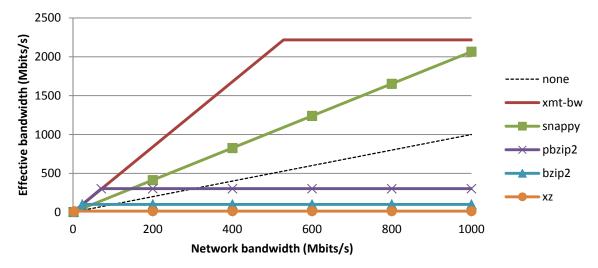

|    |      | 4.5.2 Using Compression to Increase Bandwidth                                                            | 80  |

|    | 4.6  | Conclusion                                                                                               |     |

|    | 1.0  |                                                                                                          | 02  |

| 5. | Fast | Fourier Transform (FFT)                                                                                  | 83  |

|    | 5.1  | Introduction                                                                                             |     |

|    |      | 5.1.1 Comparison to prior work on the FFT                                                                | 87  |

|    | 5.2  | Background                                                                                               | 88  |

|    |      | 5.2.1 XMT Architecture                                                                                   | 88  |

|    |      | 5.2.2 NoC (Network on Chip)                                                                              | 91  |

|    | 5.3  | Motivation for using the XMT framework in this chapter                                                   | 92  |

|    |      | 5.3.1 Ease of experimentation                                                                            | 92  |

|    |      | 5.3.2 Past XMT Speedups                                                                                  | 92  |

|    |      | 5.3.3 Ease of programming                                                                                | 93  |

|    | 5.4  | Experimental configurations                                                                              | 93  |

|    |      | 5.4.1 Baseline: 4096 TCUs ("4k")                                                                         | 94  |

|    |      | 5.4.2 3D VLSI: 8192 TCUs ("8k")                                                                          |     |

|    |      | 5.4.3 Microfluidic cooling: 65536 TCUs ("64k")                                                           | 95  |

|    |      | 5.4.4 Photonics and 14 nm node: 131072 TCUs ("128k x2")                                                  | 96  |

|    |      | 5.4.5 MFC-cooled photonics: more off-chip bandwidth ("128k x4").                                         | 98  |

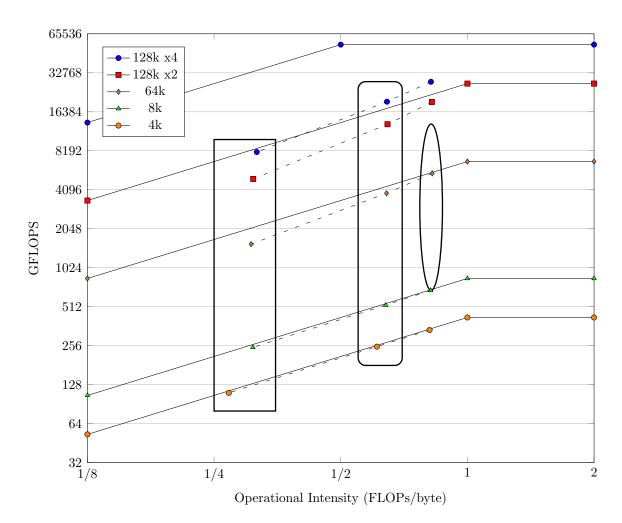

|    | 5.5  | Results                                                                                                  | 98  |

|    |      | 5.5.1 Comparison to FFTW                                                                                 | 99  |

|    |      | 5.5.2 Evaluation using Roofline model                                                                    |     |

|    |      | 5.5.3 Comparison to Edison                                                                               |     |

|    | 5.6  | Conclusion                                                                                               |     |

|    | - •  |                                                                                                          |     |

| 6. | Boos | sted decision trees (XGBoost)                                                                            | 105 |

|    | 6.1  | Introduction                                                                                             | 105 |

|    | 6.2  | Memory architecture of XMT                                                                               | 109 |

|    |      | 6.2.1 Our goal                                                                                           | 109 |

| <ul> <li>6.3 Application: boosted decision trees</li></ul>                                                                                                                                                                                                                                                                                                                                                                   | 111 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

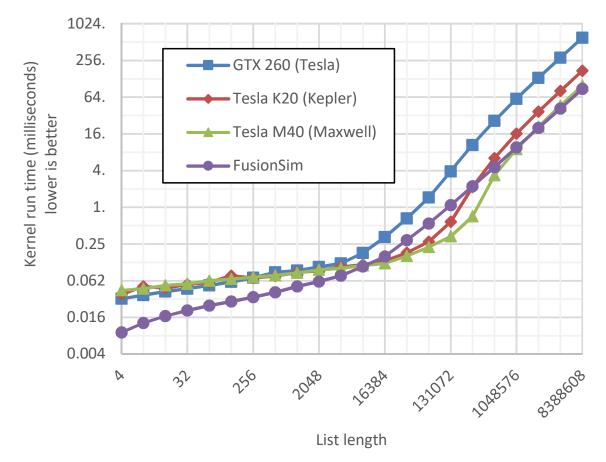

| <ul> <li>6.3.2 Method</li> <li>6.3.3 Speedups</li> <li>6.4 Discussion of design choices</li> <li>6.4.1 Evidence for advances in GPU memory architecture</li> <li>6.4.2 Integrated vs. discrete GPUs</li> <li>6.4.3 Performance on irregular algorithms: list ranking</li> <li>6.4.4 Serial-parallel transition overhead</li> <li>6.4.5 Sensitivity to serial-parallel transition overhead</li> <li>6.5 Conclusion</li> </ul> | 114 |

| <ul> <li>6.3.3 Speedups</li> <li>6.4 Discussion of design choices</li> <li>6.4.1 Evidence for advances in GPU memory architecture</li> <li>6.4.2 Integrated vs. discrete GPUs</li> <li>6.4.3 Performance on irregular algorithms: list ranking</li> <li>6.4.4 Serial-parallel transition overhead</li> <li>6.4.5 Sensitivity to serial-parallel transition overhead</li> <li>6.5 Conclusion</li> </ul>                       | 115 |

| <ul> <li>6.4 Discussion of design choices</li></ul>                                                                                                                                                                                                                                                                                                                                                                          | 118 |

| <ul> <li>6.4.1 Evidence for advances in GPU memory architecture</li> <li>6.4.2 Integrated vs. discrete GPUs</li></ul>                                                                                                                                                                                                                                                                                                        | 120 |

| <ul> <li>6.4.2 Integrated vs. discrete GPUs</li> <li>6.4.3 Performance on irregular algorithms: list ranking</li> <li>6.4.4 Serial-parallel transition overhead</li> <li>6.4.5 Sensitivity to serial-parallel transition overhead</li> <li>6.5 Conclusion</li> <li>7. Boolean satisfiability (SAT)</li> <li>7.1 Preview and introduction</li> <li>7.2 Preliminaries</li> </ul>                                               | 120 |

| <ul> <li>6.4.3 Performance on irregular algorithms: list ranking 6.4.4 Serial-parallel transition overhead 6.4.5 Sensitivity to serial-parallel transition overhead 6.5 Conclusion</li></ul>                                                                                                                                                                                                                                 | 121 |

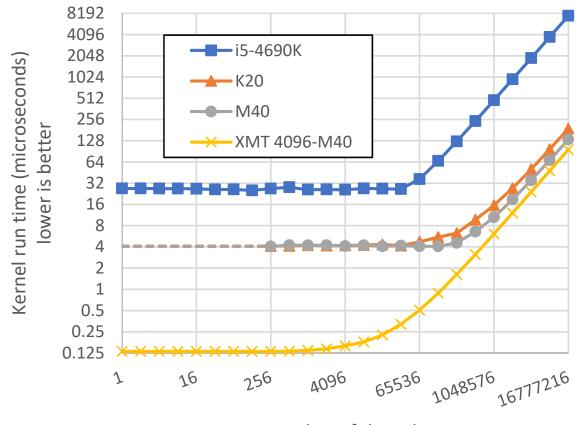

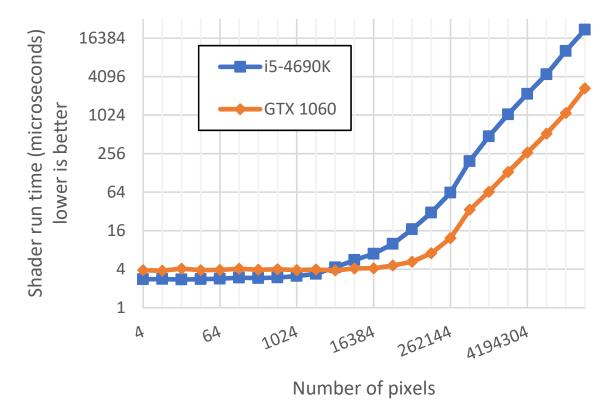

| <ul> <li>6.4.4 Serial-parallel transition overhead</li></ul>                                                                                                                                                                                                                                                                                                                                                                 | 124 |

| 6.4.5       Sensitivity to serial-parallel transition overhead          6.5       Conclusion          7.       Boolean satisfiability (SAT)          7.1       Preview and introduction          7.2       Preliminaries                                                                                                                                                                                                     | 126 |

| 6.5       Conclusion                                                                                                                                                                                                                                                                                                                                                                                                         | 126 |

| <ul> <li>7. Boolean satisfiability (SAT)</li> <li>7.1 Preview and introduction</li> <li>7.2 Preliminaries</li> </ul>                                                                                                                                                                                                                                                                                                         | 129 |

| <ul><li>7.1 Preview and introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                               | 130 |

| <ul><li>7.1 Preview and introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                               | 131 |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 7.2 Convertial CAT column almost three                                                                                                                                                                                                                                                                                                                                                                                       | 136 |

| 7.3 Sequential SAT solver algorithms                                                                                                                                                                                                                                                                                                                                                                                         | 136 |

| 7.4 Parallel SAT solver algorithms                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 7.4.1 Existing opportunities for parallelism exploited by Glucose                                                                                                                                                                                                                                                                                                                                                            |     |

| 7.4.2 Other existing opportunities not exploited by Glucose                                                                                                                                                                                                                                                                                                                                                                  |     |

| 7.4.3 Fine-grained parallelism extracted from Glucose                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.4.4 Further opportunities for parallelism                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 7.4.5 Implementation issues                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 7.4.6 Scaling across nodes                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 7.5 Architectural challenges                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 7.6 Computational model                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 7.7 Empirical results                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8 Literature review                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.1 Sequential SAT solvers                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 7.8.2 Multi-core parallel SAT solvers                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.3 GPU SAT solvers                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.4 Nested parallelism in OpenMP                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 7.8.5 Other software approaches for nested parallelism                                                                                                                                                                                                                                                                                                                                                                       |     |

| 7.8.6 Odds and ends                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 7.9 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8. Characterization of Applications on XMT and GPUs                                                                                                                                                                                                                                                                                                                                                                          | 156 |

| 8.1 Effects of data dependence                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8.2 Tension between work efficiency and data dependence                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.3 Examples                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 9. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                | 163 |

| Published work incorporated into this thesis                                                                                                                                                                                                                                                                                                                                                                                 |     |

## List of Tables

| 2.1 | Specifications of the platforms evaluated in the experiments                                                  | 22  |

|-----|---------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Properties of the graphs used in the experiments                                                              | 26  |

| 2.3 | Speedups of the parallel SV connectivity algorithm                                                            | 28  |

| 2.4 | Speedups of the evaluated biconnectivity algorithms                                                           | 30  |

| 3.1 | Properties of the graphs used in the experiments                                                              | 46  |

| 4.1 | Files in the Large Corpus                                                                                     | 74  |

| 5.1 | XMT Speedups                                                                                                  | 93  |

| 5.2 | XMT Architecture Configurations                                                                               | 94  |

| 5.3 | XMT Physical Configurations                                                                                   | 94  |

| 5.4 | FFT Performance on XMT                                                                                        | 99  |

| 5.5 | Speedups relative to FFTW                                                                                     | 99  |

| 5.6 | Comparison of Edison machine (Cray XC30) to XMT                                                               | 103 |

| 7.1 | Potential speedups for the main nested loop of Glucose on a selection of inputs from the SAT Competition 2018 | 155 |

| 8.1 | List of applications that we speculate can potentially provide speedups on the listed platforms.              | 162 |

# List of Figures

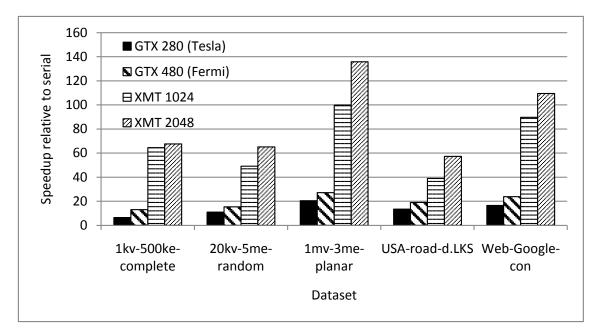

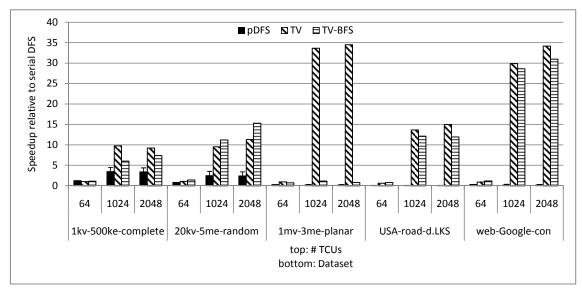

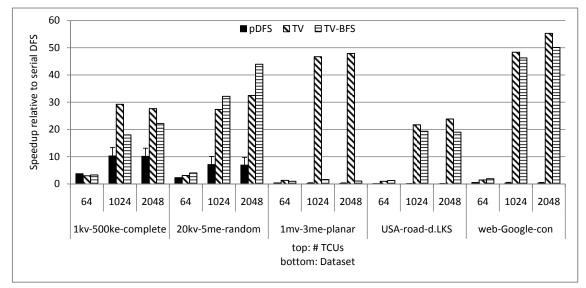

| 2.<br>2.                         |                       | Speedups of the parallel SV connectivity algorithm                                                                    |                                      |

|----------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------|

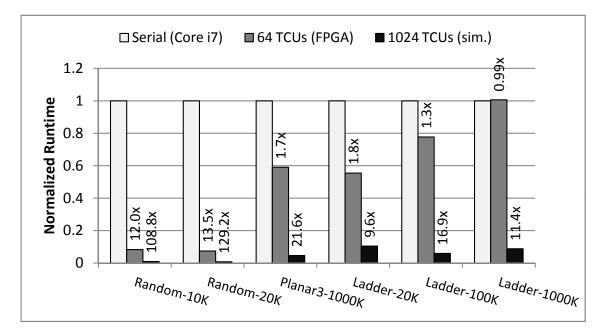

| 3.<br>3.                         |                       | Performance of the parallel triconnectivity algorithm Predicted vs. observed runtime for the 1024-TCU configuration   |                                      |

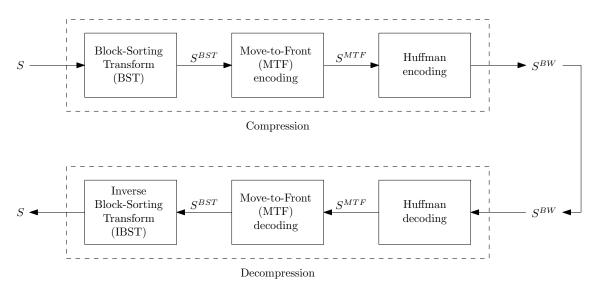

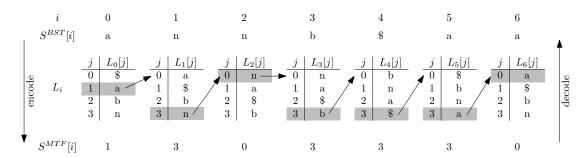

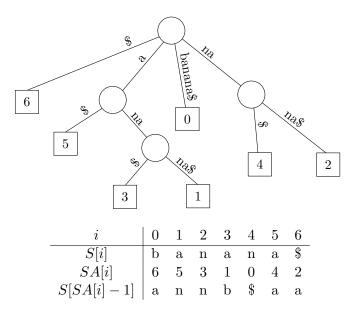

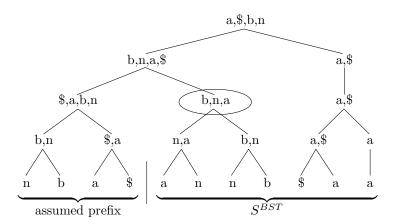

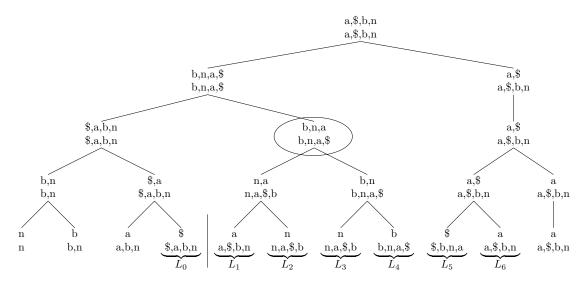

| 4.<br>4.<br>4.<br>4.<br>4.<br>4. | 2<br>3<br>4<br>5<br>6 | Stages of BW compression and decompression                                                                            | . 57<br>. 59<br>. 60<br>. 61<br>. 64 |

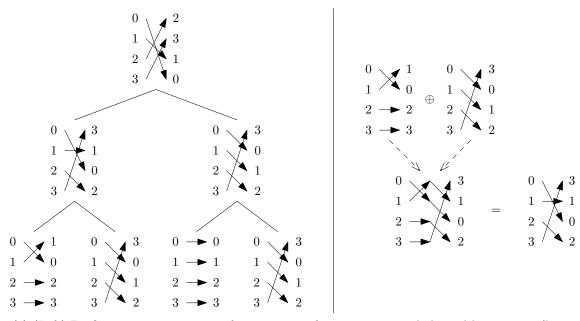

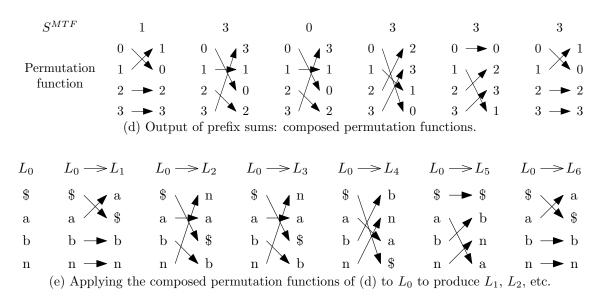

| 4.                               | 8                     | using the operator $\oplus$                                                                                           |                                      |

|                                  | 9                     | Huffman decoding of $S^{BW}$ (from Figure 4.5).                                                                       |                                      |

| 4.                               | 10                    | MTF decoding of $S^{MTF}$ from Figure 4.9                                                                             | . 70                                 |

| 4.                               | 11                    | Speedups obtained using the 64-TCU FPGA prototype                                                                     | . 77                                 |

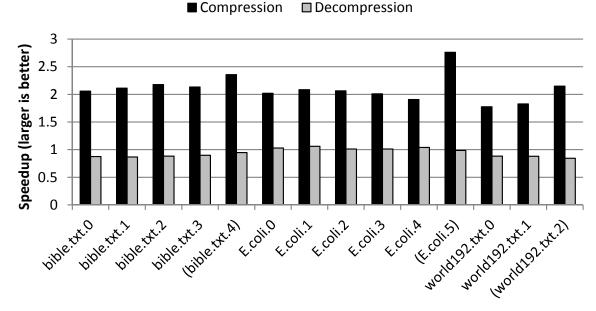

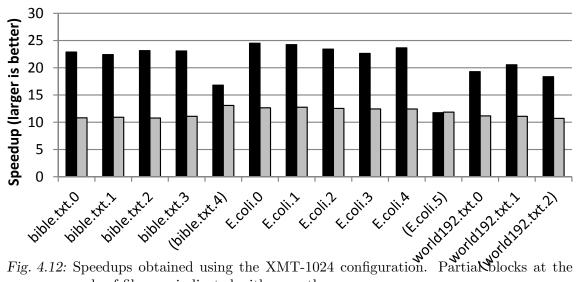

|                                  | .12<br>.13            |                                                                                                                       |                                      |

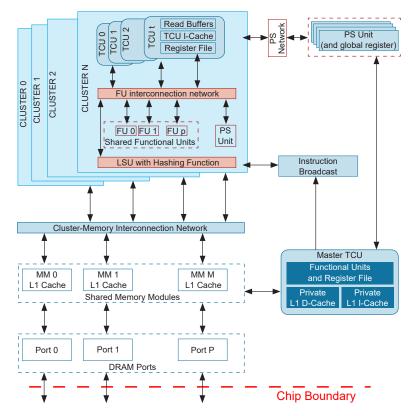

| 5.<br>5.                         |                       | Block Diagram of the XMT Architecture                                                                                 | . 89                                 |

|                                  |                       | 3D FFT                                                                                                                | . 102                                |

| 6.<br>6.                         |                       | Block diagram of hybrid memory architecture of XMT Speedups of XGBoost on various platforms relative to the most pow- | . 111                                |

| C                                | 0                     | erful NVIDIA GPU                                                                                                      | . 121                                |

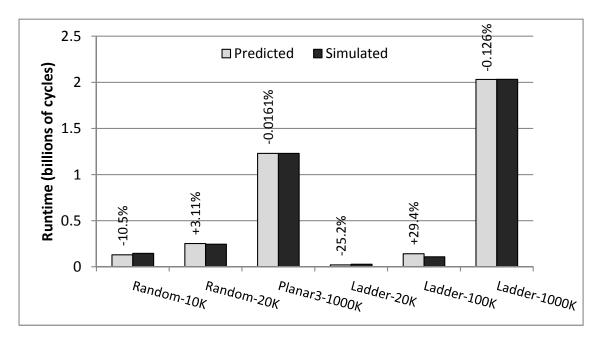

| 6.                               | .3                    | Cycle accuracy of FusionSim (GPGPU-Sim) relative to three NVIDIA<br>GPUs running a list ranking benchmark.            | . 122                                |

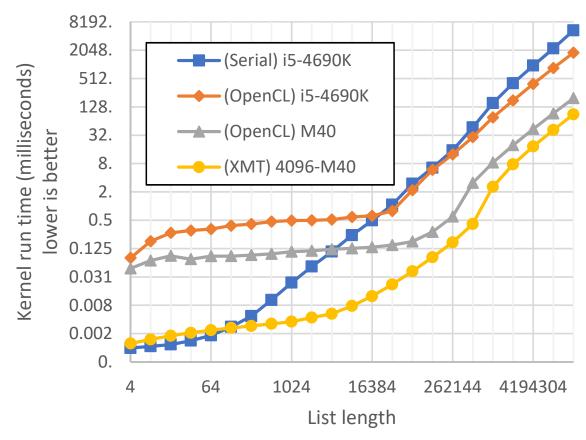

| 6.                               | 4                     | Time taken by various processors on a list ranking benchmark                                                          |                                      |

| 6.                               |                       | Time taken to launch a single empty OpenCL kernel (spawn block on                                                     |                                      |

| 6.                               | 6                     | XMT) with respect to the number of threads launched<br>Time to execute a short OpenGL shader that applies a SAXPY op- | . 127                                |

| υ.                               | 0                     | eration                                                                                                               | . 128                                |

| 6.                               | 7                     | Effect of serial-to-parallel transition (spawn) latency on speedup                                                    |                                      |

|                                  |                       |                                                                                                                       |                                      |

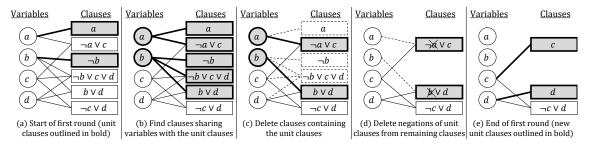

7.1 Unit propagation viewed as a BFS graph traversal in parallel.  $\ldots$  . 141

#### Chapter 1: Introduction

Improvements in the performance of serial processors are reaching a limit due to constraints on power consumption as a result of the end of Dennard scaling. In response to this, computing vendors have produced parallel processors with increasing numbers of cores, and programmers are now expected to employ parallelism in their applications to obtain maximum performance. However, constraints imposed by current computing architectures limit the improvement in performance that can be achieved in many cases.

Despite these limits, current research focuses on off-the-shelf hardware, particularly multi-core CPUs and many-core GPUs. This has led to a chicken-and-egg impasse where vendors look to existing benchmarks to guide architectural improvements while those same benchmarks are built around the limitations of existing hardware. As will be shown in this thesis, attempts to use such hardware to improve the performance of applications beyond simple benchmark kernels have been met with mixed success.

The purpose of this study is twofold: first, to show the speedups that can potentially be obtained for a variety of applications given buildable hardware, and second, to articulate the gap between what such applications require and what existing architectures provide, with the goal of helping to guide the development of future computing platforms. In order to break the above chicken-and-egg impasse, we study the performance of these applications on an experimental architecture in addition to commercial computers. This will help us to identify whether bottlenecks we encounter are inherent to the algorithm or a result of architectural choices.

This study focuses on applications that are challenging for existing platforms. They tend to exhibit *fine-grained* parallelism, which means that threads tend to be short and access small units of data from memory. Furthermore, the parallelism tends to be *irregular*, meaning that the number and length of threads, as well as the memory access patterns, cannot be predicted in advance.

The experimental computer architecture used in this study is the Explicit Multi-Threading (XMT<sup>1</sup>) general-purpose architecture [170], developed at the University of Maryland, which aims to improve single-task completion time and ease-of-programming for parallel applications by supporting Parallel Random Access Model (PRAM) programming [94, 104]. In particular, XMT was designed to efficiently support applications with fine-grained, irregular parallelism.

XMT currently has two embodiments: a 64-core FPGA prototype and a configurable cycle-accurate simulator named XMTSim. XMTSim allows us to study configurations of XMT that would require the same resources (such as silicon area, power, and bandwidth to DRAM) as contemporary platforms for a fair comparison. To further support such comparison, we compare our code on XMT versus results published by others on existing platforms where available to avoid biasing

$<sup>^{1}</sup>$  Not to be confused with the code name Cray XMT used during 2007-2011

the results.

The applications in this study cover a variety of application domains and use various data structures (trees, graphs, strings, vectors) and data types (integer and floating-point). A common theme among all of the parallel algorithms studied here is that each solves the same problem as the best serial algorithm for a given application using asymptotically the same number of operations but with a lower parallel depth.

The remainder of this thesis is organized as follows: Chapters 2 and 3 study biconnectivity and triconnectivity, two advanced graph problems whose parallel algorithms build upon simpler parallel primitives. Chapter 4 studies the Burrows-Wheeler (BW) lossless data compression algorithm and evaluates its potential application to improving effective network bandwidth. Chapter 5 studies the Fast Fourier transform (FFT), a memory-intensive mathematical operation used in digital signal processing. Chapter 6 studies XGBoost, an implementation of the boosted decision tree approach to machine learning; this chapter also examines the trend of multi-core and GPU design towards the same hybrid memory architecture underlying XMT. Chapter 7 studies Boolean satisfiability (SAT), which leads to articulating the need to add efficient support of fine-grained nesting in XMT. Finally, Chapter 9 concludes.

#### Chapter 2: Graph biconnectivity

#### 2.1 Introduction

Given an undirected graph G, two vertices u and v in G are in the same connected component of G if there is a path connecting them, and the graph connectivity problem is finding all connected components of an input graph G. The diameter of a connected graph is the length of the longest path in the set of all shortest paths between every pair of vertices in the graph.

Biconnectivity is a property of undirected graphs; an undirected graph G is called *biconnected* if and only if it is connected and remains so after removing any vertex and all edges incident on that vertex. A graph S is an *induced subgraph* of G if it comprises a subset of the vertices of G and all the edges of G connecting two vertices in S. A *biconnected component* of G is an induced subgraph of G that is biconnected whose vertex set cannot be expanded while maintaining the biconnectivity of its induced subgraph. A vertex whose removal increases the number of connected components in the graph is called an *articulation point*, and an edge whose removal increases the number of connected components is called a *bridge*. In this chapter, the *biconnectivity problem* is understood as the problem of determining the biconnected components, articulation points, and bridges of an undirected graph, and a *biconnectivity algorithm* is an algorithm that solves the biconnectivity problem.

Connectivity is one of the most elementary graph problems. However, for brevity we pay more attention to biconnectivity, the more advanced problem considered in this work. Biconnectivity is an interesting problem to study for two reasons. First, the biconnected components of a graph can reveal useful information about the graph. For instance, if the graph represents a computer network, then a biconnected component of the graph is a subset of the network that will remain connected even if one computer fails, and articulation points (or bridges) are computers (or connections between computers) whose failure will disconnect the network. Second, biconnectivity algorithms are relatively complex: they are among the most advanced algorithms given in parallel algorithms textbooks and nearly the most advanced in serial algorithms textbooks, and biconnectivity or simpler problems were the basis for papers on other parallel computing platforms. Complex algorithms for natural problems may be better predictors of system behavior than the often used small kernels.

In serial computing, depth-first search is regarded as the best biconnectivity algorithm. However, power constraints impose a limit on the maximum performance of serial processors, and parallel processors are becoming the only way to improve performance. Therefore, it is desirable to find an efficient parallel biconnectivity algorithm. When it comes to programming parallel algorithms it is often the case, more so than with serial algorithms, that there is no single algorithm that performs best in all cases (for example, see [43]). Instead, the best algorithm to use could be sensitive to the computing platform and the properties of the input data. In the PRAM theory of parallel algorithms, the two main performance parameters of an algorithm (assuming synchronous execution and availability of as many processors as needed at each step of the algorithms) are: (i) work – the total number of operations performed by an algorithm, and (ii) depth – its number of steps. In the case of graph algorithms, the performance of a given algorithm may depend not only on the size of the input graph, but other properties of the input as well, such as the ratio of edges to vertices or the diameter of the graph.

Given a platform, this suggests viewing all non-dominated biconnectivity algorithms as a "collage" composed of "patches", where each patch represents a particular biconnectivity algorithm and the whole collage is a complete solution to the biconnectivity problem.

To demonstrate this approach, we evaluate three biconnectivity algorithms on the Explicit Multi-Threaded (XMT)<sup>1</sup> architecture developed at the University of Maryland. Because XMT is an experimental platform, we validate it by comparing it to a better established platform that uses similar silicon area, the NVIDIA GPU. We compare XMT to the GTX 280 (based on the older Tesla architecture) and the GTX 480 (based on the newer Fermi architecture) on significant portions of the biconnectivity algorithms for which optimized CUDA code has already been written by other programmers.

A 1024-core version of XMT, which would use a silicon area between that of one and two quad-core Intel Core i7 920 processors, demonstrated cycle count

$<sup>^1</sup>$  Not to be confused with the Cray XMT

speedups of 9x to 33x on biconnectivity relative to a serial biconnectivity algorithm running on the Core i7 920, and further evidence suggests that speedups of 21x to 48x are possible when the investment in the design of the parallel processors matches that of the serial processor. The quantitative contributions of this chapter include

- stronger speedups than in prior parallel biconnectivity studies (9x to 33x vs.

≤4x) across a varied family of graphs and

- stronger speedups on parallel connectivity than GPUs of similar or greater area (between 2x and 4.9x faster than the GTX 480).

Since Cong and Bader [36] appears to provide the most relevant prior work, we discuss the significance of the contributions by relating it to their discussion of the challenges they faced with adopting the Tarjan-Vishkin parallel biconnectivity algorithm to a 12-processor SMP. Cong and Bader noted that: (i) the TV algorithm is representative of many parallel algorithms that take drastically different approaches than the sequential algorithm to solve certain problems, and it employs basic parallel primitives such as prefix sum, pointer jumping, list ranking, sorting, connected components, spanning tree, Euler-tour construction and tree computations, as building blocks; (ii) while prior studies demonstrated reasonable parallel speedups for these parallel primitives on SMPs, they left unclear whether an implementation using these techniques achieves good speedup compared with the best sequential implementation because of the cost of parallel overheads encountered (i.e., of resorting to using all these primitives in the first place instead of doing DFS with a stack, per Hopcroft and Tarjan's original serial algorithm); (iii) looking at the whole algorithm rather than at individual primitives allows focusing on algorithmic overhead instead of communication and synchronization overhead; considering one primitive at a time tends to focus on input representations that do not necessarily fit together when used by a single algorithm; converting representations is not trivial, and incurs a real cost in implementations; and (iv) direct implementation of TV on SMPs fell behind the sequential implementation even at 12 processors. Their conclusion was to follow the major steps of TV, but use different approaches for several of the steps, guided by the challenge of reducing the overheads of TV in order to get ahead of the sequential implementation on the 12-processor SMP.

Our goal is different. While reducing overheads remains important, we try to stay much closer to the original PRAM description of TV taking advantage of the scalable XMT platform that was engineered to accommodate that. It is remarkable that XMT manages to get the strong speedups reported with such a relatively modest silicon budget. Also, our implementation demonstrates for the first time the potential advantage of enhancing XMT by supporting in hardware more thread contexts, perhaps through context switching between them. Namely, the significance of the contributions is

- new evidence supporting the practicality of algorithms derived from parallel random-access machine (PRAM) algorithmic theory for speedups and ease-ofprogramming,

- new evidence demonstrating the advantages of the XMT architecture for the same, and

• the demonstration of a synergistic approach to the design of algorithms and architectures.

The results presented herein are specific to graph connectivity and biconnectivity. Other papers [28, 29] show similar or better speedups for other graph and non-graph problems on XMT. Admittedly, these results do not (and cannot) establish the advantage of XMT for all possible tasks for which one might want to use a general-purpose computer. However, the importance of this work goes a bit beyond just providing one more point of reference. In a similar way that performance, efficiency and effectiveness of a car should not be tested only in first gear, productivity horizons of programming parallel algorithms on a given platform cannot only be studied using elementary algorithms. Graph connectivity problems provide a test case for a proverbial low gear with the more basic graph connectivity algorithms, and higher gear with more advanced graph algorithms for biconnectivity. This and other papers will enable more informed judgment on the overall relative productivity of various approaches. Such documented comparisons will reduce the risk to vendors, allowing them to make better decisions regarding platforms they may want to build.

#### 2.1.1 Related Work

Although no studies of biconnectivity algorithms have previously been published for many-core processors, [36] examines such algorithms on a symmetric multiprocessor (SMP). Also, list ranking and connected components algorithms, two major components of the Tarjan-Vishkin biconnectivity algorithm, are examined in [11] on an SMP and on the Cray MTA.

Another parallel framework that bears limited resemblance to the many-core platforms evaluated here is MapReduce, which uses large clusters of computers to take advantage of massive parallelism in very large problems. This approach was used for estimating the diameter of large graphs in [97], and the potential to adapt PRAM algorithms into computationally feasible MapReduce algorithms was discussed in [99]. However, the applicability of MapReduce to high-end many-core platforms is not clear and the algorithms examined in this chapter are not necessarily optimal for use in distributed systems such as MapReduce.

#### 2.2 Evaluated Algorithms

Given a graph with n vertices and m edges, the biconnectivity problem can be efficiently solved on a serial computer in O(n + m) time with an algorithm by Hopcroft and Tarjan [90] that performs a depth-first search (DFS) on the graph. This algorithm does not appear to have an efficient, poly-logarithmic-time implementation [139]. It is possible to extract some parallelism from this algorithm using the approach outlined in Exercise 36 in [163], and the resulting algorithm, which we will refer to as parallel DFS (pDFS), runs in O(n) time using  $\lceil m/n \rceil + 1$  processors. The main weakness of this algorithm is that the amount of parallelism available depends on the m/n, the "density" of the graph: vertices are processed in serial, and the parallelism available at a vertex is limited by its degree. This algorithm provides little to no parallelism for sparse graphs, where m/n is small. A more scalable alternative is a biconnectivity algorithm given by Tarjan and Vishkin in [156] that runs in  $O(\log n)$  time using O(n + m) processors. The theoretical running time of this algorithm depends only on the size of the graph, not on its structure. This scalability comes at a cost, however: the Tarjan-Vishkin (TV) algorithm performs more operations per vertex and per edge than are required by the serial algorithm or pDFS. Thus, TV may be outperformed by other algorithms in certain situations despite being asymptotically more efficient, especially when running on computer hardware supporting a modest amount of parallelism (e.g. a 4- or 8-core processor).

In these situations, it may be worth modifying TV to be more work efficient. TV is a modular algorithm that calls upon parallel algorithms for simpler problems to do its work. The most significant of these in terms of running time is an algorithm to compute the connected components of an undirected graph (connectivity algorithm). To obtain the complexity bounds in [156], Tarjan and Vishkin used a variation of the Shiloach-Vishkin (SV) connectivity algorithm [145], which runs in  $O(\log n)$  time using O(n + m) processors. This algorithm is efficient in asymptotic terms, but its running time has a large constant factor due to the need to revisit vertices and edges multiple times throughout the algorithm. In some cases, it may be beneficial to use another connectivity algorithm, such as breadth-first search (BFS), in place of SV.

In this chapter, we evaluate three biconnectivity algorithms, which we describe below: parallel depth-first search and two versions of the Tarjan-Vishkin algorithm, one using the SV connectivity algorithm and another using BFS in addition to SV.

#### 2.2.1 Input and Output

The input to a biconnectivity algorithm is an undirected graph G = (V, E)with n = |V| vertices and m = |E| edges. Without loss of generality, we assume that G is connected; if not, the biconnectivity problem can be solved for G by applying a biconnectivity algorithm to each connected component of G. To allow using directly the three biconnectivity algorithms, the input graph is given in the following format:

- Each undirected edge (u, v) in E is represented as a pair of antiparallel directed edges, u → v and v → u. These 2m directed edges are stored in an array edges[2m] sorted by the first endpoint.

- For each directed edge edges<sub>i</sub> = u → v in edges, an array antiparallel[2m]

stores the index j of its antiparallel copy edges<sub>j</sub> = v → u such that antiparallel<sub>i</sub> = j and antiparallel<sub>j</sub> = i.

- An array vertices[n] stores indices into the edges array such that, if vertices[u] = i, then  $edges_i$  is the first edge in edges whose first endpoint is u.

- An array degrees[n], where  $degrees_v$  is the degree of vertex v.

Given the data listed above, the algorithm is expected to produce the following output:

• An array bcc[2m] that identifies the biconnected component to which each edge belongs such that for any pair of edges  $edges_i$  and  $edges_j$ ,  $bcc_i = bcc_j$  if and only if  $edges_i$  and  $edges_j$  are in the same biconnected component.

- An array  $artic_points[a], 0 \le a \le n$  of all the articulation points in G.

- An array  $bridges[b], 0 \le b \le 2m$  of the indices in edges of all the bridges in G.

#### 2.2.2 Parallel Depth-First Search (pDFS)

The intuition behind pDFS is that, although vertices cannot be visited in parallel without potentially violating the order required by a depth-first traversal, edges can be. Initially, all edges are considered *active*. Whenever a vertex is visited in the DFS traversal, all edges leading to that vertex are *canceled*, or removed from the set of active edges. Only active edges are considered when checking for adjacent vertices. Given an input graph in the format described in section 2.2.1, a parallel version of the standard DFS algorithm proceeds as follows:

1. For each vertex v, create a doubly-linked list of its incident edges.

- Using one thread per vertex, create an array head[n] such that head<sub>v</sub> is the index of the first active edge in edges originating from v, or −1 if no such edge exists. Initially, all edges are active, so head<sub>v</sub> ⇐ vertices<sub>v</sub> if degrees<sub>v</sub> > 0 and head<sub>v</sub> ⇐ −1 otherwise.

- Using one thread per edge, create the arrays next[2m] and prev[2m] such that next<sub>i</sub> and prev<sub>i</sub> are the indices in edges of the next and previous active edges, respectively, that originate from the same vertex as edges<sub>i</sub>, or -1 if no such edge exists. Initially, next<sub>i</sub> ⇐ i + 1 and prev<sub>i</sub> ⇐ i 1 with the following exceptions: prev<sub>i</sub> ⇐ -1 if edges<sub>i</sub> is the first edge in edges that shares its origin and next<sub>i</sub> ⇐ -1 if it is the last such edge.

This list contains all of the active edges originating from v.

- 2. Define the procedure dfs(v) as follows:

- (a) In parallel, for every edge edges<sub>i</sub> originating from v, remove edges<sub>j</sub> = w → v, where j = antiparallel<sub>i</sub>, from the doubly-linked list in which it is contained:

- if  $prev_j \neq -1$  then  $next[prev_j] \Leftarrow next_j$  else  $head_w \Leftarrow next_j$

- if  $next_j \neq -1$  then  $prev[next_j] \Leftarrow prev_j$

- (b) While  $head_v \neq -1$ , invoke dfs(w), where  $v \to w = edges[head_v]$ .

- 3. Invoke dfs(r) for some arbitrary vertex r

In order to use DFS to solve the biconnectivity problem, we need two pieces of information about each visited vertex v: its preorder number,  $pre_v$ ; and the smallest preorder number seen while performing DFS on v and its descendants,  $low_v$ . In serial DFS,  $pre_v$  can be computed by keeping track of the number of vertices visited so far in a global variable *count*. Every time a new vertex v is visited,  $pre_v$  is set to *count*, and then *count* is incremented by 1. The value of  $low_v$  is determined by initializing  $low_v$  to  $pre_v$  upon entering v and updating  $low_v$  after (re)visiting a child w as follows:  $low_v \leftarrow min(low_v, low_w)$ .

In pDFS,  $pre_v$  can be computed the same way because the vertices are still visited serially. However,  $low_v$  cannot be because, unlike in serial DFS, visited vertices are never revisited since all edges leading to a visited vertex are always canceled. The key observation that allows us to compute  $low_v$  in parallel is the following: the final value of  $low_v$  is not needed until returning from the visit to v. Therefore,  $low_v$  can be computed just before returning from v as follows:  $low_v \Leftrightarrow min(pre_v, min_{w \in children(v)}(low_w))$ . The remainder of the pDFS algorithm is identical to its serial counterpart.

#### 2.2.3 Tarjan-Vishkin (TV)

The Tarjan-Vishkin biconnectivity algorithm [156] is a PRAM algorithm that was designed as a scalable alternative to DFS. It uses the same principle as the DFS biconnectivity algorithm:3: two edges in a graph are in the same biconnected component if and only if they are on a common simple cycle. However, TV can use any spanning tree, and it performs an Euler tour of the spanning tree to compute information equivalent to that computed in the DFS biconnectivity algorithm. (An Euler tour of a graph is a cycle that visits every vertex in the graph and visits every edge exactly once.) Given an input graph G, TV proceeds as follows:

- 1. Use a parallel connectivity algorithm to find a spanning tree T of G.

- Compute an Euler tour of T', where T' is formed by replacing every undirected edge in T with a pair of antiparallel directed edges. This results in a linked list L of edges in T'.

- 3. Perform list ranking [43] on L to determine the distance of each edge from the end of the Euler tour. Use these distances to determine for each vertex v in T (1) the preorder  $pre_v$  of v in T and (2) the size  $size_v$  of the subtree of Trooted at v.

- 4. For each vertex v, compute  $low_v$  and  $high_v$ . These are the lowest and highest preorder numbers, respectively, of the vertices in the set consisting of v, the descendants of v, and all vertices that are adjacent to v or one of its descendants by an edge in G T.

- 5. Construct an auxiliary graph G', where the vertex set of G' equals the edge set of T and the edge set of G' is constructed as follows, where p(v) denotes the parent of v in T and  $v \to w$  denotes an edge in T such that v = p(w):

- for each edge {v, w} in G − T, add {{p(v), v}, {p(w), w}} to G' if and only if v and w are unrelated in T and

- for each edge  $v \to w$  in T, add  $\{\{p(v), v\}, \{v, w\}\}$  if and only if  $low_w < v$ or  $high_w \ge v + size_v$ .

- 6. Compute the connected components of G'. This defines an equivalence relation on the edges of T such that a pair of edges in T are in the same connected component of G' if and only if they are in the same biconnected component of G.

- 7. Extend the equivalence relation on the edges of T to the edges of G T by defining  $\{v, w\}$  equivalent to  $\{p(w), w\}$  for each edge  $\{v, w\}$  of G - T such that  $pre_v < pre_w$ .

- 8. Identify the bridges in G, which are the edges  $v \to w$  of T such that  $low_w$  and  $high_w$  are both descendants of w.

9. Identify the articulation points in G, which are the vertices of G that exist in more than one biconnected component of G.

In steps (1) and (6), any connectivity algorithm may be used without affecting the correctness of the overall biconnectivity algorithm. The version of this algorithm originally described by Tarjan and Vishkin uses the SV connectivity algorithm; we refer to this version simply as the Tarjan-Vishkin (TV) biconnectivity algorithm.

Our implementation of TV on XMT merits some discussion since it is pathbreaking effort towards dual validation of the XMT platform and PRAM algorithmics. Originally inspired by PRAM algorithmics and its complexity analysis, the long-term objective of the XMT platform was to revisit the more advanced PRAM algorithms and show that their merit transcends theory. Each PRAM algorithm whose implementation beats the competition for the respective problem it addresses would constitute partial accomplishment of this objective. We are not aware of any prior implementation of a biconnectivity algorithm on XMT or any similar platform. Only the concomitant work [28] represents implementation of an algorithm of similar complexity on XMT.

Implementation The high-level description given in the original paper [156] focuses on achieving complexity results, requiring us to find an implementation that provides good performance. In contrast to [36], we leave the core algorithm as is without reducing its available parallelism, but we choose an implementation that minimizes the amount of work done by the algorithm. In steps (1) and (6), we compact the adjacency list every few iterations as more vertices are discovered to be in the same connected component. In step (3), we accelerate the iterations by choosing faster but more work demanding list ranking algorithms for different iterations ("accelerating cascades", [33]). Also, to save work we transition as many computations as possible from the original input graph to the spanning tree.

The following insights were observed in programming the TV PRAM algorithm. They attest that the practical challenge of effectively programming this theoretical parallel algorithm has a similar flavor to the practice of programming serial algorithms and are much simpler than parallel programming approaches such as [39] with their requirements for decomposition, assignment, orchestration and mapping.

- 1. Although the same connectivity algorithm is used in steps (1) and (6), it is worthwhile to code two variants of it: one that saves the spanning tree computed by the connectivity algorithm and one that does not. These two versions take different approaches to handling the arbitrary concurrent writes that result when multiple vertices try to hook on the same vertex. The version that saves the spanning tree needs to know which of the writes succeeded in order to know which edge should be added to the spanning tree. On XMT, this is accomplished by performing a prefix sum to memory on a gatekeeper array. On the other hand, if the spanning tree is not needed, then it is not necessary to know which processor succeeded, and this extra work can be avoided, as the connectivity algorithm is in the common CRCW model.

- 2. The best data structure for storing the spanning tree is the same one as used

for the input graph. This can be derived from the output of step (1) in the following way. Step (1) produces an array T with one entry per edge in the input graph where entry i is 1 if edge i is in the spanning tree and 0 if it is not. The edge list for the spanning tree should be produced by the standard order-preserving PRAM compaction algorithm. The remaining arrays (vertices, degrees, and antiparallel) can then be trivially derived from the corresponding arrays in the input graph. If we use instead a platformspecific optimization (such as prefix sum to registers on XMT) to create the edge list, then we will not be able to derive the necessary tree data structure from the input graph, and it will be difficult to implement the rest of the biconnectivity algorithm (especially the Euler tour) efficiently.

- 3. Depending on the platform, it may be worthwhile to explicitly relabel the vertices in the graph after rooting the spanning tree by creating a new edge array where the entry corresponding to the edge (u, v) contains the entry (preorder(u), preorder(v)). This is an expensive operation up front, but it can save more time in later steps of the algorithm when compared to the alternative of accessing the preorder array each time a relabeled vertex number is needed.

- 4. When computing global low and high numbers for each vertex, it is necessary to find the minima/maxima of some subarrays of preorder numbers. The PRAM algorithms for doing this first find prefix minima/maxima and suffix minima/maxima relative to subarrays that occur naturally as a result of using

a balanced binary tree over an array representing an Euler tour. It has been observed in [162] that a balanced k-ary tree will be more efficient in practice than a balanced binary tree with the exact k depending on the specific machine at hand. Replacing a binary tree by such a k-ary tree generates different subarrays. This implies finding prefix minima/maxima and suffix minima/maxima relative to these subarrays, and to retrieving low and high numbers from them.

#### 2.2.4 Tarjan-Vishkin with a BFS Spanning Tree (TV-BFS)

For some inputs, better performance can be obtained using a connectivity algorithm with worse asymptotic time bounds but a lower constant factor on work, such as breadth-first search (BFS). BFS naturally lends itself to a parallel implementation, and such an implementation runs in  $O(h \log n)$  time and O(n+m) work, where h is the number of layers in the BFS traversal of the graph [50]. The value of h depends on the size and shape of the graph as well as the starting vertex for the traversal, and it can be as large as the diameter of the graph. Notably, for graphs with a diameter that is  $O(\log n)$ , BFS runs in poly-logarithmic time and thus is an asymptotically efficient parallel algorithm. Even on graphs with somewhat larger diameters, BFS can run more quickly than SV due to its lower constant factor, but for graphs with a large diameter relative to the number of vertices (long, thin graphs), there is too little parallelism available for BFS to be efficient.

In theory, BFS can be used in place of SV for computing both the spanning tree of the original graph and the connected components of the auxiliary graph. However, the most natural representation for the auxiliary graph generated by TV is a list of edges in arbitrary order. This representation is not suitable as input to BFS, which requires the graph to be represented as an adjacency list. Therefore, BFS cannot be used to find the connected components of the auxiliary graph as is. It is possible to convert the edge list produced by TV to an adjacency list, but doing so requires sorting the edge list, which reduces or eliminates the benefit of using BFS in place of SV, so we do not consider it further. If the input to the biconnectivity algorithm is in the proper format, BFS can be used in place of SV to find the spanning tree of the input graph, and we call this variation TV-BFS.

#### 2.3 Evaluated Platforms

We briefly review relevant specifics of the computing platforms on which our experiments are performed. A more detailed overview can be found in [29]. Specifications of the specific configurations evaluated can be found in Table 2.1.

#### 2.3.1 GPUs

Though not originally designed for general-purpose computing, modern graphics processing units (GPUs) are capable of being used as highly parallel computing platforms; this usage of GPUs is referred to as general-purpose GPU (GPGPU). Examples of prevalent GPGPU architectures include Tesla and Fermi, both by NVIDIA. GPUs based on the Tesla architecture are widely used, and there are many parallel applications available to run on them. GPUs based on the Fermi architecture are newer, and there are fewer applications optimized specifically for

|                                   | GTX 280            | GTX 480             | XMT-1024           | XMT-2048           |  |  |

|-----------------------------------|--------------------|---------------------|--------------------|--------------------|--|--|

| Principal Computational Resources |                    |                     |                    |                    |  |  |

| Cores                             | $240 \ \text{SP}$  | 480  SP             | 1024  TCU          | 2048 TCU           |  |  |

| Integer Units                     | 240  ALU           | 480 ALU             | 1024 ALU,          | 1024 ALU,          |  |  |

|                                   | +MDU               | +MDU                | 64  MDU            | 64  MDU            |  |  |

| (Floating Point                   | 240 FPU,           | 480 FPU,            | $64  \mathrm{FPU}$ | $64  \mathrm{FPU}$ |  |  |

| Units) <sup><i>a</i></sup>        | $60  {\rm SFU}$    | $60  {\rm SFU}$     |                    |                    |  |  |

| On-chip Memory                    |                    |                     |                    |                    |  |  |

| Registers                         | $1920 \mathrm{KB}$ | $1920 \mathrm{KB}$  | 128KB              | $256 \mathrm{KB}$  |  |  |

| Prefetch Buffers                  | -                  | -                   | 32 KB              | $64 \mathrm{KB}$   |  |  |

| Regular caches                    | 480 KB             | 1728KB <sup>b</sup> | 4104 KB            | 4104 KB            |  |  |

| Constant cache                    | 240 KB             | 120 KB              | $128 \mathrm{KB}$  | $128 \mathrm{KB}$  |  |  |

| Texture cache                     | 496KB              | 120KB               | -                  | -                  |  |  |

<sup>a</sup> None of the algorithms in this chapter use the floating-point units.

<sup>b</sup> 64KB configurable shared memory/L1 cache per SM and 768KB unified L2 cache

Tab. 2.1: Specifications of the platforms evaluated in the experiments (1 KB = 1024 bytes, SP = Streaming Processor, TCU = Thread Control Unit, ALU = Arithmetic/Logic Unit, MDU = Multiply/Divide Unit, SFU = Special Function Unit)

them, though they are backward compatible with applications written for the Tesla architecture.

The Tesla architecture consists of a number of Streaming Multiprocessors (SMs) connected to a number of DRAM controllers and off-chip memory through an interconnection network. An SM consists of a shared register file, shared memory, constant and instruction caches, special function units (SFUs), and a number of streaming processors (SPs) with integer and floating point ALU pipelines. SFUs are 4-wide vector units that can handle complex floating-point operations.

With respect to biconnectivity algorithms, which do not use floating-point operations, the main advantage of the Fermi architecture over Tesla is the addition of L1 and L2 caches. In Fermi, each SM has 64 KB of memory, which can be split into shared memory and L1 cache in one of two ways: 48 KB shared memory and 16 KB L1 cache or 16 KB shared memory and 48 KB L1 cache [3]. There is also a 768 KB L2 cache shared by all the SMs.

For more information about Tesla, see [112], and for Fermi, see [128].

#### 2.3.2 XMT

The Explicit Multi-Threading (XMT) general-purpose computer architecture is designed to improve single-task completion time. It does so by supporting programs based on Parallel Random-Access Machine (PRAM) algorithms but relaxing the synchrony required by the PRAM model. The XMT programming model differs from the strict PRAM model in two ways:

- The PRAM model requires specifying the instruction that will be executed by each processor at each point in time, but XMT uses the work-depth methodology [146], which allows the programmer to specify all of the operations that can be performed at each point in time while leaving to the runtime environment the assignment of those operations to processors.

- 2. The PRAM model requires instructions to be executed in lockstep by all processors at once, but XMT programs follow independence-of-order semantics: parallel sections of code are delimited by spawn-join instruction pairs, and threads only synchronize when they reach the join instruction at the end of the parallel section.

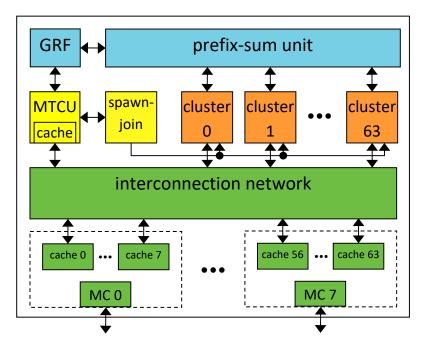

The XMT architecture consists of the following: a number of lightweight cores (TCUs) grouped into clusters, a single core (master TCU or MTCU) with its own local cache, a number of mutually-exclusive cache modules shared by the TCUs and

MTCU, an interconnection network connecting the TCUs to the cache modules, and a number of DRAM controllers connecting the cache modules to off-chip memory. Each TCU has a register file, a program counter, an execution pipeline, and a lightweight ALU. Each TCU also contains prefetch buffers, which can be used by the compiler to prefetch data from memory before it is needed, reducing the length of the sequence of round trips to memory (LSRTM) and improving performance [162]. Each cluster has one or more multiply/divide units (MDUs), floating-point units (FPUs), and a compiler-managed read-only cache, all of which are shared by the TCUs within the cluster. When a parallel section of code is reached, the MTCU broadcasts the instructions in that section to all of the TCUs, and each TCU stores the instructions in a buffer. Virtual threads are assigned to TCUs using a dedicated prefix-sum network.

As noted, a more detailed overview of XMT and the GTX 280 can be found in [29].

#### 2.3.3 Evaluated configurations

The Tesla and Fermi architectures are used in commercially-available products. Therefore, we do not need to establish the practicality of their implementation. We choose the GTX 280 GPU, based on the Tesla architecture, and the GTX 480, based on the Fermi architecture, to represent their respective architectures.