#### ABSTRACT

| Title of dissertation:    | SPECULATIVE DATA<br>DISTRIBUTION IN SHARED<br>MEMORY MULTIPROCESSORS |

|---------------------------|----------------------------------------------------------------------|

|                           | Sean Leventhal                                                       |

| Dissertation directed by: | Professor Manoj Franklin<br>Department of Electrical Engineering     |

This work explores the possibility of using speculation at the directories in a cache coherent non-uniform memory access multiprocessor architecture to improve performance by forwarding data to their destinations before requests are sent. It improves on previous consumer prediction techniques, showing how to construct a predictor that can handle a tradeoff of accuracy and coverage. This dissertation then explores the correct time to perform consumer prediction, and show how a directory protocol can incorporate such a scheme. The consumer prediction enhanced protocol that is developed is able to reduce the runtime of a set of scientific benchmarks by 10%-20%, without substantially reducing the runtime of other benchmarks; specifically, those benchmarks feature simple phased behavior and regularly distribute data to more than two processors.

This work then explores the interaction of consumer prediction with two other forms of prediction, migratory prediction and last touch prediction. It demonstrates a mechanism by which migratory prediction can be implemented using only the storage elements already present in a consumer predictor. By combining this migratory predictor with a consumer predictor, it is possible to produce greater speedups than did either individually. Finally, the signatures of the last touch predictor can be applied to improve the performance of consumer prediction.

## SPECULATIVE DATA DISTRIBUTION IN SHARED MEMORY MULTIPROCESSORS

by

Sean Leventhal

#### Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2008

Advisory Committee: Professor Manoj Franklin, Advisor Professor Donald Yeung Professor Bruce Jacob Professor Charles Silio Professor Alan Sussman © Copyright by Sean Leventhal 2008

#### Dedication

As with most graduate students, this dissertation has consumed days or weeks of my time without mercy. I doubt I would have ever come this far if it were not for my wife, Patty, watching over my shoulder, putting up with me being distracted from the rest of the world, and occasionally drawing me back to it. For every late night of typing and programming she had to put up with, every time she had to deal with all the things I did not have time for, and every time she acted as a sounding board for something very dry, I dedicate this dissertation to my wife, Patty.

### Acknowledgments

I would like to acknowledge a number of people for helping me reach this point:

- My parents for their patient proofreading of something full of words that they could not identify.

- Dr. Franklin for all the time he put in getting me to this point.

# Table of Contents

| List of Figures viii |                                         |                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                   |

|----------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Lis                  | st of .                                 | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                       | xiii                                                              |

| 1                    | Intro<br>1.1<br>1.2<br>1.3              | DeductionMotivationSummary of Work1.2.1Consumer Prediction1.2.2Migratory Prediction1.2.3Timing Prediction1.2.4Combined Coherence PredictionResearch Contributions                                                                                                                                                                                                                                   | $egin{array}{c} 1 \\ 1 \\ 3 \\ 4 \\ 5 \\ 6 \\ 6 \\ 7 \end{array}$ |

| 2                    | Bacl<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Memory Sharing Patterns2.2.1Migratory Data2.2.2Widely Shared Data2.2.2Widely Shared DataMultiprocessor Memory CoherenceCoherence Prediction2.4.1Inward Coherence Prediction2.4.2Outward Coherence Prediction2.4.3Administrative Coherence Prediction                                                                                                                                                |                                                                   |

| 3                    | Exp<br>3.1<br>3.2<br>3.3                | erimental Methodology and TerminologyMeasuring the Performance of Coherence Prediction3.1.1Measuring Prediction Quality3.1.2Measuring System Behavior3.1.3Predictor Naming ConventionsExperimental MethodologyDirectory Protocol Implementation                                                                                                                                                     |                                                                   |

| 4                    | Con<br>4.1                              | sumer Prediction         Theoretical Consumer Prediction Behavior         4.1.1         Consumer Predictor Architecture         4.1.1.1         Perceptron Consumer Prediction Design         4.1.1.2         Consumer Predictor Training         4.1.2         Sensitivity and PVP of Consumer Prediction Schemes         4.1.3         Performance of Predictors Acting on Restricted Information | 54<br>55<br>55<br>55<br>57<br>59<br>62                            |

|   | 4.2 | Struct         | cure of A Consumer Predictor                                                                                                                  | 66  |

|---|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |     | 4.2.1          | Supporting A Consumer Predictor in A Directory Protocol                                                                                       | 66  |

|   |     |                | 4.2.1.1 Coherence and Training Issues                                                                                                         | 66  |

|   |     |                | 4.2.1.2 Implementation Requirements                                                                                                           | 69  |

|   |     | 4.2.2          | Supporting Program Counter Based Techniques                                                                                                   | 71  |

|   |     | 4.2.3          | Directory and Cache Changes to Support Consumer Prediction                                                                                    | 72  |

|   | 4.3 | Behav          | rior of Consumer Prediction                                                                                                                   | 78  |

|   |     | 4.3.1          | Measuring the Behavior of a Consumer Predictor                                                                                                | 78  |

|   |     | 4.3.2          | Varying the Predictor Design                                                                                                                  | 80  |

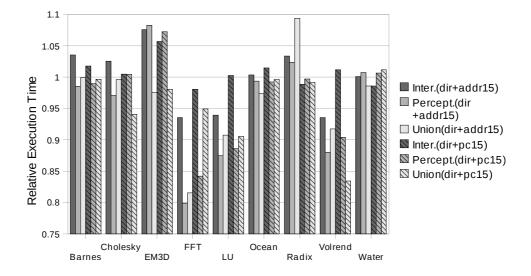

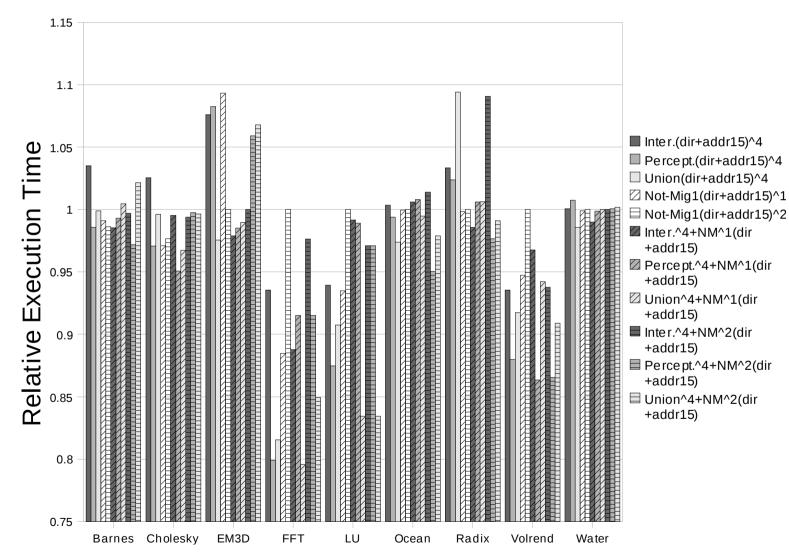

|   |     |                | <ul><li>4.3.2.1 Runtime Results Across Varying Predictor Designs .</li><li>4.3.2.2 Message Transmission Results Across Varying Pre-</li></ul> | 81  |

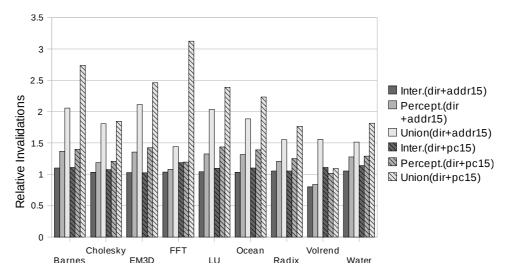

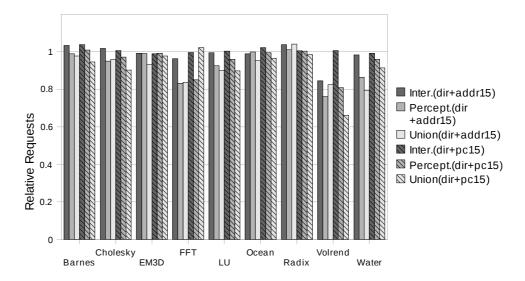

|   |     |                | dictor Designs                                                                                                                                | 82  |

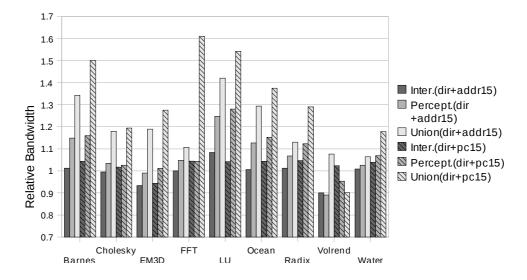

|   |     |                | 4.3.2.3 Bandwidth Usage Results Across Varying Predictor                                                                                      |     |

|   |     |                | Designs                                                                                                                                       | 87  |

|   |     |                | 4.3.2.4 Miss Rates Across Varying Predictor Designs                                                                                           | 88  |

|   |     |                | 4.3.2.5 Response Time Results Across Varying Predictor De-                                                                                    |     |

|   |     |                | signs                                                                                                                                         | 90  |

|   |     | 4.3.3          | Tying Processor Number Into the Indexing Scheme                                                                                               |     |

|   |     |                | 4.3.3.1 Writer-Mixing                                                                                                                         |     |

|   |     |                | 4.3.3.2 Address-Mixing                                                                                                                        |     |

|   |     | 4.3.4          | Global Consumer Prediction                                                                                                                    |     |

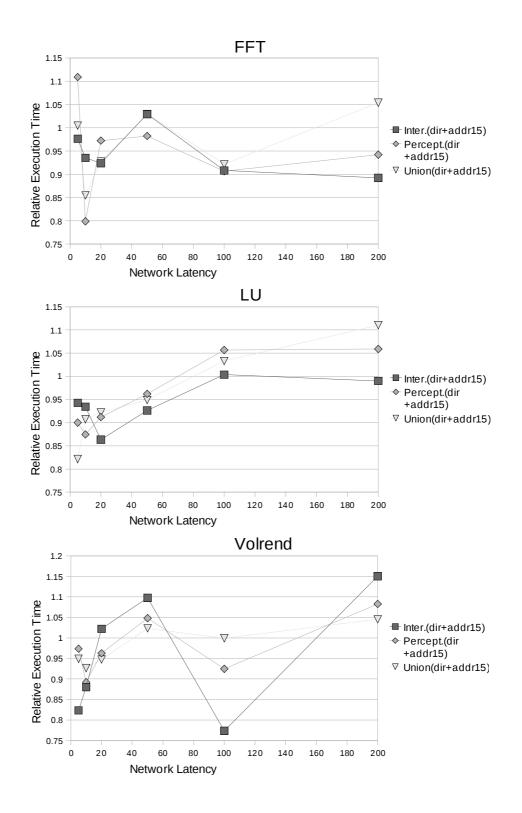

|   |     | 4.3.5          | Variance of Network Latency                                                                                                                   |     |

|   |     |                | 4.3.5.1 Runtime Results                                                                                                                       |     |

|   |     |                | 4.3.5.2 Effect on Message Transmission                                                                                                        |     |

|   |     |                | 4.3.5.3 Bandwidth Usage                                                                                                                       |     |

|   |     |                | 4.3.5.4 Directory Response Time                                                                                                               |     |

|   |     | 4.3.6          | Relationship Between Benchmark and Predictor Performance . 1                                                                                  |     |

|   | 4.4 |                | g the Perceptron                                                                                                                              |     |

|   |     | 4.4.1          | Varying the Perceptron Threshold                                                                                                              |     |

|   |     | 4.4.2          | Training a Perceptron With Non-Existent Data                                                                                                  |     |

|   | 4.5 |                | ing Confidence Estimation to Consumer Prediction 1                                                                                            |     |

|   |     | 4.5.1          | Supporting A Confidence Estimator                                                                                                             | 117 |

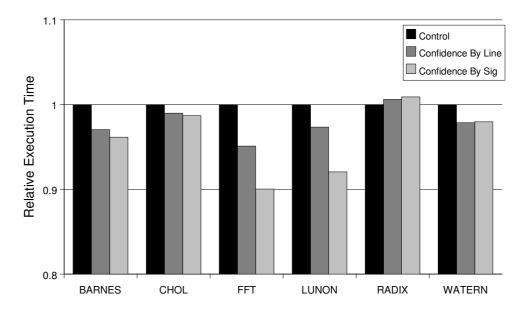

|   |     | 4.5.2          | Performance of Confidence Estimated Address-Indexed Con-                                                                                      |     |

|   |     | a              | sumer Prediction                                                                                                                              |     |

|   | 4.6 | Summ           | nary                                                                                                                                          | 119 |

| 5 | Mic | ratory I       | Prediction 1                                                                                                                                  | 121 |

| 0 | 5.1 | •              | tory Consumer Predictor Architecture                                                                                                          |     |

|   | 0.1 | 5.1.1          | Predictor Architecture                                                                                                                        |     |

|   |     | 5.1.1<br>5.1.2 | Protocol Modification                                                                                                                         |     |

|   | 5.2 | -              | ss Based Migratory Consumer Predictors                                                                                                        |     |

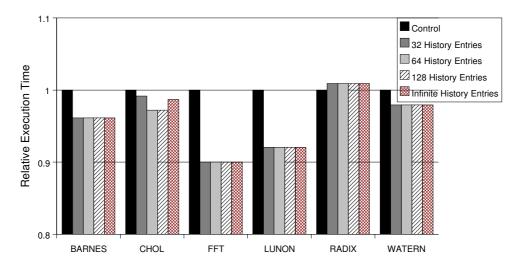

|   | 0.4 | 5.2.1          | Effects of History Depth on Migratory Prediction                                                                                              |     |

|   |     | 5.2.1<br>5.2.2 | Preventing Lock-In in Migratory Prediction                                                                                                    |     |

|   |     | 0.4.4          | 5.2.2.1 State Additions                                                                                                                       |     |

|   |     |                | 5.2.2.1 State Additions                                                                                                                       |     |

|   |     |                | 0.2.2.2 Instory rable woundation                                                                                                              | பல  |

|   |            |         | 5.2.2.3   | History Table Corruption                             | . 134 |

|---|------------|---------|-----------|------------------------------------------------------|-------|

|   |            |         | 5.2.2.4   | Not-Migratory Counters                               | . 134 |

|   |            | 5.2.3   | Results   | of Lock-In Prevention Mechanisms                     | . 135 |

|   | 5.3        | Instru  | ction Bas | ed Migratory Consumer Predictors                     | . 139 |

|   |            | 5.3.1   | Naive Ir  | nstruction-Based Migratory Prediction                | . 140 |

|   |            | 5.3.2   | Second-   | Look Instruction-Based Migratory Prediction          | . 141 |

|   |            | 5.3.3   | Forward   | l-Ahead Second-Look Instruction-Based Migratory Pre  | ;-    |

|   |            |         | diction   |                                                      | . 143 |

|   |            | 5.3.4   | Second-   | Look Instruction-Based Migratory Prediction          | . 145 |

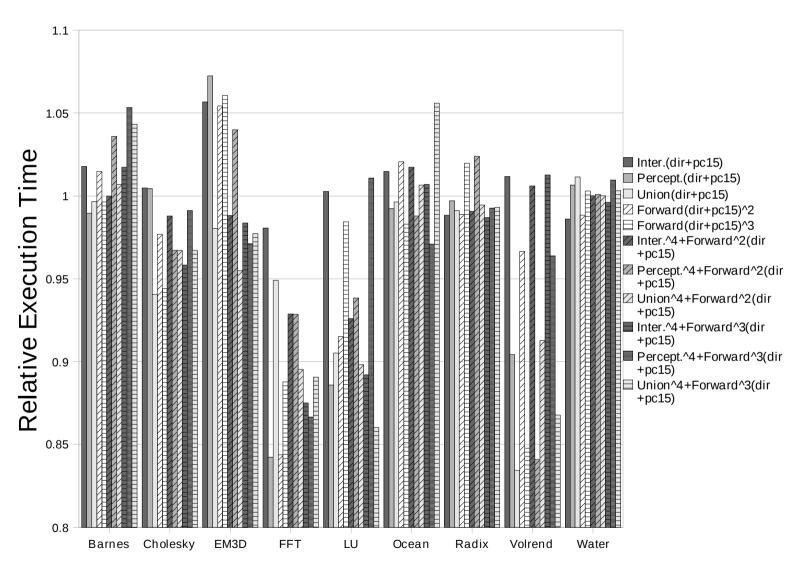

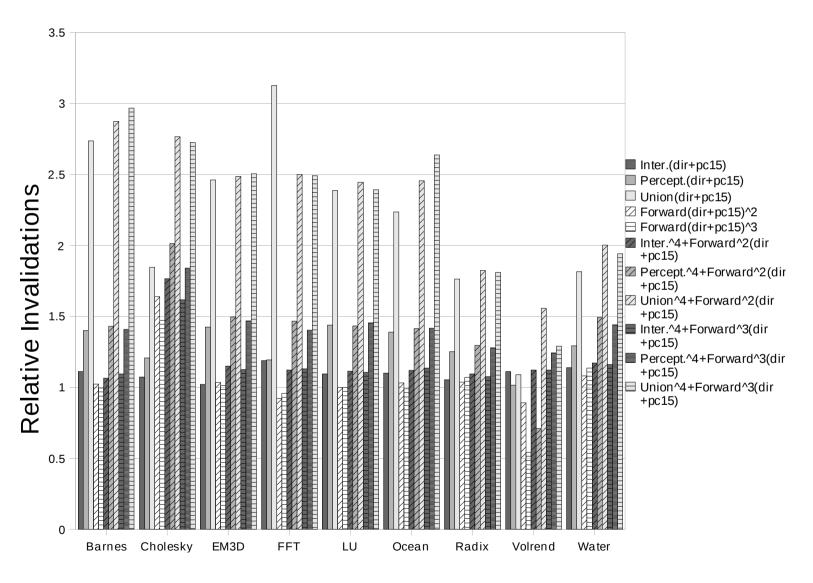

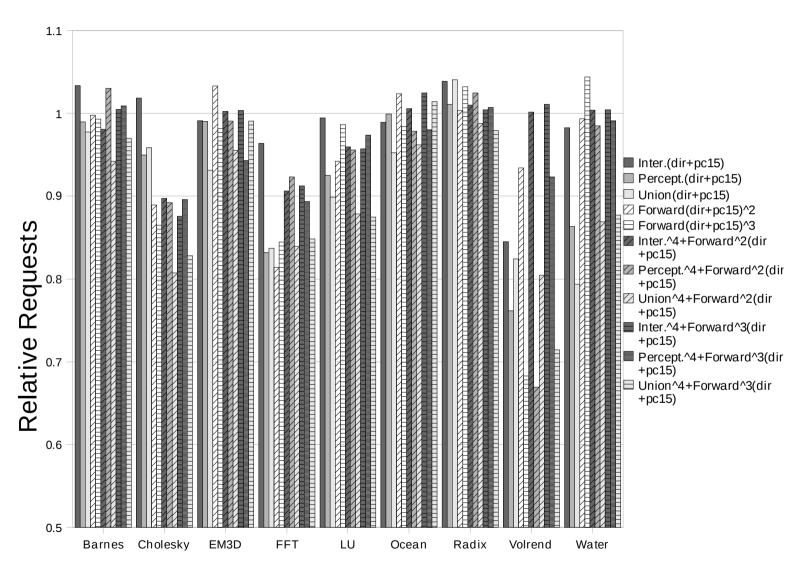

|   |            |         | 5.3.4.1   | Interprocessor Message Effects of Instruction Based  |       |

|   |            |         |           | Prediction                                           | . 146 |

|   |            |         | 5.3.4.2   | Bandwidth Effects of Instruction Based Migratory     |       |

|   |            |         |           | Prediction                                           | . 148 |

|   |            |         | 5.3.4.3   | Directory Latency of Instruction Based Migratory     |       |

|   |            |         |           | Prediction                                           | . 149 |

|   |            |         | 5.3.4.4   | Miss Rate of Stores With Migratory Prediction in U   | se150 |

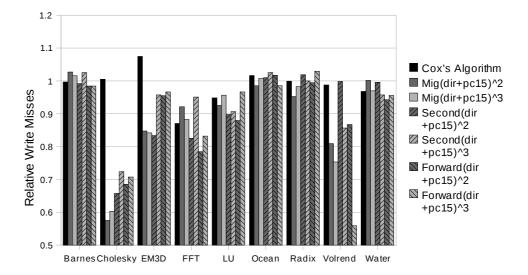

|   |            |         | 5.3.4.5   | Miss Rate of Instruction Based Migratory Predictio   | n 151 |

|   | 5.4        | Indexi  | ng a Mig  | ratory Predictor With Mixed Information              | . 151 |

|   |            | 5.4.1   |           | -Mixed Migratory Prediction                          |       |

|   |            | 5.4.2   | CPU-M     | ixed Migratory Prediction                            | . 152 |

|   | 5.5        | Summ    | ary       |                                                      | . 153 |

| c | T.         | · D     | 1         |                                                      | 150   |

| 6 |            | ing Pre |           |                                                      | 156   |

|   | 6.1        |         |           |                                                      |       |

|   |            | 6.1.1   | 0         | s to the Directory And Cache to Support Self Invali- |       |

|   |            | C 1 0   |           | · · · · · · · · · · · · · · · · · · ·                |       |

|   |            | 6.1.2   | -         | g The System                                         |       |

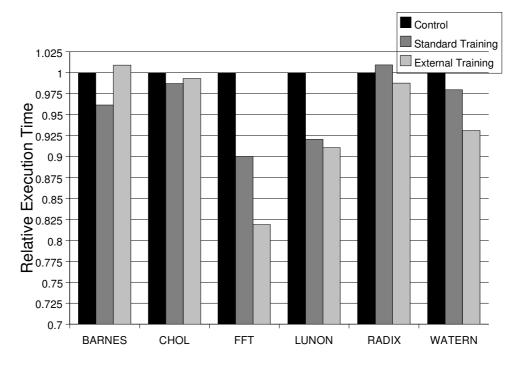

|   |            |         | 6.1.2.1   | 8                                                    |       |

|   |            | 019     | 6.1.2.2   | 0                                                    |       |

|   | <i>c</i>   | 6.1.3   |           | ry of Training Variation                             |       |

|   | 6.2        |         | -         | Predictors with Last Touch Signatures                |       |

|   |            |         |           | er Prediction                                        |       |

|   | <i>C</i> 0 | 6.2.2   | 0         | ry Prediction                                        |       |

|   | 6.3        | Summ    | ary       |                                                      | . 170 |

| 7 | Con        | bining  | Coherenc  | e Prediction Mechanisms                              | 178   |

|   | 7.1        | Potent  | ial Bene  | fits of Combining Migratory Prediction With Con-     |       |

|   |            | sumer   | Predictio | on                                                   | . 179 |

|   | 7.2        | Impler  | nenting a | a Joint Consumer/Migratory Predictor                 | . 179 |

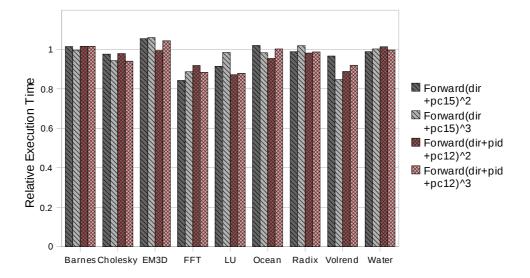

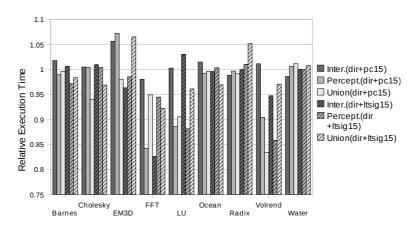

|   | 7.3        |         | -         | d Joint Consumer/Migratory Prediction                |       |

|   |            | 7.3.1   |           | ion-Indexed Joint Consumer/Migratory Prediction .    |       |

|   | 7.4        | Summ    |           | · · · · · · · · · · · · · · · · · · ·                |       |

|   |            |         |           |                                                      |       |

| 8   | Conclusions 1 |                      |  |  |  |

|-----|---------------|----------------------|--|--|--|

|     | 8.1           | Consumer Prediction  |  |  |  |

|     | 8.2           | Migratory Prediction |  |  |  |

|     | 8.3           | Timing Prediction    |  |  |  |

|     | 8.4           | Combined Prediction  |  |  |  |

|     | 8.5           | Future Work          |  |  |  |

| Bil | oliogr        | aphy 195             |  |  |  |

# List of Figures

| 2.1 | Migratory Sharing Example                                                | 14 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Widely Shared Data Example                                               | 15 |

| 2.3 | Five Different Categories of Coherence Events                            | 27 |

| 2.4 | Many Readers To One Writer Ideal Speculative Behavior                    | 30 |

| 2.5 | The ideal behavior of last touch prediction on an MROW event $\ . \ .$ . | 31 |

| 2.6 | The ideal behavior of an ILT on a MROW event                             | 32 |

| 3.1 | Measurements of Prediction Quality                                       | 35 |

| 3.2 | Simulation Parameters Used                                               | 40 |

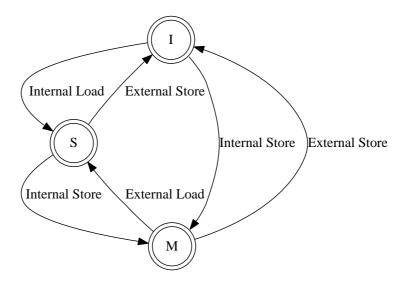

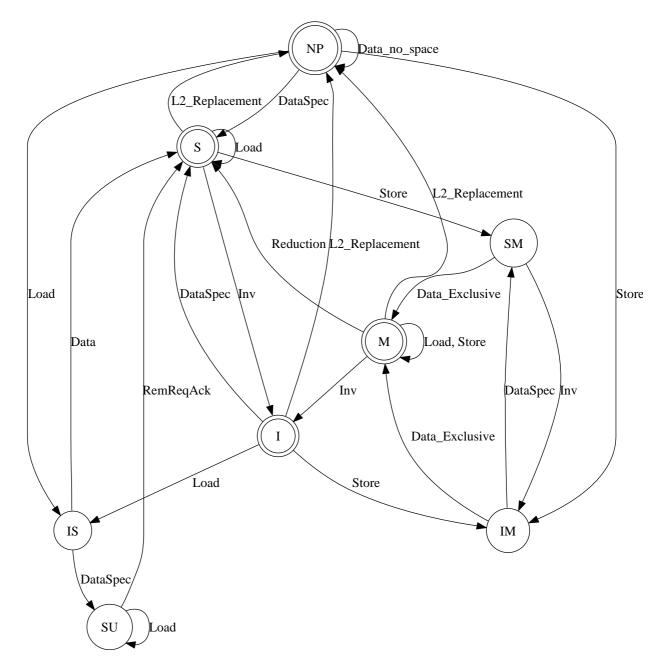

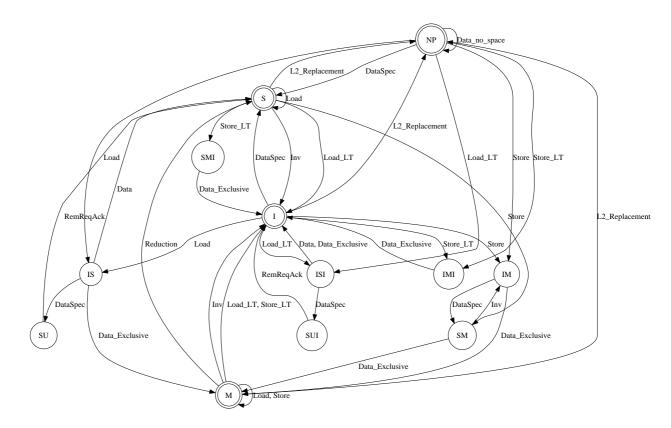

| 3.3 | State Transition Diagram of an MSI Protocol                              | 43 |

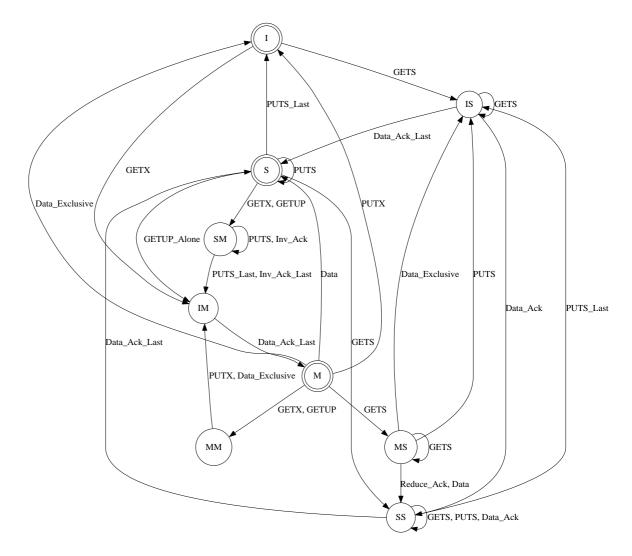

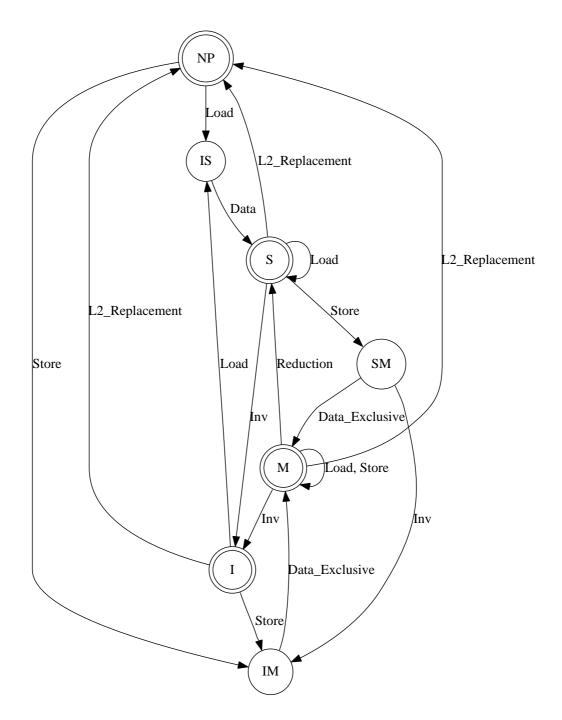

| 3.4 | States of the Cache                                                      | 46 |

| 3.5 | States of the Directory                                                  | 47 |

| 3.6 | Cache Events                                                             | 48 |

| 3.7 | Directory Events                                                         | 49 |

| 3.8 | Directory State Machine                                                  | 50 |

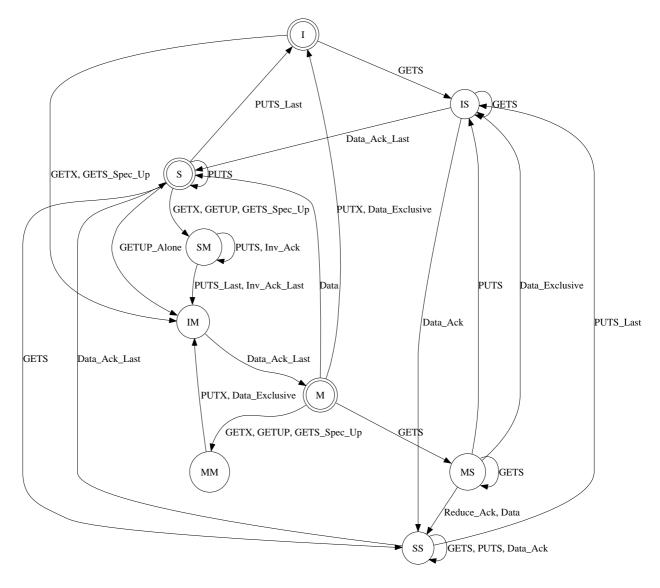

| 3.9 | Cache State Machine                                                      | 51 |

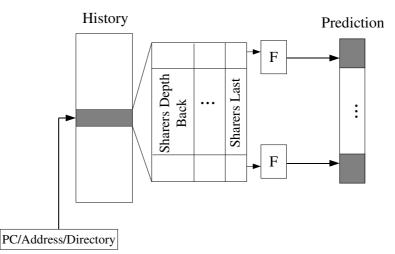

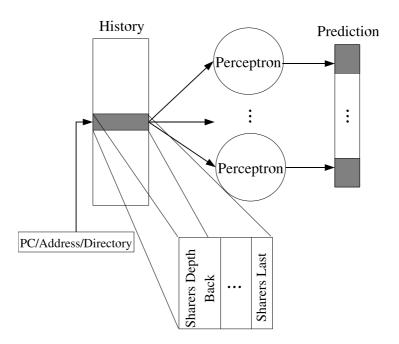

| 4.1 | General Consumer Predictor Architecture                                  | 54 |

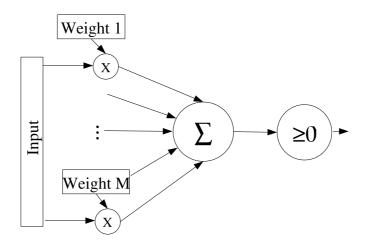

| 4.2 | Perceptron Consumer Predictor Architecture                               | 56 |

| 4.3 | Structure of a Perceptron Predictor                                      | 57 |

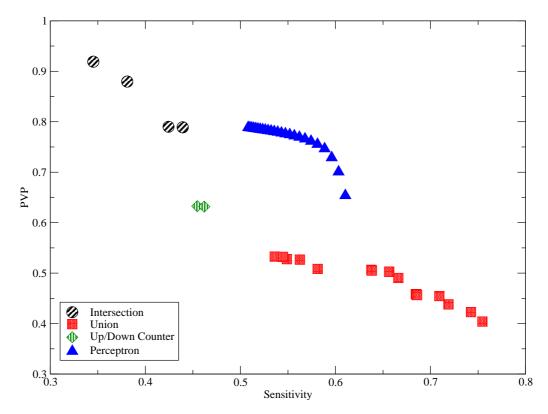

| 4.4 | Co-optimal Consumer Predictors by Trace Performance                      | 61 |

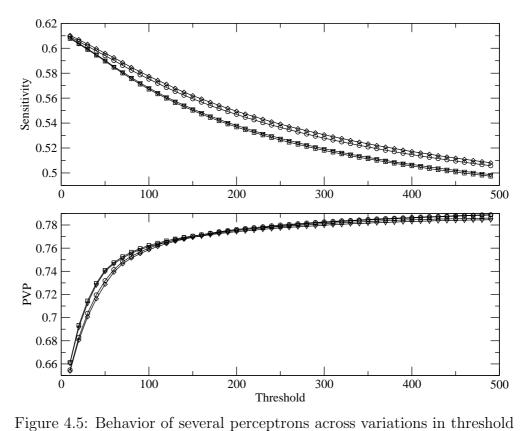

| 4.5 | Behavior of several perceptrons across variations in threshold           | 63 |

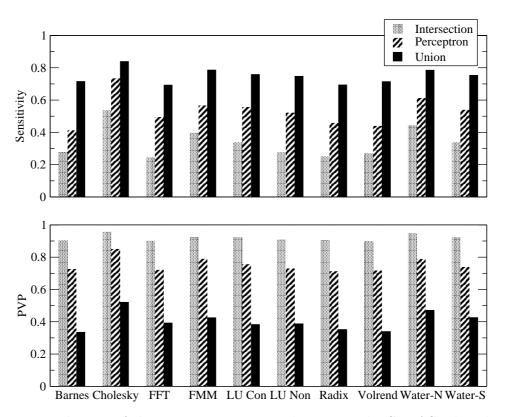

| 4.6 | Trace Based Consumer Predictor Behavior by Benchmark                     | 64 |

| 4.7 | Cache-Consumer Predictor Race Conditions                                 | 68 |

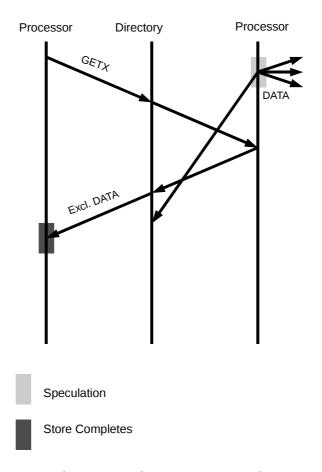

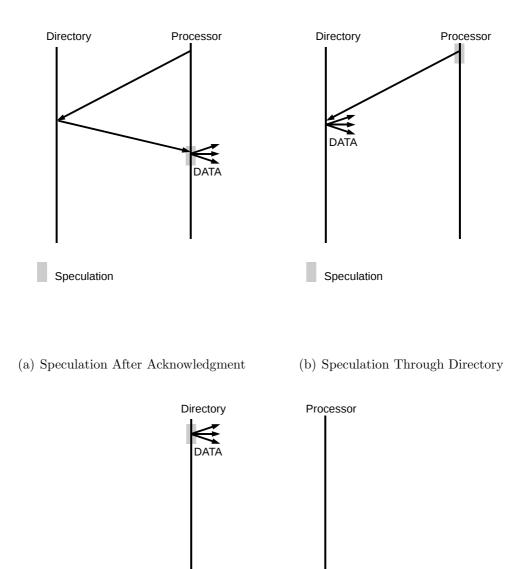

| 4.8  | Three options for implementing speculative data forwarding 70 |

|------|---------------------------------------------------------------|

| 4.9  | Consumer Prediction Cache States                              |

| 4.10 | Consumer Prediction Cache Events                              |

| 4.11 | Consumer Prediction Cache State Machine                       |

| 4.12 | Example of Consumer Prediction Behavior                       |

| 4.13 | Predictor Designs Considered Here                             |

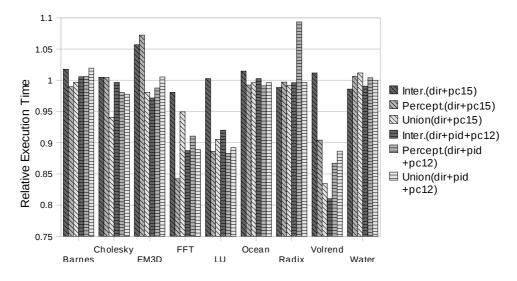

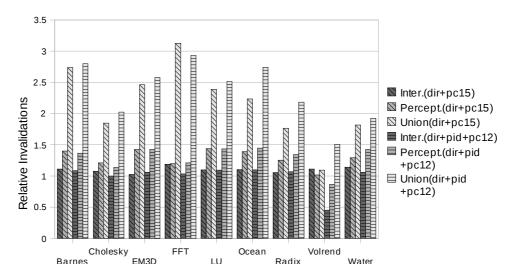

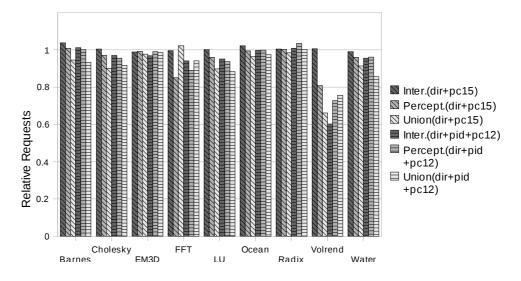

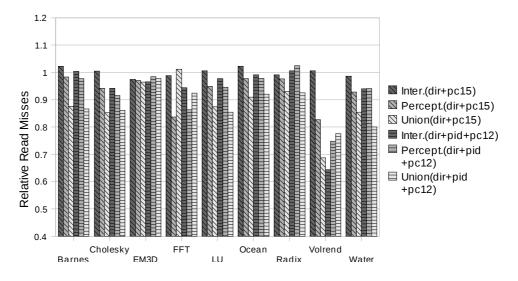

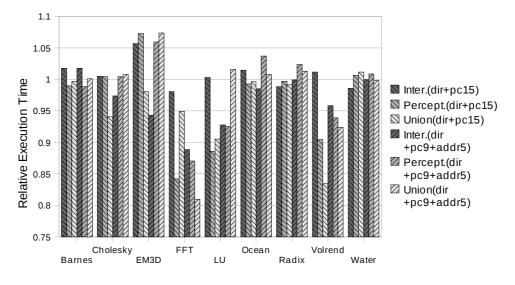

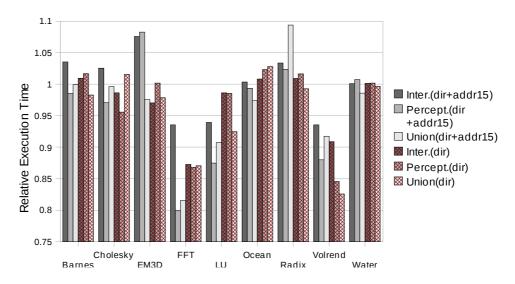

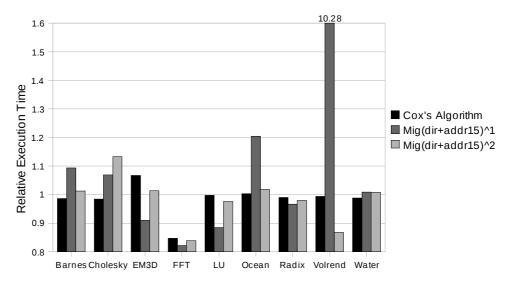

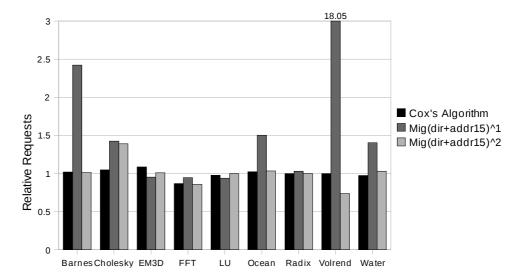

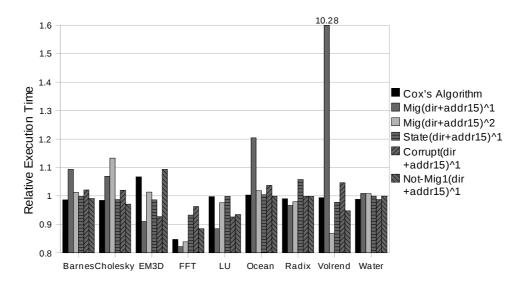

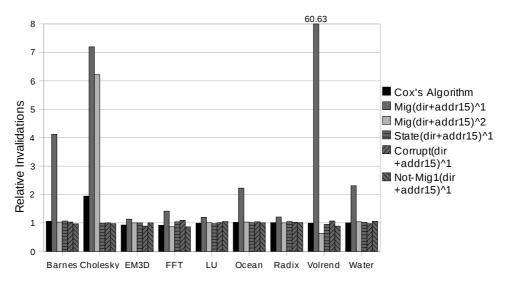

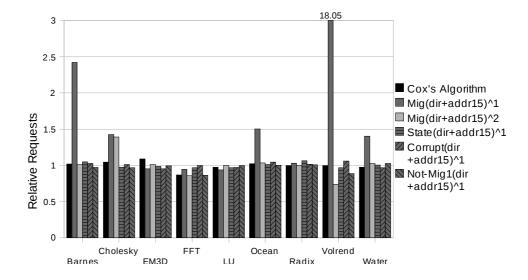

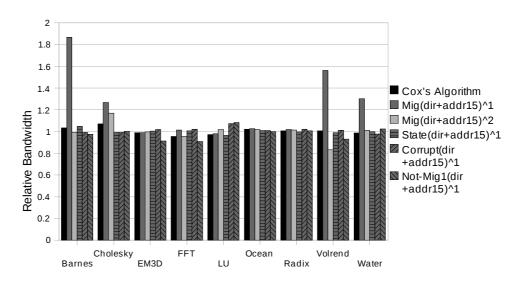

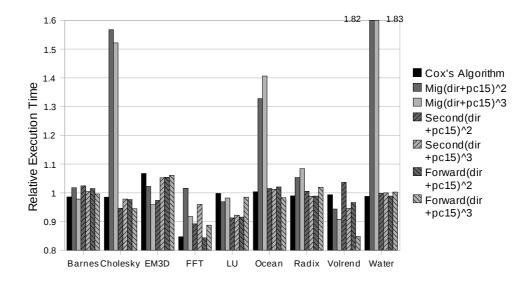

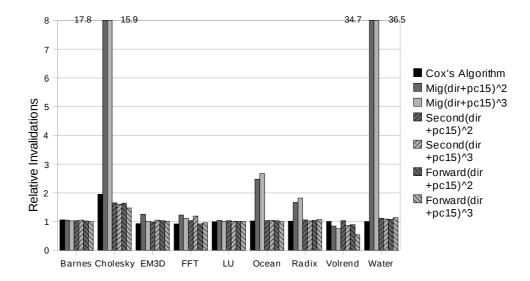

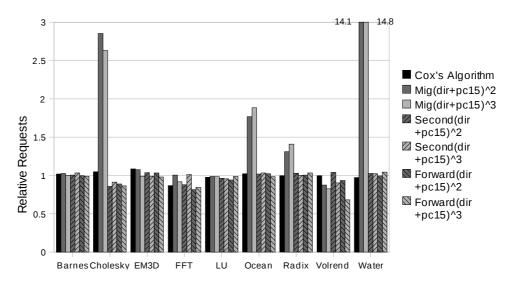

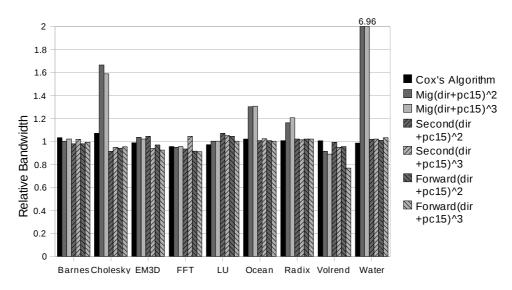

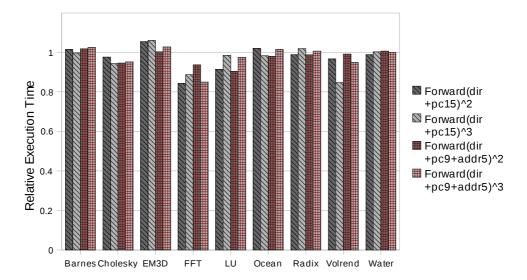

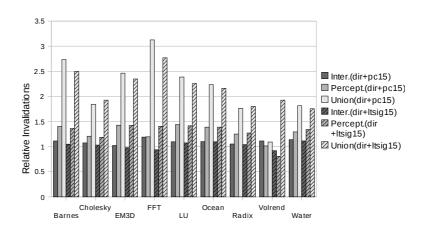

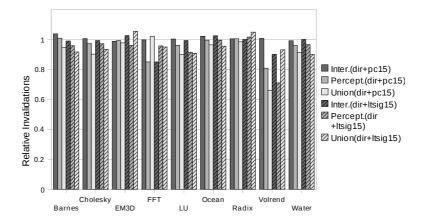

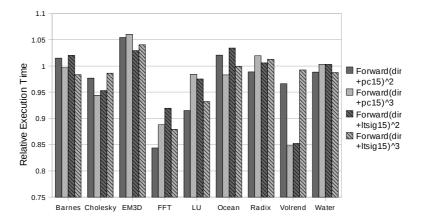

| 4.14 | Consumer Prediction Relative Execution Time                   |

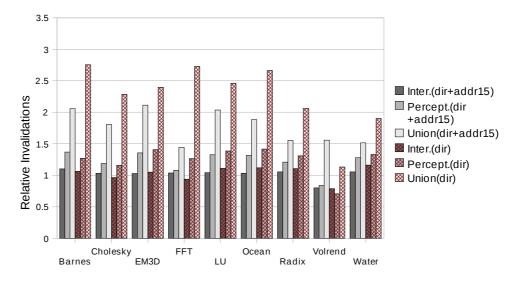

| 4.15 | Consumer Prediction Relative Invalidations                    |

| 4.16 | Consumer Prediction Relative Requests                         |

| 4.17 | Consumer Prediction Relative Bandwidth                        |

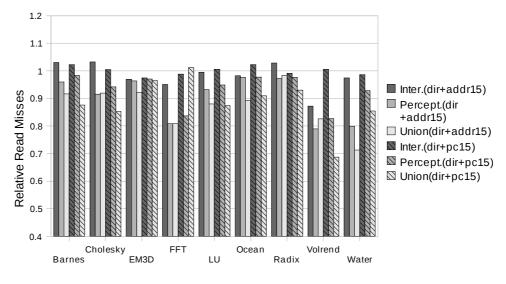

| 4.18 | Consumer Prediction Relative Read Misses                      |

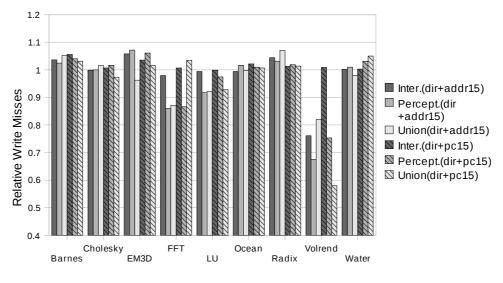

| 4.19 | Consumer Prediction Relative Write Misses                     |

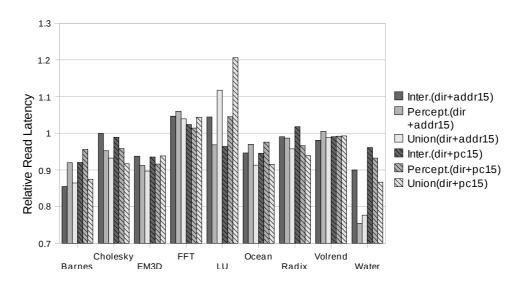

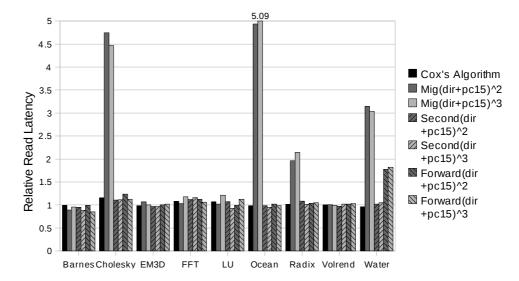

| 4.20 | Consumer Prediction Read Latency                              |

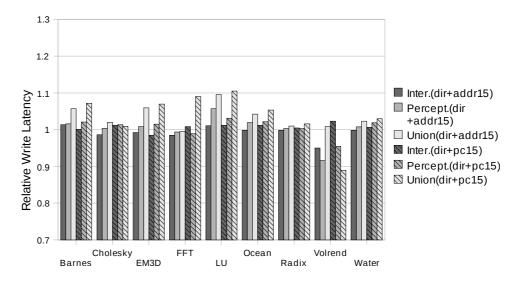

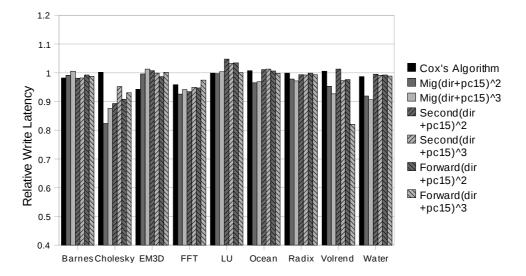

| 4.21 | Consumer Prediction Write Latency                             |

| 4.22 | Runtime of Mixed Writer-Instruction Indexing                  |

| 4.23 | Invalidation Count of Mixed Writer-Instruction Indexing 95    |

| 4.24 | Request Count of Mixed Writer-Instruction Indexing            |

| 4.25 | Read Miss Rate of Mixed Writer-Instruction Indexing           |

| 4.26 | Runtime of Mixed Address-Instruction Indexing                 |

| 4.27 | Runtime Benefits of Global Prediction                         |

| 4.28 | Global Prediction Invalidation Count Changes                  |

| 4.29 | Consumer Prediction Runtime Across Network Latency            |

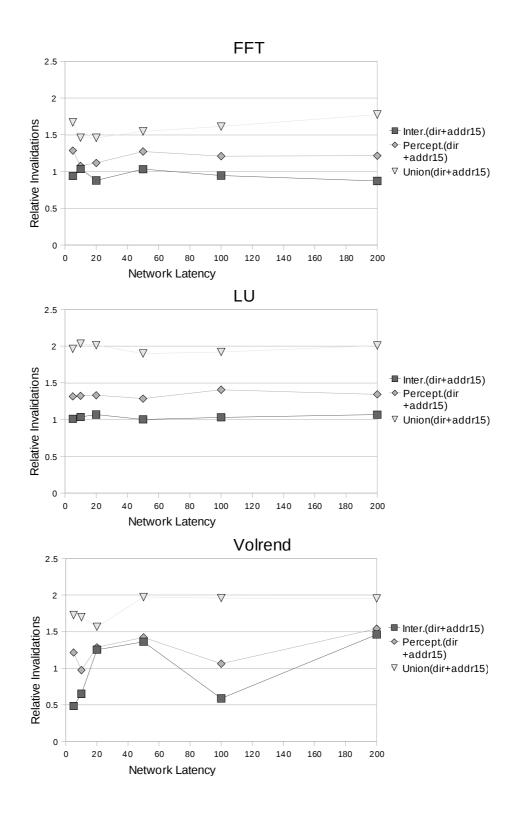

| 4.30 | Consumer Prediction Invalidations Across Network Latency 106  |

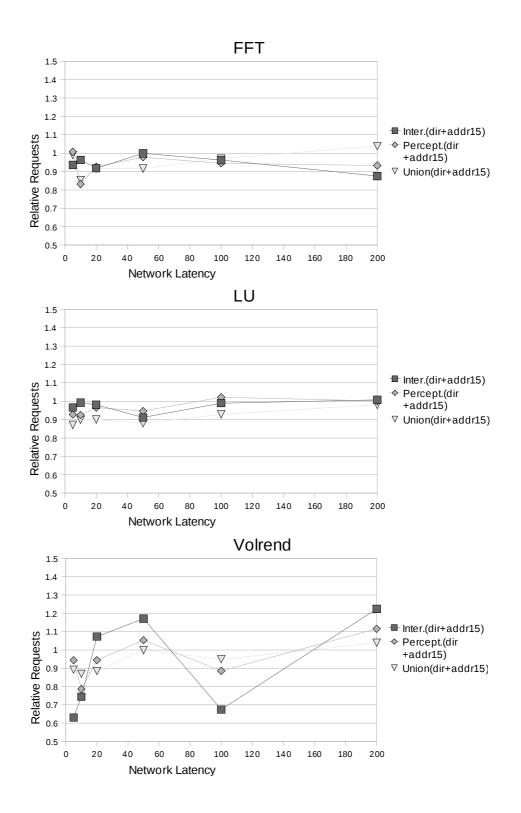

| 4.31 | Consumer Prediction Requests Across Network Latency           |

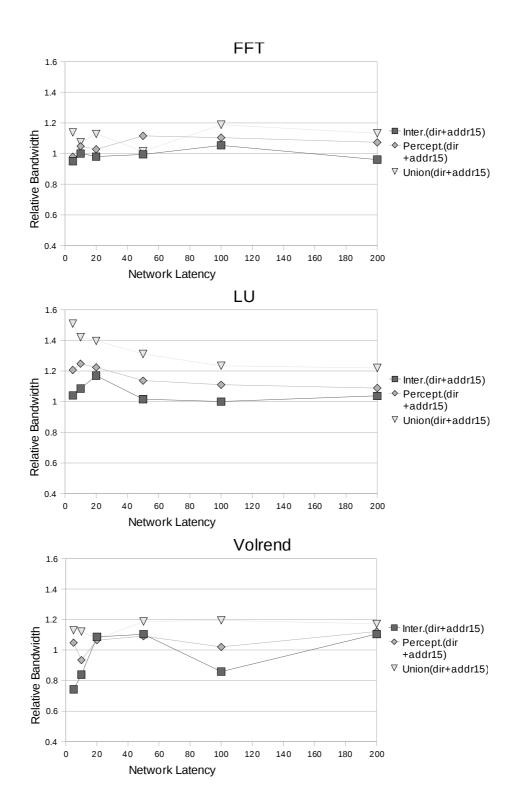

| 4.32 | Consumer Prediction Bandwidth Across Network Latency 109      |

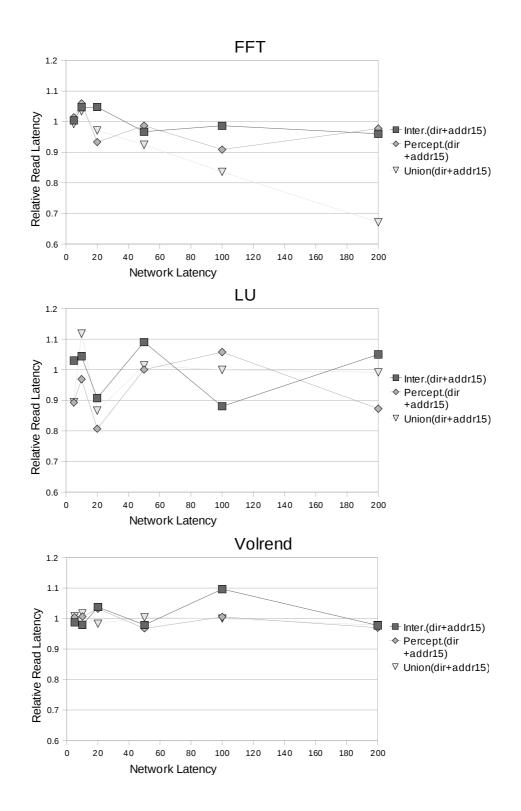

| 4.33 Consumer Prediction Read Latency Across Network Latency 111                      |

|---------------------------------------------------------------------------------------|

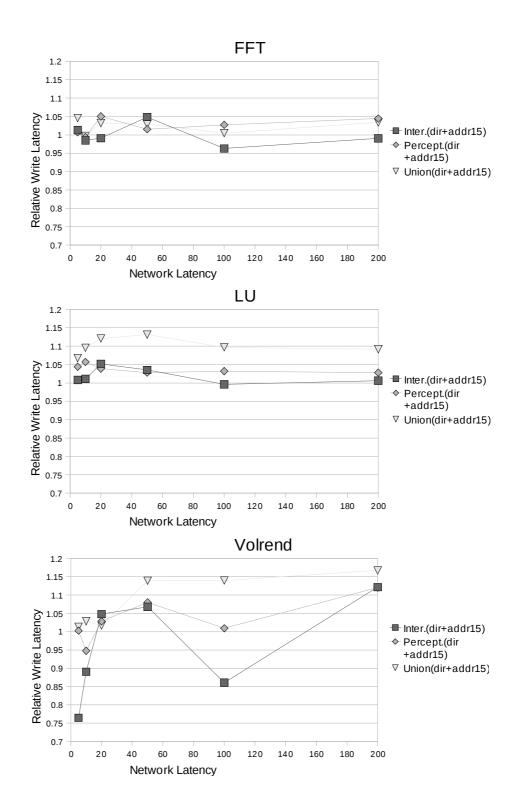

| 4.34 Consumer Prediction Write Latency Across Network Latency 112                     |

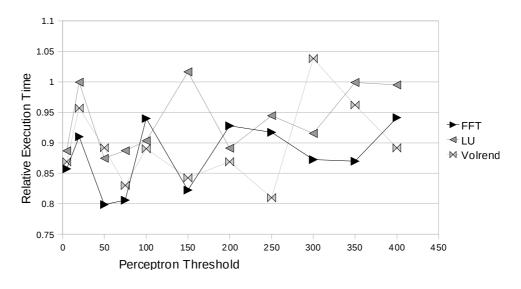

| 4.35 Effects of Varying Perceptron Threshold on Runtime                               |

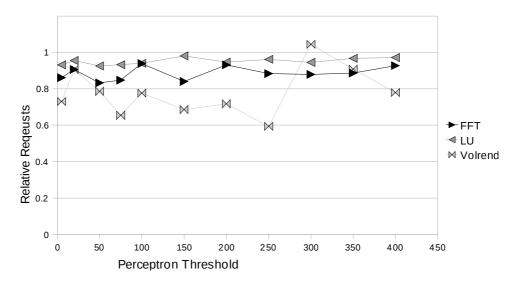

| 4.36 Effects of Varying Perceptron Threshold on Request Count 115                     |

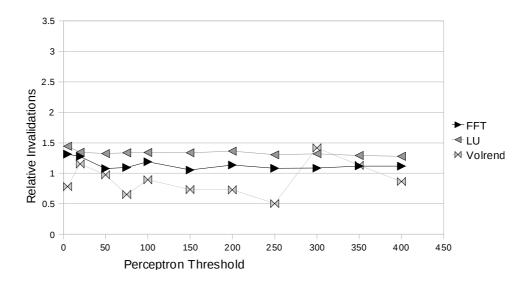

| 4.37 Effects of Varying Perceptron Threshold Invalidation Count $\ldots$ . 116        |

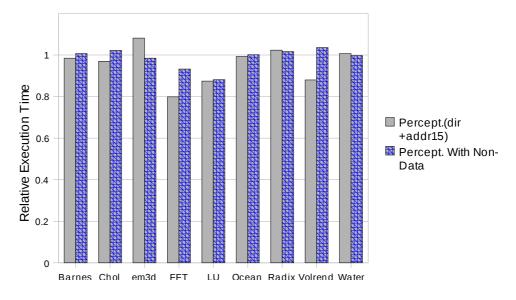

| 4.38 Benefits of Perceptron Recognizing "Non-Data"                                    |

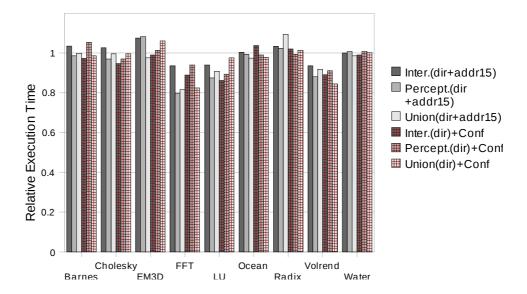

| 4.39 Confidence Estimated Consumer Prediction Performance                             |

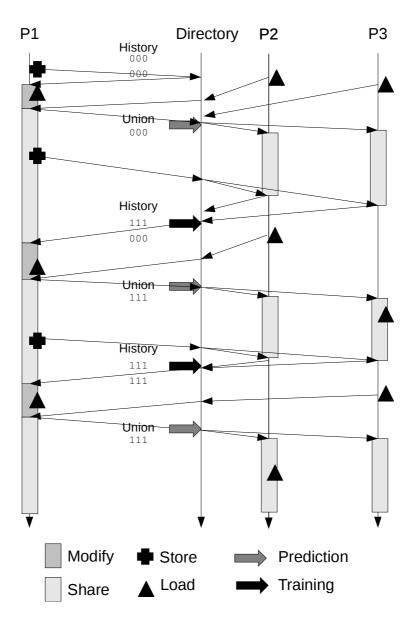

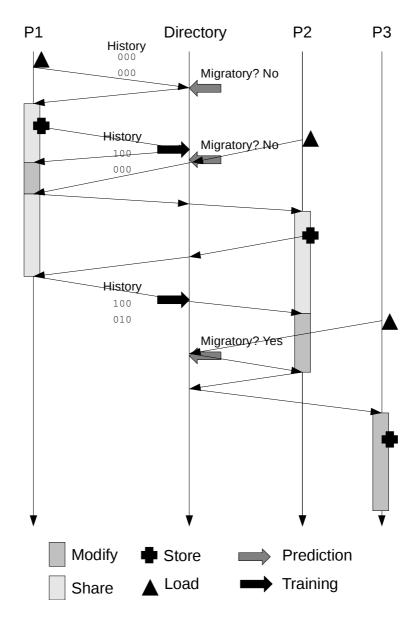

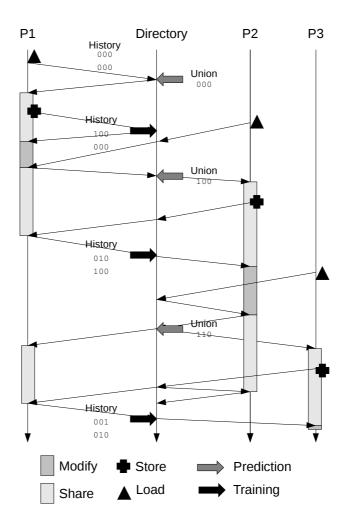

| 5.1 Example of Migratory Prediction                                                   |

| 5.2 Migratory Prediction Directory Events                                             |

| 5.3 Migratory Prediction Cache Events                                                 |

| 5.4 Migratory Prediction Cache State Machine                                          |

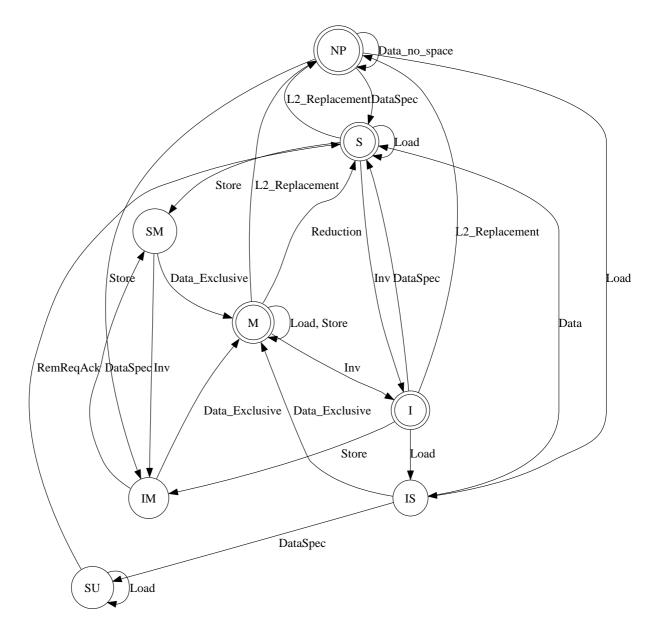

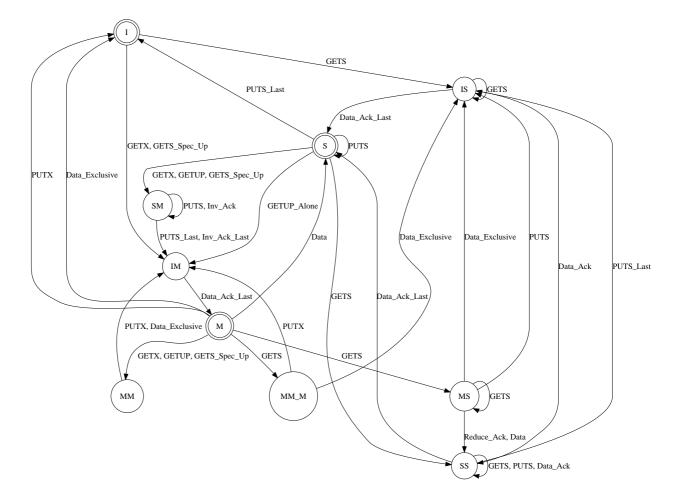

| 5.5 Migratory Prediction Directory State Machine                                      |

| 5.6 Address-Indexed Migratory Prediction Performance                                  |

| 5.7 Address-Indexed Migratory Prediction Request Count                                |

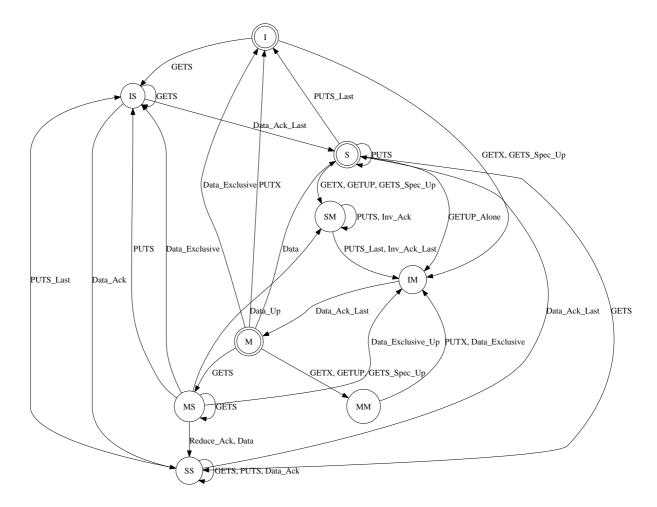

| 5.8 Directory Protocol of State Additions Scheme                                      |

| 5.9 "Lock-in" Preventing Migratory Prediction Runtime                                 |

| 5.10 "Lock-in" Preventing Migratory Prediction Invalidation Count 136                 |

| 5.11 "Lock-in" Preventing Migratory Prediction Request Count 137                      |

| 5.12 "Lock-in" Preventing Migratory Prediction Bandwidth                              |

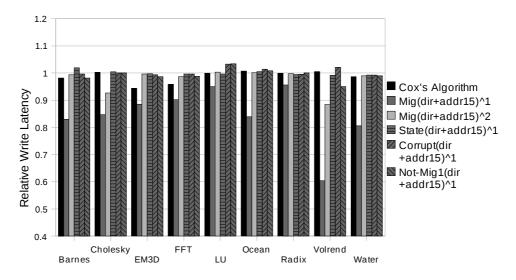

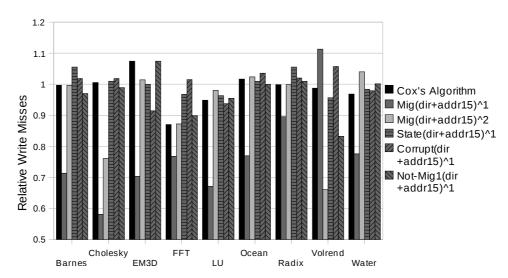

| 5.13 "Lock-in" Preventing Migratory Prediction Write Latency 138                      |

| 5.14 "Lock-in" Preventing Migratory Prediction Write Miss Count 139                   |

| 5.15 Naive Instruction-Indexed Migratory Prediction Performance 142                   |

| 5.16 Migratory Prediction Directory Events with PC information $\ldots \ldots 143$    |

| 5.17 Migratory Prediction Directory State Machine with PC information $% 100$ . $144$ |

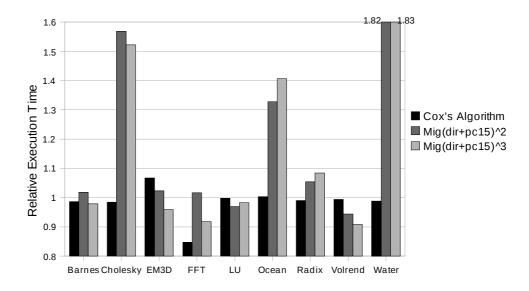

| 5.18 Instruction-Indexed Migratory Prediction Runtime                                  |

|----------------------------------------------------------------------------------------|

| 5.19 Instruction-Indexed Migratory Prediction Invalidation Count 147                   |

| 5.20 Instruction-Indexed Migratory Prediction Request Count                            |

| 5.21 Instruction-Indexed Migratory Prediction Bandwidth                                |

| 5.22 Instruction-Indexed Migratory Prediction Read Latency                             |

| 5.23 Instruction-Indexed Migratory Prediction Write Latency $\ldots \ldots \ldots 150$ |

| 5.24 Instruction-Indexed Migratory Prediction Write Miss Count $\ .\ .\ .\ .$ . 151    |

| 5.25 Address-Instruction Mixed Migratory Prediction                                    |

| 5.26 CPU-Instruction Mixed Migratory Prediction                                        |

| 6.1 Speculative Self Invalidation Example                                              |

| 6.2 The structure of Lai and Falsafi's Last Touch Predictor                            |

| 6.3 Self Invalidation Cache States                                                     |

| 6.4 Self Invalidation Cache Events                                                     |

| 6.5 Self Invalidation Cache State Machine                                              |

| 6.6 Self Invalidation Confidence Estimator Design Tradeoff                             |

| 6.7 Self Invalidation Training Logic Size Tradeoff                                     |

| 6.8 Externally Trained Self Invalidation Performance                                   |

| 6.9 Externally Trained Self Invalidation Message Counts                                |

| 6.10 LastTouch-Indexed Consumer Prediction Runtime                                     |

| 6.11 LastTouch-Indexed Consumer Prediction Invalidation Count $\ldots \ldots 173$      |

| 6.12 LastTouch-Indexed Consumer Prediction Request Count                               |

| 6.13 LastTouch-Indexed Migratory Prediction Runtime                                    |

| 7.1 Example of Poor Consumer Predictor Performance                                     |

| 7.2 Address-Indexed Combined Migratory/Consumer Runtime                                |

| Hudros indexed combined ingratory/consumer function                                    |

- 7.3 Instruction-Indexed Combined Migratory/Consumer Runtime . . . . 186

- 7.4 Instruction-Indexed Combined Migratory/Consumer Invalidations . . 187

- 7.5 Instruction-Indexed Combined Migratory/Consumer Requests . . . . 188

# List of Abbreviations

| CMP                  | Chip Multiprocessor                      |

|----------------------|------------------------------------------|

| CC-NUMA              | Cache Coherent Non-Uniform Memory Access |

| $_{\rm FN}$          | False Negative                           |

| $\operatorname{FP}$  | False Positive                           |

| ILT                  | Invalidation Lines Table                 |

| MPM                  | Message Passing Multiprocessor           |

| MROW                 | Many Readers To One Writer               |

| MSI                  | Modified-Shared-Invalid                  |

| NUMA                 | Non-Uniform Memory Access                |

| OROW                 | One Reader To One Writer                 |

| OWMR                 | One Writer To Many Readers               |

| OWOR                 | One Writer To One Reader                 |

| OWOW                 | One Writer To One Writer                 |

| $\mathbf{PC}$        | Program Counter                          |

| PVP                  | Predictive Value of a Positive Test      |

| S-COMA               | Simple-Cache Only Memory Architecture    |

| SMMP                 | Shared Memory Multiprocessor             |

| $\operatorname{SMP}$ | Symmetric Multiprocessor                 |

| TN                   | True Negative                            |

| TP                   | True Positive                            |

#### Chapter 1

#### Introduction

#### 1.1 Motivation

In the last three years, the first single chip multiprocessors (CMPs) have entered the market of general purpose computers. These include the Pentium Extreme Edition [51] from Intel and the Athlon 64 X2 [53] from AMD. In the embedded systems market, the Cell processor [17], designed by IBM as a high-end embedded processor, contains 9 distinct processing units, each with its own instruction stream. It is effectively a CMP and was designed for use in the Playstation 3, Sony's newest video game console. Its main competitor, the XBox 360 [54] also employs a CMP. Multiprocessors are now entering the world of general purpose computing and consumer electronics, but they are not new. As of November 2007 over ninety percent of the 500 fastest supercomputers in the world had more than 1024 processors [52].

Multiprocessors are valuable for a number of reasons. Modern supercomputer designers choose to use multiprocessors because single processors cannot provide performance in the range they desire. Many servers use multiprocessors because the tasks they perform, such as database lookups, web servers, etc., are naturally parallel [10, 46]. Desktops and workstations are turning to multiprocessing because additional optimizations to single processor architectures are providing diminishing returns in terms of speedup, while at the same time dramatically increasing verification complexity [17] and power consumption [44]. Verification time can be greatly reduced by relying on previously tested processors and then linking them together into a CMP. However, additional verification of the coherence protocol that links these processors may be necessary.

It is a necessity that the individual processors in a multiprocessor can communicate with one another. One class of common general purpose multiprocessors — shared memory multiprocessors — do all communication through memory. Additionally, with the emergence of CMP processors, it is increasingly likely that the individual nodes of message passing multi-processors will themselves be shared memory multiprocessors. The memory must provide performance with caching, and at the same time maintain coherence among the caches. The speed with which coherence events take place limits the ability of the processors to communicate and share data. As individual cores have become more powerful, the percentage of execution time devoted to coherence action has increased [41].

Several techniques have been proposed to enhance the speed of coherence protocols. Originally, these took the form of modifications to the state machine that made up the protocol [7, 11, 45]. Later, coherence predictors were developed that preemptively identified events, and initiated them early to provide speedups [19, 22, 27, 28, 38, 42, 48] as were prefetching schemes [25, 37, 41, 50]. However, only rarely have these later schemes been evaluated in terms of their performance benefits.

These past works have always addressed only a single class of events at a time, and frequently focus on prediction accuracy, rather than speedup or the effect of speculation on the system behavior. To cover all possible events speculatively requires a large number of different predictors and modifications to the coherence protocol. From a hardware designer's point of view, adding numerous different schemes to a cache may be unacceptable. Each of these schemes interacts with the others in an unknown way, requires access to all requests made to the cache, and needs additional space. Given these three problems, it seems unlikely that a system designer will include more than one or two of them. Further, none of these predictors were studied in the context of varying system designs, and few were studied in the context of a single full system design. Whether coherence prediction is more useful in systems with low or high network latency is not a question that has been previously addressed, nor is how these distinct prediction mechanisms can be merged into a single predictor. This dissertation addresses some of these concerns with a unified coherence predictor.

#### 1.2 Summary of Work

The work presented here focuses on the interactions between different forms of coherence prediction and the behavior of a multiprocessor. The end goal in approaching this problem was to develop a single architecture of predictors that would operate cooperatively to move data to processors before those processors requested access to the data. This study attempts to accomplish this goal by focusing on three types of prediction: Consumer Prediction, Migratory Prediction, and Timing Prediction. Together, consumer prediction and migratory prediction can provide greater speedups than either can alone. However, in general the additional benefits of using all at once are minimal.

#### 1.2.1 Consumer Prediction

Consumer Prediction has been previously studied by Kaxiras and Young [19]. In consumer prediction, the readers of a written line are identified before they send requests for the data. Kaxiras and Young's work focused specifically on the accuracy of a few predictor schemes, and addressing the extremes of sensitivity and PVP, rather than a tradeoff. This dissertation expands on their work, showing new ways to predict, and exploring the actual mechanics of prediction; specifically when to predict, where to predict and how to train the predictor. It then continues to analyze the behavior of a multiprocessor with consumer prediction.

The results presented here show that there is a class of benchmarks that benefit from consumer prediction, and a class that does not. Specifically, consumer prediction best targets applications with strictly controlled phase behavior and memory ownership. Consumer prediction is weakest in aiding benchmarks that use pointer based data structures, such as trees.

These results also show the importance of simulating the complete system, rather than working with traces, as the actual sharing patterns exhibited by the benchmarks can change when consumer prediction is in place. For example, most of the Volrend benchmark's (from the SPLASH-2 benchmark suite [49]) sharing exists to distribute data from slower processors to faster processors. When consumer prediction increases the speed of these slower processors, the amount of sharing changes as different processors are involved in these exchanges, and fewer are necessary. These kinds of feedback effects of prediction have not been properly modeled by previous work in this area, by virtue of their focus on trace-based simulation.

Consumer prediction can increase the speed of requests for Modify copies of lines, despite the fact that it does not transmit them speculatively. Because consumer prediction distributes the data earlier, it is less likely that requests for Modify permission will arrive during a transient state. That means that it is more likely that requests to the directory for Modify permission will be serviced immediately.

#### 1.2.2 Migratory Prediction

Migratory Prediction was first identified by Cox et. al [7]. It is a form of sharing in which a single processor reads and writes a line, and then passes that line on to another processor that will read and write. This work focusses on implementing migratory prediction in such a way that it can be combined with consumer prediction and timing prediction, and requires little additional hardware.

It demonstrates a migratory predictor that uses the same training information and stored history information that is already used by consumer prediction. Several options for training this predictor are also explored. This dissertation also discusses the complexities of implementing this predictor, and how the directory can be modified to take advantage of it. In general the performance benefits of migratory prediction are lower than the benefits of consumer prediction.

#### 1.2.3 Timing Prediction

This dissertation explores a number of different predictors that are intended to move data away from the processors and back to the directory so that Consumer Prediction and Migratory Prediction can be performed. Previous work has focused on specifically identifying the final touch to a line before an invalidate message can arrive [28]. The results presented here show that last touch prediction is less effective than previously reported when in a system with an operating system present.

#### 1.2.4 Combined Coherence Prediction

Finally, this dissertation demonstrates how each of these predictors can be placed together, and work in concert to speculatively move data to processors before they request access. It explores two distinct options, one in which additional information about the instructions that have touched lines can be forwarded to the directory, and one in which no additional data beyond acknowledgments can move between the components of a system. The results of this study show that the combination of migratory and consumer prediction can produce slight benefits over either alone.

#### 1.3 Research Contributions

This dissertation explores options for combining multiple coherence prediction techniques. It shows how it is possible to combine them without producing many, fully independent predictors, and how they can be combined so that they do not interfere with each other. In the process, several individual predictive techniques and interactions between predictors are discussed. These smaller contributions are listed below.

- 1. Application of Perceptron Techniques to Consumer Prediction: This work describes a novel consumer predictor that uses a global perceptron to identify future sharers. This predictor is able to operate in an accuracy vs. coverage tradeoff not available to previous predictors.

- 2. Complete Implementation of Consumer Prediction: This work is the first to produce a working system using consumer prediction at the directories to achieve processing speedups. Previous work has shown only the accuracy of these predictors. In addition to evaluating their accuracies, this dissertation demonstrates how the schemes proposed in previous work can produce speedups. This work then proposes alternate predictor architectures, and demonstrate the speedups that can be achieved.

- 3. Inclusion of Migratory Pattern Identification in Consumer Prediction: This dissertation demonstrates a method for constructing a migratory predictor that uses the same information available in the consumer predictor. It shows

that this migratory predictor can outperform other migratory schemes, and that it can be further improved by combining it with consumer prediction, at negligible hardware cost.

- 4. Extension of Training Mechanisms in Multiprocessor Systems: Previous work has demonstrated the potential of speculatively self-invalidating cache lines to provide substantial speed increases in directory-based multiprocessors. The most effective prediction scheme, last touch prediction, places a trace based predictor at each cache to identify instruction patterns that correspond to incoming invalidation messages. This study proposes and investigates the idea of sharing training information across caches. This sharing of information enables speedups of as much as 22% over a standard directory protocol and 12% over a directory protocol implementing previous last touch schemes. This work then explores the details of training such a system, and the performance tradeoffs of the decisions made in this stage of the design.

- 5. Coherence Predictor Tuning for Full System Design: Unlike the behavior of branch predictors, coherence predictors are not properly described by a single accuracy number. Two coherence predictors are needed: sensitivity and Predictive Value of a Positive Test (PVP). In isolation it is not always possible to identify the better of two predictors. This study evaluates how this tradeoff in consumer prediction behavior translates to performance benefits, and which systems benefit the most from a high or low network latency.

- 6. Analysis of the Influence of Realistic Training on Coherence Prediction: This

work analyzes the behavior of consumer prediction, and last touch prediction under a more realistic training model. Because training information is not immediately available, the theoretical results previously reported are not necessarily valid. For many cases the predictors will not have been updated from previous predictions when the next prediction is made. Additionally training information can arrive out of order. This dissertation demonstrates the result of these effects.

#### Chapter 2

#### Background

#### 2.1 Multiprocessor Design

Multiprocessors can be divided into two groups: (i) Message Passing Multiprocessors (MPMs) which give each processor a separate memory space and use explicit *send* and *receive* commands to move data and, (ii) Shared-Memory Multiprocessors (SMMPs) which move data between processors via stores and loads to a shared memory space. SMMP systems are considered easier for programmers, allowing them largely to ignore hardware implementation details [46]. In many ways this is similar to programming in a high level language as compared to programming in assembler. However, SMMPs provide challenges to the hardware designer that MPMs do not.

- Coherence How can we guarantee that the data seen by each processor are in some way coherent, so that we can be sure we are not looking at out-ofdate data? This is not an issue if we do not implement caching, but such an omission will lead to poor performance.

- Physical Location of Memory Where should we locate the actual memory and how should the processors access the memory?

Both of these problems have been researched in depth. Coherence can be maintained with either a snooping protocol [15] or with a directory protocol [6]. In a snooping protocol, memory accesses are transmitted across a bus or other strictly ordered substrate that is shared by all processors [15]. This allows the accesses to be easily serialized across processors. In a directory protocol, a centralized location called a directory tracks the current state of each line of memory [6]. When a processor writes a line to the directory, it first ensures that any other processor with a copy knows that it is no longer valid. It is possible to implement a coherence protocol using neither a directory nor a snoopy bus [32], or a hybrid of a directory and a snoopy bus [34]. However, such protocols are relatively new and often more difficult to verify and purge of race conditions.

Memory can be located at an equal distance from all processors, or distributed such that some parts of the memory are closer to some processors than others. Systems in which memory is located at an equal distance from all processors are called Symmetric Multiprocessors (SMPs). Systems in which memory is spread, some closer to some processors than others, are called Non-Uniform Memory Access (NUMA) systems. However, SMP systems are limited by memory bandwidth and can produce long latencies. NUMA systems address this by spreading memory around the network [16, 46]. The advantage of SMPs is that placement of data in memory is not as important, whereas in a NUMA it is important to locate the most frequently accessed data as close as possible to the processor that uses it.

#### 2.2 Memory Sharing Patterns

In 1989, Weber and Gupta published their work on invalidation patterns [47]. They analyzed several programs and categorized the memory sharing behavior by cache line, describing five categories. These categories are Code/Read Only, Migratory, Synchronization, Mostly-Read, and Frequently Read/Written. Code/Read Only data never suffer any invalidations. Migratory data are never read between multiple processors between writes. This typically corresponds to locked data. Synchronization data corresponds to locks and other such structures which are often heavily requested. Weber and Gupta showed that the difficulties associated with synchronization data can be reduced by more carefully written programs. Mostly-Read data is read by a large number of processors, and occasionally written. Frequently Read/Written data shows more complex behavior. This categorization led to a number of different works intended to target specific patterns of behavior [4, 7, 23, 24, 45].

#### 2.2.1 Migratory Data

Two techniques were independently developed to handle the case of migratory data [7, 45]. Both suggest modifications to the state machine that tracks read and modify permission. The state machine was modified to detect cases in which a processor received migratory data. This data was then flagged and when another processor requested read permission to the data, it was assumed that the requester would eventually want to write the data. Modify permission was sent along with the data.

Later work by Kaxiras and Goodman showed that it was possible to identify migratory data by the code operating on it [22]. They demonstrated a system in which loads associated with migratory data are marked. The processor then requests modify permission rather than read permission. The difference between this and the previous attempts is similar to the difference between inward and outward coherence prediction, one focuses on moving data from a distant position to the predictor, and the other focuses on moving data from the predictor to a distant position.

Rajwar, Kagi and Goodman proposed that the locks themselves could be detected by the hardware [40]. They identified lines of memory containing locks and the associated lines containing the protected data. In this way the data could be sent to a distant processor as soon as a lock was released, before any request had been made.

#### 2.2.2 Widely Shared Data

Bianchini and LeBlanc recognized another sharing pattern that they consider important: widely shared data [4]. This is related to, but not the same as, Mostly Read data [47]. They pointed out that bandwidth becomes more important as the processor count increases, and that a small number of cache lines uses up an increasing amount of bandwidth as the processor number grows. They called this data "hot". They then developed a system called *eager combining* in which this data would be sent to a number of servers spread throughout the system. Rather

```

while (Global->Queue[num_nodes][0] > 0) {

. . .

ALOCK(Global->QLock,local_node);

work = Global->Queue[local_node][0]++;

AULOCK(Global->QLock,local_node);

while (work < lnum_blocks) {</pre>

xindex = xstart + (work%lnum_xblocks)*block_xlen;

yindex = ystart + (work/lnum_xblocks)*block_ylen;

for (outy=yindex; outy<yindex+block_ylen && outy<ystop; outy++) {</pre>

for (outx=xindex; outx<xindex+block_xlen && outx<xstop; outx++) {</pre>

/* Trace ray from specified image space location into map.

*/

/* Stochastic sampling is as described in adaptive code.

*/

foutx = (float)(outx);

fouty = (float)(outy);

pixel_address = IMAGE_ADDRESS(outy,outx);

Trace_Ray(outx,outy,foutx,fouty,pixel_address);

}

}

ALOCK(Global->QLock,local_node);

work = Global->Queue[local_node][0]++;

AULOCK(Global->QLock,local_node);

}

}

. . .

```

Figure 2.1: An example of migratory data. This is the main processing loop of Volrend. The memory location that is used to determine the next block to process (stored in work) is migratory. Once a lock is obtained it is read and written in succession. No other processor can access it during this time because of the locks.

```

for (step=0; step<ROTATE_STEPS; step++) {

...

BARRIER(Global->SlaveBarrier,num_nodes);

...

if (my_node == ROOT) {

Select_View((float)STEP_SIZE, Y);

}

BARRIER(Global->SlaveBarrier,num_nodes);

Global->Counter = num_nodes;

Global->Queue[num_nodes][0] = num_nodes;

Global->Queue[my_node][0] = 0;

Render(my_node);

...

}

```

Figure 2.2: An example of widely shared data. This is the outermost loop of Volrend. The Select\_View function is called by only a single processor (the ROOT processor). It sets a number of data items that are used to determine the position of the "camera" in this phase of rendering. Every Processor accesses Render, which reads all of this data.

than contacting the directory, a processor in the system could contact the nearest server to receive the latest version of the data. There are two main advantages to this approach. First, the traffic of many processors trying to read at the same time is spread throughout the network, rather than all being routed to a single point. Second, the servers can be spread throughout the system so that individual processors need not send messages very far to receive the data.

Kaxiras, and later Kaxiras and Goodman proposed the GLOW extensions to a directory based multiprocessor [23, 24]. These extensions were intended to handle the same "hot" data that Bianchini et al. aimed to handle with eager combining. A set of GLOW agents are placed throughout the network, forming a tree such that the processors are spread out across them. These agents act as directories to the processors below them, and request data from the agents above them in the tree as a processor would. In this way contention for network resources is spread throughout the system.

Later, Kaxiras et al. proposed extensions to the GLOW agents [20, 21]. The GLOW agents are extended to dynamically identify widely shared data and act only on those data, allowing other requests to query the directory normally. The GLOW agents watch for requests to the same line by multiple processors in quick succession. When they see this occurring, the line is marked as widely shared and the agent acts to combine requests as originally proposed.

#### 2.3 Multiprocessor Memory Coherence

Memory coherence in a multiprocessor, refers to the way those data that are potentially stored multiple caches are handled. The coherence protocol is the system that forces the data in the caches to remain coherent, such that the cache remains invisible, and programs can be written without concern for moving data between processors.

A number of different forms of speculation have been applied to memory coherence that do not resemble traditional prediction. For example, the migratory sharing schemes described earlier use speculation based on simple static patterns to recognize a common behavior [7, 45]. Dubois et al. propose adding a Stale state to the cache [11]. This Stale state allows the system to take advantage of additional slack provided by a weak consistency processing model.

Others have suggested switching between multiple protocols, depending on the situation. For instance, Falsafi and Wood proposed Reactive NUMA [13]. Reactive NUMA combines the benefits of Simple Cache Only Memory Architecture (S-COMA), in which pages do not belong to a specific memory in the system but can be moved between locations, and Cache Coherent Non-Uniform Memory Access (CC-NUMA) in which each page has a specified location. They do this by dynamically detecting the pages that will benefit from S-COMA and applying it only to those pages. Bandwidth adaptive snooping, proposed by Martin et al., switches between a broadcast protocol and a snooping protocol based on the current network utilization [34]. When the network is not busy, they apply a broadcast snooping protocol to reduce overall latency. When the network is heavily loaded, the system switches to a directory protocol to reduce the network utilization.

Sorin et al. proposed that a protocol could be designed that detects rare race conditions, but does not handle them correctly [43]. When the race conditions are detected, the system rolls back to a previous checkpoint and applies a slower protocol that handles these conditions. With this technique a processor can use a fast but not wholly correct protocol the majority of the time.

Token coherence takes this approach one step further [32, 36] by taking away the need for a checkpoint. Martin et al. propose that tokens can be used to decide on permissions. Each line of memory is assigned a number of tokens, typically larger than the number of processors. Any processor with a token is allowed to read the line. Only a processor having all the tokens is allowed to write the line. Within this context any speculative mechanism can be employed, so long as the three conditions above are respected and tokens are never created or lost.

In order to guarantee forward progress, a timeout condition is applied. Whenever a request spends too long waiting, the system uses a slower broadcast-based protocol. This protocol guarantees correct execution and overrides any and all speculative mechanisms in the system.

Another option proposed is coherence decoupling. Huh et al. propose that the processing unit itself be allowed to speculatively execute on invalid data [18]. If the speculation turns out to be incorrect, the processor rolls back. If it is correct, the processor commits the changes.

Coherence decoupling allows processors to ignore false sharing. If a processor is currently writing a word, another processor can read a different word on the same cache line speculatively. When the reader discovers that that word did not change, it can commit any data that it has already produced. Coherence decoupling can also be used in conjunction with data forwarding. A writer can send out copies of data to potential readers before the coherence protocol has officially given them read permission. Thus the readers can begin working with some data before the coherence protocol would otherwise allow. The main disadvantage of coherence decoupling is that the coherence protocol must be visible to the processing core. The commit and issue logic needs to be redesigned to take this into account.

#### 2.4 Coherence Prediction

A number of different techniques have been proposed for using explicit predictor structures to accelerate coherence protocols. For convenience these techniques can be organized into *inward*, *outward*, and *administrative* techniques. In inward techniques a processor speculatively requests that its own permissions be increased. The classic example of this would be prefetching. Using prefetching, members of the system — typically either directories or processors — seek to move data from distant locations closer to themselves. In outward prediction, members of the system — typically either directories or processors — seek to move data from themselves closer to where those data will eventually be needed. In administrative prediction, a processor reacts to a real request for additional privilege by using speculation to take a shortcut around the strictly necessary messages that would normally be used. A good example of this would be owner prediction, proposed by Acacio et al. [2].

#### 2.4.1 Inward Coherence Prediction

Inward predictor techniques are those in which a processor identifies data it predicts it will want access to and seeks to bring any such data closer to itself. These techniques are effectively the same as prefetching, although modified to perform in a multiprocessor system with cache coherence.

Mowry and Gupta proposed that software prefetching could be used to improve multiprocessor speeds [37]. They modified several benchmarks by hand to add prefetching. Both read and modify permission were prefetched as appropriate. This showed large performance benefits, but required the prefetches to be inserted by hand.

Later, Dubois et al. described a hardware scheme for prefetching data in multiprocessor systems [12]. They implemented both stride and sequential read prefetching in a multiprocessor simulation. This yielded a dramatic reduction in read misses, a substantial reduction in execution time for some benchmarks, and an increase in network traffic.

Zhang and Torrellas proposed to create links between objects that may be distant in memory but are likely to be accessed near each other in time [50]. The compiler and programmer are responsible for identifying objects that are linked together. This information is passed to the processor. Whenever an object is requested, the pointers that it contains are also requested. Zhang and Torrellas show that this is beneficial to programs with irregular data structures.

Ranganathan et al. studied the interactions between prefetching and processor complexity [41]. They showed that as the complexity and processing power of the CPU grew, prefetching was less able to reduce memory latencies. While prefetching yielded a benefit, the amount of time devoted to memory events grew as the processor became more powerful.

Later work by Koppelman described neighborhood prefetching which combined the benefits of the previously proposed ones [25]. Neighborhood prefetching kept a record by PC of those cache misses that regularly occurred together. This provided the benefits of stride and sequential prefetching by recording that adjacent or equally spaced lines miss in sequence. It also linked objects in arbitrary positions in memory, with no regards to strides, or sequential access.

### 2.4.2 Outward Coherence Prediction

Outward coherence prediction techniques are those in which processors and directories choose to move data and permission away from themselves. Research work in this area falls into three main categories: consumer prediction and data forwarding, timing prediction, and request memory prediction.

Several general predictor structures have been proposed for coherence prediction [27, 38]. The first of these techniques, proposed by Mukherjee and Hill, was the Cosmos Coherence Message Predictor [38]. The Cosmos predictor keeps track of strings of coherence traffic associated with each address. It also keeps a global table of strings of coherence traffic it has previously seen. Each message is added to its respective string. A check is made in the global table, and if the next predicted message is something the system can act on, it does so. Mukherjee and Hill show that coherence events are predictable, but do not show the performance results of acting on them.

Lai and Falsafi highlight a number of problems with Cosmos in their work [27]. They point out that there are a number of cases in which the ordering of messages is unimportant. Their Memory Sharing Predictor removes this ordering information to simplify the look-up process. It is interesting to note that once this is done, their predictor becomes a consumer predictor. When a processor has write permission and sees a read request from a distant processor, the processor attempts to predict which other processors will request read permission. The processor also uses a simple heuristic to predict when it has finished writing a line.

Kaxiras and Young summarized previous consumer prediction schemes [19]. They demonstrated that all of the previous techniques are strongly related to one another. They proposed a taxonomy that encapsulated all of the predictors, plus additional terminology to describe them: prevalence, sensitivity, and predictive value of a positive test (PVP). This terminology allowed Kaxiras and Young to describe the performance of a consumer predictor with only two numbers. They then performed a search across all of the consumer predictors which their terminology could describe and listed the best in terms of sensitivity and PVP. This dissertation uses the terminology of Kaxiras and Young.

Rajwar et al. proposed that data can be speculatively linked to the lock to which they logically belong [40]. When a processor acquires ownership of the line containing a lock, any data associated with the lock can be sent along. Wenisch et al. propose that data is typically accessed in a specific order which they call a stream [48]. When a processor detects another processor requesting a sequence of addresses, it also transmits the additional data in the sequence. In this way, read permission can be moved between processors without a need for read requests when those two processors follow similar paths through memory.

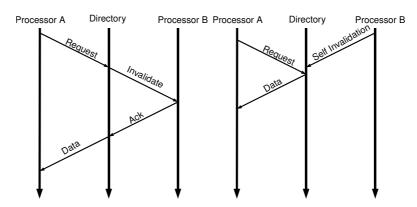

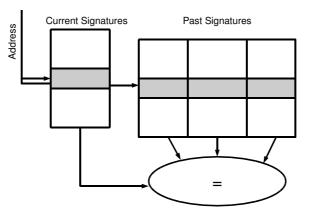

There are two principal works in timing prediction. Last touch prediction proposed by Lai and Falsafi, seeks to identify times at which a processor is "done" with a line [28]. At these times the processor will receive an invalidation message before accessing the line again. The authors base their work on the insight that the sequence of accesses a processor makes to a line during its lifetime is predictable and repetitive. The system stores the strings of program counter values (PCs) that have touched each line (compressed via truncated addition) and a hash table of strings of PCs that previously corresponded to last touches. When a match is found, the line is invalidated and the directory is notified.

Downgrade prediction is a similar technique [42]. Rather than looking for times at which to invalidate data, downgrade prediction looks for times when modify permission should be released. Functionally, this is identical to last touch prediction; however, the table is updated when modify permission is released to give another processor read permission, rather than when it gives up access entirely. When a match is found, the downgrade predictor releases modify permission and retains read permission.

#### 2.4.3 Administrative Coherence Prediction

Administrative Coherence Prediction focuses on circumventing parts of the coherence protocol. These techniques are speculative, but do not seek to change the permissions of any cache lines before a request has arrived at the processor. Instead, they seek to speed coherence transitions that have been requested by the processor.

In owner prediction, proposed by Acacio et al., a processor that wants read permission tries to predict the owner of a line [2]. The processor then sends its request to the directory and to the predicted owner. If the prediction is correct, the owner responds with data, which is available after just a two-message latency. If the prediction is incorrect, the directory forwards the request to the correct owner and data is available after a latency of three messages.

Acacio et al. later proposed a more aggressive predictor [1]. They proposed an Invalidation Lines Table (ILT) to speed the process of requesting modify permission. When a processor requests modify permission, it predicts the current readers of a line. The processor then sends requests to all of the predicted processors as well as the directory. If the prediction is correct, the directory tells it so and the other processors release the read permission they had. The entire process requires a twomessages latency. If it is incorrect, the directory notifies the processors that were not predicted. The entire process requires a three-messages latency.

Martin et al. describe how coherence prediction techniques can be used to reduce bandwidth in addition to latency [33]. They show that these techniques can dramatically decrease the bandwidth consumed when using a multicast snooping protocol. This is because these techniques decrease the number of messages that need to be multicast.

Finally, Lenosky et al. show that it is possible to predict the lines of the cache that need to be included in coherence prediction [30]. Previous techniques have assumed that some data are kept with each line in the cache, for instance, the trace of PCs to touch it in last touch prediction [28]. Their work shows that such a large quantity of storage is unnecessary. The number of lines involved in coherence activity is typically small. They propose an architecture that stores information only for lines known to be shared among processors. This dramatically decreases the size of coherence predictors with little affect on the accuracy of the predictors.

### 2.5 Coverage of Previous Work

The purpose of this dissertation is to create a predictor architecture that covers a wider range of sharing cases than have been previously suggested. To understand how to accomplish this, it is necessary to understand the limitations of the previous work. In this section one useful way to categorize sharing patterns is addressed. Each of the previous techniques that address each of these patterns and their limitations are discussed.

## 2.5.1 Division of Sharing Patterns

There are a variety of ways to categorize sharing. The most commonly cited paper on the subject analyzed cache lines and divided them into five categories, several of which have been discussed earlier [47]:

- Code/Read Only Data is never written once loaded from storage,

- Migratory Data only belongs to one processor at a time,

- Synchronization Data contains locks and other such structures accessed by many processors,

- *Mostly-Read Data* is rarely written and read by a number of different processors between reads,

- Frequently Read/Written Data is read and written regularly.

A number of papers have proposed ways of altering coherence protocols to exploit migratory data [7, 9, 45]. The categorization above considers sharing on the basis of cache lines. There is a strong intuitive reason for this. Each cache line corresponds to a set of data or a single variable in the case of single word lines. The line's behavior can be related directly to the data contained within. Others have suggested that sharing patterns may be better analyzed by Program Counter (PC) [22].

To better understand what cases are covered by previous predictors, it is possible to categorize coherence events. These coherence events are shown in Figure 2.3, and summarized below.

- One Writer To Many Readers (OWMR) In this case, a processor has modify permission and many processors will be requesting read permission before another receives modify permission.

- One Writer To One Reader (OWOR) In this case, a processor has modify

permission and only one other processor will request read permission before

the line is written again. The line here must be written by a cache other than

the reader. This case is similar to OWMR.

- One Writer To One Writer (OWOW) In this case, a processor has modify permission and another will be requesting modify permission. This may happen after either of the two processors read. When there is an intermediate read by the second processor, it is identical to migratory sharing. When there is no read, it is a silent store.

- Many Readers To One Writer (MROW) In this case, a number of other processors have read permission and a request arrives for write permission.

This category includes widely shared data in addition to data only read by a small subset of processors between writes.

• One Reader To One Writer (OROW) — In this case, only a single processor has read permission and another processor requests write permission.

| store X     | <br>load X  | Processor C<br><br>load X | Ioad X      | store X     | load X      | <br>store X   | C Processor D |

|-------------|-------------|---------------------------|-------------|-------------|-------------|---------------|---------------|

| (a) On      | ne Writer T | 'o Many Re                | aders       | (b) Or      | ne Writer   | To One R      | Reader        |

|             |             |                           |             |             |             |               |               |

|             |             |                           |             |             |             |               |               |

|             |             |                           |             |             |             |               |               |

| Processor A | Processor B | Processor C               | Processor D | Processor A | Processor B | B Processor G | C Processor D |

| Processor A | Processor B | Processor C               | Processor D | Processor A | Processor B | B Processor C | C Processor D |

|             |             |                           |             |             |             |               |               |

| store X     |             |                           |             | load X      | load X      | load X        |               |

| Processor A | Processor B | Processor C | Processor D |

|-------------|-------------|-------------|-------------|

|             |             | load X      |             |

|             |             |             | store X     |

|             |             |             |             |

(e) One Reader To One Writer

Figure 2.3: Five Different Categories of Coherence Events.

Each of these categories represents a subtly different prediction task. OWMR is related to producer-consumer prediction. Ideally, a cache could predict the processors that will request read permission and forward data to them before they actually request it. Predicting only a subset of these processors may still produce speedups, as those processors which were correctly identified can receive the benefits. Predicting additional processors can cause slowdowns by using extra bandwidth or increasing the time needed for another later operation by requiring extra invalidations when it seeks a Modify copy. Several systems have been proposed to handle this [19, 22, 27, 42] and will be explored in more depth in Chapter 4. The OWOR case is similar enough to be handled by the same mechanisms.

OWOW contains silent stores and migratory data. Migratory data results from data structures contained behind locks, which are logically owned by a single thread at a time. Several modifications to coherence protocols have been proposed to handle migratory data [7, 9, 45]. All of them work by altering the coherence protocol. The disadvantage of modifying the coherence protocol is that more complex protocols are more difficult to verify. One advantage of coherence prediction is that it can be implemented with minimal changes to the coherence protocol, thus simplifying the task of protocol design [27]. The previous predictor based approach to migratory data was proposed by Kaxiras and Goodman in [22]. This was an inward method in which the PC was used to identify reads associated with the first touch in migratory sharing. But it did nothing to act before an instruction arrived at the processing unit requesting data.

MROW is a case where a processor requests write permission and several other processors must be invalidated. Two techniques can hide some of the latency of this event. Last touch prediction can remove a level of indirection by invalidating data early at the readers [28]. An Invalidation Lines Table (ILT), as proposed by Acacio et al. [1] and several other related techniques [2, 33] can remove a level of indirection by predicting the current readers at the future writer, and skipping the directory. These two techniques have contradictory goals — one seeking to move information to the directory and the other seeking to bypass the directory. If a reader has invalidated itself using last touch prediction, the ILT will generate extra messages contacting that reader. Also, neither of these two forms of prediction moves the writer into modify permission before it has reached the store in its instruction flow, which would be ideal. OROW is a subset of MROW, and is slightly easier to predict in that only a single reader must successfully give up permission.

In addition to the issues described above, it is necessary to predict the timing of these events. Last touch prediction [28] and downgrade prediction [42] both already attempt to address this issue.

## 2.5.2 Multi-Read To One Writer Sharing

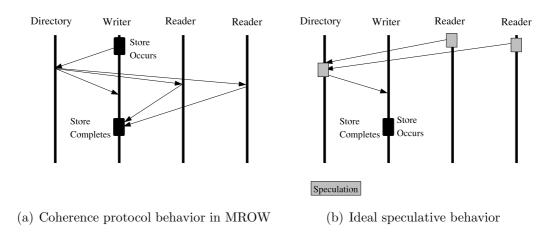

Possibly the most frequent example of a coherence event is the MROW transition. This event happens every time a processor requests write permission that is not covered by OWOW (Migratory Sharing) and where more than a single processor has read the data. Although several schemes have been proposed to aid this transition, none have attempted to completely remove all of the latencies through speculation. One of the more recent works in coherence prediction specifically mentions this limitation [27]. Figure 2.4 shows the messages that must be sent in order to properly account for an MROW event in a non-speculative directory protocol. It also shows the ideal case in which the owners speculatively release ownership and forward it to the writer ahead of time.

Figure 2.4: Normal behavior of a coherence protocol to an MROW event and the ideal speculative behavior that removes all latencies.

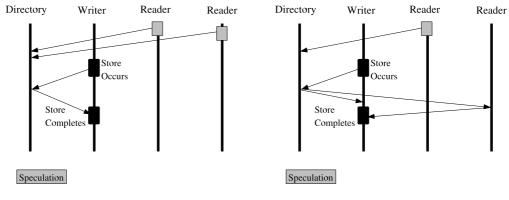

Two different predictors have been suggested to speed up this transition. The first is last touch prediction [28]. Last touch prediction identifies times when a processor is "done" with a line. It then prompts the cache to release ownership of the line. Figure 2.5 shows how Last Touch Prediction can speed an MROW event, as well as an example of how it can fail.

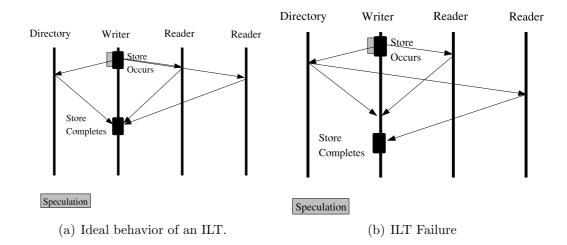

Using an ILT as proposed by Acacio et al. [1], the processor requesting write permission attempts to guess the current set of readers and bypass the directory. This process, as well as a case in which it fails, are shown in Figure 2.6.

First, notice that both an ILT and last touch prediction fail to hide all of the latency of the write even when working correctly. Last touch prediction requires the writer to contact the directory and then wait for a response. The ILT requires the requester to wait for the directory and readers to respond. Both reduce latency, but neither fully hide it.

(a) Ideal behavior of last touch prediction.

(b) Last touch prediction failure.

Figure 2.5: The ideal behavior of last touch prediction on an MROW event

Figures 2.5 and 2.6 also illustrate one of the inherent difficulties of handling MROW cases. In order for the full benefits of speculation to be achieved, many predictions must be made correctly. Last touch prediction requires that all the readers successfully invalidate their cache lines. An ILT requires that all of the readers are successfully identified by the writer. While a partial prediction can be useful, even a single mistake changes the longest path in messages from two to three. For this reason MROW events are the most difficult to handle speculatively.

In addition to the difficulty of coordinating the readers, the ideal predictor shown in Figure 2.4 can mispredict by sending write permission to the wrong processor, or more than one processor. If the wrong processor has write permission, the other processor will have to request it. This operation may be faster than with no prediction, as the directory will only have to contact a single processor. By placing the structure that forwards write permission at the directory, the second issue, that of multiple processors being selected as writers, does not exist. As with last touch

Figure 2.6: The ideal behavior of an ILT on a MROW event

and the ILT, there is a potential small benefit when not all processors give up read permission. Unlike last touch and the ILT, this ideal prediction has the potential to negate all of the delay incurred by a request for modify permission.

A key difficulty with speculatively moving modify permission to a future writer is that of authority. In the case of migratory sharing, one processor with modify permission gives up all access permission and gives another processor modify permission. Because the first processor had modify permission, we know that no other processor does. No other processor can receive read or modify permission from the directory until the first is invalidated. Thus we know that coherence is maintained. Similarly, with consumer prediction, the writer has modify permission and thus can downgrade itself and distribute read permission.