# **PH.D. THESIS**

Design for Production: Using Manufacturing Cycle Time Information to Improve Product Development

by Mandar Chincholkar Advisor: Dr. Jeffrey W. Herrmann

PhD 2002-10

ISR develops, applies and teaches advanced methodologies of design and analysis to solve complex, hierarchical, heterogeneous and dynamic problems of engineering technology and systems for industry and government.

ISR is a permanent institute of the University of Maryland, within the Glenn L. Martin Institute of Technology/A. James Clark School of Engineering. It is a National Science Foundation Engineering Research Center.

Web site http://www.isr.umd.edu

#### ABSTRACT

## Title of Dissertation: DESIGN FOR PRODUCTION: USING MANUFACTURING CYCLE TIME INFORMATION TO IMPROVE PRODUCT DEVELOPMENT

Mandar M. Chincholkar, Doctor of Philosophy, 2002

| Dissertation directed by: | Associate Professor Jeffrey W. Herrmann |

|---------------------------|-----------------------------------------|

|                           | Department of Mechanical Engineering    |

|                           | and                                     |

|                           | Institute for Systems Research          |

Product development teams employ many methods and tools as they design, test, and manufacture a new (or improved) product. It is important that the product development team understand how their design decisions affect manufacturing system performance. Having this feedback early in the design process avoids rework loops needed to solve problems of manufacturing capacity or cycle time. The team can incorporate this information and associated costs into a design decision problem aimed at choosing the best possible product design.

It is clear that the product design, which requires a specific set of manufacturing operations, has a huge impact on the manufacturing cycle time. Reducing *manufacturing cycle time* has many benefits, including but not limited to lower inventory, reduced costs, improved product quality, faster response to customer orders, increased flexibility and a reduced time-to-market.

Design For Production (DFP) refers to methods that evaluate a product design by comparing its manufacturing requirements to available capacity and estimating manufacturing cycle time. DFP can be used to design the product in a way that decreases required capacity, reduces the manufacturing cycle time, or otherwise simplifies production.

To understand how a product design impacts manufacturing system performance, this research develops analytical (not simulation) models to quantify how introducing a new product increases congestion in the manufacturing system. It presents approaches that use this information intelligently and make suggestions on product redesign and manufacturing system improvements. Similar models are also developed for manufacturing systems with process drift, a condition causing a process to deviate from expected processing parameters resulting in a reduced yield at that station. This work presents models for evaluating how embedding passives into a printed circuit board affects not only the processing times at each step in the manufacturing process but also the overall manufacturing system behavior. Finally, this dissertation demonstrates the importance of the DFP approach by presenting a comprehensive perspective on the economic impacts of reducing manufacturing cycle time. Through these models and relationships, this research aims to understand the issues and impacts associated with the design for production approach and provide better tools that improve product development.

Keywords : design for manufacture, design for production, queuing, product de-

sign, product development, manufacturing cycle time, economic impact, embedded passives, process drift.

## DESIGN FOR PRODUCTION: USING MANUFACTURING CYCLE TIME INFORMATION TO IMPROVE PRODUCT DEVELOPMENT

by

Mandar M. Chincholkar

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2002

Advisory Committee:

Associate Professor Jeffrey W. Herrmann, Chairman/Advisor Professor Michael O. Ball Associate Professor Satyandra K. Gupta Professor Edward B. Magrab Associate Professor Peter A. Sandborn © Copyright by Mandar M. Chincholkar 2002

#### DEDICATION

To my parents

#### ACKNOWLEDGEMENTS

Through the course of this research, a number of people have contributed to and helped in various ways. This doctoral work has taught me a whole lot of invaluable lessons which though not a part of this dissertation will continue to guide me throughout my life. This work would be incomplete without acknowledging various people associated with my work, their efforts and contributions.

Firstly, I would like to whole-heartedly thank my advisor, Associate Professor Jeffrey W.Herrmann, for his guidance, invaluable help, ideas and patience. Our often-held and long drawn discussions of various minute aspects of the problem helped me better understand the problem and associated intricacies. I really appreciate Dr.Herrmann for his patience during these at times frustrating discussions and tolerating my temperamental behavior. I have imbibed a number of imitable qualities from Dr.Herrmann including the ability to analyze a problem without losing sight of the big picture of which the problem is a small part, the ability to scrutinize and critique both self written works as well as those of other researchers, to persevere to solve a tough problem at times changing the viewpoint if needed, to name a few. I hope to emulate these qualities in my professional career. Next I wish to express my gratitude towards my dissertation committee, Dr.Michael Ball, Dr.Satyandra Gupta, Dr.Edward Magrab and Dr.Peter Sandborn for their ideas during the proposal presentation and problem definition effort. Thanks are also due to the committee for their guidance and evaluation of my work.

I am grateful for the superb facilities of the Computer Integrated Manufacturing Laboratory which served as a second home during the time I was working on my research. I wish to thank Dr.Edward Lin for his help with the modalities associated with the computing and other facilities in the lab. I also appreciate his help with my work and for the suggestions and ideas to improve my research. I also take this opportunity to thank all the students and researchers in the CIM Lab, both past and present, for their support and help in making my stay here an enjoyable and memorable one.

Finally I acknowledge the efforts of my parents who always stood by me during the good times and most importantly during the not so good times. I am forever indebted to them for their love and support throughout my professional and personal academic career. As I stand here, close to the end of my academic career, I look back and realize the sheer magnitude of their support over the years. My mother has always been there when I needed her, coaxing and egging me when the chips were down and deriving great happiness from my minutest achievements. She has always taught me to believe in myself and my dreams. My father has been a strong support who I have always looked to for guidance. He has taught me to look at the positive side of life and to always aim for the stars. My brother also deserves special mention here for his support and help over the years. It is impossible to fully express my gratitude and appreciation for all my parents have done for me, and this acknowledgement is but an insignificant attempt.

The material in this dissertation is based upon work supported by the National Science Foundation under Grant No. DMI 97 - 13718. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author and do not necessarily reflect the views of the National Science Foundation. I wish to thank the National Science Foundation for their support.

#### TABLE OF CONTENTS

| Li                | st of                        | Tables x                                 | i |  |  |

|-------------------|------------------------------|------------------------------------------|---|--|--|

| List of Figures x |                              |                                          | i |  |  |

| 1                 | Intr                         | roduction 1                              |   |  |  |

|                   | 1.1                          | Motivation                               | } |  |  |

|                   | 1.2                          | Design for Production                    | ł |  |  |

|                   | 1.3                          | Organization                             | 7 |  |  |

| <b>2</b>          | $\operatorname{Lit}\epsilon$ | rature Review 8                          | 3 |  |  |

|                   | 2.1                          | Introduction                             | 3 |  |  |

|                   | 2.2                          | Concurrent Engineering 13                | } |  |  |

|                   | 2.3                          | Importance of Design                     | 7 |  |  |

|                   | 2.4                          | Design for X                             | 3 |  |  |

|                   | 2.5                          | Design for Manufacturing 20              | ) |  |  |

|                   | 2.6                          | Design for Time-to-Market                | 2 |  |  |

|                   | 2.7                          | Design Refinement                        | 5 |  |  |

|                   |                              | 2.7.1 Classification and Representation  | 3 |  |  |

|                   |                              | 2.7.2 Representing Design Advisory Rules | 7 |  |  |

|                   |                              | 2.7.3 Product Redesign                   | ) |  |  |

|   | 2.8  | Manuf   | acturing System Analysis                                | 32 |

|---|------|---------|---------------------------------------------------------|----|

|   |      | 2.8.1   | Models                                                  | 32 |

|   |      | 2.8.2   | Capacity Analysis                                       | 39 |

|   | 2.9  | Estima  | ating Manufacturing Cycle Time                          | 41 |

|   | 2.10 | Proces  | s Yield, Manufacturing Cycle Time and Throughput        | 44 |

|   | 2.11 | Printe  | d Circuit Boards and Embedded                           |    |

|   |      | Passiv  | es                                                      | 48 |

|   |      | 2.11.1  | Definitions                                             | 49 |

|   |      | 2.11.2  | Pros and Cons of Embedding                              | 50 |

|   |      | 2.11.3  | Buried Passive Parameters                               | 52 |

|   | 2.12 | Embeo   | dded and Discrete Passive Components                    | 54 |

|   |      | 2.12.1  | For the Initial Embedded Passive                        | 55 |

|   |      | 2.12.2  | Changes Effective Each Time a Passive is Embedded $\ .$ | 56 |

|   | 2.13 | Summ    | ary                                                     | 57 |

| 3 | Mar  | nufactu | uring System Model                                      | 59 |

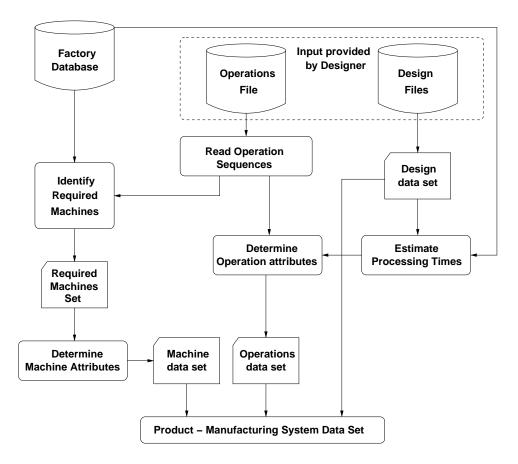

|   | 3.1  | Manuf   | acturing System Model Explanation                       | 60 |

|   |      | 3.1.1   | Data Requirements                                       | 60 |

|   | 3.2  | DFP 7   | Fool                                                    | 68 |

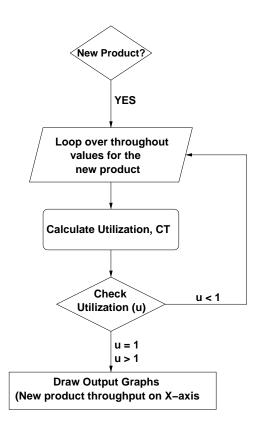

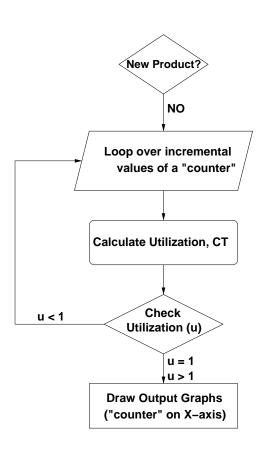

|   |      | 3.2.1   | Algorithm:                                              | 70 |

|   |      | 3.2.2   | Outputs                                                 | 74 |

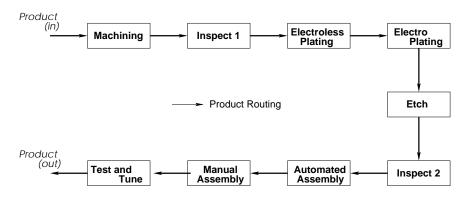

|   | 3.3  | Applic  | ation: Microwave Module DFP Tool                        | 81 |

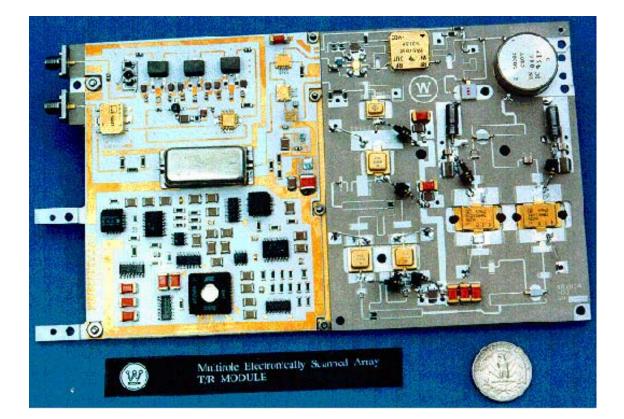

|   |      | 3.3.1   | The Microwave Module                                    | 81 |

|   |      | 3.3.2   | The Manufacturing System                                | 85 |

|   |      | 3.3.3   | Capacity Analysis                                       | 86 |

|   |      | 3.3.4   | Estimating the Manufacturing Cycle Time                 | 86 |

|   | 3.4 | Summ   | ary                                                       | 92  |

|---|-----|--------|-----------------------------------------------------------|-----|

| 4 | Cas | e Stud | ly: Embedding Passives in Printed Circuit Boards          | 94  |

|   | 4.1 | Printe | d Circuit Board Manufacturing                             | 95  |

|   |     | 4.1.1  | Double Sided Printed Circuit Boards                       | 95  |

|   |     | 4.1.2  | Multilayer Printed Circuit Boards                         | 96  |

|   |     | 4.1.3  | Steps Involved in Embedding a Resistor Component into the |     |

|   |     |        | РСВ                                                       | 98  |

|   |     | 4.1.4  | Making a Multilayer PCB Substrate With Embedded Pas-      |     |

|   |     |        | sive Components                                           | 99  |

|   | 4.2 | Mater  | ial Flow Considerations for PCB                           |     |

|   |     | Manuf  | facture                                                   | 105 |

|   |     | 4.2.1  | Processing Possibilities                                  | 105 |

|   |     | 4.2.2  | Movement Scenarios                                        | 106 |

|   | 4.3 | Desigr | 1                                                         | 108 |

|   |     | 4.3.1  | Calculating the Number of Layers                          | 108 |

|   |     | 4.3.2  | Design Parameters                                         | 111 |

|   | 4.4 | Exam   | ple                                                       | 113 |

|   |     | 4.4.1  | Assumptions                                               | 114 |

|   |     | 4.4.2  | Processing Steps and Processing Time Models               | 115 |

|   |     | 4.4.3  | Manufacturing System                                      | 124 |

|   |     | 4.4.4  | Products                                                  | 124 |

|   |     | 4.4.5  | Experiment Design                                         |     |

|   |     | 4.4.6  | Results and Discussion                                    |     |

|   | 4.5 | Summ   | ary                                                       |     |

|   |     |        | *                                                         |     |

| <b>5</b> | Moo  | leling  | Process Drift                                                                                   | 135 |

|----------|------|---------|-------------------------------------------------------------------------------------------------|-----|

|          | 5.1  | Manuf   | acturing Cycle Time and Yield                                                                   | 136 |

|          | 5.2  | Manuf   | acturing System Model                                                                           | 139 |

|          | 5.3  | Effects | s of Process Drift                                                                              | 151 |

|          | 5.4  | Flow S  | Shops $\ldots$ | 153 |

|          | 5.5  | Flow S  | Shop Example                                                                                    | 155 |

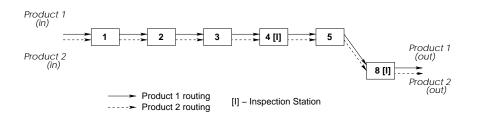

|          |      | 5.5.1   | Two Products                                                                                    | 156 |

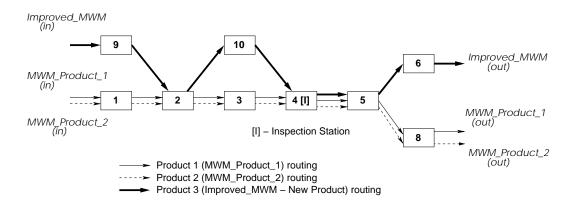

|          |      | 5.5.2   | System With New Product                                                                         | 158 |

|          |      | 5.5.3   | Comparison                                                                                      | 159 |

|          |      | 5.5.4   | Trials                                                                                          | 163 |

|          |      | 5.5.5   | Results                                                                                         | 163 |

|          | 5.6  | Creatin | ng a Graph Representation for the System Parameters                                             | 170 |

|          | 5.7  | Identif | ying the Dependencies in System                                                                 |     |

|          |      | Param   | eters                                                                                           | 174 |

|          | 5.8  | Examp   | bles of System Graphs                                                                           | 175 |

|          |      | 5.8.1   | Example 1: Implementing the Algorithm for Two Products                                          |     |

|          |      |         | in a Flow Shop                                                                                  | 175 |

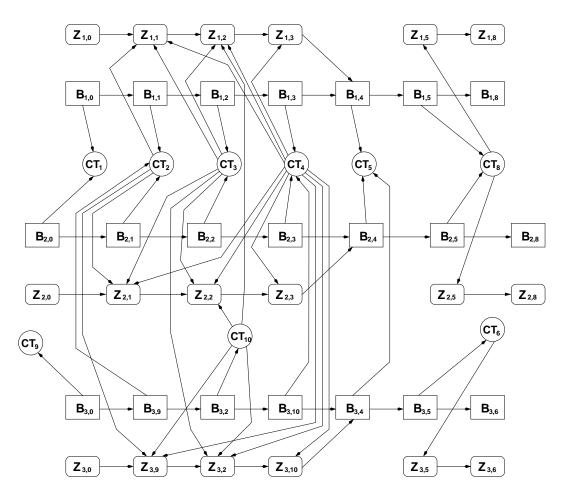

|          |      | 5.8.2   | Example 2: Implementing the Algorithm for Three Products                                        |     |

|          |      |         | in a Simple Job Shop                                                                            | 178 |

|          |      | 5.8.3   | Example 3: Implementing the Algorithm for a Job Shop                                            | 180 |

|          | 5.9  | Using   | the System Graph                                                                                | 184 |

|          | 5.10 | Detect  | ing Loops in the System Graph                                                                   | 196 |

|          |      | 5.10.1  | Algorithm Description                                                                           | 197 |

|          |      | 5.10.2  | Explanation                                                                                     | 198 |

|          |      | 5.10.3  | Example                                                                                         | 199 |

|                | 5.11   | Calcul   | lating System Parameters for the Simple Job Shop | . 200 |

|----------------|--------|----------|--------------------------------------------------|-------|

|                | 5.12   | Exam     | ple                                              | . 202 |

|                | 5.13   | Summ     | nary                                             | . 205 |

| 6              | Ove    | erall In | npact of Reducing Manufacturing Cycle Time       | 207   |

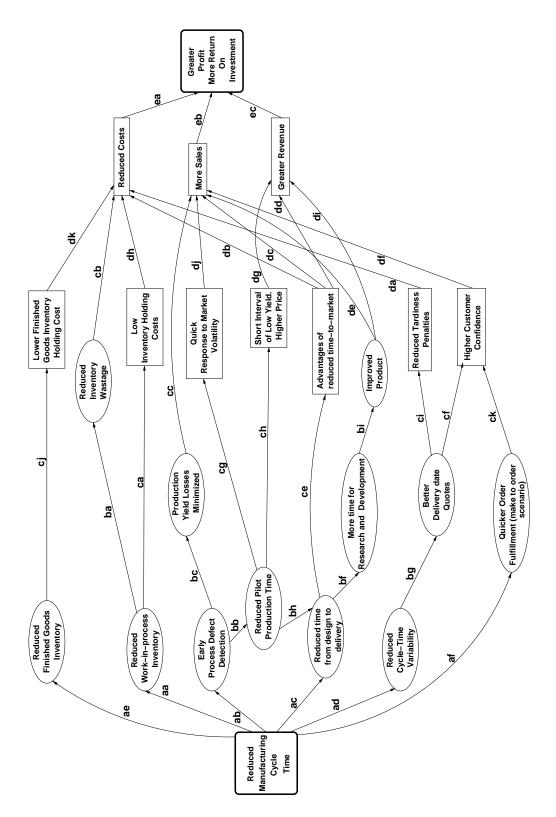

|                | 6.1    | Relati   | ing Manufacturing Cycle Time to Economic Gain    | . 208 |

|                |        | 6.1.1    | Lower Inventories                                | . 211 |

|                |        | 6.1.2    | Process Improvements                             | . 213 |

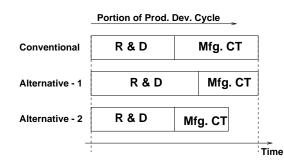

|                |        | 6.1.3    | Product Improvements                             | . 214 |

|                |        | 6.1.4    | Better Order Fulfillment                         | . 217 |

|                |        | 6.1.5    | Higher Profitability                             | . 219 |

|                | 6.2    | Work     | In Process Inventory                             | . 220 |

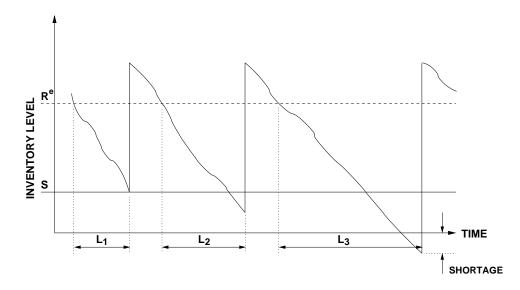

|                | 6.3    | Finish   | ned Goods Inventory                              | . 222 |

|                |        | 6.3.1    | Q-R Policy and Shortages                         | . 222 |

|                |        | 6.3.2    | Demand and Cycle Time Variability                | . 224 |

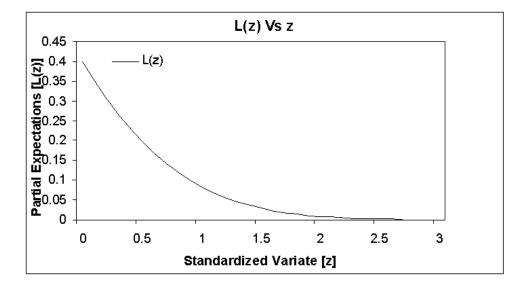

|                |        | 6.3.3    | Calculating Associated Costs                     | . 227 |

|                |        | 6.3.4    | Illustrative Example                             | . 230 |

|                | 6.4    | Comp     | osite Model                                      | . 232 |

|                | 6.5    | Summ     | nary                                             | . 234 |

| 7              | Sun    | nmary    | and Conclusions                                  | 235   |

|                | 7.1    | Summ     | nary                                             | . 235 |

|                | 7.2    | Contr    | ibutions                                         | . 239 |

|                | 7.3    | Future   | e Work                                           | . 244 |

|                | 7.4    | Concl    | uding Remarks                                    | . 249 |

| $\mathbf{B}$ i | ibliog | graphy   |                                                  | 251   |

#### LIST OF TABLES

| 3.1 | Critical Design Information for Improved MWM |

|-----|----------------------------------------------|

| 3.2 | MWM Process Plans                            |

| 3.3 | Products Process Plans                       |

| 3.4 | Desired Product Throughput                   |

| 3.5 | Resource Utilization                         |

| 3.6 | Cycle Time Estimates: Queuing Network Model  |

| 3.7 | Sensitivity Analysis (New Product)           |

| 4.1 | Sub-processes - Block IB                     |

| 4.2 | Sub-processes - Block IC                     |

| 4.3 | Sub-processes - Block ID                     |

| 4.4 | Sub-processes - Block IE                     |

| 4.5 | Sub-processes - Block A                      |

| 4.6 | Sub-processes - Block C                      |

| 4.7 | Sub-processes - Block D                      |

| 4.8 | Sub-processes - Block E                      |

| 4.9 | Sub-processes - Block F                      |

| 4.1 | ) Sub-processes - Block G                    |

| 4.1 | 1 Sub-processes - Block H                    |

| 4.12 | Sub-processes - Block I                                                                            | )3 |

|------|----------------------------------------------------------------------------------------------------|----|

| 4.13 | Sub-processes - Block J                                                                            | )4 |

| 4.14 | Sub-processes - Block L                                                                            | )4 |

| 4.15 | Sub-processes - Block M                                                                            | )4 |

| 4.16 | Sub-processes - Block N                                                                            | )4 |

| 4.17 | PCB Design Features                                                                                | 26 |

| 4.18 | Product cycle times (without new product)                                                          | 28 |

| 4.19 | Product cycle times (with new product)                                                             | 28 |

| 4.20 | Product cycle time comparison                                                                      | 29 |

| 4.21 | Resource Utilization                                                                               | 32 |

| ۳ 1  |                                                                                                    | -0 |

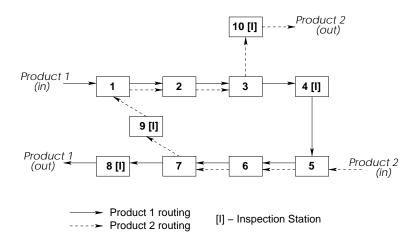

| 5.1  | System processing two products, $\mathcal{J} = \{1, 3, 4, 5, 7, 8\}, \mathcal{F} = \{2, 6, 9\}$ 15 |    |

| 5.2  | Output parameters for two product system                                                           | 58 |

| 5.3  | System parameters for the two and three product scenarios 15                                       | 59 |

| 5.4  | Comparison between the two scenarios                                                               | 59 |

| 5.5  | Scenarios for model comparison                                                                     | 34 |

| 5.6  | Batch Sizes at Inspection Station 1                                                                | 35 |

| 5.7  | Batch Sizes at Inspection Station 2                                                                | 36 |

| 5.8  | Batch Sizes at Output                                                                              | 37 |

| 5.9  | Dependence Table                                                                                   | 34 |

| 5.10 | Steps for the job shop example                                                                     | )3 |

| 5.11 | Throughput requirements                                                                            | )4 |

| 5.12 | Processing station properties                                                                      | )4 |

| 6.1  | Values of input costs and system constants                                                         | 31 |

|      |                                                                                                    |    |

| 6.2  | Values of derived quantites                                                                        | 31 |

#### LIST OF FIGURES

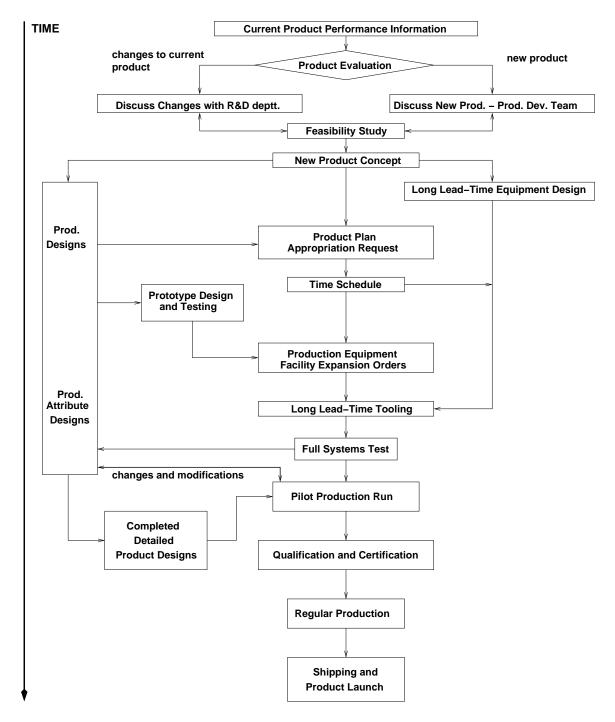

| 2.1 | Product Realization Process                                          | 12 |

|-----|----------------------------------------------------------------------|----|

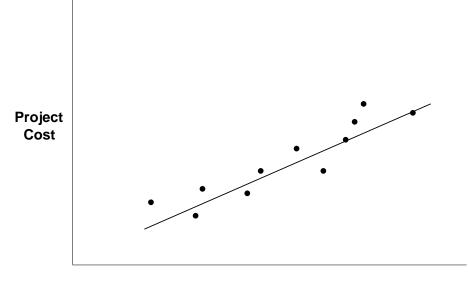

| 2.2 | Project cost increases with increase in development time $[88]$      | 13 |

| 2.3 | The intelligent agent framework proposed by Cutkosky and Tenen-      |    |

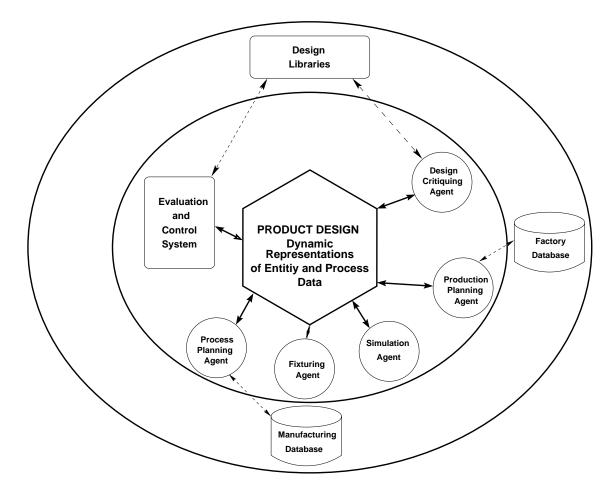

|     | baum                                                                 | 15 |

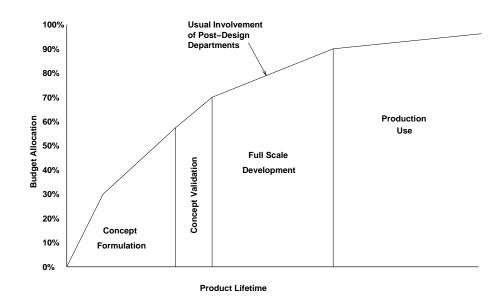

| 2.4 | We stinghouse Curve $[14]$                                           | 18 |

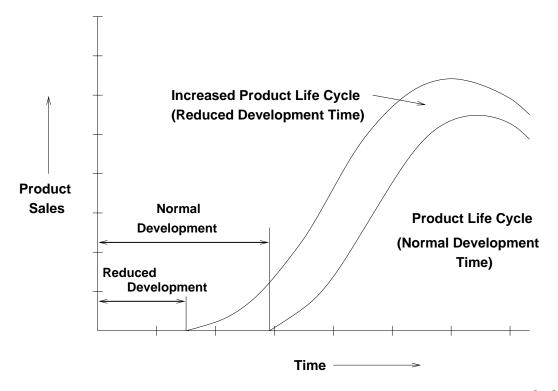

| 2.5 | Product life-cycle curves with normal and faster time-to-market [88] | 23 |

| 2.6 | Product Model Schematic                                              | 30 |

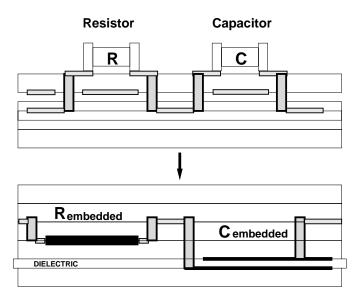

| 2.7 | Cross-section showing embedded passives $[87]$                       | 53 |

| 2.8 | Resistance of an embedded resistor                                   | 54 |

| 3.1 | Block diagram for DFP tool inputs                                    | 69 |

| 3.2 | Flow chart for Case 1                                                | 71 |

| 3.3 | Flow chart for Case 2                                                | 75 |

| 3.4 | The microwave module                                                 | 82 |

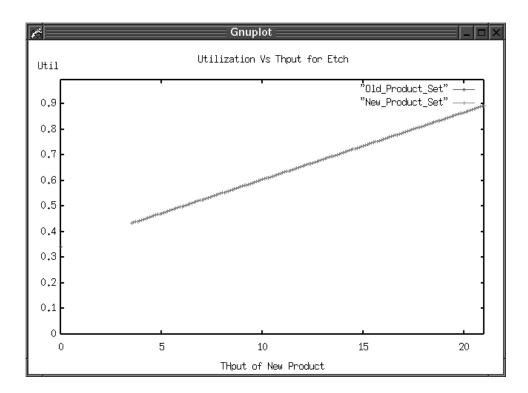

| 3.5 | Typical tool output showing utilization of Etch as a function of new |    |

|     | product throughput                                                   | 88 |

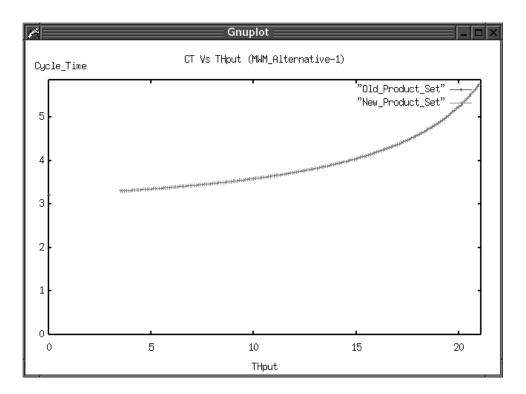

| 3.6 | Typical tool output showing cycle time of an existing product as a   |    |

|     | function of new product throughput                                   | 89 |

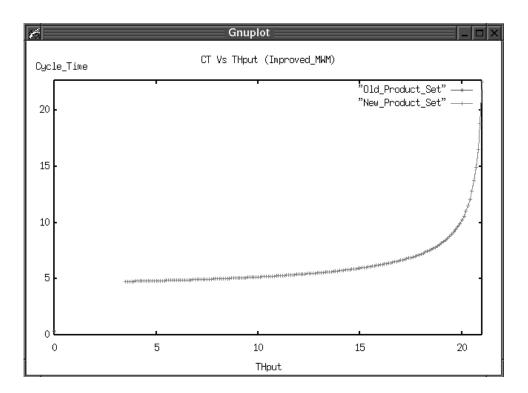

| 3.7  | Typical tool output showing cycle time of the new product as a       |

|------|----------------------------------------------------------------------|

|      | function of its throughput                                           |

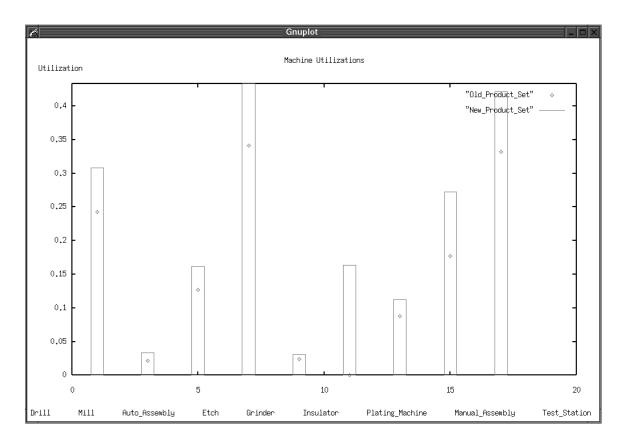

| 3.8  | Typical tool output showing bar graph of utilization of various re-  |

|      | sources                                                              |

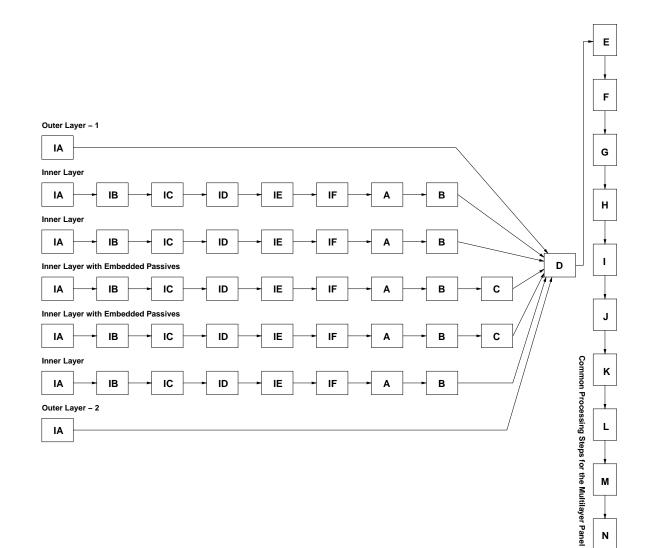

| 4.1  | Operation Network for PCB Manufacture                                |

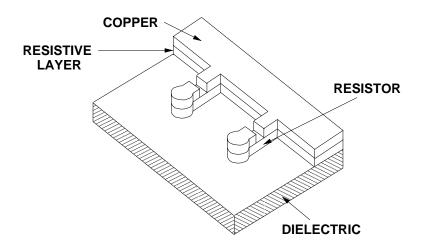

| 4.2  | Embedded Resistor [101]                                              |

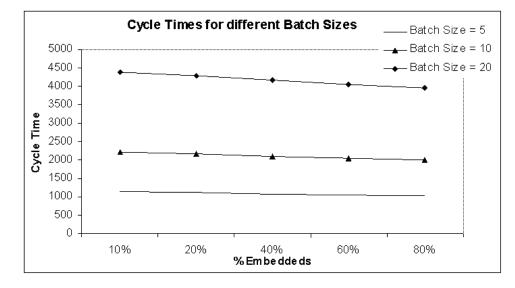

| 4.3  | Manufacturing cycle time with increasing percentage of embeddeds 130 |

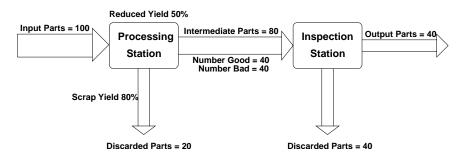

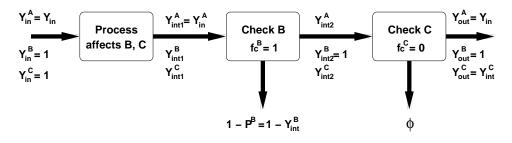

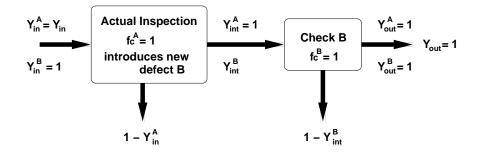

| 5.1  | Normal yield conditions at the inspection station                    |

| 5.2  | Reduced yield conditions at the inspection station                   |

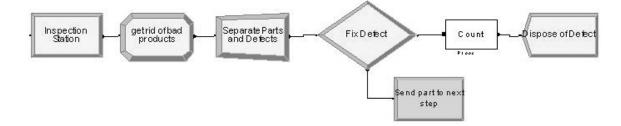

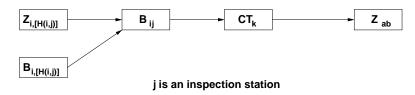

| 5.3  | Processing station block diagram internals                           |

| 5.4  | Inspection station block diagram internals                           |

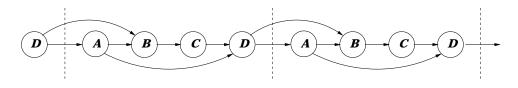

| 5.5  | Routings for the Flow Shop                                           |

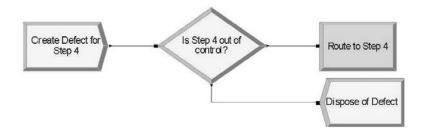

| 5.6  | Defect traverse in block diagram                                     |

| 5.7  | Raw product and defect block                                         |

| 5.8  | Logic block defect detection                                         |

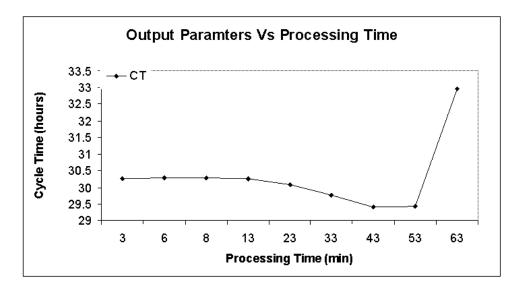

| 5.9  | System Output Vs Processing Time                                     |

| 5.10 | Node Relation                                                        |

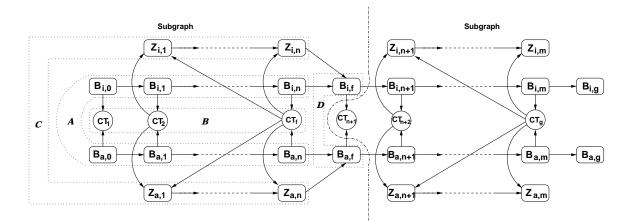

| 5.11 | Sub-graph                                                            |

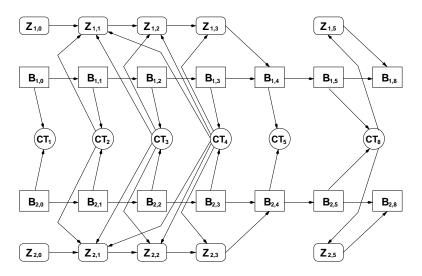

| 5.12 | Two Products Processing Sequence                                     |

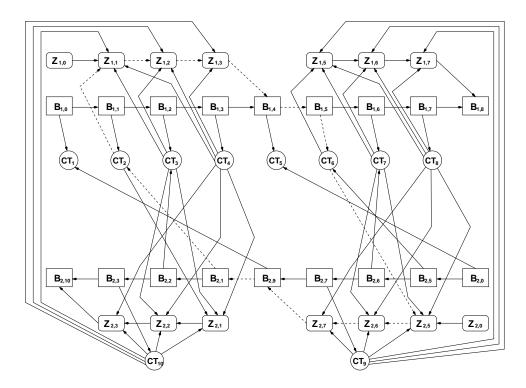

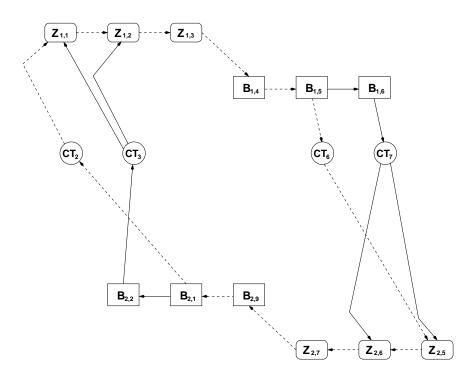

| 5.13 | System Graph for Product Set from Figure 5.12                        |

| 5.14 | Processing Sequence for 3 Product Set                                |

| 5.15 | System Graph for 3 Product Set                                       |

| 5.16 | Sample Routings for two Products                                     |

| 5.17 | System graph for system in Figure 5.16                               |

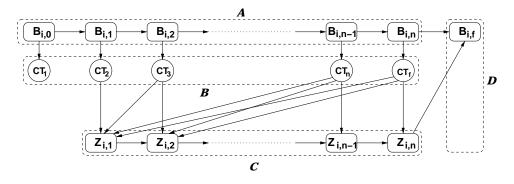

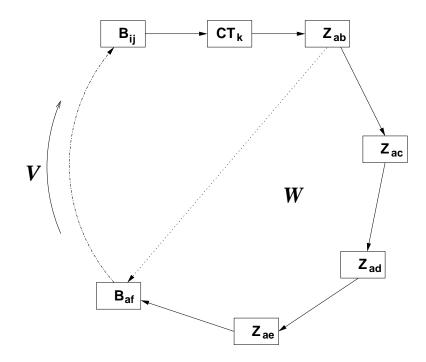

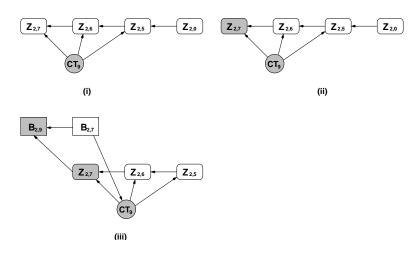

| 5.18 | 4 Sets in the sub-graph of $\mathcal{SG}$                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

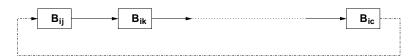

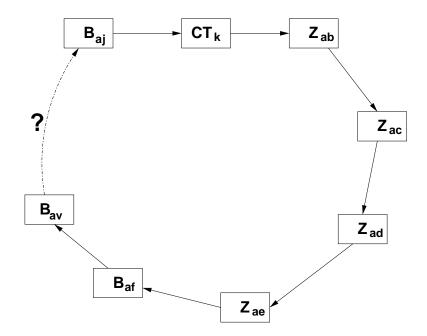

| 5.19 | Cycle $\mathcal{C}$ with all B type nodes $\dots \dots \dots$ |

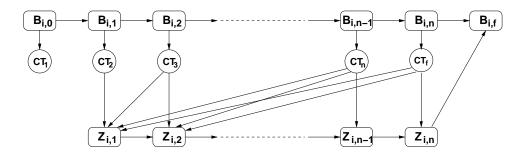

| 5.20 | Connections between type B, CT and Z nodes                                                                                                                    |

| 5.21 | Instance of a cycle in $\mathcal{SG}$ when product $a = i  \dots  \dots  \dots  192$                                                                          |

| 5.22 | Instance of a cycle in $\mathcal{SG}$                                                                                                                         |

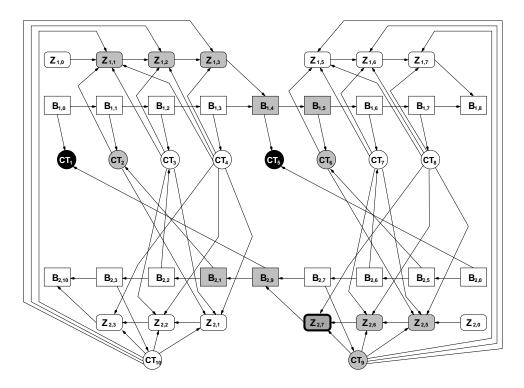

| 5.23 | Subdivided system graph for a flow shop                                                                                                                       |

| 5.24 | Set Interconnectivity                                                                                                                                         |

| 5.25 | Cycles in the System Graph                                                                                                                                    |

| 5.26 | Cycle detection algorithm example - Figure 1                                                                                                                  |

| 5.27 | Cycle detection algorithm example - Figure 2                                                                                                                  |

| 5.28 | Average manufacturing cycle time for products versus processing                                                                                               |

|      | time at electroless plate $\ldots \ldots 205$                                           |

| 6.1  | Map from reduced manufacturing cycle time to economic gains 210 $$                                                                                            |

| 6.2  | Lower manufacturing cycle time allows more time for research and                                                                                              |

|      | development                                                                                                                                                   |

| 6.3  | Q-R Policy and Cycle Time Variability                                                                                                                         |

| 6.4  | L(z) as a function of $z$                                                                                                                                     |

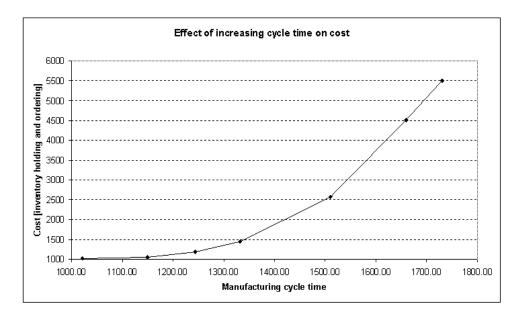

| 6.5  | Cost affected by increased cycle time                                                                                                                         |

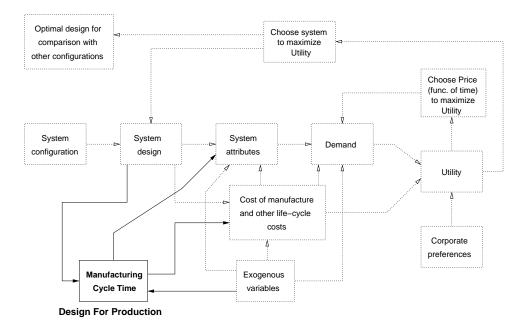

| 7.1  | Contributions of DFP to Hazelrigg's decision-based design frame-                                                                                              |

|      | work [59]                                                                                                                                                     |

## Chapter 1

## Introduction

Product variety is continuously increasing in today's world market. In such an environment, the required philosophy for a company's survival, is the constant replacement of old products with new ones, improved variations of current products and completely new products. Product development has thus become a very crucial aspect of corporate competition. The design and development of a product is a complex process involving numerous considerations such as market analysis, requirements definition, conceptual design, detailed design, materials and process selection, optimization, process control, testing and evaluation, costing, manufacturing and production, and marketing [1, 5, 14, 18].

Successful product development requires the definition of various measures of performance for different phases of the product life cycle and methods to predict these performance measures. Accurately predicting these metrics enables the product development team to develop the product "first time right" thereby avoiding or at least minimizing development costs and product redesign. Such performance measures may be numerous and influencing various aspects of the development cycle, from concept generation to product delivery. Traditionally, while designing a new product, each phase in product development is completed before the product passes to the next phase. This is known as "over the wall" design. For example, the designer finalizes the detailed designs before passing them to the manufacturing phase. There are, however, potential problems associated with this way of designing a product. Among these are the following [131]:

- There is a loss of abstract and implied information as the product passes from one phase to another. Each phase receives a different interpretation of the customer requirements. Thus there exists some risk that the final product will not completely satisfy the customer requirements.

- 2. There is significant loss of time and effort in returning the designs to the design phase from the post-design phases to correct any mistakes or short-comings discovered in these phases.

- 3. By finalizing the designs in the design phase, the designer utilizes only his knowledge of the design scenario. The knowledge of the post-design operations such as manufacturing cannot be incorporated into the designs. As a result, opportunities for product optimization over all the processes are missed due to the lack of effective communication between the two operations.

The Design for X (DFX) approach to designing a product aims to alleviate some of these problems by designing the product while keeping under consideration the performance of the design during other phases of its life cycle [47, 68, 69]. The DFX methodology evaluates product designs along with associated life cycle requirements such as those associated with manufacturability, schedulability, recyclability, dis-assemblability, producability and so on, to determine the product performance during these phases. It attempts to identify possible problems and shortcomings in the designs. DFX searches for solutions to these problems, proposing changes to the product or processes and prioritizes these ideas based on evaluation of the effects of these suggestions on the anticipated performance of the product, thereby avoiding redesigns later in the process.

#### 1.1 Motivation

Associated with each phase in the product development process are a time and a cost which may be attributed to the requirements of that phase of the process as well as possible rework cycles, constituting total product development time and cost. In order to design a product so as to maximize product profitability, it is necessary to understand the economic implications of the product design during its life cycle. To achieve this goal, it is first essential to model this economic impact along with quantifiable metrics.

This dissertation studies the association between product design and manufacturing system performance. Models developed as a part of this research along with suitable performance metrics delineate the product design - manufacturing system relationship. Such metrics include manufacturing cycle time, WIP and throughput. These key factory-level performance measures affect financial measures such as cost, revenue and profitability.

Manufacturing cycle time may be defined as the total time spent by the product in the manufacturing system. Manufacturing cycle time is the interval that elapses as the manufacturing system performs all of the operations necessary to complete a work order. This manufacturing cycle time has many components, including move, queue, setup, and processing times. The terms *Throughput Time* or *Flow Time* are also used to describe the time spent by a product in a manufacturing system. The terms *Manufacturing Cycle Time* and *Throughput Time* are used interchangeably throughout this dissertation.

An examination of the impact of the product design would be incomplete without assessing the importance of manufacturing cycle time to product profitability, evaluating the impact of the manufacturing cycle time on the product life cycle and modeling these relationships. Such an analysis requires developing maps and models that describe how modifying the manufacturing cycle time affects costs and revenues for a product. Such maps and models can then be used as part of a more comprehensive product profitability assessment schema.

In summation, this research is motivated by the need to understand the impact of a product design on manufacturing system performance through certain production metrics and to translate these metrics into quantities that contribute to overall product profitability.

#### **1.2** Design for Production

This dissertation introduces the term *Design for Production* (DFP) to describe methods that determine if a manufacturing system has sufficient capacity to achieve the desired throughput and methods that estimate the manufacturing cycle time. These methods require information about a product's design, process plan, and production quantity along with information about the manufacturing system that will manufacture the product. Knowing the capabilities of the manufacturing system can help a designer evaluate the feasibility of alternative product designs and use the information to either choose from proposed alternatives or modify the existing product design. This will remove the need to actually put the product through the post-design phases before discovering any infeasibility or prohibitive costs associated with making the product in the given manufacturing system.

Design for Manufacture (DFM) evaluates the materials, the required manufacturing processes, and the ease of assembly for the product. (This discussion will use the term manufacturing to describe both fabrication and assembly, and will include design for assembly as part of design for manufacturing.) Therefore, both DFM and DFP are related to the product's manufacture. DFM evaluates manufacturing capability and measures the manufacturing cost. It focuses on the individual operations that manufacturing requires. On the other hand, DFP evaluates quantity and rate of parts that the manufacturing system can output and how long each order will take. That is, it evaluates manufacturing capacity and measures the manufacturing system as a whole. Like DFM, DFP can lead a product development team to consider changing the product design. In addition, DFP can provoke suggestions to improve the manufacturing system. DFP is likely to find greater application to new product introduction into an existing manufacturing system already producing certain products.

DFM approaches that generate process plans and estimate processing times can be the first DFP step, since DFP methods may use this information. Traditional DFM approaches can also improve manufacturing cycle time since they minimize the number of parts and reduce the processing time of each operation. DFP approaches may be distinguished by their focus on evaluating manufacturing capacity and manufacturing cycle time. Different research works have used various names to describe DFP approaches, including design for existing environment [132], design for time-to-market [50], design for localization [81], design for speed [97], design for schedulability [79], and design for manufacturing system performance [122]. Some researchers have reported case studies in which product designs were modified to improve production.

This research studies situations where a new product, which may be an improvement of an existing design or a completely different product, will be introduced into a given manufacturing system already processing a set of products. This dissertation presents models for

- understanding how introducing a new product into an existing manufacturing system affects the performance of the manufacturing system,

- understanding how changes in the product design affect manufacturing system performance, and

- understanding the economic implications of reducing manufacturing cycle time.

Specifically, this dissertation presents models and tools for estimating the manufacturing cycle time and throughput of a manufacturing system. It also discusses and models how manufacturing cycle time affects costs, revenue and profitability.

Thus, through the DFP approach, this research aims to provide the product development team with methods to evaluate the performance of the manufacturing system before production begins. Tools based on the approach may be applied during the conceptual or embodiment or detailed design phases of the design development process. Based on the requirements of the approach, however, it may be best suited for the embodiment phase, when the design team has a reasonable idea of various design instances and before all aspects of the design have been finalized. Having said this, the utility of the approach in the chronology of the development process depends on the specific product development process. Also, it must be noted that the DFP approach addresses only one aspect of the product life cycle. While designing a product, information obtained using this approach must be combined with information from other phases of the life cycle. This dissertation presents applications that reflect the use of the DFP approach and associated tools for a typical product development process.

#### **1.3** Organization

This dissertation is organized as follows: Chapter 2 reviews previous work that researches various product development concepts. It surveys literature documenting the importance of product design to post-design product development processes. Chapter 3 presents manufacturing system models based on queuing network analysis. It demonstrates how these models play a significant role in the DFP approach. Chapter 4 applies the models and algorithms developed to understanding the impact of embedding passive components into the substrate of a printed circuit board. Chapter 5 presents algorithms to analyze manufacturing processes and systems with process drift, where defective parts processed at a workstation are detected at a subsequent inspection station. Chapter 6 describes the economic benefits of reducing manufacturing cycle time. Chapter 7 summarizes the work done as part of this research. Further, it lists the research contributions from this work and presents potential ideas for future work that would extend the approaches and models presented as a part of this research.

#### Chapter 2

# Literature Review

### 2.1 Introduction

Product development is a complicated process starting with a detailed target assessment, comprising an extensive research of the current market scenario, available products and understanding product customer requirements. This is followed by various steps from defining product specifications based on these requirements to packaging and dispatching the final product to its final destination. An effective product development process has a number of benefits [88] such as:

- 1. Increased Revenue

- (a) Increased product life-cycle revenue

- (b) Increased market penetration as a result of being first to market

- (c) Success in time-sensitive markets

- (d) More successful products

- 2. Improved product development productivity

- (a) Shorter development cycle times

- (b) Less development waste

- (c) Better resource utilization

- (d) Better ability to attract and retain technical talent

- 3. Operational Efficiencies

- (a) Design for manufacturability, serviceability and other characteristics

- (b) Higher-quality products

- (c) Lower engineering change order costs

- (d) Improved predictability of launch

New product introduction involves a long sequence of operations. The number of steps and the steps themselves depend on the type of product being developed. The schema for a product realization process may be outlined as follows:

- 1. The company analyzes feedback from the market about the current product performance and uses the information to identify need for modifications or new product launch.

- 2. Depending on the feedback, the research and product development teams discuss implications of the proposed modifications or the new product design. The costs involved, complexities (technical and other), and time required influence the decision about the changes or new product introduction.

- 3. Depending on discussions with the various constituents of a product development team such as manufacturing, reliability, a "new product concept" is formulated, which is then presented to the management for approval and authorization for further design work.

- 4. During the design process, in an ideal team environment, other development processes such as cost estimation may proceed simultaneously. Design of long lead time facilities, equipment and tooling may also commence.

- 5. Once a firm product concept has been finalized, resources are allocated towards tooling, equipment, testing, advertising, service training and allied activities. Design work continues while these decisions are being made.

- 6. The production equipment and facilities expansions are ordered and their construction proceeds. The long lead time tooling work is also begun. The product and process design continues during this phase.

- 7. Prototypes are built once the design work nears completion, and performance and reliability testing of the prototypes is undertaken. Designs are evaluated for conformance to original product plan and adherence of the project to its time schedule is examined.

- 8. Designs are finalized and sent for manufacturing and the remaining tooling, gauging and other equipment is ordered.

- 9. The field and life testing of the product referred to as *beta testing* proceeds. Potential customers are given the product for feedback and evaluation.

- 10. The production facility installations are completed. Complete detailed drawings and finalized bill-of-materials are released to the production department. A pilot production run is made and quality control features are adopted. Engineering changes are made depending on customer feedback and pilot production results.

11. Regular production is commenced and the products are shipped to the market.

Figure 2.1 shows one such combination of steps that represents the product realization process [14]. This is not an ideal sequence but only a schema to illustrate the basic approach and activities involved. The sequence would differ in different organizations.

Although the earlier paragraphs detail the product development process as a series of steps, in reality it hardly proceeds in such a regular manner. In practice, the process usually comprises of a network of paths that the product follows including a number of feedback loops between the various stages of the product development cycle. These feedback loops help ensure feasibility of the product design from perspective of post-design processes. However, these feedback loops, though useful in helping the product development team converge on a feasible design solution, nevertheless increase the time required and costs involved from demand recognition to the actual product launch and often contribute a great deal to the costs involved in making the product. Figure 2.2 depicts the relation between the project cost and the product development cycle time.

In order to make the product quickly and with minimum costs, it is prudent to minimize the number of feedback loops in the development process. This will streamline product development, taking it closer to the goal of achieving a serial procedure as outlined earlier.

For any corporate organization, short delivery times, periodic product innovations, and shorter time-to-market are very important attributes. Those organizations which can achieve and maintain such values usually outperform all competition.

Figure 2.1: Product Realization Process

**Product Development Time**

Figure 2.2: Project cost increases with increase in development time [88]

#### 2.2 Concurrent Engineering

Syan [127] defines concurrent engineering as: "Concurrent engineering is a systematic approach to the integrated, concurrent design of products and their related processes, including manufacture and support. This approach is intended to cause the developers, from the onset, to consider all elements of the product life cycle from concept through disposal, including quality, cost, schedule and user requirements". It follows from this definition that the development team in a concurrent engineering environment in aided in establishing a degree of clairvoyance in analyzing problems, that the product may to encounter during various stages of product development, aided by knowledge of development processes and tools like optimization or graph theory. The aim is to alleviate these problems at an early stage of development by making suitable development decisions. Magrab [86] presents a set of techniques under the IP<sup>2</sup>D<sup>2</sup> methodology which could also be applied to facilitate concurrent engineering towards better product development. The proposed  $IP^2D^2$  method broadly indicates the overlapping, interacting, and iterative nature of all the aspects that impact the product realization process. It is a continuous process by which a product's cost, performance, features, and values lead to a company's increased profitability and market share.

The benefits of concurrent engineering [71] are numerous and wide-spread throughout the product development cycle, including but not limited to reductions in time to market, reduced design changes and design iterations, improvements in the manufacturability, assembly, serviceability, recyclability and overall quality of the products. Hauptman and Hirji [54] survey the applicability of concurrent engineering to product development in great detail based on the study of a multitude of product development projects using concurrent cross-functional teams.

One of the methodologies for achieving this concurrency in the product and process engineering [6, 91] is based on the formulation of an optimization problem with constraints drawn from various aspects of the product life-cycle. Tan *et al.* [130, 131] suggest a model which brings together different phases of the product development process using an intelligent agent framework. The approach begins from representing customer requirements and iteratively generates the final designs based on cost evaluation of the initial designs. Initial designs are provided to the system and the set of constraints between the product and the outside systems do not change during the iterations. The system aims to create a final design while taking into consideration most aspects of the product development process. All information exchange occurs between agents governing different stages of the development life such as process-planning agent, simulation agent, design agent, and critiquing agent. Cutkosky and Tenenbaum [31] present a system based on

Figure 2.3: The intelligent agent framework proposed by Cutkosky and Tenenbaum

a similar architecture. Their paper provides details of the system architecture, representations and the software module design. Figure 2.3 represents the general framework proposed. Brookes *et al.* [16] list some relevant case studies of implementation of the concurrent engineering methodology.

The optimization modules developed for finding the best product design tend to use the product cost [32, 40, 99, 122, 142] as the objective function. Soundar and Bao [122] suggest a formulation for the problem with cost as the objective and the constraints based on

- 1. the critical design attributes as surface finish and weight

- 2. the critical manufacturing system performance attributes as WIP and queue time

and formulating a utility function to find an optimal solution. Wei and Egbelu [142] propose algorithms to model various manufacturing costs. Once these are decided, the minimum cost manufacturing sequence selection is modeled as a mixed integer problem with minimizing the summation of the costs as the objective and the operating sequence parameters as the constraints. The aim is to minimize costs while preserving product functionality.

Ball *et al.* [6] take a somewhat different approach to formulating the optimization problem. They propose that the cost be treated as an independent variable. Thus, now the cost may be used as a constraint in lieu of an objective as adopted by the earlier approaches. Often the design problem is split into constituent subproblems and optimization with cost as the objective is performed on individual sub-problems. The disadvantage of this method is that though the cost may be minimized for the local sub-problem, in the global scenario the cost may not always be a minimum. Using the cost as a constraint and solving the overall problem based on tradeoff analysis, ensures that the cost always remains constrained below the specified value. However, it is important to mention that in this case, the cost constraint decision is a designer prerogative and (s)he must be provided with adequate knowledge to help make a well-advised decision.

Thus the problem is a tradeoff problem between the costs and/or time involved in making the product and the product performance. With the optimization formulation it is hoped that the costs and time involved in the post design problems may be optimized against a slightly increased design cost and performance.

# 2.3 Importance of Design

In Section 2.1, the steps in a typical product development cycle were enumerated. Embedded in the chronology of events that formulate the development cycle, is the allocation and approval of finances without which the progress of the product development is difficult. The "Westinghouse Curve" [14] illustrates how the life cycle cost of a typical product is greatly affected by the decisions made during the early stages of the product design phase. Figure 2.4 shows this curve. From the curve, it may be seen that by the time a product concept is validated, well before the development is completed, 70% of the total budget for development has already been allocated. This underscores the importance of providing the designer with adequate knowledge of the post-design processes [72]. Using this knowledge, the designer can make the "best" design decisions in order that the costs may be minimized during the concept stage itself, well before the product goes into production.

In addition, any required redesign may be implemented in different stages of the product development process. Depending on the stage at which it is implemented, a redesign system behaves in different capabilities. In accordance, during the initial stages of the design process it serves to guide the designer in taking important design decisions [50] like materials and process selection, joint definitions and so on, based on knowledge of post design processes and customer requirements, stored in libraries. Thus, at this stage the approach complements the concurrent engineering philosophy as applied to the design stage, improving the designs by equipping the designer with knowledge from other processes. When the redesign schema is implemented at a later stage, as during the detailed design phase after the initial designs have been formalized, it serves as an evaluator of the preliminary designs.

Figure 2.4: Westinghouse Curve [14]

The system attempts to characterize the designs according to the functionality and designer intent.

# 2.4 Design for X

Magrab [86] defines DFX as: "Design for X (DFX) may be defined as a knowledgebased approach that attempts to design products that maximize all desirable characteristics such as high quality, reliability, serviceability, safety, user friendliness, environmental friendliness, and short time-to-market in a product design while, at the same time, minimizing lifetime costs, including manufacturing costs". The methodology spawns from the idea of designing products while taking into consideration the downstream processes in the product life-cycle and their effects on the product designs [47, 68, 69, 136].

The previous section explained the importance of design in the product development cycle towards overall financial management of the product development project. The DFX methodology comprises analyzing the product and processes involved and their performance characteristics, identifying the problems and shortcomings in these and highlighting them, searching for solutions to these problems, proposing changes to the product and/or processes (redesign advice) and prioritizing these ideas based on the evaluation of the effects of these suggestions on the performance of the product. The effects of a number of post-design processes such as manufacture, assembly, schedulability, recyclability, disassembly, production, fabrication, reduced time-to-market [12, 41, 50, 62, 67, 70, 98, 128, 129, 136] on the product design have been studied in detail. Magrab [86] includes a comprehensive list of broad DFX areas that may be considered while designing the product. The elements of these broad DFX areas may be considered as overlapping evaluation criteria in the IP<sup>2</sup>D<sup>2</sup> methodology.

A number of expert systems have been developed based on the DFX philosophy [24, 73, 83, 120]. An example is Wu and O'Grady's [144] research on the correlation between the concurrent engineering and design for assembly methodologies. The approach explained uses a variant of the Petri Nets concept to abstract and model the information needed for design for assembly during the design process. The effects of changes in the designs on the assembly process in terms of the cost and lead time, as the designer incorporates these changes in the design, serve as evaluation measures for incorporating the changes into the designs.

Thus, when neither the product designs nor the processes are fixed, or for the introduction of new products with new process technologies, there exists large scope for concurrency in development for which DFX tools and techniques can play a key role.

# 2.5 Design for Manufacturing

Design for manufacturing methodologies are used to improve a product's manufacturability. Three important issues dominate the discussion of design for manufacturing (DFM), also called design for manufacturability.

- Can the manufacturing process feasibly fabricate the specified product design?

- How much time does the manufacturing operation require?

- How much does the operation cost?

(For discussion, this body of work uses the term manufacturing to describe both fabrication and assembly, and includes design for assembly as part of design for manufacturing.)

DFM guidelines help a product development team design a product that is easy to manufacture, while other DFM approaches evaluate the manufacturability (feasibility, time, and cost) of a given product design with respect to a specific manufacturing process. Some manufacturability evaluation approaches give the product development team feedback on what aspects of the design make it infeasible or difficult to manufacture.

DFM compares a product's manufacturing requirements to existing manufacturing capabilities and measures the processing time and cost. DFM approaches can be used during the conceptual design and the detailed design steps. Generally, DFM approaches focus on the individual manufacturing operations, for example Boothroyd *et al.* [13], Bralla [15], and Kalpakjian [74].

In an attempt to increase the awareness of manufacturing considerations among designers, leading professional societies and some manufacturing firms have published a number of manufacturability guidelines for a variety of manufacturing processes [4, 11, 14, 102, 135]. Researchers have developed several different approaches to evaluate manufacturability of a given design. Existing approaches can be classified roughly as follows:

- 1. Direct or rule-based approaches [71, 73, 110] evaluate manufacturability from direct inspection of the design description; design characteristics that improve or degrade the manufacturability are represented as rules, which are applied to a given design in order to estimate its manufacturability. Most existing approaches are of this type. Direct approaches do not involve planning, estimation, or simulation of the manufacturing processes involved in the realization of the design.

- 2. Indirect or plan-based approaches [56, 58, 63, 66, 92] do a much more detailed analysis; they proceed by generating a manufacturing plan and examine the plan according to criteria such as cost and processing time. If there is more than one possible plan, then the most promising plan may be used for analyzing manufacturability, and some plan-based systems generate and evaluate multiple plans [52, 53]. The plan-based approach involves reasoning about the processes involved in the product's manufacture.

The direct approach appears to be more useful in domains such as near-net shape manufacturing, and less suitable for machined or electro-mechanical components, where interactions among manufacturing operations make it difficult to determine the manufacturability of a design directly from the design description. In order to calculate realistic manufacturability ratings for these latter cases, most of the rule-based approaches would require large sets of rules. DFM has been very useful for reducing the unit manufacturing cost of many products, and successful product development processes require tools like DFM [115].

# 2.6 Design for Time-to-Market

Time-to-Market is the time from product conceptualization to market introduction. Short time-to-market means that a product reaches the market early, which in turn provides the corporate organization with the opportunity to enter the market during the growth phase of the product life-cycle, when the profit margins and potential for growth are higher and the product has a longer market life. Bralla [14] enumerates some of the advantages of achieving the objective as:

- 1. Reduced time-to-market implies reduced product development time, which in turn reduces the development costs since less funds are allocated to late engineering changes, rework and delays due to bureaucratic tarries.

- 2. The design related cost reductions are applied early in the development cycle.

- 3. As a consequence of being the first to introduce the product into the market, the company can be assured of an increased market share and the distribution and retail network confidence. This in turn increases the life-cycle of the product. Figure 2.5 compares the life cycles of products under normal and reduced development times.

- 4. Typical product delays that are associated with the introduction of a new product are reduced due to the reduced introduction time of the product into the market. These may include unforeseen changes in the market conditions necessitating design changes and changes in the development team members

Figure 2.5: Product life-cycle curves with normal and faster time-to-market [88]

and the competence of these members.

Depending on the complexity, technical or otherwise, the process of introducing the new product may be very complex. Balachandra [5] identifies the following target areas for strategic initiatives by the product introduction project management in order that this complexity may be minimized as much as possible:

- 1. *Technology:* Technological information about new developments should be available to the product designers, manufacturing and marketing teams through free flow of such information and interactions between the teams.

- 2. *Market:* There should be a clear definition of the key attributes of the competitive strategy for the product within which all development should be attempted without aiming at perfection. The focus should be on incremen-

tal improvements in the product line.

- 3. Organization: All functions in the development should be treated with equal importance and there should be adequate communication [9] within and between different functional teams with suitable conflict resolution mechanisms.

- 4. *Vendors:* Vendors should be involved form the beginning in the product development.

Brookes and Backhouse [17] discuss the importance of evaluating the performance of product introduction and the difficulties faced within the task, as the product life cycle reduces and more products need to be introduced more often into the market. Some of the performance measures that can be used to evaluate the time-performance include time-to-market measures, average concept-to-launch time, time for each phase of development, average over-run and percent of products over-running, average time between product re-designs, product performance measures, product cost, technical performance, quality, return on sales, market share, design performance, manufacturing cost, manufacturability and testability. They provide case studies [17], evaluating product performance in different corporate organizations.

Govil [50] presents an approach to combining product design and production in an attempt to reducing the time-to-market of the product. The strategy, which is employed in the conceptual design stage of product design, has the following stages. First the designer inputs the product and process information into a tree structure. The system performs computations to find the production rate in order to be able to launch the product at the desired time-to-market. Next, the product and production system components that are critical to the desired production rate are identified. Alternatives for the product and production system that contribute towards improving the production rate are identified and the best set of alternatives is selected and output to the designer as improvements.

The system guides the user in creating a functionally decomposed representation of the product design based on Suh's axiomatic functional decomposition approach [124]. The user is allowed to assign materials for the parts of the product and choose compatible manufacturing processes. It also allows choice of assembly processes for various sub-assemblies leading to the final assembly. The system then calculates various processing system parameters, identifies the critical parameters and suggests improvements to the system and the processing logistics in order to reduce/eliminate the criticality of these resources.

## 2.7 Design Refinement

One of the important components of the concurrent engineering and DFX philosophies is design modification or design refinement. The aim is to modify the designs during the design phase itself before indulging in more expensive and resource intensive processes like manufacturing, while anticipating the problems that may be encountered in these stages. In order to achieve this, the redesign systems may act in a feed-forward capacity (design guidance) or in a feedback mode involving completed product designs. It is difficult to distinguish between the two mechanisms rigorously and a good redesign system combines the benefits of both.

## 2.7.1 Classification and Representation

Dixon et al. [39] propose a classification for mechanical engineering design based on a combination of the actual design, the designer and the design environment. They emphasize the need to represent functionality in product design. The objective of the classification is to enable the problems themselves to indicate possible solution processes. Bacon and Brown [3] propose using such classifications and repositories of devices derived therefrom to help discover the behavior of a device given some formal description of the structure. Haves and Gaines [57] discuss a similar approach applying similar principles, termed *near misses*, to suggest redesigns in order to improve the manufacturability of the part. The suggestions are related to the part designs, the size and shape of the stock and the manufacturing equipment. Crawford and Anderson [29] propose a different architecture for preliminary mechanical design i.e. a stage where each component of the solution can be modeled by a number of parameters, variables, constraints and goals, using network representations and graph algorithms to model problems and plan solution procedures. Rinderlie [109] proposes product representative designs as combinations of three descriptions function, form, and fabrication which then formalizes the designer's task as specifying form in order to satisfy any constraints on product function and fabrication. The paper thus lays the foundation for representation of functionality of product designs and its relationship with the form and product fabrication. Mckay et al. [89] extend the functional modeling idea and describe the use of advanced product modeling techniques to represent product families without data redundancy. Two domain models are used to depict a model of a variant in a product family - a product variety data model and a framework-based product data model. In a similar work, Kimura and Suzuki [76] outline a framework for a more efficient product design system through the representation of design intent. Their emphasis is on separating design constraints as either *well-formed* or *ill-formed* and then adapting solution methods suitably.

Aldakhilallah and Ramesh [2] propose an architecture for a self-contained product design, process planning and control system which is well suited for a practicable and comprehensive concurrent engineering approach as explained above. They propose the decomposition of the designs into the constituent elemental features, which are prioritized by functionality and represented in a graph structure. The system suggests changes, as may be required, to the product designs for suitability to the manufacturing operations. During production, the system monitors the machine breakdowns, capacity changes and other anomalies and modifies the schedule depending on the severity of these anomalies.

Thus considerable efforts have been made to represent product information as cross-functional models which can be used to represent data required for various product development stages. These unified models are then evaluated and design modifications put forth. As mentioned before, it is very difficult to decouple concurrent engineering and DFX, and a system which aims to achieve better performance should aim to use a combination of these redesign schemas (in the advisory and evaluative capacity) during the development process.

## 2.7.2 Representing Design Advisory Rules

During the conceptual design stage the product development team hopes to take into consideration the entire development life cycle of the product while making design decisions. Hence, it is essential that as much knowledge as possible be made available to the design team about all aspects of the product life cycle. Function plays a strategic role in the conceptual design stage. Deng *et al.* [38] describe strategies and methods for developing such a functional modeling design environment to guide designers during the conceptual design stage. They have developed a model based on the function, environment, behavior and structure of the product. Bardhan *et al.* [8] discuss an approach towards development of a multi-digit code system for each feature to be added to a design, that identifies its major attributes, feature essentials and unique identification. Based on this code system, the applicable design rules are checked for possible violation and modifications are suggested.

Govil's [50] advisory system guides the designer during the conceptual design phase by providing information about the post-design processes. Libraries of materials and properties are provided to the designer who is required to input the designs in the form of functional requirements (FR) of the parts and the design parameters (DP) corresponding to these functional requirements, using the axiomatic design theory [124]. Once the embodiments are finalized from these FRs, the designer is advised on the materials-processes options and the design-materialprocess model is created in the form of a tree structure. This tree structure may then be used for further analysis. Schmidt and Cagan [116] discuss the ability of grammars to generate a space of machine designs, providing a platform for a designer assistance tool. The central idea is to generate designs from a library using a grammar, the details of the representation of which are explained by Flasinski [45].

Often products exist over multiple domains and a product model defined in one domain needs to be valid and usable in another domain. Especially relevant to this situation is a product requiring construction of a prototype, since the materials and processes for the product and the prototype are normally different. Various researchers [49, 78, 146] explain problem solving architectures that cover multiple domains by managing information during the transformation between the two domains. Krishnan and Magrab [78] propose the use of interchangeable process specific entities to model the product in multiple domains. The use of such process specific entities is advantageous since the limitations of the manufacturing process are implicitly integrated into the design and the entities are representative of these limitations. Thus the geometric information and the manufacturability information are coupled into the product designs as they are created.

## 2.7.3 Product Redesign

Redesign may be included in the design process by incorporating design modifications after the detailed design phase. In this phase, the geometry of the parts is defined and the associated information needed to manufacture the part as dimensions, tolerances and related parameters is formalized. After this stage is complete, the designs may be evaluated in the context of post-design processes and relevant suggestions to improve product design performance during these post-design processes may be put forth.

In order for the system to evaluate designs efficiently and put forth viable and useful design modification options, it is imperative that the product models that act as input to these evaluation schemas be succinct and representative of all aspects of the product design. To attain this objective and to capture the functionality (what the design does) and design intent (justification of the underlying rationale behind design decisions), one well-researched approach is the creation of an *intermediate model* [60, 61, 133].

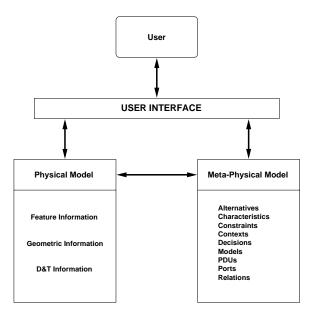

Figure 2.6: Product Model Schematic

Figure 2.6 shows the schematic for such a product model comprising two parts: a physical model and a meta-physical model along with their inter-relationships. The overall model is based on the creation of an abstract Product Definition Unit (PDU) as the basic element, which can represent anything from a system to a feature. The PDUs are given types, characteristics and links with other PDUs and physical entities. The PDU is merely a shell to encapsulate information. Features, which are natural collections of items that are used in a particular context, form the links between the physical and meta-physical entities. The information in the meta-physical realm pertains to nature, structure and behavior of objects in the physical realm.

DeMartino *et al.* [34] propose the creation of an *Intermediate Model* which is a multiple-view, feature-based representation of the product. To integrate design with other engineering processes, it is necessary to have a product model which is representative of the information of the design and the relevant engineering process and both must be able to share this information. The proposed intermediate model (called *Feature Kernel Model* [35, 36, 37, 48]) is a hybrid model comprised essentially of an adjacency graph, where each node corresponds to a feature face and arcs connecting the nodes represent the relationship between them in the form of geometric constraints or topological relationships. To make it easier to extract features [48] for use in post-design engineering processes, the shape features are represented [37] by their boundary entities and the topological adjacency relations between feature pairs. The linguistic properties of the features (semantic representation) [35] are modeled by a set of algebraic expressions representing the relations between the shapes. The model is capable of handling and representing multiple views of the designs. These multiple views adapt to the modeling requirements of other engineering processes supporting the philosophy of concurrent engineering in collaborative product design.