#### ABSTRACT

Title of dissertation: Design Space Re-Engineering

for Power Minimization

in Modern Embedded Systems

Lin Yuan, Doctor of Philosophy, 2006

Dissertation directed by: Professor Gang Qu

Department of Electrical and Computer

Engineering

Power minimization is a critical challenge for modern embedded system design. Recently, due to the rapid increase of system's complexity and the power density, there is a growing need for power control techniques at various design levels. Meanwhile, due to technology scaling, leakage power has become a significant part of power dissipation in the CMOS circuits and new techniques are needed to reduce leakage power. As a result, many new power minimization techniques have been proposed such as voltage island, gate sizing, multiple supply and threshold voltage, power gating and input vector control, etc. These design options further enlarge the design space and make it prohibitively expensive to explore for the most energy efficient design solution.

Consequently, heuristic algorithms and randomized algorithms are frequently used to explore the design space, seeking sub-optimal solutions to meet the time-to-market requirements. These algorithms are based on the idea of truncating the design space and restricting the search in a subset of the original design space.

While this approach can effectively reduce the runtime of searching, it may also exclude high-quality design solutions and cause design quality degradation. When the solution to one problem is used as the base for another problem, such solution quality degradation will accumulate. In modern electronics system design, when several such algorithms are used in series to solve problems in different design levels, the final solution can be far off the optimal one.

In my Ph.D. work, I develop a re-engineering methodology to facilitate exploring the design space of power efficient embedded systems design. The direct goal is to enhance the performance of existing low power techniques. The methodology is based on the idea that design quality can be improved via iterative "re-shaping" the design space based on the "bad" structure in the obtained design solutions; the searching run-time can be reduced by the guidance from previous exploration. This approach can be described in three phases: (1) apply the existing techniques to obtain a sub-optimal solution; (2) analyze the solution and expand the design space accordingly; and (3) re-apply the technique to re-explore the enlarged design space.

We apply this methodology at different levels of embedded system design to minimize power: (i) switching power reduction in sequential logic synthesis; (ii) gate-level static leakage current reduction; (iii) dual threshold voltage CMOS circuits design; and (iv) system-level energy-efficient detection scheme for wireless sensor networks. An extensive amount of experiments have been conducted and the results have shown that this methodology can effectively enhance the power efficiency of the existing embedded system design flows with very little overhead.

## DESIGN SPACE RE-ENGINEERING FOR POWER MINIMIZATION IN MODERN EMBEDDED SYSTEMS

by

#### Lin Yuan

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2006

Advisory Committee:

Professor Gang Qu, Chair/Advisor

Professor Shuvra S. Bhattacharyya

Professor Manoj Franklin

Professor Dennis M. Healy

Professor Martin Peckerar

Professor Ankur Srivastava

© Copyright by Lin yuan 2006

### DEDICATION

To my parents and friends

#### **ACKNOWLEDGMENTS**

First and foremost I'd like to thank my advisor, Professor Gang Qu for his invaluable guidance and never-ending help in research, teaching and all other aspects. As an advisor and a friend, he has been a perfect role model for me in the past five years. From him, I learn not only how to be a prolific researcher, but also how to be a nice person, a great mentor, a supportive friend, and an affectionate father. It is great pleasure of me to work with and learn from such an extraordinary person.

I would like to thank Professor Shuvra Bhattacharyya, with whom I have been a teaching assistant and have worked on a research project which lead to a published paper. His unique vision in research and abundant experience in teaching have been a great source of guidance for me. I would like to thank Professor Manoj Franklin, Professor Dennis Healy, Professor Martin Peckerar, and Professor Ankur Srivastava for agreeing to serve on my thesis committee and for sparing their invaluable time reviewing the manuscript. I would like to thank Professor Ankur Srivastava for his always available help, advice or simply a word of encouragement.

My colleagues at the Embedded System Research Lab are the nicest and most supportive. Ming-Yung Ko, who is the lab administrator, did a wonderful job and helped me get familiar with lab environments and computer systems. Vida Kianzad, who is like an elder sister to me, always encouraged me when I was depressed. I also enjoyed many inspiring discussions with Neal Bambha, Dong-Ik Ko, Sankalita

Saha, Mainak Sen and Ankush Varma.

My PhD years would not have been so memorable without my friends. Pushkin Pari, Sadagopan Srinivasan, and Aditya Kalyanpur are both my labmates and my best buddies. They are really good friends and fun people. I owe special thanks to Honghao Ji and Ji Luo for their enormous help and being very considerate to me. Many thanks are due to all my old and new friends in every corner of this globe; they made my life full of exciting stories.

I feel extremely happy to have amazingly nice roommates, Wei Jing, Haibin Ling, and Mei Zhang. They are like my families and I don't even want to miss a single moment with them.

I would also like to acknowledge help and supports from the staff members at ECE Help Desk, Clifford Russell, Tarjia Johnson and Jeff McKinney. Their professional technical supports have made my work efficient and smooth.

At last, I owe my deepest thanks to my parents who have always stood by me and guided me through my career. I am really proud to have such great parents.

#### TABLE OF CONTENTS

| Lis | List of Tables vii  |                                                                                                                    |              |  |

|-----|---------------------|--------------------------------------------------------------------------------------------------------------------|--------------|--|

| Lis | st of I             | Figures                                                                                                            | ix           |  |

| 1   | Intro<br>1.1<br>1.2 | oduction  Low Power Design Challenge in Modern Embedded Systems  Power Minimization in Embedded System Design Flow | 1<br>1<br>6  |  |

|     | 1.3                 | Design Space Exploration and Re-Engineering                                                                        | 8<br>8<br>10 |  |

|     | 1.4                 | Thesis Organization                                                                                                | 11           |  |

| 2   |                     | eral Re-Engineering Methodology and Framework                                                                      | 12           |  |

|     | 2.1                 | A New Design Framework for Low Power                                                                               | 12           |  |

|     | 2.2                 | Re-Constructing the Design Space                                                                                   | 14           |  |

|     | 2.3                 | Application                                                                                                        | 15           |  |

|     |                     | 2.3.1 Sequential Logic Synthesis (Chapter 3)                                                                       | 15           |  |

|     |                     | 2.3.2 Dual- $V_{th}$ CMOS Circuit Design (Chapter 4)                                                               | 15           |  |

|     |                     | 2.3.3 Input Vector Control for Static Power Reduction (Chapter 5)                                                  | 16           |  |

|     |                     | 2.3.4 Energy-Efficient Detection Scheme for Wireless Sensor Net-                                                   | 17           |  |

|     | 2.4                 | works (Chapter 6)                                                                                                  | 17<br>17     |  |

|     |                     |                                                                                                                    |              |  |

| 3   | Powe                | er-Driven Sequential Logic Synthesis                                                                               | 18           |  |

|     | 3.1                 | Introduction                                                                                                       | 18           |  |

|     |                     | 3.1.1 A Motivational Example                                                                                       | 20           |  |

|     |                     | 3.1.2 FSM Re-Engineering                                                                                           | 21           |  |

|     | 3.2                 | Related Work                                                                                                       | 23           |  |

|     | 3.3                 | Preliminary                                                                                                        | 25           |  |

|     |                     | 3.3.1 An Example of Re-constructing FSMs                                                                           | 27           |  |

|     | 3.4                 | Power-Driven FSM Re-Engineering Approach                                                                           | 28           |  |

|     | 3.5                 | FSM Re-engineering Algorithm                                                                                       | 28           |  |

|     |                     | 3.5.1 A Generic Approach                                                                                           | 29           |  |

|     |                     | 3.5.2 Genetic Algorithm Based State Duplication                                                                    | 31           |  |

|     |                     | 3.5.3 Heuristic on State Selection for Duplication                                                                 | 34           |  |

|     |                     | 3.5.4 Heuristic on How to Duplicate a Selected State                                                               | 35           |  |

|     |                     | 3.5.5 Determine the Minimum Switching Activity                                                                     | 37           |  |

|     | 3.6                 | Experimental Results                                                                                               | 39           |  |

|     | 3.7                 | Summary                                                                                                            | 44           |  |

| 4 | Dua | $1-V_{th}$ CMOS Circuit Design for Leakage Reduction               | 47    |

|---|-----|--------------------------------------------------------------------|-------|

|   | 4.1 | Introduction                                                       | . 47  |

|   |     | 4.1.1 A Motivational Example                                       | . 49  |

|   |     | 4.1.2 Main Idea and Contribution                                   | . 51  |

|   |     | 4.1.3 Chapter Organization                                         | . 52  |

|   | 4.2 | Related Work                                                       |       |

|   | 4.3 | Simultaneous Dual $V_t$ Assignment and Input Vector Selection      | . 55  |

|   |     | 4.3.1 Dual $V_t$ Assignment                                        | . 55  |

|   |     | 4.3.2 Input Vector Selection                                       | . 56  |

|   |     | 4.3.3 Combining Dual $V_t$ Assignment and Input Vector Selection . | . 58  |

|   |     | 4.3.4 Algorithm Description and Analysis                           | . 60  |

|   | 4.4 | Experimental Results                                               |       |

|   | 4.5 | Summary                                                            | . 67  |

| 5 | Gat | e-Level Input Vector Control for Static Power Minimization         | 69    |

|   | 5.1 | Introduction                                                       |       |

|   | 5.2 | Related Work                                                       | . 73  |

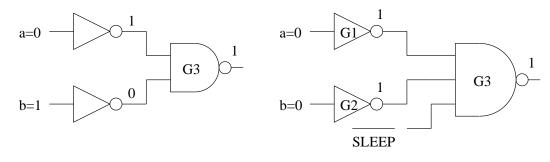

|   | 5.3 | Leakage Reduction by Gate Replacement                              |       |

|   |     | 5.3.1 Basic Gate Replacement Technique                             |       |

|   |     | 5.3.2 A Fast Gate Replacement Algorithm                            |       |

|   | 5.4 | Solving the MLV+ Problem                                           |       |

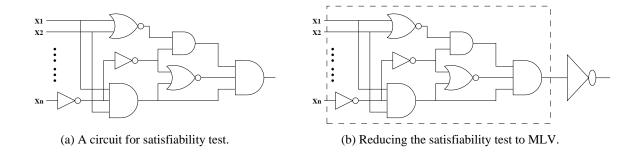

|   |     | 5.4.1 NP-Completeness of the MLV Problem                           |       |

|   |     | 5.4.2 The MLV+ Problem and Outline of the Divide-and-Conquer       |       |

|   |     | Approach                                                           |       |

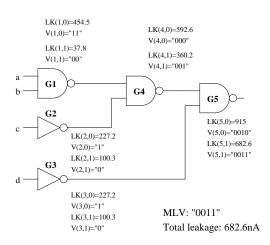

|   |     | 5.4.3 Finding the Optimal MLV for Tree Circuits                    |       |

|   |     | 5.4.4 Connecting the Tree Circuits                                 |       |

|   |     | 5.4.5 Overhead Analysis                                            |       |

|   | 5.5 | Experimental Results                                               |       |

|   | 5.6 | Summary                                                            | . 101 |

| 6 |     | rgy Efficient Detection Scheme for Wireless Sensor Network Design  | 103   |

|   | -   | Introduction                                                       | . 103 |

|   | 6.2 | Related Work                                                       | . 106 |

|   |     | 6.2.1 On Detection in Wireless Sensor Networks                     |       |

|   |     | 6.2.2 On Energy Efficiency in Sensor Network Design                |       |

|   | 6.3 | System Model                                                       |       |

|   | 6.4 | Hybrid Detection Scheme                                            |       |

|   |     | 6.4.1 Intuition                                                    |       |

|   |     | 6.4.2 Detection mechanism                                          |       |

|   |     | 6.4.3 Decision rules                                               |       |

|   |     | 6.4.4 Suboptimal algorithm                                         |       |

|   | 6.5 | Energy Consumption Model                                           |       |

|   |     | 6.5.1 Data acquisition                                             |       |

|   |     | 6.5.2 Data processing                                              |       |

|   |     | 6.5.3 Communication                                                | 121   |

|    |        | Simulation Results |     |

|----|--------|--------------------|-----|

| 7  | Cone   | lusions            | 130 |

| Α  | List   | of Publications    | 132 |

| Bi | bliogr | aphy               | 135 |

#### LIST OF TABLES

| 3.1 | Total switching activity reduction on re-constructed FSMs                                                                                                                                                                                                                                                | 42  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Area and power comparison between original FSM and reconstructed FSM                                                                                                                                                                                                                                     | 44  |

| 4.1 | Leakage current (nA) in high- $V_{th}$ (0.48V) and low- $V_{th}$ (0.33V) two-input NAND gates at different inputs from SPICE simulations                                                                                                                                                                 | 48  |

| 4.2 | Leakage current (nA) in the library gates                                                                                                                                                                                                                                                                | 63  |

| 4.3 | Propagation delay (ns) in the library gates                                                                                                                                                                                                                                                              | 63  |

| 4.4 | Comparison of individual MLV and $V_{th}$ assignment with simultaneous MLV and $V_{th}$ assignment algorithm on MCNC benchmarks in terms of runtime and leakage. The red(%) column reports the reduction over the combined serial randome MLV search and $V_{th}$ assignment                             | 64  |

| 4.5 | Number of gates in the worst leakage state (# WLS), number of WLS gates at high $V_{th}$ (# WLS*), and the total number of gates assigned high $V_{th}$ (# $V_{th}$ H) in MCNC circuits with serial dual- $V_{th}$ assignment and with simultaneous dual- $V_{th}$ assignment and input vector control.  | 65  |

| 4.6 | Comparison of individual MLV and $V_{th}$ assignment with simultaneous MLV and $V_{th}$ assignment algorithm on ISCAS benchmarks in terms of runtime and leakage. The red(%) column reports the reduction over the combined serial randome MLV search and $V_{th}$ assignment                            | 66  |

| 4.7 | Number of gates in the worst leakage state (# WLS), number of WLS gates at high $V_{th}$ (# WLS*), and the total number of gates assigned high $V_{th}$ (# $V_{th}$ H) in ISCAS circuits with serial dual- $V_{th}$ assignment and with simultaneous dual- $V_{th}$ assignment and input vector control. | 67  |

| 5.1 | Results on 26 small circuits with 22 or less primary inputs                                                                                                                                                                                                                                              | 96  |

| 5.2 | Results on 43 large circuits with primary inputs more than 22                                                                                                                                                                                                                                            | 98  |

| 5.3 | The percent of WLS gates in 43 circuits and the area increase with different input vector control algorithms                                                                                                                                                                                             | 100 |

| 5.4 | Average performance comparison with algorithm in [1]                                                                                                                                                                                                                                                     | 101 |

#### LIST OF FIGURES

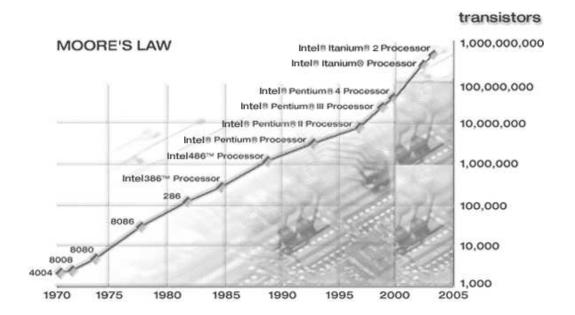

| 1.1 | Number of transistors on chip is doubled every 18 months as predicted by Gordon Moore.                                                                                                        | 5  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

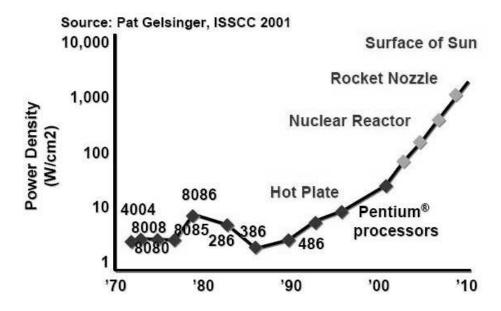

| 1.2 | Trend of increasing power density                                                                                                                                                             | 4  |

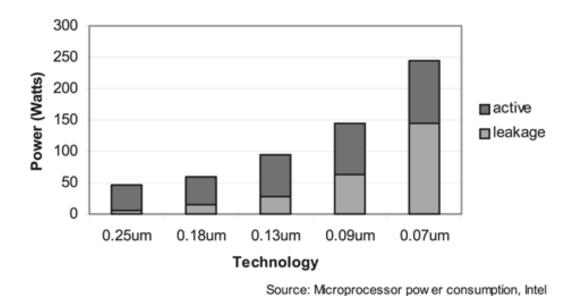

| 1.3 | Trend of increasingly significant leakage power                                                                                                                                               | Ę. |

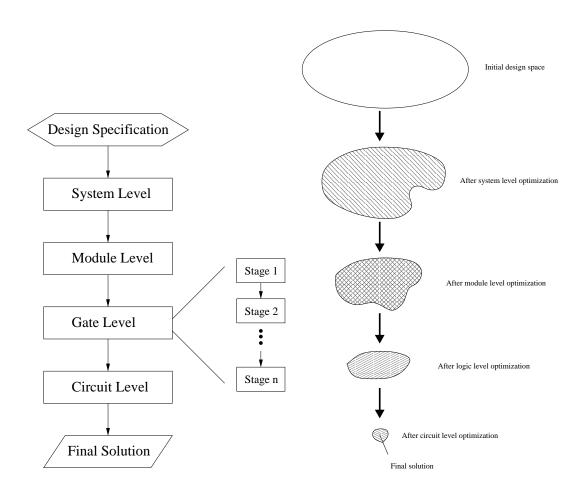

| 1.4 | Serial design space exploration strategy in the conventional design flow.                                                                                                                     | 8  |

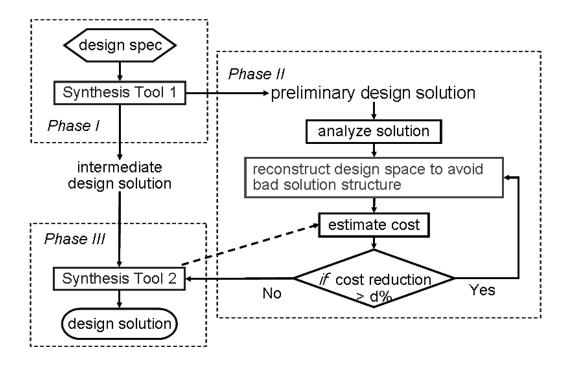

| 2.1 | Re-engineering design framework                                                                                                                                                               | 13 |

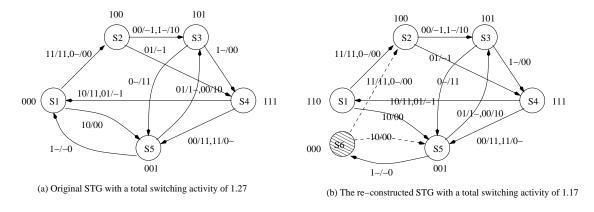

| 3.1 | A 5-state FSM and a functionally equivalent 6-state FSM                                                                                                                                       | 20 |

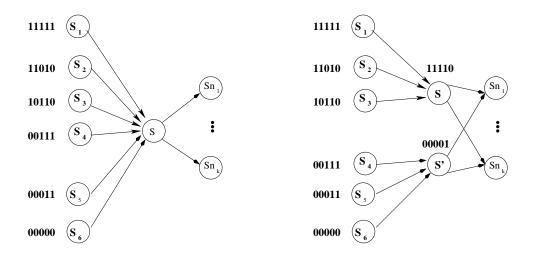

| 3.2 | Re-constructing an FSM by duplicating a state $S.$                                                                                                                                            | 28 |

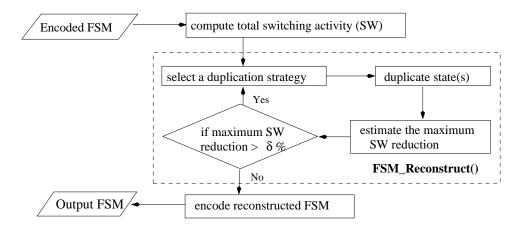

| 3.3 | FSM re-engineering for low power state encoding                                                                                                                                               | 29 |

| 3.4 | Pseudocode: State duplication via genetic algorithm                                                                                                                                           | 33 |

| 3.5 | Pseudocode: Duplicate a State                                                                                                                                                                 | 38 |

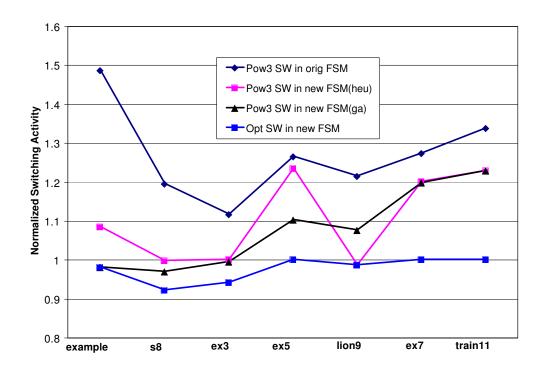

| 3.6 | Switching activity of POW3's encoding schemes on the original and re-constructed FSMs and the optimal encoding (Opt) on the new FSMs. Normalized to the optimal encoding on the original FSMs | 45 |

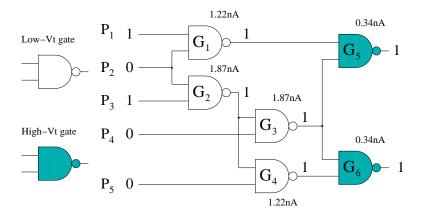

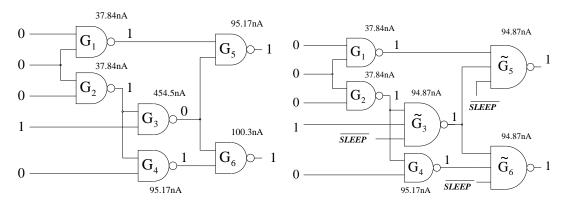

| 4.1 | Dual- $V_{th}$ assignment for circuit C17 and its impact on leakage reduction.                                                                                                                | 49 |

| 4.2 | Pseudo-code of the simultaneous dual $V_t$ assign and input vector selection algorithm                                                                                                        | 60 |

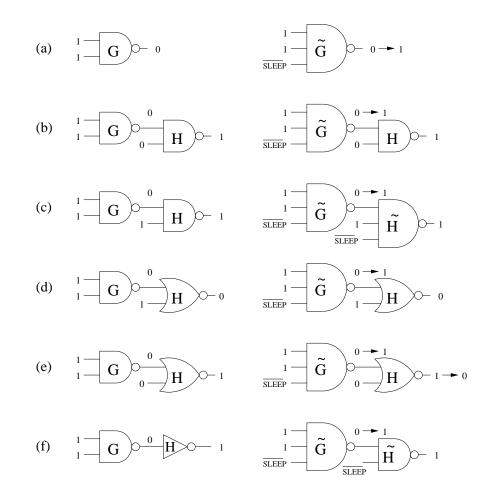

| 5.1 | Leakage current of (a)<br>INVERTER, (b)<br>NAND2 and (c)<br>NAND3. Data obtained by simulation in Cadence Spectre using 0.18<br>$\mu m$ process                                               | 70 |

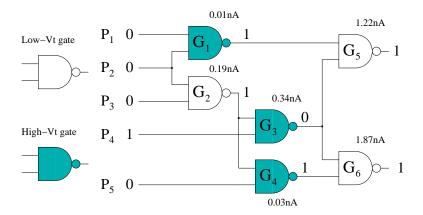

| 5.2 | A motivation example for gate replacement                                                                                                                                                     | 71 |

| 5.3 | Gate replacement and the consequence to its fanout gate                                                                                                                                       | 78 |

| 5.4 | Pseudo-code of the gate replacement algorithm                                                                                                                                                 | 81 |

| 5.5 | Illustration for the proof of the NP-completeness of the MLV problem.                                                                                                                         | 84 |

| 5.6 | Dynamic programming to find optimal MLV in a tree circuit                                                                                                                                     | 87 |

| 5.7 | MLV in a circuit before and after gate replacement 90                                                                                                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.8 | Resolving the conflict in connecting tree circuits                                                                                                                                                      |

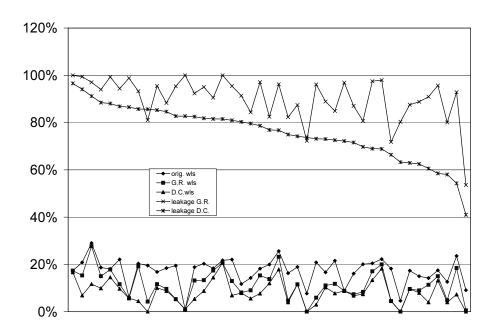

| 5.9 | Leakage and WLS percentage on 43 large circuits with 22 PIs or more. X-axis lists benchmarks sorted by leakage current in divide-and-conquer approach; Y-axis shows percentage of leakage and WLS gates |

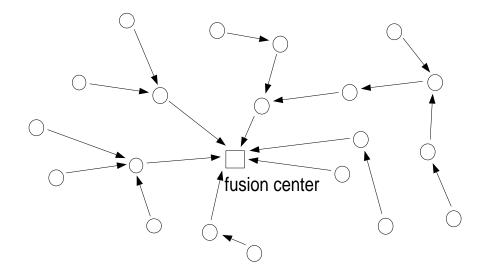

| 6.1 | Wireless Sensor Network for Detection                                                                                                                                                                   |

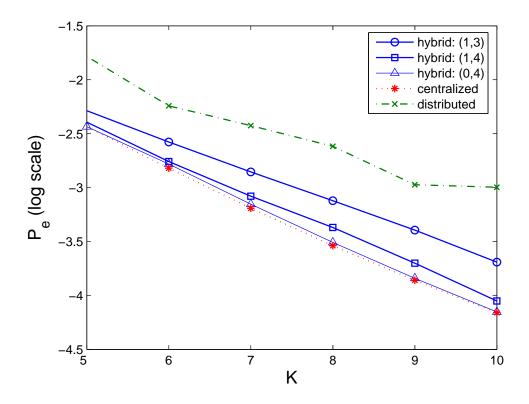

| 6.2 | Comparison of Three Schemes in Detection Accuracy                                                                                                                                                       |

| 6.3 | Dense Network: $1 \times 1$ Field                                                                                                                                                                       |

| 6.4 | Intermediate Network: $\sqrt{2} \times \sqrt{2}$ Field                                                                                                                                                  |

| 6.5 | Sparse Network: $2 \times 2$ Field                                                                                                                                                                      |

| 6.6 | Breakdown of Energy Consumption for Dense Network                                                                                                                                                       |

| 6.7 | Comparison of Energy per Node for Dense Network                                                                                                                                                         |

#### Chapter 1

#### Introduction

#### 1.1 Low Power Design Challenge in Modern Embedded Systems

With the advances of transistor integration capability and System-on-Chip (SoC) design technology, modern embedded systems can be implemented on a tiny silicon chip. For example, the wireless sensor developed at Berkeley is in the size of a nickel, yet it integrates almost a million transistors on chip [111]. This trend of technology scaling makes it possible for designers to implement a sophisticated embedded system on small and portable device and these portable embedded systems have ever become more and more popular in today's market such as cell phones, personal digital assistants (PDA), MP3 players, digital cameras, and medical sensors etc.

One of the major challenges for modern embedded system design is the power efficiency. Most portable devices are sustained by batteries; in many cases, frequently recharging the batteries are not possible or convenient. Although a substantial improvements have been made in battery technology, the increase in battery capacity can not keep pace with the rapid increase of power requirements. At the same time, the performance of embedded systems have improved dramatically and they are burning more and more power. For example, the recent embedded processors developed at Freescale are running at a clock frequency of 3 GHz [113]; the

Transmeta Crusoe processor has a maximum frequency of 1 GHz [114]. Therefore, reducing power consumption in the embedded system has been deemed as a crucial approach to extend the life-time of embedded systems.

The other reason that drives the low-power design solution for embedded systems is the continuing transistor technology scaling, which follows the famous Moore's Law [79]. Figure 1.1 shows the trend of the number of transistors integrated in microprocessors. In accordance to this trend is the power density increase on chip as shown in Figure 1.2. As more and more transistors being integrated on the chip, the power density is increasing dramatically, which will not only shorten the life-time of the system, but also cause high junction temperature that may trigger hardware failure and performance degradation.

There are two main sources of power dissipation in embedded systems: **dynamic power** and **static power**.

Dynamic power is caused by the capacitance charging and discharging in the circuits. It can be described by the equation:

$$P_{dyn} = \alpha C_L \cdot V_{dd}^2 \cdot f \tag{1.1}$$

where  $\alpha$  is the switching activity;  $C_L$  is the effective loading capacitance of the circuit;  $V_{dd}$  is the supply voltage; and f is the clock frequency.

Static power is mainly contributed by the leakage current flowing in the CMOS circuit when it is at standby mode (there are also leakage currents even when the circuit is switching):

Figure 1.1: Number of transistors on chip is doubled every 18 months as predicted by Gordon Moore.

$$P_{stat} = V_{dd} \cdot I_{leakage} \tag{1.2}$$

where the leakage current  $I_{leakage}$  consists of gate leakage and subthreshold leakage. Based on the BSIM3 MOS transistor model [112], the subthreshold leakage current of a MOSFET can be modeled as:

$$I_{sub} = Ae^{\frac{q}{n'kT}(V_G - V_S - V_{TH_0} - \gamma'V_s + \eta V_{DS})} (1 - e^{\frac{-qV_{DS}}{kT}})$$

(1.3)

where  $A = \mu_0 C_{ox} \frac{W_{eff}}{L_{eff}} (\frac{kT}{q})^2 e^{1.8}$ ;  $C_{ox}$  is the gate oxide capacitance per unit area;  $\mu_0$  is the zero bias mobility; n' is the subthreshold swing coefficient of the transistor;  $V_{TH_0}$  is the zero bias threshold voltage. The gate leakage is only a small portion of the

Figure 1.2: Trend of increasing power density.

total leakage and is projected to be controlled by high-K material [45]. Therefore, leakage reduction techniques are mainly focused on minimizing the subthreshold leakage.

Traditionally, dynamic power consumption is the dominant part and many low power techniques have been proposed to reduce it. One of the most popular approaches for dynamic power reduction is voltage scaling. This is based on the quadratic dependence of dynamic power on supply voltage. However, the circuit delay is inversely proportional to supply voltage as shown in Equation (1.4):

$$delay \propto \frac{V_{dd}}{(V_{dd} - V_{th})^{\alpha}} \tag{1.4}$$

where  $\alpha$  is between 1.0 and 1.2. As  $V_{dd}$  is scaled down, the performance of the

system will also decrease. In order to meet the performance requirements, threshold voltage  $V_t$  also has to be scaled down. However, the reduction of threshold causes exponential increase in subthreshold leakage as shown in equation (1.3.

Due to this reason, leakage power has become a significant part of power consumption in today's embedded system. Figure 1.1 shows that leakage is going to be the dominant source of power dissipation in 65nm technology node and beyond. Therefore, a holistic approach is needed to minimizing the total power in the circuit. This enlarges the design space of power minimization in embedded system and makes this problem even more complicated.

Figure 1.3: Trend of increasingly significant leakage power.

#### 1.2 Power Minimization in Embedded System Design Flow

In order to effectively minimize power, power reduction techniques are carried out at each level of the system design flow:

System level: Dynamic voltage scaling (DVS) is one of the most effective techniques at system level. It employs an operating system (OS)-supported voltage scheduler. Based on the workload and tasks' deadlines, the scheduler scales the voltage to a pre-determined level at run-time such that each task can complete before its deadline and the overall dynamic power is minimized [7, 36, 37, 38, 49, 73, 74, 83, 104]. Recently, due to the increasing significance of leakage power, leakage-aware DVS algorithms have been proposed to minimize the sum of dynamic and leakage power [41, 56, 108]. In addition to DVS, multiple supply voltages can also applied statically to each functional blocks of the system [17, 91]. IBM has proposed a voltage-island solution for System-on-Chip (SoC) design. Each block is powered by a different voltage source depending on its performance requirement [54].

Module level: At module level, the goal of power minimization is to reduce power consumption in functional-units and memory modules [23]. Power-aware synthesis algorithms have been proposed in the following procedures: resource allocation (deciding the numbers and types of functional units and registers available for synthesis) and assignment (binding an operation to a specific instance of a functional unit) [109], functional-unit selection (selection of a functional-unit type to implement an operation) [27], and scheduling (determining the cycle-by-cycle behavior of a circuit by assigning operations to control steps) [19]. The basic idea of these algorithms is

to (i) reduce the switching activities of functional-units when they are not on critical paths. (ii) turn off modules whenever they are not producing useful outputs.

Gate level: Gate level power minimization are conducted through logic synthesis procedures, with the optimization objective redefined to be power consumption. For dynamic power minimization, the synthesis algorithms are targeted at reducing the switching activities at the fanins and fanouts of logic gates. These techniques include finite state machine (FSM) minimization and state encoding [8, 47, 102, 105], boolean multi- and two-level logic optimization [14, 40], technology mapping [89], precomputation logic [2], and retiming etc. For leakage power minimization, the algorithms include power gating, FSM decomposition [24], and input vector control [18, 106] etc.

Circuit level: At circuit-level, power reduction can be further achieved by changing the characteristics of transistors and structure of the circuits. For example, one of the approaches to reduce dynamic power is transistor sizing. By choosing the optimal size for a subset of transistor, the overall power consumption in the circuit can be minimized [10]. In addition, more effective leakage power minimization techniques can be applied at circuit level. For example, multiple- $V_{th}$  CMOS technique inserts sleep transistors with large threshold voltage at either the  $V_{dd}$  or GND to reduce the leakage current at standby mode [4, 12]; dual- $V_{th}$  assigns transistors on critical and non-critical paths different threshold voltage [96, 94]; reverse body bias connect the gate with substrate of a MOSFET to reduce gate leakage [97].

As one can see, there are myriad options for power minimization even at one

level of the design. Achieving a global optimal solution across various levels in the design flow is not possible. In fact, solution from one design level is often used as the entry point for the design at its next level. Next subsection elucidates the design space exploration strategy in this design flow and introduce our methodology.

#### 1.3 Design Space Exploration and Re-Engineering

#### 1.3.1 Design Space Exploration

- (a) Embedded system design flow.

- (b) Design space exploration.

Figure 1.4: Serial design space exploration strategy in the conventional design flow.

Due to the vast design space for power minimization in embedded system, the exploration methodology usually follows a serial strategy. That is, even within one design level, the optimization is performed in consecutive stages; the solution from one stage is used as the base for the next stage. This strategy is shown in Figure 1.4(a). For example, in power-driven sequential synthesis, FSM minimization is performed first; then the minimized FSM is encoded using power-drive state encoding algorithm.

If we view this process from a design space point of view, we can see that the design space shrinks as the optimization proceeds and eventually, the solution will be chosen from a restricted solution pools. This is shown in Figure 1.4(b).

In each design level, the design space is large and finding the optimal solution is usually a NP-hard problem [26]. Therefore, many heuristic and randomized algorithms are used to explore the design space. For example, a greedy algorithm is often used to solve the binary covering problem in logic synthesis [30]; in high-level synthesis, genetic algorithm is frequently used for resource allocation and binding [34]. Comparing to a complete search in the original design space, applying these algorithms in a serial fashion is much more efficient in truncating the design space and finding the design solutions fast.

However, this approach often removes good design solutions without enough caution. It becomes much worse when such truncation of good solutions happens in the early design stage because the design space from the earlier stage will be used as the initial space for later stages. In this case, the solutions obtained after the last stage may be far off the optimal ones in the global design space. For example,

in sequential logic optimization level, a conventional optimization procedure is to first minimize the number of states in FSMs followed by state encoding algorithms. However, as it has been pointed out in [33], this serial optimization strategy may result in inferior solutions. Based on our experimental results, the solution can be 17% worse than the optimal ones in the non-minimized FSMs.

#### 1.3.2 Design Space Re-Engineering

In my Ph.D. work, I propose a re-engineering approach to explore the design space efficiently and effectively at the same time. Our goal is to enhance the performance of the existing low power techniques. Our approach can be described in three phases: (1) apply the existing technique to obtain a sub-optimal solution; (2) analyze this solution and expand the design space accordingly; and (3) re-apply the technique to re-explore the enlarged design space.

The novelty of our approach is in the second phase when we re-construct the design space. Particularly, we start with the analysis of the solution obtained by the existing technique. We first evaluate the solution based on a cost function that models the design objective. Then we study which part and what structure of the current solution contribute most to the cost. Next, we re-construct the design space such that the new solutions will not have such part or structure.

As the design space expansion is directed intelligently based on the analysis of the previous solution, this approach not only provides the potential of finding higher quality solutions, but also makes the design space re-exploration efficient.

Therefore, it opens doors for further optimization with relatively small run-time overhead.

#### 1.4 Thesis Organization

The remainder of this thesis is organized in the following way. In Chapter 2, I demonstrate a general framework on the re-engineering methodology. Then I apply this methodology to four low power design problems: the power-driven sequential synthesis (Chapter 3); dual- $V_{th}$  CMOS circuit design for leakage reduction (Chapter 4); gate-level input vector control for static power reduction (Chapter 5); and energy efficient wireless sensor network design (Chapter 6). I conclude my thesis in Chapter 7.

#### Chapter 2

#### General Re-Engineering Methodology and Framework

#### 2.1 A New Design Framework for Low Power

In this chapter, I will elaborate the *re-engineering* methodology and illustrate the design framework using this methodology. Our focus is on power minimization; however, this methodology can be also applied to solve other optimization problems.

Given a problem  $\mathcal{P}$ , the design space  $\mathcal{S}$  consists of all the solutions to  $\mathcal{P}$  that satisfy certain design constraints. A cost C is defined for each solution with respect to an objective (e.g. power consumption). The optimization process aims to find the solutions which have the least cost based on the optimization objective. Current synthesis algorithms or tools achieve this goal via step-by-step design space truncating; each step will reduce the design space  $\mathcal{S}$  and the output is used as the initial design space for the next step. The re-engineering methodology is based on the idea that some global optimal solutions may be lost during the serial design space constraining process. The word re-engineering means that it iteratively enlarge the design space and re-explore it seeking for better design solutions in the optimization. In the power minimization scenario, the solutions that consumes the least power are desired.

The *re-engineering* design framework is illustrated in Figure 2.1. This threephase approach can be used to improve the performance of power minimization

Figure 2.1: Re-engineering design framework.

design tools. First, an existing design synthesis tool is applied on the problem to obtain an "optimal" solution (i.e. the best based on the tool we use). The second phase is re-constructing the design space based on this synthesis solution. In the third and last phase, the re-constructed design space is re-explored for a new power efficient design solution.

#### 2.2 Re-Constructing the Design Space

The key part of the re-engineering methodology is how to re-construct the design space. Initially, we start with solution analysis where we evaluate the solution based on a given cost function. Such cost function is determined based on the abstraction level of the optimization objective. First of all, such cost function must be able to accurately reflect the optimization objective; second, it must be easy to calculate. For example, total switching activity is often used as a cost function for dynamic power minimization.

Then we identify the particular structure of the current solution that causes a large cost. In fact, the solution structure is an output of the previous exploration algorithm "truncating" the design space. During the exploration process, a certain solution structure will be used as criteria for design space truncating. For example, state minimization, a step in the sequential FSM synthesis, will always keep the set of FSMs with the minimal number of states and exclude the others.

Hence, in order to remove the "bad" solution structure that results in large cost, we need to reverse the previous synthesis steps and revise the current design space. That is, we will enlarge the current design space in a way to include certain solutions that may help to reduce the cost. Note that however, when enlarging the design space, we do not expand it arbitrarily; instead, we still rely on the outputs from the previous exploration and revisit those parts where better solutions may lie.

After the design space is re-constructed, a re-exploration is conducted on the new space in Phase III. This exploration can use the same algorithm as in the first

phase; it can also be a new exploration based on the re-constructing process in Phase II.

#### 2.3 Application

In the rest of this thesis, I will apply this framework to several power minimization problems at different levels of the design. The basic idea of solving these problems with re-engineering methodology is described below:

#### 2.3.1 Sequential Logic Synthesis (Chapter 3)

This problem is at the gate level of the design. The serial steps are state minimization followed by state encoding. The state minimization step removes equivalent and/or compatible states in the original FSMs and the design space for state encoding is restricted to minimized FSMs. Based on the observation made in [33] we take one step back by introducing redundant states in the minimized FSM. We found that adding the redundant states may help the state encoding tool to find a better design solution with smaller cost (total switching activity in this case).

#### 2.3.2 Dual- $V_{th}$ CMOS Circuit Design (Chapter 4)

The problem in dual- $V_{th}$  CMOS circuit design is to assign a high and low  $V_{th}$  values to transistors in the circuit in order to minimize the leakage. Conventionally, such process is performed after an input vector is determined for the primary inputs of the circuit. However, the input vectors also affect the leakage currents in the

circuit and even the best  $V_{th}$  assignment solution based on a given input vector may not be as good as the one based on another input vector. In this problem, we propose an iterative algorithm to find the best  $V_{th}$  assignment and input vector simultaneously.

#### 2.3.3 Input Vector Control for Static Power Reduction (Chapter 5)

Technology mapping in logic synthesis are often targeted at reducing dynamic power and/or improving performance. Leakage has not been considered. However, the leakage currents in different CMOS gates are quite different. Meanwhile, at standby mode, leakage power can be minimized by choosing a particular input vector to the primary inputs. Such input vector is often chosen based on an already mapped circuit. Following the re-engineering framework, we first obtain a sub-optimal MLV solution by a heuristic algorithm. Based on this input vector, we check the inputs to each logic gate in the circuit and find the ones that result in the largest leakage current. Then we replace these worst-leakage-state gates by another gate in the library, such that the output function of the circuit remains the same, while less leakage currents are generated. With the gate replacement, the input vector space is re-explored to find the new MLV in the modified circuits.

# 2.3.4 Energy-Efficient Detection Scheme for Wireless Sensor Networks (Chapter 6)

Several detection schemes are available for wireless sensor network design at system level. However, once a detection scheme is fixed, the power reduction at this level is limited. We propose a hybrid detection scheme that can trade off energy with detection accuracy. Based on the different accuracy requirements of different applications, an more flexible and more energy efficient system can be built for the sensor networks.

#### 2.4 Summary

In this chapter, I demonstrate the general design flow with re-engineering methodology. Four low power design problems are described as examples to apply this methodology. More detailed description of each problem and our solutions are provided in the rest chapters of this thesis.

#### Chapter 3

#### Power-Driven Sequential Logic Synthesis

#### 3.1 Introduction

Finite state machine (FSM) is the most commonly used model for microcontroller design in embedded systems. Logic synthesis, which has the goal of converting the symbolic description of the FSM to a hardware implementation, traditionally starts with FSM state minimization and state encoding in order to optimize design objectives such as area, delay, and testability. For example, De Micheli et al. [63] formulate the minimum area state encoding problem as generating a minimum (multi-valued) symbolic cover of the FSM and propose a heuristic row encoding technique in [64]. Villa et al. [93] use the notion of face-posets to tackle this problem and propose a state encoding technique for two-level implementation. State encoding techniques for multi-level logic minimization have been studied in [20] and [60] where the goal is to reduce the number of literals in the Boolean output and next-state functions.

With the increasing popularity of portable computing and personal communication applications, power dissipation has become critical in the design of sequential circuits. Hence, low power state encoding techniques were proposed in accordance with the design focus shifting to low power.

In light of the well-known fact that digital CMOS circuit's power dissipation

is proportional to the switching activity, state encoding is then re-formulated to minimize the number of state bit switches per transition for low power FSM synthesis. This problem is NP-hard and many heuristic algorithms have been proposed mainly based on the idea of assigning codes with small Hamming distance to pairs of states that have a high transition probability. Such techniques include state encoding with minimal code length [8, 78, 90], non-minimal code length [59, 68] and variable code length [88]; state re-encoding approaches [28, 92] and techniques that try to minimize power and area simultaneously [48, 69].

However, these work all start with the minimized FSM and seek for the best encoding for the existing states to reduce switching activity. On the other hand, there is a much longer history on the study of conducting state minimization and assignment at one step (see, for example, [6, 31, 55]), but reducing switching activity or power has never been the goal for any of these approaches.

As we will see in the following motivational example, the best solution that minimizes the switching activity does not necessarily come from the minimized FSM. A similar observation, that state encoding with the minimal code length may not be optimal in terms of switching activity or power, has also been reported earlier [59, 68, 88]. This motivates the proposed concept of **FSM re-engineering**, where we re-construct the FSM to improve the solution's quality. More specifically, we first apply a FSM synthesis technique to obtain a synthesis solution; we then identify the structure in the FSM that might prevent us from getting better solutions and re-construct the FSM accordingly; the re-engineered FSM will be re-synthesized to generate new (and often better) solution.

#### 3.1.1 A Motivational Example

We take the example from a paper on power-driven FSM state encoding [47] to show the potential of the proposed FSM re-engineering approach.

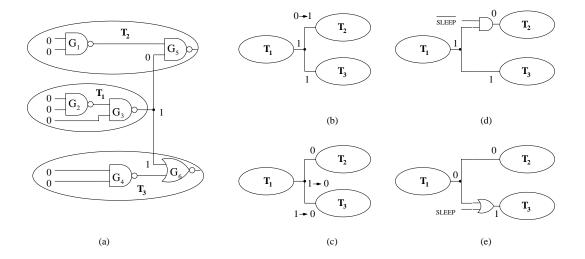

Figure 3.1: A 5-state FSM and a functionally equivalent 6-state FSM.

The state transition graph (STG) in Figure 3.1(a) represents a 2-input 2-output FSM with five states  $\{S1,S2,S3,S4,S5\}$ . Each edge represents a transition with the input and output pair shown along the edge. The FSM has already been minimized.

We re-construct this FSM by introducing state S6 as shown in Figure 3.1(b). One can easily verify that these two STGs are functionally equivalent. In fact, state S6 is an equivalent state of S1. We then exhaustively check all the possible state encoding schemes for both FSMs and report the one that minimizes total switching activity in Figure 3.1 as shown next to each state.

When we calculate the switching activity, an indicator of power efficiency of the encoding scheme, we observe that it drops from 1.27 to 1.17 (or a 7.9% reduction) after we add state S6. Note that the encoding in the original 5-state FSM is optimal

obtained from exhaustive search. This implies that we lose the most energy-efficient encoding for this FSM (and its functionally equivalent FSMs) once it is minimized!

FSM re-engineering not only gives the theoretical opportunity to build FSM with better energy efficiency, it can also be applied to existing low-power encoding algorithms. For example, when we use POW3 [8] instead of the exhaustive search to encode the original 5-state FSM, it gives a coding with switching activity 18.9% higher than the optimal. However, when we use POW3 to encode the equivalent 6-state FSM, it successfully finds a coding that is only 5.4% away from the optimal.

#### 3.1.2 FSM Re-Engineering

FSM re-engineering refers to the procedure of re-constructing an FSM that is functionally equivalent to a given FSM. The goal of FSM re-engineering is to enable synthesis and optimization tools to find better solution for the given FSM by synthesizing and optimizing the re-constructed FSMs.

In the context of low power state encoding, the proposed FSM re-engineering approach takes an encoded FSM as input and outputs a functionally equivalent FSM with reduced switching activity. The novelty of this approach, which separates it from other low power state encoding and re-encoding techniques, is that it investigates the solution space over the entire set of equivalent FSMs rather than restricting to the minimized FSM.

FSM synthesis normally starts with state minimization, which in general results in simplier function implementation, less hardware, and shorter delay. How-

ever, this may not be necessary for power efficiency because power is proportional to the switching activity, not the number of states. Leaving redundancy such as equivalent states in the FSM can be helpful in reducing switching activity. For example, state S1 in Figure 3.1(a) originally has four edges and contributes a lot to the total switching activity because states S1 and S4 have the largest Hamming distance. Duplicating state S1 solves this problem as we have seen in Figure 3.1(b).

Finally, we mention the following concerns one may have before we elaborate our FSM re-engineering approach.

- Area and delay overhead: Implementing non-minimized FSM may require increased hardware which may also cause area or delay overhead. However, this is not always true. For example, a 36-state FSM and a 42-state FSM need the same number of latches (flip flops, or state registers). Furthermore, we mention that synthesis on minimized FSM does not guarantee the optimality of area and delay either. One example is the one-bit hot encoding we will mention in the next section.

- Search cost: Although quality of the solution can be improved theoretically as we search a larger solution space, we have to pay a higher search cost. Note that the FSM re-construction is done after the first round of synthesis and driven by the optimization objective. Therefore, our search is actually guided in a subset of FSMs that could yield good solutions with better chance.

In the rest of this chapter, we apply the proposed FSM re-engineering framework to low power state encoding problem. However, one can apply it for optimiza-

tion of other design objectives such as area and testability.

Section 2 surveys the most relevant work on FSM low power state encoding and shows their difference from the proposed FSM re-engineering framework. The notation and problem formulation are given in Section 3. The power-driven FSM re-engineering approaches, a genetic algorithm and a fast heuristic, are presented in Section 4. Experimental results are reported in Section 5 and Section 6 concludes.

#### 3.2 Related Work

Dynamic power dissipation in CMOS circuits is composed of power consumed in sequential logic and combinational logic. Power dissipated in the combinational logic mainly depends on the complexity of the Boolean logic functions and their gate level implementation. Power dissipation in sequential logic is due to capacitance charging and discharging in state registers caused by the state bits switching, which is often described as

$$P = \frac{1}{2} V_{dd}^2 f \sum_{i \in sb} C(i) E(i)$$

(3.1)

where  $V_{dd}$  is supply voltage, f is clock frequency, C(i) is the capacitance of the register storing the ith state bit, and E(i) is the expected switching activity of the ith register. C(i) is technology dependent and remains, in general, constant for all the state bits.

There have been a number of power-driven state encoding algorithms to reduce the switching activity E(i) and hereby power. Roy and Prasad propose a simulated annealing based algorithm to improve any given state encoding scheme

[78]. Washabaugh et al. suggest to first obtain state transition probability, then build a weighted state transition graph, and finally apply branch and bound for state encoding [95]. Olson and Kang present a genetic algorithm, where in addition to the state transition probability, they also consider area while encoding in order to achieve different area-power trade-offs [69]. Benini and De Micheli present POW3, a greedy algorithm that assigns code bit by bit. At each step, the codes are selected to minimize the number of states with different partial codes [8]. Iman and Pedram developed a power synthesis methodology and created a complete and unified framework for design and analysis of low power digital circuits [40].

Unlike these power-driven state encoding algorithms, low power state reencoding techniques start from an encoded FSM and seek for a better coding scheme

to reduce switching activity. Hachtel et al. recursively use weighted matching

and mincut bi-partitioning methods to re-assign codes [28]. Veeramachaneni et al.

propose to perform code exchange locally to improve the coding scheme's power

efficiency [92]. Our FSM re-engineering approach is conceptually different from reencoding in that we look to change the topology of the FSM, not only re-assign

codes to the existing states.

The above work takes two common assumptions, 1) they look for codes with the minimal length, that is, the number of bits to represent a state will be  $\lceil \log n \rceil$  for any n-state FSM; 2) their encoding (or re-encoding) algorithms are applied after state minimization is done. There are a couple of recent work on non-minimal length encoding algorithms showing that power may be improved with code length longer than this bound [59, 68]. These methods require extra state register(s) in the

FSM implementation which will add to the hardware cost and cause area increase. However, none of the papers have reported the area overhead. Our approach is essentially different from theirs in that we do not introduce extra state bits (when the number of states is not  $2^k$ ). Therefore, the area overhead in our approach expects to be much less. Besides, as we have mentioned earlier, our technique is a stand-alone FSM encoding enhancement. FSM re-engineering can be applied to non-minimal length encoding algorithms to find better solutions as well.

Finally, we mention the one-bit hot encoding where each state in an n-state FSM receives an n-bit code with exactly one bit to be 1. This encoding scheme can greatly simplify the logic implementation of the FSM and could also reduce the switching activity because now every pair of states will have a Hamming distance equal to two. However, it requires a code of length the same as the number of states and this makes it impractical for FSMs of large size.

### 3.3 Preliminary

We consider the standard state transition graph (STG) representation of an encoded FSM G = (V, E), where a node  $v_i \in V$  represents a state  $s_i$  with code  $C_i$  in the FSM M, and a directed edge  $(v_i, v_j) \in E$  represents a transition from state  $s_i$  to state  $s_j$  with transition probability  $P_{ij}$  (please refer to section 4.0 for calculation of  $P_{ij}$ ). We simplify this directed weighted graph G to an undirected weighted graph  $\tilde{G} = (V, \tilde{E}, \{C_i\}, \{p_{ij}\})$ :

• V, the set of states, which is the same as in G;

- $\tilde{E}$ , the set of edges. An edge  $(v_i, v_j) \in \tilde{E}$  if and only if  $(v_i, v_j) \in E$ , or  $(v_j, v_i) \in E$ , or both;

- $C_i$ , the weight of node  $v_i \in V$ , which is the code of state  $s_i$ ;

- $p_{ij}$ , the weight of edge  $(v_i, v_j) \in \tilde{E}$ ,  $p_{ij} = P_{ij} + P_{ji}$ .

Denote  $H(v_i, v_j)$  as the Hamming distance between the codes, two bitstreams  $C_i$  and  $C_j$ , of states  $s_i$  and  $s_j$  under the given encoding scheme. The total switching activity of the encoded FSM can be calculated as

$$\sum_{(v_i, v_j) \in \tilde{E}} p_{ij} H(v_i, v_j) \tag{3.2}$$

Recall that two FSMs, M and M', are equivalent if and only if they always produce the same sequence of outputs on the same sequence of inputs, regardless of the topological structure of their STGs. We formally formulate the FSM reengineering problem as:

Given an encoded FSM M and its corresponding graph  $\tilde{G} = (V, \tilde{E}, \{C_i\}, \{p_{ij}\})$ , construct an equivalent FSM M' and encode it such that in the corresponding graph  $\tilde{G}' = (V', \tilde{E}', \{C_i'\}, \{p'_{ij}\})$ , we maximize the total switching activity reduction:

$$\sum_{(v_i, v_j) \in \tilde{E}} p_{ij} H(v_i, v_j) - \sum_{(u_i, u_j) \in \tilde{E}'} p'_{ij} H(u_i, u_j)$$

(3.3)

The FSM re-engineering problem targets the re-construction and encoding of a functionally equivalent FSM for low power FSM implementation. Clearly, it is NP-hard because it requires the best state encoding for the re-constructed FSM M', which is an NP-hard problem. Furthermore, when we restrict M' to be the same

as M, the problem becomes "determining a new encoding scheme to minimize the total switching activity", which becomes the existing FSM re-encoding problem.

The novel contribution of the FSM re-engineering problem is that it re-constructs the original (minimized and encoded) FSM to allow us explore a larger design space for power-efficient FSM encoding. In this chapter, we focus on the FSM re-construction and defer the state encoding problem to existing algorithms. We give an example on how to re-engineer an FSM and explain why it can reduce the switching activity.

### 3.3.1 An Example of Re-constructing FSMs

We have already seen from Figures 3.1 how to add a new state to the FSM without altering its functionality. Figure 3.2 illustrates a systematic way to do so. We see that a new state, S', is added as a duplicate of state S as follows: S' goes to the same next state under the same transition condition as state S; the transitions from other states to state S in the original STG will be split such that some of them still go to state S while the rest go to the new state S'.

To see the advantage of this non-minimized FSM, we consider a scenario where state S has a large Hamming distance to one of its previous states  $Sp_j$  and the transition from  $Sp_j$  to S contributes a lot to the total cost. In the re-constructed FSM, we can redirect the next state of this transition to S' and assign S' a code with a small Hamming distance to  $Sp_j$ .

For example, in Figure 3.2, no matter which code we assign to state S, it will

Figure 3.2: Re-constructing an FSM by duplicating a state S.

have a Hamming distance three or larger to at least one of its previous states. (To see this, notice that both codes 11111 and 00000 are assigned to its previous states). However, in the re-constructed FSM, we can assign code 11110 and 00001 to state S and its duplicate S', respectively. This ensures that S will have Hamming distance one from all of its previous states, and S' will have Hamming distance two from  $S_4$  and distance one from all the other previous states.

# 3.4 Power-Driven FSM Re-Engineering Approach

# 3.5 FSM Re-engineering Algorithm

In this section, we elaborate the FSM re-engineering approach by showing how the state duplication technique can improve state encoding algorithms. We first propose two heuristic algorithms, based on Hamming distance, on how to select a state for duplication and how to duplicate the selected state. We then present a genetic algorithm for state duplication to target power minimization. Finally, we describe an integer linear programming (ILP) method that can find the most powerefficient state encoding to evaluate our proposed FSM re-engineering approach.

# 3.5.1 A Generic Approach

Figure 3.3 outlines the proposed low power state encoding approach by FSM re-engineering. We first compute the original FSM's total switching activity for a reference. Then we re-construct a functionally equivalent FSM and encode it for reduced switching activity. We will use the state duplication technique as an example to illustrate the three key steps for this approach:

- 1. select the best candidate state for duplication;

- 2. decide how to duplicate the selected state;

- 3. estimate the (maximum) switching activity reduction after the state duplication.

Figure 3.3: FSM re-engineering for low power state encoding.

The strength of FSM re-engineering, as we have discussed earlier, is to improve the performance of FSM synthesis and optimization tools/algorithms. This can be seen from Figure 3.3 as we use the same algorithm, which gives us the input encoded FSM, to encode the re-constructed FSM and produce the encoded FSM in the two lower boxes. In our simulation, POW3 developed by Benini and De Micheli [8] is used as the state encoding scheme.

In this section, we first describe the method to compute switching activity. Next, we present a generic algorithm and a fast heuristic to select states for duplication. We then explain a heuristic on how to duplicate a given state. Finally, we give an integer linear programming formulation of the problem from which the minimum switching activity can be obtained to demonstrate the potential of the proposed FSM re-engineering approach.

# 4.0 Compute FSM's Switching Activity

As we have mentioned earlier, the proposed FSM re-engineering method seeks for a functionally equivalent FSM that provides opportunity to a low power state encoding scheme so that it can find coding with reduced switching activity.

According to Equation (2), the state transition probability of each edge and the Hamming distance between the two states of each edge must be determined before the calculation of total switching activity. The former measures how frequently each transition occurs and the latter gives the amount that each transition contributes to the total switching activity. The Hamming distance between the two states of

each transition can be conveniently determined after state encoding is performed.

To compute the transition probability, it is necessary to have the input distribution at each state, which can be obtained by simulating the FSM at a higher level of abstraction [95]. This gives us  $p_{j|i}$ , the conditional probability that the next state is  $s_j$  if the current state is  $s_i$ . Then we build a Markov chain based on these conditional probabilities to model the FSM. The Markov chain is a stochastic process whose dynamic behavior depends only on the present state and not on how the present state is reached [29]. We now can obtain the steady probability  $P_i$  of each state  $s_i$  corresponding to the stationary distribution of the Markov chain. The state transition probability  $P_{ij}$  for the transition  $s_i \rightarrow s_j$  is given by

$$P_{ij} = p_{j|i} P_i \tag{3.4}$$

### 3.5.2 Genetic Algorithm Based State Duplication

As we have seen in Figure 3.2, we make it possible to assign the same state more than one codes, one for that state and the rest for its duplicate(s), by duplicating that state. However, as it has also been implied in Section 3, choosing an optimal state duplication strategy is also NP-hard. The reason is that it is necessary to encode the duplicated states optimally first to determine whether a state duplication strategy is optimal. This necessary condition itself is already known as NP-hard.

Figure 3.4 depicts the proposed genetic algorithm that searches for a good state duplication strategy. First, since duplicating only a state with only one previous state does not help in reducing the Hamming distance between this state and its

previous state. We eliminate all the states with only one previous state from the queue of states to be duplicated (lines 1-3). For the 5-state FSM in Figure 3.1(a), the candidate queue for state duplication is  $\{S1, S3, S4, S5\}$ .

A state duplication scheme is represented by a boolean vector of the same length as the above candidate queue. A bit '1' at the  $i^{th}$  position of the vector indicates that the  $i^{th}$  candidate state is duplicated and a bit of '0' means that the scheme chooses not to duplicate this state. For example, the 6-state FSM in Figure 3.1(b), where state S1 is duplicated, corresponds to vector 1000. Each vector is referred as a *chromosome*.

According to each *chromosome*, we duplicate the states (lines 7-9) and calculate its fitness (line 10), which is defined as the total switching activity according to that *chromosome*. The smaller the total switching activity, the better the *chromosome*. We start with an initial population of N randomly generated chromosomes (line 5). Children are created by the *roulette wheel* method in which the probability that a *chromosome* is selected as one of the two parents is proportional to its fitness (line 13). With certain ratio, *crossover* is performed among parents to produce children by exchanging substrings in their *chromosomes*. A simple *mutation* operation flips a bit in the *chromosome* with a given probability known as *bit mutation rate* (line 14). When the population pool is full, i.e., the number of new *chromosomes* reaches N, the algorithm stops to evaluate fitness of each individual for the creation of next generation. This process is repeated for  $MAX\_GEN$  times and the best *chromosome* gives the optimal duplication strategy.

We will discuss how to calculate or estimate the fitness of each chromosome,

### Genetic Algorithm

```

/* Traverse STG and duplicate states. */

for each state in STG

1.

2.

if it has more than one incoming edge

3.

put it in candidate queue;

chromosome_length = the size of candidate queue;

initialize N random vectors;

6.

while generation < MAX_GEN

7.

for each chromosome v_k

if v_k[i] == 1

8.

duplicate the i^{th} candidate state;

9.

10.

v_k.fitness = total switching activity;

11.

do

12.

sort chromosome by non-decreasing fitness;

13.

roulette wheel selection to select parents;

14.

crossover & mutate to create children;

until number of new chromosomes = N

15.

```

Figure 3.4: Pseudocode: State duplication via genetic algorithm

that is, the total switching activity for a new FSM with certain states duplicated.

To calculate switching activity in each step after state duplication, one way is to encode the re-constructed FSM and compute the total switching activity using Equation (2) as stated above in section 4.0. This gives us the actual gain in switching activity reduction by duplicating a set of states. When it is expensive to apply the state encoding algorithm on the entire FSM, we use the following alternative to locally assign the new state the "best" code (might not be feasible) and calculate the lower bound for switching activity.

**Lemma 1.** Let  $\{x_i : (x_{i1}x_{i2}\cdots x_{in})\}$  be the set of states that have transition to/from state s and their codes. Let  $p_{x_is}$  be the transition probability between states  $x_i$  and s. The total switching activity is minimized at state s when it has code  $c_1c_2\cdots c_n$ ,

where

$$c_j = \begin{cases} 1 & \text{if } \sum_{x_i} p_{x_i s} (1 - 2x_{ij}) < 0 \\ 0 & \text{otherwise} \end{cases}$$

[Proof]. From the definition, the switching activity at the j-th bit will be  $\sum_{x_i} p_{x_i s} x_{ij}$  if  $c_j = 0$ , and  $\sum_{x_i} p_{x_i s} (1 - x_{ij})$  if  $c_j = 1$ . Comparing these two values, we conclude that  $c_j$  should be assigned 1 if  $\sum_{x_i} p_{x_i s} (1 - x_{ij}) < \sum_{x_i} p_{x_i s} x_{ij}$ , which yields the result as above.

### 3.5.3 Heuristic on State Selection for Duplication

While genetic algorithm can find a very good state duplication strategy, it may take a long time to converge for FSMs of large size. In fact, the length of *chromosome* (i.e., the size of the queue for states to be duplicated) can be close to the size of the original FSM. (In the worst case, it is only two less than the number of states.) Therefore, we propose a heuristic that select the states for duplication efficiently.

As we have seen from Figure 3.2, states with large (average) Hamming distance from its previous states will benefit because they will have less previous states in the re-constructed FSM, which allows the encoding scheme to find a better code to reduce the Hamming distance. Outgoing edges to the next states and the codes of the next states do not have the same importance because each duplicate state will be connected to the same set of next states to preserve the correct functionality.

For each state  $s_i$ , we define:

$$r(s_i) = \sum_{(v_j, v_i) \in E} H(v_i, v_j) / \text{indgree}(v_i)$$

(3.5)

where node  $v_i$  represents state  $s_i$  in the STG and the sum is taken over the number of all the incoming edges  $(v_j, v_i)$  at node  $v_i$ .

This value measures the average Hamming distance between state  $s_i$  and all its previous states. We duplicate one state at a time and each time we select the state according to the following rules:

- 1. select the state with the largest r-value.

- 2. if there is a tie, select the state with fewer previous and/or next states.

- 3. if the tie still exists, break it by selecting a state randomly.

Rule 1. helps us to locate the state(s) such that state duplication can give us large gain in reducing Hamming distance. Rule 2. helps us reduce the size of the re-constructed FSM because each duplicated gate needs to be connected to all the next states and some of the previous states. This could eventually help the encoding algorithm to find a better encoding scheme.

## 3.5.4 Heuristic on How to Duplicate a Selected State

We now present our algorithm that duplicates the selected state. Ideally, we want to duplicate the state in such a way that the new FSM will maximally reduce the switching activity when encoded optimally. Apparently, this requires solving the NP-hard state encoding problem optimally. Instead, we focus on how to duplicate a state to minimize switching activity locally.

More specifically, let s be the state we select for duplication, PS and NS be the sets of previous states and next states of s respectively in the original FSM. The state duplication procedure 1) creates a state s' that also has NS as its next states, and 2) splits PS into  $PT_1$  and  $PT_2$  and make them as the previous states for s and s' in the new FSM. The goal of such local state duplication is to minimize

$$\sum_{t \in PT_1} P_{ts} H(t, s) + \sum_{t \in NS} P_{st} H(t, s) + \sum_{t \in PT_2} P_{ts'} H(t, s') + \sum_{t \in NS} P_{s't} H(t, s')$$

where  $P_{ts}$  is the transition probability from state t to state s and H(t,s) is the Hamming distance between the two states.

The challenge is how to partition the previous states PS into two subsets. Our solution, as shown in Figure 3.5, is based on the fact that the two states in PS with the largest Hamming distance should belong to different partitions. We find, in line 3, states  $v_k$  and  $v_l$  that have the largest Hamming distance and put them into  $PT_1$  and  $PT_2$  as their respective centers (lines 4-5). For each of the other states  $t \in PS$ , we include it to the subset whose center is closer to t (lines 6-9). After we finish the partition, we re-compute the centers  $c_1$  and  $c_2$  of the two subsets (line 10) following the method described in Lemma 2 below. We then re-partition set PS based on these new centers and continue if the new partition results in reduced total Hamming distance (line 12).

The following lemmas show the correctness of this approach.

**Lemma 2.** In any optimal partition, state s and its duplicate s' will have the codes of the two centers.

[Proof]. Suppose that one partition has k states with codes  $\{x_{i1}x_{i2}\cdots x_{in}:$   $i=1,2,\cdots,k\}$  and they will have state s as their next state in the re-constructed FSM. We want to find the code  $c_1c_2\cdots c_n$  for state s to minimize the total Hamming distance

$$\sum_{i=1}^{k} H(s, x_i) = \sum_{i=1}^{k} \sum_{j=1}^{n} |x_{ij} - c_j| = \sum_{i=1}^{n} (\sum_{j=1}^{k} |x_{ij} - c_j|)$$

Because each bit is independent, the above is minimized if and only if  $\sum_{i=1}^{k} |x_{ij} - c_j|$  is minimized for each  $j = 1, 2, \dots, n$ . Let a be the number of 1's in  $\{x_{ij} : i = 1, 2, \dots, k\}$  and b be the number of 0's.  $\sum_{i=1}^{k} |x_{ij} - c_j| = b$  if  $c_j = 1$  and  $\sum_{i=1}^{k} |x_{ij} - c_j| = a$  if  $c_j = 0$ . Clearly, it is minimized when  $c_j$  is defined as the majority of  $\{x_{ij} : i = 1, 2, \dots, k\}$ .

**Lemma 3.** The optimal partition is reached in time linear to the size of set PS, i.e., the number of previous states of state s.

[Proof]. Because of its discrete nature, every time the loop (lines 6-12) is repeated, the total Hamming distance is reduced by at least 1. Therefore, this loop will stop after being repeated finite times. Furthermore, the largest Hamming distance from s (or its duplicate s') to any state in PS is n. If there are k states in PS, then the loop will not be executed more than kn times.

# 3.5.5 Determine the Minimum Switching Activity

There are two reasons for us to determine the optimal encoding scheme for a given FSM. First, it allows us to test the quality of low power state encoding heuristics. Second, comparing the minimum switching activity of the original FSM

```

Local Algorithm to Duplicate a State

/* Duplicate state s */

1. for each pair s_i and s_j in PS, the previous states of s

2.

compute the Hamming distance H(s_i, s_j);

3. pick s_1 and s_2 s.t. H(s_1, s_2) = \max_{s_i, s_j \in PS} \{H(s_i, s_j)\};

4. PT_1 = \{s_1\}; PT_2 = \{s_2\};

5. c_1 = s_1; c_2 = s_2;

6. for each state t \in PS

if (H(t, c_1) < H(t, c_2))

7.

PT_1 = PT_1 \cup \{t\};

8.

9.

else PT_2 = PT_2 \cup \{t\};

10. re-compute c_1 and c_2, the centers of PT_1 and PT_2;

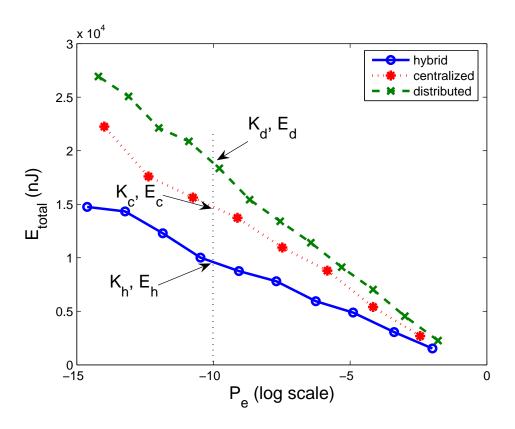

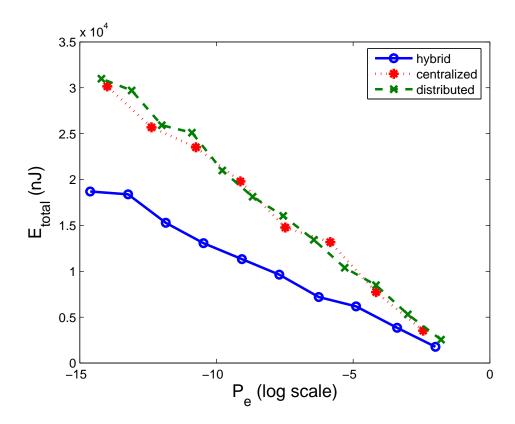

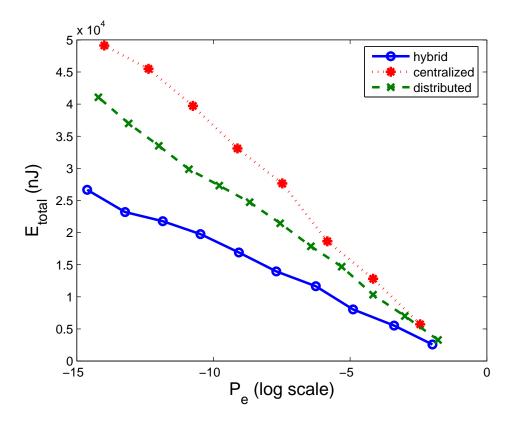

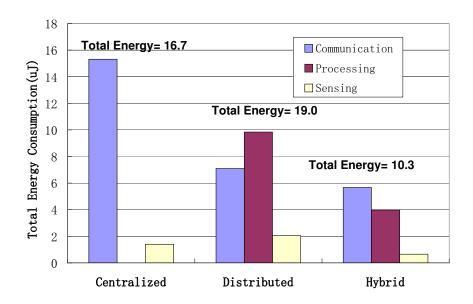

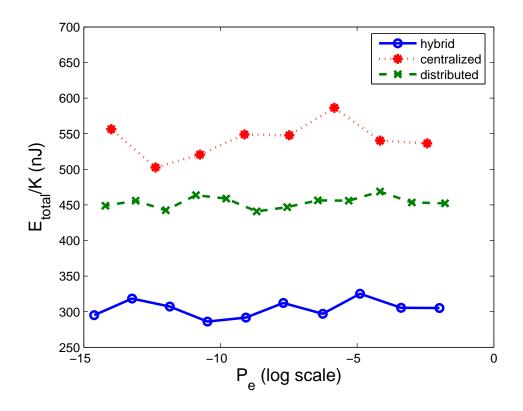

11. H_{total} = \sum_{t \in PT_1} H(t, c_1) + \sum_{t \in PT_2} H(t, c_2);