ABSTRACT

Title of Dissertation:

PROVIDING QOS WITH REDUCED ENERGY

CONSUMPTION VIA REAL-TIME VOLTAGE

SCALING ON EMBEDDED SYSTEMS

Shaoxiong Hua, Doctor of Philosophy, 2004

Dissertation directed by: Professor Gang Qu

Department of Electrical and Computer Engineering

Low energy consumption has emerged as one of the most important design objectives for many modern embedded systems, particularly the battery-operated PDAs. For some soft real-time applications such as multimedia applications, occasional deadline misses can be tolerated. How to leverage this feature to save more energy while still meeting the user required quality of service (QoS) is the research topic this thesis focuses on. We have proposed a new probabilistic design methodology, a set of energy reduction techniques for single and multiple processor systems by using dynamic voltage scaling (DVS), the practical solutions to voltage set-up problem for multiple voltage DVS system, and a new QoS metric.

Most present design space exploration techniques, which are based on application's worst case execution time, often lead to over-designing systems. We have proposed the probabilistic design methodology for soft real-time embedded systems by using detailed execution time information in order to reduce the system resources while delivering the user required QoS probabilistically.

One important phase in the probabilistic design methodology is the offline/online resource management. As an example, we have proposed a set of energy reduction techniques by employing DVS techniques to exploit the slacks arising from the tolerance to deadline misses for single and multiple processor systems while meeting the user required completion ratio statistically.

Multiple-voltage DVS system is predicted as the future low-power system by International Technology Roadmap for Semiconductors (ITRS). In order to find the best way to employ DVS, we have formulated the voltage set-up problem and provided its practical solutions that seek the most energy efficient voltage setting for the design of multiple-voltage DVS systems. We have also presented a case study in designing energy-efficient dual voltage soft real-time system with (m, k)-firm deadline guarantee.

Although completion ratio is widely used as a QoS metric, it can only be applied to the applications with independent tasks. We have proposed a new QoS metric that differentiates firm and soft deadlines and considers the task dependency as well. Based on this new metric, we have developed a set of online scheduling algorithms that enhance quality of presentation (QoP) significantly, particularly for overloaded systems.

# PROVIDING QOS WITH REDUCED ENERGY CONSUMPTION VIA REAL-TIME VOLTAGE SCALING ON EMBEDDED SYSTEMS

by

#### Shaoxiong Hua

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2004

#### Advisory Committee:

Professor Gang Qu, Chair Professor Shuvra S. Bhattacharyya Professor Ralph Etienne-Cummings Professor K. J. Ray Liu

Professor Chau-Wen Tseng

©Copyright by Shaoxiong Hua 2004

## DEDICATION

To my wife and our parents

#### ACKNOWLEDGEMENTS

First of all, I would like to sincerely thank my advisor, Professor Gang Qu, for his academic guidance, encouragement and patience over the past three years. When I switched my major to computer engineering, it is him who gave me a lot of advice and helped me find a good research topic. I wish to thank him for dedicating so much time to help me learn how to conduct high quality research and how to present our results. This dissertation would not be possible without his encouragement and suggestions.

I would also like to thank Professor Shuvra S. Bhattacharyya for his kind help and suggestions during my Ph.D. studies. I also wish to thank the other members of my dissertation committee, Professor Ralph Etienne-Cummings, Professor K. J. Ray Liu, and Professor Chau-Wen Tseng, for kindly serving on the committee with invaluable comments.

Next, I would like to thank Professor Bingen Yang of University of Southern California and Professor John S. Baras for their kind support and giving me the chance to USA and University of Maryland to pursue further education. I would like to thank Mr. Lane Smith and Mr. Fred Fischer, both in Agere Systems Inc., for kindly providing me the summer intern position in the last three years. Furthermore, I would like to thank Professor Manoj Franklin and Professor William Hawkins for their kind help during my Ph.D. studies.

I would like to thank my officemates and colleagues in the Embedded Systems Research Laboratory. I enjoyed the collaboration with other fellow graduate and undergraduate students, in particular Vida Kianzad, Guang Han, Pushkin R. Pari, Yuan Lin and Melissa Barker, to name a few.

I owe a great deal to my parents and parents-in-law for their love, encouragement and unconditional support throughout the course of my Ph.D. studies.

Finally and most importantly, I would like to especially thank my lovely wife, Huixian, for her endless love, patience, encouragement and support in these many years. Without her support, the dissertation would not have been completed.

## TABLE OF CONTENTS

| Lis | st of | Tables                                                        | viii |

|-----|-------|---------------------------------------------------------------|------|

| Lis | st of | Figures                                                       | X    |

| 1   | Intr  | roduction                                                     | 1    |

|     | 1.1   | Soft Real-Time Embedded Systems                               | 2    |

|     | 1.2   | Dynamic Voltage Scaling (DVS)                                 | 4    |

|     | 1.3   | Quality of Service (QoS)                                      | 12   |

|     | 1.4   | Contribution of this Dissertation                             | 15   |

|     | 1.5   | Organization of this Dissertation                             | 17   |

| 2   | Pro   | babilistic Design Methodology                                 | 20   |

|     | 2.1   | Introduction                                                  | 20   |

|     | 2.2   | Related Work                                                  | 22   |

|     | 2.3   | Probabilistic Design Methodology Overview                     | 24   |

|     | 2.4   | Estimating the Probabilistic Timing Performance               | 27   |

|     | 2.5   | Managing System Resource under Probabilistic Performance Con- |      |

|     |       | straint                                                       | 30   |

|     | 2.6   | Conclusions                                                   | 31   |

| 3   | Ene   | ergy Reduction Techniques for Single and Multiple Processor   | ,    |

|     | Syst  | tems                                                          | 33   |

|     | 3.1   | Introduction                                                  | 33   |

|     | 3.2   | Problem Formulation                                           | 39   |

|     | 3.3   | Energy-Driven Voltage Scaling Techniques                      |      |

|     |       | with Completion Ratio Constraint                              | 41   |

|     |       | 3.3.1 A Naïve Best-Effort Approach                            | 42   |

|     |       | 3.3.2 BEEM: On-Line Best-Effort Energy Minimization           | 43   |

|     |       | 3.3.3 QGEM: Completion Ratio Guaranteed Energy Minimization   | 46   |

|     | 3.4   | Simulation Results                                            | 50   |

|     | 3.5   | Conclusions                                                   | 55   |

| 4 | Vol           | tage Set-up Problem on Embedded Systems with Multiple               |           |

|---|---------------|---------------------------------------------------------------------|-----------|

|   | Vol           | tages                                                               | <b>57</b> |

|   | 4.1           | Introduction                                                        | 57        |

|   | 4.2           | The Voltage Set-up Problem                                          | 61        |

|   |               | 4.2.1 Application Model                                             | 61        |

|   |               | 4.2.2 Multiple-Voltage DVS System Model                             | 62        |

|   | 4.3           | Solving the Voltage Set-up Problem                                  | 64        |

|   |               | 4.3.1 Case I: Dual Voltages Three Applications ( $m=2$ and $n=3$ ). | 67        |

|   |               | 4.3.2 Case II: Dual Voltages Multiple Applications (m=2 and n>3)    | 68        |

|   |               | 4.3.3 Case III: Multiple Voltages Multiple Applications (m $>$ 2)   | 69        |

|   |               | 4.3.4 Finding the Best Voltage Set-up                               | 72        |

|   | 4.4           | Simulation Results                                                  | 74        |

|   | 4.5           | Conclusions                                                         | 77        |

| 5 | Ene           | ergy-Efficient Dual-Voltage System with (m,k)-Firm Guarantee        |           |

|   | $-\mathbf{A}$ | Case Study                                                          | 80        |

|   | 5.1           | Introduction                                                        | 81        |

|   |               | 5.1.1 Motivation                                                    | 81        |

|   |               | 5.1.2 Problem and Contributions                                     | 82        |

|   |               | 5.1.3 A Motivational Example                                        | 83        |

|   |               | 5.1.4 Previous Work                                                 | 85        |

|   |               | 5.1.5 Chapter Organization                                          | 86        |

|   | 5.2           | Optimal On-Line Voltage Scheduling Policy                           | 86        |

|   | 5.3           | Determining the Most Energy-Efficient Dual-Voltage System with      |           |

|   |               | (m,k)-Firm Guarantee                                                | 90        |

|   |               | 5.3.1 Computing $\bar{E}$ for Case $(k-1,k)$                        | 91        |

|   |               | 5.3.2 Computing $\bar{E}$ for Case $(m, k)$                         | 93        |

|   |               | 5.3.3 Determining the Optimal Dual-Voltage System                   | 96        |

|   | 5.4           | Simulation Results                                                  | 98        |

|   | 5.5           | Conclusions                                                         | 102       |

| 6 | Qos           | S-Driven Scheduling for Firm/ Soft Real-Time Applications 1         | 04        |

|   | 6.1           | Introduction                                                        |           |

|   | 6.2           | A New QoS Metric                                                    |           |

|   |               | 6.2.1 QoS Model                                                     |           |

|   |               | 6.2.2 Simulation of MPEG Streams                                    |           |

|   | 6.3           | Online Schedulers                                                   |           |

|   |               | 6.3.1 S2F: Soft to Firm Deadline Conversion                         |           |

|   |               | 6.3.2 EDF*, FCFS* and LETF*                                         |           |

|   |               | 6.3.3 IFF: Important Task (Frame) First                             |           |

|   | 6.4           | Experimental Results                                                | 118       |

|   | 6.5           | Conclusions                                                         | 122       |

| 7  | Con  | clusior | as and Future Work               | 123 |

|----|------|---------|----------------------------------|-----|

|    | 7.1  | Conclu  | isions                           | 123 |

|    |      | 7.1.1   | Probabilistic Design Methodology | 124 |

|    |      | 7.1.2   | Voltage Set-up Problem           | 125 |

|    |      | 7.1.3   | A New QoS Metric                 | 125 |

|    | 7.2  | Future  | e Work                           | 126 |

| D: | 1. 1 | 1       |                                  | 100 |

| ВI | Bona | graphy  |                                  | 129 |

## LIST OF TABLES

| 3.1 | Characteristics of the tasks and the processor. (a): each entry                      |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | shows the best/worst case execution time at $V_1$ and the probability                |    |

|     | this execution time occurs at run time. (b): power is normalized                     |    |

|     | to the power at $V_1$ and $delay$ column gives the normalized processing             |    |

|     | time to execute the same task at different voltages                                  | 36 |

| 3.2 | Expected completion ratio and energy consumption for the three                       |    |

|     | algorithms. $t@V_1$ , $t@V_2$ , and $t@V_3$ are the average time that the            |    |

|     | processor operates at three voltages for each iteration; E is the av-                |    |

|     | erage energy consumption to complete one iteration; and the last                     |    |

|     | column, obtained by $E \cdot 60\%/\mathcal{Q}$ , corresponds to the case of shutting |    |

|     | the system down once 6,000 iterations are completed                                  | 38 |

| 3.3 | Average energy consumption per iteration by naïve, BEEM1, BEEM2                      |    |

|     | and QGEM to achieve $Q_0 = 0.900$ with deadline constraints $\mathcal{D}$ . (n:      |    |

|     | number of vertices in the benchmark task graph; $m$ : number of pro-                 |    |

|     | cessors; $\mathcal{Q}$ : the actual completion ratio achieved by QGEM without        |    |

|     | forcing the processors stop at $Q_0$ ; energy is in the unit of the dissi-           |    |

|     | pation in one CPU unit at the reference voltage 3.3V.)                               | 53 |

| 4.1 | The average energy consumption per iteration of dual-voltage sys-                    |    |

|     | tem with different voltage set-ups                                                   | 60 |

| 4.2 | Information on the two ad hoc applications                                           | 75 |

|     |                                                                                      |    |

| 4.3 | The optimal voltage set-ups and their corresponding average energy     |

|-----|------------------------------------------------------------------------|

|     | consumption per execution. (In the parenthesis of energy columns,      |

|     | "-" is the energy saving over the fixed voltage system, "+" is the     |

|     | "wasted" energy comparing to the ideal voltage system.) 76             |

| 5.1 | Characteristics of the iterations and the processor. (a): each entry   |

|     | shows execution time at $V_1$ and the probability this execution time  |

|     | occurs at run time. (b): $power$ is normalized to the power at $V_1$   |

|     | and delay column gives the normalized processing time to execute       |

|     | one iteration at different voltages                                    |

| 5.2 | The average energy consumption per iteration for systems with dif-     |

|     | ferent voltage set-ups                                                 |

| 5.3 | Impact of different $m$ to the selection of $V_{lo}$ and $\bar{E}$ 101 |

| 5.4 | Impact of different $k$ to the selection of $V_{lo}$ and $\bar{E}$     |

| 5.5 | Information on three periodic streams                                  |

## LIST OF FIGURES

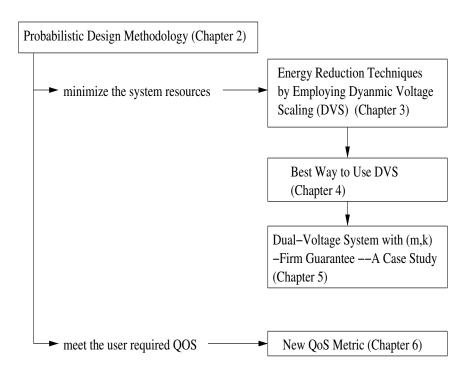

| 1.1 | The overview of my Ph.D. research                                                                   | 15 |

|-----|-----------------------------------------------------------------------------------------------------|----|

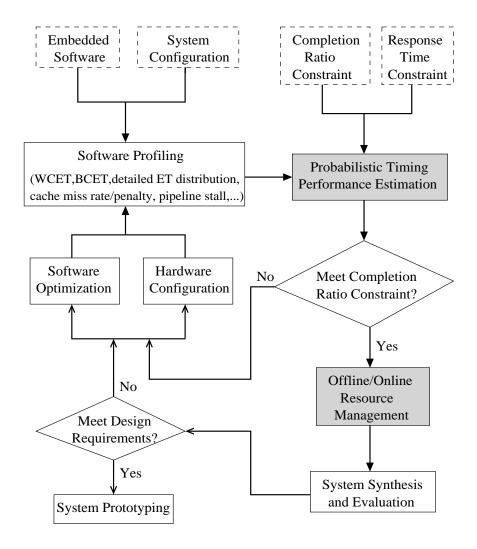

| 2.1 | Design flow in the probabilistic design methodology                                                 | 26 |

| 3.1 | QGEM's offline part to determine the minimum commitment to                                          |    |

|     | provide $Q_0$                                                                                       | 47 |

| 3.2 | QGEM's offline part to allocate execution time for each task                                        | 49 |

| 3.3 | On-line scheduling policy for algorithm QGEM                                                        | 50 |

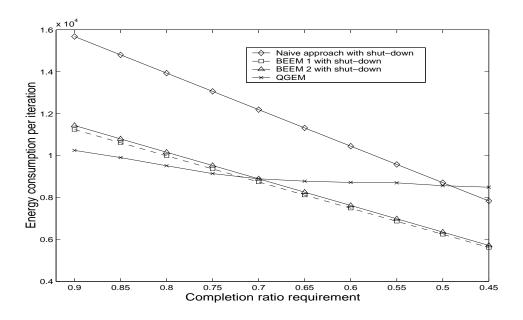

| 3.4 | Different completion ratio requirement's impact to the average en-                                  |    |

|     | ergy consumption per iteration on benchmark TGFF8 with 3 pro-                                       |    |

|     | cessors                                                                                             | 54 |

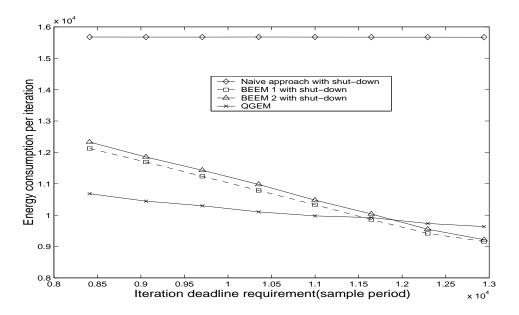

| 3.5 | Different deadline requirement's impact to the average energy con-                                  |    |

|     | sumption per iteration on benchmark TGFF8 with 3 processors                                         | 54 |

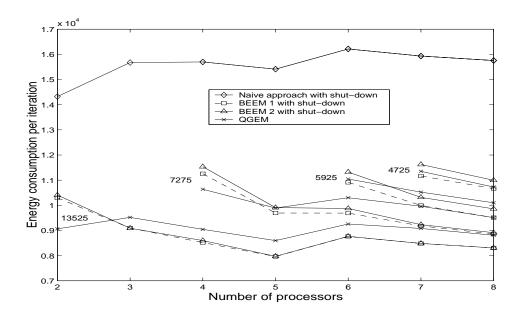

| 3.6 | The average energy consumption per iteration on benchmark TGFF8                                     |    |

|     | with different number of processors and different deadlines (13525,                                 |    |

|     | 7275, 5925 and 4725)                                                                                | 56 |

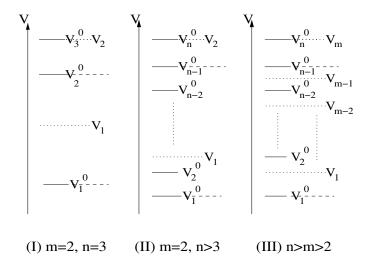

| 4.1 | Summary of voltage set-up solutions for m-voltage system with n                                     |    |

|     | applications. $(V_i^0)$ is the ideal voltage for i-th application, $V_1^0 \leq$                     |    |

|     | $V_2^0 \leq \cdots \leq V_n^0$ ; $V_j$ is the j-th supply voltage and $V_1 < V_2 < \cdots < V_m$ .) | 66 |

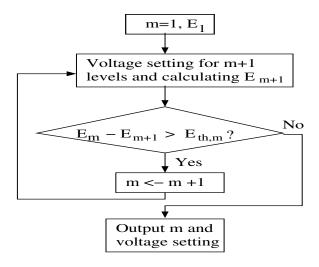

| 4.2 | Voltage set-up algorithm for the case of $m=2, n \geq 3$                                            | 70 |

| 4.3 | General voltage set-up problem as a nonlinear programming prob-                                     |    |

|     | lem for the case of $m > 2$                                                                         | 71 |

| 4.4 | Flow to find the best voltage set-up                                                                | 73 |

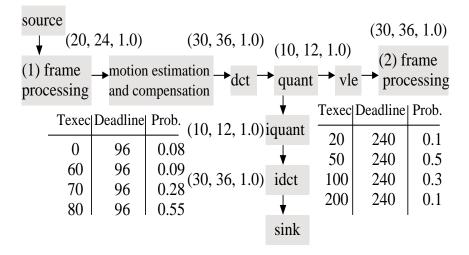

| 4.5 | MPEG video encoder execution time distributions and correspond-               |

|-----|-------------------------------------------------------------------------------|

|     | ing deadlines in $10^4$ cycles (redrawn from [59]). The lower left table      |

|     | is related to motion estimation and compensation; the lower right             |

|     | table is related to vie (variable length encoding)                            |

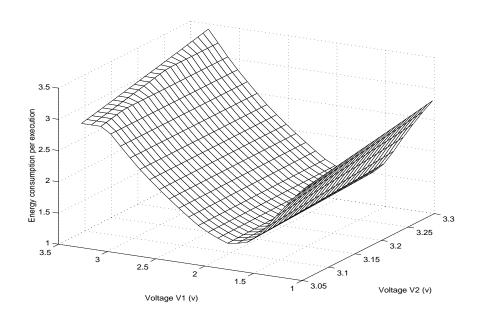

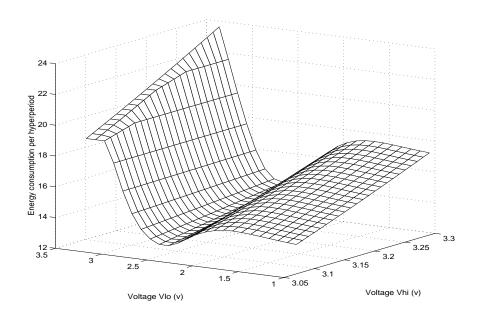

| 4.6 | Dual-voltage system's average energy consumption for the two ad               |

|     | hoc applications with different voltage set-ups                               |

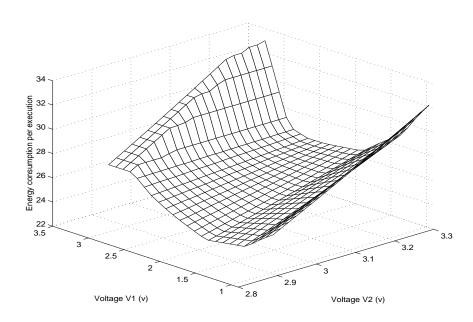

| 4.7 | Dual-voltage system's average energy consumption for the MPEG                 |

|     | encoder with different voltage set-ups                                        |

| 5.1 | The on-line greedy scheduler for (m,k)-firm guarantee 89                      |

| 5.2 | On-Line Greedy vs. <i>p-random</i> on-line schedulers                         |

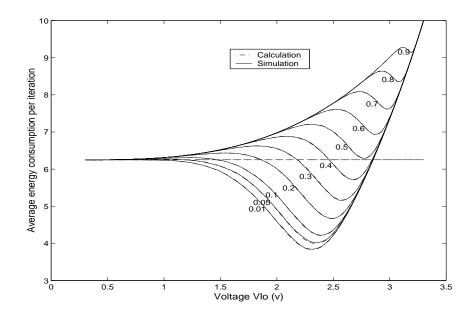

| 5.3 | Accuracy of the proposed numerical method in computing the av-                |

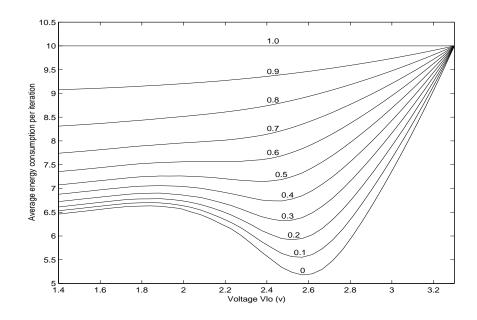

|     | erage energy consumption per iteration $\bar{E}$                              |

| 5.4 | Simulated $\bar{E}$ for three applications with different (m,k)-firm require- |

|     | ments                                                                         |

| 6.1 | A typical GOP pattern (I-to-I=12, I-to-P=3)                                   |

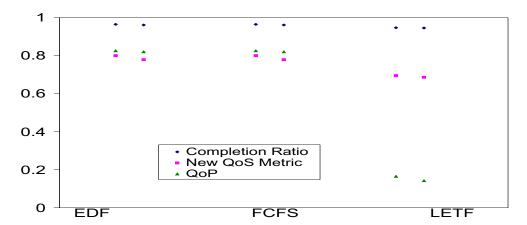

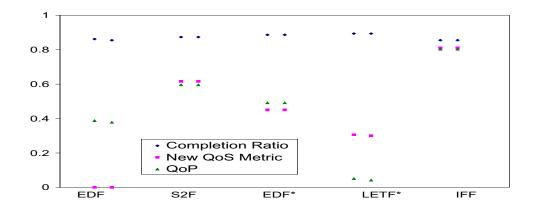

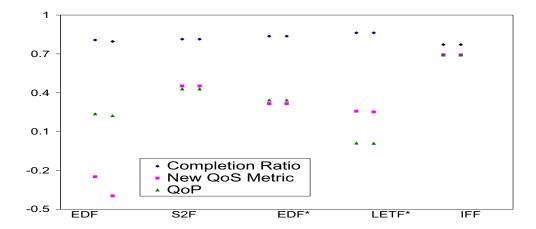

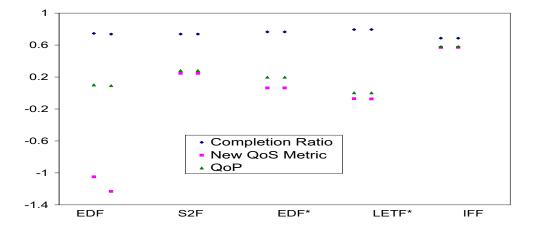

| 6.2 | Comparison of some widely used online schedulers on movie "Goldfin-           |

|     | ger" in the frame rate of 30 fps in the case of, from left to right,          |

|     | non-preemptive and preemptive                                                 |

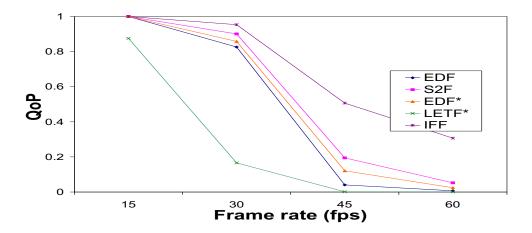

| 6.3 | Comparison of QoP under different online schedulers on movie "Goldfin-        |

|     | ger" in the case of non-preemptive with different frame rates (15,            |

|     | 30, 45, 60 fps)                                                               |

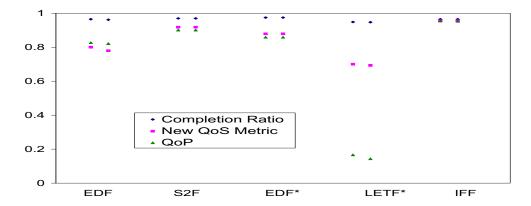

| 6.4 | Comparison of different online scheduling policies on movie "Goldfin-         |

|     | ger" in the frame rate of 30fps in the case of, from left to right,           |

|     | non-preemptive and preemptive                                                 |

| 6.5 | Comparison of different online scheduling policies on movie "Wizard           |

|     | of OZ" in the frame rate of 30fps in the case of, from left to right,         |

|     | non-preemptive and preemptive                                                 |

| 6.6 | Comparison of different online scheduling policies on movie "Silence          |

|     | of Lambs" in the frame rate of 45fps in the case of, from left to             |

|     | right, non-preemptive and preemptive                                          |

| 6.7 | Comparison different online scheduling policies on movie "Star Wars" |

|-----|----------------------------------------------------------------------|

|     | in the frame rate of 45fps in the case of, from left to right, non-  |

|     | preemptive and preemptive                                            |

# Chapter 1

# Introduction

With the development of Very Large Scale Integration (VLSI) techniques, the total number of devices on a chip has doubled every 24 months, known widely as "Moore's Law". It is predicted that before 2010, the chip will have 1 billion transistors [37]! This results in the fact that embedded systems have been moving from board-level systems to System-on-Chips (SoCs) and it provides us the opportunities to find more embedded system applications.

On the other hand, the importance of time-to-market becomes more and more significant. The Semico Research Corporation reports that for Black & White TV, it took almost 18 years to reach the shipment of one million units while for DVD player it took only less than one year. The profit window is open for a short period of time and only to the early technology providers [38]. Therefore the design of embedded systems must move from craft to discipline to increase the productivity and decrease the time-to-market.

With the decrease in the transistor feature size and the increase in the number of transistors on a chip, the power dissipation has been increased dramatically. For example, when the transistor feature size is less than 100nm, the power dissipation will be more than 300Watts [1]. High power dissipation results in many hot spots in the thermal map of the working chip that will limit the allowed performance. More power consumption means more heat dissipation and we have to use more and bigger heatsinks and fans, bigger and more expensive motherboards and cases. And more power also means the lower reliability and shorter battery life time for the battery-operated systems. Because of the importance of power, low power has emerged as one of the most important design objectives for the embedded system designers.

In order to reduce the design cost (e.g., decrease the time-to-market and reduce the fabrication cost) and system cost (e.g., power), one needs to increase the level of design abstraction and develops system-level design methodology. In this dissertation, I will mainly focus on the soft real-time embedded system design. Specifically, we have developed energy reduction techniques by employing dynamic voltage scaling (DVS) while meeting user required quality of service (QoS) statistically. In this chapter, I will give the introduction of soft real-time embedded systems, dynamic voltage scaling and quality of service.

## 1.1 Soft Real-Time Embedded Systems

Embedded systems are widely used in many applications such as encoding and decoding of audio and video, digital control, the monitoring of large rotating machinery, radar signal processing and tracking and so on. Different from the general-purpose systems such as desktop systems, the embedded systems are those that use single or multiple microprocessors to implement the dedicated applications [20]. This means that every application is the subject of a special development that must directly produce the product satisfying user requirements, costs and dead-

line. Therefore it is possible for the designers to get the detailed information of the application such as sampling data rate, data distribution etc. that can be used during the design stage.

Most embedded systems are *real-time* systems, which are required to react to stimuli from the environment and complete their work and deliver their services within time intervals dictated by the environment [75]. In real-time systems, time-liness is the key characteristic. In such systems, we often use the *deadline* to be one of the important time constraints of the task (workload). There are three types of deadline:

- Hard deadline: A task has a hard deadline if it must be completed before the deadline otherwise the system will be in fault and deadline missing may cause catastrophic consequences.

- Firm deadline: A task has a firm deadline if it must be completed before the deadline otherwise although the system will not be in fault, it will not get any reward for serving the task.

- Soft deadline: A task has a soft deadline if the system can still benefit even if the deadline is missed, subjected to a deadline miss penalty.

In hard real-time systems all deadlines of the tasks are hard while in soft real-time systems portion of deadlines are soft. In this dissertation, we mainly focus on the design of soft real-time embedded systems that conduct the repetitive data processing that can be found in many DSP applications. Such systems require moderately high performance and can tolerate occasional deadline misses. The timing requirements of such systems are often specified in probabilistic terms [75].

And the actual execution time of the task is often varied and deviates from its worst case execution time (WCET), sometimes by a large amount.

## 1.2 Dynamic Voltage Scaling (DVS)

As low power/energy consumption has emerged as one of the most important design objectives, reducing the supply voltage (voltage scaling) becomes one of the most effective techniques to decrease the power/energy consumption [123].

There are three major sources of power consumption, i.e., switching component, direct-path short circuit current and leakage current [23]. Although leakage power dissipation is gaining more and more attention recently, switch component (dynamic) power still dominates in most embedded systems. Dynamic power in a CMOS circuit is proportional to  $\alpha C_L V_{dd}^2 f_{clock}$ , where  $\alpha C_L$  is the effective switched capacitance,  $V_{dd}$  is the supply voltage, and  $f_{clock}$  is the clock frequency. As the power and energy are the quadratic functions of supply voltage, reducing the supply voltage can result in substantial power and energy saving and in general more effective than the technique that shuts down a processor when it is idle. Roughly speaking, system's power dissipation is halved if we reduce  $V_{dd}$  by 30% without changing any other system parameters. The switching of voltage can be done rapidly with negligible overhead by using efficient DC-DC converters [91]. However, this energy saving comes at the cost of reduced throughput, slower system clock frequency, or higher gate delay. The gate delay is proportional to  $\frac{V_{dd}}{(V_{dd}-V_t)^{\beta}}$ , where  $V_t$  is the threshold voltage and  $\beta \in (1.0, 2.0]$  is a technology dependent constant. Dynamic voltage scaling, which varies the system's operating voltage and clock frequency according to the workload at run-time, can achieve the highest possible energy efficiency for the time-varying computational loads while providing desired performance [18]. It has been demonstrated as one of the most effective low power system design techniques.

In 1996, an actual hardware implementation using voltage scaling was described in [21]. The implementation applies voltage scaling to MPEG video decoding on a DSP. The clock frequency and voltage are adjusted to match the varying complexity of video frames. In [22], a dedicated cryptography processor was presented that uses voltage scaling to reduce the power and energy consumption. The research group in Berkeley Wireless Research Center has developed a dynamic voltage scaled microprocessor system in which the supply voltage and clock frequency can be dynamically varied so that the system can deliver high throughput when required while significantly extending battery life during the low speed periods [17, 18]. The system can dynamically vary the supply voltage from 1.2V to 3.8V in less than  $70\mu$ s. In [94], they showed DVS can be efficiently integrated into existing operating systems without extensive modification. Pouwelse et al. [96] described a low-power microprocessor system that allows power-aware applications to quickly adjust the performance level of the processor whenever the workload changes. Hong et al. [45] developed a design methodology for the low power core-based real-time system-on-chip based on dynamically variable voltage hardware. Many modern microprocessors, such as Transmeta's Crusoe, AMD's K-6, Intel's XScale and Pentium III and IV, can support dynamic voltage scaling.

Early research on voltage scaling was on systems that have multiple simultaneous available voltages [24, 58, 72, 106]. For example, Raje and Sarrafzadeh [106] presented a supply voltage driven technique to minimize power consumption at the behavioral level. They used data flow graph to define systems and exploited the parallelism evident among all of operations. Some operations can be slowed down

by applying a smaller supply voltage that reduces the system energy consumption and the system throughput still meets the given time constraint. Such variable voltage systems can be more energy-efficient because of the flexibility of choosing the operating voltage and clock frequency [100]. In [65, 66], the authors propose the energy efficient synthesis techniques for datapath circuits using dynamic frequency clocking and multiple voltages.

There are a lot of research on task-level scheduling strategies for adjusting CPU speed and supply voltage so as to reduce power and energy consumption of the systems. A scheduling method to reduce energy consumption by dynamically changing the clock speed along with the supply voltage of the processor was first proposed in [125] and was later extended in [39]. The voltage scheduling algorithms proposed in [39, 125] have been improved with PACE (Processor Acceleration to Conserve Energy), an approach to reducing the energy consumption of dynamic voltage scheduling (DVS) algorithms without affecting their performance [77]. The foundation for the simulation and analysis of DVS algorithms can be found in [93]. The above works [39, 77, 93, 125] are in the context of non-real-time workstation environment. Furthermore, Qu et al. [103] combined the variable voltage scaling with variable size packet fragmentation to minimize the power consumption in system-level pipelines under latency constraints.

Recently, many research groups have investigated the DVS problem for hard real-time systems [41, 46, 47, 64, 117, 128]. Yao, Demers and Shenker [128] have provided the minimum-energy preemptive static scheduling algorithm for a set of independent tasks with arbitrary arrival times and deadlines. They assumed that tasks are scheduled according to the earliest-deadline-first (EDF) scheduling policy [73]. In the same paper [128], the authors also proposed two on-line scheduling

heuristics, called Average Rate Heuristic (AVR) and Optimal Available Heuristic, with the same model as in the static version. They showed that for the power function  $P(s) = s^p (p \ge 2)$ , the AVR has a constant competitive ratio  $r^p$  satisfying  $p^p \leq r^p \leq 2^{p-1}p^p$ . Hong etc. developed the non-preemptive offline variable voltage scheduling heuristic with the assumption of zero delay in changing voltage levels [45]. In [47], they focused on the preemptive variable voltage scheduling heuristic while taking into account the inherent limitation on the rates at which voltage and clock frequency can be changed by the power supply controllers and clock generators. The same group also describes an on-line scheduling algorithm for hard real-time tasks on variable voltage processor, where it is assumed that the release times of tasks are not known a priori [46]. Ishihara and Yasuura [56] presented some significant theorems for voltage scheduling and formulate the static voltage scheduling problem as an integer linear programming (ILP) problem. Recently, Quan and Hu [105] studied the problem of determining the optimal voltage schedule for a real-time system with fixed-priority jobs implemented on a variable voltage processor based on the assumption that the timing parameters of each job is known offline. Manzak and Chakrabarti [85] proposed variable voltage task scheduling algorithms (periodic as well as aperiodic) that minimize energy. Pillai and Shin [95] presented a class of algorithms called real-time DVS (RT-DVS) that modify the OS's real-time scheduler and task management service to provide significant energy savings while maintaining real-time deadline guarantees. The algorithms have been verified through simulations and a working prototype implementation.

Reducing power and energy consumption of processors is fundamentally equivalent to exploiting the idle intervals or slacks of processors [118]. Offline voltage scheduling algorithms [45, 56] use the worst-case execution time (WCET), which

can be obtained through static analysis [71], profiling, or direct measurement, as one of the timing parameters for each of the tasks. However, the execution time of each task frequently deviates from its WCET, sometimes by a large amount. In order to exploit the slacks arising from the run-time variation of each task execution, the on-line voltage scheduling algorithms need to be applied with the offline algorithms in order to achieve more energy saving [41, 46, 64, 67, 117, 118]. Krishna and Lee [64] presented cyclic scheduling algorithm and EDF scheduling algorithm that is voltage-clock scheduling for the EDF (Earliest Deadline First) algorithm. Both algorithms consist an offline phase, in which voltage settings are picked to reduce energy consumption assuming that tasks run to their WCETs, and an online phase that adjusts the voltage setting on-the-fly to reclaim any slacks released by the tasks which actual execution time are less than their WCETs, thus making for a further round of energy saving. Shin and Choi [117] presented a power efficient version of a widely used fixed priority scheduling method. The method yields a power reduction by exploiting the slack times inherent in the system and those arising form variations of execution time task instances. The same authors also showed that combined offline and on-line components bring about more power saving [118]. In [41] Gruian also addressed scheduling for reduced energy of hard real-time tasks with fixed priorities assigned in a rate monotonic (RM) [73] or deadline monotonic (DM) [6]. Taking into account the real behavior of a real-time system, which is often better than the worst case, his method employs stochastic data to derive energy efficient schedules that are combined with on-line slack distribution to achieve energy reduction. Kumar and Srivastava [67] presented a power-saving prediction strategy that exploits the fixed priority scheduling of the real-time tasks running on the embedded systems. But there is a penalty of tasks

missing their deadlines. Pouwelse, Langendoen and Sips [97] described the energy priority scheduling (EPS) heuristic and show that by requiring applications to be power aware (i.e. they must specify their future demands) much better energy reduction can be achieved while still meeting all deadlines.

Most of papers introduced so far focus on the DVS problem on task-by-task basis on a single processor. In recent several years there are many research works that concentrate on intra-task voltage scheduling or multiple processor voltage scheduling.

Intra-task voltage scheduling [116] that adjusts the supply voltage within individual task boundary may not involve operating system (OS) in adjusting the clock speed, so it has an advantage that existing OS can be used without any modifications on a variable voltage processor. Lee and Sakurrai [70] presented a novel run-time dynamic voltage scaling scheme for low-power real-time systems that fully exploits slack time arising from task execution time variation and reduces the energy consumption significantly. It partitions a task into several timeslots and performs run-time software feedback control of supply voltage on timeslotby-timeslot basis. Shin, Kim and Lee proposed an intra-task voltage scheduling algorithm, which controls the supply voltage within an individual task boundary [116]. The proposed algorithm makes the voltage scaling decisions in compile time, not run time, and allows programmers with no knowledge on DVS to develop low-energy hard real-time applications. This idea can also be found in [90] that integrated compiler-assisted techniques with power aware operating system services and presented scheduling techniques to reduce energy consumption of applications that have deadlines. The difference between [116] and [90] is that [90] considers an embedded system with a single application that is divided into n sections or tasks, while [116] considers single-task applications or multi-task applications where one task is dominant in total execution time. Most recently, Dudami et al. [31] presented the energy-conserving feedback EDF scheduling for embedded systems with real-time constraints to exploit slack time generated by the invocation of the task at multiple frequency levels within the same invocation.

Tasks in real-world applications usually have control or data dependencies and many systems have multiple processors. Approaches in [8, 9, 42, 79, 80, 81, 113, 114 solve the energy minimization problem for dependent tasks on multiple variable voltage processors. Schmitz and Al-Hashimi [113] presented an efficient algorithm for voltage scaling of a distributed embedded system considering variations in the power dissipation among processes and inter process communications. The same authors [114] investigated the problem of considering DVS processing elements (DVS-PEs) power variations dependent on the executed tasks, during the synthesis of distributed embedded systems and its impact on the energy savings. Gruian and Kuchcinski [42] assumed a given task assignment and introduced a new scheduling approach, LEneS, that uses list-scheduling and a special priority function to derive static schedules with low energy consumption. Given a task scheduling Luo and Jha [79] presented a power-conscious algorithm for jointly scheduling multi-rate periodic task graphs and aperiodic tasks in real-time multiprocessor embedded systems in order to improve the response times of soft aperiodic tasks and reduce the power. The same authors have extended their work by using static and dynamic variable voltage scheduling algorithms to exploit the slacks more efficiently and achieve more energy saving [81]. In [80] they proposed static battery-aware scheduling algorithms in battery-powered distributed real-time embedded systems to increase the battery lifespan. Bambha and Bhattacharyya et al. have examined voltage scaling for multiprocessors under known computation time to reduce the overall power consumption under a given throughput constraint. The schedule of tasks on different processors is assumed to be known a priori. In [8], they proposed a local search approach for static voltage scaling based on the period graph model [10]. The same group presented a hybrid global/local search optimization framework for DVS in embedded multiprocessor systems [9]. They applied the simulated heating [131] approach to control parameterized local search such as hill climbing or Monte Carlo within a global search process in order to attain high search efficiency. Zhu et al. [130] introduced the concept of slack sharing on multiprocessor systems to reduce energy consumption. Based on this concept, they proposed two power-aware algorithms GSSR (global scheduling with shared slack reclamation) and LSSR (fixed-order list scheduling with shared slack reclamation) and simulation results showed the scheduling algorithms result in substantial energy saving compared to static power management. The essence of the above works is to utilize the slacks to allow voltage scaling to reduce power consumption without suffering any performance degradation. In [74], a power-aware scheduling algorithm was presented for mission-critical embedded systems with variable power constraints and heterogeneous power consumers, as well as different energy sources such as a non-rechargeable battery and a solar panel. It satisfies the min/max timing and max power constraints. In addition, it also tries to satisfy the minimum power constraint in order to fully utilize free power or to control power jitter. Mishra et al. [88] proposed a static power management algorithm (SPM) with considering processor parallelism for distributed real-time systems. They claimed that their algorithm is better than other existing algorithms such as simple SPM and Greedy SPM in terms of energy saving [88].

Finally, Zhang, Hu and Chen [129] presented a two-phase framework that integrates task assignment, ordering and voltage scaling (VS) together to minimize energy consumption of real-time dependent tasks executing on a given number of variable voltage processors. In the first phase, they applied an EDF scheduling that can be proved to be optimal for a single processor, and a scheduling with prioritybased task ordering and a best-fit processor assignment for multiple processors. In the second phase, they formulated the VS problem as an Integer Programming (IP) problem and solve the IP efficiently. Schmitz et al. [115] presented a two-step iterative synthesis approach for distributed embedded systems containing dynamic voltage scalable processing elements by employing two nested genetic algorithms, where the outer GA generates the assignments and the inner one creates various orderings. This algorithm is not however efficient in terms of run time. Recently, Luo and Jha [82] presented an efficient algorithm, which performs execution order optimization of scheduled events, power-profile and timing-constraint driven slack allocation to minimize the power consumption for heterogeneous distributed real-time embedded systems.

## 1.3 Quality of Service (QoS)

With the increasing popularity of real-time multimedia and wireless communication applications, quality of service (QoS) attracts a lot of attention. Providing the required QoS guarantees becomes vital for the design of embedded systems that carry out such applications. For many embedded systems applications such as distributed multimedia applications, the QoS requirements can be assessed in terms of users' subjective wishes or satisfaction with the quality of the applicationsperformance, synchronization, cost, and so forth [124]. The assessment results will be mapped onto the constraints of QoS parameters such as processor completion ratio, network throughput, delay, jitter and reliability etc. for various system components or layers [120]. The QoS parameters of the operating systems (OS) in the end systems can have a strong impact on the QoS the users eventually perceive.

Various QoS requirements, such as bounded delay, minimal throughput, guaranteed synchronization or resolution, task completion ratio, were first addressed in the network and real-time operating systems (RTOS) communities. Lawrence [68] presented a QoS Model that is defined by three attributes: timeliness, precision and accuracy. These attributes can be used for system specification, instrumentation, and evaluation. Altmann and Varaiya [5] defined QoS as a combination of the basic quality metrics for the network layer: delay, jitter, bandwidth and reliability. Wijesekera and Srivastava [127] presented quality of service metrics for continuity and synchronization specifications in continuous media. The most formally sound and practically relevant QoS model based on the demand curve and the service curve in the networking community was proposed by Cruz [28]. Based on service curves, Sariowan and Cruz etc. [111] propose a new scheduling policy SCED(Service Curve-based Earliest Deadline first) that guarantees the service curve for the connection in Virtual Circuit Switched Networks. The main conceptual result in RTOS literature, i.e., Q-RAM (QoS-based Resource Allocation Model), was presented by Rajkumar et al. [107]. They introduced an analytic approach for satisfying multiple QoS dimensions under a given set of resource constraints. They showed that the problem is NP-hard and developed an approximation polynomial algorithm for the problem by transforming it into a mixed integer programming problem [108]. Lee et al. [69] presented a QoS management framework to analytically allocate resources for QoS optimization in systems that must satisfy application needs along multiple QoS dimensions for given relations between QoS dimensions and resources. Comprehensive survey of QoS research can be found in [7, 124].

Task completions [11, 19], deadline miss-ratio [78], and loss-rate [126] have been widely used as the measurement of QoS particularly for overloaded and real-time systems in both academic and industry [3]. Baruah et al. [11] studied how to maximize task completions for overloaded systems. They concluded that any online algorithm may perform arbitrarily poorly as compared to a clairvoyant scheduler, but discussed competitive online schedulers for a few special cases such as Equal Request Times, Equal Execution Times, Monotonic Absolute Deadlines and Equal Relative Deadlines. Mittal et al. [89] proposed integrated dynamic scheduling algorithms for hard and QoS degradable tasks, represented by the workload models such as imprecise computation [76] and the (m,k)-firm guarantee [109] that quantify the trade-off between schedulability and result quality, in multiprocessor real-time systems. The proposed algorithms improve schedulability by exploiting the properties of these models in QoS degradation.

Recently QoS-driven system design also received attention from EDA (Electronic Design Automation) community, in particular embedded system design automation and low power system design [86, 98, 99, 102]. Qu et al. studied system synthesis for synchronous multimedia applications, where they focused on how to minimize the chip size while providing synchronization guarantees [99]. The same authors later showed how to use dynamic voltage scaling technique to provide guaranteed QoS with the minimal energy consumption [102]. Kornegay et al. [63] outlined foundations and framework in which QoS system design trade-offs and optimization can be addressed. They concluded by identifying and discussing the

future directions related to synthesis of QoS-sensitive systems. Qiu et al. modeled the power-managed multimedia system with QoS guarantees as a generalized stochastic Petri nets and used linear programming formulation to find the most energy-efficient solution [98]. Marculescu et al. presented a new methodology for system-level power and performance analysis based on the product of power and delay of wireless multimedia systems [86].

#### 1.4 Contribution of this Dissertation

This dissertation mainly focuses on how to reduce the energy consumption of soft real-time embedded systems by employing dynamic voltage scaling while still delivering the user required quality of service. Fig. 1.1 shows the overview of my Ph.D. research.

Figure 1.1: The overview of my Ph.D. research.

The main contributions of this dissertation are as follows:

- we have proposed a new design methodology, i.e. probabilistic design, for soft real-time embedded systems in order to reduce the system resources while meeting the user required quality of service statistically [54]. One important phase in the probabilistic design flow is offline/on-line resource management. By using energy/power as an example of resources, we have developed a set of system power management techniques by using dynamic voltage scaling to exploit the slack arising from the tolerance to deadline misses in both single and multiple processor systems [52, 53].

- In order to find the best way to use dynamic voltage scaling, we have first formulated the voltage set-up problem and presented practical solutions to this problem in order to minimize the energy consumption of multiple voltage DVS system in the system level [49]. This is a novel extension under current DVS research framework. We have also conducted the case study of provably most energy efficient voltage set-up for dual voltage system with (m,k)-firm deadline guarantee.

- As the traditional completion ratio metric can only be applied to independent tasks, we have proposed a new quality of service (QoS) metric to capture the different deadline types (firm or soft) and task dependency as well [50]. Furthermore, we have developed a set of low run-time overhead on-line scheduling algorithms to improve QoS and more importantly, to enhance quality of presentation (QoP) significantly with no extra hardware [51].

## 1.5 Organization of this Dissertation

The remainder of this dissertation is organized as follows.

In Chapter 2, we propose the novel concept of probabilistic design for soft realtime systems and a methodology to quickly explore such design space at an early design stage. The two important phases in the probabilistic design flow, i.e. estimating the probabilistic timing performance and managing system resources with probabilistic performance guarantee, are discussed in detail. The method takes advantage of soft real-time system's unique features (e.g., tolerance for occasional deadline misses, uncertainties in actual execution time) to relax the rigid hardware requirements for software implementation and eventually avoid over-designing the system.

In Chapter 3, we use energy as the example of system resources to explain how to conduct offline/on-line resource management with quality of service guarantee. Specifically, we developed a set of voltage scheduling techniques by taking the tolerance to deadline misses into account in conjunction with the modest non-determinism in application's execution time. First, we give a simple best-effort approach that achieves the maximum completion ratio; then we propose an enhanced on-line best-effort energy minimization (BEEM) approach and a hybrid offline/on-line completion ratio Q guaranteed energy minimization(QGEM) approach. Simulation results show that significant energy savings for both single and multiple processor systems can be achieved while probabilistically meeting the completion ratio requirements.

In Chapter 4, in order to find the best way to employ DVS, we formulate the voltage set-up problem and provide the practical solutions to minimize the system's energy consumption. Voltage set-up problem is *how many levels and at*  which values should voltage be implemented for the multiple-voltage DVS system to achieve the maximum energy saving. It challenges whether DVS technique's full potential in energy saving can be reached on multiple-voltage systems. In this chapter, (1) we derive analytical solutions for dual-voltage system. (2) For the general case that does not have analytic solutions, we develop efficient numerical methods. (3) We demonstrate how to apply the proposed algorithms on system design. (4) Interestingly, the experimental results suggest that multiple-voltage DVS systems, when the voltages are set up properly, can be very close to DVS technique's full potential in energy saving.

In Chapter 5, as a case study we discuss how to design dual-voltage soft realtime systems with (m,k)-firm guarantee for energy efficiency. We first propose an on-line greedy deterministic scheduler that provides the (m,k)-firm guarantee with the provably minimum energy consumption. We then develop a novel exact method to compute the scheduler's average energy consumption per iteration. This leads us to the numerical solution to the voltage set-up problem, which seeks for the values of the two supply voltages to achieve the most energy efficiency with (m,k)-firm guarantee. Simulation results show that dual-voltage system can reduce significant amount of energy over single voltage system. Our numerical method finds the best voltage set-ups in seconds, while it takes hours to obtain almost identical solutions by simulation.

In Chapter 6, we propose a new quantitative QoS metric based on task completion ratio while differentiating firm and soft deadlines and taking task dependency into consideration. Using the decoding of simulated MPEG movies as an example, we show that the proposed QoS metric is much better than completion ratio in measuring the quality of presentation (QoP) of the movies. However, when replacing the completion ratio by the new QoS metric, popular online algorithms, such as Earliest Deadline First (EDF) and Least Execution Time First (LETF), give only limited improvement on QoP. Therefore, we develop a set of online schedulers with low overhead to enhance QoP significantly, particularly when the system is overloaded.

Chapter 7 concludes this dissertation with a summary of my Ph.D. research work. Some possible directions for future work are also provided.

# Chapter 2

# Probabilistic Design Methodology

### 2.1 Introduction

Soft real-time embedded systems such as multimedia embedded systems are widely used in a lot of areas such as movies, education, entertainment, teleconferencing and information service. These systems require the processing of signal, image, and video data streams in a timely fashion to the end user's satisfaction. Such applications are often characterized by the repetitive processing on periodically arriving inputs, such as voice samples or video frames, and the tolerance to occasional deadline misses without being noticed by human visual and auditory systems. The deadline can be (implicitly) determined by the throughput requirement of the input data streams. For example, in packet audio applications, loss rates between 1% - 10% can be tolerated [15], while tolerance for losses in low bit-rate voice applications may be significantly lower [60]. Furthermore, in many multimedia DSP applications, although the execution time of a task can vary dramatically due to a number of factors such as cache miss(es) or conditional branches, it is possible to obtain the execution time distribution for each task by knowing (e.g., by sampling

technique) detailed timing information about the system or by profiling the target hardware [122].

Prior design space exploration methods for hardware-software codesign of embedded systems, e.g., [32, 44, 83], guarantee no deadline missing by considering worst case execution time (WCET) of each task. As the soft real-time embedded systems can tolerate some violations of timing constraints, these methods will often lead to over-designed systems that deliver higher performance than necessary at the cost of expensive hardware, higher energy consumption, and other system resources.

There are plenty of studies on the estimation of soft real-time system's probabilistic performance when the application's computation time can be varied [48, 59, 122]. However, their goals are to improve system's performance or to provide probabilistic performance guarantees. To the best of our knowledge, there is no reported effort on systematically incorporating application's performance requirements, uncertainties in execution time, and tolerance for reasonable execution failures to guide rapid and economic design of real-time embedded systems.

In this chapter, we study the problem of how to integrate such tolerance to deadline misses into the design of soft real-time embedded systems. We propose the novel concept of probabilistic design for soft real-time embedded systems and a methodology to quickly explore such design spaces at an early design stage. Given the execution time distribution of each task and the tolerance to deadline misses (measured by the quantitative completion ratio), we have developed a set of algorithms to estimate the probabilistic timing performance and to manage system resources in such a way that the system achieves the required completion ratio probabilistically with a reduced amount of system resources. This method relaxes

the rigid hardware requirements for software implementation to meet the WCET and eventually avoids over-designing the soft real-time embedded systems. In the next chapter we will use system's energy consumption, one of the most critical resources for soft real-time embedded systems, as an example to demonstrate how our approach can lead to significant energy-efficient designs.

The rest of the chapter is organized as follows: Section 2.2 describes the related work in design space exploration, performance analysis, and low power design techniques. Section 2.3 gives the overview of our probabilistic design space exploration methodology. Our method has two key steps, i.e., the probabilistic timing performance estimation, which is discussed in Section 2.4, and the offline/on-line resource management with the probabilistic performance guarantee, which is introduced in Section 2.5. We conclude the paper in Section 2.6.

### 2.2 Related Work

The most relevant work is on design space exploration and performance analysis, probabilistic performance estimation, and scheduling techniques for low power.

An integrated hardware-software codesign system should support design space exploration with optimization [33]. There are several works on performance analysis for design space exploration based on monoprocessor architecture. In PMOSS [32], the authors presented a methodology for rapid analysis, synthesis and optimization of embedded systems by providing modularity. Henkel and Ernst [44] have presented high-level estimation techniques for the hardware effort and hardware/software communication time. They claimed that the proposed techniques are well suited for fast design space exploration. In the LYCOS system [83], the authors used profiling techniques and evaluations of low-level execution time for

hardware, software and communication to estimate the system performance. For the rapid prototyping of hardware-software codesigns, Chatha and Vemuri [25] introduced their performance evaluation tool to provide fast and accurate performance estimates based on profiling and scheduling. However, all of the above works specify the deadline as one of the design constraints that has to be met.

There are several papers on the probabilistic timing performance estimation for soft real-time systems design [48, 59, 122]. The general assumption is that each task's execution time can be described by a discrete probability density function that can be obtained by applying path analysis and system utilization analysis techniques [84]. In [122], the authors extended the scheduling algorithms and schedulability analysis methods developed for periodic tasks in order to provide probabilistic performance guarantee for semi-periodic tasks when the total maximum utilization of the tasks on each processor is larger than one. They described the transform-task method that transforms each semi-periodic task into a periodic task followed by a sporadic task. The method can provide an absolute guarantee for requests with shorter computation times and a probabilistic guarantee for longer requests. In [59], a performance estimation tool that outputs the exact distribution of the processing delay of each application was introduced. It can help the designers develop multimedia networked systems requiring soft real-time guarantees in a cost efficient manner. Given that the execution time of each task is a discrete random variable, Hu et al. [48] proposed a state-based probability metric to evaluate the overall probabilistic timing performance of the entire task set. Their experimental results show that the proposed metric reflects well the timing behavior of systems with independent and/or dependent tasks. However, their evaluation method becomes very time consuming when the task has many different execution time values.

Low power consumption is one of the most important design objectives. Power is proportional to the square of the supply voltage, therefore, reducing supply voltage can result in great power saving. Dynamic voltage scaling (DVS), which varies the clock frequency and supply voltage according to the workload at run-time, can achieve the highest possible energy efficiency for time-varying computation load [18]. For the literature review of DVS research, one can check the Section 1.2 in this dissertation.

# 2.3 Probabilistic Design Methodology Overview

Many design methods have been developed based on WCET to meet the timing constraints without any deadline misses. However, the actual execution time of each task frequently deviates from its WCET, sometimes by a large amount. Therefore these methods are pessimistic and are suitable for developing systems in a "hard real-time" environment, where any deadline miss will be catastrophic. However, there are also many "soft real-time" systems, such as multimedia systems, which can tolerate occasional deadline misses. The above pessimistic design methods can't take advantage of this feature and will often lead to over-designed systems. In order to avoid over-designing systems, we propose the concept of "probabilistic design" where we design the system to meet the timing constraints of periodic applications statistically. That is, the system may not guarantee the completion of each execution or iteration, but it will produce sufficiently many successful completions over a large amount of iterations to meet the user-specific completion ratio. Or even better, the probability that any execution will be completed is not lower than the desired completion ratio.

Clearly, the proposed "probabilistic design" will be preferred for many embedded systems such as portable multimedia systems where high portability, low power consumption, and reasonably good performance are equally important. However, the corresponding "probabilistic design space" becomes larger than the above mentioned pessimistic design space because it includes designs that fail some iterations while still meeting the desired completion ratio requirement statistically. This increases the design complexity and makes early design space exploration difficult. The "probabilistic design" will thrive only when designers can quickly explore the larger probabilistic design spaces.

Figure 2.1 depicts our probabilistic design space exploration approach for rapid and economic multimedia system design. We start with the popular dataflow graph representation of the embedded software, the system's performance requirements (in terms of timing and completion ratio constraints), and a pool of target system architectures to select from. We partition the application into a set of tasks and use profiling tools to collect detailed execution information of each task. Next, we estimate the system timing performance to check whether it is feasible for the current system configuration to achieve the desired performance. If not, we change the hardware configuration and/or apply software optimization techniques and update the software profiling results that will be used in the next round of system timing performance estimation. We mention that any change on the target hardware configuration and/or software optimization may affect the application's actual execution information and therefore the software profiling process needs to be re-started. This iterative design loop terminates when all the design requirements are met.

Once the completion ratio constraint can be met, we move on to the phase of

Figure 2.1: Design flow in the probabilistic design methodology.

offline/on-line resource management. This is the key step in the proposed probabilistic design where we 1) allocate minimum system resources to each task offline in order to make the desired completion ratio probabilistically achievable, and 2) develop real time schedulers to manage the resources at run time such that the required completion ratio can be achieved probabilistically. Finally, we conduct system synthesis, simulation, and evaluation before prototyping the system.

# 2.4 Estimating the Probabilistic Timing Performance

In order to determine whether a given system implementation can meet the desired completion ratio constraint, we need to estimate the system's probabilistic timing performance. Specifically, in this step we calculate the upper bound of the completion ratio that the system with current configuration can achieve to help us in exploring the probabilistic design space efficiently.

We consider the task graph G = (V, E) for a given application. V is the set of vertices in the graph that represent the task computations and E is the the set of directed edges that represent the data dependencies between vertices. We adopt the assumption that the execution time of each vertex can be described by a discrete probability density function [48, 122]. Specifically, for each vertex  $v_i$ , we associate a finite set of possible execution times  $\{t_{i,1}, t_{i,2}, \dots, t_{i,k_i}\}$  (under a reference system configuration) and the set of probabilities  $\{p_{i,1}, p_{i,2}, \dots, p_{i,k_i} | \sum_{l=1}^{k_i} p_{i,l} = 1\}$  that such execution times will occur at run-time. That is, with probability  $p_{i,j}$ , vertex  $v_i$  requires an execution time of  $t_{i,j}$ . Such statistics on task's execution time can be obtained by profiling tools.

The completion time of the task graph G (or equivalently the given application) under a fixed execution order  $\langle v_1v_2\cdots v_n\rangle$ , is the sum of each vertex's runtime execution time  $e_i$ :  $C(\langle v_1v_2\cdots v_n\rangle)=\sum_{i=1}^n e_i$ . The deadline constraint  $\mathcal{D}$  specifies the maximum time allowed to complete the application. The application (or its task graph) will be executed periodically and its period is no less than the deadline  $\mathcal{D}$ . We say that an iteration is successfully completed if  $C(\langle v_1v_2\cdots v_n\rangle)$   $\leq \mathcal{D}$ . The performance requirement is measured by a real-valued completion ratio  $\mathcal{Q}_0 \in [0,1]$ , which is the minimum ratio of completions that the system has to maintain over a sufficiently large number of iterations. For the hard real-time system,  $\mathcal{Q}_0 = 1$ ; and for the soft real-time system,  $\mathcal{Q}_0 < 1$ . Let K be the number of successfully completed iterations over a total of N >> 1 iterations, the actual completion ratio can be denoted by  $\mathcal{Q} = \frac{K}{N}$ . We say that the completion ratio constraint is achievable if  $\mathcal{Q} \geq \mathcal{Q}_0$ .

For a given system configuration, let  $t'_{i,j_i}$  be the time to execute task  $v_i$  that requires an execution time  $t_{i,j_i}$  under the reference configuration, where  $j_i \in \{1, 2, \dots, k_i\}$ , we have a completion if the completion time is less than the deadline, that is,  $\sum_{i=1}^{n} t'_{i,j_i} \leq \mathcal{D}$ . The probability that this occurs is  $\prod_{i=1}^{n} p_{i,j_i}$ . Therefore, we have

**Theorem 2.1.** The maximum achievable completion ratio is given by:

$$Q^{max} = \sum_{\sum_{i=1}^{n} t'_{i,i} \le \mathcal{D}} \prod_{i=1}^{n} p_{i,j_i}$$

(2.1)

where the sum is taken over the execution time combinations that meet the deadline constraint  $\mathcal{D}$  and the product computes the probability each such combination happens.

This is similar to the state-based feasibility probability defined in [48].  $Q^{max}$  helps us to quickly explore the probabilistic design space. Specifically, if  $Q^{max}$

$Q_0$ , which means that the completion ratio requirement is not achievable under current system configuration, we can make the early and correct decision to reconfigure the hardware or optimize the software implementation rather than further investigating the current system configuration.

The drawback of this estimation is that Equation (2.1) is computationally expensive particularly when there are many tasks and each task has multiple execution times. For example, a task graph with 50 vertices and each vertex having only the best, average, and worst case execution time yields  $3^{50}$  different execution time combinations! Due to the importance of determining whether the required  $Q_0$  is achievable in designing fast probabilistic design space exploration techniques, we have developed the following polynomial heuristic.

Assuming that the task's execution times under the reference configuration are ordered such that  $t_{i,1} < t_{i,2} < \cdots < t_{i,k_i}$ , we define the prefix sum of the occurrence probability

$$P_{i,l_i} = \sum_{i=1}^{l_i} p_{i,j} \tag{2.2}$$

which measures the probability that the computation at vertex  $v_i$  is not longer than  $t_{i,l_i}$ . If we allocate time  $t_{i,l_i}$  to task  $v_i$  and drop the iteration if its actual execution time is longer, then we achieve a completion ratio

$$Q = \prod_{i=1}^{n} P_{i,l_i} = \prod_{i=1}^{n} \sum_{j=1}^{l_i} p_{i,j}$$

(2.3)

We use a greedy approach to estimate whether completion ratio  $Q_0$  can be achieved within the deadline  $\mathcal{D}$ . First, we assign each vertex its WCET. This yields Q = 1 but the total assigned completion time  $\sum_{i=1}^{n} t_{i,k_i}$  will most likely exceed the deadline constraint. From Equation (2.3), if we cut the time slot of vertex  $v_i$  from  $t_{i,l_i}$  to  $t_{i,(l_i-1)}$ , the completion ratio will be reduced by the factor of  $\frac{P_{i,(l_i-1)}}{P_{i,l_i}}$  and the total assigned time will be reduced by  $t_{i,l_i} - t_{i,(l_i-1)}$ . We iteratively

cut the time slot of vertex  $v_j$  that yields the largest  $(t_{j,l_j} - t_{j,(l_j-1)}) \cdot \frac{P_{j,(l_j-1)}}{P_{j,l_j}}$  as long as it gives a completion ratio larger than  $\mathcal{Q}_0$ . This greedy selection approach frees more assigned time slot at the minimum level of completion ratio reduction. When we cannot reduce the completion ratio any further and the total assigned time  $\sum_{i=1}^n t_{i,l_i}$  is not larger than the deadline  $\mathcal{D}$ , our heuristic will conclude that the required  $Q_0$  is achievable. Otherwise, it will report that  $Q_0$  cannot be guaranteed, even though in some cases  $\mathcal{Q}^{max}$  is actually larger than  $\mathcal{Q}_0$ . The complexity of the proposed heuristic is  $O(n^2)$ .

# 2.5 Managing System Resource under Probabilistic Performance Constraint

When  $Q^{max} \geq Q_0$ , it becomes theoretically possible to deliver the probabilistic performance guarantee (in terms of completion ratio) with the current system configuration. The resource management phase in our design space exploration aims to reduce the design cost. Specifically, we are given a task graph corresponding to the application that includes a set of vertices (tasks), each of which represents certain computation, and a set of directed edges, each of which represents data dependency. Each task has a finite set of possible execution time, which can be obtained by profiling or simulation on target hardware. Based on the above information together with the deadline constraint  $\mathcal{D}$  and user required QoS  $Q_0$ , we want to 1) determine the minimum system resource required to provide the probabilistic performance guarantee; and 2) develop on-line scheduling algorithms to guide the system to achieve such guarantee at run time with the determined minimum resource.

As energy consumption has emerged as one of the most important concerns in the design of embedded systems particularly for the battery-operated portable systems, in this dissertation we consider energy as one example of resource to manage and present our newly developed offline/on-line energy reduction techniques with completion ratio guarantee. We achieve the energy saving by the dynamic voltage scaling method on multiple supply voltage and multiple threshold voltage system, which has been identified by the International Technology Roadmap for Semiconductors (ITRS) as the trend of future systems [2]. Specifically, we consider the following problem:

For a given task graph, its deadline, its completion ratio constraint and the task execution time distribution, find a scheduling strategy for a multiple voltage system such that the resource (e.g., energy) consumed to satisfy the completion ratio constraint is minimized.

In the next chapter, we will present our recent results on energy/power management methods for both single and multiple processor systems in order to minimize the system energy consumption while meeting user required completion ratio.

## 2.6 Conclusions

In this chapter we present the novel concept of probabilistic design for soft real-time embedded systems and a methodology to quickly explore such design spaces at the early design stage in order to rapidly achieve economic system design. By taking advantage of soft real-time DSP application's unique features, namely application's performance requirements, uncertainties in execution time, and tolerance for reasonable execution failures, our method systematically relaxes the rigid hardware

requirements for software implementation and eventually avoids over-designing the system. There are two key steps in our probabilistic design methodology, which are the probabilistic timing performance estimation and the offline/on-line resource management. In this chapter, we have introduced our heuristic method to rapidly estimate the probabilistic timing performance. In the next chapter, we will show how to design soft real-time embedded systems with reduced resource (energy consumption in our case) while providing the desired performance (completion ratio) statistically.

# Chapter 3

# Energy Reduction Techniques for Single and Multiple Processor Systems

In Chapter 2, we propose a probabilistic design methodology to avoid over-designing the systems. One important step in the design flow (see Fig. 2.1) is offline/on-line resource management. In this chapter, by using energy as one example of resource, we show how to reduce the system resource while the system still meets the user required quality of service (completion ratio).

# 3.1 Introduction

Performance guarantee and energy efficiency are becoming increasingly important for the design of embedded systems. Traditionally, the worst case execution time (WCET) is considered to provide performance guarantee, however, this often leads to over-designing the system (e.g., more hardware and more energy consumed than necessary), We discuss the problem of how to implement single or multiprocessor embedded systems to deliver performance guarantee with reduced energy consumption.

Many applications, such as multimedia and digital signal processing (DSP) applications, are characterized by repetitive processing on periodically arriving inputs (e.g., voice samples or video frames). Their processing deadlines, which are determined by the throughput of the input data streams, may occasionally be missed without being noticeable or annoying to the end user. For example, in packet audio applications, loss rates between 1% - 10% can be tolerated [15], while tolerance for losses in low bit-rate voice applications may be significantly lower [60]. Such tolerance gives rise to slacks that can be exploited when streamlining the embedded processing associated with such applications. Specifically, when the embedded processing does not interact with a lossy communication channel, or when the channel quality is high compared to the tolerable rate of missed deadlines, we are presented with slacks in the application that can be used to reduce cost or power consumption.

Typically, slacks arise from the run-time task execution time variation and can be exploited to improve real-time application's response time or reduce power. For example, Shin and Choi used fixed priority scheduling method to achieve power reduction by exploiting slack times in real-time systems [117]. Bambha and Bhattacharyya examined voltage scaling for multiprocessor with known computation time and hard deadline constraints [8]. Luo and Jha presented a power-conscious algorithm [79] and static battery-aware scheduling algorithms for distributed real-time battery-powered systems [80]. Zhu et al. introduced the concept of slack sharing on multi-processor systems to reduce energy consumption [130]. The essence

of these works is to exploit the slacks by using voltage scaling to reduce energy consumption without suffering any performance degradation (execution failures).