**ABSTRACT**

Title of Document: ULTRA LOW POWER FSK RECEIVER

AND RF ENERGY HARVESTER

Bo Li, Doctor of Philosophy, 2012

Directed By: Professor Neil Goldsman

sources.

Department of Electrical an Computer

Engineering

This thesis focuses on low power receiver design and energy harvesting techniques as methods for intelligently managing energy usage and energy sources. The goal is to build an inexhaustibly powered communication system that can be widely applied, such as through wireless sensor networks (WSNs). Low power circuit design and smart power management are techniques that are often used to extend the lifetime of such mobile devices. Both methods are utilized here to optimize power usage and

RF energy is a promising ambient energy source that is widely available in urban areas and which we investigate in detail. A harvester circuit is modeled and analyzed in detail at low power input. Based on the circuit analysis, a design procedure is given for a narrowband energy harvester. The antenna and harvester co-design methodology improves RF to DC energy conversion efficiency. The strategy of co-design of the antenna and the harvester creates opportunities to optimize the system power

conversion efficiency. Previous surveys have found that ambient RF energy is spread broadly over the frequency domain; however, here it is demonstrated that it is theoretically impossible to harvest RF energy over a wide frequency band if the ambient RF energy source(s) are weak, owing to the voltage requirements. It is found that most of the ambient RF energy lies in a series of narrow bands.

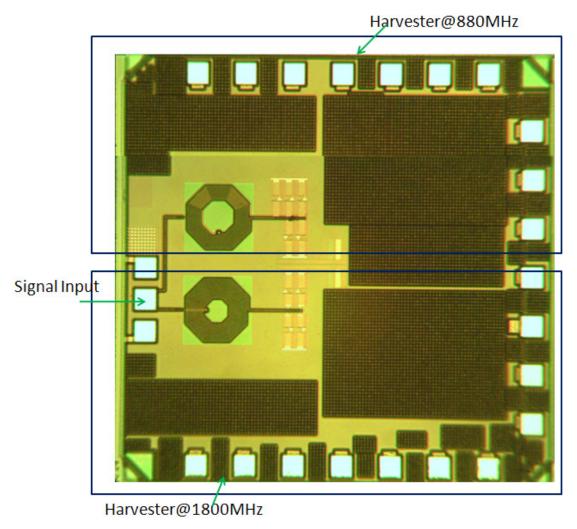

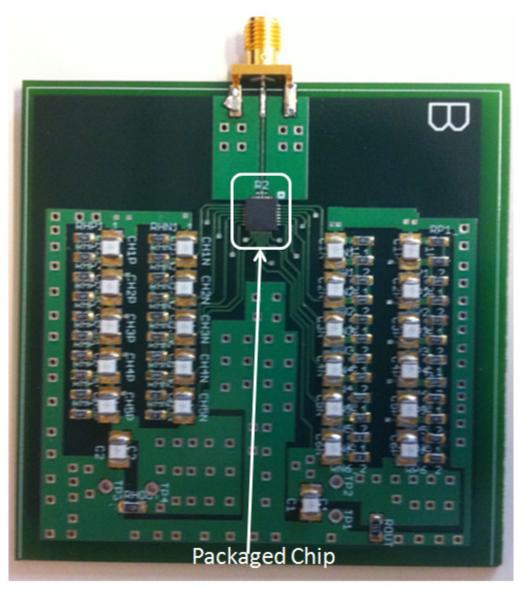

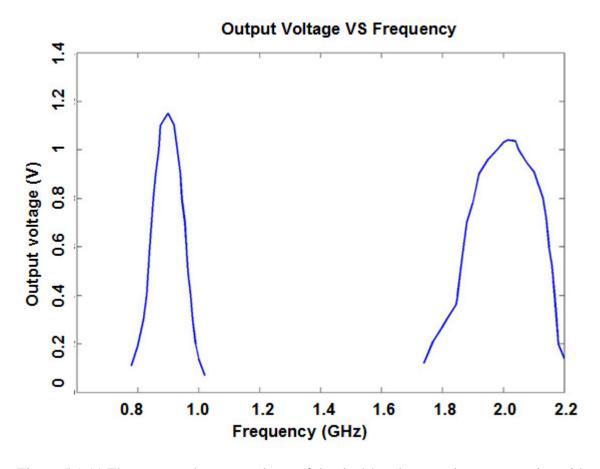

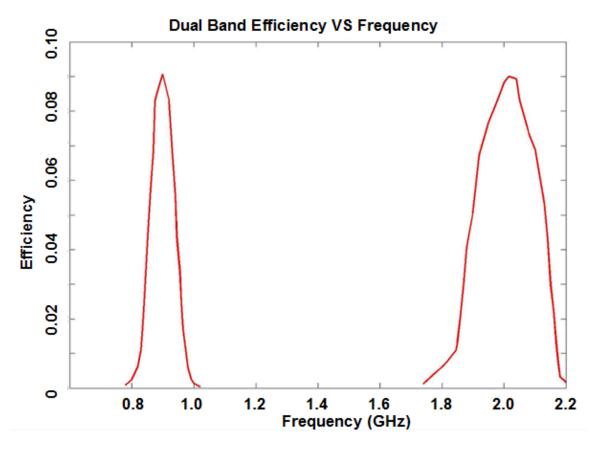

Two different versions of harvesters have been designed, fabricated, and tested. The simulated and measured results demonstrate a dual-band energy harvester that obtains over 9% efficiency for two different bands (900MHz and 1800MHz) at an input power as low as -19dBm. The DC output voltage of this harvester is over 1V, which can be used to recharge the battery to form an inexhaustibly powered communication system.

A new phase locked loop based receiver architecture is developed to avoid the significant conversion losses associated with OOK architectures. This also helps to minimize power consumption. A new low power mixer circuit has also been designed, and a detailed analysis is provided. Based on the mixer, a low power phase locked loop (PLL) based receiver has been designed, fabricated and measured.

A power management circuit and a low power transceiver system have also been co-designed to provide a system on chip solution. The low power voltage regulator is designed to handle a variety of battery voltage, environmental temperature, and load conditions. The whole system can work with a battery and an application specific integrated circuit (ASIC) as a sensor node of a WSN network.

#### ULTRA LOW POWER FSK RECEIVER AND RF ENERGY HARVESTER

By

Bo Li

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2012

Advisory Committee: Professor Neil Goldsman, Chair/Advisor Martin Peckerar Shuvra S. Bhattacharyya Pamela Abshire Drew Baden (Dean's Representative) © Copyright by Bo Li 2012 To my parents for their encouragement, love, and support

### Acknowledgements

I would like to acknowledge people who have contributed to the projects and helped me during my Ph.D. study and research.

The first person I want to thank is my advisor, Professor Neil Goldsman. I want to thank him not only because of his broad knowledge and his profound insights, but also because of his decent, warm, sensitive, and caring personality. He gave me a promising and significant research project, strong encouragement, and full support. I would like to thank him for his trust and confidence in me and his appreciation of my work.

I wish to thank Drs. Yiming Zhai and Bo Yang, who gave me a lot of help when I started the project. They have spent an enormous amount of time to help me on the usage of the RFDE simulator and cadence layout tool.

I gladly express my gratitude to Drs. Thomas Salter, Chung-Ching Shen, Xi Shao, Akin Akturk, Siddharth Potbhare, and Zeynep Dilli as well as Mr. Timir Datta for their kind assistance and useful discussions in the smart dust project. Without them struggling with me together, this dissertation would not have been possible right now.

I wish to thank Professors Martin Peckerar, Shuvra S. Bhattacharyya, Pamela Abshire, and Drew Baden for serving on my dissertation exam committee.

I also wish to thank all my friends, especially Stephen Schwartz, Ke Zhang, Daniel Jontof-Hutter, Bo Yang, etc. Without their friendship and consistent help, I could hardly have finished my Ph.D.

Finally, I give my sincere gratitude to my parents for their unconditional support and love.

## Table of Contents

| Acknowledgements                                                             | iii |

|------------------------------------------------------------------------------|-----|

| Chapter 1: Introduction                                                      |     |

| 1.1 Motivation                                                               |     |

| 1.1.1 Challenges of Energy Needs for Wireless Devices                        | 1   |

| 1.1.2 Strategy                                                               |     |

| 1.2 Review of Energy Harvesting Technology                                   |     |

| 1.2.1 Overview                                                               |     |

| 1.3 Review of Low cost, Low Power Receiver Design Methods                    |     |

| 1.3.1 Receiver Architecture Background                                       |     |

| 1.3.2 Low Data Rate, Weak Interference-Rejection, Ultra Low Power            |     |

| Applications                                                                 | 15  |

| 1.3.3 This work: PLL Based FSK Architecture                                  |     |

| 1.4 Summary of Contributions                                                 |     |

| 1.5 Thesis Organization                                                      |     |

| Chapter 2: Low Power Receiver                                                |     |

| 2.1 Overview of the Low Power Receiver Architecture                          |     |

| 2.2 Low Power Mixer Architecture                                             |     |

| 2.2.1 PLL Architecture                                                       |     |

| 2.2.2 Overview of Different Mixer Architectures                              |     |

| 2.2.2 Down-Conversion Mixer Topology                                         | 31  |

| 2.2.3 Design and Analysis of the New Mixer                                   |     |

| 2.2.4 Characteristics of the Mixer                                           |     |

| 2.2.5 Phase Detector                                                         | 42  |

| 2.2.6 Summary                                                                |     |

| 2.3 Low Power VCO Design                                                     |     |

| 2.4 Phase Locked Loop and Its Applications: Background                       |     |

| 2.4.1 Theoretical Study of PLL Based Receiver Architecture                   |     |

| 2.5 Receiver Selectivity                                                     |     |

| 2.6 Receiver Sensitivity                                                     | 60  |

| 2.7 Receiver Measurement                                                     | 62  |

| 2.8 Conclusion                                                               | 68  |

| Chapter 3: Integrated OOK Transceiver with On-Chip Voltage Regulator         | 70  |

| 3.1 Introduction                                                             |     |

| 3.2 Integrated Transceiver System                                            | 72  |

| 3.3 Transceiver Circuit Designs                                              | 74  |

| 3.3.1 Integrated Voltage Regulator                                           | 74  |

| 3.3.1.1 CMOS Based Voltage Reference Circuit                                 | 74  |

| 3.3.2 Receiver Design                                                        | 80  |

| 3.3.3 Simulation Results of the Transceiver System with Power Management     | 104 |

| 3.4 Measured Results                                                         | 107 |

| 3.5 Conclusions                                                              | 109 |

| Chapter 4: Voltage Doubler Analysis and Theory of Dual-/Multi-Band RF Energy |     |

| Harvesters                                                                   | 111 |

| 4.1 Overview of Power Harvesting Concept                                     | 111 |

| 4.1.1 Motivation in Relation to Wireless Device Power Needs                  | 111 |

| 4.1.2 Viability of Available Ambient Energy Sources                       | . 112 |

|---------------------------------------------------------------------------|-------|

| 4.1.3 Review of Previous RF Energy Harvesting Work                        | . 113 |

| 4.1.4 Characteristics of Available RF Ambient Energy Sources              | . 118 |

| 4.1.5 Strategy                                                            |       |

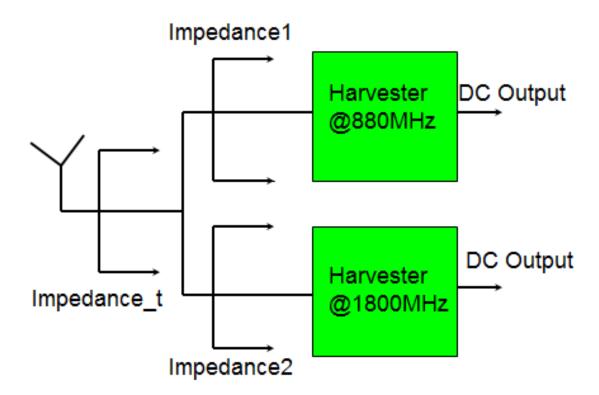

| 4.2 Dual-/Multi-Band Parallel Energy Harvester                            | . 120 |

| 4.2.1 Narrowband Energy Harvesting Techniques                             |       |

| 4.2.2 Wideband Energy Harvesting Limitations                              |       |

| 4.2.3 Analysis of Multiband Energy Harvesting                             |       |

| 4.3 Summary                                                               | . 148 |

| Chapter 5: Dual-/Multi-Band RF Energy Harvester Design                    | . 151 |

| 5.1 Dual-/Multi-Band Energy Harvester                                     | . 151 |

| 5.1.1 Design Specifications                                               | . 151 |

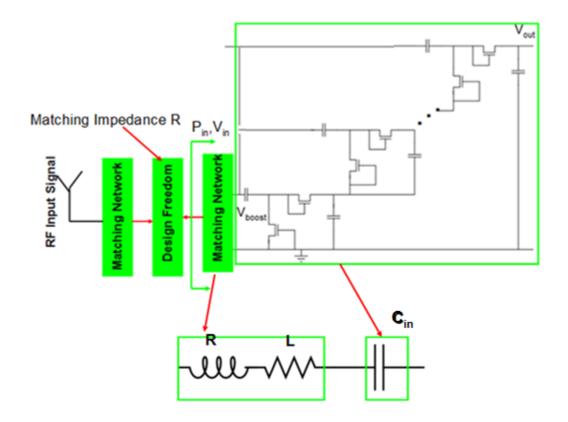

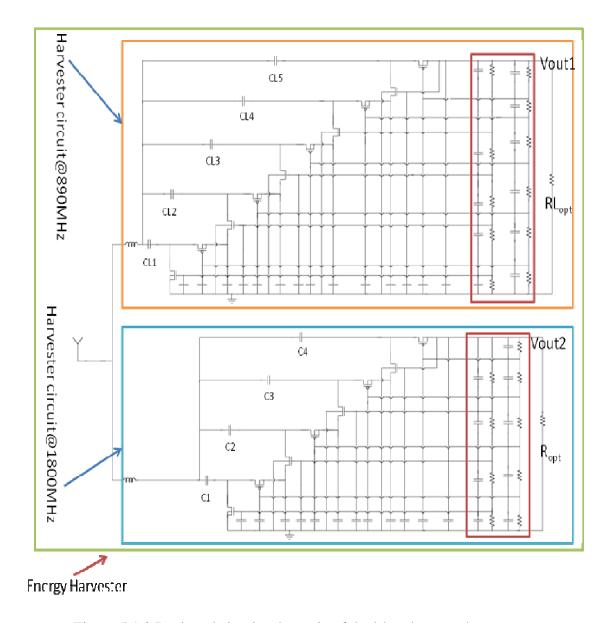

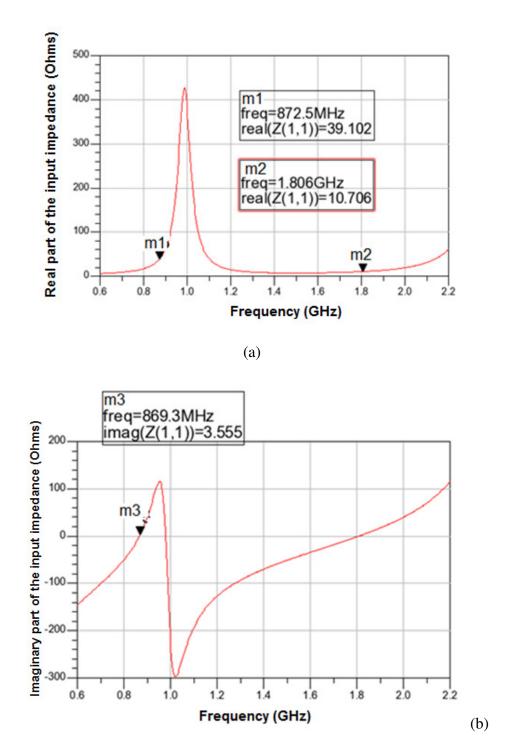

| 5.1.2 Design for Dual-/Multi-band Energy Harvesting                       | . 152 |

| 5.1.3 Dual-band Monopole Antenna Design and Fabrication                   | . 163 |

| 5.1.4 Measurement and Design Achievements                                 | . 166 |

| 5.2 Dual-Band Antenna Coupled RF Energy Harvester                         | . 171 |

| 5.2.1 Design of Antenna-Coupled Dual-Band Energy Harvester and Simulation |       |

| Results                                                                   | . 172 |

| 5.2.2 Antenna Design and Simulation Results                               | . 177 |

| 5.3 Summary:                                                              | . 179 |

| Chapter 6: Future Work                                                    | . 183 |

| 6.1 Super-regenerative receiver                                           | . 183 |

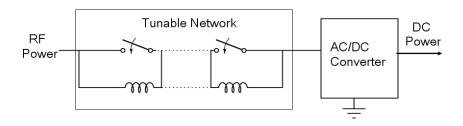

| 6.2 Tunable energy harvester                                              | . 185 |

| Appendix A                                                                | . 187 |

| Appendix B: Lump Model Extraction of on-chip Inductor                     | . 190 |

| Appendix C                                                                |       |

| Appendix D (Inductor and Capacitor Real Layout Effects)                   | . 195 |

| Reference                                                                 | . 198 |

## **Chapter 1: Introduction**

### 1.1 Motivation

### 1.1.1 Challenges of Energy Needs for Wireless Devices

Wireless technologies greatly shape communication and continue to play ever more important roles in modern society. There are different wireless services that have been rolled out to meet different market requirements. For example, the Global System for Mobile communication (GSM) provides voice services, the Global Positioning System (GPS) provides location information, and Bluetooth provides data transfers over small distances. For all the above services, mobile devices exist that use regular batteries which can be recharged once every few days.

Wireless transceivers are often implemented in mobile devices to access those wireless services. They serve as bridges between the physical and the digital world. Almost all transceivers in mobile devices use batteries as their power sources. In many potential applications, the fact that the batteries must be recharged every few days using currently applied commercial designs is a serious limitation.

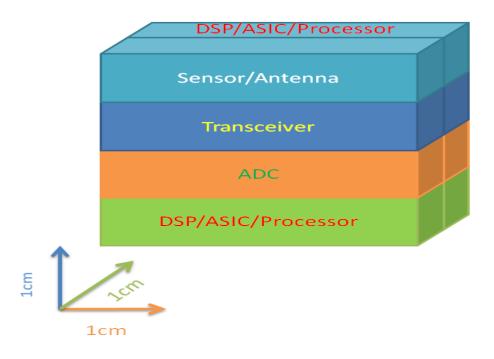

Recently, there has been increased market demand for wireless services such as wireless sensor networks (WSNs) and Smart Dust Systems (SDSs). These systems are typically very low cost wireless ad hoc networks distributed over a relatively small area. These devices sense, transmit, and receive signals. The current infrastructure supports low power protocols such as TDMA [Shen2008]. Figure 1.1.1 shows a SDS node which includes an antenna, transceiver, microprocessor, and ADC. SDSs are characterized by a

low data rate (10 bits/day to 100 Kbits/s), long duration operation (years), and small sizes (1cm<sup>3</sup>) [Cook2006]. These systems are ideal for applications requiring long duration in particular, and some examples are health monitoring, environmental sensing, fire alarms, security, military intelligence and operations, etc. [Salter2009]

For these applications, the mobile devices are required to be left unattendant for several years without the batteries being recharged [Priyantha2002]. Generally, these applications also have volume limitations as well. For example, each node of a SDS system can be required to be housed in less than 1cm<sup>3</sup>. Thus, there exist power application gaps between the transceiver operational power that is desired and the limited battery storage power that can be contained within the required volume. Furthermore, a low cost for each node is commonly required as well.

Figure 1.1.1 Sensor node of a Smart Dust System (SDS).

Two methods have generally been used to address the power gap: alternative power solutions and extremely low power transceiver design. Alternative power sources other than batteries will be discussed briefly below.

Various environment energy sources such as solar, vibrational, and electromagnetic waves (RF energy), etc. exist ambiently. The average power can be as high as mW for solar power and tens or hundreds of uW for vibrational and RF power.

On the other hand, as devices continue to be scaled down to smaller and smaller sizes as Moore's law predicts, the required digital energy to switch digital inverters keeps decreasing as well. For example, the switching power of a minimal size inverter in 65nm CMOS technology is as low as 0.08fW. The required power of a transceiver keeps decreasing as well. Table 1 shows the power consumption of available commercial products [Penella2009]. The required power in the sleep mode has been reduced from 3 uW to 0.06 uW. The low power Zigbee transceiver CC2420 [Penella2009] only consumes 0.06uW in sleep mode.

Table 1: Power consumption of low power transceivers [Penella2009].

| Commercial transceivers | V <sub>cc</sub> (V) | P <sub>active</sub> <sup>a</sup> (mW) | $P_{\text{sleep}}^{a} (\mu W)$ |

|-------------------------|---------------------|---------------------------------------|--------------------------------|

| CrossBow, MicaZ OEM     | 2.1 - 3.6           | 55                                    | 3                              |

| Ember, EM 250/260       | 2.1 - 3.6           | 108                                   | < 3                            |

| FreeScale, MC1320X      | 2.0 - 3.4           | 100                                   | < 3                            |

| Jennic, JN513X          | 2.2 - 3.6           | 102                                   | 0.6                            |

| Atmel, AT86RF230        | 1.8 - 3.6           | 48                                    | 0.3                            |

| TI, CC2420              | 2.1 - 3.6           | 54                                    | 0.06                           |

a. Calculated for Vcc = 3 V.

It is very attractive to attempt to harvest some form of environmental energy to help meet these needs. Alternative power sources may be able to help meet the power lifetime requirements for WSN applications. The sleep mode is not the only consideration, of course. Note, that the data in Table 1 indicates that the *active* power consumption of commercial low transceivers are on the level of tens of milliwatts, which is still tens of times of the largest available environment energy sources. (for what distance) Low power transceivers in a range of 10 meters represent another important and promising solution to meet the power requirements for WSN applications overall. The required energy of nodes of a WSN on each day can be defined as follows:

$$E = [P_{active} \times \eta + (1 - \eta) \times P_{sleep}] \times 86400$$

Where E,  $P_{active}$ ,  $P_{sleep}$ , and  $\eta$  are the required energy for each day, the required device power in active mode and sleep mode, and percentage of the time that the device spends in active mode, times the number of seconds in a day which is 86400, respectively. The power available from the environment on each day is described by Equation 1.2:

$$E_{avail} = 86400 \times \beta \times P_{env}$$

1.2

where  $E_{avail}$ ,  $\beta$ , and  $P_{env}$  are the harvesting energy for each day, the harvesting efficiency, and the average power density in the environment.

The mobile device can function inexhaustibly if Equation 1.3 holds:

$$\begin{split} E_{avail} &\geq E \\ P_{harvester} &= \beta \times P_{env} \geq P_{active} \times \eta + (1 - \eta) \times P_{sleep} \end{split}$$

If  $P_{sleep}$  <  $P_{harvester}$ , Equation 1.3 can always be satisfied by adjusting the percentage of sleep time per day. For a 10 uW environment energy source with 10% power conversion efficiency, and taking  $P_{sleep}$  = 0.06  $\mu$ W as shown in Table 1, and  $P_{active}$  = 1mW, then the percentage of active time will need to be chosen to satisfy Equation 1.4:

$$1 - \eta \le 9.4 \times 10^{-4}$$

The above discussion concludes that mobile devices can work inexhaustibly if they are only awake 0.1% of the time (86.4 second per day). Such a percentage is sufficient for low-data applications such as environmental monitoring, monitoring of bridges and other structures, etc. The percentage of up-time can be increased by a low power transceiver design which consumes even less power than 1mW.

### 1.1.2 Strategy

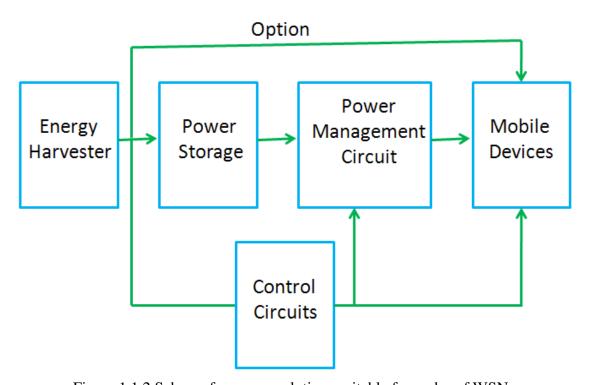

Figure 1.1.2 Scheme for power solutions suitable for nodes of WSNs.

Figure 1.1.2 shows a scheme for future designs of WSN nodes. In this scheme, each node uses harvested energy as a virtual battery. When the devices work in sleep mode, the harvested power is stored and can be used when the devices work in active mode. Furthermore, the low power transceiver needs to be able to maintain low power

consumption in both the active and sleep modes. Most importantly, in sleep mode, the power consumption is required to be less than the harvested power. In this thesis, we follow the above scheme to meet the power requirements for WSN applications.

The strategies used in the thesis can essentially be divided into two different paths based on the scheme. In the first half of the thesis, RF energy harvesting for dual-/multi-band applications has been investigated. In the second half of the thesis, a PLL based ultra-low power receiver has been designed and fabricated which consumes hundred of micro-watts. Finally, a CMOS based transceiver system with on-chip voltage regulators is also provided in the thesis to demonstrate a system on-chip solution.

## 1.2 Review of Energy Harvesting Technology

### 1.2.1 Overview

Large scale energy harvesting such as via windmills, watermills, etc. contributes a significant amount of power for commercial consumption in different countries. These methods have been in place for a long period of time. More recently, there is a trend to harvest environmental energy in a limited volume to enable long term mobile applications such as WSNs. Unlike battery power, the harvested energy can be replenished from the environment all the time. The use of ambient power harvesting strategies is emerging as a promising solution for long term wireless applications such as WSNs.

There are different kinds of ambient energy existing in the environment. Solar, vibrational, thermal, and radio frequency electromagnetic wave energy are some of the ambient power sources that can be utilized [Paradiso2005]. Solar energy has the highest power density in sunny weather, but also displays large variability. Its power density varies from 100uW/cm³ to 100mW/cm³ [Paradiso2005] depending on the weather conditions, incident angles, etc. Photovoltaic devices can convert solar energy into electrical energy with roughly 25% efficiency [Green1986]. [Atwood2001], [Warneke2001], and [Warneke2002] studied the use of solar energy as a power source for WSN nodes, and [Bertacchini2008] has analyzed solar harvester circuit performance. Other recent publications have reported using harvested solar energy to form battery-less nodes for WSN applications, such as [Guilar2006], [Brunelli2009], [Wang2010], and [Chini2010]. While promising, solar energy is not always available.

Vibrational sources have energy densities of ~100 uW/cm³ [Paradiso2005]. [Callaway2004] reports research on harvesting vibrational energy from human activity. A vibrational energy harvesting system has been developed by S Roundy and P. K. Wright [Roundy2004]. The cantilever is fabricated using piezoelectric materials. Piezoelectric materials can convert mechanical energy into electrical energy, or vice versa. However, the vibrational power source is very limited in the environment and often is not suitable for WSN applications.

Thermoelectric devices can harvest energy from objects at different temperatures. The conversion efficiency is limited by the Carnot efficiency [Feynman1971]:

$$\eta = \frac{T_H - T_L}{T_H}$$

1.5

Where  $\eta$ ,  $T_H$ , and  $T_L$  are the maximum efficiency, the high and low temperature, respectively, whose difference represents the differential in temperature between device and environment. [Lawrence2002] proposes a method to convert thermal energy into electrical energy, while [Sodana2004, Sodano2009] reports work to convert thermoelectric energy into electrical energy. However, thermal energy is not widely available or practical for WSN applications.

While the above sources have generally been often thought of for energy applications, RF energy can have many applications as for low power electronics as suggested above as well. Moreover, there is tremendous radio frequency energy in urban areas which can be harvested.

One successful use of harvested RF energy as a power sources has been an implementation designed for passive RFID devices [Namjun2005][Weinstein2005]. RFID tags are placed close to RFID readers which transmit RF energy at designed frequency such as 13.56 MHz for near field communication (NFC) applications. There have been medical applications to monitor long term biomedical signals which have used RFID techniques [Qiuting1997][Qiuting1998][Otis2009].

There has also been research on battery-free systems using RF energy [Sample2007][Sample2008]. The literature [Joe1998] has provided a lump model for rectifying diodes. More recently, there have been publications on using RF energy as a virtual battery [Avago] [Hama2002]. Other work also explores the possibility to harvest RF power as a virtual battery [Theeuwes2007]; however, their input power is 0dBm which is much higher than the available ambient RF energy. The literature [Seeman2008] reports a power management circuit for harvested energy. Other work investigates the

interface between a low power harvester and a micro-battery to maximize harvesting power [Paing2009]'s. There have also been studies about the possibility to use RF energy to charge a cell phone battery [Harris2004]. Another recent document reports DC to DC conversion in low power applications with efficiency as high as 70%, which might be usable for providing biasing voltages with high efficiency [Ramadass2007]. Some research work also discussed a method to charge a cell phone battery at high RF frequency to minimize charger size [Sabate2000].

Recent work has studied the feasibility of extracting energy from TV or radio station signals, and their work harvested RF energy at 1.584MHz [Sogorb2008]. The energy density of RF power was reported to be ~0.5  $\mu$ W/cm<sup>2</sup> a kilometer away from a TV tower [Burch2006]. Other reports RF energy density from 0.1  $\mu$ W to 9.5  $\mu$ W for different sources such as a TV tower, radar, etc [Khalaf]. Other work reports a similar amount of environment RF power [Fields]. The antenna effective area is given by [Balanis2005]:

$$A_{eff} = \frac{1}{8}\lambda^2 = \frac{1}{8}(\frac{c}{v})^2$$

Assuming the frequency of the RF source is 900MHz, the available power is given by:

$$P = P_{den} A_{eff} = \frac{1}{8} \left(\frac{c}{v}\right)^2 P_{den}$$

1.7

Where P is the available power and  $P_{den}$  is the power density of the RF power source, which was 0.5 uW/cm<sup>2</sup> at a distance of 1 kilometer from a TV tower [Burch2006]. The total available power is 69.4  $\mu$ W (-11.58 dB).

A previous energy survey [Salter2009] shows a range of -30 to -20 dBm of power on average in the Baltimore/DC area. These sources are widely available in urban/suburban

areas and thus represent promising power sources for energy harvesting. Cascade voltage doublers (voltage multipliers) have been used to convert RF energy into DC energy. Previous research [Salter2009][Yao2005][Tan2005] has focused on boosting the input voltage for a narrowband frequency to improve the efficiency. In [Texas2010], Texas Instruments also reported that GSM has a RF energy density of  $0.1\mu\text{W/cm}^2$  which corresponds to a RF signal of -30dBm.

RF energy harvesting should be relative natural to integrate with CMOS technology. For example, piezoelectric and thermoelectric components need different processes and rectifier circuits to power the electrical circuits. Moreover, RF power sources have strong and accurate frequency pattern; the output voltage from a RF energy harvester can be very stable as long as the amount of the available power is stable [RFpower].

### 1.3 Review of Low cost, Low Power Receiver

### Design Methods

In addition to energy harvesting, this thesis also explores very low power transceiver designs, especially for WSN and SDS application. Wireless transceivers serve as bridges between the physical and the digital world to access different services and information. Generally, receivers [Tadjpour2001, Shaeffer1998, Samavati2001, Darabi2001, Steyaert2000, Su2002] demodulate the high frequency input signals and extract low frequency digital signals. The demodulated digital signal is further manipulated via digital signal processing and/or an application specific integrated circuit (ASIC) to extract various forms of video or audio information. Transmitters mix the digital information with a high frequency carrier signal at different frequency channels and

radiate the modulated information through an antenna into the air [Darabi2001, Steyaert2000, Su2002, Hegazi2002].

Historically, Gallium Arsenide (GaAs) devices have been widely implemented in RF front-ends due to their high mobility, high break-down voltage, and reliability. However, these devices cannot integrate with the baseband CMOS digital circuits to provide a system on chip solution and are thus relatively costly [Abidi2004].

As CMOS processes are scaled down, CMOS devices have less and less parasitic capacitances and thus are able to operate and obtain current gain at frequencies as high as 100GHz. Considerable research has been conducted to investigate and improve CMOS circuit performance via innovations such as low noise CMOS LNAs, low phase noise LC CMOS oscillators, etc. Due to those efforts, CMOS based RF front-end transceivers have emerged to dominate the commercial marketplace due to their low cost and excellent integration capabilities with digital systems [Abidi2004]. Currently, CMOS based RF solutions can meet the application requirements for most of RF front ends. A CMOS based PA is still under investigation and remains a topic of major interest in RF design. In this thesis, we mainly focus on CMOS based receiver designs.

Wireless application requirements such as data rate, operation distance, sensitivity, power consumption, and cost determine receiver system architectures. Based on the data rate and power requirements, receiver architectures can be roughly divided into low data rate/high sensitivity applications such as GPS which operate globally, low power/low data rate applications such as WSNs, high data rate/moderate sensitivity applications such as WLANs, Ultra Wideband (UWB) transceivers which provide high data rate service in a small area, and extremely spectrum efficient applications such as GSM transceivers

which provide voice services over large areas. A brief overview of the typically selected architectures for each application is detailed below.

GPS receivers require low data rates (50Hz symbol rate) with extremely high sensitivities (-130 dBm) [Shaeffer1998] [Abidi2004]. Super-heterodyne receiver architectures are widely used in GPS applications.

GSM receivers require spectrum efficiency in order to provide services over large areas and provide service access to everyone. They operate within crowded spectrum traffic and thus need excellent anti-interference capabilities to handle blocks. Superheterodyne, Weaver, and direct conversion architectures are generally implemented to suppress/reduce the image interferences as well as high power blocks at adjacent frequency channels [Vassiliou2003][Lee2003].

WLAN and UWB receivers generally require high data rates to enable applications with large data transfers between two local devices or streaming video. They generally have high data rates with relative low sensitivity requirements because of the short distances between devices. Those services also operate within industrial, scientific, and medical (ISM) frequency bands. WLAN devices operate at 2.4-2.48GHz or 5.725-5.825GHz [Samavati2001]. UWB technology employs a wide frequency spectrum between 3.1-10.6 GHz under FCC regulation [Razavi2005].

Commercial receiver architectures are designed specifically with high anti-interference capabilities in order to accommodate more customizations. Direct conversion, and Weaver architectures can greatly suppress interference at image frequencies. The power consumption of these architectures is normally a few tens or even hundreds of mW

[Tadjpour2001, Shaeffer1998, Samavati2001, Darabi2001, Steyaert2000, Su2002, Hegazi2002]; thus these designs are not suitable for ultra low power applications.

Super regenerative architectures obtain extremely high voltage gain using positive feedback [Shi2008]. They normally have high gain, low data rates, and low/moderate power consumption [Moncunill-Geniz2005][Chen2007][Shi2008]. This architecture is widely used in non-critical applications such as toys [Shi2008]. Off-chip high quality inductors are commonly used in super-regenerative receivers to improve the system selectivity capability and to obtain lower power consumption. Previous research [Shi2008] reports a super-regenerative receiver using an on-chip inductor with 6.6mW@5GHz and a data rate between 200Kbits/s to 1.2Mbits/s.

On/off key (OOK) architectures are widely implemented for low power applications [Daly2007] due to the simplicity of their receiver designs. OOK architecture only requires a low noise amplifier (LNA) to amplify the signal to a detectable level for the demodulator, such as by a peak detector. OOK demodulators such as peak detectors suffer from large voltage conversion losses (>30 dB) especially under weak signal conditions. They thus require large power amplification at high frequencies. However, high frequency amplification uses considerable power (milliwatt levels). Recently there has been research [Salter2009] on using energy harvesting techniques to lower the OOK demodulation conversion loss, even though the results still show a 30dB loss [Salter2009].

### 1.3.1 Receiver Architecture Background

Depending on the application, the receivers' sensitivities may vary in a wide range from -130 dBm for GPS applications [2] to -70 dBm for some wireless local area network

(WLNA) applications [Samavati2001]. White thermal noise places a physical limitation on the system sensitivities. The thermal noise power per Hz is  $k_BT$ , where  $k_B$  is Boltzmann's constant and T is the temperature in Kelvin. The physical limit of receiver sensitivity is described by equation 2.1:

$$P_{in} = -174dBm/Hz + NF + 10 logB + SNR_{min}$$

2.1

Where -174dBm/Hz is the thermal noise per Hz in decibels. NF is the system noise figure, mainly determined by the first stage of the receiver; the system noise figure can be mathematically described by Friis formulas for noise [Lee2003]. The noise factor is defined as the ratio of the total output noise power to the output noise power due to the input source, and noise figure units are in decibels [Lee2003]. B is the channel bandwidth, and the  $SNR_{min}$  is the required signal to noise ratio for a particular bit error rate. B is closely linked with the data rate.

There are different receiver architectures used to meet different application requirements, such as spectrum efficiency, power consumption, block interference, etc. For example, super heterodyne architectures are widely used in global positioning system (GPS) applications due to high interference (block) rejection capabilities. The details of the super heterodyne, direct conversion, and Weaver architectures can be found in [Lee2003].

# 1.3.2 Low Data Rate, Weak Interference-Rejection, Ultra Low Power Applications

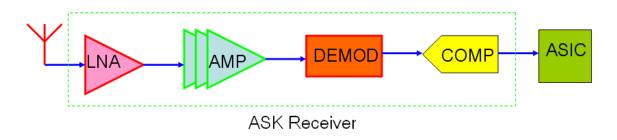

#### 1.3.2.1 ASK Receiver

Figure 1.3.1 shows the block diagram of an amplitude shift key (ASK) receiver. ASK receivers represent the simplest receiver architecture and require minimal circuit blocks. The RF signal is first amplified by LNAs and then demodulated by demodulation circuits such as peak detectors. However, the peak detector has significant conversion loss. A high power gain LNA is thus necessary for high sensitivity applications that have large power consumption.

Recent research [Salter2009] has used energy harvesting voltage doubler techniques to lower the conversion loss; however, a -30dB conversion loss is still reported. Additionally, ASK receivers are spectrum inefficient and have no anti-interference capabilities.

Figure 1.3.1 Block diagram of the ASK receiver.

#### 1.3.2.2 Wake-up Receiver

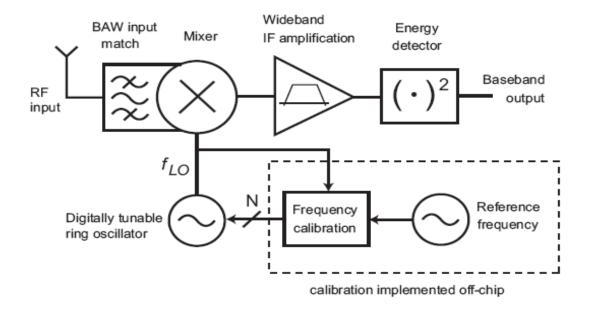

Figure 1.3.2 shows a block diagram of a wake-up receiver [Pletcher2009]. The wake-up receiver does not require a LNA with large power consumption. A mixer is used to convert the high frequency signal into an intermediate frequency (IF). The amplification is performed at the IF frequency to save power. The system sensitivity is generally low due to the lack of amplification and the mixer's high noise figure. A ring oscillator is used due to its low power consumption. However, this receiver structure has no anti-

interference capabilities either. A 100 MHz IF is chosen to overcome the uncertainty of the ring oscillator frequency and its inferior phase noise. A surface acoustic wave (SAW) resonator is used to boost the input voltage and help with interference problems. Reported results show a power consumption of 52 uW with sensitivity of -72 dBm [Pletcher2009].

Figure 1.3.2 Wake up receiver block diagram [Pletcher2009].

## 1.3.2.3 Low Data Rate, Moderate Interference-Rejection, Low Power Application— Super Regenerative Receiver

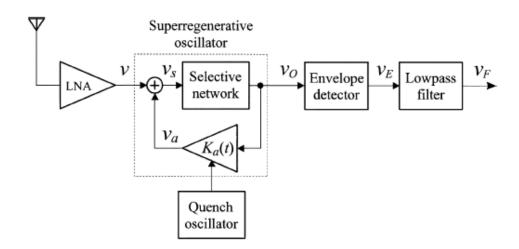

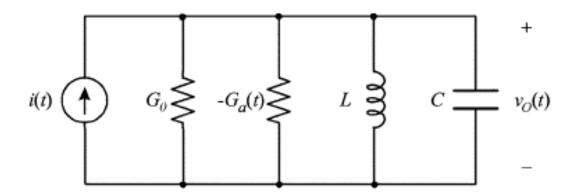

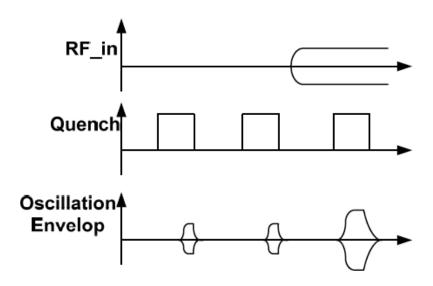

Figure 1.3.3 shows the circuit diagram of a super regenerative receiver [Moncunill-Geniz2005]. In the super regenerative stage, the quench bias signal generates a negative resistor to compensate the intrinsic resistor of inductor to start oscillation. During other times, the signal is quenched. The envelope detector rectifies the oscillator output and filters out the high frequency signal.  $G_m$ -C (transconductor-capacitor) filters are used to

filter out the quench signal and get the demodulation signals. The data rate is less than the quench signal frequency, which is normally less than 500 KHz. The quench signal is a sinusoidal or sawtooth waveform. The data rate of these kinds of receivers is generally low [Moncunill-Geniz2005] and might be suitable for low date rate applications.

Oscillator power consumption is determined by the inductor quality factor. Off-chip inductors (Bulk Acoustic Wave (BAW) devices) have high quality factors that offer low power consumption [Moncunill-Geniz2005]. However, off-chip inductors are costly and also add significant package costs. On-chip inductors offer high integration and low cost but consuming considerable power [Chen2007].

Figure 1.3.3 Super-regenerative receiver architecture [Moncunill-Geniz2005].

### 1.3.3 This work: PLL Based FSK Architecture

We have surveyed various receiver architectures and summarized their features. Table 2 lists the different architectures detailed above along with their pros and cons for various applications [Shi2008]. A major thrust of this thesis is to introduce a new PLL based

receiver architecture for low power applications such as wireless sensor networks as as a very competitive option when low power is required.

Table 2 Comparison of different receiver architectures.

|                         | Pros                                                  | Cons                                                                                                              | Applications                                                                 |

|-------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| OOK architecture        | Easy to implement<br>Low power                        | Poor anti-interference capability Poor selective                                                                  | Non-critical communication<br>Low power WSN network                          |

| PLL architecture        | Low power                                             | Poor anti-interference capability Poor selectivity                                                                | Non-critical communication<br>Low power WSN network                          |

| Super regenerative      | Low power                                             | Moderate selectivity<br>Moderate anti-interference<br>capability                                                  | Short distance, low data rate<br>links<br>Walkie-talkie<br>Radar application |

| Direct conversion       | No image effect<br>High level integration<br>Low cost | DC offset Transmitter noise interference Flick noise Even order distortion I/Q mismatch                           | WLANs Cell phone communication Multi-band cell phone communication           |

| Super heterodyne        | Superior to interference<br>High power<br>consumption | Low integration due to SAW filter High Cost Limited multiband capability due to SAW filter High power consumption | GPS<br>Cell phone<br>WLAN                                                    |

| Wake-up<br>Architecture | Low Power                                             | Poor anti-interference capability Poor selectivity                                                                | Non-critical communication<br>Low power WSN network                          |

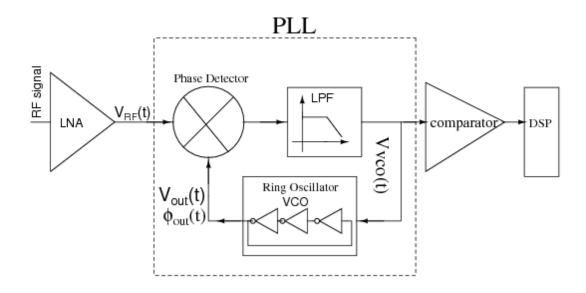

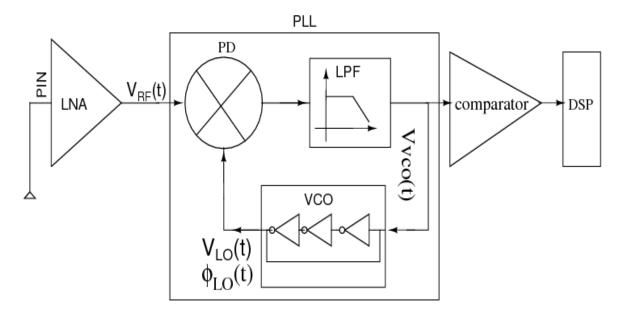

Phase locked loops are widely used in communication circuits as frequency synthesizers. In this work, we investigate their application as natural demodulators for low power receivers. Figure 1.3.4 shows the PLL based receiver architecture. A LNA amplifies the small input signal, and the PLL picks up this signal and compares it with

the local oscillator. This PLL has been integrated with a LNA to work as a RF receiver. The receiver can demodulate both FM and FSK signals. Detailed analysis of this receiver is provided in Chapter 2.

Figure 1.3.4 Block diagram of PLL and its application as an FSK receiver when used with a LNA, comparator, and a DSP.

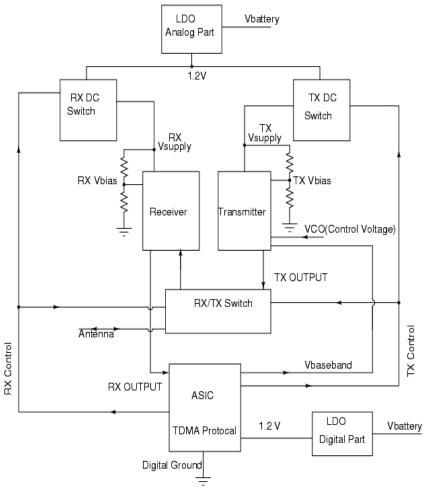

In order to provide an accompanying system on chip solution, we have designed an integrated transceiver system with on-chip power management circuits to handle the battery voltage variation as a part of this work. A voltage regulator is used to integrate with the transceiver to handle the battery voltage variation due to temperature and load. We have also designed a low power OOK transceiver with on-chip integrated power management circuits. The designed integrated transceiver can work as a node in a WSN. This work is reported in Chapter 3.

## 1.4 Summary of Contributions

Our contributions are summarized as follows:

- Multi-band RF Energy Harvesting

- Analysis of voltage doublers.

- o Study of the characteristics of ambient RF power.

- o Study of battery recharging requirements.

- o Provided design specification for energy harvesting in WSN applications.

- o Discussion of theoretical difficulty of wideband energy harvesting.

- Creation of a multi-band energy harvesting scheme that uses energy harvesters connected in parallel for dual-/multi-band energy harvesting.

- Use of on-chip inductors to boost voltage for the 890MHz and 1800MHz bands.

- Use of an improved voltage doubler structure to maximize the conversion efficiency.

- Use of the matching impedance of the antenna and the harvester circuits as a system parameter to optimize the conversion efficiency.

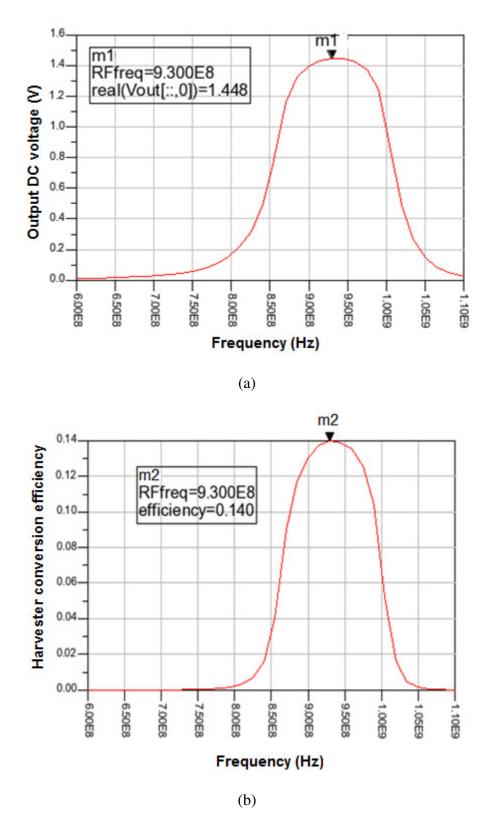

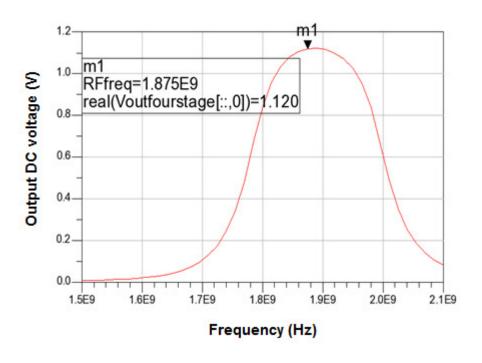

- The harvester achieves 14% conversion efficiency at 890MHz and 13.4% conversion efficiency at 1800MHz. The output voltage is over 1V at both frequencies.

- The design harvester can function as two separate power sources when there is

RF energy at both frequencies.

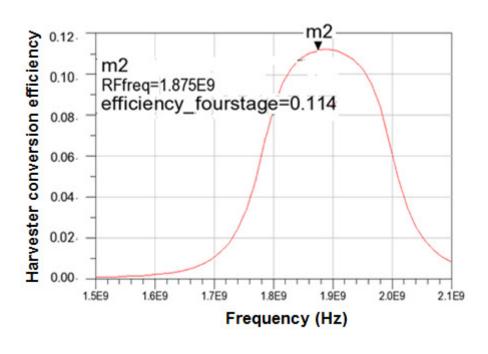

- A planar dual-band monopole has been designed, fabricated, and measured. It has an impedance of 50 Ohms at 890 MHz and 14 Ohms at 1800 MHz, respectively. The antenna structure (e.g., the arm lengths and spacing) can be tuned to adapt to other frequency bands and different impedances.

#### • Dual-band RF Energy Harvesting

- o Dual-band energy harvester for 1800MHz and 2400MHz frequency bands.

- Antenna coupled voltage boosting technique.

- o On-chip inductor voltage boosting technique.

- Loop antenna achieves inductive-like behavior at 1800MHz and impedance-like behavior at 2400MHz to match energy harvester.

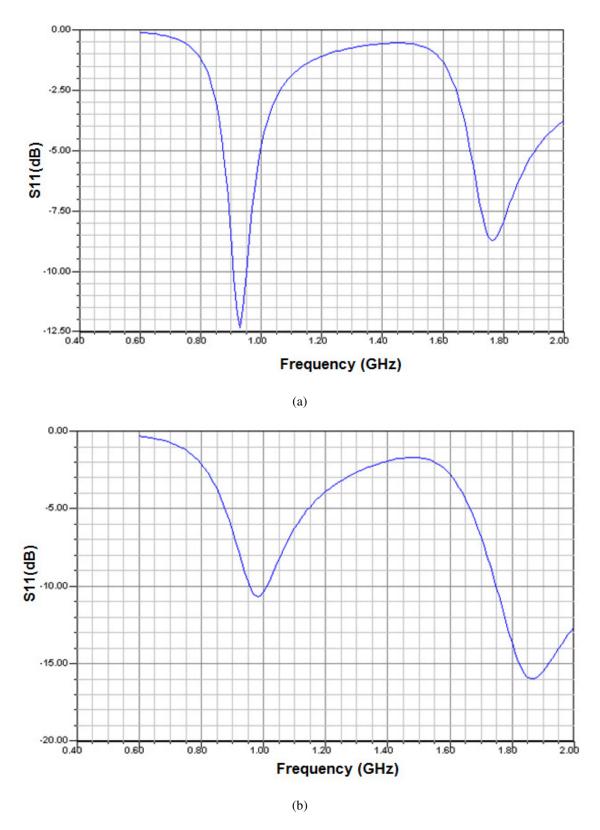

- The simulated efficiency of the harvester is 14.4% at 1800MHz and 12% at 2400MHz.

- Ultra-low power receiver design, fabrication and testing

- Design and analysis of an ultra-low power mixer.

- Analysis of the power limitations of the LC oscillator topology and implement current starving ring oscillator as a VCO.

- A FM/FSK receiver using PLL as a demodulator.

- The power consumption of the PLL can be scaled down as the CMOS technology scales down.

#### Integrated transceiver system

- Pure low power CMOS voltage regulator.

- o Integrated low power OOK transceiver system design.

- o Integrated low power OOK transceiver with voltage regulator co-design

## 1.5 Thesis Organization

The chapters of the thesis are organized as follows:

In Chapter 2, we introduce a new low power mixer architecture. Detailed analysis and design procedures are given as well. We also discuss the LC oscillator power limitations and show that the low quality inductor requires milliwatts of power to enable oscillations. One conclusion is that ring oscillator topology is more suitable for uW power applications. We then discuss the design considerations for a low power phase locked loop and its application as a receiver.

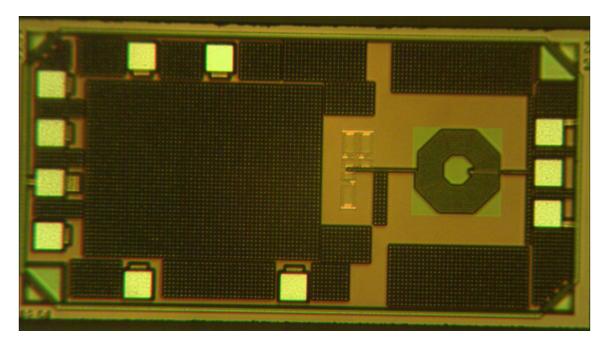

In Chapter 3, we design a highly integrated pure CMOS based transceiver with an onchip voltage regulator. This design can work with a battery to provide a system solution for low power mobile applications. The transceiver system is designed and fabricated in a 2x2 chip die using a pure CMOS process.

In Chapter 4, we model and analyze the voltage doubler circuits. The difficulty of the wideband energy harvesting method under low input power is an aspect of importance. A theoretical analysis of the dual-/multi-band energy harvester is developed.

In Chapter 5, we design dual-/multi-band energy harvesters to fully take advantage of the existing multi-band ambient RF energy. The dual-/multi-band energy harvester is codesigned with dual-/multi-band antennas to maximize the harvested energy.

In Chapter 6, we discuss possible future extensions of this work on low power receiver architecture, such as a super-regenerative receiver and a method for low power energy harvesting such as by using a tunable energy harvester.

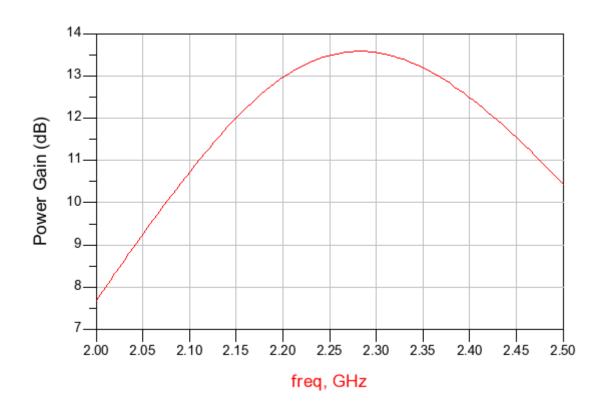

## **Chapter 2: Low Power Receiver**

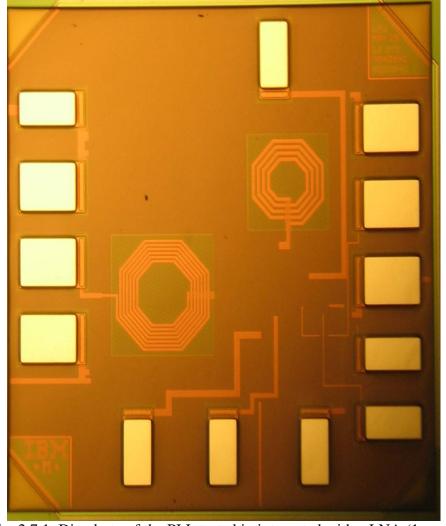

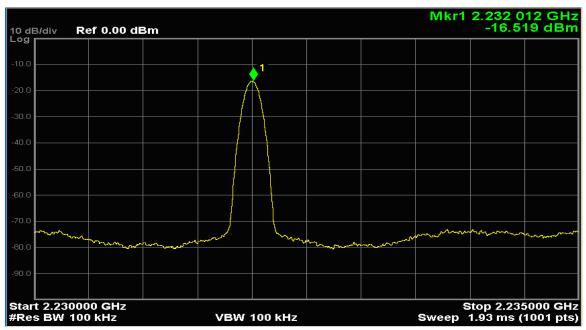

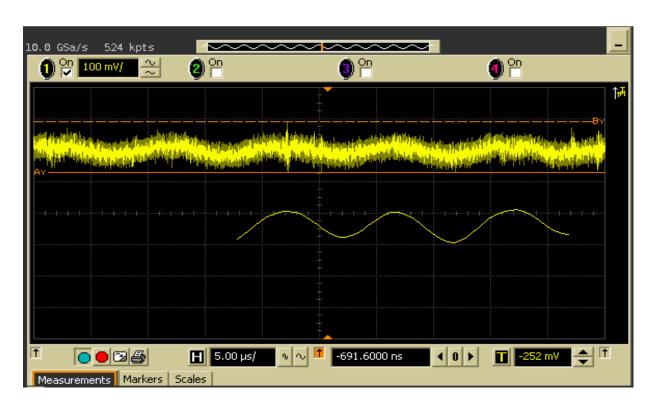

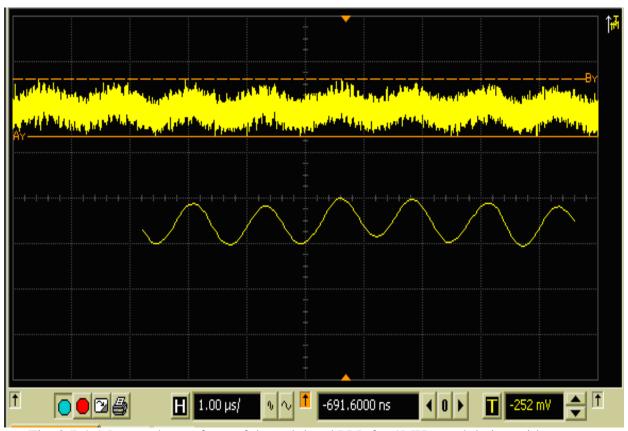

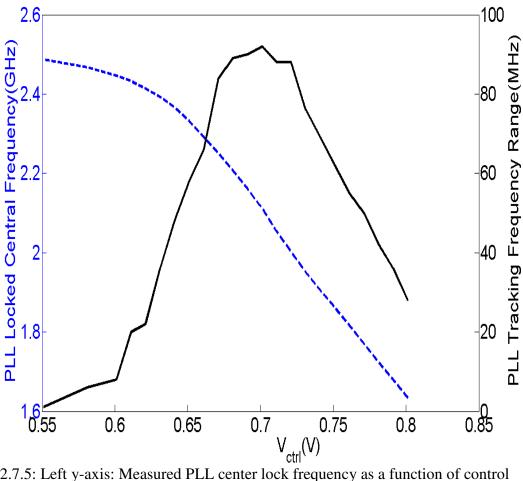

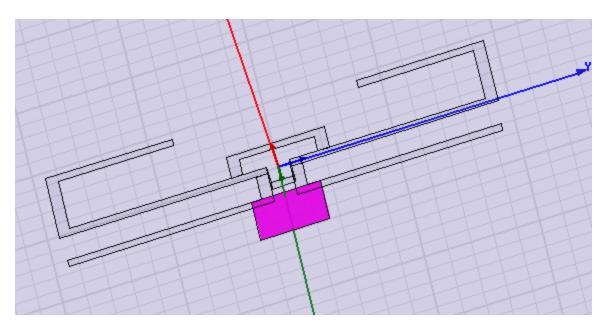

In this chapter, we present a new low power phase-locked loop (PLL) based frequency shift key (FSK) receiver. We first present a down-conversion mixer design with single RF and LO input topology that consumes 48µW power. Detailed analysis of the mixer has been provided. We then discuss the power limitations of two major oscillator topologies: LC oscillators and ring oscillators. Our analysis concludes that a LC oscillator structure using on-chip inductors cannot meet wireless sensor network (WSN) power requirements, and thus is not suitable for WSN applications because of its lossy on-chip inductors. A current starving ring oscillator topology is implemented in this work to meet the power specification of WSN systems. Using the presented mixer as a phase-detector and the current starving ring oscillator as voltage controlled oscillator, a low power PLL has been designed and fabricated. The PLL based receiver architecture has been developed and analyzed for FM/FSK receiver applications. The designed circuits have been fabricated through a 0.13µm eight metal layer CMOS process. Dissipating 0.26mW from a 1.2V supply, the fabricated PLL can track radio signals in a wide frequency range from 1.62GHz to 2.49GHz. The combination of the PLL and a low noise amplifier (LNA) can work as a FSK receiver. The energy per bit of the receiver is as low as 0.26nJ, making it attractive for low power applications including WSNs.

#### 2.1 Overview of the Low Power Receiver Architecture

High speed, low power phase locked loops (PLL) are extensively used in frequency synthesis, clock generation, and recovery circuits for microprocessors and wireless communication systems. A PLL can also be used as a natural FM/FSK demodulator for wireless communication receiver applications. Wireless communication ICs are extensively used in mobile cellular devices, portable electronics, and positioning systems. For most of these applications, limited battery power necessitates low power designs. This chapter discusses circuit techniques as well as low power circuit design methodologies to build a high speed, low power PLL, with specific application for ultra low power FSK and FM receivers such as those used in ad-hoc distributed wireless sensor networks (WSN). For such applications, receivers are typically required to be left unattended for extended periods of time (perhaps several months or even years), and thus require maximum power efficiency. In addition, these receivers need to detect extremely low power signals. To help meet these low power requirements, instead of using a digital phase detector [Tak2005, Hu2009, Krishnaswamy2008], we have designed an extremely low power PLL using an analog phase detector for signal demodulation.

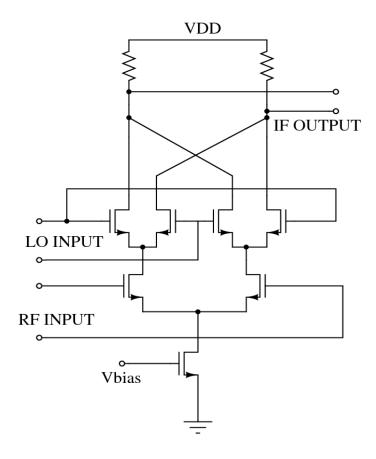

Generally, Gilbert cell based mixers are widely used as analog phase detectors in PLLs [NG2006]. However Gilbert cell based mixers (phase detectors) [NG2006, Sullivan1997, Jeng-Han2007] often consume prohibitive amounts of power for WSN applications because of current sources and related stacked structures. The Gilbert cell also uses differential inputs that usually require additional accessory circuitry for low noise amplifiers (LNAs) and voltage controlled oscillators (VCOs). A differential topology of a VCO [Ng06], LNA, or balun [Chiou1997] is often used to meet the differential input

requirements of the Gilbert cell. However, a differential input structure can be vulnerable to phase errors due to device mismatch, and a balun usually occupies a large area on the chip. [Hermann2005] use on-chip transformer to achieve high current gain for a down convert mixer with power consumption of 1.6mW. Other previous reported mixes consume milli-watts or even tens of milli-watts power as well [Tan2003][ Hung2006][ Vidojkovic2005]. [Klimperink2004] reports a mix with 0.57 milli-watts power consumption. However, part of their power consumption is due to the low supply voltage (0.5V).

In this chapter, a single RF and LO input mixer, which we use as a phase detector for the PLL, is presented and implemented. The phase detector achieves ultra low power consumption and high linearity. The presented phase detector consumes low power due to its single end topology and current re-use. This phase detector also takes advantages of the parasitic capacitors of the MOSFET to filter out high harmonic signals and thus achieve high linearity. Furthermore, constituent PLL circuit components can be simplified as a result of this phase-detector topology.

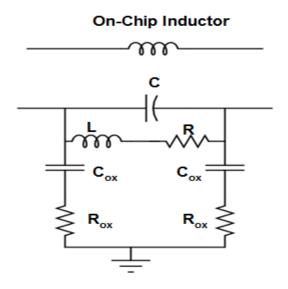

An oscillator is another essential circuit component in a PLL. LC oscillators and ring oscillators are widely explored for different applications. Both LC oscillators [NG2006] and ring oscillators [Ingino2001] have previously been implemented in PLL applications. LC oscillators are generally used in favor of ring oscillators due to their superior phase noise properties [Hajimiri1999A] [Hajimiri1999B], while consuming milliwatts of power in on-chip topologies [Hajimiri1999A] [Lee2005, Andreani2002]. However, for ultra-low power applications (on the order of 100µW), we find the losses due to on-chip inductors limit the applicability of on-chip LC oscillators.

In this work, we explore the LC oscillator power limitation in detail. An extraction procedure for the values of lump components for on-chip inductors is given in Appendix 2B. Following the same procedure, we extract the lump component values of the on-chip inductor. Our analysis shows that the losses of the on-chip inductor cause the LC oscillator to consume an inordinate amount of power. This disadvantage thus excludes the use of the on-chip LC oscillator in ultra-low receiver applications. Ring oscillators do not suffer from the on-chip inductor losses, and can achieve oscillations while operating at a 100µW power level using 0.13 µm CMOS technology. We thus find that it is preferable to use a current-starved ring oscillator for WSN applications. Similar results have been obtained by other authors for ultra low power receiver applications [Pletcher2009] [Krishnaswamy2008].

The Type-I analog PLL demodulates the RF signal and is at the core of the ultra low power receiver. Often, OOK architectures [Daly2007] or super-regenerative architectures [Chen2007] [Otis2005] are implemented for low power applications. In this chapter, a PLL based architecture is investigated. Compared with the super-regenerative architecture [Chen2007] [Otis2005], the data rate of the PLL based FSK receiver architecture is higher. However, one potential difficulty of OOK and the presented FSK ultra low power receiver is that this design can be susceptible to outside interference. This problem can be solved by using a highly selective surface acoustic wave (SAW) filter to remove the interference [Daly2007].

This chapter consists of five sub-sections. Section 2.2 presents the overview of the Gilbert cell based mixer and its limitations for low power applications. It then presents new mixer circuit components: a mixer/phase detector and an oscillator. Detailed circuit

analysis and design procedures have been given for the presented single input low power mixer. This topology has also been compared with previous mixer design works. Section 2.3 investigates the power limitations of the cross-coupled LC and ring oscillator topologies for 100uW power applications. We conclude that the ring oscillator is preferred for 100uW power applications. This analysis is then followed by a detailed current starving ring oscillator design. The design methodology is given, as well as simulation results. Section 2.4 demonstrates PLL's applications as FM/FSK receivers and presents the simulation results of demodulated FM/FSK signals. Section 2.5 and 2.6 discuss the selectivity and interference of the designed receiver, respectively. Section 2.7 presents the fabricated integrated circuit and the measured results for the PLL, and its performance as a receiver. Section 2.8 summarizes the work and provides conclusions.

#### 2.2 Low Power Mixer Architecture

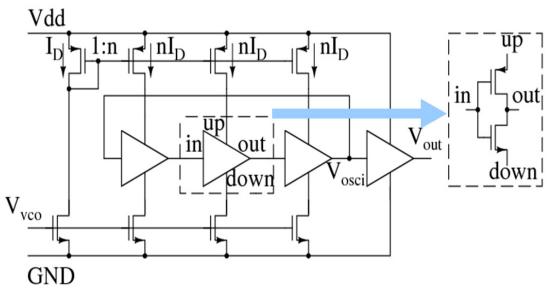

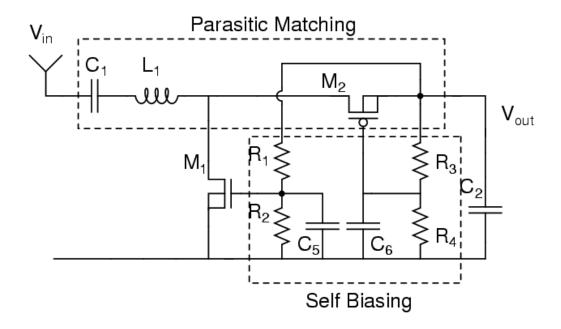

#### 2.2.1 PLL Architecture

A block diagram of the second-order PLL architecture we used is enclosed in the dashed-line box in Fig. 2.2.1. The analog phase detector (PD) compares the phase difference between RF and local oscillator signals and generates a voltage proportional to the phase difference of the two signals. The phase detector employs a single RF and LO input mixer topology. This topology simplifies voltage-controlled oscillator design for the PLL application. It also simplifies the LNA circuit design when the PLL is used in FM and FSK demodulation. The first order low pass filter (LPF) removes the high frequency signal components from the phase detector and is fundamental in determining the dynamics of the PLL. As will be discussed later, we use a relatively high bandwidth

low pass filter to increase the lock-in range of the PLL to facilitate FM/FSK signal demodulation. A ring oscillator topology is utilized as the VCO to obtain  $\mu W$  power consumption and a large tuning range with reasonable phase noise.

Fig. 2.2.1. Block diagram of PLL and its application as an FSK receiver when used with a LNA, comparator, and a DSP.

### 2.2.2 Overview of Different Mixer Architectures

Mixers are non-linear circuits widely used in communication circuits to shift signal frequencies up and down for modulation and demodulation. In most receiver applications, a mixer shifts the incident radio signal frequency down to an intermediate frequency to be further processed by the baseband circuits, while in transmitter applications, they multiply the low frequency digital baseband signal with the high frequency oscillator signal to shift up the baseband signals into different communication channels.

Ideally, mixer output is the just the multiplication of the two input signals with some amplification. Figure 2.2.2 shows the schematic of a commonly used Gilbert cell mixer. The Gilbert mixer uses differential structure at the RF input to cancel the white thermal noise at the RF input. It also uses two differential pairs (four transistors) to remove the LO leakage. Gilbert cell based mixers (phase detectors) [NG2006] [Sullivan1997] often consume power at prohibitive levels for WSN applications because of current sources and related stacked structures. The Gilbert cell also uses a differential input, which usually requires additional accessory circuitry to connect with other circuit parts of the receiver. Differential VCOs [NG2006], LNAs, or baluns [Chiou1997] are often used to meet the differential input requirements of the Gilbert cell. However, a differential input structure can be vulnerable to phase errors due to device mismatches, and a single to differential balun usually occupies a large chip area since the balun is usually implemented by onchip inductors or off-chip transmission lines.

In this chapter, we design a new mixer topology for low power applications. We analyze the new mixer topology and provide small signal analysis results mathematically. Following the mathematical analysis, we gain insight and understanding of the mixing process and develop a design procedure. Finally, the simulated characteristics of the mixer are presented along with a comparison with previously published mixers.

Figure 2.2.2 Schematics of Gilbert cell.

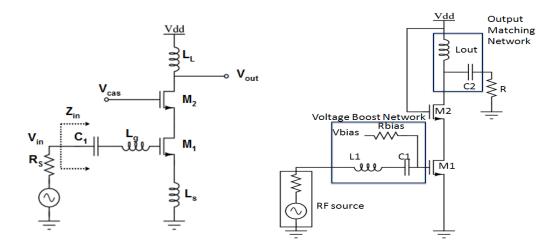

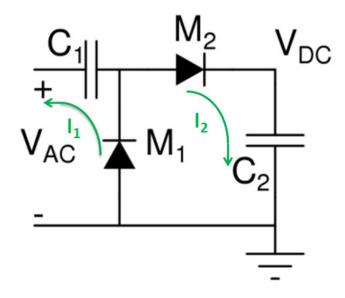

### 2.2.2 Down-Conversion Mixer Topology

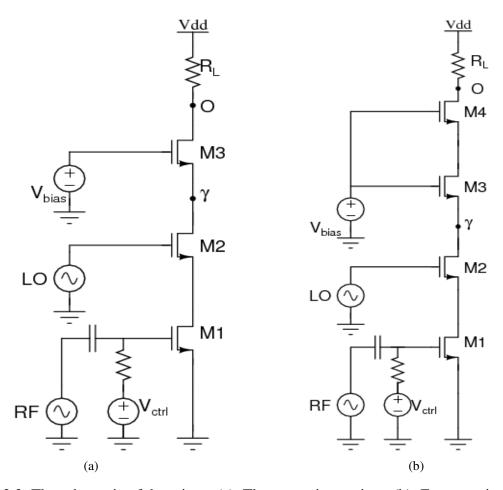

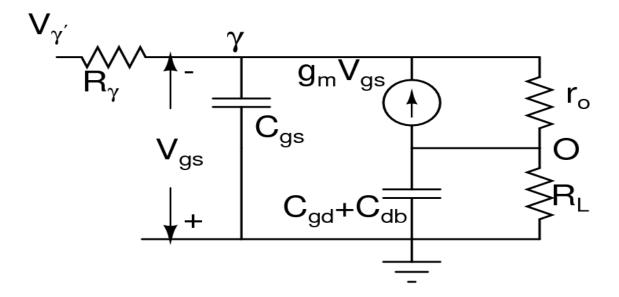

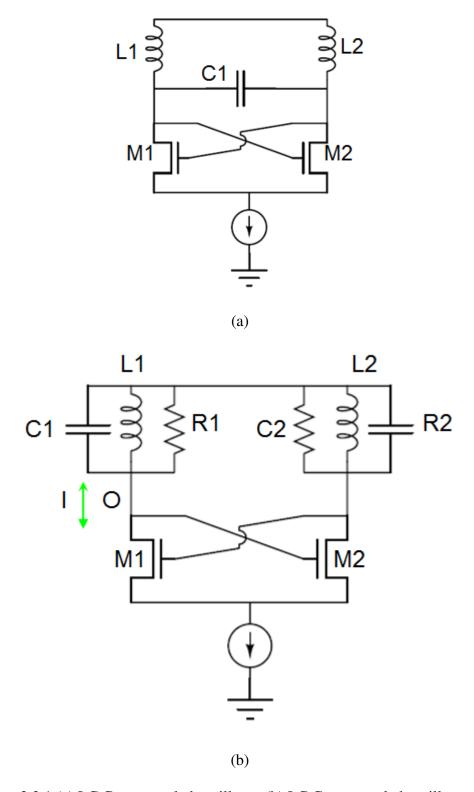

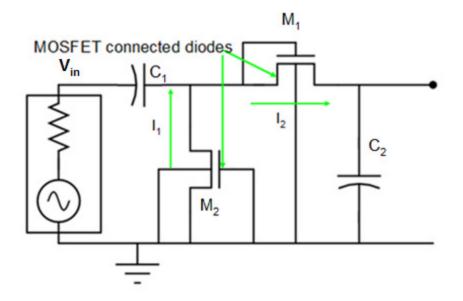

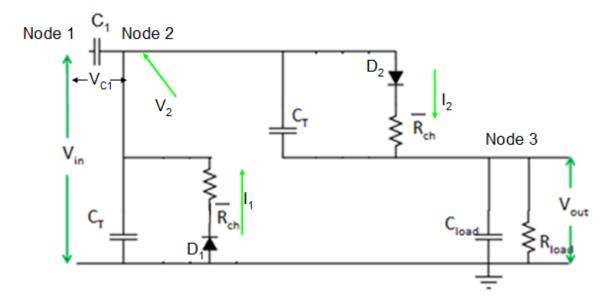

Fig. 2.2.3 (a) and (b) are the schematic of the single RF and LO input mixer. The radio frequency signal and local oscillator signals are connected to the gates of transistors M1 and M2, respectively. The mixer (Fig. 2.2.3a) core consists of three transistors M1, M2, and M3. M1 and M3 work in the saturation region, and M2 is switched on/off by the local oscillator signal. M2 chops (multiplies with a square wave) the RF signal. We used the intrinsic capacitors of M3 to filter out the high frequency harmonic signals to obtain high mixer linearity. Fig. 2.2.3b shows the mixer with one extra transistor (M4) to further filter out high frequency harmonic signals and thus to improve mixer linearity. In addition, since M2 chops the RF signal, only the down-converted signal needs to be

amplified by M3 and M4. Therefore, the frequency limitation of the mixer is due to M1 and M2, which have very large unity gain frequencies, since they are minimum size devices. Thus, the designed mixer can operate at very high input frequencies.

Figure 2.2.3b adds an extra transistor to further filter out the high harmonic signals. Transistor M3 works in the linear region and transistor M4 works in the saturation region. The extra transistor further filters out the high harmonic signal and thus improves the linearity of the mixer. Since M3 works in saturation region, the mixers in Figure 2.2.3 panels (a) and (b) have similar voltage gain.

The presented mixer topology consumes less power due to its single branch structure

Fig. 2.2.3: The schematic of the mixers (a): Three transistor mixer. (b): Four transistor mixer.

and current re-use. In other words, we use a single current through the structure to multiply, amplify, and filter the signal. In addition, M2 is chosen to be a minimum size device, and it requires minimal power for device switching.

Another attribute of the mixer is that it provides a natural DC bias for the next stage (VCO) of the PLL. More specifically,  $V_{ctrl}$  sets the DC bias for M1 and controls the DC output voltage (point O). Since the output has a DC connection to the VCO (after the LPF),  $V_{ctrl}$  controls both the DC bias point and the VCO operation frequency with a single bias. This multi-purpose bias thereby also provides the ability of the PLL to track in a wide frequency range.

### 2.2.3 Design and Analysis of the New Mixer

The mixing process is described as follows: The local oscillator signal switches the transistor M2 on and off at the oscillator's frequency.

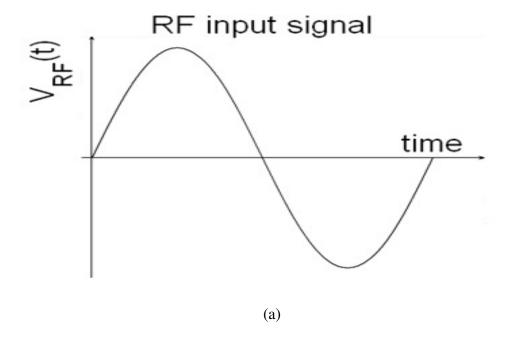

Fig. 2.2.4: (a): Input RF signal. (b): Local oscillator signal. (c) Output signal

The RF signal applied to the gate of M1 is coupled to the LO signal and appears at the drain of M2 in the form of a function of the LO signal. Figure 2.2.4 shows the

multiplication process. As the local oscillator turns on/off the M2, the output signal looks like the wave at in Figure 2.2.4c. For a purely sinusoidal radio signal, the signal source at point  $\gamma$  can be mathematically described by equation 2.2.1:

$$V_{\gamma'}(t) = V_{RF} \sum \frac{\Delta_n G}{2} (\cos(n\omega_{LO} + \omega_{RF})t + \cos(n\omega_{LO} - \omega_{RF})t), \quad \Delta_n = V_{pp} \frac{\sin\frac{n\pi}{4}}{\frac{n\pi}{2}}$$

2.2.1

Where G is the magnitude of the gain of the multiplier from the RF input port to the output at point  $\gamma$ ,  $V_{\gamma}$  is the loaded voltage at point  $\gamma$ , and  $V_{\gamma}$  is the open circuit voltage at  $\gamma$ .  $V_{pp}$  is the square wave peak to peak voltage.

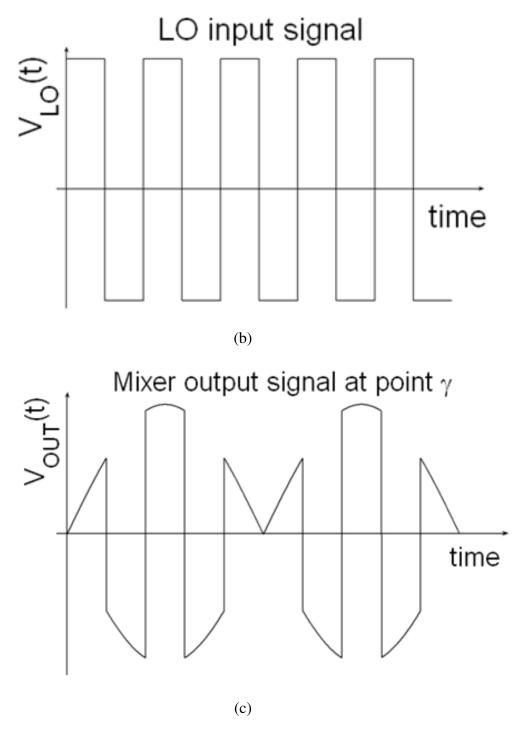

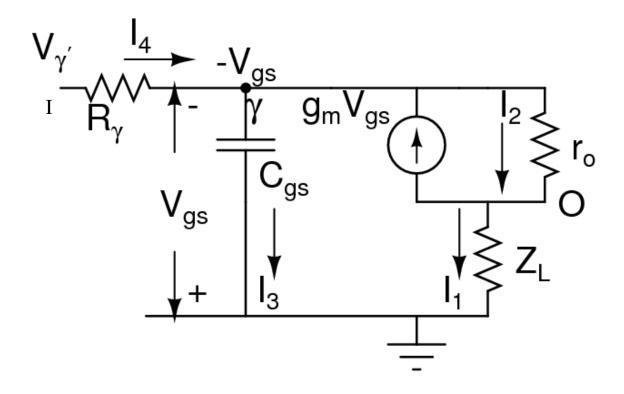

Figure 2.2.5: Equivalent circuit of transistor M3 as seen by voltage source  $V_{\gamma'}$  with source resistance  $R_{\gamma}$ .

As indicated previously, transistor M3 amplifies the desired low frequency signal and filters out the high frequency harmonic components to improve the linearity of the down-conversion mixer. Figure 2.2.5 shows the small signal equivalent circuit seen at the point

$\gamma$ , looking into the source of M3.  $R_{\gamma}$  and  $r_{o}$  are the output resistance looking toward M2 at point  $\gamma$  and the M3 channel modulation resistance, respectively. A detailed small signal analysis can be found in Appendix A.

The small signal voltage gain  $V_0/V_\gamma$  is given as:

$$A = \frac{Z_L(1 + g_m r_o)}{(Z_L + r_o)(1 + sC_{gs}R_{\gamma}) + (g_m r_o + 1)R_{\gamma}}$$

2.2.2

Where  $C_t$  is  $(C_{gd}+C_{db})$  and  $Z_L$  is  $R_L/\!/(1/\omega C_t)$ . Since  $g_m r_o >> 1$ , for low frequency signals the voltage gain is

$$A_{low} = \frac{R_L}{R_{\gamma}}$$

2.2.3

For high frequencies,

$$Z_L \approx \frac{1}{sC_t}$$

and the voltage gain is

$$A_{high} = \frac{(1 + g_m r_o)}{(1 + sC_r r_o)(1 + sC_{ro}R_v) + R_v sC_r (g_w r_o + 1)} < \frac{1}{R_v sC} << 1$$

2.2.4

Judging by equations (2.2.3) and (2.2.4), the transistor M3 should be designed to be large enough to filter out the high frequency harmonic signals but be small enough to amplify the desired intermediate frequency (IF) signal. To achieve this, the size of transistor M3 has been chosen as 200µm/640nm in this design. Transistors M1 and M2 are chosen to be as small as possible for high frequency application. The ADS simulation results show that the mixer can operate from 1 GHz to 60 GHz using a 1.2V supply voltage. Such a high operation frequency originates from the mixer topology. The signal multiplication process is only performed by the transistors M1 and M2 where minimal

devices have been chosen. This observation is further confirmed by the ADS simulation results of the mixer.

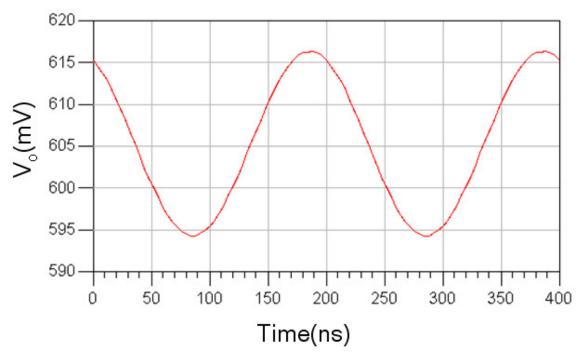

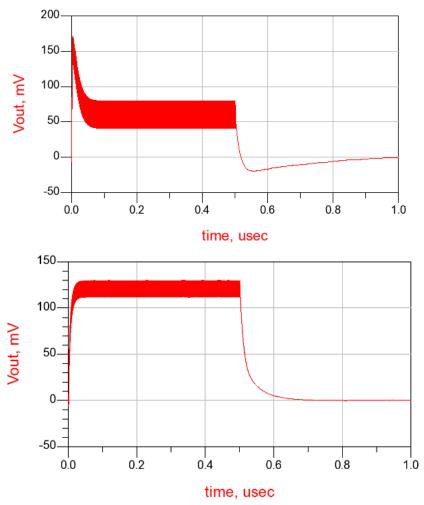

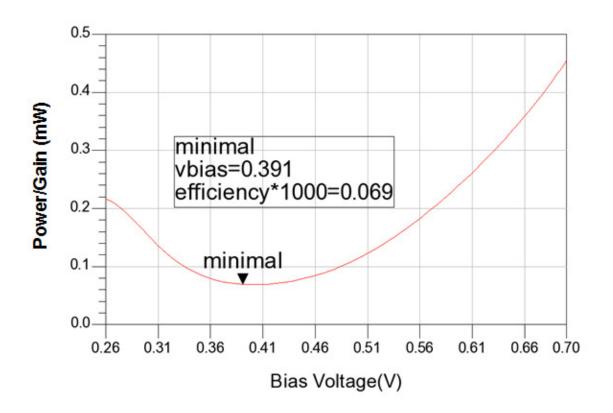

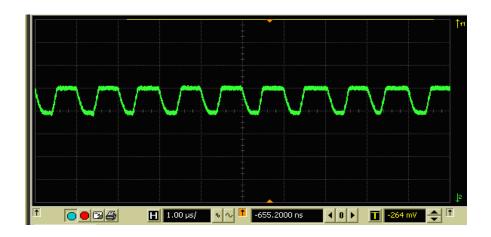

The power consumption is mainly determined by the supply voltage  $(V_{dd})$  and the RF DC bias voltage  $(V_{ctrl})$ . Figure 2.2.6 shows the simulation result of the mixer (the input signal are -60dBm@2.2GHz and 1.2V peak to peak square wave@2.195GHz).

ADS simulation results show that the mixer can operate from 1.6 GHz to 60 GHz with a 1.2V supply voltage. The power consumption, which is verified by ADS simulations, is mainly determined by supply voltage ( $V_{dd}$ ) and RF DC bias voltage ( $V_{ctrl}$ ).

Figure 2.2.6 The 5MHz output signal of the mixer (the input signal are -40dBm@2.2GHz and 1.2V peak to peak.square wave @2.195GHz).

In Fig. 2.2.3b, we show a small revision to the mixer topology by adding an additional transistor M4 to improve linearity. For this circuit, transistor M3 works in the linear region. The operation of this circuit is analogous to that in Fig. 2.2.2a; however, the

addition of the extra transistor M4 acts as a second filter in series with the filtering effects provided by M3, thereby increasing the high-frequency roll-off of the mixer and improving the linearity of the mixer. In addition, it should be pointed out that M4 provides a voltage gain of the down-converted (IF) signal, while in Fig. 2.2.3a, M3 provided the voltage gain. The design in Fig. 2.2.3b commonly achieves a higher linearity than the one in Fig. 2.2.3a, while having a similar voltage gain. These analyses agree with ADS simulation results.

The mixer voltage gain is constrained by the power consumption, so is the noise. M1 is chosen as a minimum length device (L=130nm) to help minimize indirect flicker noise [Darabi2000], as well as to achieve a high unity gain frequency  $f_T$ . The transistor M2 is turned on/off by the ring oscillator signal and consumes  $CV^2f$  power where C is the M2 gate capacitance, V is the peak to peak voltage of the oscillation signal (LO as shown in Fig. 2.2.3) and f is the oscillation frequency. M2 is chosen to be the minimum size device to minimize the device capacitance and thus minimize the power consumption. Due to the ultra low power constraints,  $g_{ml}$  needs to be small to meet the low power requirements. The mixer requires a large resistor at the drain of the transistor M3 as shown in figure 2.2.3 (a) in order to obtain reasonable gain. Furthermore, for the receiver application, the next stage following the mixer is a low pass loop filter, and thus does not load down the AC voltage gain at base-band frequencies. We use a resistor load  $R_L$  instead of an active load to eliminate flicker noise of the active load.

To arrive at our circuit, we established several constraints to facilitate design in a 130nm CMOS process for WSN applications. The power is constrained to be less than 50  $\mu$ W and the voltage amplitude of the down converted signal is required to be at least 50 times

larger than the amplitude of harmonic signals. Furthermore, the output voltage at point O, which is DC connected to the mixer through the low pass filter, needs to vary around a quiescent voltage of 0.6V (half of the  $V_{dd}$ ) to ease the voltage controlled oscillator design. The bias current is set by the power consumption,  $I=P/V_{dd}$ . The resistor value (R<sub>L</sub>) is calculated using the current and the required voltage gain. The M1 size is calculated from the current, after a single DC bias voltage is applied to both  $V_{ctrl}$  and  $V_{bias}$ . The minimal device area of the transistor M3 is calculated from equations 2.2.3 and 2.2.4. The precise sizes of the transistors are then refined using ADS, while employing accurate BSIM4 transistor models to optimize performance and satisfy the design constraints. The simulation results agree reasonably well with the analytical results.

### 2.2.4 Characteristics of the Mixer

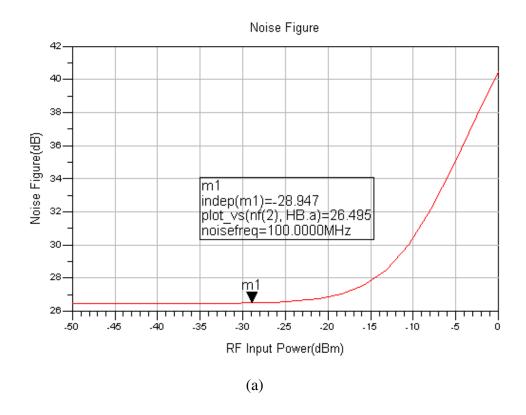

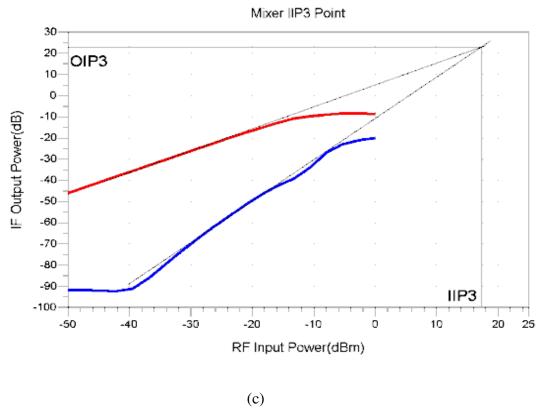

Power consumption, noise figure, conversion gain, and linearity (IIP3) help to evaluate mixer performance. Figure 2.2.7 shows the mixer noise figure, conversion gain, and linearity of the mixer as a function of input power. For our mixer design, simulation results show that the power consumption, voltage conversion gain, noise figure, and IIP3 are 48µW, 8dB, 26.5dB, and 23dB, respectively, as shown in Figure 2.2.7. The mixer figure of merit (*FOM*) can be expressed [Liang2007] as

$$FOM = 10\log(\frac{10^{G/20}.10^{(IIP3-10)/20}}{10^{NF/10}.P})$$

2.2.5

Where G and NF represent voltage gain and the noise figure in dB, P represents power consumption in Watts, and IIP3 describes the linearity in dB. It can be seen from equation 2.2.5 that a higher FOM indicates better performance. Figure 2.2.7 shows the

simulation results of mixer noise figure, voltage gain, and IIP3 respectively using ADS simulator. Our mixer shows a simulated *FOM* of 27.2. The values for *FOM* found in the literature range from -2.28 to 13.2 [Liang2007]. Table 2.1 summaries and compares this mixer simulation performance with other published results.

Figure 2.2.7 (a): Mixer noise figure. (b): Conversion gain of mixer. (c): Linearity of the mixer (IIP3).

Table 2.1 Comparison with previous mixers [Liang2007]

| Ref          | Process                | RF Frequency<br>(GHz) | NF<br>(dB) | Gain<br>(dB) | IIP3<br>(dBm) | Power<br>Consumption<br>(mW)/V <sub>DD</sub> (V) | F.O.M<br>(dB) |

|--------------|------------------------|-----------------------|------------|--------------|---------------|--------------------------------------------------|---------------|

| 52           | 0.13μm<br>CMOS         | 2.1-3                 | 14.8       | 5.4          | -2.8          | 1.6/0.6                                          | 9.45          |

| 53           | <b>0.18µm</b><br>СМОS  | 2.4                   | 12.9       | 15.7         | 1             | 8.1/1.8                                          | 11.3          |

| 54           | <b>0.18</b> µm<br>СМОS | 0.3-4                 | 14         | 11           | 4.1           | 6.6/1                                            | 10.3          |

| 55           | <b>0.18</b> µm<br>СМОS | 2.45                  | 16         | 13.3         | -1            | 7.2/1.8                                          | 6.6           |

| 56           | 0.18µm<br>CMOS         | 5.25                  | 24.5       | 8.3          | 0.03          | 4.95/0.9                                         | -2.28         |

| 26           | <b>0.13</b> µm<br>СМОS | 0.5-7.5               | 15         | 5.7          | -5.7          | 0.48/0.77                                        | 13.2          |

| This<br>work | <b>0.13</b> µm<br>СМОS | 1-10                  | 26.5       | 8            | 23            | 0.048/1.2                                        | 27.2          |

#### 2.2.5 Phase Detector

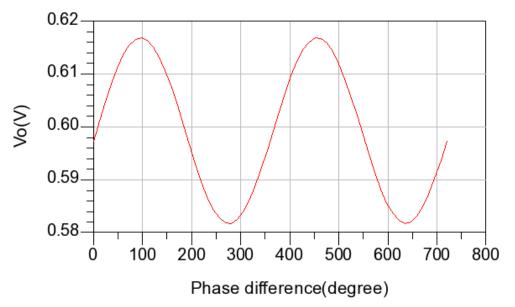

The analog mixer works as a natural analog phase detector when the two input signal frequencies are the same. Figure 2.2.8 shows the output voltage varies with the phase difference of the two signals having the same frequency. The phase detector output voltage can be described by equation 2.2.6:

$$Vout = Vdc + A \times V_{rf} \times V_{LO} \times \sin(\phi)$$

(2.2.6)

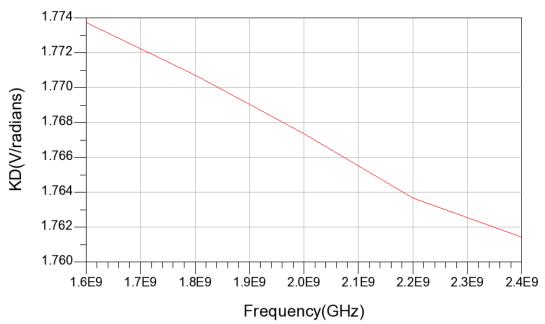

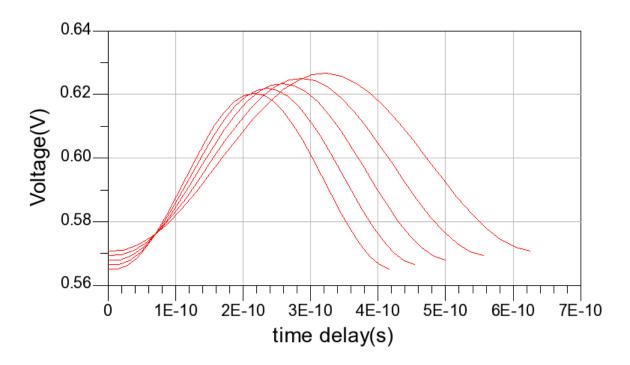

Where A is the phase detector voltage gain and  $\phi$  is the phase difference of the two input signals of the phase detector. Figure 2.2.9 indicates the simulation result of the phase detector gain (A), which varies with different frequencies. The voltage gain of the phase detector remains constant over the frequency range (1.6GHz to 2.4GHz). Figure 2.2.10 shows the simulation results of the phase detector voltage output for different input

frequencies. The result indicates that the phase detector successfully generates a voltage corresponding to the phase difference across the frequency range of 1.6GHz to 2.4GHz.

Figure 2.2.8 The phase detector output signal of the mixer (the input signal are - 35dBm@2.2GHz and 1.2V peak to peak square wave @2.2GHz with different phase).

Figure 2.2.9. Phase detector gain varies with frequency.

Figure 2.2.10 Phase detector output varies with phase differences for different frequencies (the inputs are 10mV RF signal and 0-1.2 square wave LO signal for frequency 1.6G, 1.8GHz, 2.0GHz, 2.2GHz, and 2.4GHz.

### 2.2.6 Summary

A low power mixer circuit topology has been designed. A detailed analysis of this mixer circuit has been given. The contribution of this work can be summarized as follows:

- A novel down conversion mixer topology has been presented with

- Low power consumption due to current reuse

- High linearity

- Wide operation frequency of the mixer

- o Control of the output voltage using DC bias of RF signal

- Simplified the connection circuits such as for VCO and LNA designs because there is a single input topology of the mixer

- Detailed analysis and design procedures of the mixer

- o Detailed small signal model analysis of the proposed mixer

- o Identification of the key parameters to optimize mixer performance

- Detailed design procedure

# 2.3 Low Power VCO Design

Voltage controlled oscillators generate high frequency carriers for both modulation and demodulation and are one of the key components in FSK/PSK transceivers. They provide the carrier signal to mix with baseband signals to generate different kinds of modulation such as BFSK, 8-FSK, etc. in transmitter circuits. For the receiver, they generate the extremely accurate (less than 10KHz frequency drift) carrier signals to mix down the modulation signal to lower frequencies for further baseband signal processes.

The main VCO topologies are LC based oscillators and positive feedback based ring oscillators.

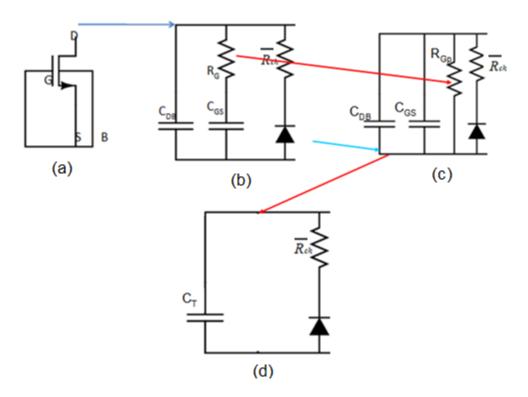

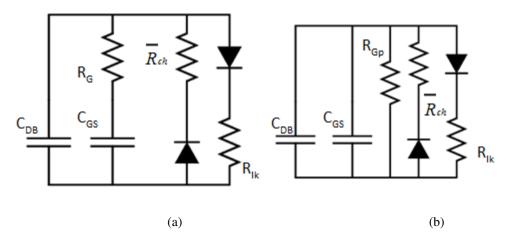

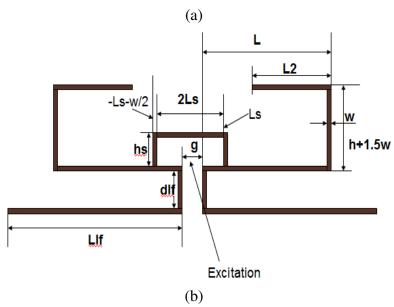

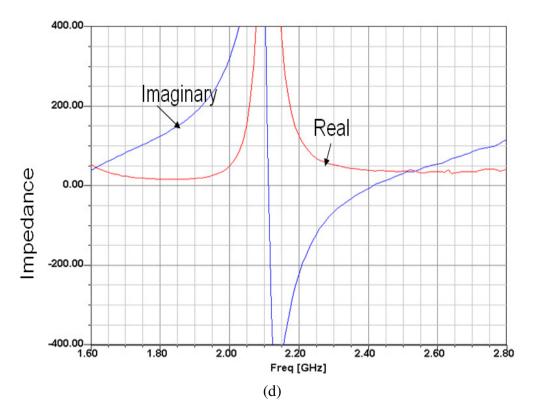

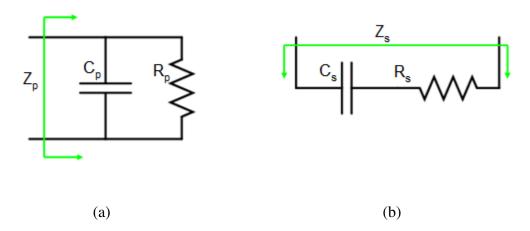

In WSN applications, we seek extremely low power circuits. LC oscillators are widely used in portable applications due to their superior phase noise characteristics. For a transmitter, low phase noise is necessary to meet FCC spur specifications. For a receiver, low phase noise oscillators help to strongly suppress the out of band interferences. However, all published LC oscillators consume more than mW power[Lee2005] [Andreani2002] [Margarit1999]. Theoretically, a parallel connected lossless inductor with a lossless capacitor can oscillate naturally at resonant frequency with zero power consumption, and they strongly amplify the thermal noise at its resonant frequency and suppress noise power at all other frequencies. However, in reality, there are always losses accompanied with capacitors and inductors. Quality factors can be used to describe the loss characteristics of networks. In order to oscillate using the lossy LC network, the oscillator needs to pump in power to the LC network to compensate for the losses of the network. Figure 2.3.1 is the schematic of the commonly used differential LC oscillator. It uses the transistors M1 and M2 to compensate for the losses of the inductors L1, L2 as well as losses due to capacitor C1, where capacitor C1 is the parasitic capacitance of the transistors M1 and M2. In a simplified case, the on-chip inductor can be modeled by a parallel R,L,C network as shown in Figure 2.3.1b. In the next paragraph, we present a detailed analysis of a LC oscillator to investigate their power limitations.

Figure 2.3.1 (a) LC Cross coupled oscillator. (b) LC Cross coupled oscillator using inductor model.

In figure 2.3.1 (b), the resistor R1 represents the losses of the inductors and capacitors. The capacitors in modern CMOS processes have quality factors on the order of hundreds because the electrical field can be limited inside the metal layer of the capacitors and ohmic losses due the metal can be minimized by choosing proper sizes for the capacitors. However, the on-chip inductors have poor quality factors because the magnetic field cannot be constrained inside metal layers: the magnetic field penetrates the lossy silicon substrates which causes significant losses for the inductor. Also, the ohmic losses of the metal are significant because of the skin effects (high frequency current is constrained at the very narrow edge of the metal) [Lee2003]. On-chip inductors typically have a quality factor less than 10 in current CMOS processes. The losses from the capacitors are significantly lower than the losses from the inductors. The inductor losses can be characterized by resistance R<sub>1</sub> as described by equation 2.3.1:

$$R_1 = \omega L_1 Q \tag{2.3.1}$$

Where Q is the quality factor of the LC network.

The output oscillator signal amplitude is defined as  $V_{ac}$ . The AC power consumed by R1 can then be described as equation 2.3.2:

$$P_{ac} = \frac{V_{ac}^2}{2R_1} = \frac{V_{ac}^2}{2\omega L_1 Q}$$

2.3.2

In an extreme case, if the network has no loss, the quality factor is infinite. The power consumption is zero which agrees with previous statements that an LC component oscillate can oscillate with zero power for a lossless network.

In order to oscillate, the oscillators need to pump power into the RLC network via the transistors M1 and M2. The inductor L1 works as shorted in DC, and the DC voltage at

point O is thus equal to  $V_{DD}$ . The DC current is controlled by the DC current source as shown in figure 2.3.1. The amount of DC current controls the trans-conductance of the MOSFETs and also the amount of power pumped into the LC tank. In order to maintain oscillations, the following equation needs to be satisfied:

$$g_{m1} > 1/R_1 \tag{2.3.3}$$

The drain current of the mosfet is proportional to the square of the voltage difference between the gate and source when the mosfet works in saturation regions. The current can be estimated as:

$$I = g_{m1}(VDD - Vth)/2 > (VDD - Vth)/(2R_1) = (VDD - Vth)/(2\omega L_1Q)$$

(2.3.4)

$$P_{M1} = VDD * I = VDD(VDD - Vth)/(2\omega L_1 Q)$$

(2.3.5)

$$P_{\min} = 2 \times VDD \times I \ge VDD \times \frac{VDD}{\omega L_1 Q}$$

(2.3.6)

Equation 2.3.6 clearly indicates that the LC oscillator power is limited by the supply voltage, inductor value, and tank quality factor. For an ideal inductor, the quality factor (Q) is infinite. The required power of the LC oscillator is zero, which agrees with previous statements. Equation 2.3.2 and 2.3.6 also indicate that the required oscillation power is inversely proportional to the inductor value L. If the inductor value is infinite, the power consumption is zero, too. However, there is a limitation on the maximum inductor value based on the design frequency. This is because on-chip inductors have inherent capacitances that cause self-resonance frequencies of on-chip inductors. Since the transistors M1 and M2 can only contribute extra capacitance, the maximum inductor needs to have a resonant frequency larger than the designed frequency to achieve oscillations at the designed frequency. Moreover, the tuning requirements of the VCOs

impose extra requirements on the maximum inductor value that can be chosen. The detailed extraction of the lumped components of on-chip inductors can be found in Appendix B. A simple example is shown below to estimate the minimal required oscillation power for operation at 2.2 GHz.

An inductor with 3GHz self-resonant frequency has been chosen for a 2.2GHz application to provide some tuning range margin. The extracted lumped components of the inductor show a 10 nH inductance for the inds type inductor from the IBM foundry. The extraction results also show the inductor quality factor of the inductor is about 10.

For long channel MOSFET devices, the drain current has a square-law dependence on the gate-source voltage minus the threshold voltage. The minimal oscillator power consumption for an oscillator using a 10 nH inductor under 1.2V supply voltage is

$$P_{\min} = VDD * I = VDD(VDD - Vth)/(2\omega L_1 Q) = 0.26mW$$

(2.3.7)

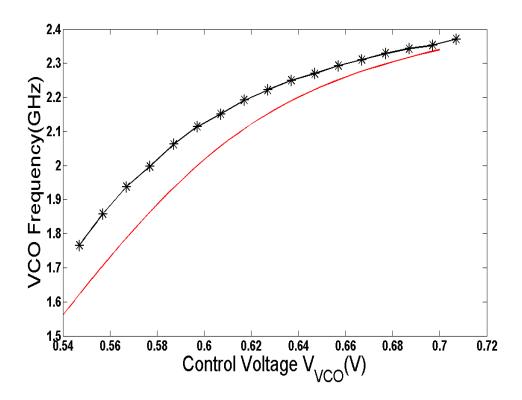

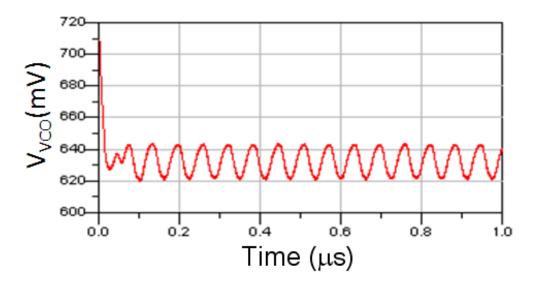

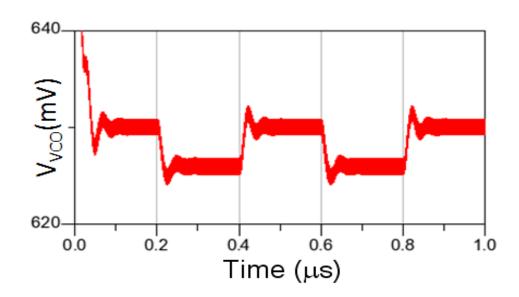

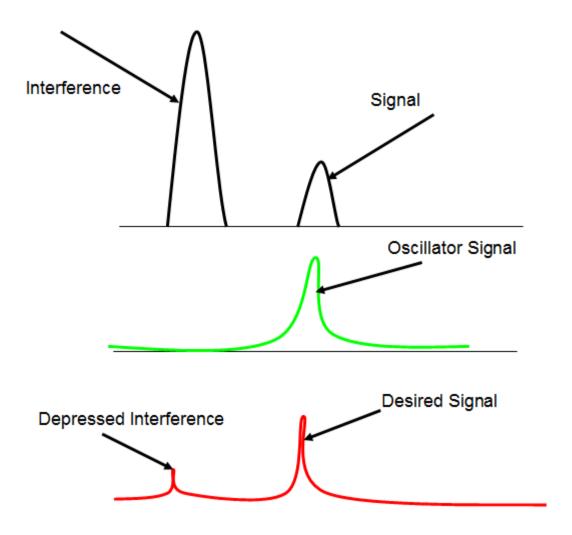

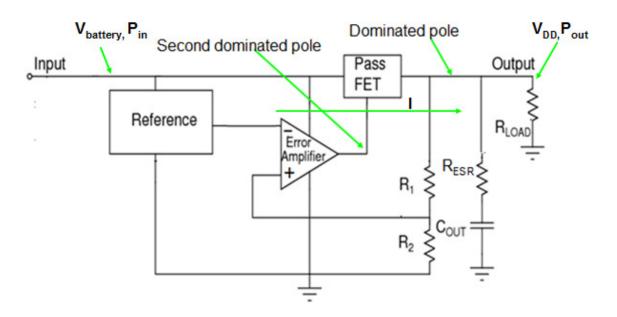

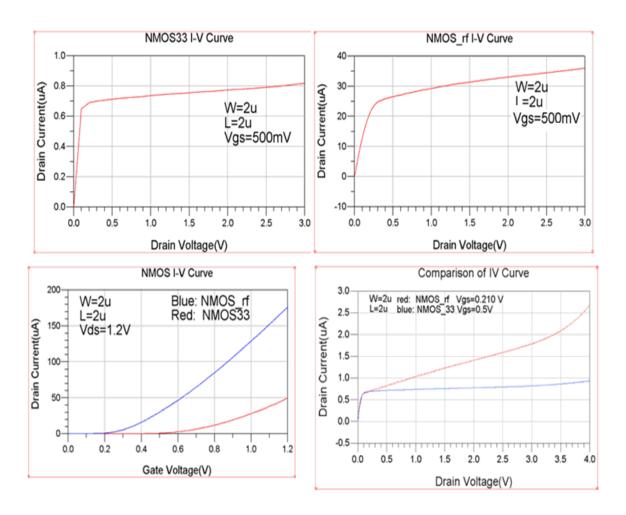

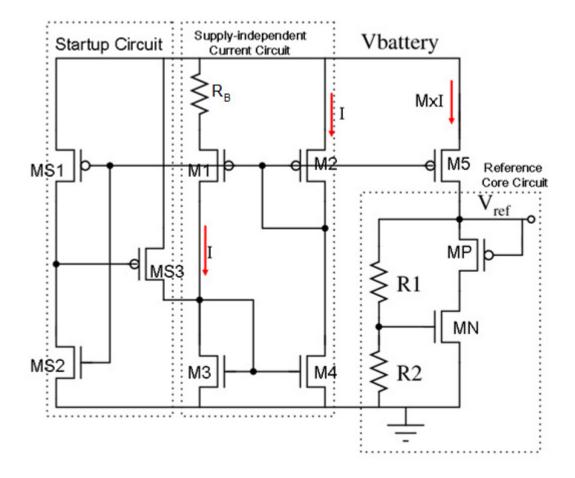

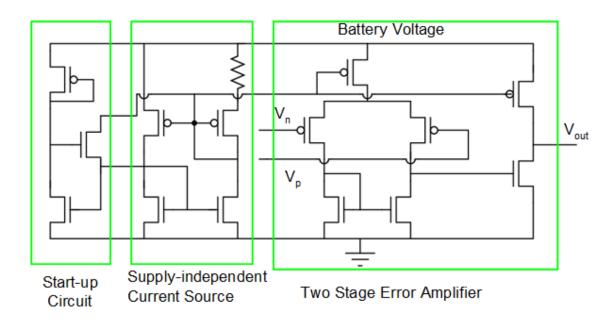

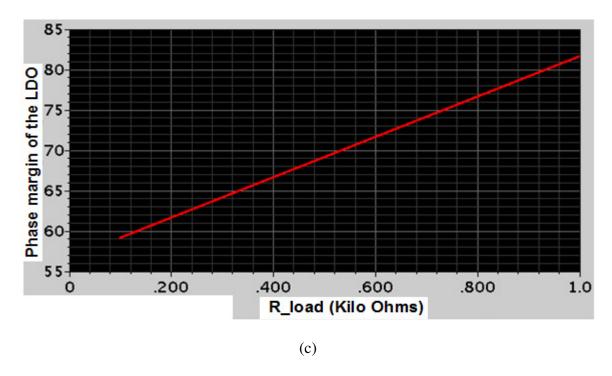

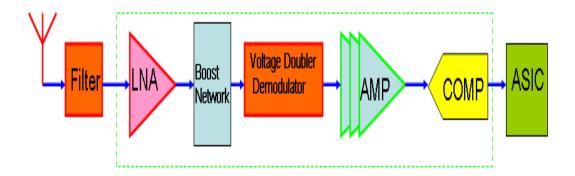

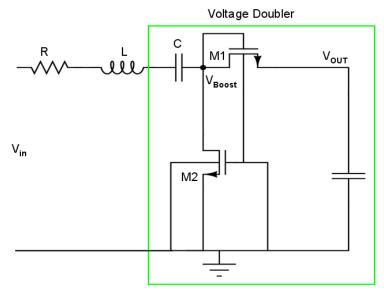

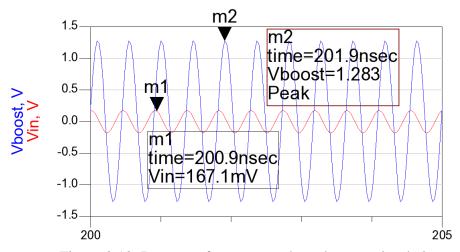

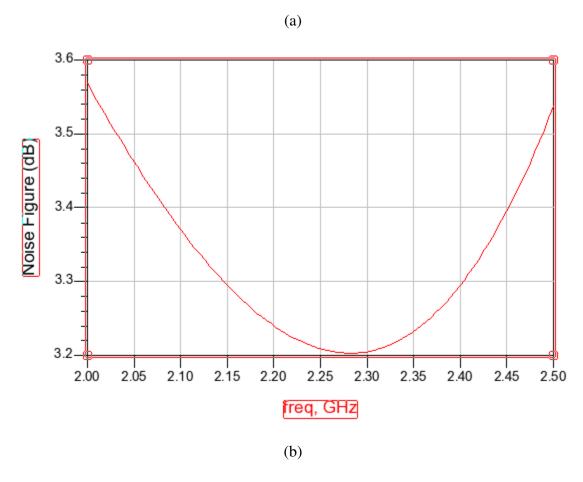

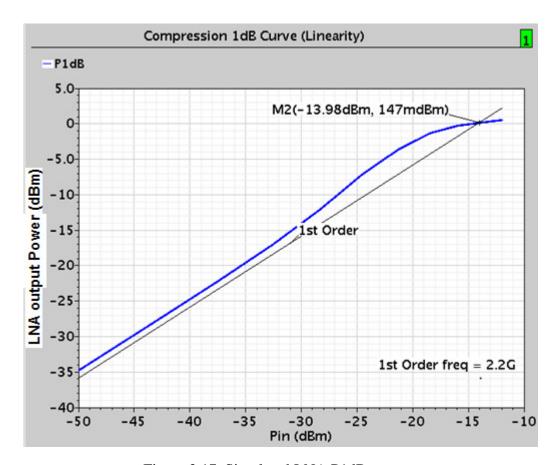

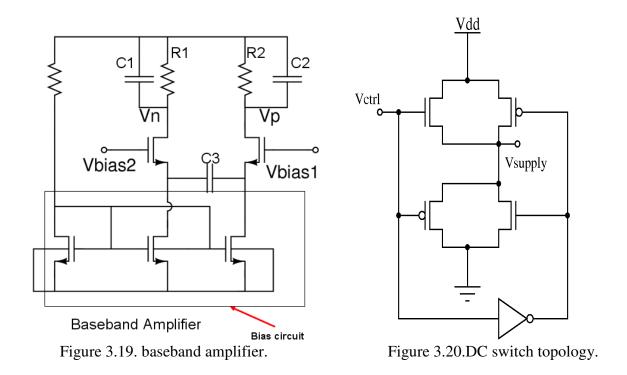

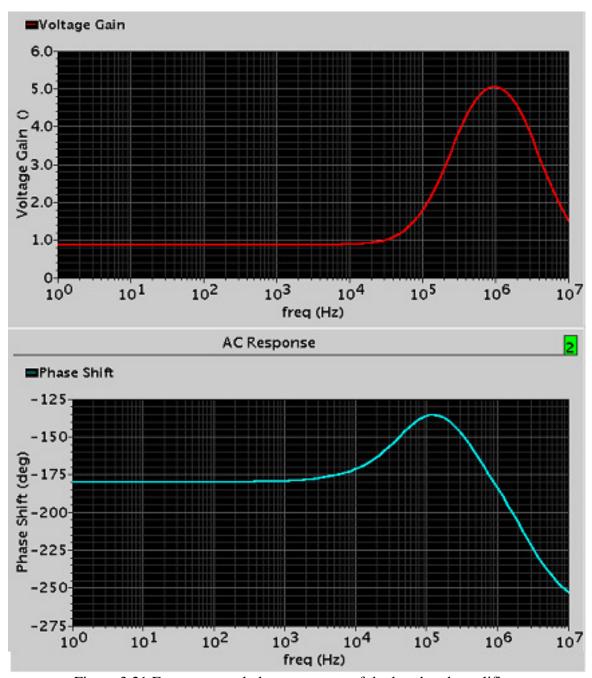

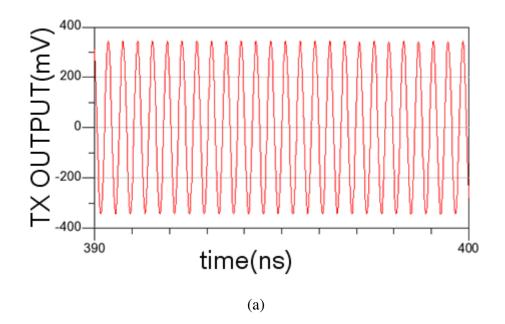

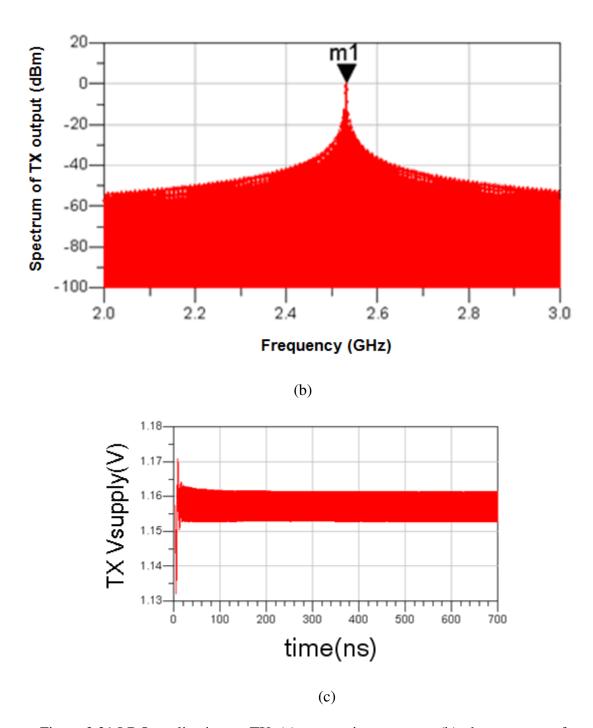

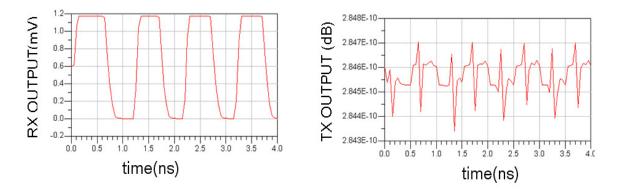

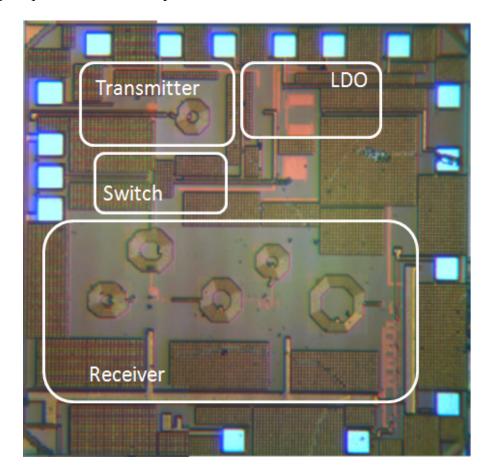

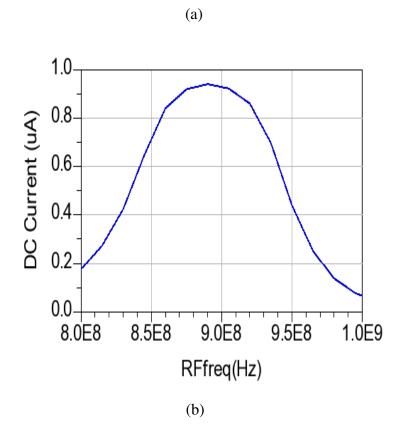

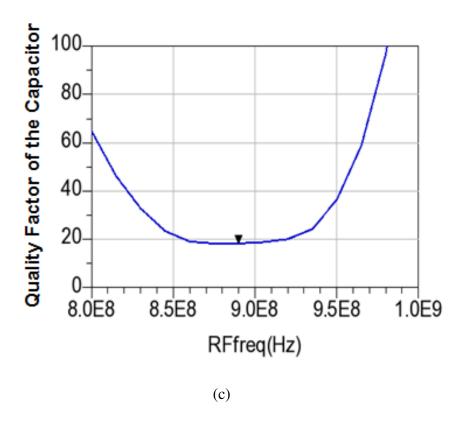

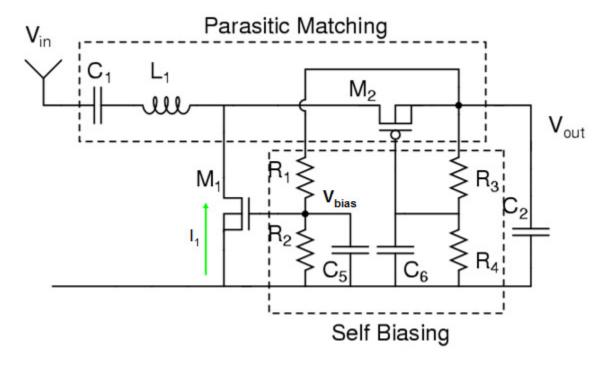

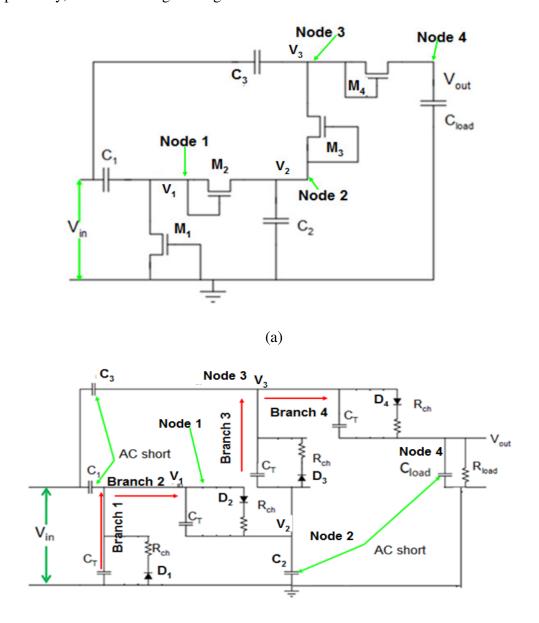

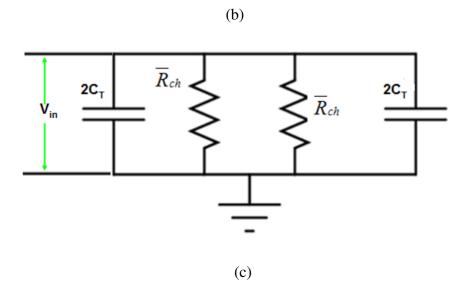

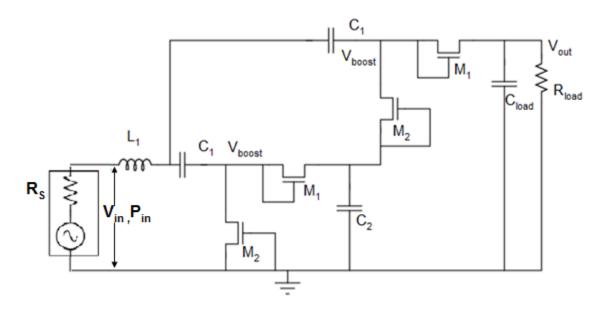

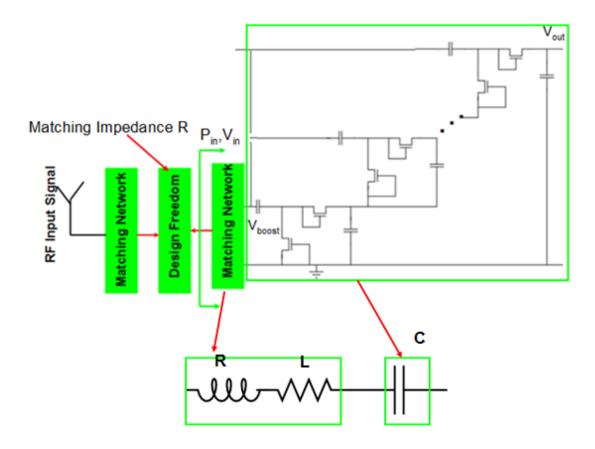

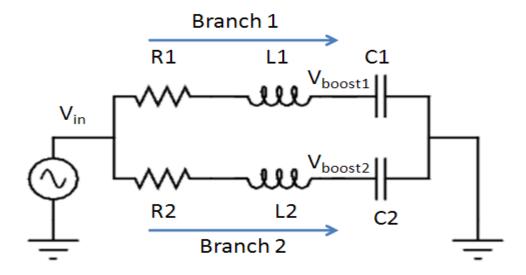

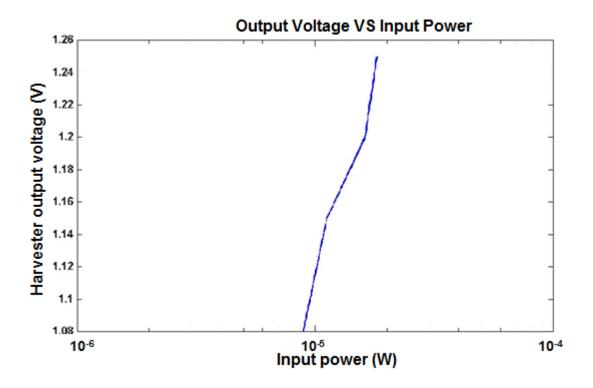

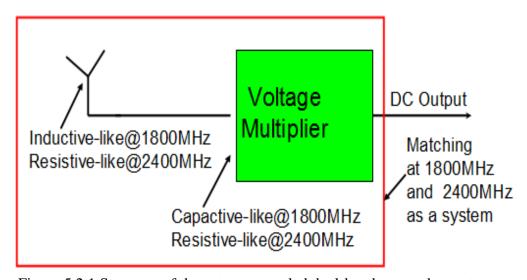

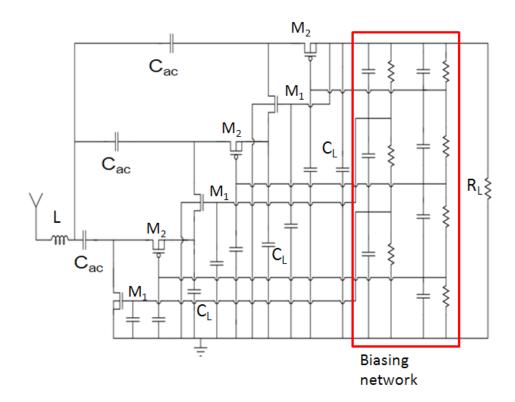

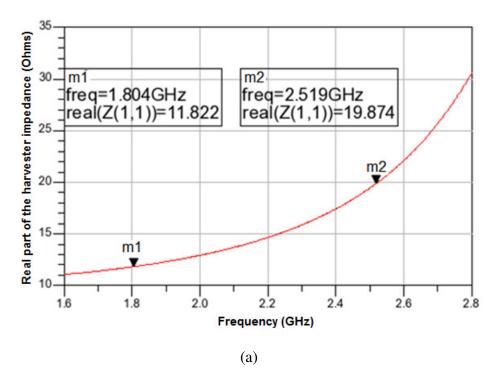

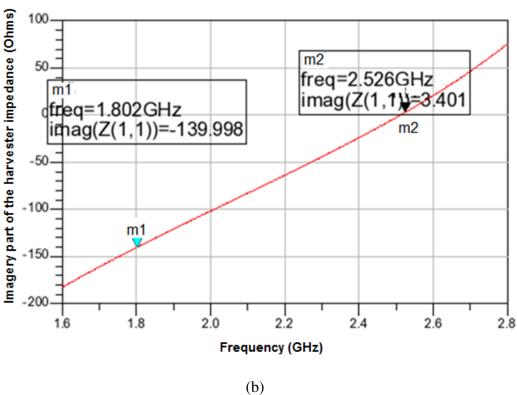

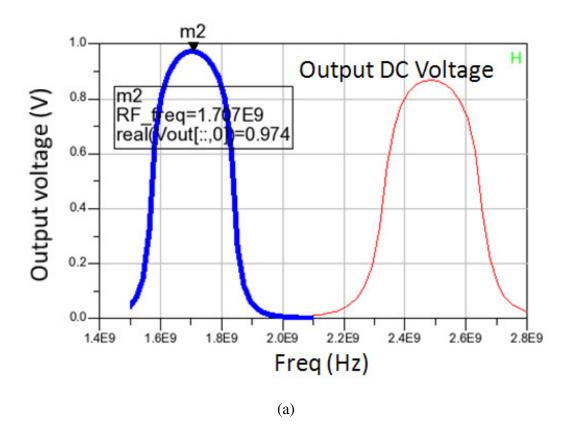

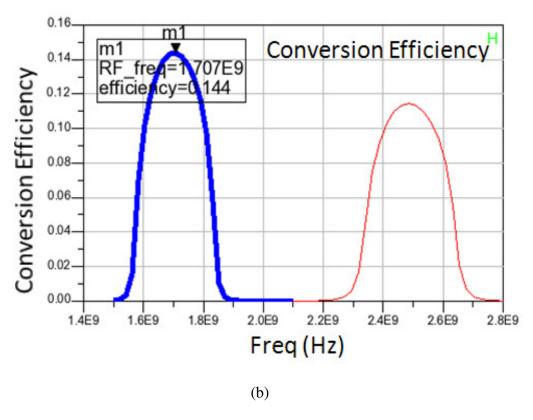

where VDD, Vth, and  $L_1$  are the supply voltage, threshold voltage, and inductor value which are equal to 1.2, 0.6, and 10nH, respectively.