**ABSTRACT**

Title of Thesis: LOW POWER AMPLIFIERS FOR RECORDING

ACTIVITY OF ELECTRICALLY ACTIVE CELLS

Makeswaran Loganathan, Master of Science, 2003

Thesis directed by: Dr. Pamela Abshire

Department of Electrical and Computer Engineering

Biological applications that require sensing individual cells have led to developments in the synthesis of large multielectrode arrays and single cell isolating microstructures. This in turn drives the need for the integration of low power electronic circuitry at or very close to the site of activity. We describe low voltage low power CMOS amplifiers that address this need by rejecting DC offsets, and have tunable bandwidths. They operate at 1.35V, with a power consumption of 37.8μW and have an input referred noise of 23μV. We also describe the design of a wireless transmission system capable of transmitting the electrical signals sensed from cells. Integration of the amplifier array with the wireless link brings continuous monitoring of neurophysiologic activity of unanesthized and freely moving animals closer to realization. The transmitter is

capable of generating an ASK modulated signal at a power level of -36 dBm at a frequency of  $820 \ \text{MHz}$ .

# LOW POWER AMPLIFIERS FOR RECORDING ACTIVITY OF ELECTRICALLY ACTIVE CELLS

by

#### Makeswaran Loganathan

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science

2003

### Advisory Committee:

Dr. Pamela Abshire, Chair

Dr. Ralph Etienne-Cummings

Dr. Timothy Horiuchi

Dr. Elisabeth Smela

© Copyright by

Makeswaran Loganathan

2003

# Dedication

To my parents and my sister

### **ACKNOWLEDGEMENTS**

I thank my advisor Dr. Pamela Abshire for her invaluable guidance and support during the course of my thesis. Without her motivation and encouragement this work would not have been possible.

I would also like to thank Dr. Ralph Etienne-Cummings, Dr. Timothy Horiuchi, and Dr. Elisabeth Smela for their assistance through various technical discussions, and taking time off to serve on my thesis committee.

Thanks to Dr. Junghwan Kim and Russell for spending a lot of their valuable time and resources in helping me make the RF measurements. Dr. Reza Ghodssi and Alireza Modafe were very resourceful in letting me use their probe station for characterization.

Colleagues at the IBIS lab were very helpful, resourceful and fun-loving and made my stay here very rewarding. I would like to thank them all, especially Suvarcha Malhotra for helping me with the Bio-amplifiers, Somshekar Bangalore Prakash for his help with the RF transmitter, and Hong Hao Ji for the several technical discussions that we had. I would also like to thank Jack Chaiyupatumpa, Kory Schoenfloss, Natasha Reeves and Jean-Marie Lauenstein for helping me during the course of my thesis.

I would also like to thank my dear friends who were ever so willing to help me, especially Harini Raghunthan, Ranjani Sridharan, Deepika Krishnaswamy, Arvind Aiyar and Suresh Kumar.

My parents' constant support and encouragement helped me identify and pursue opportunities in research and higher education. Thanks to them and to my sister Deepika for making significant contributions in my life.

# TABLE OF CONTENTS

| List o | f Table  | S                                                       | ix |

|--------|----------|---------------------------------------------------------|----|

| List o | f Figure | es                                                      | X  |

| 1.     | Introd   | duction                                                 | 1  |

|        | 1.1      | Design Specifications.                                  | 3  |

|        | 1.2      | Overview                                                | 4  |

| 2.     | Revie    | ew of Medical Instrumentation and Biological Recordings | 7  |

|        | 2.1      | Introduction                                            | 7  |

|        | 2.2      | Amplifiers for Medical and Biological purposes          | 8  |

|        | 2.3      | Microstructures and microtechniques                     | 14 |

| 3.     | Bio-a    | mplifier Design                                         | 17 |

|        | 3.1      | Introduction                                            | 17 |

|        | 3.2      | Device Specifications, Layouts and Test Results         | 22 |

|        | 3.3      | Performance comparison with existing designs            | 26 |

|        | 3.4      | Packaging for Interaction with cells                    | 28 |

|        | 3.5      | Power Supply requirement of the Bio-Amplifier           | 30 |

| 4.     | Low      | Power Techniques                                        | 32 |

|        | 4.1      | Introduction                                            | 32 |

|        | 4.2      | Circuit Blocks.                                         | 33 |

|        |          | 4.2.1 Transistor                                        | 33 |

|    |         | 4.2.2 Current Mirror                                 | 34  |

|----|---------|------------------------------------------------------|-----|

|    |         | 4.2.3 Transconductor.                                | 36  |

|    |         | 4.2.4 Voltage Gain Units                             | 37  |

|    | 4.3     | Voltage Follower Technique                           | 38  |

|    |         |                                                      |     |

| 5. | Low V   | Voltage Techniques applied to the Bio-Amplifier      | .46 |

|    | 5.1     | Voltage Follower                                     | .46 |

|    | 5.2     | Level Shifting.                                      | .47 |

|    | 5.3     | Design Considerations.                               | .49 |

|    | 5.4     | Noise Analysis                                       | .53 |

|    | 5.5     | Test and Measurement Results.                        | 54  |

|    | 5.5.1.1 | Amplifier with PMOS differential pair and NMOS input |     |

|    |         | stage                                                | 54  |

|    | 5.5.1 2 | 2 Discussion of Measurement Results                  | 55  |

|    | 5.5.2.1 | Amplifier with NMOS differential pair and PMOS       |     |

|    |         | input                                                | 57  |

|    | 5.5.2 2 | 2 Discussion of Measurement Results                  | 59  |

|    | 5.5.3.1 | Amplifier with Source Follower configuration.        | .59 |

|    | 5.5.3 2 | 2 Discussion of Measurement Results                  | 61  |

|    | 5.6     | Conclusions                                          | .61 |

|    |         |                                                      |     |

| 6. | Wirele  | ess Transmission System                              | 63  |

|    | 6.1     | Introduction                                         | .63 |

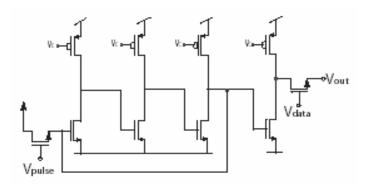

|      | 6.2   | Voltage Controlled Oscillator                               | 64 |

|------|-------|-------------------------------------------------------------|----|

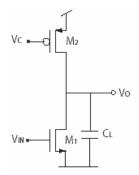

|      | 6.3   | Pre-Amplifier                                               | 66 |

|      | 6.4   | Power Amplifier.                                            | 67 |

|      |       | 6.4.1 Choice of Scheme for Power Amplifier                  | 67 |

|      |       | 6.4.2 Choice of Passive elements and transistor dimensions. | 69 |

|      |       | 6.4.3 Improvement of performance of the PA for ASK          |    |

|      |       | scheme                                                      | 70 |

|      |       | 6.4.4 Realization of On-Chip Inductors                      | 71 |

|      | 6.5   | Layouts                                                     | 74 |

|      |       |                                                             |    |

| 7.   | RF T  | est and Measurement                                         | 77 |

|      | 7.1   | Inductance                                                  | 77 |

|      | 7.2   | VCO                                                         | 78 |

|      | 7.3   | Pre-Amplifier                                               | 80 |

|      | 7.4   | Transmitter                                                 | 80 |

|      | 7.5   | Conclusions.                                                | 82 |

|      |       |                                                             |    |

| 8.   | Conc  | lusions                                                     | 84 |

|      | 8.1   | Amplifiers                                                  | 84 |

|      | 8.2   | Wireless Transmission System.                               | 85 |

|      | 8.3   | Future Work                                                 | 85 |

|      |       |                                                             |    |

| Appe | endix |                                                             | 87 |

| A.1           | Principle of operation of a Class F PA | 37 |

|---------------|----------------------------------------|----|

| A.2           | Realization of a class F PA9           | 90 |

| Bibliography. | 9                                      | 1  |

# LIST OF TABLES

| 3.1 | Dimensions of transistors used in the bio-amplifier                                    | 23 |

|-----|----------------------------------------------------------------------------------------|----|

| 3.2 | On-chip capacitors used in the bio-amplifier                                           | 23 |

| 3.3 | Characteristics of the bio-amplifiers                                                  | 25 |

| 3.4 | Performance of different instrumentation and neural amplifiers                         | 27 |

| 4.1 | Characteristics of the 2 <sup>nd</sup> order Filter at different voltage supply levels | 45 |

| 5.1 | Sizes of transistors used in the amplifiers.                                           | 52 |

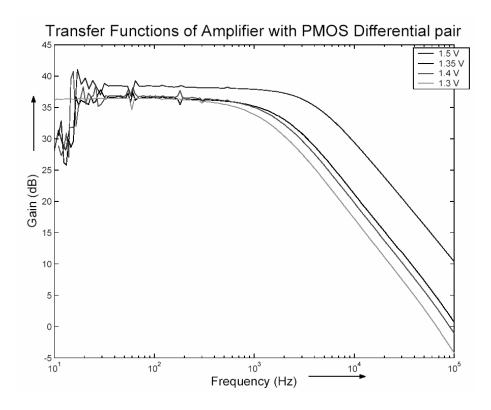

| 5.2 | Characteristics of amplifier with PMOS differential pair                               | 55 |

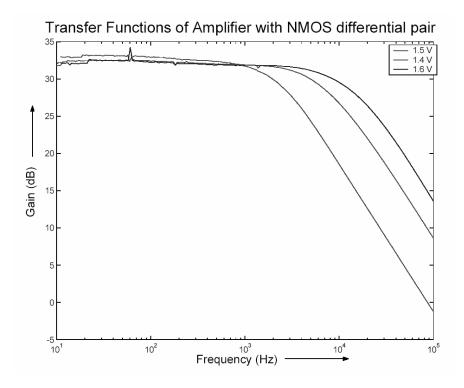

| 5.3 | Characteristics of amplifier with NMOS differential pair                               | 58 |

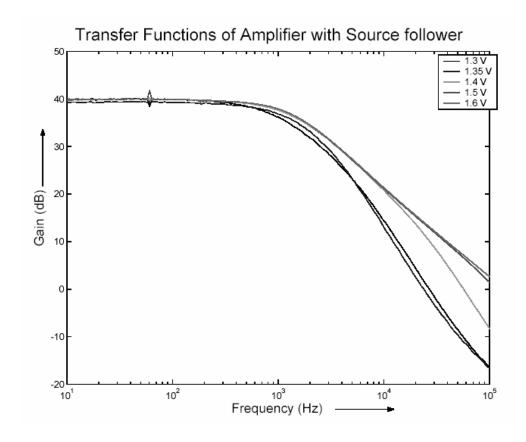

| 5.4 | Characteristics of amplifier with source follower and cascades                         | 60 |

| 6.1 | Sizes of active devices on chip.                                                       | 74 |

| 6.2 | On-chip capacitors realized with 2 poly layers                                         | 75 |

| 6.3 | Characteristics of the different inductors in the Power Amplifier                      | 75 |

# LIST OF FIGURES

| 1.1  | Cell Clinic capable of characterizing single cells                     |

|------|------------------------------------------------------------------------|

| 1.2  | Proposed integration of cell clinics and amplifiers for recording      |

|      | activity of cells                                                      |

| 2.1  | Electrode used for probing neural cells                                |

| 2.2  | Design to remove DC offsets at the membrane electrode interface10      |

| 2.3  | Low Power Low Noise amplifier for measuring extra-cellular             |

|      | activity11                                                             |

| 2.4  | Multiplexing signals and automation of recording process11             |

| 2.5  | Recording and wireless telemetry of extra-cellular activity12          |

| 2.6  | Neural transceiver that uses inductive power                           |

| 2.7  | Amplifiers to filter and sort neural spikes before transmission14      |

| 2.8  | High impedance seal technique using microstructures14                  |

| 2.9  | Setup for directly recording the activity of cells                     |

| 2.10 | Cell clinic for single cell sensing                                    |

| 3.1  | Schematic of the bio-amplifier                                         |

| 3.2  | Diode connected MOSFET to implement high resistance                    |

| 3.3  | Measured Characteristics of two reverse diode-connected MOSFETs18      |

| 3.4  | Operational Transconductance Amplifier                                 |

| 3.5  | Transfer Functions of the amplifiers for different power dissipation24 |

| 3.6  | Array of bio-amplifiers for direct recording from cells                |

| 3.7  | Setup for recording from cells using discrete components               |

| 4.1  | Simple transistor                                                      |

| 4.2  | Schematic of a current mirror                                                      | 34 |

|------|------------------------------------------------------------------------------------|----|

| 4.3  | Schematic of a basic transconductor                                                | 36 |

| 4.4  | Voltage gain units and their gain as a function of supply voltage                  | 38 |

| 4.5  | Improved transconductor structure for low voltage operation                        | 39 |

| 4.6  | Current conveyor configurations                                                    | 40 |

| 4.7  | Simulated transfer functions & Quality factors with variations in                  |    |

|      | $I_{in}(g_{m1}) \& I_{bias}(g_{m2})$                                               | 41 |

| 4.8  | Measured transfer function response of the improved transconductor a               | ıt |

|      | low voltage operation                                                              | 43 |

| 4.9  | 2 <sup>nd</sup> order low pass filter                                              | 43 |

| 4.10 | Transfer functions of the 2 <sup>nd</sup> order filter at different voltage levels | 44 |

| 5.1  | OTA modified with voltage follower for low voltage operation                       | 46 |

| 5.2  | OTA modified with level shifter for low voltage operation                          | 48 |

| 5.3  | OTA modified with voltage follower, and gain in the Level shifter                  |    |

|      | for low voltage operation.                                                         | 49 |

| 5.4  | Measured transfer functions of the amplifier with PMOS                             |    |

|      | differential pair                                                                  | 54 |

| 5.5  | Common mode equilibrium state with the output stage turned off                     | 56 |

| 5.6  | Resistor arrangement to prevent common mode equilibrium state                      | 57 |

| 5.7  | Measured transfer functions of the amplifier with NMOS                             |    |

|      | differential pair                                                                  | 58 |

| 5.8  | Measured transfer functions of the amplifier with source follower                  |    |

|      | and cascodes.                                                                      | 60 |

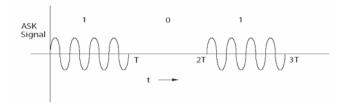

| 6.1  | ASK modulation scheme                                        | 63 |

|------|--------------------------------------------------------------|----|

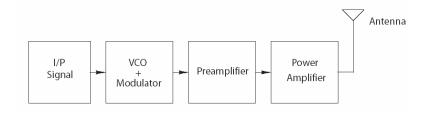

| 6.2  | Block diagram of the ASK transmitter                         | 64 |

| 6.3  | Single stage of the VCO.                                     | 64 |

| 6.4  | VCO and the ASK modulator.                                   | 66 |

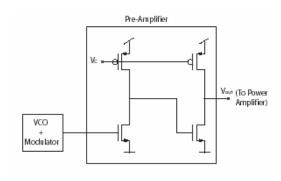

| 6.5  | VCO and the Pre-amplifier                                    | 66 |

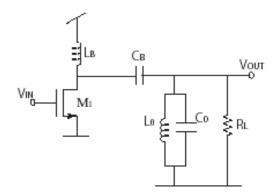

| 6.6  | Schematic of a general Power Amplifier                       | 67 |

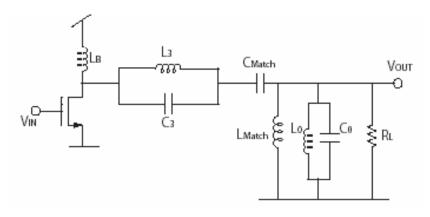

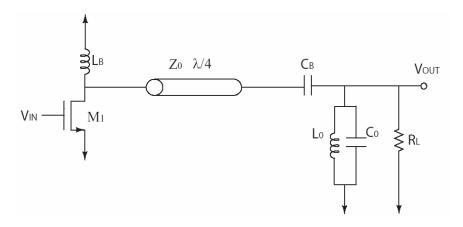

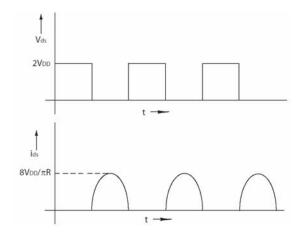

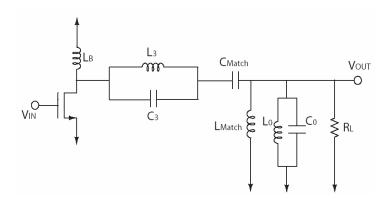

| 6.7  | Schematic of the class F Power Amplifier                     | 69 |

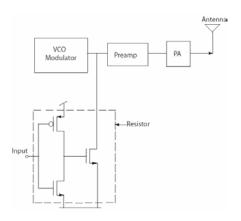

| 6.8  | Resistor to reduce power dissipation during '0' transmission | 71 |

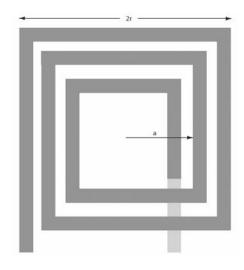

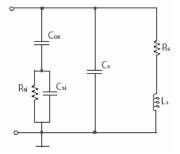

| 6.9  | Spiral Inductor                                              | 72 |

| 6.10 | Inductor's lumped model                                      | 72 |

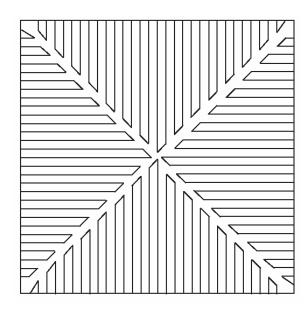

| 6.11 | Patterned Ground Shield to reduce substrate coupling         | 73 |

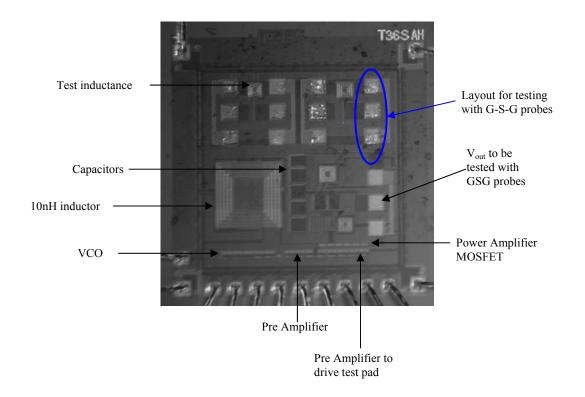

| 6.12 | Photograph of the ASK transmitter                            | 76 |

| 7.1  | Test inductance layout.                                      | 78 |

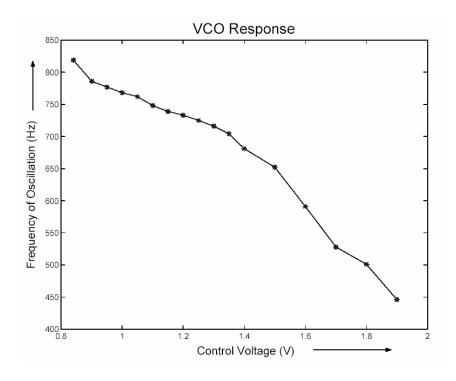

| 7.2  | Measurement results of the VCO                               | 79 |

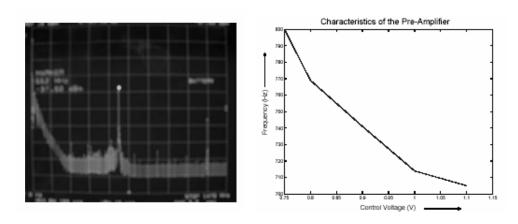

| 7.3  | Measured output of the Pre-amplifier.                        | 80 |

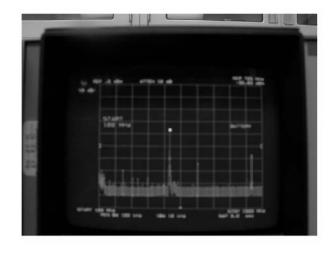

| 7.4  | Measured output response of the transmitter                  | 81 |

| A1   | Schematic of a class F Power Amplifier                       | 87 |

| A2   | Voltage and current waveforms of an ideal class F PA         | 89 |

| A 3  | Realization of the class F Power Amplifier                   | 90 |

### Chapter 1

### Introduction

A major challenge in the field of biology is the study of the response of individual and single cells to different stimuli. Previous studies in cell biology have been performed on cell cultures, and results from them have been used to understand the behavior of single cells. The ability to observe the responses of individual cells will provide insight into variations among cells as well as statistical distributions. This knowledge will help understand better the mechanisms behind cell secretions, cell metabolism and coding of protein information [1, 2, 9, 10]. Interfacing of single cells to analyze different types of blood cells can be found in [2, 9, 10]. We are attempting to develop integrated microstructures and microelectronics that would help study the response of single cells, and also of groups of cells.

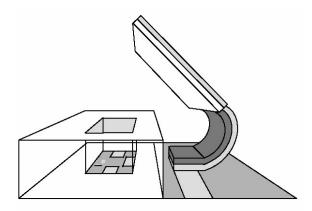

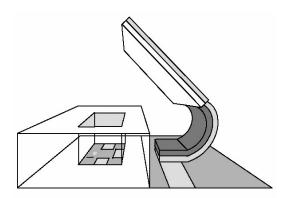

Various attempts have been made at developing microprobes [22, 23, 25, 30] and microelectronic structures [1] that are capable of localizing and studying the response of individual cells. Abshire et. al. [1] have reported the design of microstructures called "Cell Clinics" that have a vial to contain the cells, and a plastic lid that can be closed to contain the cells. By fabricating the cell clinics on silicon substrate and having electrodes at the base, it is possible to monitor electrical properties of cells. A diagram of the cell clinic is shown in Fig. 1.1.

Fig. 1.1 Cell clinic capable of characterizing single cells [1]

The cells can be maneuvered towards the cell clinics by using techniques such as optical tweezing, micro fluidic manipulation, and dielectrophoresis [13, 17, 28]. We are conducting experiments to investigate optical tweezing and dielectrophoresis. Once the techniques to localize cells to these cell clinics have been perfected, we plan to conduct single cell experiments to understand responses from cells better. We also hope to modify the cell clinics to assist in experimental techniques like fluorescence probing, optical microscopy, and impedance analysis, chemical secretions of cells and recording of extra-cellular electrical activity.

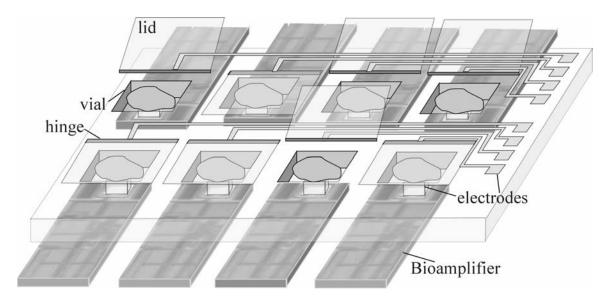

In my dissertation, I aimed at recording the extra-cellular activity of electrically active cells like cardiac and nerve cells. To achieve this goal, I focused on designing VLSI amplifiers (bio-amplifiers) that could be used to record the signals from these cells at the site of activity. The cell clinics are currently being fabricated on silicon substrate and will have a gold electrode at the base to enable electrical measurements. The bio-amplifiers that I designed could later be integrated with the cell clinics to enable recording responses from cells very close to the site of electrical activity.

Fig. 1.2 Proposed integration of cell clinics and amplifiers for recording activity of cells

In the second part of my thesis, I aimed at designing a short range wireless transmitter to transmit the data from the bio-amplifiers. The integration of this transmitter with the bio-amplifiers would enable the realization of untethered recording units, and remote sensing recording applications. It would also bring closer the realization of continuous monitoring of cells in moving creatures in their natural habitats.

### 1.1. Design Specifications

The extra-cellular response of these electrically active cells has frequency content in the low kHz range (1-5 kHz) and amplitudes in the 100s of  $\mu V$  range. They also have huge DC offsets (~100s of mV) which usually contain no useful information. Amplifiers to record their activity should be designed for bandwidths

in the range of 1-5 kHz, provide high gain with a good signal to noise ratio (SNR). They should also have the capability of rejecting the DC offsets that occur across the membrane of the cell. Low power operation of these amplifiers helps prevent heating effects that may disrupt the functioning of the cells. On-chip area and input referred noise are also important considerations in the design of these amplifiers.

The wireless transmitter should be designed to operate at high frequencies in order to allow for multiplexing of data from many bio-amplifiers onto one transmitter. The data from the bio-amplifiers can either be scanned and transmitted serially or transmitted based on the presence of activity. The range of communication need not be very large, and the complexity of the transmitter should be minimal in order to allow for integration with the rest of the recording structures and electronics.

#### 1.2. Overview

Keeping the above mentioned design specifications, we investigated and designed bio-amplifier schemes to record the extra-cellular activity of cells and a simple RF transmitter system to enable remote sensing of the bioelectric measurement setup. The rest of this document is organized as follows

Chapter 2: Review of Medical Instrumentation and Biological Recordings presents a literature review of some of the amplifier schemes that have been implemented for recording and monitoring signals from biological applications. In this section, I discuss the different amplifier schemes, the different

microstructures and the techniques that have been used in the literature to record activity of cells.

Chapter 3: Bio-Amplifier Design discusses the design, implementation and the measurement results of a CMOS integrated bio-amplifier that could be used for recording activity from electrically active cells. It also identifies scope for improvement in the designs for low power operation.

Chapter 4: Low Voltage Techniques deals with some of the low voltage techniques applied to CMOS designs that are of particular interest to our design. In this chapter, we also discuss the design and experimental measurements of a low power filter from which the low power techniques can be used to our bioamplifier.

Chapter 5: Low Voltage Low Power Bioamplifier discusses the implementation of low voltage low power bio-amplifiers from the basic design in chapter 3 and techniques from chapter 4. Different schemes are possible, and they are discussed in this chapter. We also present results and conclusions of our measurement in this chapter.

Chapter 6: Wireless Transmission System discusses the design of a short range wireless transmitter that implements a digital scheme of communication called Amplitude Shift Keying (ASK). The issues involved in the design and the parameters chosen are also discussed in detail.

Chapter 7: RF Test & measurement deals with the experimental procedure that was setup for measuring the output of our transmitter, and the results of our

measurement. We also placed a few test structures in our chips to help troubleshoot the system, and these are also discussed in this chapter.

Chapter 8: Conclusions and Future Work briefly summarizes this work, and presents techniques and suggestions for improving and integrating the designs developed here.

### Chapter 2

### **Review of Medical Instrumentation and Biological**

### **Recordings**

#### 2.1. Introduction

Understanding the metabolic activities of cells, chemical secretions from cells, the communication pattern, the overall functioning of the central nervous system and the muscular system on a single cell basis has been a major challenge and an active area of research in micro and cell biology in the past few years [7, 15, 28]. A better understanding of the protein patterns, metabolic activities and cell secretions will play an important role in the identification and cure of several diseases like cystic fibrosis, long QT syndrome [33]. The ability to identify and classify the spiking behavior of nerve cells will help in the realization of real-time direct interfaces between the brain and electronic and mechanical devices to help restore sensory and motor functions lost through injury or disease [31]. Another emerging field of research from the study of single cell behavior is bio-inspired circuits where neuronal systems are being implemented in silicon using adaptive algorithms and learning principles learned from biological cells.

Amplifiers and implantable microstructures capable of recording activity from cells have been a primary focus of research in the past few decades. In this chapter, we discuss a few amplifier schemes that have been developed for medical and instrumentation techniques, implantable micro probes with active circuitry, hardware designs to sort the activity of neural signals, and the introduction of telemetry to bioelectric applications.

#### 2.2. Amplifiers for Medical and Biological Purposes

One of the earliest micropower instrumentation amplifiers was designed by Degrauwe, et. al. [5]. Their design comprises a switched capacitor integrator structure that reduces the offset at the input and charge injection effects by an auto-zero technique. By using a single amplifier stage and a novel feedback method, they were able to achieve a stable configuration and a high CMRR amplifier operating from a voltage supply of 3V.

Staeyart et. al [38] describe the design of a micropower low noise amplifier for medical purposes. They designed a medical instrumentation amplifier of bandwidth 0.5 to 500 Hz and programmable bandwidths of 14/20/26/40 dB. The bandwidth is set by varying the values of resistors on chip. Their low frequency cut-off and their high frequency cut-off were selected by capacitors on chip. By sizing the transistors and choosing the bias current appropriately, they were able to obtain a low input equivalent noise voltage. They also introduced a term called the noise efficiency factor (NEF), which compares the input referred noise of any amplifier with that of a simple BJT amplifier with the same current drain and bandwidth. This gives a quantitative comparison between the performances of different amplifiers.

Implantable electrodes and multi-electrode arrays that enable on-site signal processing are key components for studying the nervous systems at the

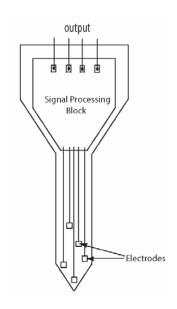

cellular level. Najafi et. al. [30] have developed multi-channel multi-electrode recording arrays that could be used for recording of extra cellular neural biopotentials. Their active probes comprise on-chip circuitry for amplifying, multiplexing and buffering neural signals recorded from open electrodes present on the probe. The block diagram of their electrode is shown in Fig 2.1.

Fig. 2.1 Electrode used for probing neural cells [30]

By integrating the signal processing block at the site of activity, leakage and noise associated with the low amplitude neural signals are minimized. It also minimizes packaging issues that arise in the use of multiple probes and having a wire bonded to each of the pads. The important factors that have to be considered in designing these implantable probes is the minimization of tissue damage, and long term reliability of the probe in the cell medium.

Ji et. al. [22, 23] demonstrated the multiplexing of recordings from open pads in an implantable probe. Their probe had the same structure as shown in Fig.

2.2, and they incorporated CMOS circuitry that enabled the electronic positioning of the recording sites with respect to the active neurons. They also multiplexed the amplified output signals. This feature of selectively recording has a tradeoff with respect to the number of simultaneous recording sites, but enables possibility of recoding from those sites that are more crucial to the active neurons. They also used adaptive algorithms to move the recording sites if the probe's relative position changes in implants.

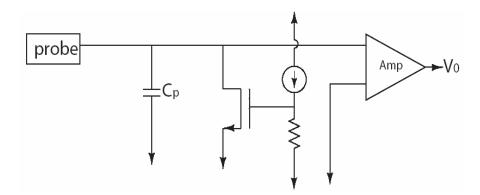

Signals from the cells have huge DC offsets, sometimes up to 100 times the magnitude of the signal. Chandran et. al. [3] introduced the addition of a very high resistor implemented using a saturated weak inversion MOSFET to the probe electrolyte interface to leak the DC offset. This resistance determines the low frequency cutoff of the measurement process. The schematic is shown in Fig. 2.2

Fig. 2.2 Design to remove DC offsets at the membrane electrode interface [3]

Harrison et. al. [16] introduced the design of a low power low noise CMOS amplifier for neural recording applications. They implemented a high resistor to leak out the DC offset with a diode connected MOSFET as described in

[6]. The small size and the low power consumption enabled the integration of a large number of amplifiers on to one single chip. They also reported successful recording from neurons. Their schematic is shown in Fig. 2.3

Fig. 2.3 Low power low noise amplifier for measuring extra-cellular activity [16]

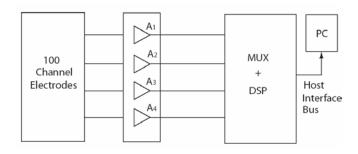

Advancements in the field of neural recordings to understand the brain and the central nervous system better require the ability to simultaneously monitor densely packed neural arrays. Guillory et. al. [14] have presented and demonstrated multiplexing techniques that enable the continuous monitoring of activity from a 100-channel system. This system can be interfaced with the multi-electrode and probe arrays discussed above. Fig. 2.4 shows a block diagram of their setup.

#### Fig. 2.4 Multiplexing signals and automation of recording process [14]

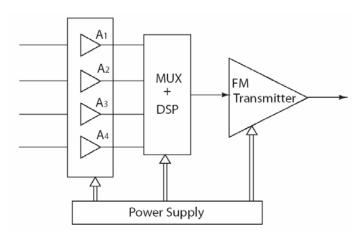

The integration of wireless telemetry to monitor and study the activity the behavior of neural cells enables long term neurophysiological studies of unanesthized and freely moving animals. Dorman et. al. [7] developed a multiplexing system and a wireless telemetry system to record and transmit the activity of neural cells. They used low noise JFET input stages for their amplifiers and reverse biased diode connections and reverse biased configurations to remove the DC offsets. The output of the recording amplifiers are multiplexed and fed into an FM transmitter. Block diagram of their schematic is shown in Fig. 2.5

Fig. 2.5 Recording and wireless Telemetry of extra-cellular activity [7]

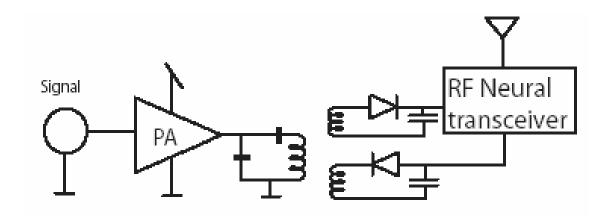

Irazoqui-Pastor et. al. [19, 20] have designed an implantable wireless neural recording device that frequency modulates and transmits neural signals. They use inductive power as replacement for batteries in their circuits. A wireless transmitter sends power to the inductive elements, which pick up the transmitted power and stores them in capacitors for the circuits to operate on. These circuits

amplify the neural recordings transmit the data through a wireless transmitter. Schematic of their design is shown in Fig. 2.6.

Fig. 2.6 RF Neural transceiver that uses inductive power [19]

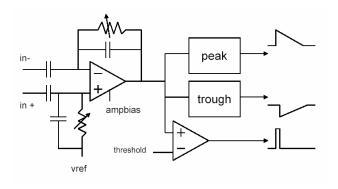

Horiuchi et. al. [18] designed and implemented a technique that helps in pre-filtering, sorting and classifying the neural spikes before transmission. This would greatly reduce the load on the transmitter, and increase efficiency in recordings. They used an amplifier that rejects DC offsets using a MOSFET resistor and the amplifier's low frequency roll off is controlled by an external voltage. The spike sorting is done with peak and trough detector structures designed on the chip. The schematic of their design is shown in Fig. 2.7.

Fig. 2.7 Amplifiers to filter and sort neural spikes before transmission [18]

### 2.3. Microstructures and Micro-techniques

To remove leakage and noise for efficient recordings of biological activity of cells, progress towards the integration of recording pads and signal processing units are being investigated. One technique to study extra-cellular activity is the usage of patch clamps, as shown in Fig. 2.8. A small suction is applied through the glass pipette and this creates a high impedance seal and restricts leakage currents. Pederson et. al. [33] demonstrated the use of silicon based orifice that would help realize a giga-seal. A small suction mechanism from the backside of the chip would help push the cell into the orifice. This technique can be used in the realization of large scale integrated circuits as described by Han. et. al.[15].

Fig. 2.8 High impedance seal technique using microstructures [33]

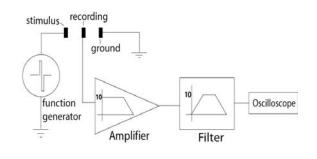

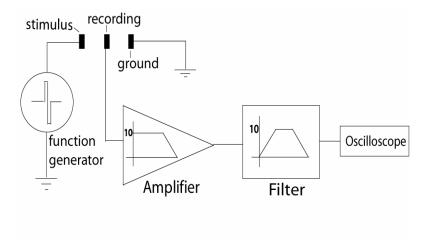

Another method to record activity of cells is to plate them on to electrodes, and realize amplifiers connected to these electrodes to record the extracellular activity of these cells. Reeves et. al. [37] have demonstrated extra cellular recordings from cells plated to electrodes and placed on a DIP package, and connected to external instrumentation filters and amplifiers. A block diagram of their schematic is shown in Fig. 2.9. Pancrazio et. al. [32] have also demonstrated activity from similar recording structures with the outputs being amplified, and multiplexed for interaction with PCs.

(a) The amplifier with epoxy for containing the electrolyte

(b) Block diagram of the measuring unit

Fig. 2.9 Setup for directly recording the activity of cells [37]

Jenkner et. al. [21] fabricated a silicon chip for two-way interfacing with neurons. The neurons were joined to each other by electrical synapse and to the chip by a capacitive stimulator and a recording transistor. The cells and the medium were contained in a perspex chamber made of glue, and the interfacing with the electronic circuitry was done by connecting the output pins to a standard DIP package.

Lorenzelli et. al. [25] reported the use of an ion sensitive field effect transistor (ISFET) for recording the pH variations of the medium due to cell metabolic activity. The changes in the pH cause a variation in the threshold voltage of the device and this shift is measured by sensor electronics. By integrating other sensing components like voltage regulators, multiplexers and band gap references, they automated the measurement and control process.

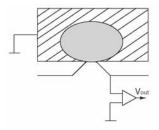

Abshire et. al. [1] describe integrated microstructures (cell clinics) and instrumentation for capture and characterization of individual cells. These cell clinics have a cell sized cavity and a closable lid that helps in the capture of cells. By placing gold electrodes at the base of the cell clinics, they enable the interfacing of electronic circuitry with cells. A block diagram of their cell clinic design is shown in Fig. 2.10.

Fig. 2.10 Cell clinic for single cell sensing [1]

In the next chapter, we discuss the design of a suitable amplifier that could be used for recording the biological activity of cells

### **Chapter 3**

### **Bio-amplifier Design**

### 3.1. Introduction

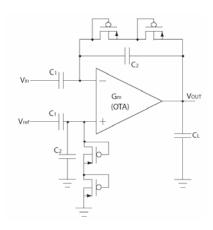

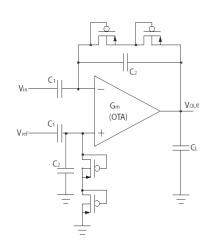

We describe a bio-amplifier that is suitable for direct recording of signals from electrically active cells. The main constraints in the design are the requirement of low input referred noise, low power consumption, and a small area on chip. It should also have the capability of removing any DC offsets from the input. We describe a bio-amplifier that addresses the above issues [16]. It comprises on an Operational Transconductance Amplifier (OTA) coupled in capacitive feedback configuration, as shown in Fig. 3.1.

Fig 3.1 Schematic of the bio-amplifier [16]

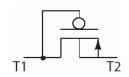

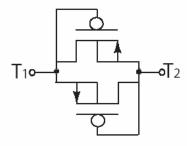

To reduce DC offsets at the input and the output, a high resistance can be used in parallel with the feedback capacitor [16]. The resistor may not be easily realizable on chip due to area considerations. A high resistance can be implemented by a MOS transistor controlled by an external voltage, or by using a diode connected MOSFET [6] as shown in Fig. 3.1. When the terminal  $T_1$  is

negative relative to T<sub>2</sub> (refer Fig. 3.2a), the gate source voltage is negative and the MOSFET channel is turned on. The MOSFET now has the gate connected to the drain and behaves like a diode. For low voltages, the current voltage relationship is exponential due to the sub-threshold region operation, and follows a square law relationship in the above threshold region. On the other hand, when the voltage of T<sub>1</sub> is greater than T<sub>2</sub>, the parasitic p-n-p transistor, with the source, the n-well, and the drain acting as the emitter, base and collector respectively is turned on. Since the base and the collector are shorted, the device behaves like a diode with exponential current voltage relationship.

(a) Diode connected MOSFET [6]

(b) Setup for measurement

Fig. 3.2 Diode connected MOSFET to implement high resistance

a. Current voltage characterisitic

b. Resistance as function of voltage

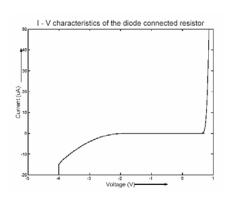

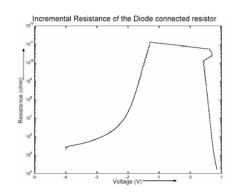

Fig. 3.3 Measured characteristics of two diode-connected MOSFETs (setup shown in Fig. 3.2 b)

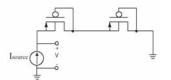

The voltage current relationship across a series combination of two diode connected MOSFETs (setup shown in Fig. 3.2(b)) was measured. The reason for

using two of these devices in series is to reduce distortion for large input signals. The measurement was made by varying the bias current from the pico ampere to micro ampere using a current source unit (Keithley 216). The voltage drop across the device was measured, and the resistance was calculated from the readings. We notice that at very low currents, the back diode connected device has a very high incremental resistance (R<sub>inc</sub>), and hence can be used as a high resistor which helps set the DC point. The kink at around 0.5V is because the voltage readings were fluctuating for bias currents in the 10 pA range. The reason for choosing a PMOS transistor is that the fabrication process is done on a p-substrate which will be connected to the most positive voltage of the circuit. Hence we would not be able to control the bulk voltage of the NMOS transistor as shown in Fig. 3.2(a). The PMOS transistor is fabricated in an N-well giving us the freedom to control the bulk voltage.

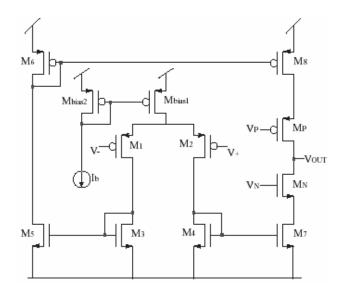

The midband gain of the amplifier is given by  $C_1/C_2$ . The low frequency roll-off is given by the combination of  $C_2$  and  $R_{inc}$  and is given by  $\frac{1}{2\pi R_{inc}C_2}$ . The high frequency roll off is determined by the output load capacitance and the equivalent resistance at output node. Cascodes are used at the output to increase the open loop gain of the OTA. The schematic of the OTA is shown in Fig. 3.4. Bias voltages for the cascade transistors were given from off chip potentiometer arrangements.  $M_{bias2}$  enables the control of amount of power supplied to bias the amplifier.

Fig 3.4 Operational Transconductance Amplifier

In designing the bio-amplifier, it is important to reduce the input referred noise voltage. The dominant noise sources in a MOSFET are the thermal and the flicker noise components [24]. The input referred noise voltage of a single MOSFET is given by [24].

$$\overline{V_n^2} = \left(\frac{4kT\gamma}{g_m}\right) + \left(\frac{KF * I_D^{AF}}{C_{ox} * f}\right) * \left(\frac{1}{g_m^2}\right)$$

(3.1)

where kT is the thermal voltage,  $\gamma$  is a constant equal to ½ for subthreshold devices, and 2/3 for transistors in the srong inversion region,  $g_m$  is the transconductance of the MOSFET,  $C_{ox}$  is the gate oxide capacitance, AF and KF are empirical constants equal to 1 and  $10^{-25}$  respectively, and f is the frequency of operation. The first term corresponds to the thermal noise component (white noise), and the second component to the flicker noise component (colored noise).

We choose  $M_1$  and  $M_2$  to be identical,  $M_3$ ,  $M_4$ ,  $M_5$ , and  $M_7$  to be identical. The input referred noise of the OTA is calculated using transfer function analysis, and is given by (3.2).

$$\overline{V_{inOTA}^2} = 2\overline{V_{n1}^2} + 4\left(\frac{g_{m3}}{g_{m1}}\right)^2 \overline{V_{n3}^2} + 2\left(\frac{g_{m6}}{g_{m1}}\right)^2 \overline{V_{n6}^2} + \left(\frac{g_{mN}}{g_{m1}}\right)^2 \overline{V_{nN}^2} + \left(\frac{g_{mP}}{g_{m1}}\right)^2 \overline{V_{nP}^2}$$

(3.2)

where  $g_{mN}$  is the transconductance of transistor N and  $V_{nN}$  is the input referred noise of transistor N. From the above equation, we notice that the input referred noise can be reduced by increasing the  $g_m$  of the transistors  $M_1$ ,  $M_2$ , and reducing the  $g_m$  of  $M_3$ ,  $M_4$ ,  $M_5$ ,  $M_6$ ,  $M_N$  and  $M_P$ . We also notice that the OTA has three inherent poles, two at  $g_{m3}/C_3$  and one at  $g_{m6}/C_6$ . Hence, the reduction in the sizes of  $M_3$ ,  $M_4$ ,  $M_5$ , and  $M_6$  will lead to a reduction in the phase margin of the circuit. To maintain stability, they cannot be reduced arbitrarily. As described by Harrison [16], the input referred noise of the bio-amplifier can be calculated from (3.3).

$$\overline{V_{in-AMP}^{2}} = \overline{V_{in-OTA}^{2}} \left( \frac{C_{1} + C_{2} + C_{in}}{C_{1}} \right)^{2}$$

(3.3)

For a typical gain of 100, the input referred noise of the bio-amplifier is almost the same as that of the OTA, and a reduction in the noise level of the OTA will lead to an equal reduction in the noise level of the bio-amplifier. Another important figure of merit in the design of an amplifier is the Noise Efficiency Figure (NEF) [39] which is defined as the noise generated by the amplifier relative to the noise generated by a single bipolar junction transistor amplifier having the same total current and bandwidth. The lower the NEF, the better is the performance of the circuit, and the best possible NEF is by that of a single stage BJT amplifier and is equal to 1. The formula for calculating the NEF is given by [39] and is shown in (3.4).

$$NEF = V_{ni,rms} \sqrt{\frac{2I_{tot}}{\pi \cdot U_T \cdot 4kT \cdot BW}}$$

(3.4)

where  $V_{ni,rms}$  is the input referred noise voltage,  $I_{tot}$  is the total current in the circuit,  $U_T$  is the thermal voltage, k is the Boltzmann constant, T is the absolute temperature, and BW is the bandwidth of the circuit.  $V_{ni,rms}$  is the equivalent noise source and is calculated by integrating the input referred noise over the bandwidth of the circuit.

## 3.2. Device Specifications, Layouts, and Test Results

The circuits were designed using scalable CMOS design rules and fabricated through MOSIS in a commercially available 0.5µ CMOS process. We designed bio-amplifiers of gains 20, 40 and 100 for test purposes. In choosing the sizes of the transistors, we chose a high W/L for the input differential pair, a large enough L for the current mirror transistors in order to reduce the Early effect, and to increase the matching, and sufficiently long devices for the cascade transistors in order to boost the gain [38]. The device sizes of the individual transistors are

specified in Table 3.1 The value of  $C_2$  was chosen to be greater than 200 pF so as to reduce the effect of fringing capacitances and the interconnect capacitances.  $C_1$  was chosen to give the appropriate gain.  $C_1$  and  $C_2$  were placed on chip, and  $C_L$  was off chip, and included the loading of the measurement stage too. Their chosen values are listed in Table 3.2.

| Transistor                                                        | Width | Length |  |

|-------------------------------------------------------------------|-------|--------|--|

| $M_1, M_2$                                                        | 35μm  | 2.1µm  |  |

| M <sub>3</sub> , M <sub>4</sub> , M <sub>5</sub> , M <sub>7</sub> | 3.5µm | 3.5μm  |  |

| M <sub>6</sub> , M <sub>8</sub>                                   | 7μm   | 3.5µm  |  |

| $M_N$ , $M_P$                                                     | 7μm   | 7μm    |  |

Table 3.1 Dimensions of transistors used in the bio-amplifier

| Amplifier Gain | C <sub>1</sub> | C <sub>2</sub> |

|----------------|----------------|----------------|

| 26 dB          | 10pF           | 0.5pF          |

| 32 dB          | 20pF           | 0.5pF          |

| 40 dB          | 20pF           | 0.2pF          |

Table 3.2 On-chip capacitors used in the bio-amplifier

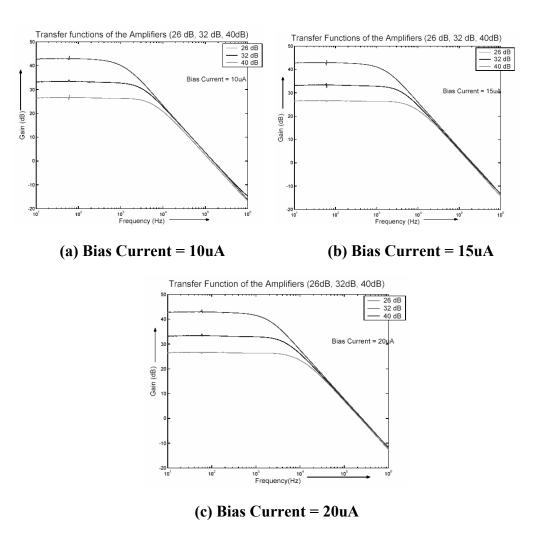

The output node is a high impedance node and is typically used for driving another on-chip stage. In designing the test fixture for characterizing the amplifier, we reduced the loading capacitance by using a commercially available op-amp in source follower configuration to buffer the output stage. The transfer functions of the amplifiers were measured using a Spectrum Analyzer (Agilent 4395A), and the bias current was supplied from a current source unit (Keithley 236). The transfer function measurements of the bio-amplifier are plotted in Fig. 3.5, and the characteristics of the amplifier are tabulated in Table 3.2.

Fig. 3.5 Measured transfer functions of the amplifiers for different power dissipation

| Bias<br>Current | Power | Gain<br>(dB) | Bandwidth | I/p referred<br>noise | Phase<br>Margin | NEF   |

|-----------------|-------|--------------|-----------|-----------------------|-----------------|-------|

|                 |       | 42.29        | 1.16 kHz  | 1.167 μV              | 85.69°          | 6.113 |

| 10 μΑ           | 60 μW | 32.84        | 3.55 kHz  | 2.6 μV                | 82.6°           | 7.78  |

|                 |       | 26.36        | 6.15 kHz  | 9.7 μV                | 86.7°           | 22.1  |

|                 |       | 42.49        | 1.61 kHz  | 1.21 μV               | 84.16°          | 6.588 |

| 15 μΑ           | 90 μW | 32.84        | 4.41 kHz  | 2.93 μV               | 80.9°           | 9.64  |

|                 |       | 26.37        | 8.21 kHz  | 11.3 μV               | 85.21°          | 27.25 |

|                 |       | 42.36        | 1.96 kHz  | 1.303 μV              | 82.92°          | 7.425 |

| 20 μΑ           | 120   | 32.88        | 5.188 kHz | 3.23 μV               | 79.43°          | 11.31 |

|                 | μW    | 26.36        | 10.21 kHz | 11.4 μV               | 83.70°          | 28.46 |

Table 3.3 Characteristics of the bio-amplifiers (Voltage Supply = 3V)

The designed gains were obtained, and these amplifiers appear to be suitable for integrating with the cell clinics microstructures. Their input referred noise levels in the  $1.2\mu V$  -  $11.5\mu V$  is also acceptable as extra-cellular signals have amplitudes of about  $100\mu V$ . Flicker noise is the main component of noise for these amplifiers, and corner frequencies occur in the order of 100s of kHz. As expected, the noise levels increase with an increase in the total current level and

with an increase in the bandwidth. However, noise voltage levels do not vary as the square root of the bandwidth as the principal component is flicker noise. The use of PMOS transistors at the input stage has reduced the flicker noise, and hence the overall noise performance of the circuit.

The bandwidth is degraded because of the loading of the pins in the DIP package through which the output was recorded. An improvement in the bandwidth can be achieved by using on-chip loading and output driving stages to follow the amplifiers. NEF is inversely proportional to the square root of bandwidth, and hence an increase in the bandwidth would also lead to an improvement in the NEF of the bio-amplifiers.

### 3.3 Performance comparison with existing designs

A brief discussion of the designs and implementations of different schemes of instrumentation and neural recording amplifiers has been presented in Chapter 2. In this section, we discuss the performance metrics and characteristics designs listed in the literature. The characteristics of different amplifiers are presented in Table 3.4.

Some of the parameters for the table have not been reported by the authors, and are shown by a '-' indicating missing data. All amplifiers reported here are capable of rejecting DC offsets at the input.

| Authors                         | Voltage | Current | Power       | Bandwidth | I/p<br>referred | NEF  |

|---------------------------------|---------|---------|-------------|-----------|-----------------|------|

|                                 |         |         |             |           | noise           |      |

| Degrauwe et. al. [5]            | 3 V     | 7 μΑ    | 21 μW       | 4 kHz     | 79 μV           | 130  |

| Staeyart et. al. [39]           | 5 V     | 31 μΑ   | 155<br>μW   | 0.570 kHz | 8.2 μV          | 74   |

| Najafi et. al. [30]             | 3 V     | 44.3 μΑ | 133<br>μW   | 6.5 kHz   | -               | -    |

| Harrison et. al.                | 5 V     | 16 μΑ   | 80 μW       | 7.2 kHz   | 2.2 μV          | 4    |

| Irazoqui-Pastor<br>et. al. [20] | -       | -       | -           | 10 kHz    | 8 μV            | -    |

| Horiuchi et. al.                | 2 V     | 0.62 μΑ | 1.325<br>μW | 9 kHz     | 27 μV           | 8.94 |

| Bio-amplifier described here    | 3 V     | 20 μΑ   | 60 μW       | 1.16 kHz  | 1.17 μV         | 6.11 |

Table 3.4 Performances of different instrumentation and neural amplifiers

The current and the power levels reported for our amplifier are in close agreement with other designs reported in the literature. The bandwidth of the bioamplifier can be improved by using on-chip driving stages at the output. NEF varies inversely as the square root of the bandwidth, and hence an increase in the bandwidth would reduce the NEF of the bio-amplifier. The input referred noise of the amplifier is significantly low due to the use of PMOS input devices which have lower flicker noise than NMOS devices. The NMOS current mirrors have been sized much smaller than the input stage PMOS devices, and that reduces the noise contribution from the later stages.

Power consumption of our circuit can also be reduced by pushing the devices into sub-threshold region of operation. Horiuchi et. al. [18] achieves low power operation at 1.3  $\mu$ W by operating the transistors in the sub-threshold region. In the next two chapters, we identify the limitations on voltage supply reduction to our amplifiers, and implement techniques to reduce the voltage supply and power consumption of the bio-amplifier.

## 3.4. Packaging for Direct Interaction with Cells

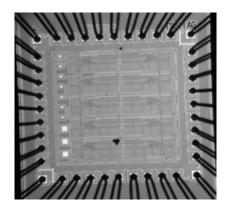

The bio-amplifier was then designed with provision for direct loading of cells. We designed an array of ten bio-amplifiers with bare aluminum pads as input. The design specifications and the layouts are exactly the same as discussed above. They were tested by applying an input signal through a passive probe and the output was observed on an oscilloscope. It gave a gain of 40 dB, and a bandwidth of 1.8 kHz as discussed in 3.2. The photograph of the array of bio-

amplifiers is shown in Fig. 3.6. These input pads to the amplifiers have to be plated with gold for bio-compatibility.

Fig. 3.6 Array of bio-amplifiers for direct recording from cells

Prior to plating of the amplifier directly with cells, we made measurements with a passive test fixture, where the cells where plated to the pads of an empty chip, and their activity was detected with discrete amplifiers and filters. The test fixture and the results of the measurement are shown in Fig. 3.7. This arrangement is more prone to noise and loss of signal strength due to the distances that the low power content signal has to travel before being amplified.

Fig. 3.7 Setup for recording from cells using discrete components

### 3.5. Power Supply Requirement of the Bio-amplifier

Voltage supply requirement is an important parameter in the design of the bio-amplifier, as we will be working with arrays of bio-amplifiers interfaced with cells. In this section, we identify the power supply requirements of the bio-amplifier. The above mentioned design works well with a power supply of 3V from  $V_{dd}$  to  $V_{ss}$ . The minimum required power supply for the entire circuit can be found out by tracing all the paths from  $V_{dd}$  to  $V_{ss}$ . They are listed in 3.5

$$V_{dd} - V_{SS} = V_{DSAT5} + V_{DSAT6}$$

(3.5a)

$$V_{dd} - V_{SS} = V_{GS3} + V_{OD3} + V_{DSAT1} + V_{DSATMbias1}$$

(3.5b)

$$V_{dd} - V_{SS} = V_{DSAT7} + V_{DSATN} + V_{DSATP} + V_{DSAT8}$$

(3.5c)

where  $V_{dd}$  and  $V_{SS}$  are upper and lower supply voltages,  $V_{DSATx}$  is the drain source saturation voltage of transistor x,  $V_{GSx}$  is the gate source voltage of transistor x, and  $V_{ODx}$  is the over-drive voltage of transistor x. Since the amplifier uses negative feedback, the output voltage  $V_{OUT}$  and the input voltages  $V_{\{+,-\}}$  should be at the same potential. This introduces a new path which has to be considered while reducing the power supply. The power supply requirement for that path is given by (3.5d). If M1 and M2 are operated in weak inversion, then  $V_{OD1}$  may not be of concern in the design.

$$V_{dd} - V_{SS} = V_{DSAT7} + V_{DSATN} + V_{SG1} + V_{OD1} + V_{DSATMbias1}$$

(3.5d)

The voltage supply requirement given by 3.4c and 3.4d are significantly higher than the requirements given by 3.4a and 3.4b. These are the limiting factors in the reduction of the power supply of the OTA. In the next chapter, we analyze a few low voltage techniques that have been applied to CMOS circuit design. In chapter 5, we apply these methods to reduce the power supply requirement of our bio-amplifier.

# **Chapter 4**

# **Low Power Techniques**

### 4.1. Introduction

Low power techniques are important for integrated circuits as they enhance the level of integration by limiting heating effects and enable operation from single cell batteries. With processes scaling down to the submicron level and the voltage levels accordingly, and switching speeds of digital circuits reaching the GHz range, different techniques for the reduction of power supply and voltage levels are necessary and are being implemented. These low power techniques play an important role in the design of various portable devices like electronic watches, low power calculators, and hearing aids. They have also gained considerable importance in the design of implanted biomedical devices like cardiac pace setters and neural amplifiers.

Circuits described here are intended to directly record the activity of live cells. The need for low power circuits is important to prevent the evaporation of the electrolyte, and to prevent any temperature disturbance of the normal operation of these cells. The use of low power techniques also limits the temperature gradients from circuit power dissipation. Besides, the use of low power amplifiers will also enable integration of amplifiers with large arrays of recording microstructures and microelectrodes.

In the design of analog circuits, the reduction of voltage and current levels usually involves tradeoffs in dynamic range and speed. Most of these tradeoffs are

generally accepted and can be minimized by implementing different circuit techniques. In this chapter, we discuss some of the blocks used in our amplifier design, and the tradeoffs involved in low power operation.

### 4.2. Circuit Blocks

#### 4.2.1. Transistor

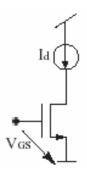

Fig. 4.1 Simple transistor

The transistor can be either in the strong inversion or the weak inversion region depending on whether its gate to source voltage is above or below its threshold voltage. The current and the transconductance  $(g_m)$  of the transistor are higher in strong inversion region. To enable power reduction techniques, the current levels are pushed down requiring the transistors to be biased in the weak inversion region. This reduces the  $g_m$  of the transistors. To compensate for the reduction in  $g_m$ , the aspect ratios (W/L) have to be increased.

The primarily dominant noise sources in a MOSFET are thermal and flicker noise. The input referred noise of the MOSFET M<sub>1</sub> shown in Fig. 1 is given by (3.1) Biasing the transistor in the subthreshold region enables low power operation by reducing the current levels. The saturation voltage of the transistors is also only about 80mV, and hence lower power supply levels can be reached.

The cost of operation in the subthreshold region is the reduced transconductance and increased input referred noise.

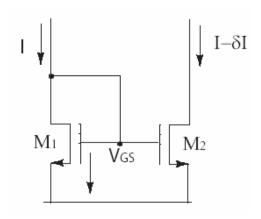

### 4.2.2. Current Mirror

Fig. 4.2 Schematic of a current mirror

A simple current mirror schematic is shown in Fig. 4.2. It is widely used in the design of analog circuits [38], and its matching properties are very important. Mismatch in current mirrors has been studied and modeled by various research groups [34, 8]. The variation between the two drain currents arises mainly due to variations in the threshold voltages and the sizes of the two transistors in the fabrication processes. A simple first order derivation for the mismatch ( $\Delta I_d$ ) can be derived as follows [11, 34].

$$I_{d} = \beta (V_{GS} - V_{T0})^{2}$$

$$\Rightarrow \Delta I_{d} = (V_{GS} - V_{T0})^{2} (\Delta \beta) + \beta (\Delta (V_{GS} - V_{T0})^{2})$$

$$\Rightarrow \frac{\Delta I_{d}}{I_{d}} = \frac{(\Delta \beta)}{\beta} - \left(\frac{2\Delta V_{T}}{(V_{GS} - V_{T0})}\right)$$

(4.1)

where  $\beta = {}^{\mu C_{OX}W}/L$ , and  $V_{T0}$  is the threshold voltage of the MOSFETs. The standard deviation  $\sigma$  (I<sub>d</sub>) of the current mismatch is given by (4.2)

$$\frac{\sigma^2(I_d)}{I_d^2} = \frac{4\sigma^2(V_{T0})}{(V_{GS} - V_{T0})^2} + \frac{\sigma^2(\beta)}{\beta^2}$$

(4.2)

where the  $\sigma_x$  is the standard deviation of x. At moderate and weak inversion operation, this mismatch term is given by (4.3)

$$\frac{\sigma^2(I_d)}{I_d^2} = \left(\frac{g_m}{I_d}\right)^2 \sigma^2(V_{T0}) + \frac{\sigma^2(\beta)}{\beta^2}$$

(4.3)

The first term models the mismatch effect due to variations in the threshold voltages, and the second term the effect due to the variations due to size mismatch. We observe that biasing the transistors in strong inversion can reduce the threshold voltage mismatch factor. Weak inversion topologies are generally not preferred for current mirrors as  $\frac{g_m}{I_d}$  ratio is highest for a transistor at weak inversion.

The second term models the mismatch effect due to size variations. Increasing the width and the length of the transistors can reduce the size mismatch factor. Choice of minimum length transistors is not preferred for current mirrors also due to the Early voltage effect. For submicron processes, and short/narrow devices, this first order approximation cannot be used as fabrication parameters play an important role. A more rigorous analysis for submicron processes has been done in [8], and their results follow a similar trend to 4.1 for long and wide devices, and devices operating the strong inversion region.

In reducing the voltage supply of our amplifier, care should be taken to account for the strong inversion of the current mirror.

### 4.2.3. Transconductor

Fig. 4.3 Schematic of a basic transconductor

The basic transconductor shown in Fig. 4.3 is a building block in many analog amplifier configurations. It comprises a differential pair  $(M_1 \text{ and } M_2)$ , a current mirror  $(M_3 \text{ and } M_4)$ , and a current source  $(M_{bias})$ . The voltage supply requirement for this configuration is determined by the requirement that all transistors are saturated, and the current mirror transistors are in strong inversion. Assuming perfectly matched devices, the voltage requirement is given by (4.4)

$$V_{dd} - V_{ss} = V_{T3} + V_{OD3} + V_{DSAT1} + V_{DSATMbias}$$

(4.4)

where  $V_{T3}$  is the threshold voltage of  $M_3$ ,  $V_{OD3}$  is the overdrive voltage of  $M_3$  to keep it in strong inversion,  $V_{DSATx}$  is the saturation voltage of transistor x.

Decreasing the current level can reduce the power consumption of this circuit. This can be achieved by operating the differential pair in the subthreshold region. To compensate the degradation in the transconductance due to the decrease in current levels, the aspect ratios of  $M_1$  and  $M_2$  have to be increased. The aspect ratio of the current mirror transistors should be small to reduce their gate source voltage. The current source  $M_{bias}$  can also be operated in the subthreshold region. Operating the transistors  $M_1$ ,  $M_2$  and  $M_{bias}$  in subthreshold region also reduces their saturation voltage, and this reduces the  $V_{dsat}$  terms of 4.4.

The input referred noise of this circuit can be calculated using transfer function analysis [24], and is given by (4.5)

$$\overline{V_i^2} = \overline{V_1^2} + \left(\frac{g_{m3}}{g_{m1}}\right)^2 \overline{V_3^2}$$

(4.5)

Designing the aspect ratios of the transistors so as to keep  $g_{m1}>>g_{m3}$  reduces the input referred noise of the circuit.

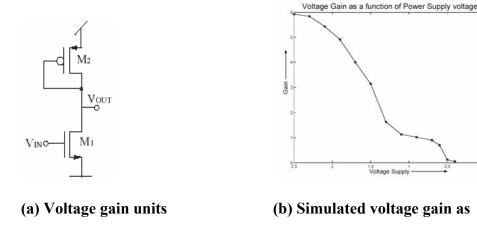

### 4.2.4. Voltage Gain Unit

Operating the transconductor in the subthreshold region with a very strict power budget will lead to a significant reduction in the transconductance and also the dynamic range. To compensate for this reduction, we used a voltage gain unit comprising a single stage common source transistor with a diode-connected load as shown in Fig.4.4a. Simulations for the gain of these units were made at different voltage supply levels using Cadence. The DC level of  $V_{\rm in}$  was varied to

keep the two transistors in saturation. The results of simulation are plotted in Fig. 4.4b.

Fig. 4.4 Voltage gain units and their gain as function of supply voltage

The gain of this stage is maximum when the two transistors are in strong inversion [40]. As the voltage supply of this circuit is reduced, the two transistors leave strong inversion and enter into the weak inversion region, and the overall gain is reduced. The input referred noise of this circuit is given by (4.6)

$$\overline{V_{in}^2} = \overline{V_1^2} + \left(\frac{g_{m2}}{g_{m1}}\right)^2 \overline{V_2^2}$$

(4.6)

function of supply voltage

By increasing  $g_{m1}$  to be much greater that  $g_{m2}$ , we can minimize the input referred noise of the voltage gain units.

## 4.3. Voltage Follower Technique

The power supply requirement of the basic transconductor is given by (4.4). The dominant term is the gate to source voltage of the current mirror transistors. The direct connection between the gate and the drain is to ensure that

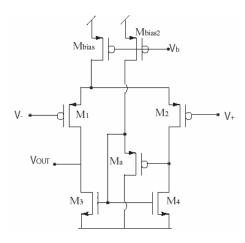

the gate voltage tracks the voltage changes in the drain, and also to maintain the output transistor in deep saturation. This connection can be removed and replaced with a voltage follower circuit [35] which drives the gate to track voltage changes in the drain as shown in Fig. 4.5

Fig. 4.5 Improved transconductor structure for low voltage operation [35]

It uses a PMOS current conveyor configuration as opposed to the more common NMOS current conveyor arrangement to drive the current mirror. The voltage supply requirement of the improved transconductor structure is given by

$$V_{dd} - V_{ss} = V_{T3} + V_{OD3} + V_{DSATMbias2}$$

(4.7)

The current source and the differential pair transistors are operated in the subthreshold region, and the current mirror is biased in the strong inversion. The transistor  $M_{bias2}$  need not support large currents and can be in weak inversion. By operating it in weak inversion, its saturation voltage can be reduced to about 80mV and the power supply requirement can be reduced. The differential pair transistors are made very large to improve the transconductance. The drain source saturation voltage of  $M_3$  and  $M_4$  is provided by the difference in the gate source voltages of  $M_4$  and  $M_a$ . Hence the aspect ratio of  $M_a$  has to be large to keep the

current mirror in strong inversion and in deep saturation. The input referred noise of this circuit is the same as shown in (4.6).

Schematics of the NMOS and the PMOS current conveyor circuits are shown in Fig. 4.6. Their small signal circuit models are exactly identical.

(a) NMOS Current conveyor

(b) PMOS Current conveyor

Fig. 4.6 Current conveyor configurations

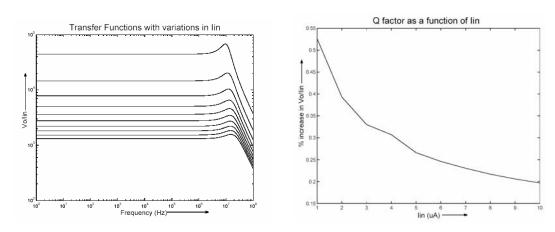

Te PMOS current conveyor was biased with a very small current to provide the saturation of the current mirror transistors at low supply voltages. This could potentially lead to a stability problem, and we performed a small signal analysis to analyze the same. The transfer function  $V_{out}/I_{in}$  is shown in (4.8).

$$\frac{V_0}{I_{in}} = \frac{g_{m2} + sC_2}{s^2 C_2 C_L + s \left(\frac{C_2}{r_{02}} + \frac{C_2 + C_L}{r_{01}} + g_{m1}C_2\right) + \left(g_{m1}g_{m2} + \frac{g_{m2}}{r_{01}} + \frac{1}{r_{01}r_{02}}\right)}$$

(4.8)

It is a second order response, and it has a peaking nature at high frequencies. The Q factor is given by (4.9)

$$Q = \frac{\sqrt{C_2 C_L \left(g_{m1} g_{m2} + \frac{g_{m2}}{r_{01}} + \frac{1}{r_{01} r_{02}}\right)}}{\frac{C_2}{r_{02}} + \frac{C_2 + C_L}{r_{01}} + g_{m1} C_L} \propto \sqrt{\frac{g_{m2}}{g_{m1}}}$$

(4.9)

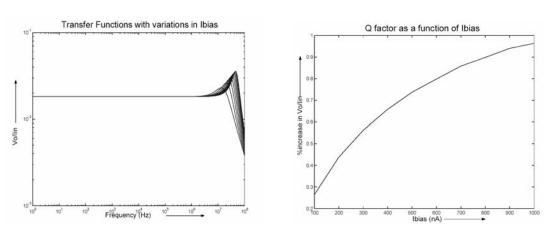

where  $C_2$  is the gate source capacitance of  $M_2$ ,  $r_{0x}$  is the output resistance of transistor x,  $g_{mx}$  is the transconductance or transistor x, and  $C_L$  is the loading capacitance of other transistors connected to that node. The results of simulations for different  $g_{m1}$  and  $g_{m2}$  are shown in Fig. 4.7.

### (a) Transfer function variation with Iin

### (b) Quality factor variation with Iin

(c) Transfer function variation with  $I_{in}$  (d) Quality factor variation with  $I_{in}$

Fig. 4.7 Simulated transfer functions & Quality factors with variations in

$I_{in}(g_{m1}) \ \& \ I_{bias}(g_{m2})$

Fig. 4.7(a) shows the variation of the quality factor for different values of  $g_{m1}$  with  $g_{m2}$  constant. There is a potential instability at frequency ranges of about 1 MHz, and is plotted in Fig. 4.7(b). This shows that for a given  $I_{bias}$ , it is better to have a higher  $I_{IN}$ . We chose  $I_{bias}$  to be 100nA, and  $I_{in}$  to vary from 1 $\mu$ A to 10 $\mu$ A for the simulations. Similarly, Fig. 4.7(c) shows the variation of the quality factor for different values of  $g_{m2}$  with  $g_{m1}$  fixed. For a given  $I_{IN}$ , it is better to have a lower  $I_{bias}$  to reduce the peaking nature of the response. The value of  $I_{in}$  was chosen to be 5 $\mu$ A and the bias current was varied from 100nA to 1 $\mu$ A for the simulations. These peaks occur at high frequencies of around 1 MHz, and can be avoided by operating the circuits at lower frequency ranges.

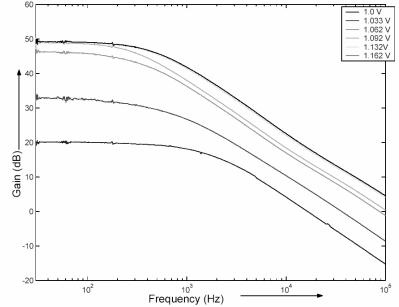

We designed a low voltage transconductor as described above. We tested the performance of the open loop gain of the transconductance amplifier at low voltage supplies of around 1V. A buffer was used whil making measurements. The results of the measurement are shown in Fig. 4.8.

The open loop gain of these transconductance amplifiers showed gains of over 20dB at a voltage supply level of 1V, and gains of over 50dB at 1.16V. Threshold voltages of the PMOS and the NMOS devices are 0.75V and 0.93 V, and that limited the power supply reduction of our design. Sub-volt operation of this transconductor can be achieved by amploying processes with lower threshold voltages.

Fig. 4.8 Measured transfer function response of the improved transconductor at low voltage operation

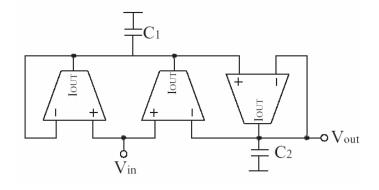

Using this transconductance amplifier, a low pass filter was developed as described in [35], to test the functionality of these transconductors at near 1 V operation. This filter could also be later used in RF communication systems. It is a second Bessel filter realized using the repetitive  $g_m$  C structures as shown in Fig. 4.9.

Fig. 4.9 2<sup>nd</sup> order low pass filter

Its transfer function is given by (4.10).

$$\frac{V_{out}}{V_{in}} = \frac{1}{1 + s \frac{C_1 + C_2}{2g_m} + s^2 \frac{C_1 C_2}{2g_m^2}}$$

(4.10)

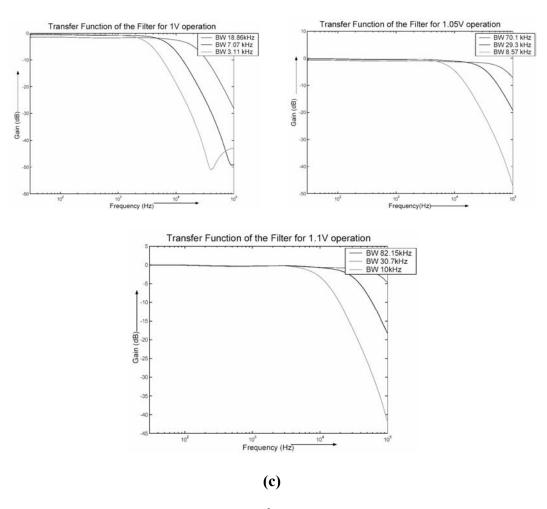

Varying the  $g_m$  of the transconductance structures can control the cutoff frequency. This in turn can be achieved by tuning the bias current. The test results of our filter at very low voltages, and different control voltages are shown in Fig, 4.10 and tabulated in Table 4.1.

Fig. 4.10 Transfer functions of the 2<sup>nd</sup> order filter at different voltage levels. The transfer functions are measured for different values of the control voltage, showing the tunable range of operation.

| Voltage Levels | Bandwidth | Gain      |

|----------------|-----------|-----------|

|                | 18.86 kHz | -1.5 dB   |

| 1 V            | 7.07 kHz  | -0.705 dB |

|                | 3.11 kHz  | -0.3 dB   |

|                | 70.1 kHz  | -1 dB     |

| 1.05 V         | 29.3 kHz  | -0.48 dB  |

|                | 8.57 kHz  | -0.37 dB  |

|                | 82.15 kHz | -0.29 dB  |

| 1.1 V          | 30.7 kHz  | -0.25 dB  |

|                | 10 kHz    | -0.226 dB |

Table 4.1 Characteristics of 2<sup>nd</sup> order filter at different voltage supply levels.

The transfer function of the filter was measured at various low voltage levels. At each power supply level, the bandwidth of the filter was controlled by varying its  $g_m$ , which was achieved by tuning the bias voltage. The filter gave a unity gain, and a high range for the bandwidth at voltage supply levels of 1.05V, and gives encouraging results for operating OTA based structures at around 1V.

The low voltage and the low power techniques described in this chapter are very significant to the amplifier that is described in chapter 3. The building blocks of the bio-amplifier described in chapter 3 essentially comprise transistors, current mirrors and a transconductor. In the next chapter, I discuss the applications of these principles to modify the bio-amplifier for low voltage low power operation.

# **Chapter 5**

# Low Voltage Techniques applied to the Bio-amplifier

The two main limitations in reducing the power supply for the bioamplifier is determined by the two paths given by 3.5c and 3.5d. In this chapter, we present methods that help us counteract these limitations.

### 5.1. Voltage Follower

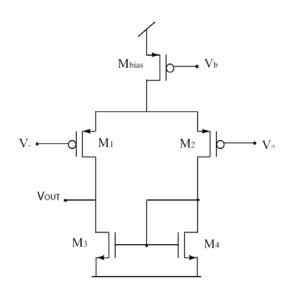

The voltage requirement in 3.5c arises primarily from the gate source voltage of the current mirror transistor  $M_3$ . This voltage cannot be reduced too much as that would lead to a degradation in the matching properties of the current mirror. We also note that the purposes of the drain source connections of  $M_3$  and  $M_4$  are to keep them in saturation and to make the voltage of the gate follow any changes in the drain voltage. This can be achieved by using the voltage follower circuit principle described in Section 4.3. The OTA modified with the voltage follower circuit is shown in Fig. 5.1

Fig. 5.1 OTA modified with voltage follower for low voltage operation

This arrangement echoes the current conveyor current mirror, using a PMOS rather than the more conventional NMOS source follower for an NMOS current mirror.  $M_a$  and  $M_b$  are connected in the source follower configuration which drives the gate of  $M_3$  and  $M_4$  to follow changes in their drain voltages. The drain source voltage of  $M_3$  is given by the difference in the gate to source voltages of  $M_3$  and  $M_a$ . By choosing a low value of  $I_{b1}$  and large aspect ratios for  $M_a$  and  $M_b$ ,  $M_3$  and  $M_4$  can be kept in saturation. The power supply requirement in that path is now given by

$$V_{dd} - V_{SS} = V_{DSAT3} + V_{DSAT1} + V_{DSATMbias1}$$

$$(5.1)$$

The dominant term in the power supply requirement is

$$V_{dd} - V_{ss} = V_{T3} + V_{OD3} + V_{DSATMbias 2}$$

(5.2)

where  $V_{DSATMbias2}$  corresponds to the saturation voltage of the transistor used to realize the current source  $I_{b1}$ . By biasing the transistor  $M_a$  and  $M_{bias2}$  in weak inversion, the  $V_{DSATMbias2}$  term can be reduced to 80 mV, thus reducing the power supply requirement in that path.

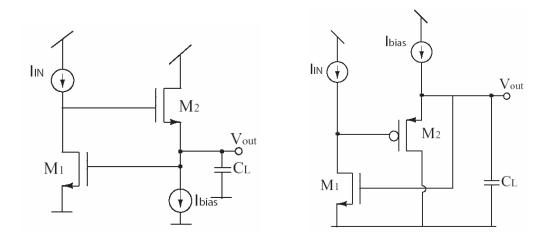

# **5.2.** Level Shifting

The other factor that limits the reduction in power supply is the term that arises due to the feedback in the whole amplifier. The dominant term in 3.5d is the gate to source voltage of  $M_1$  and  $M_2$ . By introducing a level shifting circuit, we can enable a reduction in the power supply requirement. Simple level shifting circuits can be realized using single transistors biased in the common source configuration as shown in Fig. 5.2.

Fig. 5.2 OTA modified with level shifter for low voltage operation

The introduction of the level shifter removes the necessity for the output node and the gates of  $M_1$  and  $M_2$  to be at the same level. The input voltages are transferred to the differential pair by the source follower transistors. By choosing appropriate bias current  $I_{b2}$  and sizing the source follower transistors  $M_i$  and  $M_{ii}$ ,  $M_{bias1}$  can be kept in saturation, and  $M_1$ ,  $M_2$  can be operated either in the subthreshold or in the strong inversion regime. The power supply requirement in that path is now given by (5.3).

$$V_{dd} - V_{SS} = V_{DSAT7} + V_{DSATN} - V_{GSi} + V_{SG1} + V_{OD1} + V_{DSATMbias1}$$

(5.3)

By introducing a common source configuration transistor to provide the level shifting, we do not introduce any additional gain in the process of level shifting; thus making the cascodes at the output necessary. We could introduce a gain in the level shifting process by using a transistor in the common source configuration to perform the level shifting process as shown in Fig. 4.3. The open loop gain of the amplifier can be increased by providing sufficient gain in the

common source stage, and the cascades at the output stage can be removed. This would also give the amplifiers a higher bandwidth.

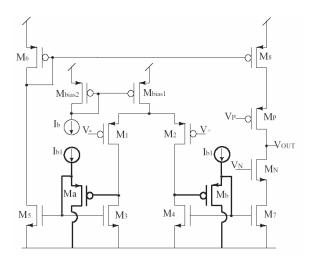

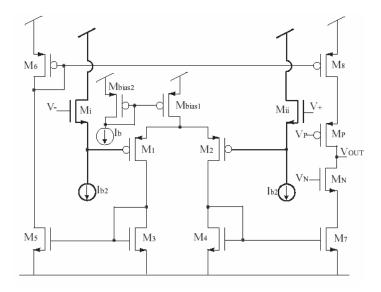

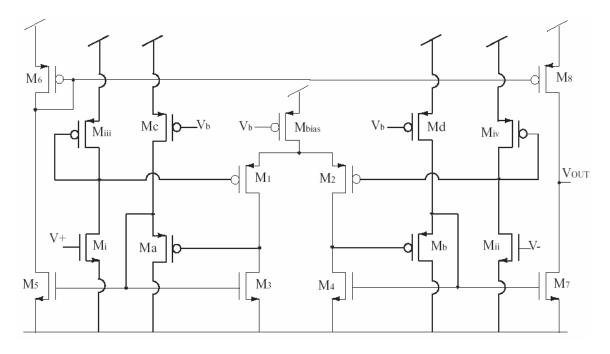

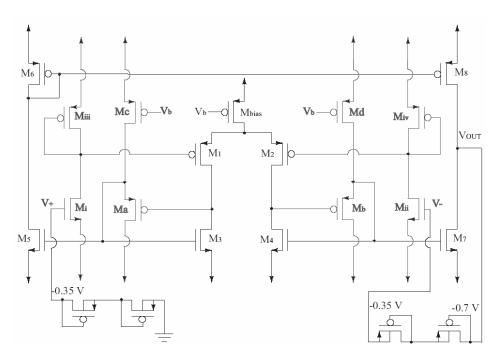

Fig. 5.3 OTA modified with voltage follower, and gain in the level shifter for low voltage operation

Transistors  $M_a$  and  $M_b$  act as the voltage follower,  $M_c$  and  $M_d$  are the biasing current sources for  $M_a$  and  $M_b$ . Transistors  $M_i$  and  $M_{ii}$  act as the level shifter transistors and are biased in the common source mode to provide additional gain.  $M_{iii}$  and  $M_{iv}$  are diode connected loads for  $M_i$  and  $M_{ii}$ . The design has also been realized with a NMOS differential pair.

## 5.3. Design Considerations

While designing the circuits, the aspect ratios of the transistors and the bias currents must be chosen in order to keep all the transistors saturated. In implementing the voltage follower configuration, we note that the drain to source voltage of the transistor  $M_3$  is provided by the difference in the gate source

voltages of  $M_3$  and the source gate voltage of  $M_a$ . Hence, to keep  $M_3$  saturated, we reduce the source gate voltage of  $M_a$  by choosing a large W/L and a small current through it. The current cannot be made very small as that will degrade the voltage following capability of the transistors  $M_a$  and  $M_b$ .

The gate to source voltages of  $M_1$  and  $M_2$  and the saturation voltage of the bias transistor  $M_{bias}$  is provided by the gate to source voltages of  $M_{iii}$  and  $M_{iv}$ . Hence we choose small aspect ratios for them, and a sufficiently high bias current. Choosing a high bias current also increases the gain of the common source stages, but at the cost of increased power.

The modified OTA structure has three inherent poles given by

$$g_{m-iii}/C_{gs1}$$

,  $g_{m-6}/(C_{gs6}+C_{gs8}+C_{ds8}(1+A_8))$ , and  $f_{gsa-35}/(r_{01} \| r_{03})$  where  $g_{m-n}$  is

the transconductance of transistor n,  $C_{gsn}$  is the gate to source capacitance of transistor n,  $A_8$  is the gain at the output stage taken in order to account for the Miller effect,  $r_{0n}$  represents the output resistance of transistor n in the small signal approximation.  $C_{gsa-35}$  is the effective capacitance of  $C_{gsa}$  in series with  $C_{gs3}$  and  $C_{gs5}$ , given by (5.4).

$$C_{gsa-35} = \frac{C_{gsa}(C_{gs3} + C_{gs5})}{C_{gsa} + C_{gs3} + C_{gs5}}$$

(5.4)

By reducing the lengths of  $M_a$  and  $M_b$ ,  $C_{gsa}$  is reduced and  $g_m$  is increased which enhances its voltage following capability. Minimum lengths were chosen for  $M_a$  and  $M_b$ . The value of the load capacitance should be chosen depending on

the required bandwidth, and should also ensure a safe phase margin. Higher open loop gains may be achieved by adding output cascodes to the circuit in Fig. 5.3, at the cost of reduced output swing. The sizes of all the transistors in the circuits are summarized in table 5.1. We also fabricated an amplifier with the level shifter being realized using a source follower transistor, and the gain being boosted with cascodes at the output. The sizes of the transistors in the circuit are summarized in table 5.1(c).

| Transistor                                       | Width  | Length |

|--------------------------------------------------|--------|--------|

| $M_1, M_2$                                       | 35μm   | 1.75µm |

| M <sub>3</sub> , M <sub>4</sub> , M <sub>5</sub> | 3.5µm  | 3.5µm  |

| $M_6$                                            | 10.5μm | 3.5µm  |

| $M_7$                                            | 7μm    | 3.5µm  |

| $M_8$                                            | 21μm   | 3.5µm  |

| Mi, M <sub>ii</sub>                              | 17.5μm | 1.75µm |

| Miii, M <sub>iv</sub>                            | 3.5µm  | 7μm    |

| M <sub>a</sub> , M <sub>b</sub>                  | 35μm   | 0.7μm  |

| $M_c, M_d$                                       | 1.75µm | 7μm    |

| Transistor                                       | Width  | Length |  |

|--------------------------------------------------|--------|--------|--|

| M <sub>1</sub> , M <sub>2</sub>                  | 21μm   | 1.75µm |  |

| M <sub>3</sub> , M <sub>4</sub> , M <sub>5</sub> | 3.5µm  | 3.5µm  |  |

| $M_6$                                            | 10.5μm | 3.5µm  |  |

| $M_7$                                            | 3.5µm  | 3.5µm  |  |

| $M_8$                                            | 10.5μm | 3.5µm  |  |