#### ABSTRACT

Title of dissertation: ENHANCING PRODUCTIVITY AND

PERFORMANCE PORTABILITY OF

GENERAL-PURPOSE

PARALLEL PROGRAMMING

Alexandros Tzannes,

Doctor of Philosophy, 2012

Dissertation directed by: Professor Rajeev Barua &

Professor Uzi Vishkin

Department of Computer Science

This work focuses on compiler and run-time techniques for improving the productivity and the performance portability of general-purpose parallel programming. More specifically, we focus on shared-memory task-parallel languages, where the programmer explicitly exposes parallelism in the form of short tasks that may outnumber the cores by orders of magnitude. The compiler, the run-time, and the platform (henceforth the system) are responsible for harnessing this unpredictable amount of parallelism, which can vary from none to excessive, towards efficient execution. The challenge arises from the aspiration to support fine-grained irregular computations and nested parallelism. This work is even more ambitious by also aspiring to lay the foundations to efficiently support *declarative code*, where the programmer exposes all available parallelism, using high-level language constructs such as parallel loops, reducers or futures. The appeal of declarative code is twofold for general-purpose programming: it is often easier for the programmer who does not have to worry about the granularity of the exposed parallelism, and it achieves better performance portability by avoiding overfitting to a small range of platforms and inputs for which the programmer is coarsening. Furthermore, PRAM algorithms, an important class

of parallel algorithms, naturally lend themselves to declarative programming, so supporting it is a necessary condition for capitalizing on the wealth of the PRAM theory. Unfortunately, declarative codes often expose such an overwhelming number of fine-grained tasks that existing systems fail to deliver performance.

Our contributions can be partitioned into three components. First, we tackle the issue of **coarsening**, which declarative code leaves to the system. We identify two goals of coarsening and advocate tackling them separately, using static compiler transformations for one and dynamic run-time approaches for the other. Additionally, we present evidence that the current practice of burdening the programmer with coarsening either leads to codes with poor performance-portability, or to a significantly increased programming effort. This is a "show-stopper" for general-purpose programming. To compare the performance portability among approaches, we define an experimental framework and two metrics, and we demonstrate that our approaches are preferable. We close the chapter on coarsening by presenting compiler transformations that automatically coarsen some types of very fine-grained codes.

Second, we propose Lazy Scheduling, an innovative run-time scheduling technique that infers the platform load at run-time, using information already maintained. Based on the inferred load, Lazy Scheduling adapts the amount of available parallelism it exposes for parallel execution and, thus, saves parallelism overheads that existing approaches pay. We implement Lazy Scheduling and present experimental results on four different platforms. The results show that Lazy Scheduling is vastly superior for declarative codes and competitive, if not better, for coarsened codes. Moreover, Lazy Scheduling is also superior in terms of performance-portability, supporting our thesis that it is possible to achieve reasonable efficiency and performance portability with declarative codes.

Finally, we also implement Lazy Scheduling on XMT, an experimental manycore platform developed at the University of Maryland, which was designed to support codes derived from PRAM algorithms. On XMT, we manage to harness the existing hardware support for scheduling flat parallelism to compose it with Lazy Scheduling, which supports nested parallelism. In the resulting hybrid scheduler, the hardware and software work in synergy to overcome each other's weaknesses. We show the performance composability of the hardware and software schedulers, both in an abstract cost model and experimentally, as the hybrid always performs better than the software scheduler alone. Furthermore, the cost model is validated by using it to predict if it is preferable to execute a code sequentially, with outer parallelism, or with nested parallelism, depending on the input, the available hardware parallelism and the calling context of the parallel code.

# Enhancing Productivity and Performance Portability of General-Purpose Parallel Programming.

by

# Alexandros Tzannes

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2012

Advisory Committee:

Professor Rajeev Barua, Chair/Advisor

Professor Uzi Vishkin, Co-Advisor

Professor Jeff Foster

Professor Alan Sussman

Professor William Dorland

© Copyright by Alexandros Tzannes 2012

#### Preface

I started my PhD in the fall of 2004. I had come to the University of Maryland at College Park to do theory, and my main interest was structural complexity. I also had an affinity to programming languages and compilers as an undergrad, and I especially enjoyed the equivalence of different automata to formal languages. In my first semester, I took approximation algorithms and randomized algorithms. Randomized algorithms, it turns out, were not my thing. I really liked approximation algorithms, but as I looked closer to the research being done in the field, I was turned off by the need to motivate theoretical research as being immediately applicable in order to apply for funding. I felt this requirement clouded the purity of theory and drove researchers away from fundamental questions which, if answered, would not necessarily provide useful fruits immediately. So, I had to reconsider what I wanted to do for my PhD.

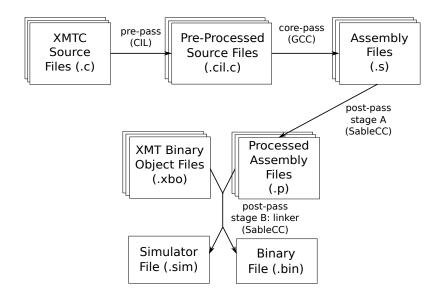

In my second semester, I took Parallel Algorithms with Prof. Uzi Vishkin. He taught PRAM algorithms in the classroom, and we had to implement some parallel algorithms in XMTC, a small extension of C, and run the assignments on a simulator of the XMT on-chip parallel platform. In my last year of undergrad, I had taken a course on high-performance computing where we had to write code in MPI and OpenMP for a relatively simple 3D stencil computation. That was not fun. On the contrary, programming XMT was straightforward, intuitive, and fun. But the XMTC compiler was a disaster: the compiler was almost as likely to produce buggy binaries as for a programmer to write buggy code. During that time, the influential popular article by Herb Sutter [80] "The free lunch is over: A Fundamental Turn Toward Concurrency in Software" was calling attention to the fact that clock speeds of processors had stopped getting faster and were unlikely to pick up again. Therefore, the main path for increasing performance of code from one hardware-generation to the next would presumably be through parallelism.

That was it! I was sold on the idea of working in a "hot" field, with the

XMT architecture which I thought (and still do) was unique and very promising, combining compilers and theory, with Prof. Vishkin who I admired from undergrad for his deterministic coin tossing [28]. At that time, I did not yet know exactly what I wanted to do research on, but I offered Prof. Vishkin to write a decent compiler for XMTC (I had written a compiler for a large subset of C almost from scratch as an undergrad and had enjoyed it a lot, so I thought I had what it took), and Prof. Vishkin accepted the challenge of giving such a demanding project to a first year PhD student (me). He also brought on board Prof. Rajeev Barua, a compiler expert, to help with my daunting task, a very wise move. So, by the end of my first year in grad school, I had not one but two advisors Rajeev Barua and Uzi Vishkin.

During my years as a PhD student, I witnessed some parallel platforms attract significant attention but quickly loose steam, such as the IBM Cell BE, others slowly moving from domain-specific towards general-purpose, such as GPUs, some encountering difficulties to launch such as the Intel Larrabee, and others, more domain specific, trying to find a niche, such as Tilera and the Intel Single Chip Cloud. Even the now ubiquitous multicores seem to be a transitional solution, while we figure out how to adapt the hardware-software stack for parallelism.

Since I started my PhD and to this day, everyone is talking about how hard it is to write correct and efficient parallel code and how important it is to come up with practical parallel programming models, something that is still an open question [79, 75]. But instead of starting with the programming model and the algorithmic thinking and then engineering the programming languages and the platforms around them, many researchers start with a commercial product (e.g., multicores, GPUs, Cell, etc), and try to invent easy and efficient programming models for them. Undoubtedly, if someone were to succeed, the impact would be great because the hardware would already exist and the solution would be less disruptive. This approach, however, precludes quick feedback from programming models research into the development cycle of the platforms for effective codesigning the software-

hardware stack. For that reason, interest quickly migrates from one trend to the next, generating many publications but with unclear long-term contributions. For example, in the first few years of my PhD, IBM's Cell became very popular, but it has now lost most of its steam. It got replaced by the CUDA GPUs, which have had a good run, possibly because they keep evolving towards more programmable and more general-purpose parallelism. Recently, a new buzz word, *cloud computing*, is attracting a lot of interest. And the cycle starts again.

I consider myself lucky to have had advisors who stayed out of such passing fashions. It allowed me to stay focused on the bigger question of how to enable efficient and performance portable general-purpose programming. Certainly, this dissertation does not give a definitive answer to that question, but I believe it offers several steps towards that direction, including a run-time scheduler, some static compiler transformations, and a methodology for preserving performance portability of code while tuning the amount of parallelism to optimize performance. I had a great time doing research at Maryland, and I am very thankful to have the amazing opportunity to continue research in this exciting field of parallel computing at the University of Illinois at Urbana Champaign.

As a stylistic note, although dissertations are presented as the work of a single author, I am using the first-person plural as an acknowledgement of the priceless help of my advisors, research collaborators, committee members, and friends with whom I discussed my research all these years.

# To my grandmother $I\omega.$

There's nothing I can write that can begin to express my gratitude and love.

"May you always do for others and let others do for you."

"May your heart always be joyful, and may your song always be sung.

May you stay forever young."

Bob Dylan

## Acknowledgments

I would like to extend my gratitude to all the people who made this thesis possible and due to whom my graduate experience has been one that I will cherish forever.

First and foremost, I would like to thank my advisor, Professor Rajeev Barua, who showed me his trust and patience and taught me how to do high quality research and the importance of presenting my work in a way that is accessible to a large audience. I have always had a hard time explaining my ideas, especially soon after their inception, when they are still fuzzy and not fully formed. Rajeev was always patient and helped me both with crystallizing the ideas and with presenting them in a comprehensible way.

Equally, I would like to extend my appreciation to Uzi Vishkin, my co-advisor, who taught me to wander off the beaten path and away from hypes, while staying relevant and with significant impact.

I also want to thank my dissertation committee, Prof. Jeff Foster, Prof. Alan Sussman, and Prof. William Dorland, for their time, effort, and comments, which improved this dissertation. I especially want to thank Jeff and Alan for our discussions, both on academic and other issues.

This work would have not been possible without the other members of the XMT research group who helped maintain all the software and hardware infrastructure needed for my experiments. In particular, I want to thank my close friends George C. Caragea and Fuat Keceli for sharing in the good and bad moments, as well as for their advice, support, help, and good spirits! Also the rest of the XMT team during my studies here: Xinghzhi Wen, Aydin Balkan, Beliz Saybasili, James Edwards, Darya Fillipova, Nghi Nguen Ba, Mike Detwiler, Yoni Ashar, Michael Horak, Mary Kiemb, and Tom Dubois.

I want to thank my wonderful family for their unquestioned faith in me, which was instrumental at times.

Special appreciation goes out to my close friend Manolis Georgakakis for our long discussions on all topics imaginable, for playing music together, for reluctantly sitting next to the "new guy" in high-school (that was me), and for being an inspiration.

Petros Tsamatropoulos, Nikos Prasianakis, and Dimitris Sklivagos have also blessed me with their friendship since high-school and significantly contributed to the person I am now.

I also want to thank my good friends in Maryland, Konstantinos Koutrolikos (θυρωρός), Kostas Spiliopoulos (πρόεδρος), Christos Papadopoulos (ψηλός), Nikos Frangiadakis (ntg), Konstantinos Bitsakos (kbits), Alex Enurah (Lex), Mike Hughes, Tiffany Dean, Vlassis Vassileiou, Thodoris Rekatsinas, Vassilis Zikas, Jimmy Hart, and Thanos Chryssis.

I am also deeply thankful to Michelle (Darth) Hugue for the privilege of having been her teaching assistant, and my professors from undergrad, Stathis Zachos and Nikos Papaspyrou, who inspired me to follow Computer Science.

I am truly indebted to Yolanda Mahnke for her support, patience, love, and understanding, especially during the months leading to the defense. I am looking forward to what comes next.

It is impossible to remember all, and I apologize to those I've inadvertently left out.

Finally, I would like to thank people who have inspired me through their timeless music, especially Ludwig Van Beethoven and Bob Dylan.

"You've been with the professors, and they've all liked your looks.

With great lawyers you have discussed lepers and crooks.

You've been through all of F. Scott Fitzgerald's books.

You're very well read, it's well known.

But something is happening here, and you don't know what it is...

do you, Mister Jones?"

Bob Dylan

# Contents

| Lis      | st of   | Tables 1           |                                                              | xii      |

|----------|---------|--------------------|--------------------------------------------------------------|----------|

| Lis      | st of l | Figures            |                                                              | xiii     |

| Lis      | st of A | Abbrevi            | iations                                                      | xvi      |

| 1        | Intro   | oduction<br>Contri | n<br>Butions                                                 | 1<br>. 5 |

| 2        | Roel    | kground            |                                                              | 9        |

| <i>_</i> | 2.1     | _                  | Background                                                   |          |

|          | 2.1     | 2.1.1              | Overview of the XMT Platform                                 |          |

|          |         | 2.1.1              | From C to XMTC: Simple Extensions                            |          |

|          |         | 2.1.2              | Performance Advantages of XMT                                |          |

|          |         | 2.1.4              | Ease of Programming and Teaching                             |          |

|          |         | 2.1.4 $2.1.5$      | My personal experience with the XMT Architecture             |          |

|          | 2.2     | _                  | Stealing Scheduling                                          |          |

|          | 2.2     | 2.2.1              | Motivation for Dynamic Scheduling                            |          |

|          |         | 2.2.2              | Work Stealing Background                                     |          |

|          |         |                    | 2.2.2.1 Serializing Work Stealing (SWS): Work-First          |          |

|          |         |                    | 2.2.2.2 Help-First Work Stealing                             |          |

|          |         |                    | 2.2.2.3 Eager Binary Splitting (SP & AP)                     |          |

|          |         | 2.2.3              | Theoretical Bounds                                           |          |

| 3        | Coar    | rsening            |                                                              | 31       |

| 0        | 3.1     |                    | cterizing Coarsening                                         |          |

|          | 3.2     |                    | of Parallelism                                               |          |

|          | 3.3     | _                  | ivity of Performance to Coarsening                           |          |

|          | 0.0     | 3.3.1              |                                                              |          |

|          |         | 0.0.               | 3.3.1.1 Benchmarks                                           |          |

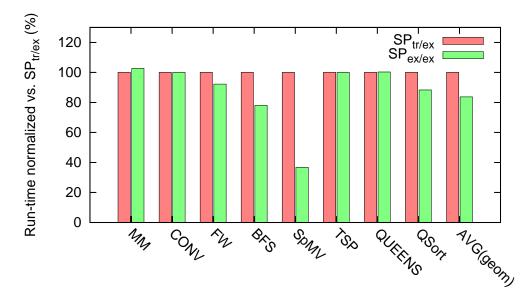

|          |         |                    | 3.3.1.2 Results                                              |          |

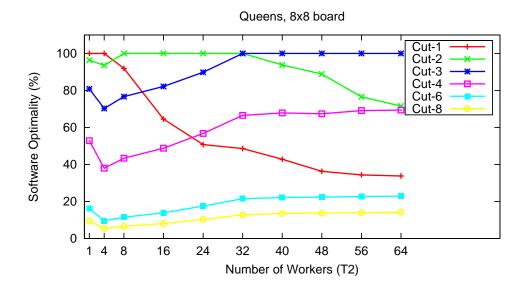

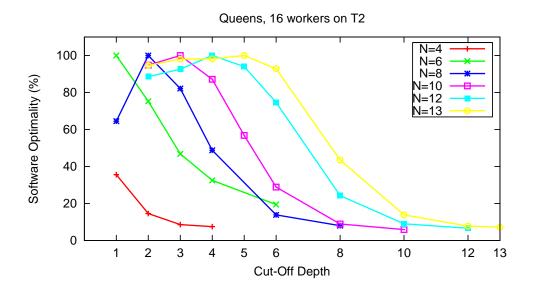

|          |         | 3.3.2              | Sensitivity to picking the right cut-off for QUEENS          |          |

|          | 3.4     |                    | ating the Quality of General Purpose Parallel Code: Proposed |          |

|          |         |                    | work                                                         | . 52     |

|          |         | 3.4.1              | Discussion                                                   |          |

|          |         | 3.4.2              | Using the Framework: An Example                              |          |

|          | 3.5     | Coarse             | ening in the XMTC Compiler                                   |          |

|          |         | 3.5.1              | Cost Estimation                                              |          |

|          |         | 3.5.2              | Picking a Grain-Size                                         |          |

|          |         | 3.5.3              | Serializing Spawn Statements (Parallel Loops)                |          |

|          | 3.6     | Concli             | usion and Future Directions                                  |          |

| 4 | Lazy | Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64   |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 4.1  | The two Insights of Lazy Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64   |

|   | 4.2  | Lazy Binary Splitting (Depth-First Lazy Work Stealing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66   |

|   | 4.3  | Analytical Comparison of Lazy Work Stealing with existing Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|   |      | Stealing schedulers: A First approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68   |

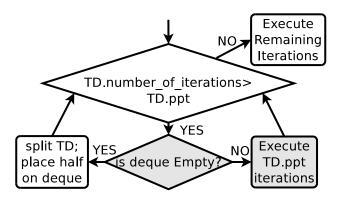

|   |      | 4.3.1 Deque Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73   |

|   |      | 4.3.2 Role of the Profitable Parallelism Threshold $(ppt)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

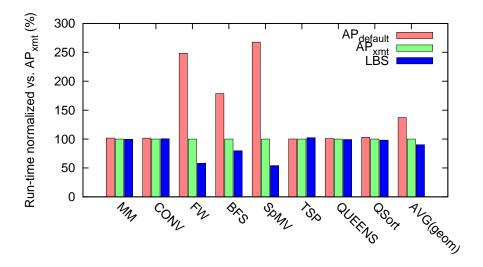

|   | 4.4  | Experimental Evaluation of Depth-First Lazy Work Stealing (LBS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   |      | on XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74   |

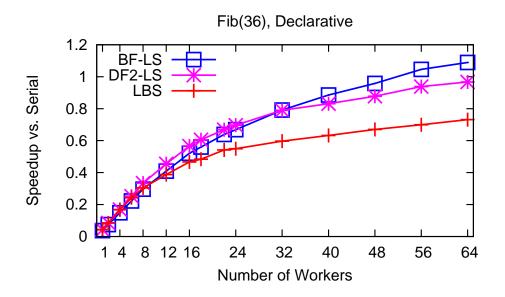

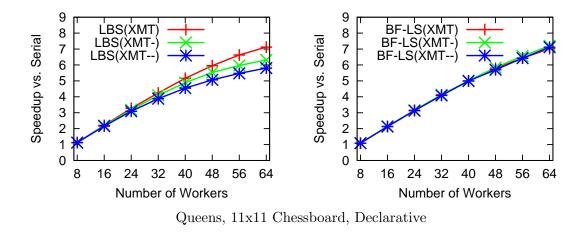

|   |      | 4.4.1 Scalability and Speedups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82   |

|   | 4.5  | Scalability Issues of Depth-First Lazy Work Stealing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|   | 4.6  | Lazy Scheduling for Declarative Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|   |      | 4.6.1 Breadth-First Lazy Scheduling (BF-LS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|   |      | 4.6.2 DF-LS with a threshold of 2 (DF2-LS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

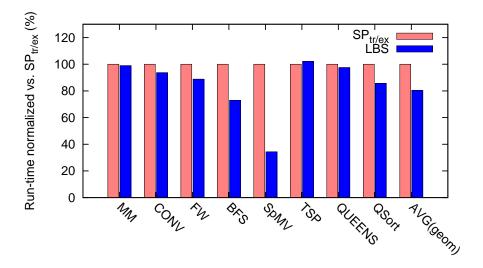

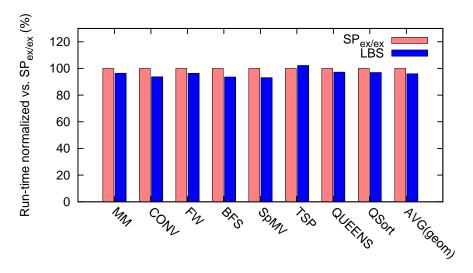

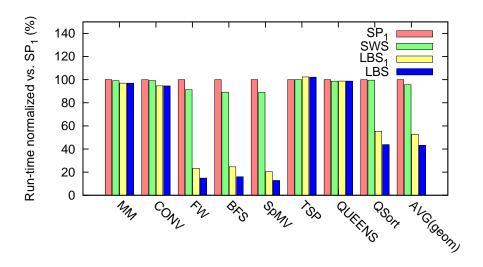

|   | 4.7  | Experimental Evaluation of Lazy Work Stealing on Multicores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

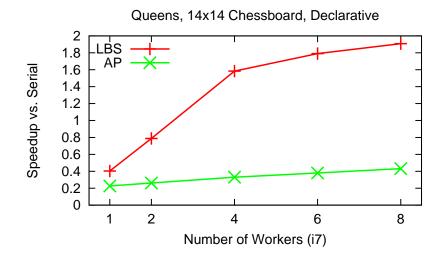

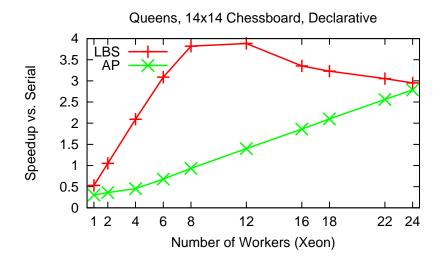

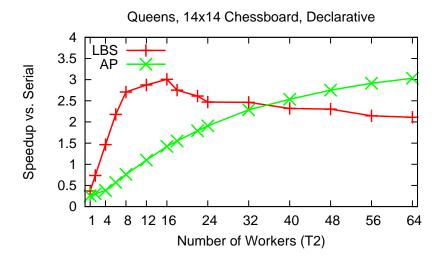

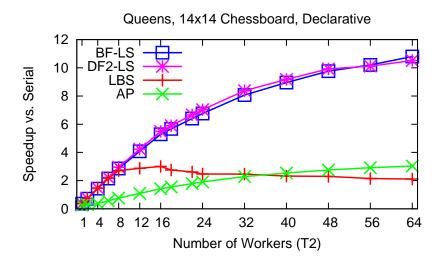

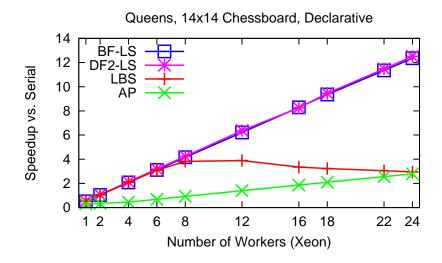

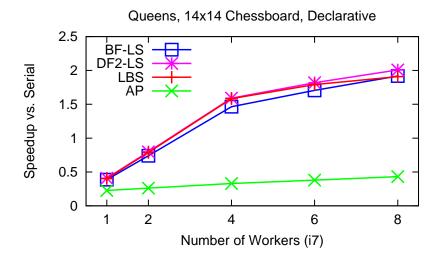

|   |      | 4.7.1 Scaling of Lazy Scheduling on Multicores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|   |      | 4.7.2 Counting Thefts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

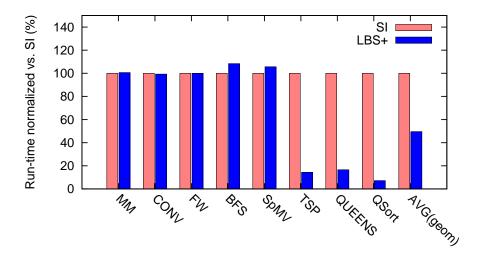

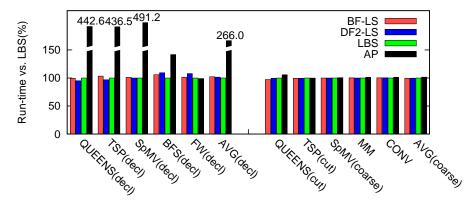

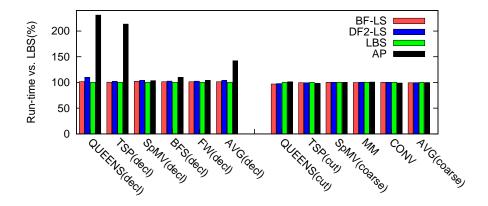

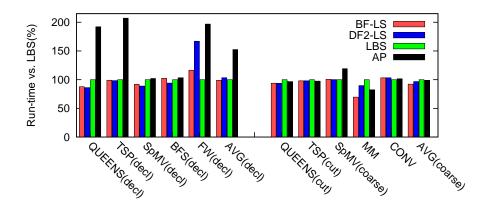

|   |      | 4.7.3 Evaluation on a set of benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|   |      | 4.7.4 Software Optimality of Declarative Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|   |      | 4.7.5 Software Optimality of Code with Amortizing Coarsening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|   |      | 4.7.6 Worst-Case Software Optimality of Lazy Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|   | 4.8  | Experimental Evaluation of Scalable Lazy Work Stealing on XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|   |      | 4.8.1 Scaling of Lazy Scheduling on XMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|   |      | 4.8.2 Counting Thefts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|   |      | 4.8.3 Evaluation on a set of Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|   | 4.9  | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|   |      | 4.9.1 Schedulers without Parallel Loop Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 118  |

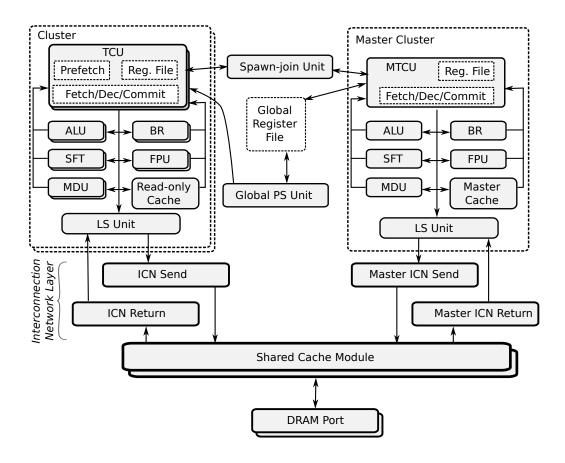

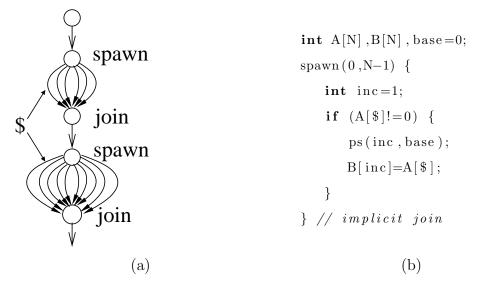

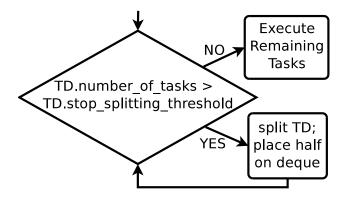

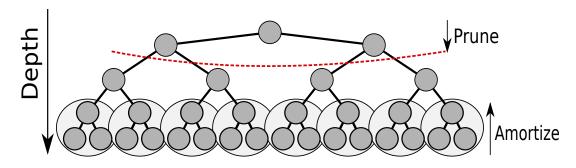

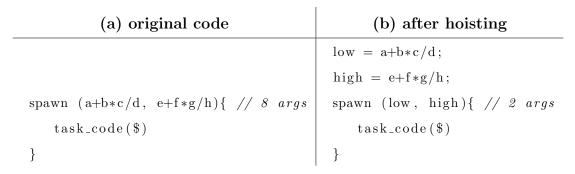

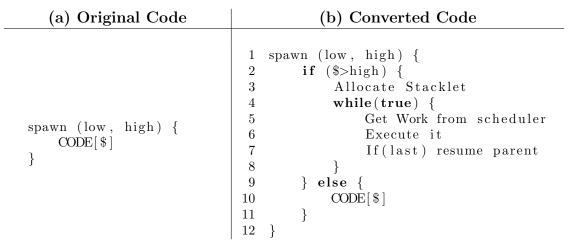

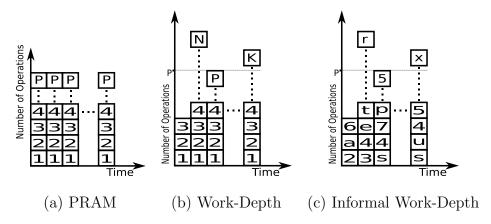

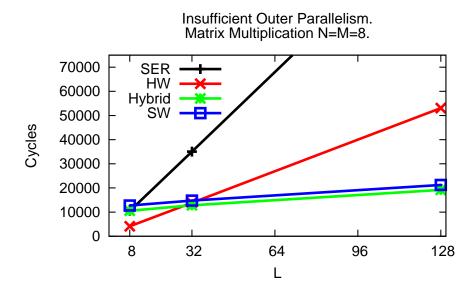

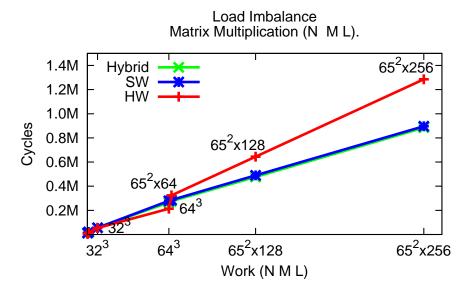

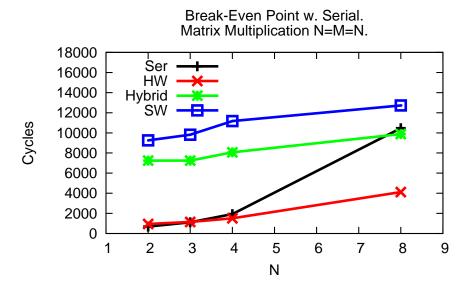

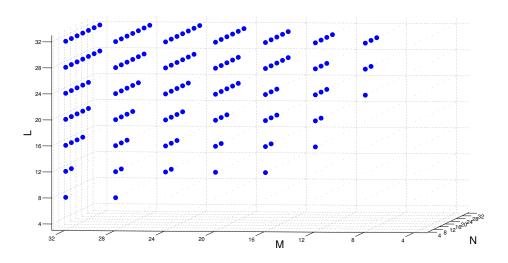

|   |      | 4.9.2 Schedulers with Parallel Loop Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |