**ABSTRACT**

Title of Thesis: MODELING AND SIMULATION OF A

SEMICONDUCTOR MANUFACTURING FAB FOR CYCLE TIME ANALYSIS

Aditya Shinde, Master of Science in Systems

Engineering, 2018

Thesis Directed By: Dr. Michael Fu,

Decision, Operations & Information

**Technologies**

Robert H. Smith School of Business

The goal of the thesis is to conduct a study of the effects of scheduling policies and machine failures on the manufacturing cycle time of the Integrated Circuit (IC) manufacturing process for two processor chips, namely Skylake and Kabylake, manufactured by Intel. The fab simulation model was developed as First in First Out (FIFO), Shortest Processing Time (SPT), Priority based (PB), and Failure FIFO (machine failures) model, and the average cycle times and queue waiting times under the four scheduling policy models were compared for both the Skylake and Kabylake wafers. The study revealed that scheduling policies SPT and PB increased the average cycle time for Skylake wafers while decreasing the average cycle time for the Kabylake wafers, when compared to the base FIFO model. Machine failures increased the average cycle time for both types of wafers.

# MODELING AND SIMULATION OF A SEMICONDUCTOR MANUFCATURING FAB FOR CYCLE TIME ANALYSIS

by

### Aditya Ramaji Shinde

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science

2018

Advisory Committee: Professor Michael Fu, Chair Professor Jeffrey W. Herrmann Professor Steve I. Marcus © Copyright by Aditya Ramaji Shinde 2018

### Preface

The goal of this thesis is to present a comprehensive study of the manufacturing processes involved in the fabrication of Integrated Chips (IC's). The motivation for this research stemmed from my passion in semiconductors and their wide applications in the electronic industry.

With the advent of technology and the need to maintain a strong competitive position in the market, semiconductor manufacturing companies employ various techniques to enhance systems in the manufacturing process while producing chips with better performance at similar or lower costs.

This extensive scope for improvement in various aspects of the IC manufacturing process, fueled my passion to pursue a master's thesis research in this industry. This thesis is a result of the best understanding of the IC fabrication process by the author.

## Dedication

I would like to dedicate this thesis to my beloved parents. I am deeply indebted to them for their continuous support and love through all my endeavors in life.

### Acknowledgements

I am using this opportunity to express my gratitude to everyone who supported me throughout the course of this thesis. I am thankful for their aspiring guidance, invaluably constructive criticism and friendly advice during the thesis work. I am sincerely grateful to them for sharing their truthful and illuminating views on a number of issues related to the thesis.

I express my warm thanks to my advisor and mentor, Dr. Michael Fu, for his continuous support and guidance throughout the course of this thesis.

I would also like to thank my thesis committee members, Dr. Herrmann and Dr. Marcus, and all the other people who provided me with the great feedback and their proactive contributions and involvement in each phase of my thesis.

I am also very grateful to Dr. John MacCarthy, the Director of the Systems

Engineering Program at The University of Maryland, who gifted me the opportunity

to pursue a master's degree at an esteemed University and for assisting me throughout

my journey as a master's student. I would also like to thank all the Professors in the

Systems Engineering program, for imparting rich knowledge. Lastly, I would like to

thank all my fellow graduate students for their moral and knowledge support.

Thank you,

Aditya Ramaji Shinde

## Table of Contents

| Preface                                                      | ii   |

|--------------------------------------------------------------|------|

| Dedication                                                   | iii  |

| Acknowledgements                                             | iv   |

| Table of Contents                                            | v    |

| List of Tables                                               | vii  |

| List of Figures                                              | viii |

| List of Abbreviations                                        | ix   |

| Chapter 1: Introduction                                      | 1    |

| General                                                      | 1    |

| Moore's Law                                                  | 2    |

| Chip Design and Architecture                                 | 3    |

| Thesis Organization                                          | 6    |

| Chapter 2: Semiconductor Manufacturing Process Challenges    | 9    |

| Semiconductor Manufacturing Process                          |      |

| Semiconductor Manufacturing Process Components               | 9    |

| Unit Manufacturing Processes                                 | 12   |

| Process Challenges                                           | 20   |

| Chapter 3: Literature Review and Approaches in the Past      | 22   |

| IC Manufacturing Modeling and Simulation                     |      |

| Cycle Time Analysis                                          | 26   |

| Production Sequencing                                        | 28   |

| Queueing Theory and Con-WIP                                  |      |

| Chapter 4: ARENA IC Fab Model                                |      |

| SysMl Architecture                                           | 33   |

| System Block Definition Diagram                              | 33   |

| System Activity Diagram                                      | 36   |

| Discrete-Event Simulation (DES)                              | 37   |

| DES Overview and Simulation Software                         | 37   |

| Arena Random Number Generator (RNG) and Statistical Analyzer | 38   |

| Statistical Analyzers                                        | 39   |

| Input Analyzer                                               | 39   |

| Output Analyzer                                              | 39   |

| Arrival Process Distribution                                 | 40   |

| Service Process Distribution                                 | 41   |

| Little's Law                                                 | 43   |

| Dispatching rules (FIFO, SPT, Priority Based)                | 43   |

| FIFO Model                                                   |      |

| SPT Model                                                    | 44   |

| Priority-Based Model                                         | 45   |

| Arena IC Fab Model                                           | 45   |

| Model Performance Measures                                   | 46   |

| Model Algorithm                                              | 46   |

| Batching                                                     |      |

| Entity Attribute                                             | 47   |

| Processing Station                         | . 47 |

|--------------------------------------------|------|

| Entity Type Decide Logic                   |      |

| Repeat Logic                               |      |

| Push System                                |      |

| Resource Levels and Allocation             |      |

| Resource Failures                          |      |

| Warm-up Period                             | . 51 |

| Chapter 5: Simulation Results and Analysis | . 53 |

| Purpose                                    | . 53 |

| Cycle Time Analysis                        |      |

| FIFO vs SPT                                | . 53 |

| FIFO vs PB                                 | . 54 |

| FIFO vs Failure FIFO                       | . 55 |

| Average Waiting Time Analysis              | . 56 |

| FIFO vs SPT                                | . 57 |

| FIFO vs PB                                 | . 58 |

| FIFO vs FIFO Failure                       | . 58 |

| Statistical Output Analysis                | . 59 |

| ANOVA Test                                 | . 60 |

| Skylake ANOVA Analysis                     | . 60 |

| Kabylake ANOVA Analysis                    | . 61 |

| Tukey Test                                 | . 62 |

| Skylake Tukey Test                         | . 63 |

| Kabylake Tukey Test                        | . 64 |

| Chapter 6: Conclusion and Future Scope     | . 66 |

| Future Research                            | . 68 |

| Constant WIP                               | . 68 |

| Profit/Cost Analysis                       | . 68 |

| Other Queueing Sequences                   | . 69 |

| Appendices                                 | . 70 |

| Appendix A: SIMAN Code for FIFO model      | . 70 |

| Bibliography                               | . 89 |

| References                                 | 89   |

## List of Tables

| Table 1.1 Intel Skylake(i7-7800X) Specifications             | 4  |

|--------------------------------------------------------------|----|

| Table 1.2 Intel Kabylake (i5-7400T) Specifications           | 5  |

| Table 4.1 Batching Stations and Number of Entities per Batch | 47 |

| Table 4.2 Resource Levels at Processing Stations             | 50 |

| Table 4.3 Resource Failures in terms of MTBF and MTTR        | 51 |

| Table 4.4 Warm-Up Period Simulation Result                   | 52 |

| Table 5.1 Skylake ANOVA Analysis                             | 61 |

| Table 5.2 Kabylake ANOVA Analysis                            | 62 |

| Table 5.3 Skylake Tukey Test                                 | 64 |

| Table 5.4 Kabylake Tukey Test                                |    |

# List of Figures

| Figure 1.1 Moore's Law Validity                                      | 3  |

|----------------------------------------------------------------------|----|

| Figure 1.2 Intel i7 Processor Die Shot                               | 4  |

| Figure 1.3 Intel i5 Processor Die Shot                               | 5  |

| Figure 2.1 IC Manufacturing Process                                  | 9  |

| Figure 2.2 Sand to Silicon Ingot                                     | 13 |

| Figure 2.3 Three stages of Photolithography                          | 15 |

| Figure 2.4 Ion Implantation Stages                                   | 16 |

| Figure 2.5 Stages in the Etching Process                             | 18 |

| Figure 2.6 Stages in the Gate Formation and Metal Deposition Process | 19 |

| Figure 4.1 IC Fab System Block Definition Diagram                    | 35 |

| Figure 4.2 IC Fab System High-Level Activity Diagram                 | 37 |

| Figure 4.3 Exponential Interarrival Times                            | 41 |

| Figure 4.4 Polymer Machine Service Time Distribution                 | 42 |

| Figure 5.1 FIFO vs SPT Average Cycle Time                            | 54 |

| Figure 5.2 FIFO vs PB Average Cycle Time                             | 55 |

| Figure 5.3 FIFO vs FIFO Failure Average Cycle Time                   | 56 |

| Figure 5.4 FIFO vs SPT Average Waiting Time                          | 57 |

| Figure 5.5 FIFO vs PB Average Waiting Time                           |    |

| Figure 5.6 FIFO vs FIFO Failure Average Waiting Time                 |    |

### List of Abbreviations

IC Integrated Circuit

FIFO First in First Out

SPT Shortest Processing Time

PB Priority Based

SysML Systems Modeling Language

FOUP Front Opening Unified Pod

WIP Work-in Process

MBSE Model Based System's Engineering

BDD Block Definition Diagram

DES Discrete Event Simulation

SIMAN Simulation Language

RNG Random Number Generator

MTBF Mean Time Between Failures

MTTR Mean Time to Repair

### Chapter 1: Introduction

#### General

An integrated circuit (IC) is a device made of interconnected electronic components that are imprinted onto a tiny slice of a semiconducting material, such as silicon or germanium. An integrated circuit is smaller than a fingernail and can hold millions of circuits that are capable of performing a wide range of computing operations at high speeds. Monocrystalline silicon was identified as the main-substrate that can be used to manufacture IC's. This material is abundantly available in nature and has very special properties making it extremely affordable and appealing. It acts as a semiconductor, wherein it conducts electricity under some conditions and alternatively acts as an insulator in others. These properties have enabled IC's to be extensively used in electronic devices like computers and mobile phones.

Semiconductor manufacturing takes place under constant change of manufacturing conditions. With the advent of process technology, the size of the area per function on the wafer has reduced to almost half. Also, many new chips with complex architectures are introduced, which need to be accommodated in the existing process technology. This calls for continuous process improvement in the semiconductor chip manufacturing process to cater to the fast-changing market demands.

IC's undergo manufacturing in production units called fabs. Big giants like Intel, Texas Instruments and Apple manufacture IC's in their own fabs, whereas other companies like Advanced Micro Devices and Qualcomm outsource the manufacturing process to other global chip manufacturers around the world. Fabs require expensive devices to function, and estimates suggest the cost of establishing a new fab plant to values as high as \$3-\$4 billion. The central part of the fab, referred to as the clean room, houses the machines required for the manufacturing process. This room is designed as a dust-free environment, since even a small speck of dust can ruin the micro-circuit. The room also maintains a controlled temperature and humidity and is also damped against vibration.

#### Moore's Law

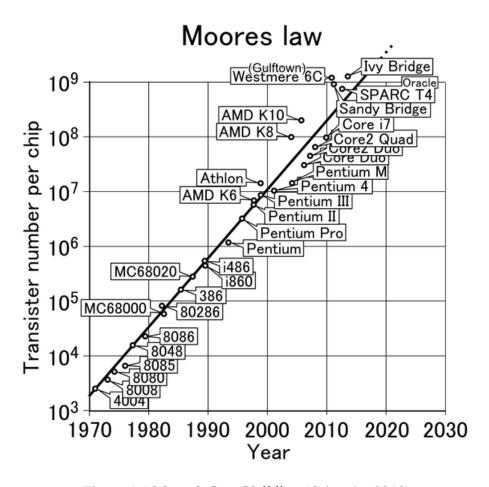

Moore's Law was an observation made by Gordon E. Moore, the co-founder of Intel. This law states that the number of transistors per area doubles approximately every two years (Moore, 1975). Because of the accuracy with which Moore's Law has predicted past growth in IC complexity, it is viewed as a reliable method of calculating future trends as well, setting the pace of innovation, and defining the rules and the very nature of competition. And since the semiconductor portion of electronic consumer products keeps growing by leaps and bounds, the Law has aroused in users and consumers an expectation of a continuous stream of faster, better, and cheaper high-technology products (Schaller, 1997). Further, the simple idea that transistor density is continually increasing means computing power goes up just as costs and energy consumption go down. As of today, the number of transistors on an integrated chip have substantially increased from a mere 10<sup>3</sup> in 1970 to 10<sup>9</sup> in 2017.

Figure 1.1 Moore's Law Validity (Cringely, 2013)

### Chip Design and Architecture

The scope of the study was confined to manufacturing two different types of processor chips manufactured by Intel, namely Skylake (i7-7800X) and Kabylake (i5-7400T).

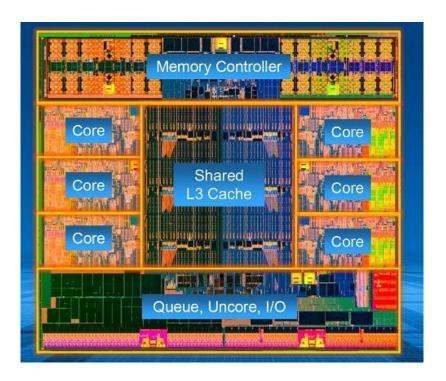

### Skylake Architecture

Skylake is a chip micro-architecture that was launched by Intel in August 2015 as a successor to Broadwell to overcome processing delays. Skylake was branded as the 6<sup>th</sup> generation of Intel's processors (Intel Developer Forum, 2015). The thesis deals

with the process analysis of the i7 family of the Skylake processor. This processor has a high-end performance and uses the 14 nanometer (14 nm) lithography process of semiconductor manufacturing.

The following table describes the specifications of a Skylake (i7-7800X) processor,

| Specification Type     | Specification Description |

|------------------------|---------------------------|

| Processor Name         | i7-7800X                  |

| Lithography Process    | 14nm                      |

| Average Customer Price | \$386                     |

| Number of Cores        | 6                         |

| Number of Thread       | 12                        |

| Memory Channels        | 4                         |

Table 1.1 Intel Skylake (i7-7800X) Specifications (Intel, 2016)

Figure 1.2 Intel i7 Processor Die Shot (Intel, 2017)

### Kabylake Architecture

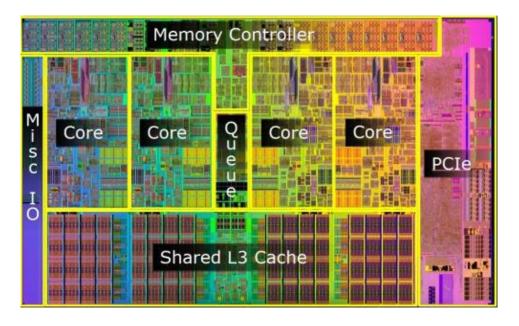

Kabylake is a chip micro-architecture that was launched by Intel in August 2016. Kabylake is branded as the 7<sup>th</sup> generation Intel processor (Intel Developer Forum, 2016). The thesis deals with the process analysis of the i5 family of the Kabylake processor. This processor has a mid-range performance and uses the 14 nanometer (14 nm) lithography process of semiconductor manufacturing.

The following table describes the specifications of a Kabylake (i5-7400T) processor,

| Specification Type     | Specification Description |

|------------------------|---------------------------|

| Processor Name         | i5-7400T                  |

| Lithography Process    | 14nm                      |

| Average Customer Price | \$185                     |

| Number of Cores        | 4                         |

| Number of Thread       | 4                         |

| Memory Channels        | 2                         |

Table 1.2 Intel Kabylake (i5-7400T) Specifications (Intel, 2016)

Figure 1.3 Intel i5 Processor Die Shot (Intel, 2017)

A semiconductor chip's core defines its performance. It comprises of a logical execution unit containing cache and functional units. More number of cores can be associated with higher performance.

A semiconductor chip's thread defines its ability to run multiple applications on a single core. It increases processor throughput, improving overall performance on threaded software. Higher number of threads can be associated with higher application loading capacity.

A semiconductor chip's memory channel is its memory bandwidth availability for the CPU. It facilitates the random-access memory (RAM) capability of a CPU. Higher the number of memory channels, better the memory bandwidth availability.

Skylake, as can be observed from the analysis, has higher values for the chip specifications compared to Kabylake. This suggests that Skylake is a much complex processor compared to Kabylake and hence requires advance processing at some stages of the IC manufacturing process.

### Thesis Organization

The goal of the thesis is to conduct a study on the different factors that affect the production cycle time of the IC manufacturing process. The research encompasses 2 major factors that have a significant effect on the cycle time, namely: production sequences (FIFO, SPT, and Priority Based) and machine failures (mean time between failure and mean time to repair).

The study is conducted on an ARENA simulated representative IC fab for two different processor chips manufactured by Intel. Skylake being an i7 processor is assumed to have a complex structure and hence requires more number of iterative processes and higher processing times at some processing stations.

The first part of the study involves developing a process architecture using SysML modeling language. These architectures were used to construct the FIFO base model on Arena. Further, queueing analysis and sensitivity study were performed to analyze the number of resources required at each processing station to attain maximum resource utilization for a stable system operation.

The second part of the study involves evaluating the performance of the fab for different queue sequences. The manufacturing process is first simulated as a first-in first-out (FIFO) queue model, and the average queue waiting times at each processing station are recorded. These processes are then subjected to SPT (Shortest Processing Time), priority-based queueing (higher priority for Kabylake over Skylake) and their effect on cycle times are observed.

The third part of the study involves incorporating machine failure in terms of mean time between failure (MTBF) and mean time to repair (MTTR) in the simulation model, to develop the FIFO failure model. This cycle time generated in this model is also compared to the base FIFO model.

The final part of the thesis presents a hypothesis study for statistical significance of the cycle time using the ANOVA test of the four simulation models developed. The individual cycle time differences of the models are compared using the post-hoc Tukey Test.

### Chapter 2: Semiconductor Manufacturing Process Challenges

### Semiconductor Manufacturing Process

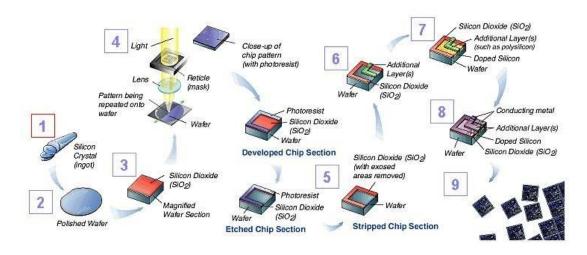

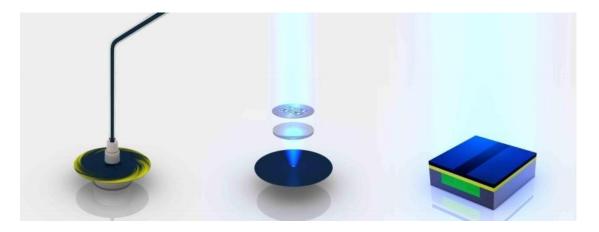

The technology behind engineering an IC goes far beyond the simple assembling of individual components. In fact, microscopic circuit patterns are built on multiple layers of various materials, and only after these steps have been repeated a few hundred times is the chip finally complete (Samsung, 2015). It involves multiple photolithographic and chemical processing steps during which the electronic circuit layers are gradually developed over the silicon wafer. The entire process from sand to packed silicon chips takes almost 3-4 weeks.

Figure 2.1 IC Manufacturing Process (Fishman, 2017)

### Semiconductor Manufacturing Process Components

Fab: Semiconductor fab is the facility that houses the IC fabrication process. The air inside a fab cleanroom is filtered and recirculated continuously, and employees wear special clothing such as dust-free gowns, caps, and masks to help keep the air particle-free.

Wafer: Wafers can be defined as a thin slice of silicon crystal that is used in the fabrication of semiconductor chips. Usually the wafer serves as a substrate for the microcircuit to be built in and on it. Wafers undergo processing at each stage of the semiconductor manufacturing process and are finally cut at the end of the fabrication. A single silicon wafer may consist of anywhere between 450-700 chips. Chips fabricated on the same wafer generally possess the same architecture.

Product: Fabricated chip/IC serves as the final product of a semiconductor manufacturing process. These undergo different levels and routes of processing at each stage of the manufacturing process based on their architecture.

FOUP: FOUP (Front Opening Unified Pods) acts a material handling system for transportation of wafers. It is specialized plastic enclosure designed to hold silicon wafers securely and safely in a controlled environment. Wafers are transported in batches of 25 around the fab facility.

Wafer Batch: A batch of wafers refers to a lot or collection of wafers. Generally, batches are formed, where more than one wafer can be processed at a time.

Route: Process route can be described as the path taken by the wafer inside the fab facility. The route for each wafer differs based on complexity and architecture.

Complex wafers experience reentrant flows through the same equipment/route

fabricate gradual layers. Alternatively, some lesser complex wafers skip some workstations and routes because of their simple architectures. All wafers start at the initial point and process through the route to reach the packaging station.

Process operation: A process operation is a step within the route of the where different equipment's work on the wafer to customize its architecture. Most of the processing operations are performed on a single wafer.

Machine: The tools that perform operations on these wafers are the fabricating machines. The machines performing similar operations are grouped at product workstations.

Recipe: Each wafer undergoes specific process steps at workstations referred to as the recipe for the chip. The recipe for the chip is determined by the architecture that needs to be fabricated.

Scheduling Rule: A scheduling rule dictates which job among those waiting for service is to be scheduled in preference to others. Scheduling a job means scheduling the next operation of the job.

Work-In Process: Work in process can be defined as those entities that are being either just fabricated or waiting in a queue or buffer to be processed. Production

management's aim to minimize and control the work in process in order to manage capacity and reduce slack in the production system (LeanKit, 2018).

Cycle Time: Manufacturing cycle time refers to the time required or spent to convert raw materials into finished goods. Technically, it is the length of time from the start of production to the delivery of the final products. It comprises of process time, move time, inspection time, and queue time (Accounting Verse, 2017).

### **Unit Manufacturing Processes**

The following section briefly describes the high-level unit manufacturing stages in manufacturing integrated circuits.

#### Silicon Wafer Fabrication

Before a semiconductor can be built, sand needs to be converted to silicon. Sand, especially Quartz, has high percentages of Silicon in the form of Silicon dioxide (SiO<sub>2</sub>), and is the base ingredient for semiconductor manufacturing (Intel, 2011). Sand is first melted to a temperature of 1420°C, above the melting point of silicon. Dopants from the Group III and Group IV elements (Boron, Phosphorous, Arsenic, etc.) of the periodic table are added to give desired electrical properties to the melted silicon.

Figure 2.2 Sand to Silicon Ingot (Intel, 2011)

The molten silicon is then purified in multiple steps until the manufacturing quality of Electronic Grade Silicon is reached. The molten silicon is then molded into large cylindrical ingot rods that weigh around 100 kg and have a silicon purity of 99.9% (Intel, 2011). The ingot growth process begins from a single purified silicon seed that grows the crystal in opposite direction to mold the melt. The initial growth is rapid and decreases subsequently to allow the diameter of the ingot to increase to the required dimension, generally 300mm. The ingot growth process can take anywhere from 1 week to 2 weeks. Once pure silicon ingots are formed, they are sliced into very thin wafers which have a thickness of 1mm (Silicon Valley Micro-electronics, 2015).

#### Thermal Oxidation

Semiconductor manufacturing companies like Intel and Global Foundries receive sliced wafers on which they fabricate the processing circuits. Thermal oxidation is the process of exposing silicon wafers to a temperature of 800-1200°C to grow a layer of

silicon-dioxide. A single furnace accepts many wafers at the same time in a specially designed quartz rack (Appels et al. (1970)). These quartz racks can enter the furnace vertically or horizontally, depending upon the uniformity, thickness and time constraints of the oxide-layer deposition.

Oxidation can be of two types, depending on the quality and the thickness of the oxide layer desired. There is a trade-off in using wet and dry oxidation for thermal oxidation of silicon wafer, as wet oxidation has higher growth rate compared to dry oxidation, while on the other hand, the higher oxidation date of wet oxidation leaves behind dangling bonds at the oxide surface which leads to leakages in the current flow inside chips

Hence, depending on the quality and thickness of the oxide layer required, the time for oxidation is decided. The time for oxidation is hence governed by the Deal-Grove model which gives the relation between the oxidation time ( $\tau$ ) and oxide-layer thickness ( $X_0$ ).

$$\tau = \frac{X_0^2}{B} + \frac{X_0}{\frac{B}{A}}$$

where A and B are process-related constants (Liua, et al., 2016).

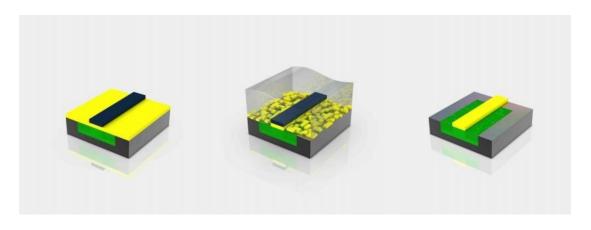

#### Photolithography

This process involves the use of light-induced polymerization to transform liquid resin into a solid polymer in the lithographic illuminated areas. The photopolymers

are then exposed to real-time infrared spectroscopy using UV light or laser to cure the solid polymer (Decker, 2002).

A photo-resist material is applied which changes its characteristics upon exposure to light, i.e. either softening or hardening depending on the type of photoresist.

Chromium masks are generally used for photolithography. Depending on the circuit architecture and the areas to be illuminated, positive or negative photoresist material is used. Although positive photoresist materials require a higher exposure time and are more expensive than the negative photoresists, they are more widely used than the later because of their higher step coverage (Printed Circuit Imaging, 2014).

The high-level processes modelled under Photolithography as a part of the thesis are follows:

- Applying Photo-resist Material

- Stepper Exposure

- Photoresist Development

Figure 2.3 Three Stages of Photolithography (Intel, 2011)

### Ion Implantation

Ion Implantation is the process of transferring ions from one element into a solid target by fast accelerations at a low temperature. This leads to changes in the physical, chemical and electrical properties of the solid target. Ion ranges are between 10 nanometers and 1 micrometer. Ion implantation is highly effective at the surface of the solid target. The concentration and energy of these ions gradually decreases as they travel through the solid, due to collisions with the atoms of the solid target and drag from the electron orbitals (Hamm, Robert, & Marianne, 2012).

Doping is a common technique used in ion implantation to introduce dopant impurities into the crystalline silicon. Dopants, when injected into the semiconductor act as charge carriers and depending upon the dopant element used, a hole is formed for the p-type dopant and an electron for the n-type dopant (Philip Laube, 2010).

Figure 2.4 Ion Implantation Stages (Intel, 2011)

Hence, the energy of the ions, the ion species, ion dosage and the target scanning areas greatly affect the time required for the implantation process. The ion dosage time varies amongst processor chips, depending on the ion dosage and level of complexity of the chip (Cheung, 2010).

The following equation is used by chemical engineers at semiconductor manufacturing industries to calculate the implant time and dosage required for a processor chip (Cheung, 2010):

$$Dose = \frac{(Ion \, Beam \, Current) * (Implant \, Time)}{Ion \, Beam \, Scanning \, Area}$$

### Etching

Etching is process that is used either to remove material from the surface of the wafer or to create a pattern on it. Etching in semiconductor manufacturing can be of two type, Dry etching and Wet Etching. Dry or plasma etching used for circuit-defining steps, while Wet etching is used mainly to clean wafers. Although both methods are used extensively, dry etching is more frequently used over wet etching. Etching removes material away from the patterns developed in the photolithography step. The sequence of patterning and etching is repeated multiple times during the chip-making process (Applied Materials, 2017).

Figure 2.5 Stages in the Etching Process (Intel, 2011)

Etchants crystalline and remove material from the surface of the wafer depending upon several factors like:

- Wafer side facing the etchant

- Required etch uniformity

- Etch agent

- Etch agent type

Taking these factors into consideration, semiconductor manufacturers deduce the time to etch wafers to avoid over-etching or under-etching of the wafers (National Taipei University of Technology, 2006).

### Gate Formation and Metal Deposition

Gate Formation and metal deposition is the process of fabricating high-k dielectric gates and metal layers onto the wafer. Gate formation starts with developing a temporary gate electrode and dielectric, which is then etched away. This is followed by adding molecular layers of high-k dielectric to the wafer surface, which is again etched at areas where it is undesired. The combination of this and the high-k material

gives the transistor much better performance and reduced leakage than would be possible with a traditional silicon dioxide gate (Intel, 2012).

Metal deposition is the process of making connections to link circuits together.

Conductive pathways are formed on the surface of the wafer by metal deposition.

Materials like copper, aluminum, nickel and other alloys are used to form connections. A single layer recipe is fabricated during one visit of the wafer at the processing station. It is followed by polishing the polished layer. Layers of deposited metal are fabricated for a single wafer based on its defined circuit architecture (Intel, 2012).

Figure 2.6 Stages in the Gate Formation and Metal Deposition Process (Intel, 2011)

### Board Assembly and Packaging

This is the last step in the semiconductor manufacturing process. Once the wafer visits all the stations in its predefined routes, it is cut into individual chips. This is followed by assembling cut chips on a printed circuit board (PCB and making the

necessary connections. The assembled PCB's are then packed and shipped to the customer.

### **Process Challenges**

- IC Manufacturing is known for its multiple or large number of process steps.

Even with the most modern technology, a wafer visits on an average 25 processing stations during fabrication.

- The fabrication process is complex, with most of the tools being single wafer

processing tools to fabricate wafers with varying architectures. Also, the recipe

for each wafer varies; hence different routes and reentrant flows to the same

workstation are common.

- There is an intermixture of batches/lots of wafers containing different recipes,

hence assigning priority to lots in order to meet schedule constraints and reduce

manufacturing cycle time poses a big challenge. This might also lead to long

queues at some stations.

- At some stations wafers having the same recipe, which can be processed in lots,

are batched together. The challenge here is to calculate the optimum batch size at

each station for faster and quality processing.

- The biggest challenge in this industry is to identify the type and quantity of each wafer to be manufactured, as the optimum goal of any fab is to achieve shorter

cycle times, increase throughput and acquire more flexibility to products while maintaining the same production costs.

Some of the high-level advantages of short cycle times are (Stubbe, 2010):

- lean inventory

- faster time to market

- fast yield learning

- fast excursion finding

- less reliance on demand forecast

- flexibility in product output enabling fast reactions to customer demand.

### Chapter 3: Literature Review and Approaches in the Past

### IC Manufacturing Modeling and Simulation

Pillai, Bass, Dempsey, & Yellig (2004) developed and implemented a simulation model of Intel's 300-mm fab that uses 90-nm high volume manufacturing and 65-nm technology. Their objective of developing this simulation was to understand the key attributes associated with the simulators that were being utilized for capacity planning, automation systems designs and tactical manufacturing execution and decision support for continuous improvement. Their simulations presented a dynamic behavior of several production tools and engineering lots along with automated material handling system (AMHS) behavior in the production simulation. They identified 5 critical data elements in the model; automated input data integration (DI) system with the automatic model builder and simulation runs configurator; production equipment and work-in process (WIP) management rules simulator; intrabay AMHS simulator; data analysis systems for reviewing model outputs and model validation and calibration. They observed that when lots are prioritized, priority lots start to dominate equipment capacity, and regular production lots may be in danger of getting increasingly deprioritized, resulting in an inordinate increase in its cycle time. It was also observed that the cycle time (fab velocity) increases at lower priority lots with increasing number of higher priority lots.

Domaschke, Brown, Robinson, & Leibl (1998) developed a discrete-event simulation model to evaluate the production practices of a high-volume semiconductor back-end

operations of the Siemens fab. The goal of their simulation was to identify the potential areas for productivity improvement that would yield a 60% reduction in the manufacturing cycle time. The scope of the paper was confined to the analysis of the Assembly, Burn-In and the test operations in the fab. The higher work in process and cycle times problem faced by Siemens was related to an exceed in the original loading plan due to a high production demand. The software used for modelling and simulating the fab was Factory Explorer. The simulation model used MTBF and MTTR aspects to express and record the machine down times. Real-time observations and conversations with operators and engineers on the shop floor were made to collect valid input data for the simulation. In order to obtain the data from the same data warehouse, a team of IT and Computer Integrated Manufacturing engineers was formed to collect, organize and store shop floor data. For the purpose of model validation, historical records of factory cycle time, cycle time by tool group, equipment utilization, and average inventory were compared against model outputs and were found to be within 10% of the value range. The results of the simulation revealed that improvement in areas like cross-functional teams at the shop floor, using smaller transport lot sizes, lower variability in lots and operating non-constraint equipment have a great impact on the cycle time. Implementing these factors in the simulation model, the fab achieved a 41% reduction in average cycle time.

Arisha & Young (2004) discuss the importance of simulation in the semiconductor fab to meet the complexities of market and process steps. They identify the various phases a semiconductor fab production planner goes through: factory layout design,

factory construction, process selection and design, start-up and full production. They describe the qualities of a good simulation model as good correlation with the existing system performance, good integrity in the model and timeliness. They also present a comparative study between a complex and simple model and explain how a process modeler should confine model scope based on the current production bottleneck areas and the required level of detail. The paper discusses how additional experiment features like length of simulation run, warm-up period, number of replications and design of simulation experiments using DOE techniques, saves time, provides high quality outputs (avoid misinterpretation) and better statistical control. Lastly, the paper also provides a comparative analysis on the advantage and disadvantages of using modeling and simulation in semiconductor manufacturing.

Tullis, Mehrotra, & Zuanich (1990) developed a discrete-event simulation model of their R&D fabrication facility at Hewlett Packard using the ManSim software to analyze capacity limitations and capacity changes that impact the manufacturing cycle time. Since their model featured more than one type of product, the lot start rate and the maximum work-in process values were set for each product. They also modelled random delays for equipment breakdown and repair times, material transfer etc between some recipe steps. Equipment reliability parameters like MTBF and MTTR were specified for each piece of equipment and preventive maintenance schedules were generated for workstations. A time-consuming but educational data collection technique was adopted, by collecting fab related data from the shop floor technicians and supervisors through interviews and written requests. The analysis

was extended to observing the effects of operator skills (skilled vs non-skilled), staffing and shift schedules on cycle times. They also incorporated different queueing sequences like First-In-First-Out, Shortest-Processing-Time, and Least-Work-In-Next-Queue at bottleneck work-stations to observe their effects on cycle times. The results of the analysis identified the effects of adding staff or resources that had the greatest effects on cycle time. The results also provided a comparative cycle time study between base model and models developed through improved staffing, removal of unscheduled maintenance and the combination of both. The results were presented using Pareto charts and chicken charts (to display lot re-visits at stations).

Becker (2003) introduces the concept of using Petri nets in a semiconductor manufacturing model for the complete production process, to observe its effects on the total simulation time. The modelling is performed on a MASM Lab developed tool, PSim, which is based on combined queueing and Petri net formalism. They used a modular approach by first assigning the structure of a machine as a Petri net and then instantiating as many machines as needed. The process considered for the study involves a two-product system of making non-volatile chips, where the first product needs 210 production steps and the second product needs 245 production steps. Both the product routes need 28 different machines with 87 and 102 different configurations for product 1 and 2, respectively. The machines used in the Petri net model are also subjected to failure and maintenance. First the lots are tested by machines (based on complexity), to test whether the lots need to be reworked or need to be scrapped. This is followed by wafer level machine testing at certain stations,

which then assigns an input buffer token for wafers waiting for processing. Queueing logic was used wherever appropriate and features like queueing disciple and priority lots was tested on the model. The simulation was run for 50,000 hours on an 800 MHz Linux PC. The results observed as an outcome of the simulation was that the system took between 19-48 hours for processing and validating the model to reach the defined confidence intervals.

## Cycle Time Analysis

Chen (2013) presents a systematic procedure to plan and evaluate cycle time reduction actions by evaluating the factors that influence the job cycle time. Additionally, the relationship between the controllable factors and job cycle time are fitted with back propagation network. He identified the following reasons as pinnacle to shortening the cycle time; each job represents an opportunity cost for the factor, long cycle times lead to accumulation of WIP and the risk of wafer contamination in larger cycle times. He identified the factors associated with job cycle time as follows; utilizations of the bottleneck machines, queue length and product waiting time at a bottleneck machine, job type (size, priority and processing time) and the worker productivity. He used the method of stepwise backward elimination which involved the deletion of each factor variable, to optimize a fitness indicator (t-test). This method helped identify the factor variable that could improve fitness the most, and this process was repeated until no further improvement could be achieved. Further, a BPN (Back-propagation neural network) was established to fit the relationship between the controllable variables and the job cycle time. Based on the fitted BPN,

actions for controlling the factors that affect the cycle time were planned. He proposed an estimated 7% decrease in the cycle time using this approach.

Janakiram (1996) discusses the use of Theory of Constraints (TOC) and simulation to achieve fab cycle time reduction at Motorola's advanced custom technologies R&D Fab. The cross-functional team associated with this project was trained on the principle of theory of constraints to develop custom cycle time reports, device techniques to measure theoretical cycle time and use multiples of theoretical cycle times to make wafer fab comparisons. Benchmarking was performed within Motorola to determine how other labs and fabs were measuring their performance to study their cycle time reduction techniques and the use of cycle time as a fab metric. A five-step rule identifying the elements of TOC was used as follows:

- Identify the system's constraints

- Decide how to exploit the system's constraints

- Subordinate everything else to the above decision

- Elevate the system's constraints

- Test and reiterate

The process of using TOC and simulation resulted in identifying bottleneck stations, one of them being the inspection station where the lots were piling up. Critical analysis revealed that these problems were caused due to inadequate sampling plans and previous processes having lesser load.

Stubbe (2010) discuss how a Next Generation Production System (NGPS) concept can address the cycle time needs. The high-level elements of the NGPS were identified as small lot manufacturing, transition to mini-batch and single wafer processing, changes in cluster tool design, and rapid, high volume material handling systems. Her model incorporates reentrancy in flow lines where the same workstation is visited several times during at different steps. Also, since there are more than one products being modeled, the recipe for each product varies, which is an important feature in her model. She also introduces the aspect of x-factor, which is the ratio of actual cycle time to raw process time. The purpose of using the x-factor is associated with performance comparison of routes of different lengths and fabs having different routes or technologies. For performing the simulation experiments, she used Factory Explorer 2.8 along with MS Excel as output interface. The analysis involved replacing large batch tools with mini-batch or single wafer tools at some stations. The original fab consisted of 15% batch tools. All batch tools were replaced with single wafer tools to achieve a cycle time reduction benefit of 40%. Batches comprised of four classes, namely original batch, mixed-product batch, mini-batch, hybrid batch and single wafer tool batch. Comparative analysis revealed that single wafer tools had the greatest reductions in the cycle time.

## **Production Sequencing**

Silva et al. (2012) study the effects of production sequencing rules in the performance of Job Shop and Flow Shop manufacturing environments. The rules they considered

for their study were SIPT (Shortest Imminent Processing Time), EDD (Earliest Due Date), DLS (Dynamic Least Slack), LWQ (Least Work in next Queue), FIFO (First In First Out), LIFO (Last In Last Out), CR (Critical Ratio) and LS (Least Slack). They modeled 8 machines and 10 different products using ARENA software, accounting for randomness in product arrival and service times. Excel was used to evaluate the effect of the work in process in relation to the total tardiness and the total number of tardy orders. The simulation was run for 20 replications and 1000 minutes each for a 95% confidence for each run. The results for the Job Shop environment suggested that the best performance was presented by the EDD and LIFO sequencing rules. On the Flow Shop environment, the results suggested that the SIPT and the CR rules demonstrated the best performance. Further, since their prominent metric of interest was number of tardy orders, they concluded that LIFO and SIPT had the best overall performance for Job Shop and Flow Shop, respectively.

Wein (1998) analyzed the impact of scheduling on the performance measure, mean throughput time, on a lot of wafers. He developed a representative but fictitious model of fab that was developed using the SIMAN simulation language. For the purpose of the analysis, four types of input mechanisms were evaluated, namely, Poisson, deterministic, closed loop and workload regulating (releases a lot of wafers into the system whenever the total amount of remaining work in the system for any bottleneck station falls below a prescribed level). Certain sequencing rules were developed by identifying the stations that are heavily utilized and using a Brownian

network model to approximate a multiclass queueing network. Simulation results suggested that scheduling had a great impact (35-45 percent reduction in average total queueing time) on the fab performance. In particular workload regulating, closed loop and deterministic inputs had better performance over Poisson inputs as it substantially reduced the mean and variability of throughput times. Further, queueing analysis also suggested that reducing variability at the input also enhanced the performance of the fab.

## Queueing Theory and Con-WIP

Shanthikumar, Ding, & Zhang (2007) survey the applications of queueing theory in semiconductor manufacturing systems (SMS). The paper discusses methods to reduce cycle time using queueing theory in addition to simulation. They begin with analyzing the queueing models (M/M/1 and M/G/1) that are formed at the single machine stations. Further they study how these models closely represent the actual queue behavior though being oversimplified assumptions. The next study is performed on the multimachine stations using a G/G/m system where they analyze the effects on queue waiting times due to higher variances in the interarrival or service times. Further, they analyze the methods to obtain numerical solutions to complex multi-server systems that experience machine breakdowns and other interruptions that occur within the facility. The numerical solutions calculate how a smart scheduler will try to push out maintenances when the WIP level is high and resume them after the system load becomes relatively low. They discuss the queueing network models developed by Jackson as a dynamic job shop Poisson external arrival process, exponentially distributed processing times, and Markovian job transfers

between tools. Further, since this model does not instantiate the realistic complications of a manufacturing system, they propose 3 important approaches namely: Decomposition approach, Fluid Networks and Diffusion Approximation.

Their analysis concludes that the accuracy of classical queueing models is less satisfactory than that of simulation, partly because the complex operational behaviors of semiconductor fabs cannot be represented by one single model.

Pierreval et al. (2013) address the application of ConWIP (constant work-in process) in semiconductor manufacturing fabs to reduce work-in process and maintain good customer satisfaction. They discuss rules that are based on thresholds, which are known to influence system performance, and hence propose a model that sets these cards in the best way and avoids changing the number of cards too often. These cards control the manufacturing process by authorizing production only after receiving an order, called the pull mechanism. Hence, optimization involves determining, for each stage of the manufacturing process, the best number of cards so as to reduce the longterm production costs, while taking into account the cost caused by backward demands, WIP and inventory. They perform the simulation optimization on an ARENA simulation model using OPTQUEST. An upstream module was used to track demands entering the manufacturing process and accordingly reducing the changes in the number of cards. Additionally, order arrival trends were observed and were compared to a fixed number of demand arrivals. Hence, if an increase in demand was detected, then authorization to adaptation module was given to add an extra card; else, a new card was not added. Their experiments concluded with proving that

decreasing the frequency of the number of card changes in the ConWIP system greatly affects the system performance and that this decrease can be achieved by using an adaptation module to detect trends and control the card generation.

# Chapter 4: ARENA IC Fab Model

## SysMl Architecture

The first step in developing a process/system model involves defining a baseline architecture. Systems Engineers use an approach referred to as Model Based Systems Engineering (MBSE) to develop system and process flow architectures to support system requirements traceability, design, analysis and verification and validation. This thesis uses the MBSE approach to identify the high-level system elements and process sequences to support system design and analysis of the IC Fab model and simulation.

MBSE is implemented on architecture modeling languages like Systems Modeling Language (SysML) and Unified Modeling Language (UML). This thesis uses SysML to capture the IC Fabs architecture by developing SysML structure and behavior diagrams. The MBSE architecture also helps convey the scope of the model to the stakeholders. For the purpose of this thesis, the scope of the wafer fabrication process is confined to the stage where the sliced and polished wafers reach the Intel Fab to the stage where the chips are tested and are ready for packaging.

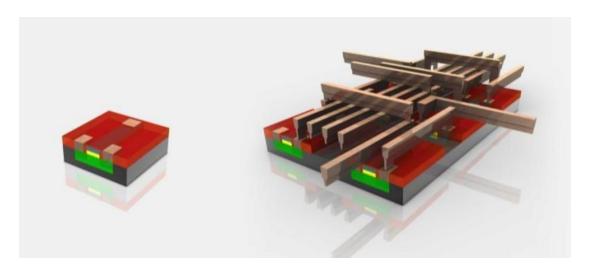

## System Block Definition Diagram

A block definition diagram (BDD) is used to display various kinds of system model elements and relationships between those elements to express information about the systems structure (Delligatti, 2013). The IC Fab BDD model decomposes the system

architecture into the system of interest (SOI) domain, the system users and the SOI environment. The primary users of the IC Fab system are identified as the Fab owner and the maintainer, who interact with the system to trigger the IC fabrication processes. The IC Fab system domain is comprised of the IC Fab processing subelements. The sub-elements are modeled based on their functionality and resource groups. The wafers to be processed and the FOUP's used to transport the wafers around the Fab constitute the system environment, as they are external systems that interact with the SOI.

Figure 4.1 IC Fab System Block Definition Diagram

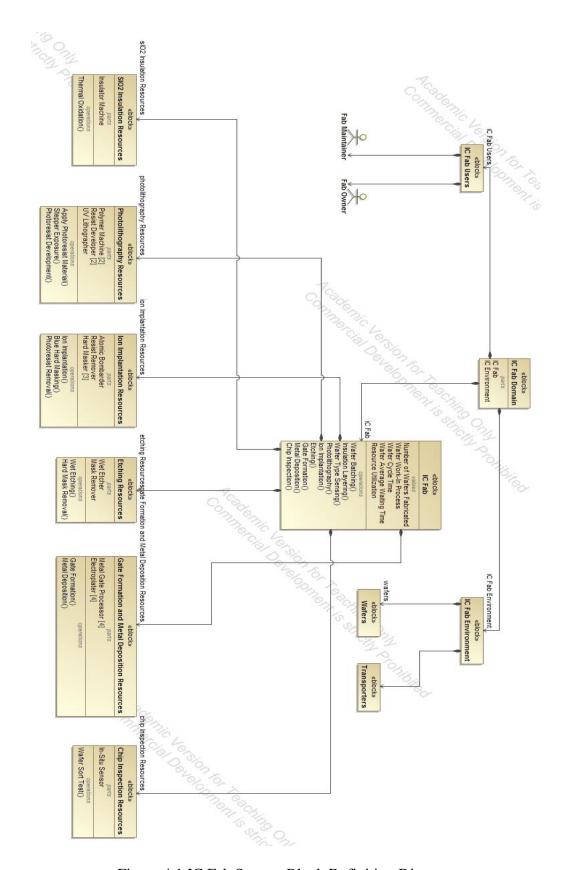

# System Activity Diagram

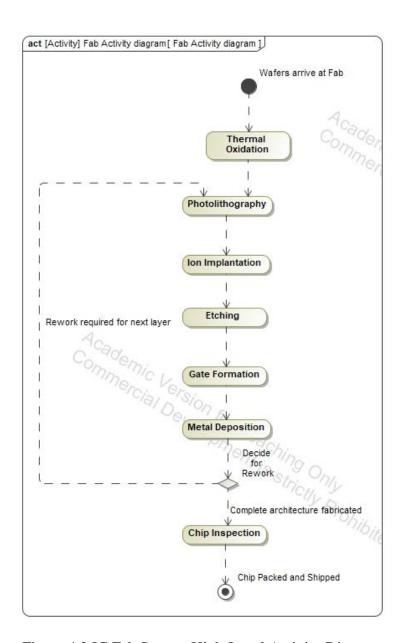

An activity diagram is a kind of behavior diagram that provides a dynamic view of the system that expresses sequences of behaviors and event occurrences over time (Delligatti, 2013). The IC Fab activity diagram models a set of sequential actions that occur during the IC fabrication process. The Fab activity diagram comprises of swim lanes that organizes the model based on the high-level processes that are performed during the fabrication process. The model illustrates how the flow of activities occurs between different stations and what actions trigger this flow. Further, decision gates were used at different stages of the model to depict the wafer flow in different directions of the model based on some defined condition. This architecture was essentially useful to identify, design and analyze process routes and condition-based decisions to be taken at each and very processing stage of the IC Fab model.

Figure 4.2 IC Fab System High-Level Activity Diagram

# Discrete-Event Simulation (DES)

## DES Overview and Simulation Software

Discrete-event simulation (DES) models the operation of a system as a discrete sequence of events in time. Each event occurs at a particular instant in time and marks

a change of state in the system (Robinson, 2004). Both the nature of the state change and the time at which the change occurs mandate precise description.

Arena is a discrete-event simulator that makes modeling easy and also provides flexibility at the lowest level simulation modules using the SIMAN simulation language. These functionalities and ease of use makes Arena the primary simulation tool used of this study, with MATLAB and Excel being used as secondary tools for specific computations and data analysis.

Arena Random Number Generator (RNG) and Statistical Analyzer

One of the important aspects to be considered while developing simulation models is the randomness in the input to ensure that the model is a representation of reality and can be subject to several uncertain events. Hence, it is important as a simulator to have the knowledge of the probability distributions from which the observations would be generated, and the random number generator (RNG) used to calculate the values of each of the observation.

The old version of Arena used an Linear Congruential Generator (LCG) with  $m = 2^{31} - 1$ ,  $a = 7^5$  and c = 0; the cycle length of it being 2.1 billion, whereas the updated versions of Arena (14 and newer) use a new RNG, which uses the same ideas as LCG, but involve two separate component generators that are later combined, and the recursion to get to the next value looks back beyond just the single preceding value.

Arena new RNG (Kelton, Sadowski, & Swets, 2010):

The two separate recursions

$$A_n = (1403580A_{n-2} - 810728A_{n-3}) \mod 4294967087$$

$$B_n = (527612B_{n-1} - 1370589B_{n-3}) \mod 4294944443$$

The program then combines these two values at the nth step

$$Z_n = (A_n - B_n) \mod 4294967087$$

• Finally, the RNG delivers the nth random number:

$$U_n = \frac{Z_n}{4294967088}$$

, for  $Z_n > 0$

Statistical Analyzers

Input Analyzer

The Input Analyzer is a standard tool built-in Arena that is designed to fit distributions to the observed data, provide estimates of their parameters, and measure how they fir the data. The thesis uses the Arena Input Analyzer to decide the best theoretical probability distributions to be used to generate sample data based on mathematical formulation.

Output Analyzer

The Output Analyzer is a separate application that is a part of Arena that is used to analyze the results obtained from the Arena simulation. The thesis uses this

application to plot curves, compare means and calculate the confidence intervals for the data.

#### Arrival Process Distribution

Arrival process for a system characterizes the input sources to the simulation model.

Arrival process for the fab system was calculated based on the approximate data values obtained from online research followed by identifying the best theoretical distribution to represent the arrival process.

The parameter for the exponential distribution is the mean( $\beta$ ) and the probability density function is calculated as (Kelton, Sadowski, & Swets, 2010):

$$f(x) = \begin{cases} \frac{1}{\beta} e^{-\frac{x}{\beta}} & for \ x > 0 \\ 0 & otherwise \end{cases}$$

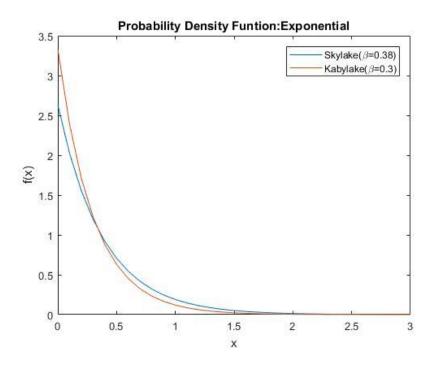

Arrival process for the fab is characterized by two important elements, namely the interarrival times and the arrival process probability distribution. The exponential distribution was selected to generate data observations for the entity arrival process and hence drive the simulation. Exponential distribution was selected, because it being a continuous theoretical distribution, models time between independent events or the interarrival times for machine part arrivals in manufacturing systems (Kelton, Sadowski, & Swets, 2010). The mean time between arrivals for the Skylake wafer is approximated to 0.38 hours and Kabylake wafer to 0.3 hours based on the data obtained (Lapedus, 2017).

Figure 4.3 Exponential Interarrival Times

# Service Process Distribution

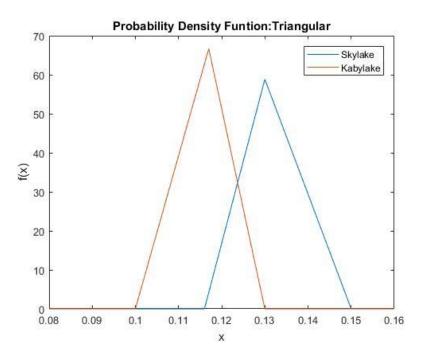

Service process for a system characterizes the entity processing time distribution at each station. The service process at a processing station is featured by the number of servers and the service time characteristic or the probability distribution. The service process distribution was generated by obtaining data from various online sources and was fitted into a triangular distribution using the data obtained from sources referred in Chapter 2.

The parameters for the triangular distribution are the minimum (a), mode(m), and the maximum (b). The probability density function is calculated as follows (Kelton, Sadowski, & Swets, 2010):

$$f(x) = \begin{cases} \frac{2(x-a)}{(m-a)(b-a)} & for \ a \le x \le m \\ \frac{2(b-x)}{(b-m)(b-a)} & for \ m \le x \le b \\ 0 & otherwise \end{cases}$$

Most of the service processing distributions in the fab model were generated using a triangular distribution because the data sets obtained were in the form of minimum, maximum and the most likely or modal values. Further, it has the advantage of allowing a non-symmetric distribution of values around the most likely, which is commonly encountered in real manufacturing processes. On the other hand, it is also a bounded distribution, and hence erroneous machine activities, outside the minimum and maximum values, which are very rare in semiconductor manufacturing fabs, are not encountered in the model.

Figure 4.4 Polymer Machine Service Time Distribution

Little's Law

Little's law is an important concept in queueing theory for its simplicity and generality. Little's law states that, under steady state conditions, the average number of items in a queueing system equals the average rate at which items arrive multiplied by the average time an item spends in the system (Little & Graves, 2008). It is mathematically expressed as

$$L = \lambda * W$$

where,

L =average number of items in the queueing system,

W = average waiting time in the system for an item,

$\lambda$  =average number of items arriving per unit time

This law relates to the fundamental quantities in manufacturing process. The Work-In Process (WIP) in a stable system can be expressed as a product of throughput (T) multiplied by the average cycle time (CT). This relation is used to study the effects of varying WIP's (pull system) at different simulation times on the measured cycle times.

$$WIP = T * CT$$

Dispatching rules (FIFO, SPT, Priority Based)

In production systems, the key task of implementing Lean Principles lies in understanding how parts flow between each workstation and what dispatching rule decides which part to be processed first. This helps production planners determine

which parts flow easily, which parts need direction and which sections need the highest level of control. The thesis models the fab manufacturing process using 3 different dispatching rules namely: First In First Out (FIFO), Shortest Processing Times (SPT) and Priority Based (PB).

#### FIFO Model

The first-in first-out (FIFO)queue dispatching rule is the most basic dispatching rule where entities are processed on a first-come first-served orderly basis. The goal of FIFO is to prevent earlier orders from being delayed in favor of newer orders, which would result in an increased lead time and delay. The base model of the thesis uses FIFO dispatching rule at the various processing stations. Since there are two different entities (Skylake and Kabylake) being fabricated in the fab, and the same machines processing them, the first one to arrive at a processing station gets served first followed by the next in queue, when the first one exits the processing workstation.

#### SPT Model

The shortest processing time dispatching rule processes the entities in the order of increasing processing times. The dispatching rule uses the algorithm of identifying the shortest assigned processing time among the two entities being fabricated and places the entity with the shortest assigned processing time to the start of the queue at a particular instance in the simulation time. The major goal of applying SPT to a fabrication model is to minimize the average cycle time.

## Priority-Based Model

The priority-based dispatching rule processes entities in the order of the predefined priority for an entity. The model has two different entities (Skylake and Kabylake wafers) being fabricated at the same time; hence, several factors go into deciding which product to prioritize over the other. The dispatching rule uses the algorithm of assign a numerical priority value to each part waiting in the queue of a machine group and to select for processing next, the one with the minimum or maximum value of the priority index. Priority-based dispatching rule being a heuristic algorithm has an aim to achieve an acceptable solution but not the accurate solution.

To assign the higher priority amongst the two wafers, the method weighting was used. In this procedure, weights are assigned on a scale of 1-10 for chip production factors, namely; chip revenue, chip rework, chip processing time, wafer production waste generated, customer popularity and defects. Based on the weights assigned to these wafers, the total weighted score is calculated. The scoring analysis reveals that Kabylake has higher priority over Skylake. (Appendix B, Page 88)

# Arena IC Fab Model

The purpose of this section is to walk the reader through the procedure used for developing the 4 models that were used for analyzing the performance of the IC Fab.

The FIFO model forms the basic model, upon which the SPT, Priority Based and Failure FIFO models are developed.

#### Model Performance Measures

The performance of a model depends upon the performance measures or the model measures of effectiveness. The two-important metrics that were measured as a part of the thesis were the cycle time and the average waiting time. These metrics were evaluated over the 4 IC Fab models that were developed using Arena. The four factor models whose impacts on the two-metric's studied are:

- a. Base Model (FIFO)

- b. SPT Model

- c. PB Model (Priority Based)

- d. Failure FIFO (Machine Failures in FIFO)

# Model Algorithm

The following sections discuss the components and characteristics of the model.

# Batching

The entities are carried around in the fab using FOUPS in batches. Batching of entities was done for the stations where the processing takes place in batches and not on individual wafers. The entities keep arriving at the FOUP batching station until the batch size is reached, after which they proceed as a batch to the processing stations. The stations where the entities were batched for processing are shown in the table below:

| <b>Processing Station</b> | Number of Entities/Batch |

|---------------------------|--------------------------|

| Insulator Machine         | 25                       |

| Atomic Bombarder          | 5                        |

| Wet Etcher                | 25                       |

| In-Situ Sensor            | 5                        |

Table 4.1 Batching Stations and Number of Entities per Batch

A separate batch of predefined batch size is formed differently for both the Skylake wafer and the Kabylake wafer. Arena provides two types of batching options, namely the temporary batch and the permanent batch. The thesis uses the temporary type batching, because the IC fabrication process is a combination of batching and single wafer processing stations and hence involves batching and separating entities depending upon the processing strategy at each station.

#### **Entity Attribute**

This thesis models the fabrication process of two entities, namely the Skylake wafer and the Kabylake wafer. The chip design and architecture, as discussed in Chapter 1, are clear indications of the fact that both the entities have different processing times at each workstation, which is defined by their level of complexity and architecture. Hence, processing times are generated from a triangular distribution and assigned for each of the entities before entering a workstation.

# **Processing Station**

A processing station is the workstation where the entities are worked upon for an assigned period of time. The processing stations first seize the singular entity or batch

to be processed and delays the simulation clock for the time assigned previously using the triangular distribution. Once the simulation clock advances to the allocated value, the entity is released from the resource, so that other entities can seize it. Each of the processing work-stations are characterized by a set of resources to process entities, and the number of resources is anywhere between 1-4 resources per workstation.

#### Entity Type Decide Logic

The entities that exit the processing station enter a decide module. The decide module is an abstraction of the sensors that are used by the fab to bifurcate the entity type before it enters the next processing station. The decide module is programmed to allocate routes to the individual entities to the next processing station.

## Repeat Logic

The repeat logic is modeled at the end of the gate formation and metal deposition processing module. The purpose of the repeat logic is to count the number of passes and automatically route the entities to the inspection station or back to the photolithography station and through all the stations following it. As discussed in Chapter 2, several layers are built over one another, and one layer is fabricated per cycle. Due to the complexity and extensive functionality of the Skylake wafer, the repeat logic is programmed to route Skylake wafer entities thrice through the stations starting from photolithography. On the other hand, the Kabylake wafer entities are

sent back only twice through these stations. Once the entities complete their required level of fabrication, a decide module routes them to the inspection station.

# Push System

The modeling approach considered is of a push system, wherein the work-in process at the shop floor is not controlled. The reason behind modeling the fab as a push system was to avoid excessive back locks on orders that wait to start processing. A pull system can also be used to model the fab but requires advance production techniques knowledge and hence is beyond the scope of this study.

## Resource Levels and Allocation

Resource levels at each station through the fabrication process have a major impact on the fab performance measures. Developing the basic FIFO model involved making decisions of the required level of resources at each station to attain maximum utilization and minimal waiting of entities for processing. Once the required number of resources were assigned to each station, a resource allocation rule was developed. The random (equiprobable) resource allocation rule was selected, so that entities select available resources randomly. The resource levels at each station are described in the following table:

| Workstation       | Number of Machines |

|-------------------|--------------------|

| Insulator Machine | 1                  |

| Polymer Machine   | 2                  |

| UV Lithographer   | 1                  |

| Resist Developer  | 2                  |

| Atomic Bombarder  | 1                  |

| Resist Remover    | 1                  |

| Hard Masker          | 3 |

|----------------------|---|

| Wet Etcher           | 1 |

| Mask Remover         | 1 |

| Metal Gate Processor | 4 |

| Electroplater        | 4 |

| InSitu Sensor        | 1 |

Table 4.2 Resource Levels at Processing Stations

It can be observed from the resource allocation table that some of the workstations have more than one resource. This is because these are single wafer workstations, which are preceded by batch workstations, where wafer processing is done in batches. Hence, a load of 5 to 25 wafers arrives at these workstations, which requires more than one resource for processing to avoid excessive work-in process and back locks.

# Resource Failures

Failures are primarily intended to model events that cause the resource to become unavailable for a period of time. Every manufacturing facility experiences machine failures, either scheduled or unscheduled. Typically, when a machine failure occurs, the machine is down/non-operational, followed by the machine undergoing repair before becoming operational again. Failures in Arena can be modeled as either count based, or time based. The model uses the time-based algorithm, as data was obtained in the form of mean time between failures (MTBF) and mean time to repair (MTTR), which were modeled as exponential distributions. The machine MTBF and MTTR data is provided in the table below:

| Resource                 | MTBF (days) | MTTR(hours) |

|--------------------------|-------------|-------------|

| Mask Remover Failure     | EXPO (70)   | EXPO (3.5)  |

| Bombarder Failure        | EXPO (47)   | EXPO (5)    |

| Hard Masker Failure      | EXPO (150)  | EXPO (8)    |

| Resist Developer Failure | EXPO (120)  | EXPO (7)    |

| UV Lithographer Failure  | EXPO (73)   | EXPO (3)    |

Table 4.3 Resource Failures in terms of MTBF and MTTR

Further, Arena provides three rules to model failures, namely, Ignore, Wait and Preempt. The thesis uses the preempt rule wherein the resource stops the processing of the entities and resumes operation after the down time duration. The ongoing processes for the station are interrupted immediately when the simulation clock enters the failure mode and resume when the resource becomes available and the clock exits the failure.

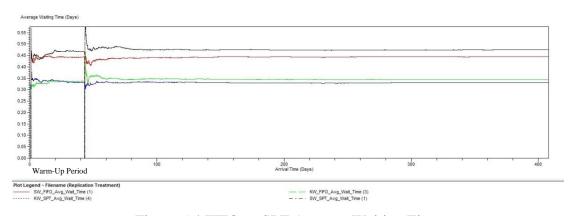

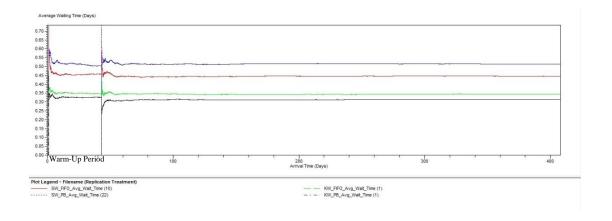

# Warm-up Period

The IC Fab model starts out empty of entities and all resources are idle. So, if a model starts empty and idle, where entities eventually become congested, the output data for some period of time after initialization understates eventual congestion (Kelton, Sadowski, & Swets, 2010). In other words, the queues at resources get congested eventually, and hence the results might experience a low bias. To avoid this initialization bias, and to make the simulation more realistic and steady state, the IC Fab model was given a warm-up period. The warm-up period runs the simulation for

the entire defined run but starts collecting statistics after the end of the warm-up period.

The challenge with modeling the initialization bias for the model was to decide the how to throw some entities around in the model and at what time. This problem was approached by using the half-width smallness criterion and removing all other replication and simulation stopping criterion. The Arena time-persistent output statistic DSTAT was used and a simulation stopping condition of [DHALF(Total\_WIP\_FIFO) <1] was used with a confidence interval of 95%. The results of the simulation were obtained as follows.

| Time-      | Run    | Average | Half- | Minimum | Maximum |

|------------|--------|---------|-------|---------|---------|

| Persistent | Length |         | Width | Value   | Value   |

| Statistic  | (days) |         |       |         |         |

| Total WIP  | 43     | 88.16   | 0.94  | 0       | 145     |

Table 4.4 Warm-Up Period Simulation Result

Hence, the FIFO and all the models that were subsequently built on FIFO were modeled with a warm-up period of 43 days. Further remedy to initialization bias were running the model for a long period of time (43+365 =408 days).

# Chapter 5: Simulation Results and Analysis

## Purpose

The goal of a simulation study is to implement a model in a specific environment that allows the model's execution over time. As discussed in Chapter 4, the base model for the fab is developed as FIFO, upon which SPT, Priority Based and Failure FIFO models are developed. The results and statistics are presented and analyzed in this section. The simulation output analysis was performed on the Arena Output Analyzer and Excel (data exported from Arena).

## Cycle Time Analysis

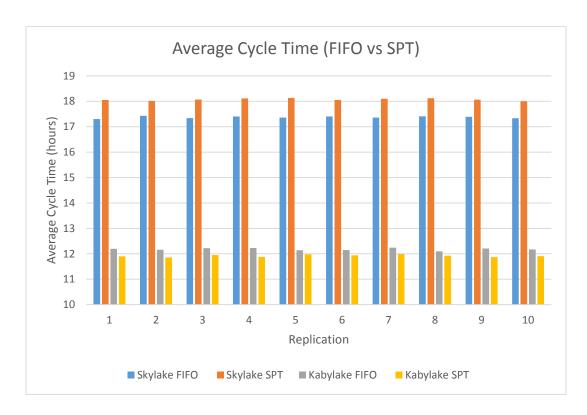

The average cycle time for 10 replications of the 3 models (SPT, PB and Failure FIFO) are compared to the base model (FIFO).

#### FIFO vs SPT

The average cycle time analysis result between FIFO and SPT is shown below. It can be observed from the clustered column graph that the average cycle time for the Skylake FIFO is much less than that for the Skylake SPT, while on the other hand, Kabylake SPT has a smaller average cycle time than Kabylake FIFO model. Technically, the SPT is supposed to perform better than the FIFO, but since we have two wafers being processed at the same time, and Kabylake having lower processing time compared to Skylake, Kabylake entities tend to be pushed ahead in the queue near the processing station and the Skylake entities tend to be pushed behind in the queue. Hence, on an average the cycle time increases for the Skylake wafer and

decreases for the Kabylake wafer when the FIFO model is converted to an SPT model.

Figure 5.1 FIFO vs SPT Average Cycle Time

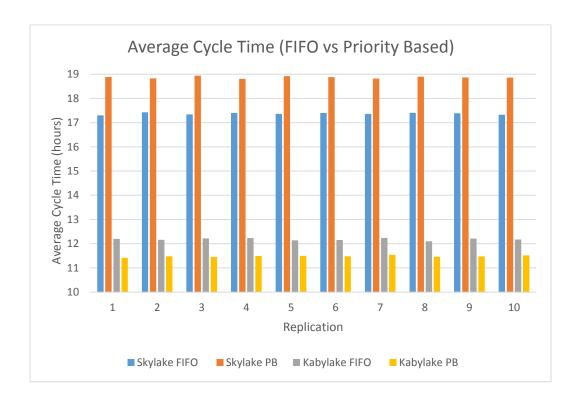

## FIFO vs PB

The clustered graph below provides a comparative study between the average cycle time for FIFO and PB. It can be observed from the graph that Skylake FIFO has a much lower average cycle time compared to the Skylake PB model, while Kabylake PB has a smaller average cycle time than Kabylake FIFO model. This can be explained by the fact that Kabylake is the prioritized wafer, and hence Kabylake entities are pushed to the start of the processing station queue, hence reducing the

overall average cycle time. On the other hand, Skylake entities are pushed back in the queue, which results in an increased time in the fab, and hence an increased average cycle time.

Figure 5.2 FIFO vs PB Average Cycle Time

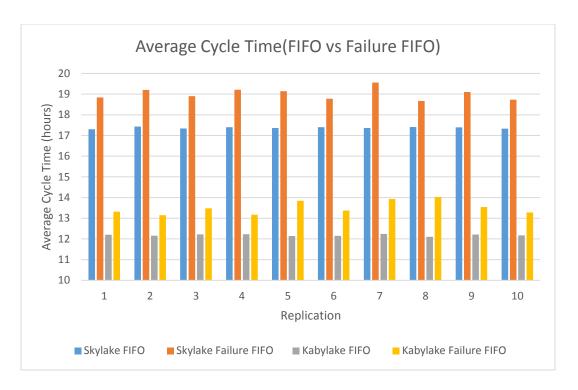

## FIFO vs Failure FIFO

The clustered graph below presents a comparative study between the average cycle time for the FIFO and Failure FIFO. It can be observed from the curve that the average cycle time for both the Skylake and Kabylake FIFO is much less than that for the Skylake and Kabylake Failure FIFO. This result can be associated to the fact that failures are modeled as preemptive; hence, when a machine fails, processing is

stopped, and long queues are formed at these stations, leading to an increase in the overall cycle time for the entities.

Figure 5.3 FIFO vs FIFO Failure Average Cycle Time

# Average Waiting Time Analysis

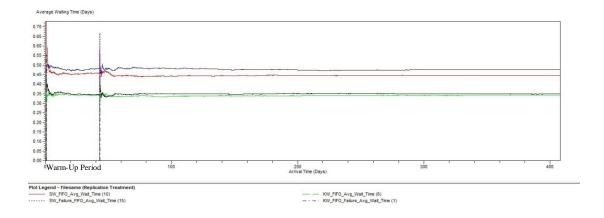

# Average waiting time