#### ABSTRACT

Title of dissertation: THERMAL AND PERFORMANCE

MODELING OF NANOSCALE MOSFETS,

CARBON NANOTUBE DEVICES AND INTEGRATED CIRCUITS

Akin Akturk, Doctor of Philosophy, 2006

Dissertation directed by: Professor Neil Goldsman

Department of Electrical and

Computer Engineering

We offer new paradigms for electronic devices and digital integrated circuits (ICs) in an effort to overcome important performance threatening problems such as self heating. To investigate chip heating, we report novel methods for predicting the thermal profiles of complex ICs at the resolution of a single device. We resolve device and IC temperatures self-consistently, with individual device performances, while accounting for IC layout and software application details. At the device level, we calculate performance and generated heat details. We then extend these performance figures to the overall chip using a stochastic or Monte Carlo type methodology. Next, at the IC level, we solve for the device temperatures using the chip's layout and application software details. Here, we apply our mixed-mode algorithm to two-dimensional (planar) and three-dimensional ICs. To relieve thermal stresses and performance degradation in specific areas of extreme heating or hot spots, we offer design strategies using thermal contacts or different IC layouts. Moreover, we

also show chips that we had designed and fabricated through IC fabrication clearing house MOSIS for experimental investigations.

We also investigate carbon nanotubes (CNTs) and CNT embedded MOSFETs as new device paradigms for future electronic circuits. To examine the effects of CNTs on device performance, we develop a CNT Monte Carlo simulator, and determine scattering rates and CNT electron transport. Here, we report positiondependent velocity oscillations and length effects in semiconducting single-walled zig-zag carbon nanotubes. Our calculated results indicate velocity oscillations in the Terahertz range, which approaches phonon frequencies. This may facilitate new high frequency RF device and circuit designs, opening new paradigms in communication networks. Furthermore, to obtain device performance figures for MOSFETs that embed CNTs in their channels, our device solver determines interactions between the CNT and silicon (Si) by obtaining quantization and transport effects on the tube and the Si, and at the CNT-Si barrier. We predict that the CNT-MOSFET yields a better performance than the traditional MOSFET. Especially, CNT-MOSFETs employing lower diameter tubes exhibit improved performance capabilities. We also perform similar analyses for CNT embedded SOI-MOSFETs.

# THERMAL AND PERFORMANCE MODELING OF NANOSCALE MOSFETS, CARBON NANOTUBE DEVICES AND INTEGRATED CIRCUITS

by

### Akin Akturk

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2006

#### Advisory Commmittee:

Professor Neil Goldsman, Chair/Advisor

Professor Martin Peckerar

Professor Chia-Hung Yang

Professor Christopher Davis

Associate Professor Michael Fuhrer

© Copyright by

Akin Akturk

2006

# DEDICATION

To my parents, Fatma and Hüseyin Aktürk.

# ACKNOWLEDGMENTS

I would like to thank my research advisor Prof. Dr. Neil Goldsman for guiding me in my research studies. His support made this work both possible and enjoyable for me. Also, I especially would like to thank Prof. Martin Peckerar for valuable discussions. In addition, I would like to thank the Department of Electrical and Computer Engineering of the University of Maryland College Park, LPS and George Metze for their supports.

Next, I would like to thank members of my dissertation committee. I would like to thank Prof. Chia-Hung Yang, Prof. Christopher Davis, Associate Prof. Michael Fuhrer, and once again Prof. Martin Peckerar and my advisor Prof. Neil Goldsman.

I also wish to thank my colleagues in my research group for their support and help: Zeynep Dilli, Dr. Gary Pennington, Dr. Chung-Kuang, Dr. Stephen Powell, Siddharth Potbhare, Bo Yang, Latise Parker, Datta Sheth, Yun Bai, Amrit Bandyopadhyay and Ben Funk.

Finally, I would like to thank my parents and Adam Markowski for their support and love.

### TABLE OF CONTENTS

| Lis | t of T                                   | Tables                                                | vi                                                                         |

|-----|------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|

| Lis | t of I                                   | Figures                                               | vii                                                                        |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Device Modeling                                       | 1<br>3<br>16<br>18<br>19                                                   |

| 2   | Devi<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5  | 2.1.2 Discretized Drift-Diffusion Equations           | 23<br>25<br>25<br>31<br>33<br>38<br>40<br>43<br>47                         |

| 3   | Cark<br>3.1<br>3.2<br>3.3                | 3.1.1 Monte Carlo for Long Tubes: The Continuum Model | 49<br>51<br>52<br>54<br>56<br>63<br>63<br>66<br>67<br>67<br>69<br>71<br>72 |

|     | 3.5<br>3.6<br>3.7                        | 3.4.4 Length Dependent CNT Mobility                   | 75<br>78<br>79<br>80                                                       |

| 4   | Carl       | oon Nar  | notube Embedded Device Modeling                                                                                    | 82  |

|-----|------------|----------|--------------------------------------------------------------------------------------------------------------------|-----|

|     | 4.1        | Quant    | um Modeling and Proposed Designs of Carbon Nanotube (CNT)                                                          |     |

|     |            | Embed    | dded Nanoscale MOSFETs                                                                                             | 84  |

|     |            | 4.1.1    | Quantum CNT-Silicon Device Simulator                                                                               | 85  |

|     |            | 4.1.2    | Simulation Results                                                                                                 |     |

|     |            | 4.1.3    | Section Summary                                                                                                    | 99  |

|     | 4.2        | Device   | e Behavior Modeling for Carbon Nanotube Silicon-On-Insulator                                                       |     |

|     |            |          | ETs                                                                                                                | 99  |

|     |            | 4.2.1    | Carbon Nanotube Model                                                                                              | 101 |

|     |            | 4.2.2    | Quantum CNT-SOI-MOSFET Model                                                                                       | 103 |

|     |            | 4.2.3    | Simulation Results                                                                                                 | 105 |

|     | 4.3        | Chapte   | er Summary                                                                                                         | 109 |

| 5   | Into       | mated (  | Circuit Modeling, Heating Effects                                                                                  | 111 |

| 9   | 5.1        | _        | Circuit Modeling: Heating Effects Integrated Circuits (ICs): Two-Dimensional (2D)                                  |     |

|     | 5.1        | 5.1.1    | Device Performance Model                                                                                           |     |

|     |            | 5.1.1    | Full-Chip Heating Model                                                                                            |     |

|     |            | 5.1.2    | Coupled Device and Full-Chip Heating Model: Methodology .                                                          |     |

|     |            | 5.1.4    | Coupled Device and Full-Chip Heating Model: Methodology .  Coupled Device and Full-Chip Heating Model: Application | 124 |

|     |            | 9.1.4    | and Results                                                                                                        | 197 |

|     |            | 5.1.5    | Section Summary                                                                                                    |     |

|     | 5.2        |          | d Integrated Circuits (ICs): Three-Dimensional (3D)                                                                |     |

|     | 0.2        | 5.2.1    | Device Performance and 3D IC Modeling                                                                              |     |

|     |            | 5.2.2    | Mixed-Mode Device Performance and 3D IC Heating: Cou-                                                              | 112 |

|     |            | 0.2.2    | pled Algorithm                                                                                                     | 143 |

|     |            | 5.2.3    | Mixed-mode Device Performance and 3D IC Heating: Appli-                                                            | 110 |

|     |            | 0.2.0    | cation and Results                                                                                                 | 149 |

|     |            | 5.2.4    | Effects of Different Layer Thicknesses on 3D IC Heating                                                            |     |

|     |            | 5.2.5    | Section Summary                                                                                                    |     |

|     | 5.3        | Metho    | ds for Cooling ICs                                                                                                 |     |

|     | 5.4        |          | imental Investigations                                                                                             |     |

|     | 5.5        |          | eating Effects at Cryogenic Temperatures                                                                           |     |

|     |            | 5.5.1    | Device and Chip Model                                                                                              |     |

|     |            | 5.5.2    | Simulation Results                                                                                                 |     |

|     | 5.6        | Chapt    | er Summary                                                                                                         |     |

| 6   | TI         | aia D1 1 | lications                                                                                                          | 100 |

| O   |            |          |                                                                                                                    | 189 |

|     | 6.1<br>6.2 |          | al Publications                                                                                                    |     |

|     | 0.2        | Comer    | ence i upincations                                                                                                 | 190 |

| Bil | bliogr     | aphy     |                                                                                                                    | 194 |

# LIST OF TABLES

| 3.1 | Spring constants, in N (kg·m/s <sup>2</sup> ), of the graphene in $x$ (radial), $y$ (transverse in-plane) and $z$ (transverse out-of-plane) directions, shown in Fig. 3.3, for the first to the forth nearest neighbors [16] 58 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | CNT parameters                                                                                                                                                                                                                  |

| 5.1 | Percentage areas and powers of functional blocks in a Pentium III chip [79, 80]                                                                                                                                                 |

| 5.2 | Comparison of peak boundary and channel temperatures 165                                                                                                                                                                        |

# LIST OF FIGURES

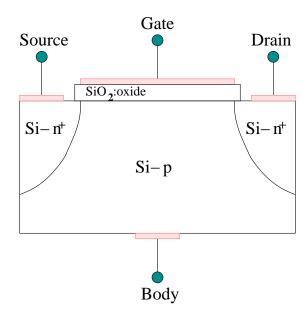

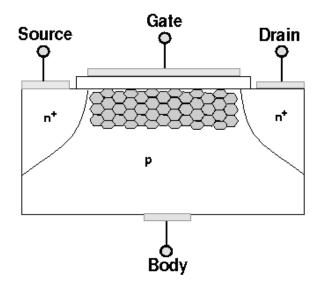

| 2.1  | A silicon n-MOSFET                                                                                                                                                                                                                              | 24 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

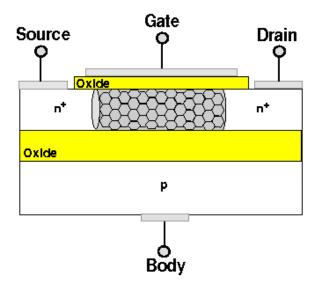

| 2.2  | A CNT embedded SOI-MOSFET                                                                                                                                                                                                                       | 34 |

| 2.3  | A CNT embedded silicon MOSFET                                                                                                                                                                                                                   | 40 |

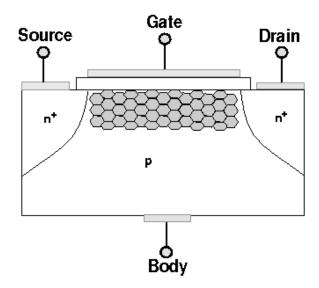

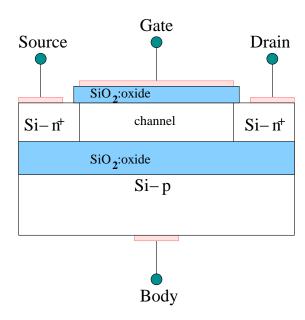

| 2.4  | An SOI-MOSFET                                                                                                                                                                                                                                   | 44 |

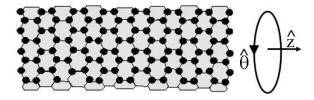

| 3.1  | A single wall zig-zag carbon nanotube, with fundamental indices $n$ and $m=0,$ and length $L.$                                                                                                                                                  | 49 |

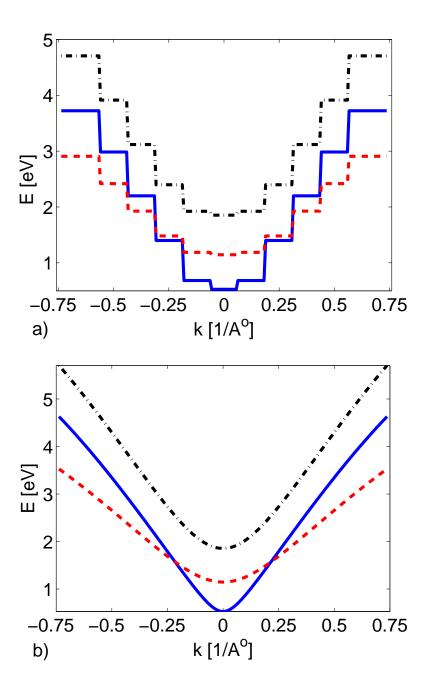

| 3.2  | a) Discretization of the energy dispersion curves of a 5nm long $n=10$ CNT ( $T=0.46$ nm). b) Energy dispersion relations for the first three subbands of an infinitely long $n=10$ CNT                                                         | 55 |

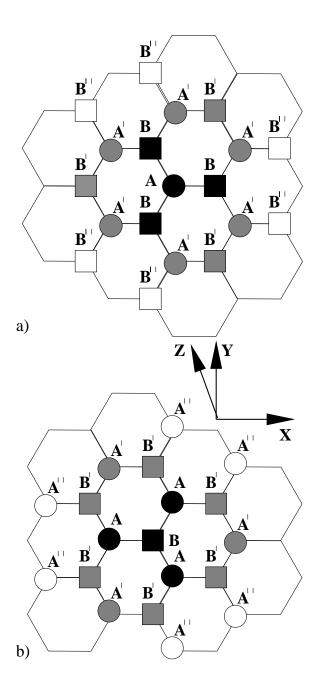

| 3.3  | Four nearest neighbors of the two atoms, solid circle A in a) and solid square B in b), in the graphene unit cell $[16]$                                                                                                                        | 59 |

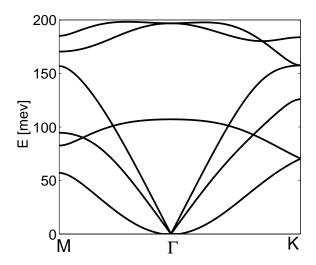

| 3.4  | The graphene phonon dispersion curves along the symmetry lines                                                                                                                                                                                  | 60 |

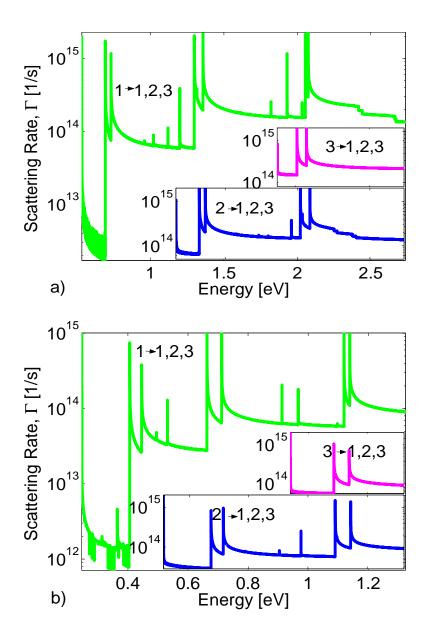

| 3.5  | Scattering rates from the first, second (lower left corner) and third (on top of the lower left corner plot) subbands to the lowest three subbands of CNTs with indices of a) 10 and b) 22. Insets share the same abscissa with the mother plot | 62 |

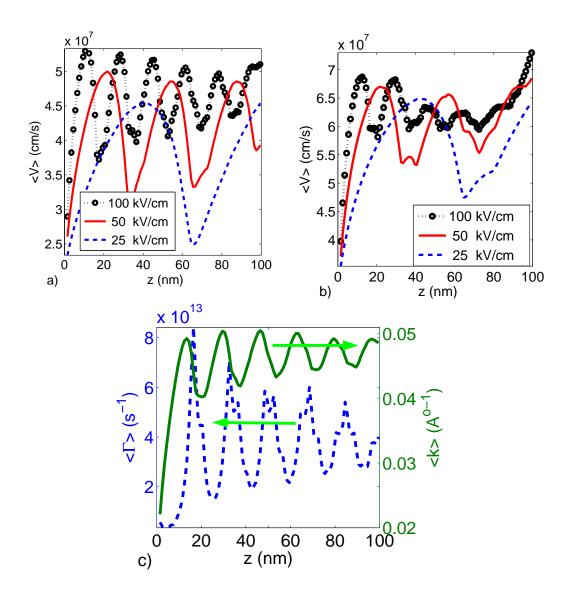

| 3.6  | Average local electron velocities on 100nm-long CNTs with indices of a) 10 and b) 22. c) Average local scattering rate and momentum for the $n=10$ tube under $F=100 \mathrm{kV/cm}.$                                                           | 65 |

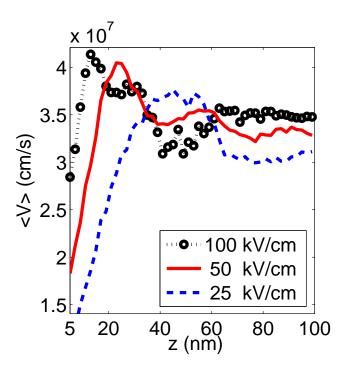

| 3.7  | Average velocity of an electron on various length $n{=}10~\mathrm{CNTs}$                                                                                                                                                                        | 66 |

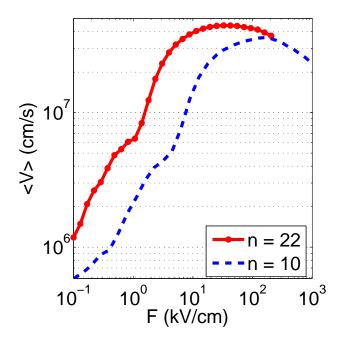

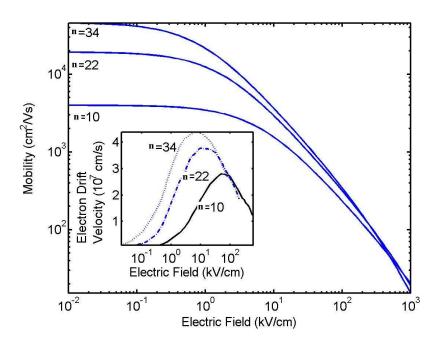

| 3.8  | Average electron velocities as a function of applied field on infinitely long CNTs with indices of 10 and 22                                                                                                                                    | 67 |

| 3.9  | Average electron velocities as a function of applied field on infinitely long CNTs with indices of 10 and 22                                                                                                                                    | 68 |

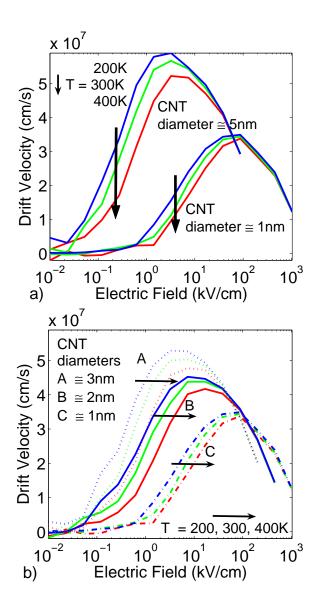

| 3.10 | Electron drift velocities as a function of the applied electric field for different CNTs varying in diameter and temperature                                                                                                                    | 73 |

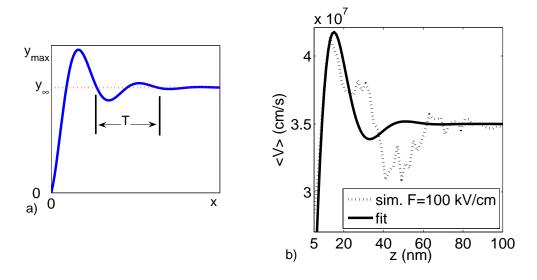

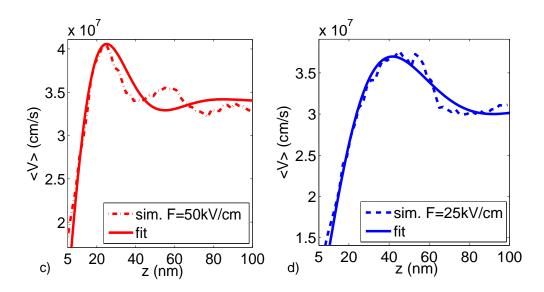

| 3.11 | a) Unit response of a second order differential system (damped case).<br>b), c), d) Average velocity curves of an electron on various length $n=10$ CNTs for different applied fields are fitted to an analytical expression given in Eqn. 3.31 | 77 |

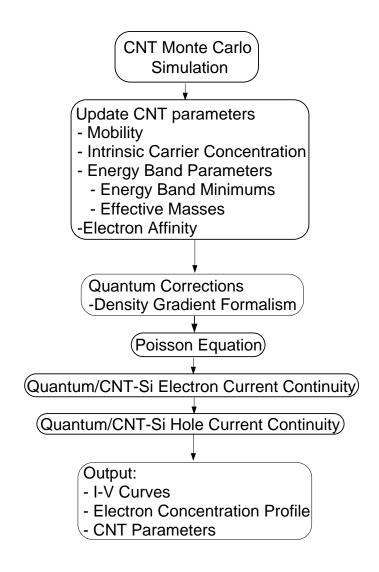

| 4.1  | Simulated CNT-MOSFET device                                                                                                                                                                                                                                                                                                                                                                                                               | 83  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | Coupled algorithm flowchart                                                                                                                                                                                                                                                                                                                                                                                                               | 91  |

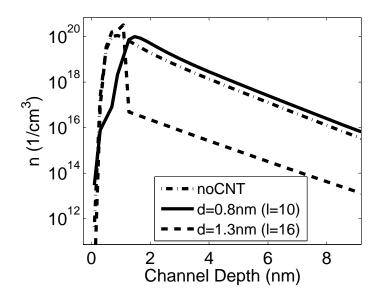

| 4.3  | Calculated electron concentration profile in the middle of the CNT-MOSFET channel, for different diameter CNTs and $V_G$ =1.5V ( $V_D$ and $V_S$ are 0V), starting from the Si-SiO <sub>2</sub> interface and going down about 9nm                                                                                                                                                                                                        | 92  |

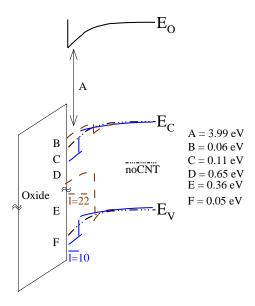

| 4.4  | Energy-band diagrams of CNT-MOSFETs, with diameters of 0.8nm and 1.3nm, and a MOSFET in the vertical channel direction. Dashed line is the band diagram of a CNT-MOSFET that has $l=22$ ( $d=1.3nm$ ) CNTs in its channel. Solid line is the band diagram of a CNT-MOSFET that has $l=10$ ( $d=0.8nm$ ) CNTs in its channel. Dot-dash line is the band diagram of the silicon in the vertical MOSFET channel direction                    | 93  |

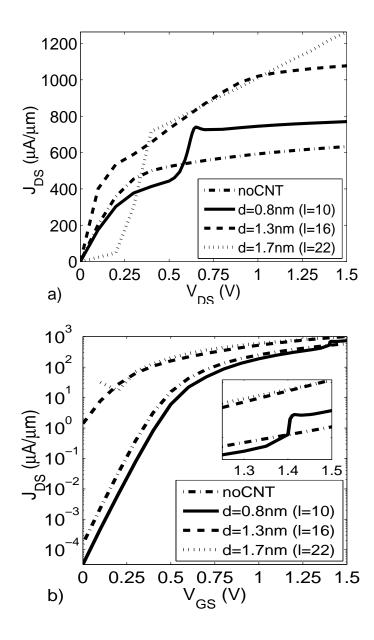

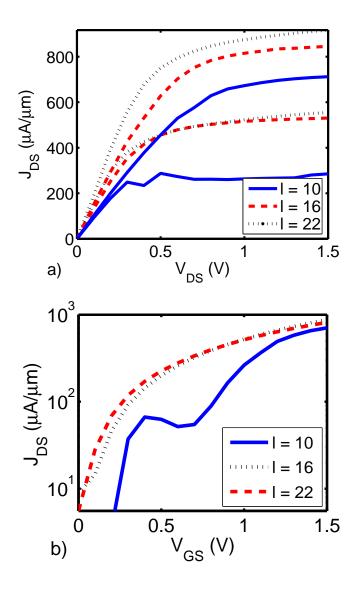

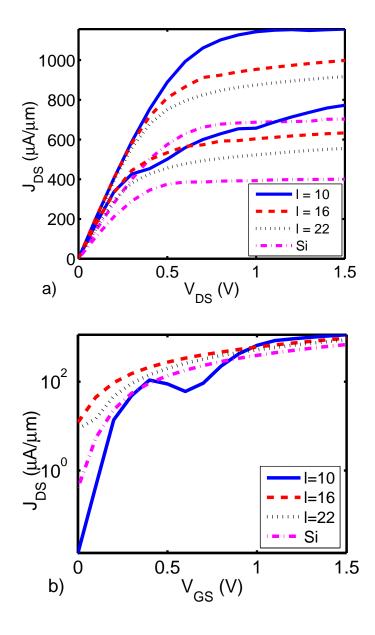

| 4.5  | Current-voltage curves for CNT-MOSFETs with different diameter CNTs. Calculated currents are for a) $V_{GS}$ =1.5V and b) $V_{DS}$ =1.0V (Inset shows the local maximum point for the $d$ =0.8nm tube CNT-MOSFET around $V_{GS}$ =1.4V.)                                                                                                                                                                                                  | 95  |

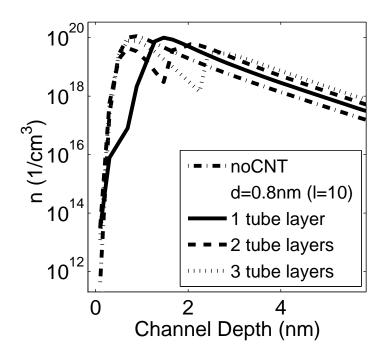

| 4.6  | Electron concentration profile in the middle of the CNT-MOSFET channel, for different number of CNT layers in the vertical channel direction and $V_G=1.5V$ ( $V_D$ and $V_S$ are 0V), starting from the Si-SiO <sub>2</sub> interface and going down about 6nm                                                                                                                                                                           | 97  |

| 4.7  | Current-voltage curves for CNT-MOSFETs with CNTs of 0.8nm in diameter and varying number of tube layers (planar CNT sheets) in the vertical channel direction. Calculated currents are for a) $V_{\rm GS}{=}1.5V$ and b) $V_{\rm DS}{=}1.0V$ (Inset shows the local maximum point for the one layered CNT-MOSFET around $V_{\rm GS}{=}1.4V$ . Two and three layered CNT-MOSFETs show a weaker local maxima around $V_{\rm GS}{=}0.5V$ .). | 98  |

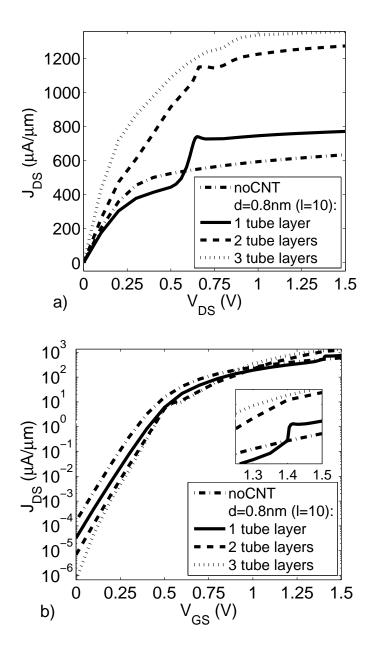

| 4.8  | Simulated design of CNT-SOI-MOSFET                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |

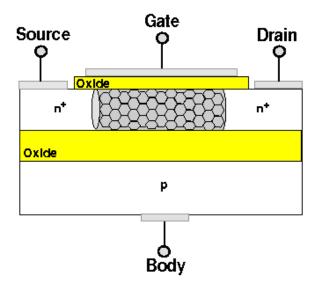

| 4.9  | a) Current-voltage ( $V_{GS}=1.0V,1.5V$ ) and b) subthreshold ( $V_{DS}=1.0V$ ) characteristics for CNT-SOI-MOSFETs with channel thicknesses equal to the diameter of the tube embedded. (Nanometer scale diameters of $l=10,16$ and 22 tubes are 0.8, 1.28 and 1.76, respectively.)                                                                                                                                                      | 106 |

| 4.10 | a) Current-voltage ( $V_{GS}=1.0V, 1.5V$ ) and b) subthreshold ( $V_{DS}=1.0V$ ) characteristics for CNT-SOI-MOSFETs with channel thicknesses equal to 1.76nm, which is the diameter of the biggest tube. (Nanometer scale diameters of $l=10$ , 16 and 22 tubes are 0.8, 1.28 and 1.76, respectively.)                                                                                                                                   | 108 |

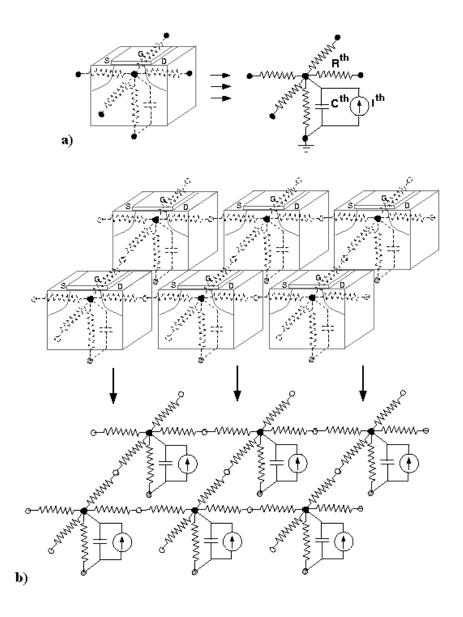

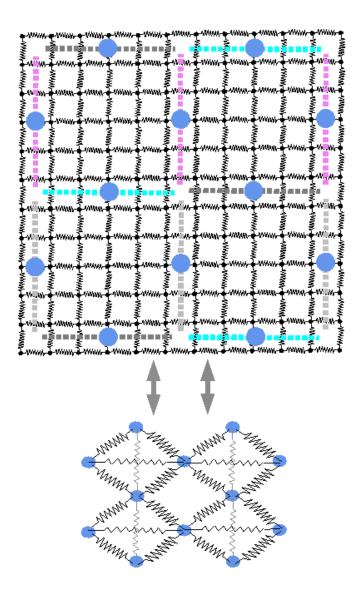

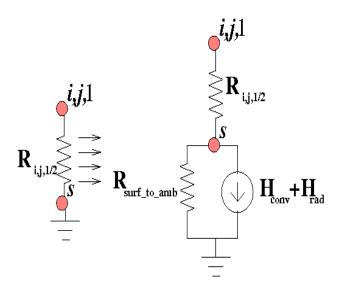

| 5.1  | a) Each MOSFET device is modeled by a lumped circuit for chip thermal analysis. b) Devices and their interaction are shown. Heat flow between devices causes thermal coupling                                                                                                                                                                                                                                                                                                 | . 115 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

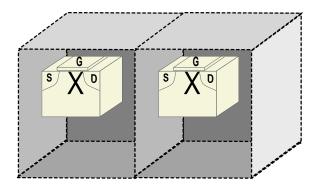

| 5.2  | We enclose each MOSFET by a rectangular prism to derive the lumped model. Here, the two enclosing prisms for two adjacent MOSFETs are shown, with X showing their centers of heat generation.                                                                                                                                                                                                                                                                                 | . 122 |

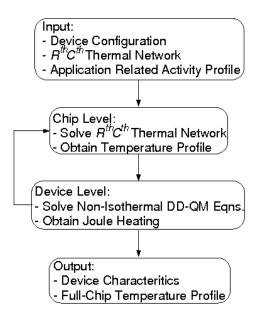

| 5.3  | Coupled algorithm flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 127 |

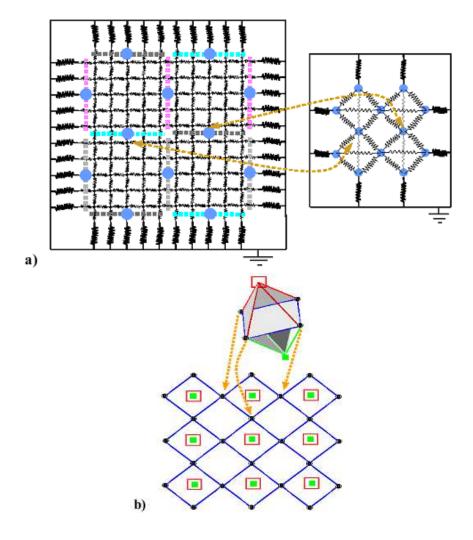

| 5.4  | Size reduction methods are applied on a subblock of five by five. We obtain four-port Norton representation of each block and use that representation instead, as shown at the bottom of the figure                                                                                                                                                                                                                                                                           | . 129 |

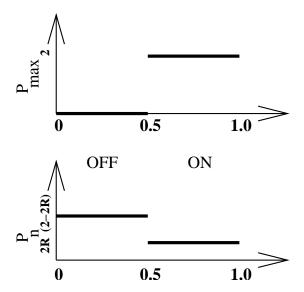

| 5.5  | Probability density functions for calculating the heat generated of devices in different functional blocks. Top is for a functional block, which has devices that are always mostly "on", Bottom is for any other functional block that has devices in "on" and "off" states                                                                                                                                                                                                  | . 133 |

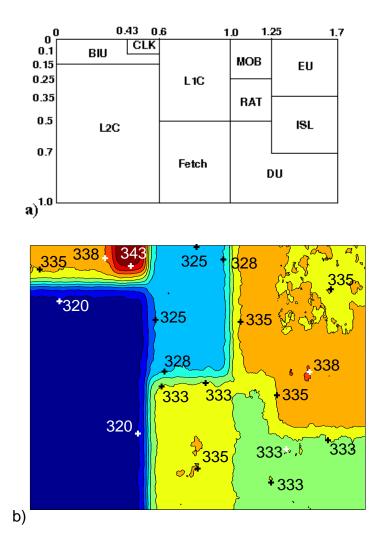

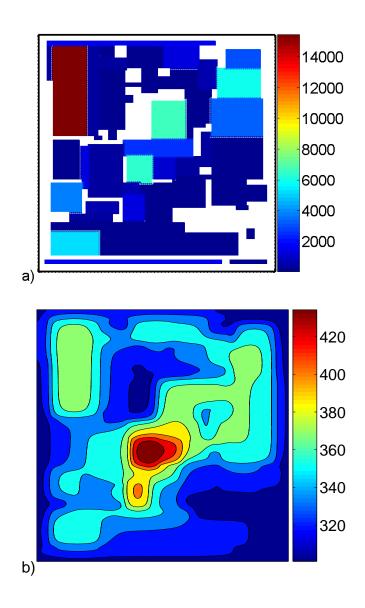

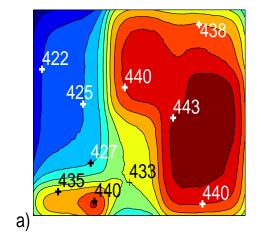

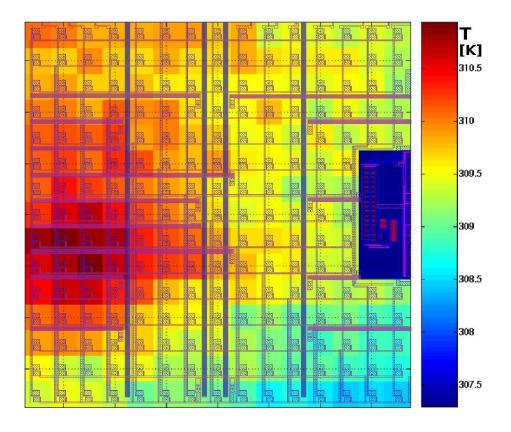

| 5.6  | a) Functional blocks of the Pentium III chip: Clock has the smallest area but the largest normalized power. Unlike L2 Cache that has the largest area but smallest normalized power as pointed out in Table 5.1. b) Our calculated temperature map for Pentium III reaches a peak in the clock block (forty three degrees above the ambient) and has the lowest temperature plateau in L2 cache (twenty degrees above the ambient). Ambient temperature is 300 degrees Kelvin | . 135 |

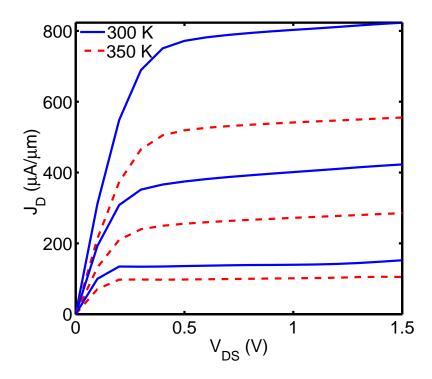

| 5.7  | Temperature dependent current-voltage characteristics of a $0.13\mu m$ n-MOSFET for $V_{GS}{=}0.7V,~1.0V,~1.5V.$ As temperature increases, current decreases                                                                                                                                                                                                                                                                                                                  | . 136 |

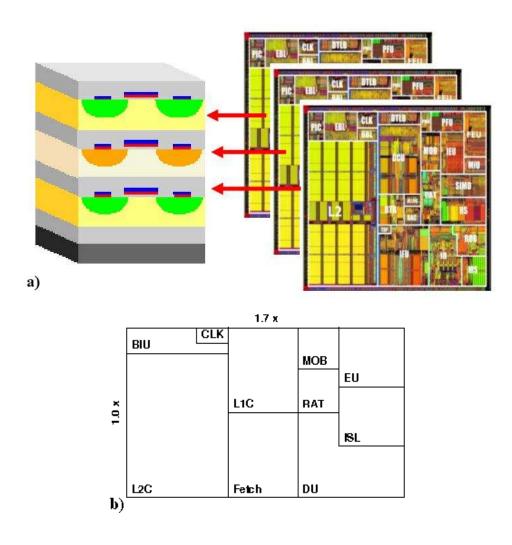

| 5.8  | a) A vertically stacked three layer 3D IC, where each layer is modeled after a Pentium III [1]. b) Floor plan of each layer in conjunction with Table 5.1                                                                                                                                                                                                                                                                                                                     | . 138 |

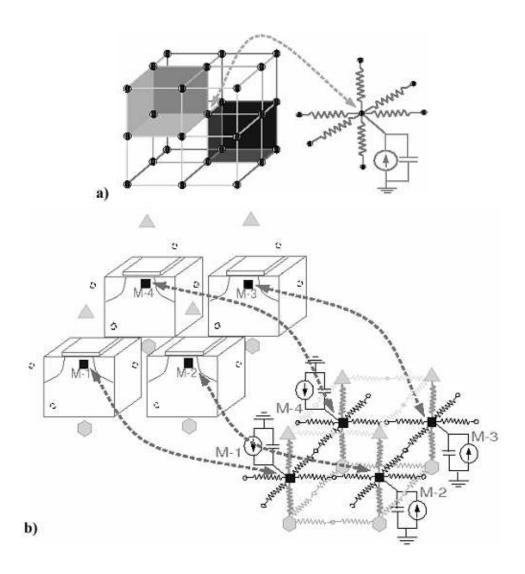

| 5.9  | a) To analyze 3D IC heating, each MOSFET (M) device is replaced by a current source and an $R^{\rm th}C^{\rm th}$ circuit. b) 3D IC's transistors interact thermally with each other as a result of thermal coupling                                                                                                                                                                                                                                                          | . 141 |

| 5.10 | Coupled algorithm flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 148 |

| 5.11 | To include surface heat transfer due to convection and radiation, we replace the ground resistor connected to the chip's surface, $s$ , shown on the left with the circuit shown on the right. The figure shows the boundary for the bottom layer, $k=1$ , in the vertical direction                                                                                                                                                                                          | . 150 |

| 5.12 | a) We apply size reduction methods to a planar chip with one hundred mesh points. We divide it up into four blocks. We then replace the original mesh with twelve nodes corresponding to four-port Norton representations of each block. (Bold resistors are for package.) b) In 3D, we have six-port tetrahedral shape Norton representations for cubes of grid points like the one shown in Fig. 5.9(a). Coupling to layers above and below is through nodes at the top and bottom of each tetrahedral shape, respectively                                                                                                                                                                                                                                                                                                                                      | 153 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

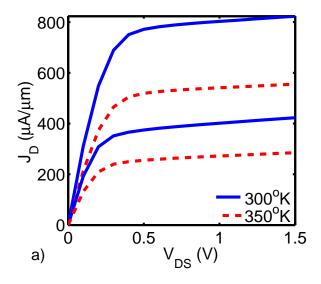

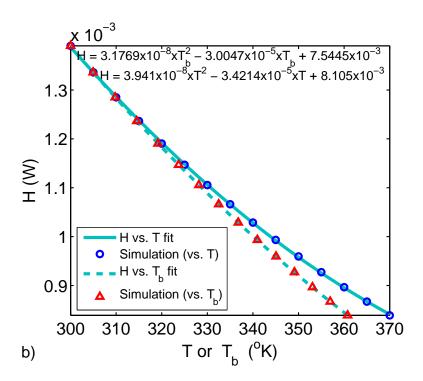

| 5.13 | a) Temperature dependent current-voltage characteristics of a $0.13\mu m$ N-MOSFET for $V_{GS}=1.0V,~1.5V.$ a) Steady-state heat generated $(V_{GS}=V_{DS}=1.5V)$ as a function of temperature $(T)$ and $\overline{T}$ $(T_b)$ . Conversion from $T$ to $\overline{T}$ is given in Eqn. 5.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 155 |

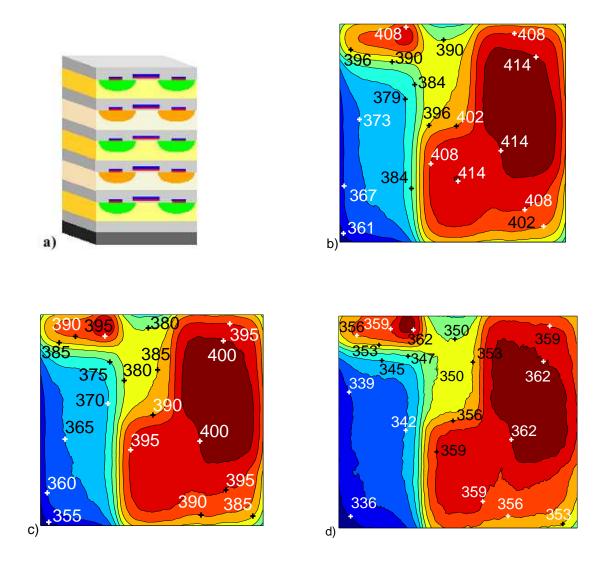

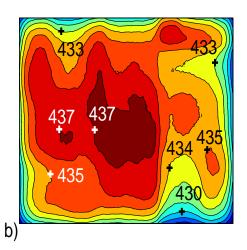

| 5.14 | a) A 3D IC with five layers of stacked Pentium III chips. Our calculated temperature maps corresponding to the b) middle, c) second and d) bottom layers shown in a). Here, ambient is at room temperature (300°K)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 156 |

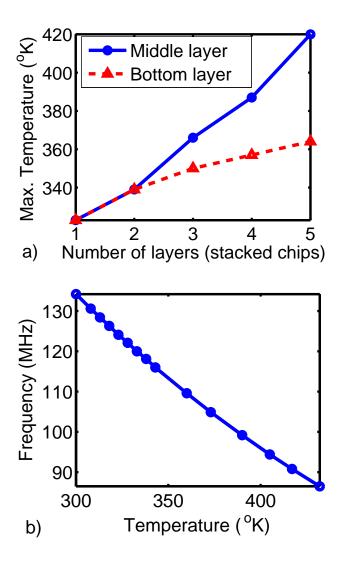

| 5.15 | a) Maximum temperature of the middle (also the maximum of the entire 3D IC) and bottom layers as a function of number of layers. b) Oscillation frequency of a thirty one stage ring oscillator calculated by Cadence [89] decreases as temperature increases. Here, ambient is at room temperature (300°K)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 158 |

| 5.16 | a) Maximum temperature of the middle (also the maximum of the entire 3D IC) and bottom layers as a function of number of layers. b) Oscillation frequency of a thirty one stage ring oscillator calculated by Cadence [89] decreases as temperature increases. Here, ambient is at room temperature $(300^{\circ}\mathrm{K})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 160 |

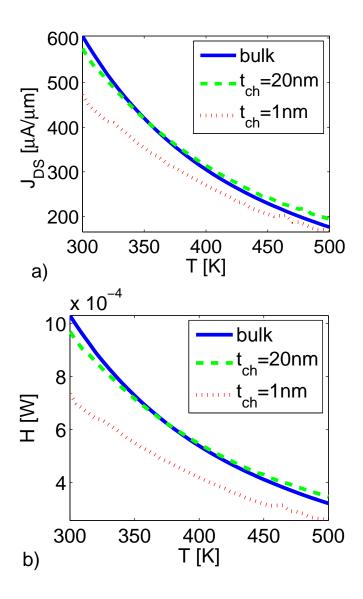

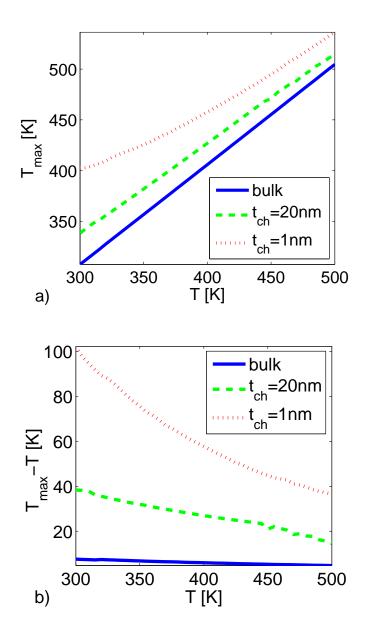

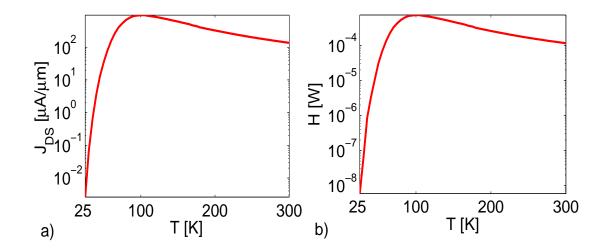

| 5.17 | Calculated a) current and b) heating figures of bulk and SOI-MOSFETs (0.13 $\mu m)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 162 |

| 5.18 | Calculated a) current and b) heating figures of bulk and SOI-MOSFETs (0.13 $\mu m)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 163 |

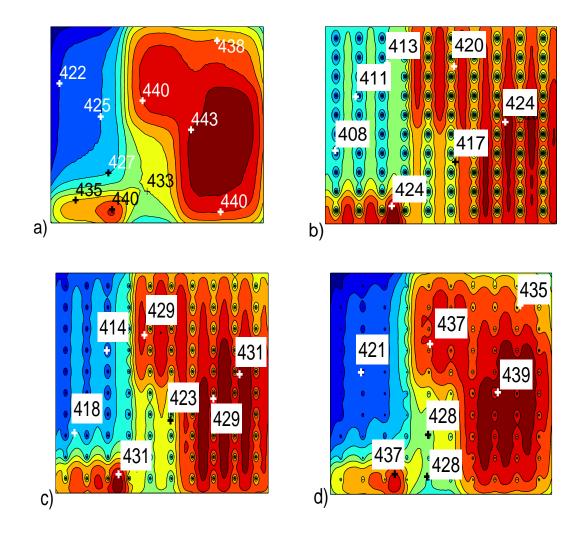

| 5.19 | Thermal maps for a 3D IC employing 1nm channel thickness SOI-MOSFETs and an array of 10 x 10 vertical vias. Thermal maps of peak channel temperatures are shown for the middle layer of a five layered 3D IC that employs thermal vertical vias, between the layers $(R_l)$ , and the top or bottom layer and the ambient $(R_b)$ . a) No vertical vias, where $T_{\text{max}}=445^{\circ}\text{K}$ and $T_{\text{ave}}=436^{\circ}\text{K}$ . b) $R_l=0.01\text{K/W}$ and $R_b=0.04\text{K/W}$ , where $T_{\text{max}}=426^{\circ}\text{K}$ and $T_{\text{ave}}=417^{\circ}\text{K}$ . c) $R_l=10\text{K/W}$ and $R_b=0.04\text{K/W}$ , where $T_{\text{max}}=432^{\circ}\text{K}$ and $T_{\text{ave}}=426^{\circ}\text{K}$ . d) $R_l=10\text{K/W}$ and $R_b=40\text{K/W}$ , where $T_{\text{max}}=441^{\circ}\text{K}$ and $T_{\text{ave}}=443^{\circ}\text{K}$ | 167 |

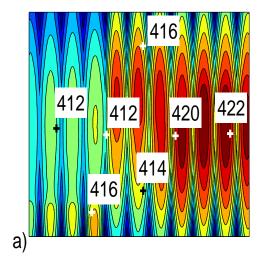

| 5.20 | Thermal maps for a 3D IC employing 1nm channel thickness SOI-MOSFETs and an array of 10 lateral vias. Thermal maps of peak channel temperatures are shown for the middle layer of a five layered 3D IC that employs lateral heat sinks, with resistances of $R_l$ within the layer, and $R_b$ at the boundaries. a) $R_l$ =0.01K/W and $R_b$ =0.04K/W, where $T_{\rm max}$ =424°K and $T_{\rm ave}$ =414°K. b) $R_l$ =10K/W and $R_b$ =0.04K/W, where $T_{\rm max}$ =445°K and $T_{\rm ave}$ =434°K |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

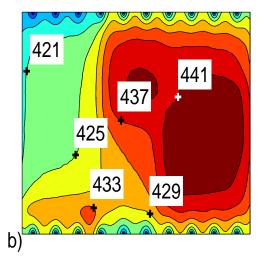

| 5.21 | Thermal maps for a 3D IC employing 1nm channel thickness SOI-MOSFETs. Thermal maps of peak channel temperatures are shown for the middle layer of a layered 3D IC using a) the same layout for each layer ( $T_{\rm max}$ =445°K and $T_{\rm ave}$ =436°K), or b) the ninety degrees rotated version for each consecutive layer ( $T_{\rm max}$ =438°K and $T_{\rm ave}$ =435°K)                                                                                                                    |

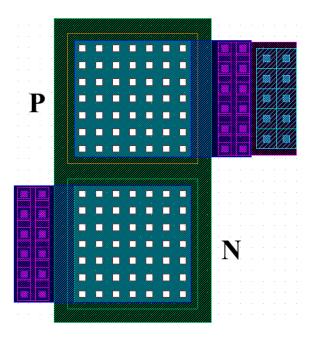

| 5.22 | We use a $pn$ junction diode as a temperature sensor. This $10 \times 10 \mu m^2$ diode was laid out using the Cadence Virtuoso tool [89] 172                                                                                                                                                                                                                                                                                                                                                       |

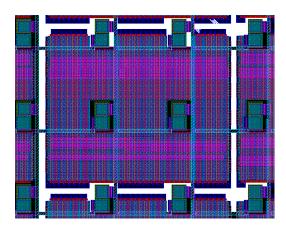

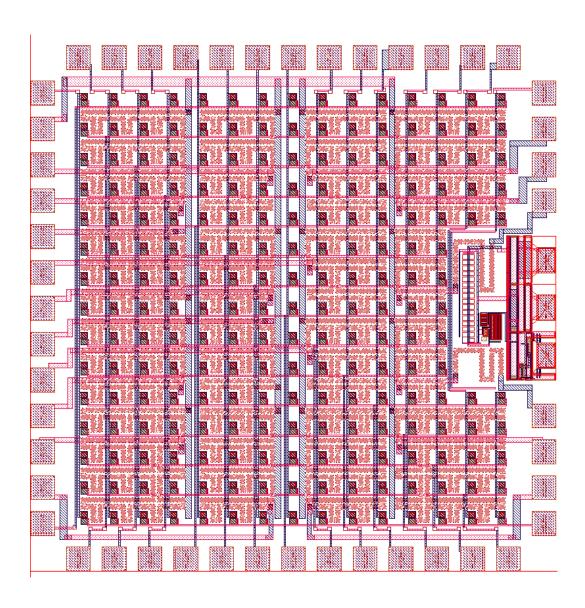

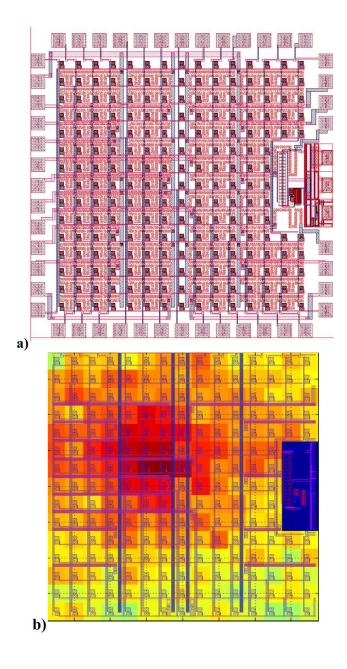

| 5.23 | A $10\times10$ diode array is laid out to locally measure temperatures on the chip. To facilitate readout, we included a multiplexer on the left to selectively enable different rows. The chip was laid out using the Cadence Virtuoso tool [89], and was fabricated through MOSIS [94] 174                                                                                                                                                                                                        |

| 5.24 | A rectangular NMOS microheater block is shown. The NMOS block is comprised of hundreds of smallest size NMOS devices with their gates, sources and drains shorted together to enable maximum heat generation                                                                                                                                                                                                                                                                                        |

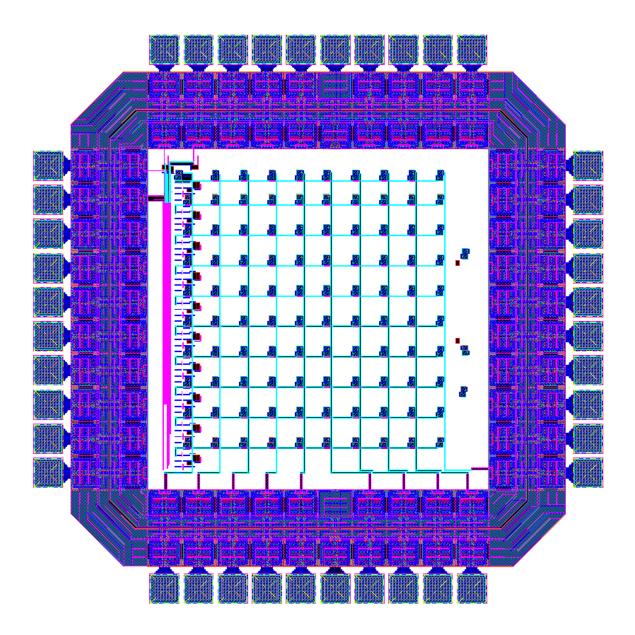

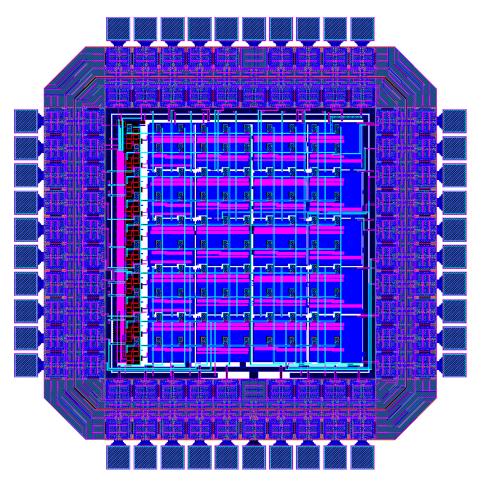

| 5.25 | An array of $4\times4$ NMOS heater blocks was superimposed onto the temperature sensing diode array network shown in Fig. 5.23. The chip was laid out using the Cadence Virtuoso tool [89], and was fabricated through MOSIS [94]                                                                                                                                                                                                                                                                   |

| 5.26 | Our fabricated chip with the $4\times4$ poly silicon differential microheater blocks superimposed onto the diode array sensor [95] 177                                                                                                                                                                                                                                                                                                                                                              |

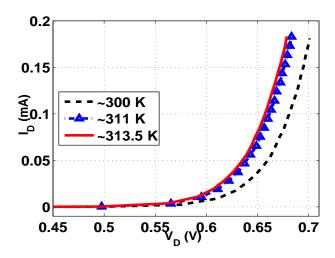

| 5.27 | Measured current-voltage characteristics of a diode used in the diode array as a function of temperature                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.28 | Measured temperatures after turning the third row-first column poly resistor block on. Peak temperatures, reaching 10 degrees above the ambient, are induced around this block, as shown on the left of the figure                                                                                                                                                                                                                                                                                  |

| 5.29 | Calculated a) current density and b) heat generated of a $0.13\mu m$ N-MOSFET. ( $V_{GS}=V_{DS}=0.7V$ )                                                                                                                                                                                                                                                                                                                                                                                             |

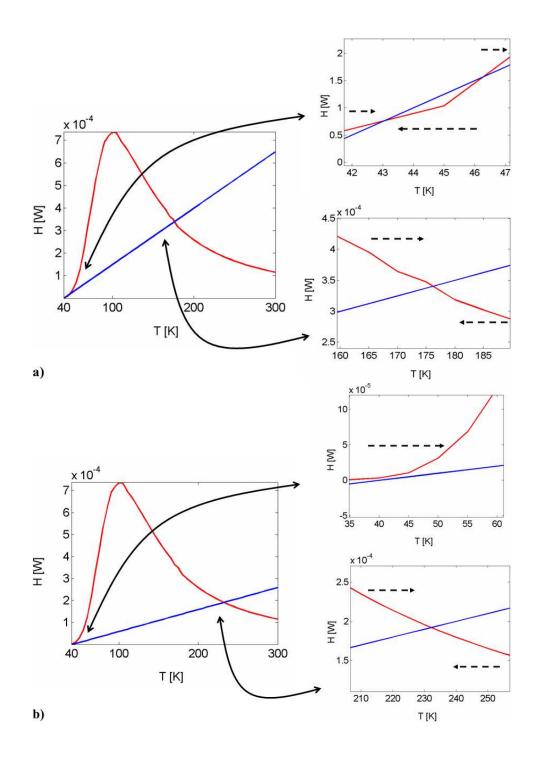

| 5.30 | Heat generated by a device and the resistive linear thermal current.                                                             |     |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Intersections (zoomed in on the right) are operating temperature con-                                                            |     |

|      | ditions. a) $T_A=40^{\circ}\text{K}$ , $R_C=4\times10^5\text{ K/W b}$ ) $T_A=40^{\circ}\text{K}$ , $R_C=1\times10^6\text{K/W}$ . |     |

|      | 183                                                                                                                              |     |

|      |                                                                                                                                  |     |

| 5.31 | a) Our fabricated chip with uniformly distributed $4\times4$ differential                                                        |     |

|      | microheater blocks and $15 \times 15$ thermal diode sensors. b) Induced                                                          |     |

|      | temperatures by turning the second row-second column resistor block                                                              |     |

|      | on. Darker middle region is about seven degrees warmer than the                                                                  |     |

|      | lighter regions                                                                                                                  | 184 |

### Chapter 1

#### Introduction

### 1.1 Motivation

As integrated circuits (ICs) become more densely packed with transistors and we approach the end of the semiconductor roadmap, manufacturers are facing several important problems threatening chip performance. To overcome these problems, investigators are exploring new paradigms for electronic devices and digital integrated circuits [1, 2].

For future integrated circuits, one especially important difficulty is chip heating [1]-[11]. Investigators have pointed out that towards the end of the semiconductor roadmap, there will be more devices per unit area due to scaling of physical device dimensions. This real estate crowding induces high temperatures, since power density can not be kept in line with the conventional scaling algorithm. The rule of thumb for the traditional scaling algorithm is that all relevant parameters are scaled by the same factor S, either proportionately or inversely, to keep the power density fixed. For example, physical dimensions and supply voltage are scaled downward by S, while frequency and capacitance per area are scaled upward by S. The power density, therefore, stays the same after scaling. However, voltage scaling will no longer be applicable for such small dimensions because of the intrinsic limitations of silicon (Si) bandgap and built-in voltages [1]-[5]. Therefore, IC manufacturers

deviate from the traditional scaling methods to guarantee good device and chip performances such as high on/off current ratios and subthreshold slopes. This results in clock frequencies and supply voltages that are higher than previously expected. In addition, nanoscale devices can not provide as much isolation between supply rails as previously employed longer channel devices. This leads to higher leakage levels. The chip also is likely to overheat faster than conventional cooling methods can account for. Thus power density per unit area keeps increasing exponentially for future electronic devices, making full-chip heating increasingly influential in the performance of next generation ICs. Hence, chip heating is considered as one of the major obstacles to be overcome for future IC designs [1]-[11].

To fully understand the chip-heating problem, researchers need tools to simulate and examine the phenomenon. These modeling tools can also be used to relieve heating problems by offering new design approaches to the chip layout. Preliminary research has been done to estimate the temperature profile for given chips [7]-[11]. Here, we develop a tool that establishes the necessary link between single device operation and full-chip heating for the first time in the literature.

We also explore new alternatives to conventional MOSFETs. Carbon nanotubes (CNTs) are being explored as a structure that may play a leading role in future electronic systems [12]-[15]. CNTs are planar graphite sheets (graphene) that are seamlessly wrapped into tubes. CNTs possess favorable electrical characteristics and can be fabricated in dimensions as small as 8Å in diameter. The electrical characteristics of CNTs vary with the diameter and the wrapping angle of the graphene [16]. Both the diameter and the wrapping angle can be described by the tube's

fundamental indices (l,m) (Standard notation uses (n,m)). However, l is used in some chapters instead of n to avoid confusion with electron concentration). Theory indicates that CNTs can be metallic or semiconducting according to the fundamental tube indices (l,m), with the bandgap of the semiconducting tube depending on the CNT diameter. Analysis shows semiconducting CNTs have very high low-field mobilities, with peak electron drift velocities that can be as much as five times higher than that of silicon [17]-[21]. It has also been shown that tubes can be doped by donors and acceptors [22]-[24]. Experiments and calculations also indicate that CNTs may facilitate devices with large transconductances and high drive currents [20]-[39]. Experiments have demonstrated the viability of CNT-based FETs [34, 35], and CNT-SOI type MOSFETs [36, 37]. Moreover, we did preliminary research on modeling and design of CNT embedded bulk MOSFETs [30, 31].

Here, we investigate several CNT-MOSFET devices for the first time in the literature. Our calculations indicate that CNT-MOSFETs can have improved device performance over conventional MOSFETs [30, 31]. To investigate the potential attributes of the new designs, we developed a methodology for modeling nanoscale CNT-MOSFETs. We also used the same methodology to obtain device performance figures for SOI-MOSFETs that have CNTs embedded in their channels.

### 1.2 Device Modeling

To obtain performance details of devices like nanoscale MOSFETs and Silicon-On-Insulator (SOI) MOSFETs, several modeling methods either based on compact analytical equations or physics can be utilized. Even though the ones based on compact analytical equations such as the SPICE model are useful for fast performance computation of devices and circuits containing several nodes, their results can not be extrapolated to predict performance details of smaller devices. The reason is that the parameters inherent to these models are empirically determined using experimental data or simulated (using a lower level device solver) device performance characteristics for that technology node. Therefore, their applicability to other, especially smaller, technology nodes might lack underlying physics. Also, these models can not be extended to unconventional device structures, since these novel structures are not geometrically relevant to those used to extract fitting parameters. In addition, they may not be governed by the same physical relations. Thus, to investigate nanoscale devices, researchers need to use physics based models.

Depending on the number of details and assumptions included, physical models can be divided up into three main categories:

- Classical Model

- Semiclassical Model

- Quantum Model

The classical models are the moments of the Boltzmann Transport Equation (BTE). On the other hand, the BTE is a semiclassical model. Moreover, the BTE is a continuity equation for electrons, and keeps track of the electron distribution in real space, momentum space and time. According to carrier continuity, conservation of carriers requires that the change in carrier distribution in time should differ

from the gradient of the net flux in real space and momentum space by the net contribution of "sources" and "sinks" in the enclosed momentum and real space volume. More specifically, if f(r, p, t) is the distribution function that gives the probability of finding a particle at position r and time t with momentum p, then particle continuity equation is the following.

$$\left(\frac{\partial}{\partial t} + \frac{\partial \vec{r}}{\partial t}\frac{\partial}{\partial r} + \frac{\partial \vec{p}}{\partial t}\frac{\partial}{\partial p}\right)f = G - R \tag{1.1}$$

Here, G and R are generation ("source") and recombination ("sink") terms, respectively. The net generation-recombination rate in real space is determined by the net scattering rate s(r,p,t) that accounts for phenomena such as photogeneration and recombination through traps or from band-to-band (Auger recombination). In momentum space, the collision ratio  $\frac{\partial f}{\partial t}\Big|_{\text{coll}}$  gives the net generation-recombination rate, which accounts for phenomena such as reflections and transmissions. Using the two terms for the net generation-recombination rate in real and momentum spaces, and replacing  $\frac{\partial \vec{r}}{\partial t}$  and  $\frac{\partial \vec{p}}{\partial t}$  with  $\vec{v}$  (velocity) and  $\vec{F}$  (force, which is equal to  $-q\vec{E}$  in an electric field  $\vec{E}$ ), respectively, the BTE becomes:

$$\frac{\partial f}{\partial t} + \vec{v} \cdot \vec{\nabla_r} f + \vec{F} \cdot \vec{\nabla_p} f = s(r, p, t) + \frac{\partial f}{\partial t} \bigg|_{\text{coll}}$$

(1.2)

To find the spatial and time distribution of a physical parameter  $\zeta(r,t)$ , the distribution function f(r,p,t) is first scaled by associated weighting coefficients w(p) and normalization factor  $\Omega$ , and then integrated over the momentum space, as written below:

$$\zeta(r,t) = \frac{1}{\Omega} \int w(p) f(r,p,t) dp \tag{1.3}$$

Above, substituting w(p) with 1, p (momentum) or  $\varepsilon$  (energy) respectively gives electron concentration n, average momentum P or average energy W for  $\zeta(r,t)$ . To obtain values for these physical parameters, we first need to calculate f(r,p,t). This requires finding a solution for the BTE [40, 41] for the physical parameter of interest. Below, we include the continuity equation for any physical parameter, which is obtained by multiplying Eqn. 1.2 by  $\frac{1}{\Omega} \int w(p) dp$ :

$$\frac{1}{\Omega} \int w(p) \frac{\partial f}{\partial t} dp + \frac{1}{\Omega} \int w(p) \vec{v} \cdot \nabla_r \vec{f} dp - q \frac{1}{\Omega} \int w(p) \vec{E} \cdot \nabla_p \vec{f} dp$$

$$= \frac{1}{\Omega} \int w(p) s(r, p, t) dp + \frac{1}{\Omega} \int w(p) \frac{\partial f}{\partial t} \Big|_{\text{coll}} dp \quad (1.4)$$

To derive continuity equations, we substitute w(p) with 1, which is equal to  $p^0$ . Thus, the drift-diffusion model is a classical model, and can be derived using the zeroth and first moments of the BTE. Moreover, the electron current continuity equation is derived using Eqn. 1.4 and the aforementioned expansion in  $p(p^0)$ . Next, the integrals in Eqn. 1.4 are evaluated, and the following expressions are substituted for each term above in the given order:

$$\frac{1}{\Omega} \int \frac{\partial f}{\partial t} dp = \frac{\partial n}{\partial t} \tag{1.5}$$

$$\frac{1}{\Omega} \int \vec{v} \cdot \vec{\nabla_r} f dp = \vec{v} \cdot \vec{\nabla_r} n \tag{1.6}$$

$$-q\frac{1}{\Omega}\int \vec{E} \cdot \vec{\nabla_p} f dp = -\frac{qEf}{\Omega}$$

(1.7)

$$\frac{1}{\Omega} \int s(r, p, t) dp = G_n - R_n \tag{1.8}$$

$$\frac{1}{\Omega} \int \frac{\partial f}{\partial t} \Big|_{\text{coll}} dp = -\frac{\Delta n}{\langle \tau_n \rangle}$$

(1.9)

Here, we have change in carrier (electron n) concentration in time, Eqn. 1.5, divergence of drift flux, Eqn. 1.6, field generation rate, Eqn. 1.7, net generation-

recombination term, Eqn. 1.8, and divergence of carrier diffusion flux, Eqn. 1.9. In addition,  $G_n - R_n$  is the net generation-recombination rate and  $\langle \tau_n \rangle$  is the ensemble relaxation rate. Furthermore, since f approaches zero fast, Eqn. 1.7 can be approximated by zero for low fields. Also, we further simplify the divergence of the diffusion flux using the diffusion constant  $D_n$ :

$$\frac{\Delta n}{\langle \tau_n \rangle} = \frac{\Delta r^2}{\langle \tau_n \rangle} \frac{\Delta n}{\Delta r^2} \cong D_n \nabla_r^2 n \tag{1.10}$$

Combining drift and diffusion fluxes together, we write the electron current continuity equation in a familiar form, as follows:

$$\frac{\partial n}{\partial t} = -\nabla_r \cdot (\vec{v}n + D_n \vec{\nabla_r}n) + G_n - R_n \tag{1.11}$$

Likewise, substituting w(p) with p in Eqn. 1.4, we derive the momentum balance equation. In this case, we have the following terms for the BTE (in one dimension):

$$\frac{1}{\Omega} \int p \frac{\partial f}{\partial t} dp = \frac{\partial P}{\partial t}$$

(1.12)

$$\frac{1}{\Omega} \int p\vec{v} \cdot \vec{\nabla_r} f dp = 2\nabla_r \cdot \vec{W}$$

(1.13)

$$-q\frac{1}{\Omega}\int p\vec{E}\cdot\vec{\nabla_{p}f}dp = -\frac{qEpf}{\Omega} - qnE$$

(1.14)

$$\frac{1}{\Omega} \int p \left. \frac{\partial f}{\partial t} \right|_{\text{coll}} dp = -\frac{\Delta P}{\langle \tau_p \rangle} \tag{1.15}$$

We have change in carrier momentum in time, Eqn. 1.12, divergence of average energy  $(\frac{1}{\Omega} \int p\vec{v} \cdot \nabla_r \vec{f} dp = \frac{1}{\Omega} \int 2\varepsilon \cdot \nabla_r \vec{f} dp = 2W)$ , Eqn. 1.13, field generation rate, Eqn. 1.14, and collision term, Eqn. 1.15. We do not have the scattering term as the one in Eqn. 1.8, because that does not contribute to a change in momentum space.

Additionally, in Eqn. 1.14,  $-qEpf \cong 0$  because f approaches zero fast for large p. Therefore, we can write a compact momentum balance equation, which is the first moment of the BTE, as shown below:

$$\frac{\partial P}{\partial t} = -2\nabla_r \cdot \vec{W} - qnE - \frac{\Delta P}{\langle \tau_p \rangle} \tag{1.16}$$

The second moment of the BTE is the energy balance equation. It is derived by substituting w(p) with  $\varepsilon = p^2/2m^*$  for parabolic bands, where  $m^*$  is the effective mass) in Eqn. 1.4. This gives the following terms for the energy balance equation:

$$\frac{1}{\Omega} \int \varepsilon \frac{\partial f}{\partial t} dp = \frac{\partial W}{\partial t}$$

(1.17)

$$\frac{1}{\Omega} \int \varepsilon \vec{v} \cdot \vec{\nabla_r} f dp = \nabla_r \cdot \frac{1}{\Omega} \int \varepsilon \vec{v} f dp \qquad (1.18)$$

$$-q\frac{1}{\Omega}\int \varepsilon \vec{E} \cdot \vec{\nabla_p} f dp = -\frac{qE\varepsilon f}{\Omega} - \frac{q\vec{E}\vec{P}}{m^*}$$

(1.19)

$$\frac{1}{\Omega} \int \varepsilon s(r, p, t) dp = G_{\varepsilon} - R_{\varepsilon}$$

(1.20)

$$\frac{1}{\Omega} \int \varepsilon \left. \frac{\partial f}{\partial t} \right|_{\text{coll}} dp = -\frac{\Delta W}{\langle \tau_{\varepsilon} \rangle}$$

(1.21)

Here, change in average energy in time, Eqn. 1.17, is related to the flow of energy, Eqn. 1.18, self-heating, Eqn. 1.19, energy exchange due to scattering leading to recombination and generation, Eqn. 1.20, and energy exchange between lattice and carriers, Eqn. 1.21. In Eqn. 1.19, the first term on the right-hand-side is approximately zero due to fast decay of f for large p, and the second term is equal to  $\vec{J} \cdot \vec{E}$  noting that  $\frac{q\vec{P}}{m^*} = \vec{J}$ , where  $\vec{J}$  is the current density. Also,  $\vec{J} \cdot \vec{E}$  can be recognized as Joule Heating. Therefore, the energy balance equation can be written in a concise form, as shown below:

$$\frac{\partial W}{\partial t} = -\nabla_r \cdot \frac{1}{\Omega} \int \varepsilon \vec{v} f dp + \vec{J} \cdot \vec{E} - \frac{\Delta W}{\langle \tau_{\varepsilon} \rangle} + G_{\varepsilon} - R_{\varepsilon}$$

(1.22)

We have shown zeroth, first and second moments of the BTE in Eqns. 1.11, 1.16 and 1.22, respectively. They are the carrier balance, momentum balance and energy balance equations in the aforementioned order. We note that each balance equation requires solution of higher order balance equations. For example, in Eqn. 1.11,  $\vec{v} = \vec{P}/m$ ; thus, to solve for n, we need to know P. Likewise, to solve for P in Eqn. 1.16, we need the spatial variation of W. Thus, it is impossible to solve the BTE moment equations unless we achieve closure using some approximations. The most commonly-used approximation is to write the drift velocity in terms of the electric field  $\vec{v} = \mu \vec{E}$ , where mobility  $\mu$  is the proportionality constant that is determined empirically from experimental data or detailed simulations such as low-level Monte Carlos (MCs). This provides the closure for the current continuity equation. We now need a relation between the carrier densities and the electric field to have a complete set of equations. This is provided by the Poisson Equation, which relates divergence of local electric field weighted by the dielectric constant,  $\epsilon$ , to the net charge density,  $\rho$ , as written below:

$$\nabla_r \cdot \epsilon \vec{E} = \rho \tag{1.23}$$

The carrier balance (current continuity) equation 1.11 along with the Poisson Equation, written above, forms the drift diffusion model. This is the most commonly-solved model to obtain device characteristics, mainly due to its simplicity and clear physical interpretation. However, ignoring the higher order moments of the BTE results in some loss of physical details. This includes loss of distribution details of carriers in energy space or temperature, which may be important

to characterize effects involving hot-electrons. It also includes the assumption that carriers reach equilibrium with the lattice through scattering. This enables the use of mobility and diffusion coefficient concepts. For not-so-high electric fields, hot electron effects are negligible; therefore, we can tolerate the loss of those data. In terms of scattering dominated electron current, unless the system is purely quantum mechanical such as those that can be found in ultra small devices, we can still develop a mobility model that accounts for non-equilibrium conditions by adjusting the mobility through experiments, published data or MC simulations. To improve the drift-diffusion model, researchers sometimes solve for the energy balance equation in addition to the carrier balance equation. In this case, the model is called the hydrodynamic model. Even though this model may successfully predict hot-electron effects, it may also produce erroneous data showing energy peaks near the MOSFET channel-source junction [40]. Therefore, its results should be carefully interpreted.

So far, we have described classical models, which are essentially the drift-diffusion and hydrodynamic models. Next comes the semiclassical models in the list of physical models. The main characteristics of semiclassical models are their use of scattering rates at the microscopic level (instead of using a mobility concept as in the classical model), and slope of the energy dispersion curve to determine the electron velocity.

Obtaining device characteristics using a semiclassical model can be done mainly in two ways. First is the single particle approach or the Monte Carlo (MC) method. This method includes statistical means to obtain macroscopic characteristics such as terminal currents. In this method, carriers are randomly picked from an energy-

momentum pool using carrier distribution details such as Fermi-Dirac statistics in conjunction with the energy dispersion curves. They then are accelerated under the macroscopic field with an effective mass  $m^*$  for a predetermined time that is long enough for acceleration but too short for any scattering event to take place. At the end of the flight, depending on a probabilistically dictated selection criteria, either the carrier continues its free flight or a randomly determined microscopic scattering event that generally depends on the carrier's energy and momentum occurs. Repeating this drift-scattering combination a significantly large enough number of times allows determination of average macroscopic field dependent parameters such as drift velocity for the carrier with the preselected initial energy-momentum combination. For different energy-momentum combinations in the energy-momentum pool, we can obtain similar average macroscopic field dependent parameters. Lastly, scaling these average macroscopic field dependent parameters in conjunction with the associated initial selection statistics would give the average macroscopic field dependent parameters for the carrier ensemble.

The second way of calculating device characteristics using a semiclassical model is to solve the BTE that includes scattering details at the microscopic level and field-propelled drift of a particle with an effective mass  $m^*$  at the macroscopic level. One common practice is to solve for the space, time and momentum distributions. This forms a seven dimensional problem: 3 in space, 3 in momentum and 1 in time. It is a challenging problem that puts too much burden on the CPU. However, the total number of dimensions can be reduced using spherical harmonic basis functions [40]. This would make the problem more manageable for the CPU,

by putting some of the analytical burden on the programmer's side.

Semiclassical models include more physical details than classical models. They involve fewer approximations and more elemental properties. Thus, one can simulate devices with different geometries without the need to have fitting parameters. In addition, semiclassical models can provide energy distribution resolving phenomena such hot-electron effects.

One important deficiency of the BTE model is that the carriers are treated as particles; therefore, they obey classical or Newtonian mechanics. However, the particle approach can not resolve transport in ultra-small devices, and quantization in the MOSFET channel near the silicon/silicon dioxide (Si-SiO<sub>2</sub>) interface, where a potential well depending on bias conditions may form. This is related to the failure of the particle approach in the characterization of phenomena such as quantization and tunneling. To resolve these effects, a quantum model needs to be employed. One common practice is to solve the single-particle Schröndinger equation. Using a general form, the time-independent Schröndinger equation can be written as follows:

$$-\frac{\hbar^2}{2m_o}\nabla_r^2\psi + \left[E_C(r) + U_C(r) + U_S(r)\right]\psi = \varepsilon\psi$$

(1.24)

Above,  $\psi$  is the wave function, from which the probability of finding an electron in a volume  $(V = r^3)$  can be determined using the definite integral  $\int_V \psi^*(r) \psi(r) dr^3$ . The actual form of  $\psi$  depends on the slowly varying potential  $E_C(r)$  due to applied field and built-in potentials, quickly varying  $U_C(r)$  due to crystal or lattice potential, and scattering potential  $U_S(r)$  due to phonons (lattice vibrations), ionized impurities, etc. Also,  $\psi$  is the eigenfunction and  $\varepsilon$  is the eigenvalue of Eqn. 1.24.

In traditional device and material analyses, generally the three potential terms on the left-hand-side of Eqn. 1.24 are treated separately, assuming that impurity or defect densities are low compared to the actual material density, lattice vibrations do not significantly alter the relative positions of the neighboring atoms, applied potential varies slowly compared to the crystal potential, etc.

A common practice is first to solve the following equation to obtain energy dispersion curves.

$$\left[ -\frac{\hbar^2}{2m_o} \nabla_r^2 + U_C(r) \right] \psi_1 = \varepsilon_1 \psi_1 \tag{1.25}$$

Crystal potential  $U_C(r)$  has the periodicity of the lattice due to the periodic assembly of the atoms in the material. If the sample is long enough that fringe effects can be ignored, we can assume that the wavefunctions have the same spatial periodicity. This enables us to write eigenfunctions  $(\psi s)$  of Eqn. 1.25 in terms of Bloch waves. A Bloch wave is a product of two terms. The first term is a periodic function that has same periodicity with the underlying structure  $(u_k(\vec{r}) = u_k(\vec{r} + \vec{T}),$  where T is the lattice translational vector in space that is equal to lattice separation), and the second term is a plane wave  $(e^{i\vec{k}\cdot\vec{r}},$  where lattice periodicity dictates  $k = k + \frac{2\pi l}{T}, l = 0, \pm 1, \pm 2...$ ). Mathematically, it is defined as follows:

$$\Psi_k = u_k(r)e^{i\vec{k}\cdot\vec{r}} \tag{1.26}$$

Substituting  $\psi_1 = \sum \Psi_k$  in Eqn. 1.25, and canceling common terms on both sides give:

$$\left[ -\frac{\hbar^2}{2m_o} \left( \nabla_r^2 + 2ik - k^2 \right) + U_C(r) \right] u_k = \varepsilon(k) u_k \tag{1.27}$$

Here, we also dropped the sum written above, because solutions for each k

form a linearly independent set for solutions of the sum. This can be verified by multiplying the original equation by  $e^{-i\vec{k}\cdot\vec{r}}$ , and integrating it over k. Additionally, we can solve for the eigenenergies  $\varepsilon(k)$  for a given k, since we know the terms in brackets on the left-hand-side of Eqn. 1.27. Tracing over k values and finding the associated allowable energies give the energy dispersion curves including conduction and valence bands for that material. Using these dispersion curves, we can extract pertinent parameters to be used in transport calculations such as effective mass  $m^*$  and bandgap  $\varepsilon_q$ .

Next, we add the scattering potential related details in addition to crystal potential related dynamics to our quantum system by solving:

$$\left[ -\frac{\hbar^2}{2m^*} \nabla_r^2 + U_S(r) \right] \psi_2 = \varepsilon_2 \psi_2 \tag{1.28}$$

Generally, the scattering potential is time-dependent; therefore, it is more appropriate to write the above equation as follows:

$$\left[ -\frac{\hbar^2}{2m^*} \nabla_r^2 + U_S(r, t) \right] \psi_2 = i\hbar \frac{\partial \psi_2}{\partial t}$$

(1.29)

Equation 1.29 includes perturbations to the crystal potential. Assuming that these perturbations are small, we can use perturbation theory to calculate scattering rates. This leads to the basic result of scattering theory that is also known as Fermi's Golden Rule, which defines scattering rate from momentum k to k' as written below:

$$S(k,k') = \frac{2\pi}{\hbar} |H_{k'k}^a| \delta(E(k) + \hbar\omega - E(k')) + \frac{2\pi}{\hbar} |H_{k'k}^e| \delta(E(k) - \hbar\omega - E(k')) \quad (1.30)$$

Here,  $H_{k'k}^{a,e}$  is the time-independent scattering potential matrix element between states k and k'. In addition, we have conservation of energy as explicitly

written in the arguments of the Dirac- $\delta$  functions for phonon absorption (<sup>a</sup>) and emission (<sup>e</sup>). Moreover, we also have conservation of momentum that is not explicitly shown above.

To find scattering rates from k to k', we first need to determine matrix elements either in exact form or in approximate form using the deformation potential approximation [42]. Second, we need to obtain phonon dispersion curves to calculate phonon energy  $\hbar\omega$  and momentum q. This can be done in various ways including the tight binding approximation [16]. Once we calculate scattering rates, we can use Monte Carlo simulations to extract parameters such as drift velocity and mobility to be used in device simulators.

Lastly, to complete the full quantum treatment, we resolve the contribution from the last potential term in Eqn. 1.24, which is the combined term for applied and built-in potentials.

$$\left[ -\frac{\hbar^2}{2m^*} \nabla_r^2 + E_C(r) \right] \psi_3 = \varepsilon_3 \psi_3 \tag{1.31}$$

From the dispersion curves (solution of Eqn. 1.25), we obtain the effective mass  $m^*$ . Next, using the scattering rate data, we obtain transport details that can be used in balance equations. (For ballistic transport, the scattering potential is approximately zero resulting in undisturbed flight between two device terminals.) Now, we include the last quantum effect that provides the link between quantum potential and transport. Here,  $E_C(r)$  accounts for the externally applied field, and the built-in fields due to doping, difference in workfunctions and bandgaps, etc. The details of solving this equation in conjunction with scattering data will be given later

in the following chapters.

So far, we have discussed three main physical device models: Classical, semiclassical and quantum. We here make use of modified drift-diffusion equations that combine details from the classical and quantum models, and a Monte Carlo scheme using the semiclassical model. More specifically, we solve the modified drift-diffusion equations to obtain comparative device performance figures. Our modifications are for resolving quantum, heterostructure and thermal effects. To resolve these effects using the drift-diffusion model, we develop methodologies. In the following chapters, we explain how we incorporate those effects in detail. Furthermore, to obtain electrical characteristics of CNTs, we make use of a semiclassical model, which is a Monte Carlo simulator.

#### 1.3 Carbon Nanotube Devices

As we approach the end of the semiconductor roadmap, investigators are exploring new paradigms for electronic devices. Carbon nanotubes (CNTs) are being explored as a structure that may play a leading role in future electronic systems [12]-[15] due to their favorable electrical characteristics and angstrom scale dimensions. Therefore, we develop methodologies to obtain their electrical properties and possible relative gains associated with their use in devices.

To investigate CNT electronics, we first determine CNT electrical characteristics. Since, there has not been enough research done on CNT electrical properties, we start from low level physics, and extract pertinent CNT electrical characteristics. Low-level CNT modeling requires solution of the single-particle Schröndinger equation. Therefore, we first determine the energy dispersion curves using details of its crystal structure. Noting that CNTs are graphite sheets (graphene) rolled into tubes, we use well-known details of the graphene band structure with modifications. Mainly, the modifications take into consideration that CNTs exhibit folding effects, which lead to bound states around the circumference. Details of these states are determined by the diameter of the tube and the wrapping angle using the zone-folding method. Moreover, restrictions due to finite lengths of the tubes are also considered for some applications. In summary, instead of solving for the CNT band diagram from scratch, well-known details of the graphene band structure are used to approximate energy-momentum curves of CNTs. Likewise, the phonon dispersion curves of CNTs are determined from those of graphene.

Next, our quantum modeling includes extraction of macroscopic electrical properties that are relevant for device performance calculations such as drift velocity and mobility. This requires resolving scattering effects on CNT electron transport using Monte Carlo (MC) simulations. In these MC simulations, scattering rate calculations are facilitated using the deformation potential approximation.

Essentially, MC simulators use numerical techniques that rely on a theorem called the weak law of large numbers [43]. According to this theorem, the average values associated with independent and identically distributed random sequences will converge to constant values as the size of the sequence, or the number of samples, go to infinity. In practical terms, average values of independent and identically distributed random sequences can be obtained if a large sequence of the correspond-

ing event is simulated, or recorded experimentally.

Once low-level effects are resolved, we obtain electrical CNT performance details, and do comparative device analyses of various CNT-embedded and traditional devices. We will give details of the underlying physics and employed modeling techniques in the following chapters.

### 1.4 Integrated Circuit Modeling

As industry reduces the size of devices further to increase speed and functionality of Integrated Circuits (ICs), two main challenges in IC operation have emerged: self-heating effects [1]-[11], and interconnect and input/output (I/O) delays. Here, we concentrate on the self-heating effects. (The I/O delays can partially be reduced using three-dimensional ICs or Systems-on-Chips (SoC). However, this further exacerbates the self-heating problem.)

To characterize ICs, we start from individual devices that together form the IC. This first requires the characterization of device performances, and next the resolution of their effects on the overall IC performance. Considering device and IC levels, we develop methodologies to find thermal maps of planar and three-dimensional ICs at the resolution of a single device. Resolving IC thermal effects at the device level has been done for the first time by us. Previously, it had been done using several thermal nodes and not self-consistently for the entire IC, instead for hundreds of million nodes like we do. Also, we self-consistently resolve IC self-heating effects in conjunction with device operation, IC applications and layout

details for the first time.

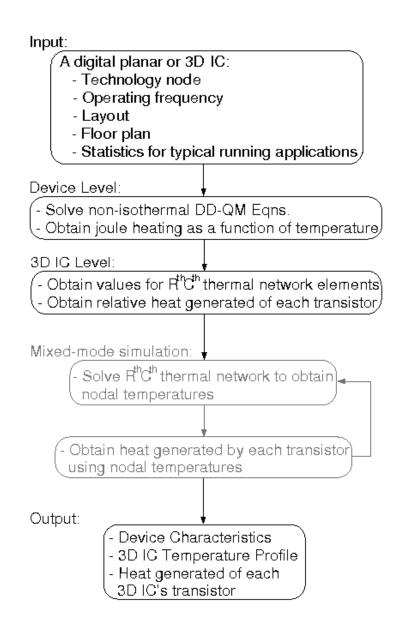

We first obtain device performance details for a representative device utilized for the given technology. Once we determine device performance as a function of temperature, we go to the IC level, which has dimensions millions of times bigger than those of a single device. To facilitate quick computation of the IC temperature map, we develop lumped thermal models for the whole chip. This gives a resistivecapacitive thermal network with nodes that correspond to individual devices. Also, thermal resistances and capacitances between each device is determined by the chip layout. Then, we extend the device performance details calculated for a single device to the entire chip volume using IC-wide operation details such as clock frequency, and software application details such as how frequently accesses are granted for the cache, how often arithmetic manipulations are executed at the arithmetic logic unit, etc. We do this using a Monte Carlo type methodology that determines relative power density for each device on the IC. Lastly, we iterate between the IC and the device levels until we obtain the IC thermal map. We explain the coupled algorithm in detail in the following chapters.

#### 1.5 Thesis Overview

In the following chapter, we explain our modified drift-diffusion models. We show the methodologies we developed to resolve quantum, heterostructure and self-heating effects within the drift-diffusion model that includes the Poisson, and the electron and hole current continuity equations. We first describe the drift-diffusion

equations and the auxiliary parameters such as mobilities and current densities used in conjunction with the state variables; electrostatic potential, and electron and hole concentrations. Next, we briefly talk about the discretization method we employ. This is followed by a derivation of the methodology that shows how we incorporate the aforementioned effects. Specifically, we start from the fundamental electron current density equation, and write electron concentration in terms of the electrostatic potential and the electron Fermi potential. Next, we transform this expression in such a way that the aforementioned effects can be resolved within our discretization scheme using space dependent effective potential terms in addition to the electrostatic potential we calculate. Details concerning the derivation and utilization of the modified equations to obtain device performance details will be explained later.

In Chapter 3, we develop methodologies to obtain CNT electrical properties including mobility and intrinsic carrier concentration. To obtain an expression for the mobility, we first calculate the CNT energy dispersion curve from that of graphene using zone-folding effects. Next, we import these energy dispersion curves to the Monte Carlo (MC) simulator we developed. Briefly, we explain how we determine scattering rates and CNT electron transport. Also, we include length effects on electron transport by modifying the energy dispersion curves. Next, using our MC simulations, we obtain drift-velocity versus field curves. In addition, we report position-dependent velocity oscillations and length effects in semiconducting single-walled zig-zag carbon nanotubes for the first time. Our calculated results indicate velocity oscillations with Terahertz frequencies approaching phonon fre-

quencies. This may facilitate new high frequency RF device and circuit designs, opening new paradigms in communication networks. Furthermore, to obtain comparative device performance figures between traditional devices and the ones that embed CNTs in their channels, we extract pertinent CNT electrical parameters such as intrinsic carrier concentrations and electron affinities to be used in our semiconductor equations.