#### **ABSTRACT**

Title Of Dissertation: UNDERSTANDING AND OPTIMIZING

HIGH-SPEED SERIAL MEMORY SYSTEM ARCHITECTURES

Brinda Ganesh, Doctor of Philosophy, 2007

Dissertation Directed by: Professor Bruce Jacob

Department of Electrical and Computer Engineering

Performance improvements in memory systems have traditionally been obtained by scaling data bus width and speed. Maintaining this trend while continuing to satisfy memory capacity demands of server systems is challenging due to the electrical constraints posed by high-speed parallel buses. To satisfy the dual needs of memory bandwidth and memory system capacity, new memory system protocols have been proposed by the leaders in the memory system industry. These protocols replace the conventional memory bus interface between the memory controller and the memory modules with narrow, high-speed, uni-directional point-to point interfaces. The memory controller communicates with the memory modules using a packet-based protocol, which is translated to the conventional DRAM commands at the memory modules.

Memory latency has been widely accepted as one of the key performance bottlenecks in computer architecture. Hence, any changes to memory sub-system architecture and protocol can have a significant impact on overall system performance. In the first part of this dissertation, we did an extensive study and analysis of how the behavior of newly proposed memory architecture to identify clearly how it impacts memory sub-system performance and what the key performance limiters are. We then went on to use the insights we gained from this analysis to propose two optimization techniques focussed on improving the performance of the memory system.

We first evaluated the performance of the current *de facto* serial memory system standard, FBDIMM (Fully Buffered DIMM) with respect to the conventional wide-bus architectures that have been in use for decades. We found that the relative performance of a FBDIMM system with respect to a conventional DDRx system was a strong function of the bandwidth utilization, with FBDIMM systems doing worse in low utilization systems and often out-performing DDRx systems at higher system utilizations. More interestingly, we found that many of the memory controller policies that have been in use in DDRx systems performed similarly on a FBDIMM system.

Memory latency typically has a significant impact on overall system performance. FBDIMM systems, by using daisy chaining and serialization, increase the default latency cost of a memory transaction. In a longer memory channel, i.e. a channel with 8 DIMMs of memory, inefficient link utilization and memory controller scheduling policies can contribute to a further reduction in system performance. We propose two main optimization techniques to tackle these inefficiencies reordering data on the return link and buffering at the memory module. Both these policies lower read latency by 10-20% and improve application performance by 2-25%.

# UNDERSTANDING AND OPTIMIZING HIGH-SPEED SERIAL MEMORY SYSTEM PROTOCOLS

by

#### Brinda Ganesh

Thesis submitted to the Faculty of the Graduate School of the

University of Maryland, College Park in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

2007

Advisory Committee:

Professor Bruce Jacob, Chair Professor Shuvra Bhattacharyya Dr. Xiaowei Shen Professor Ankur Srivastava Professor Lawrence Washington Professor Donald Yeung

To

Ankush, Mummy and Daddy

You are simply the best!!

#### **ACKNOWLEDGEMENTS**

This thesis would not have been possible if it were not for a number of people with whom I have shared this journey through graduate school. First of all, I would like to thank my wonderful husband, Ankush who has been on my side the entire way. He has made me laugh, proof read my papers so many times that he knows the details of my own research more than me, accompanied on numerous hikes and bike rides and most importantly believed in me throughout.

Most importantly, I would like to thank my wonderful family who have been patient, supportive and very understanding through my years in graduate school. My parents have been one of my biggest cheerleaders, while I went through the ups and downs of graduate school. I would also like to thank my aunt, Kalpanachikkamma and my grandmother, Ammamma who have given me a home to go to in the United States. I have, thanks to both their efforts, not ever felt alone in this country or far from my family.

My advisor, Dr. Bruce Jacob, has provided me invaluable guidance and advice through all my years in graduate school. He has taught me much of what I know about how to do research, how to write papers and how to give presentations. I would really like to thank him for his patience and support, while I took my time finding my way out of graduate school.

My mentor at IBM, Xiaowei Shen, has been one of the best mentors anybody could ask for. Xiaowei is an insightful researcher, a great mentor and wonderful person to work with. Xiaowei has been largely instrumental in me getting sufficient momentum to get done with the final disseratation. While at IBM, I also had the pleasure of working with Jessica Tseng, who was always ready to discuss everything from issue queue architectures to what to do in New York City. Thanks Jessica for my fun time at Watson and for opening my mind about how to approach problems!! Thanks also to Dustin Vanstee, with whom I had very interesting discussions on memory protocol choices.

Thanks to my committee members, Dr. Donald Yeung, Dr. Shuvra Bhattacharyya, Dr. Ankur Srivastava and Dr. Lawrence Washington, for their feedback and many suggestions which have been invaluable.

Many thanks to Wanli who helped me with porting DRAMsim to M5 and answered all my ridiculous questions cheerfully. Thanks also to Men-ju Wu for his help with getting checkpoints to work and Jayanth Gummaraju for providing me his DRAMsim port to the M5 simulator.

While at Maryland, I got to work with many wonderful folk who made my days in the SCA Lab a fun experience. Aamer Jaleel has always been available to discuss computer architecture, life and to roller blade down Paint branch trail. Thanks Aamer for all the fun times in the good old SCA lab. I am also very grateful to David Wang, who has taught me much of what I know about memory system architectures and has been always willing to explain the same thing to me multiple times. I shall definitely miss Ohm, who was always around to take off to watch cartoon movies with, discuss Korean series and the bug currently irking me. Thanks to Sada for his willingness to discuss any idea of mine no matter how half-baked. I also had a lot of fun in the lab thanks to many folks, in no particular order, Anasua, Iyerb, Sumesh, Surupa, Rania, Xuanhua, Choi, Lei, Mainak,Mike and Hima.

Ayan and Ayush, with whom I have shared the Ph.D. journey have always been willing to provide me with a cup of coffee, listen to my troubles and help me out. Thanks to Ayush for constantly challenging my boundaries with arguments and discussions about fair-trade coffee, free speech and workers rights and to Ayan who tolerated these heated discussions and on other occasions added fuel to the fire. Avanti has been a wonderful room-mate and friend. I will always cherish the times we spent laughing our daily troubles off, staying up well past our bed-time watching Jay Leno and for having, at least temporarily, helped me maintain a squeaky clean house. Thanks also to Andre, Gelareh, Anubha, Anu, Soumya, Jo for fun-times at Maryland.

# **Table Of Contents**

| Chapter 1: Introduction                                           | 1   |

|-------------------------------------------------------------------|-----|

| Chapter 2: Related Work                                           | 8   |

| 2.1. Performance Optimizations for the Memory Sub-System          | 8   |

| 2.2. Power Management                                             |     |

| 2.3. Commercial Memory Controllers                                |     |

| 2.4. Processor-in-Memory Architectures                            |     |

| 2.5. Split-Transaction Buses                                      | 19  |

| Chapter 3: Background                                             |     |

| 3.1. Memory Request Overview                                      |     |

| 3.2. DRAM Architectures over time                                 |     |

| 3.2.1 Serial Memory Protocols                                     |     |

| 3.3. Memory System Trends                                         |     |

| 3.3.1 Bandwidth                                                   |     |

| 3.3.2 Latency                                                     |     |

| 3.3.3 Capacity                                                    |     |

| 3.4. FBDIMM Overview                                              |     |

| 3.4.1 FBDIMM protocol                                             | 40  |

| Chapter 4: Performance Evaluation                                 |     |

| 4.1. Methodology                                                  |     |

| 4.1.1 Memory Controller Model                                     |     |

| 4.2. FBD vs. DDRx                                                 |     |

| 4.2.1 Application Latency and Bandwidth Characteristics           |     |

| 4.2.2 Latency Contributors                                        |     |

| 4.2.3 Impact of Scheduling Policy                                 | 69  |

| 4.2.4 Impact of Row buffer Management Policy                      |     |

| 4.2.5 Impact of Variable Latency Mode                             | 81  |

| 4.2.6 Impact of posted CAS                                        |     |

| 4.2.7 Southbound link utilization                                 | 89  |

| 4.3. Summary of Results                                           | 92  |

| Chapter 5: Optimizations for Variable Latency Mode                | 96  |

| 5.1. Performance Characteristics of Variable Latency Mode Systems |     |

| 5.1.1 Limit Study                                                 |     |

| 5.1.2 Application Performance Characteristics                     | 107 |

| 5.2. Re-ordering of Data Returns                                  |     |

| 5.2.1 Mechanisms to track North Link Usage                        | 122 |

| 5.2.2 Mechanism to re-order the Response Queue                    | 130 |

| 5.2.3 Re-ordering Data Returns : Limit Study                      | 133 |

| 5.2.4 Re-ordering Data Returns : Application Performance Impact | 138 |

|-----------------------------------------------------------------|-----|

| 5.3. Buffering on the AMB                                       | 154 |

| 5.3.1 Buffering Techniques                                      | 156 |

| 5.3.2 Buffering: Impact on Application Performance              | 164 |

| 5.4. Re-ordering and Buffering                                  | 187 |

| 5.5. Full System Simulation Studies                             | 198 |

| 5.5.1 Methodology                                               | 198 |

| 5.5.2 Results                                                   |     |

| 5.6. Summary                                                    | 205 |

| Chantar C. Canalysiana                                          | 200 |

| Chapter 6: Conclusions                                          | ∠∪8 |

| References                                                      | 213 |

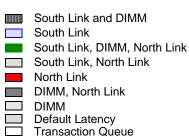

# **List of Figures**

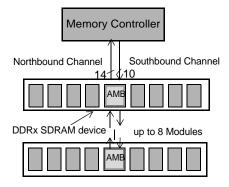

| Figure 1.1.  | FBDIMM Memory System                                                                   | 2    |

|--------------|----------------------------------------------------------------------------------------|------|

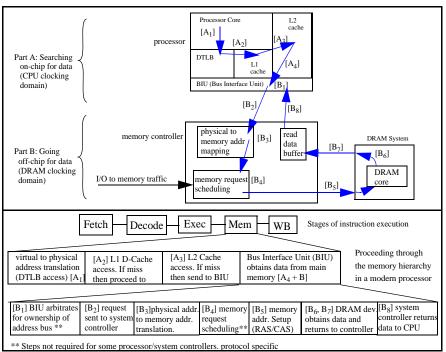

| Figure 3.1.  | Abstract Illustration of Data being obtained from memory for a Load Instruction [10]21 |      |

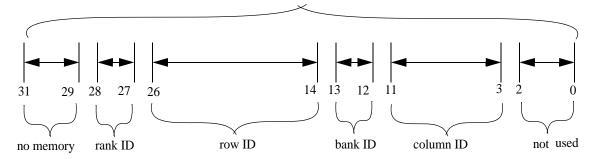

| Figure 3.2.  | Address Mapping                                                                        | . 22 |

| Figure 3.3.  | DRAM Commands associated with a transaction                                            |      |

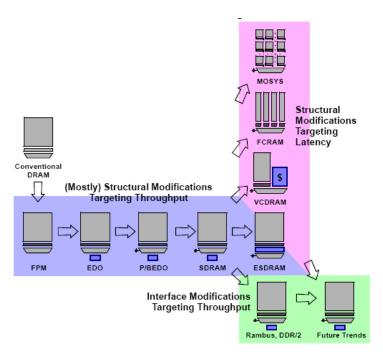

| Figure 3.4.  | Evolution of the DRAM                                                                  | . 26 |

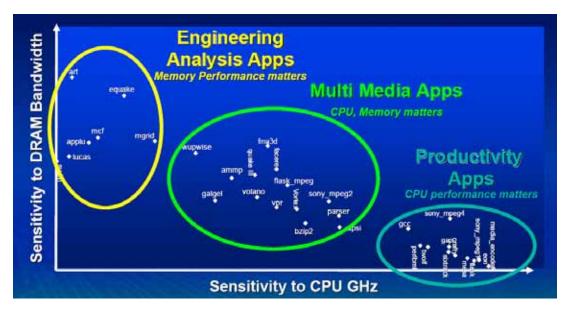

| Figure 3.5.  | Application sensitivity to Bandwidth and CPU frequency                                 | . 32 |

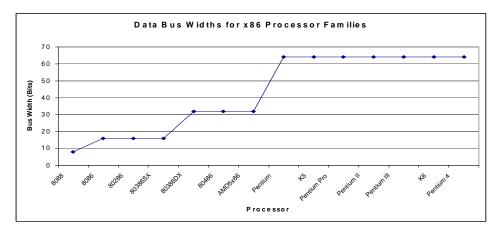

| Figure 3.6.  | Memory Data Bus Widths for Different Processors                                        |      |

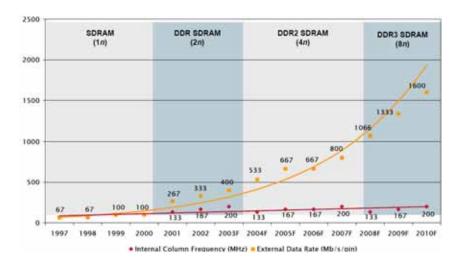

| Figure 3.7.  | DRAM Data Rate Trends                                                                  |      |

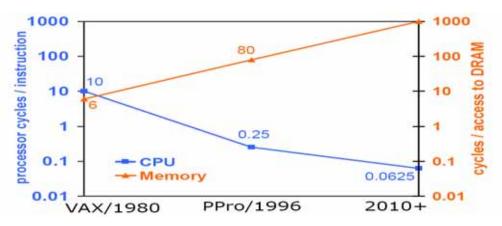

| Figure 3.8.  | Memory/Processor Speed Gap                                                             | . 34 |

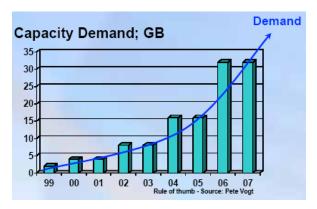

| Figure 3.9.  | Server Capacity Demand                                                                 |      |

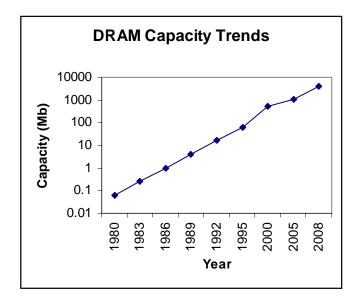

| Figure 3.10. | DRAM Capacity Trends                                                                   |      |

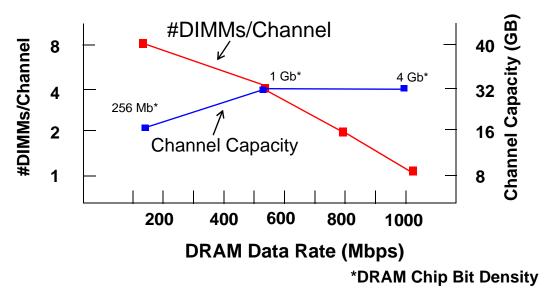

| Figure 3.11. | DIMM Capacity/Channel with increasing data-rates                                       |      |

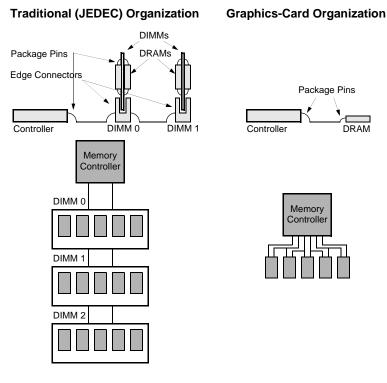

| Figure 3.12. | Motivation for the design of FBDIMM                                                    |      |

| Figure 3.13. | FBDIMM Frames                                                                          |      |

| Figure 3.14. | Read Transaction in FBDIMM system                                                      | . 43 |

| Figure 3.15. | Write Transaction in FBDIMM system                                                     | . 44 |

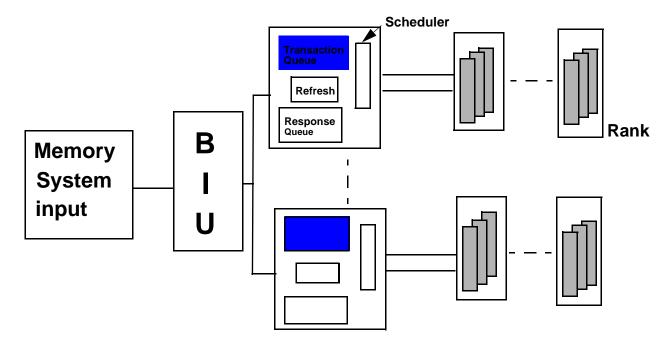

| Figure 4.1.  | Memory Controller Architecture                                                         |      |

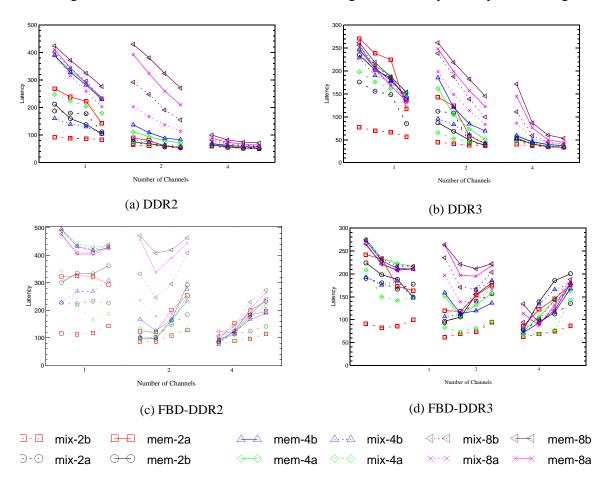

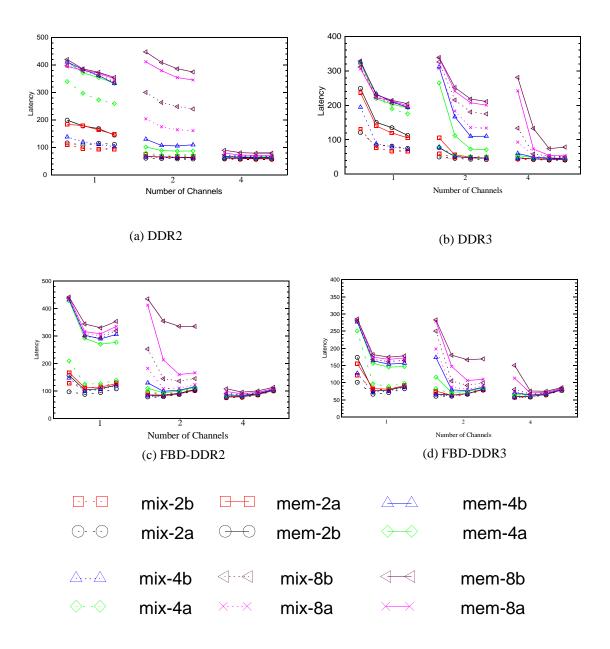

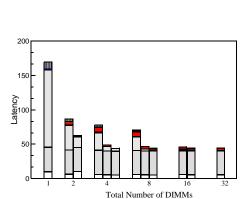

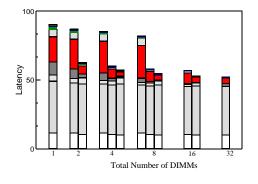

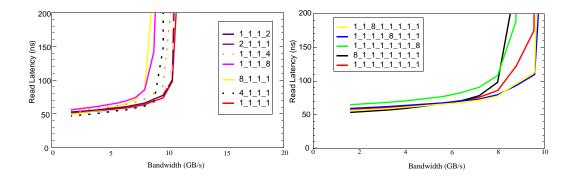

| Figure 4.3.  | Read Latency Characteristics in an Open Page System                                    | . 50 |

| Figure 4.2.  | Read Latency Characteristics in a Closed Page System                                   | . 51 |

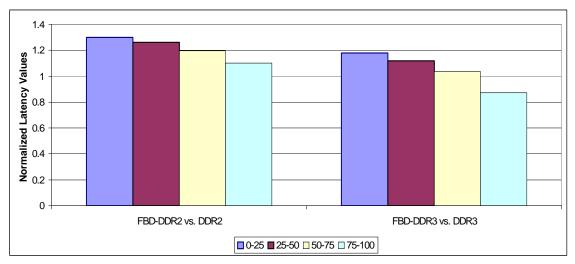

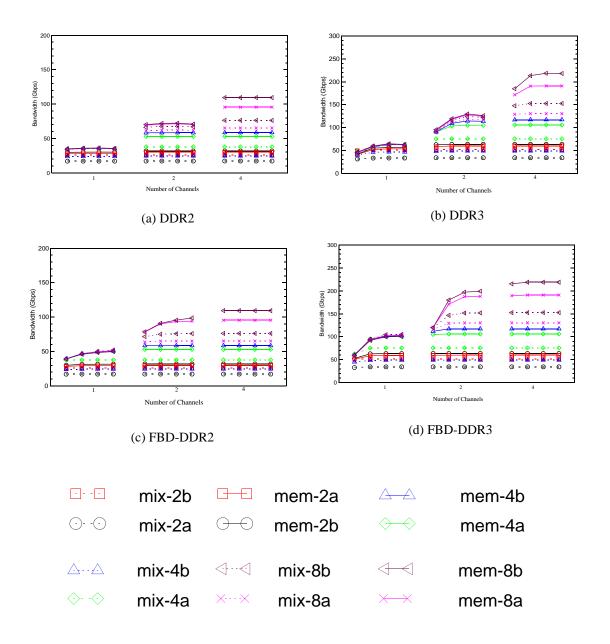

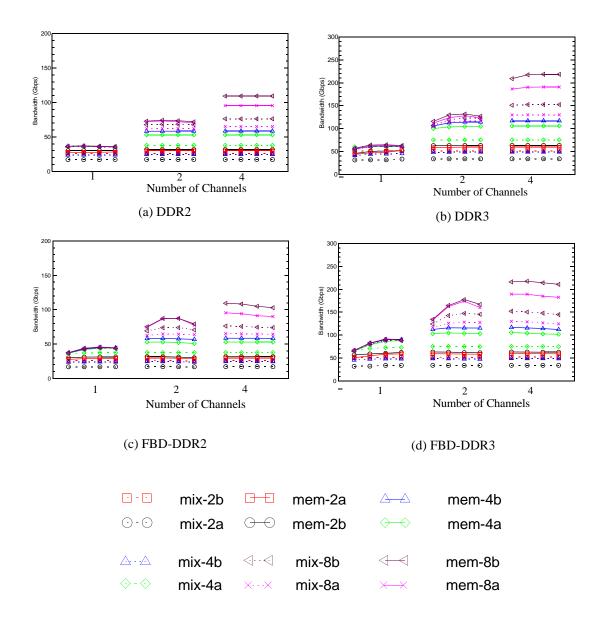

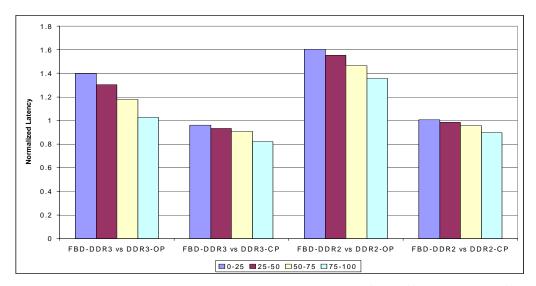

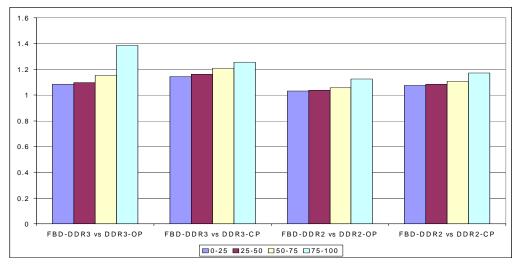

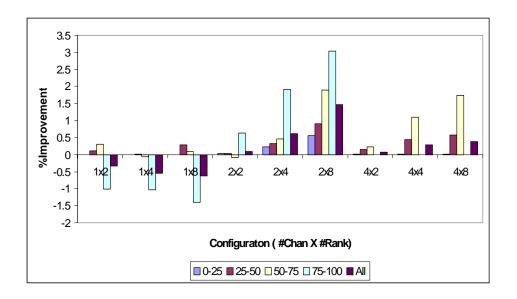

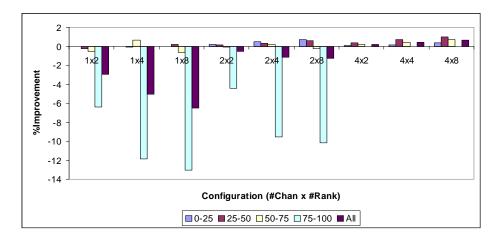

| Figure 4.4.  | FBD vs. DDRx: Latency Improvements as a function of bandwidth utilization53            |      |

| Figure 4.5.  | Sustained Bandwidth Characteristics in a Closed Page System                            | . 55 |

| Figure 4.6.  | Sustained Bandwidth Characteristics in an Open Page System                             | . 56 |

| Figure 4.7.  | FBD vs. DDRx: Bandwidth Improvements as a function of Bandwidth Utilization57          |      |

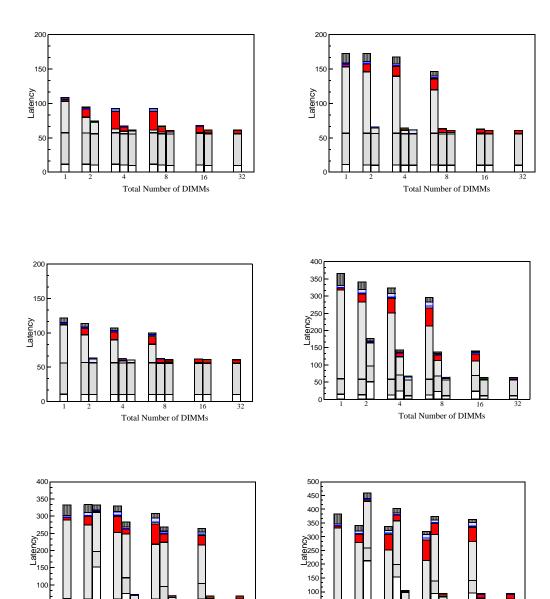

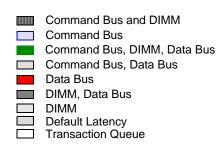

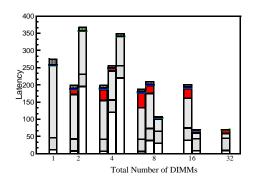

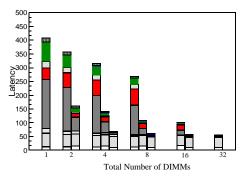

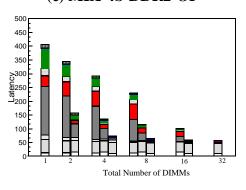

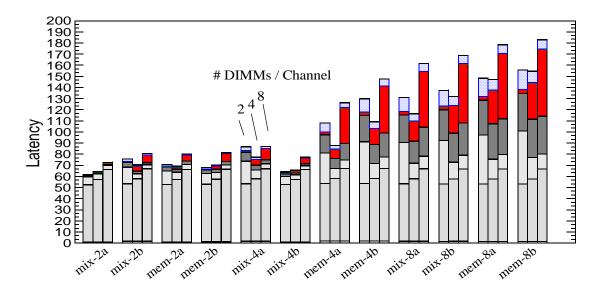

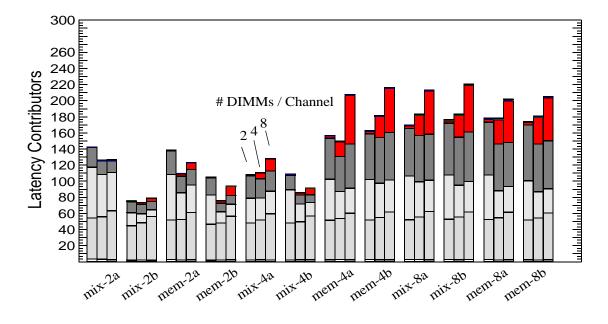

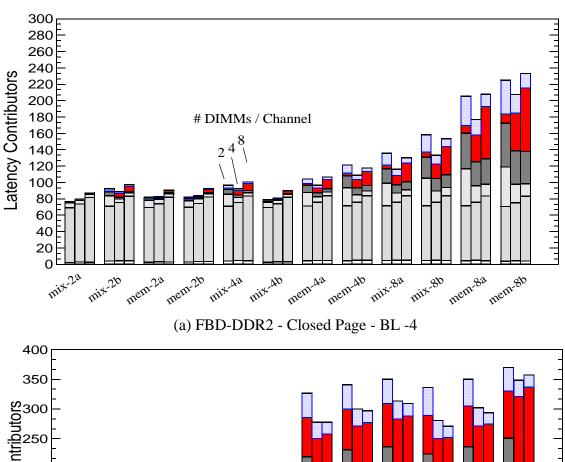

| Figure 4.8.  | Latency Contributors for DDR2 Closed Page Systems                                      | . 59 |

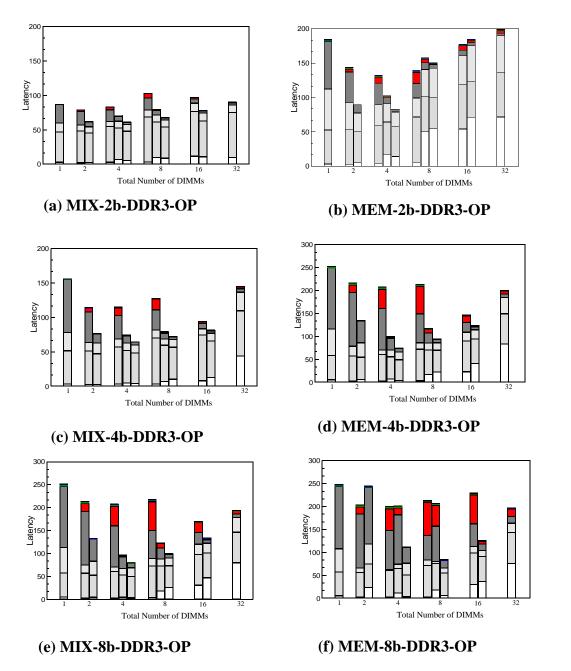

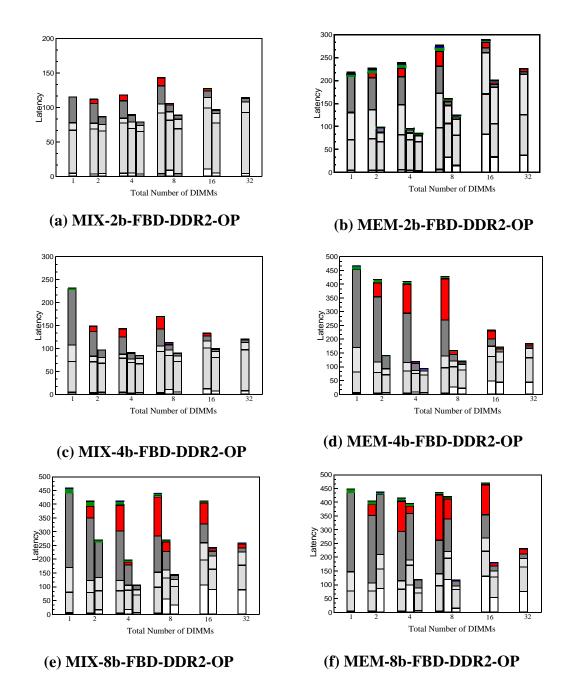

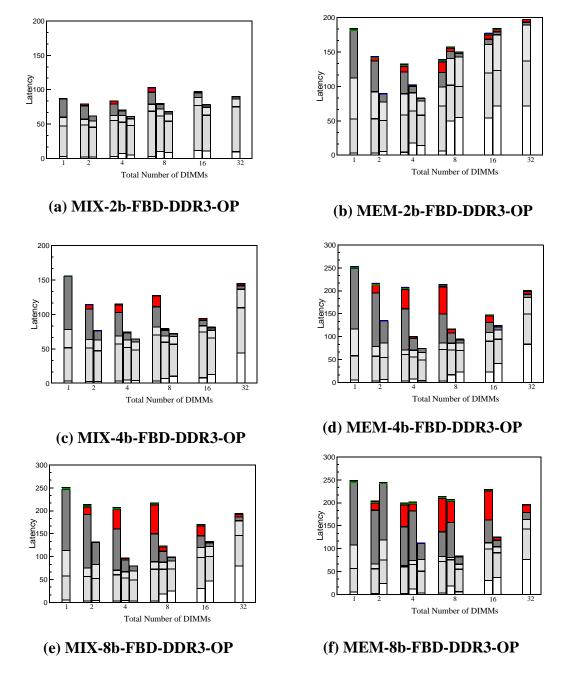

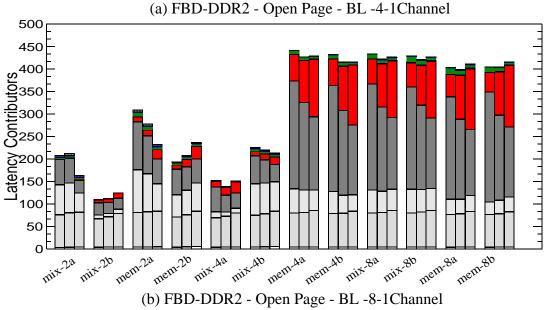

| Figure 4.9.  | Latency Contributors for FBD-DDR2 Closed Page Systems                                  | . 60 |

| Figure 4.10. | Latency Contributors for DDR3 Closed Page Systems                                      | . 61 |

| Figure 4.11. |                                                                                        |      |

| Figure 4.12. | Latency Contributors for DDR2 open page systems                                        | . 63 |

| Figure 4.14. | Latency Contributors for DDR3 open page systems                                        | . 64 |

| Figure 4.13. | Latency Contributors for FBD-DDR2 open page systems                                    | . 65 |

| Figure 4.15. | Latency Contributors for FBD-DDR3 open page systems                                    | . 66 |

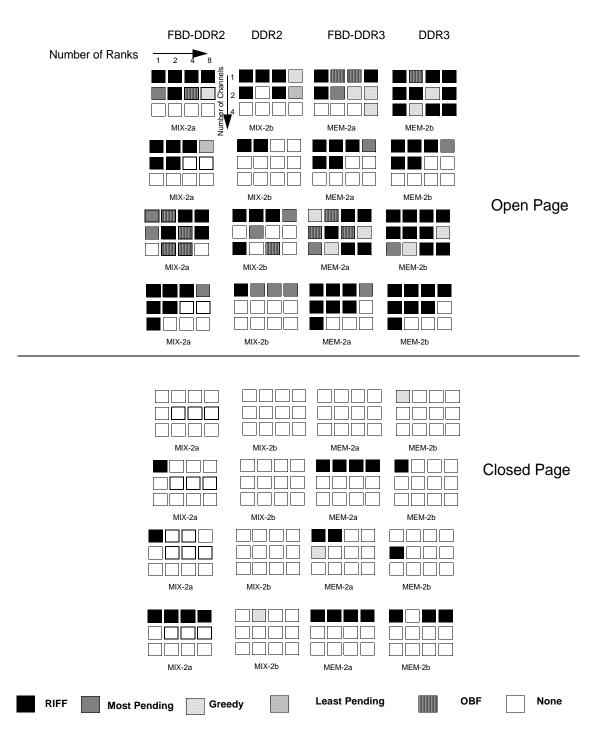

| Figure 4.16. | Best Scheduling Policy for Average Read Latency                                        | . 71 |

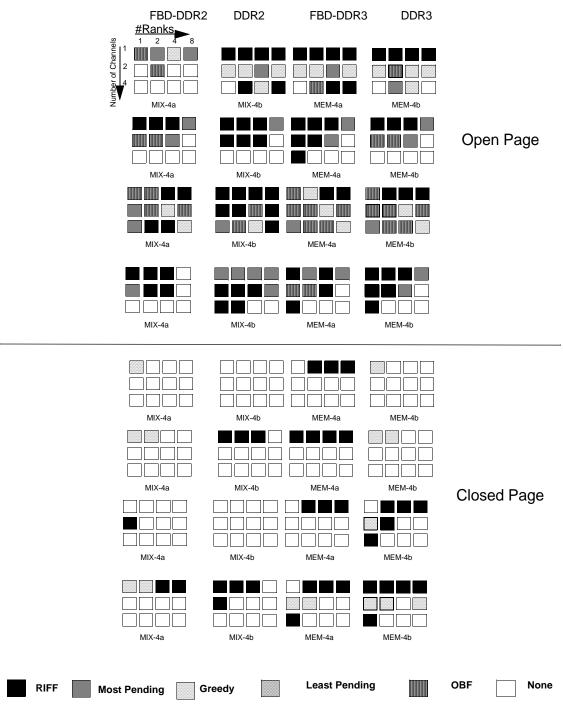

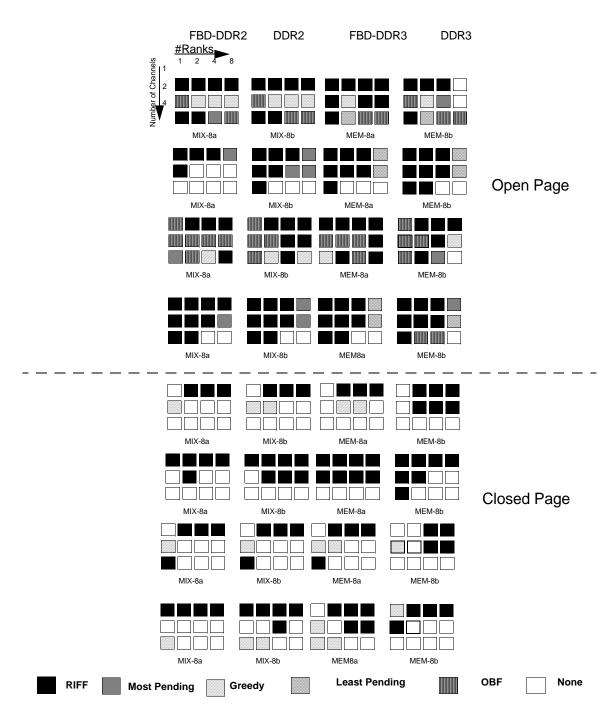

| Figure 4.17. | Best Scheduling Policy for Average Read Latency                                        | . 72 |

| Figure 4.18. | Best Scheduling Policy for Average Read Latency                                        | . 73 |

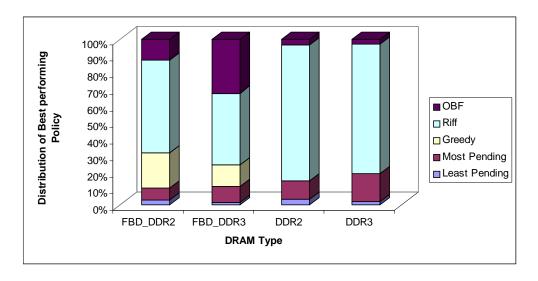

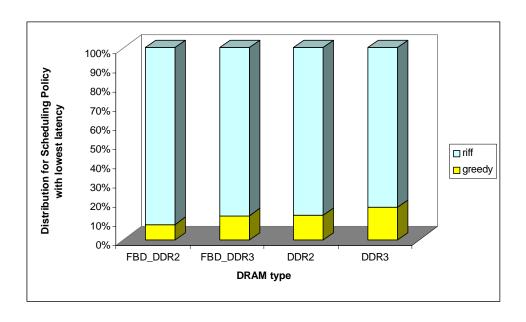

| Figure 4.19. | Histogram of scheduling policy with lowest read latency                                | . 74 |

| Figure 4.23. | FBD vs. DDRx: Latency Improvements for different row buffer management policies75      |      |

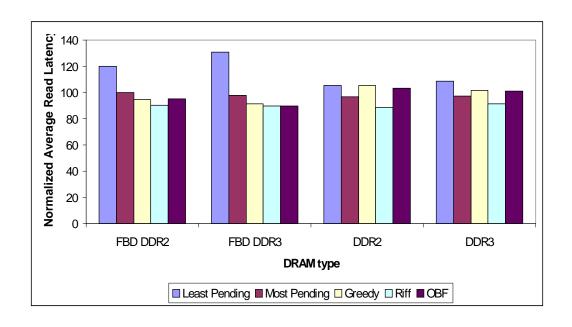

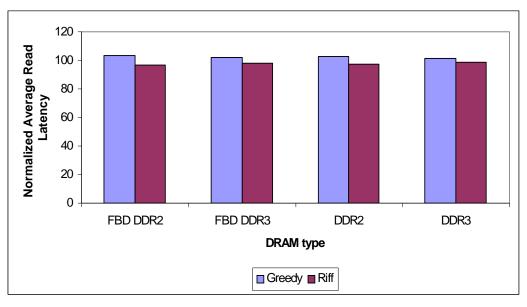

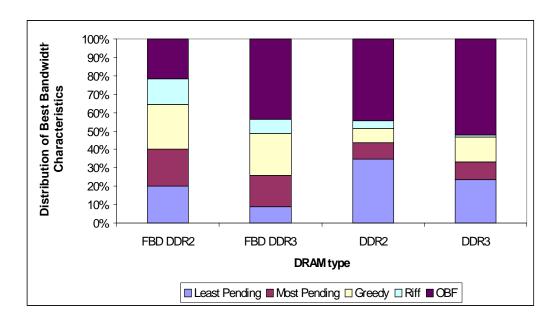

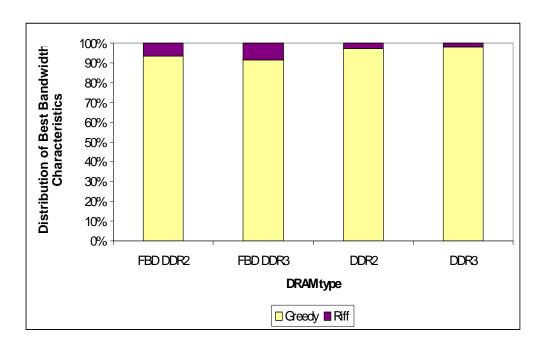

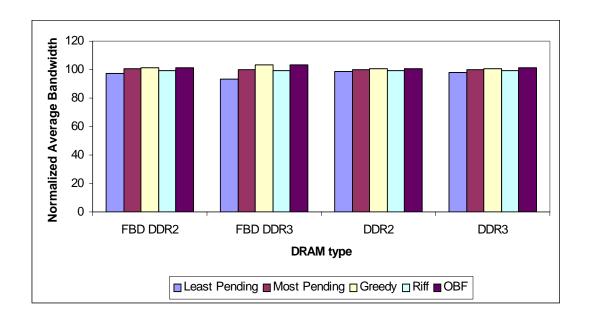

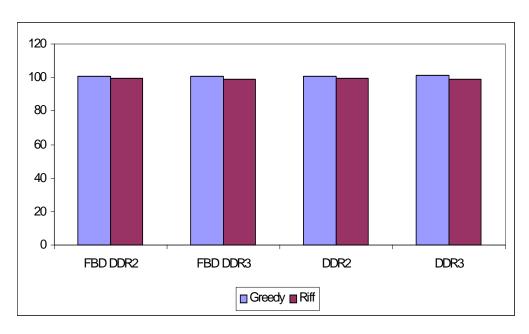

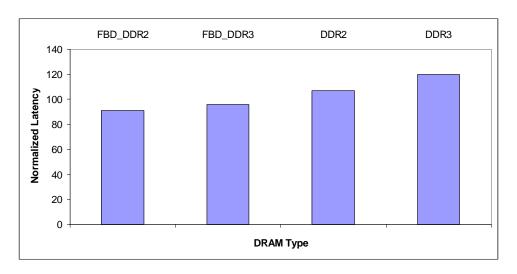

| Figure 4.20. | Normalized Average Read Latency for different DRAM types                                                      |

|--------------|---------------------------------------------------------------------------------------------------------------|

| Figure 4.21. | Distribution of which scheduling policy has best bandwidth characteristics 77                                 |

| Figure 4.22. | Normalized Average Bandwidth for different DRAM types                                                         |

| Figure 4.24. | FBD vs. DDRx: Bandwidth Improvements for different row buffer management policies79                           |

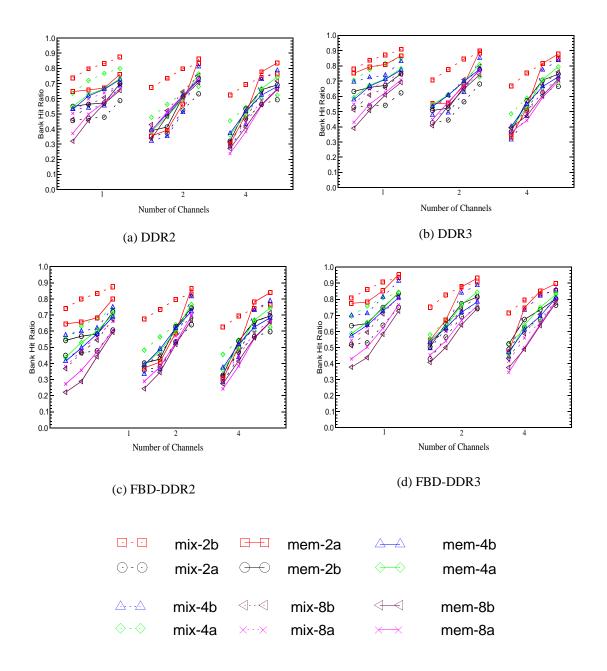

| Figure 4.25. | Average Bank Hit Ratios for various workloads 80                                                              |

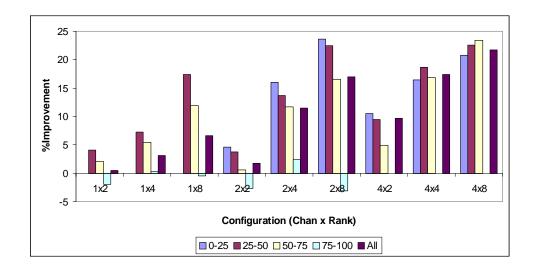

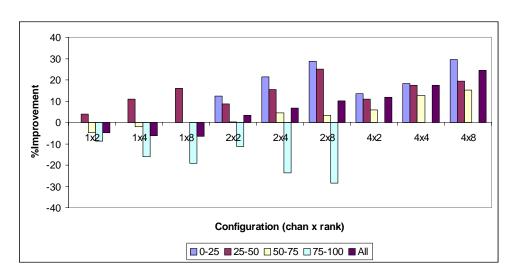

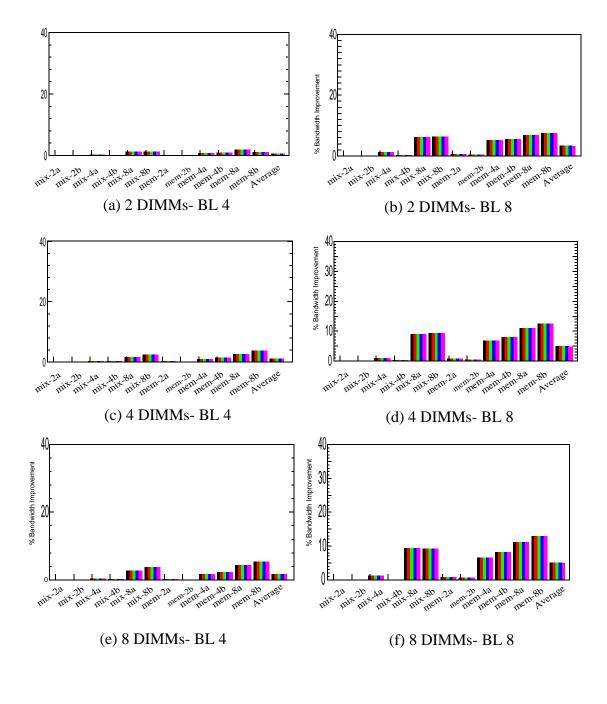

| Figure 4.26. | Improvements in read latency from using Variable Latency Mode 82                                              |

| Figure 4.27. | Improvements in read latency from using Variable Latency Mode as a function of row buffer management policy83 |

| Figure 4.28. | Improvements in bandwidth from using Variable Latency Mode 84                                                 |

| Figure 4.29. | Improvements in read latency from using Variable Latency Mode 86                                              |

| Figure 4.30. | Improvements in bandwidth by using Variable Latency Mode                                                      |

| Figure 4.31. | Latency Improvements by using posted CAS                                                                      |

| Figure 4.32. | Southbound bus utilization                                                                                    |

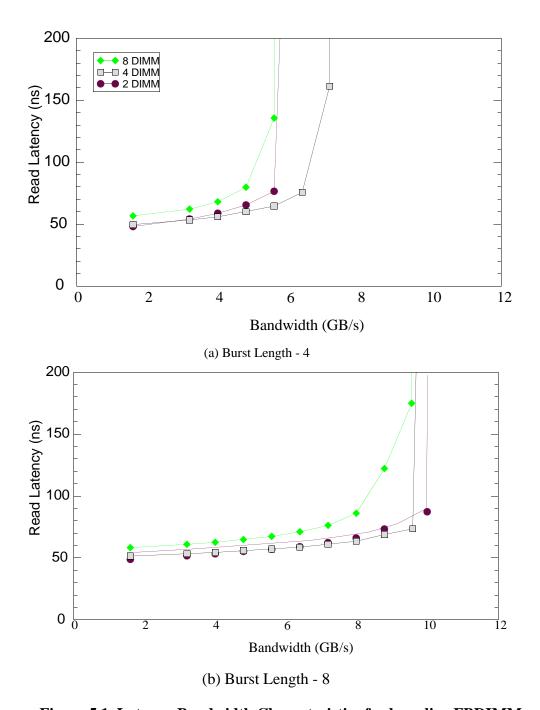

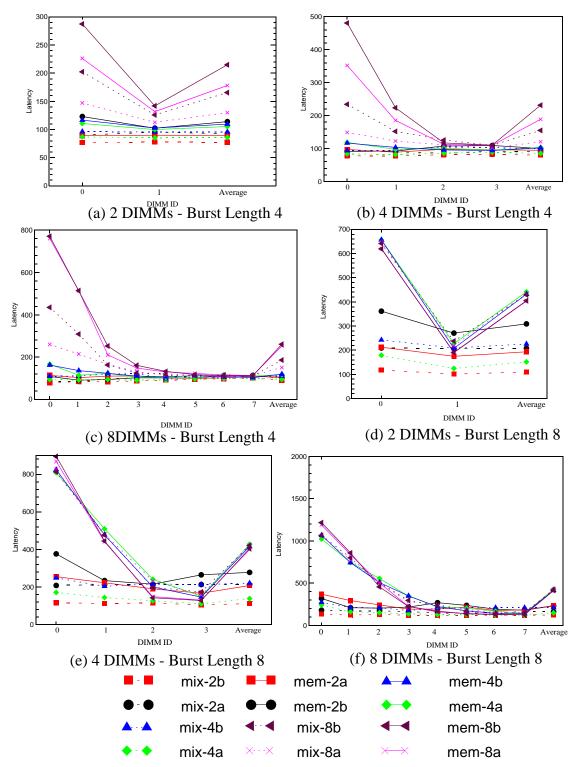

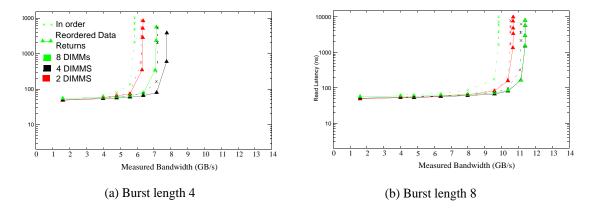

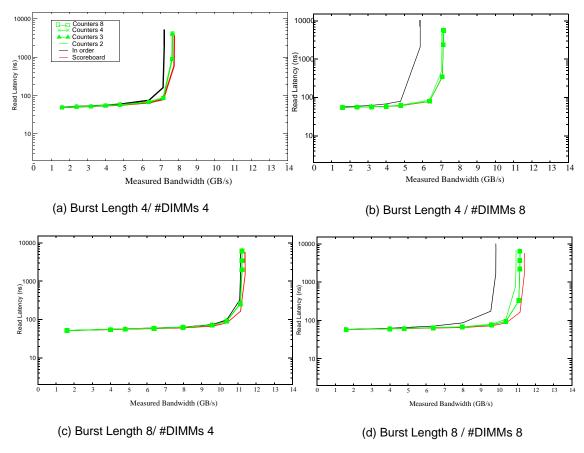

| Figure 5.1.  | Latency-Bandwidth Characteristics for base-line FBDIMM system 99                                              |

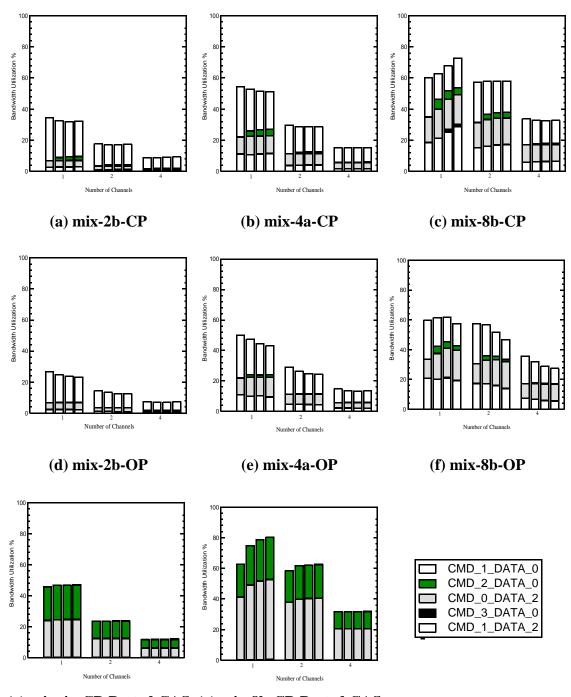

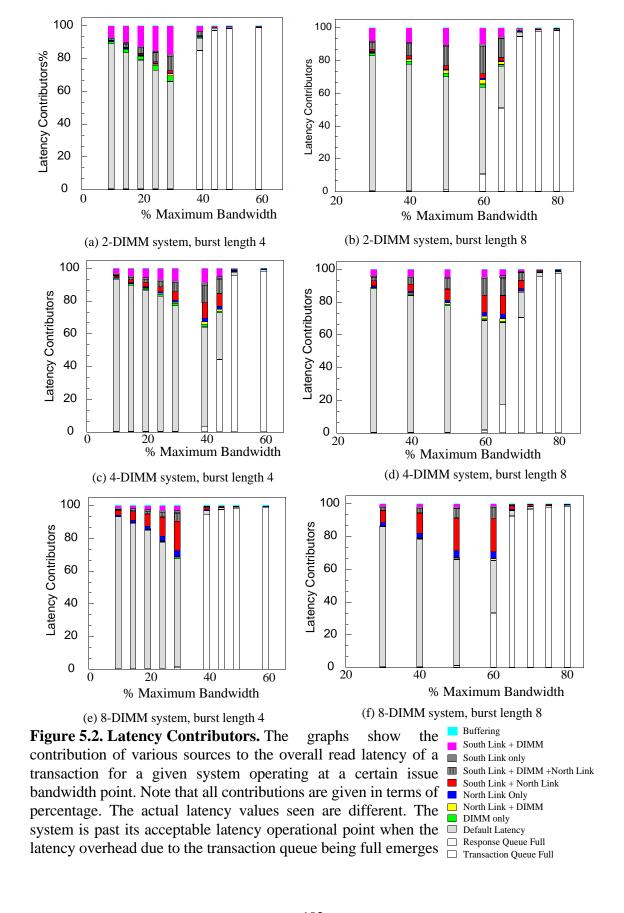

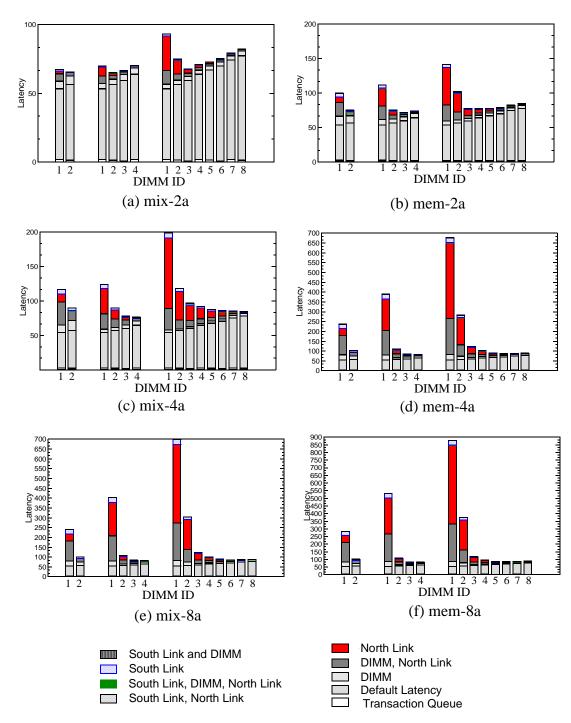

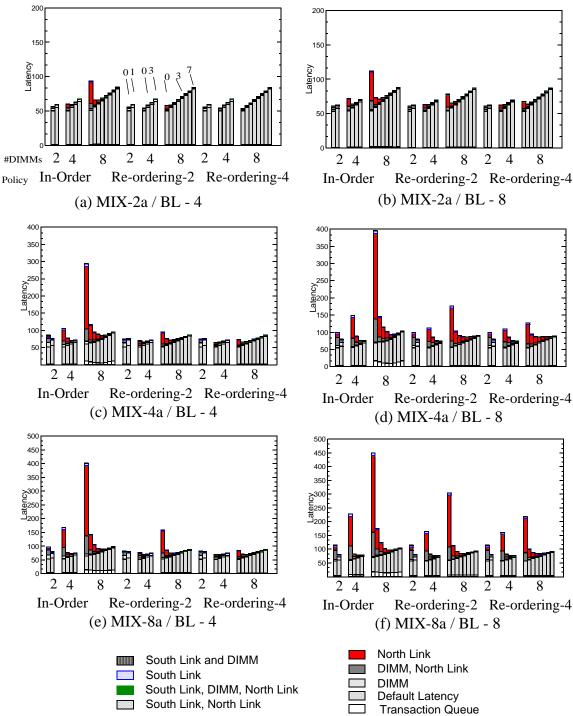

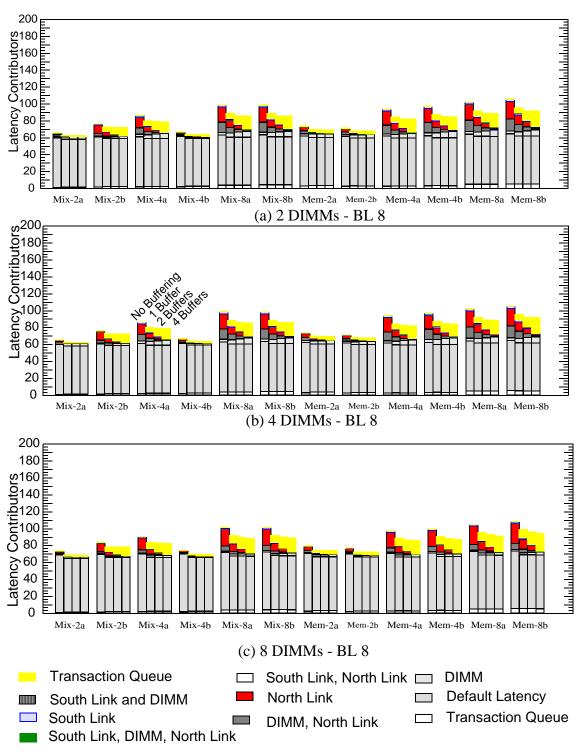

| Figure 5.2.  | Latency Contributors                                                                                          |

| Figure 5.3.  | Impact of hot-spotting on latency-bandwidth                                                                   |

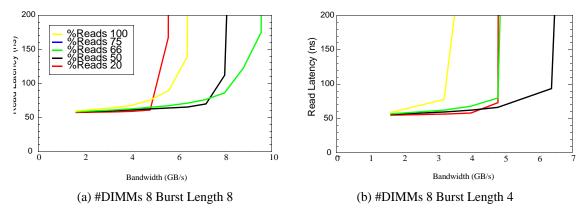

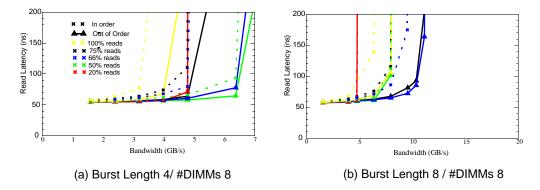

| Figure 5.4.  | Impact of proportion of read-traffic on latency-bandwidth 106                                                 |

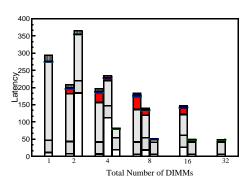

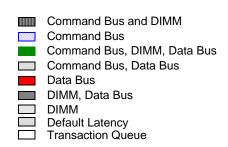

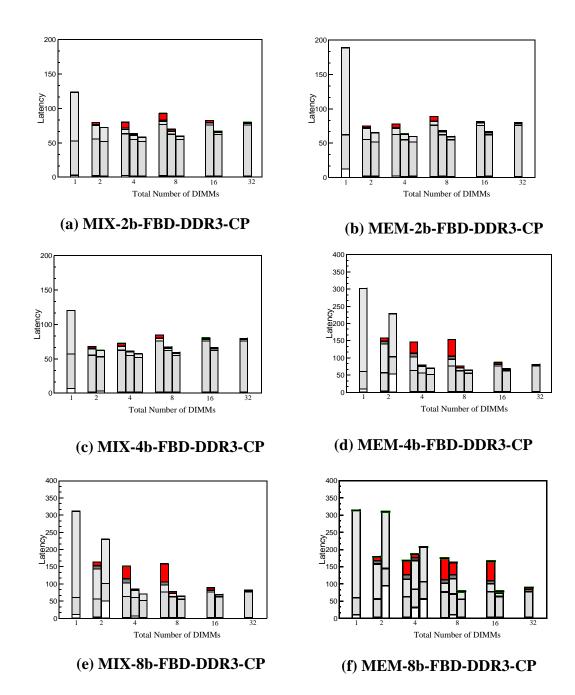

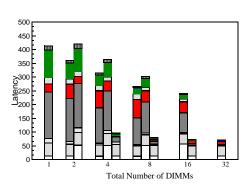

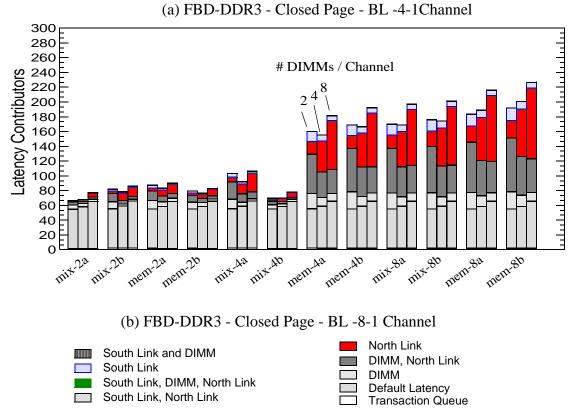

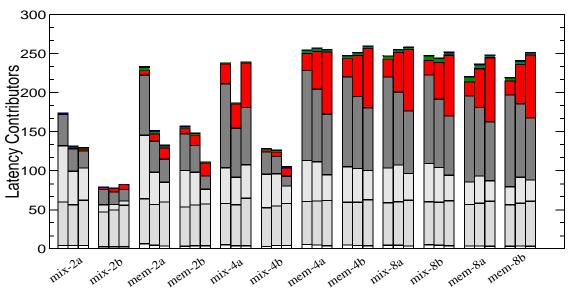

| Figure 5.5.  | Latency contributors in a closed page FBD-DDR3 system 108                                                     |

| Figure 5.6.  | Latency Contributors for Open Page System FBD-DDR3                                                            |

| Figure 5.7.  | Latency Contributors for Open Page Systems                                                                    |

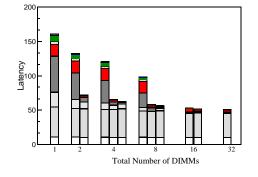

| Figure 5.8.  | Latency Contributors for FBD-DDR2 Closed Page Systems                                                         |

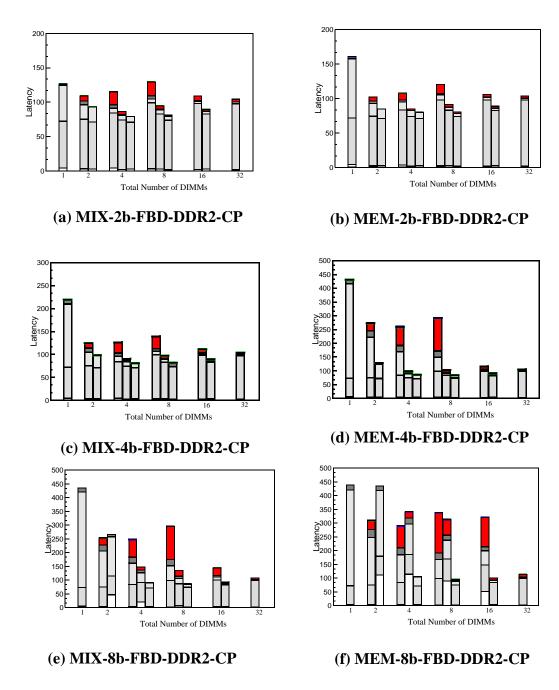

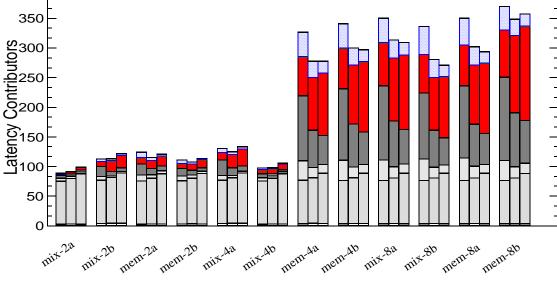

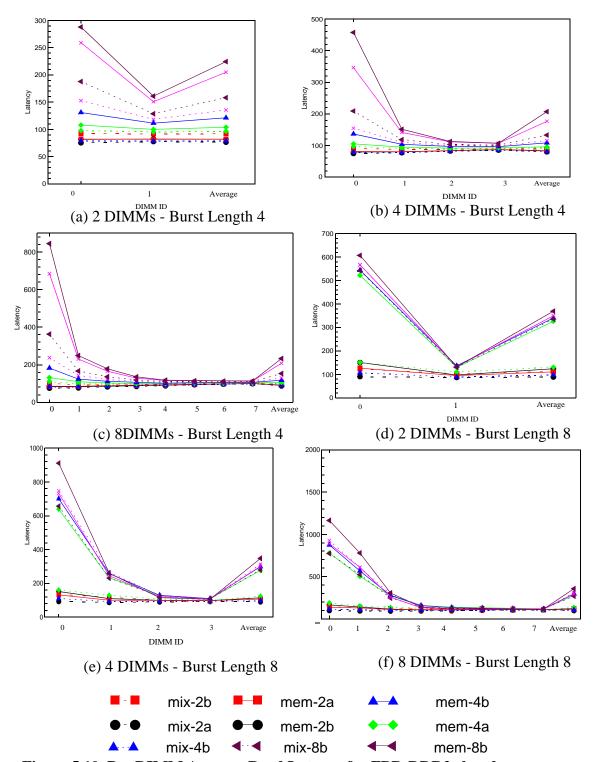

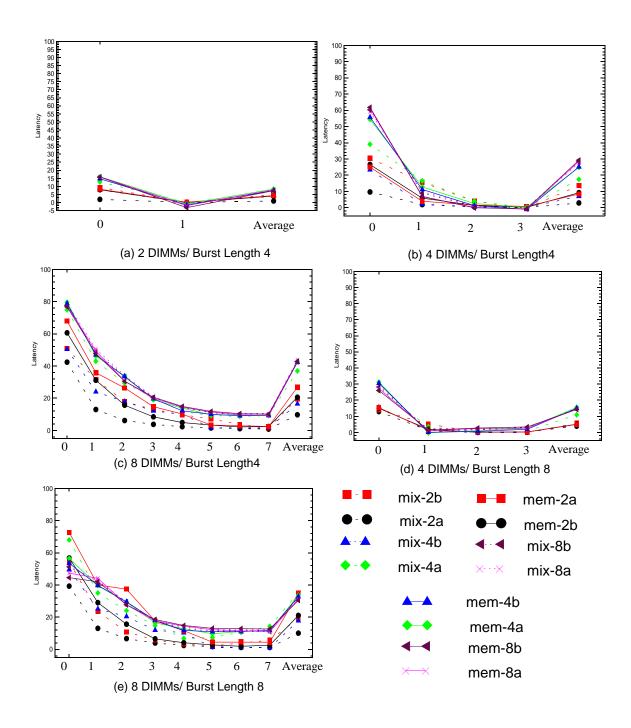

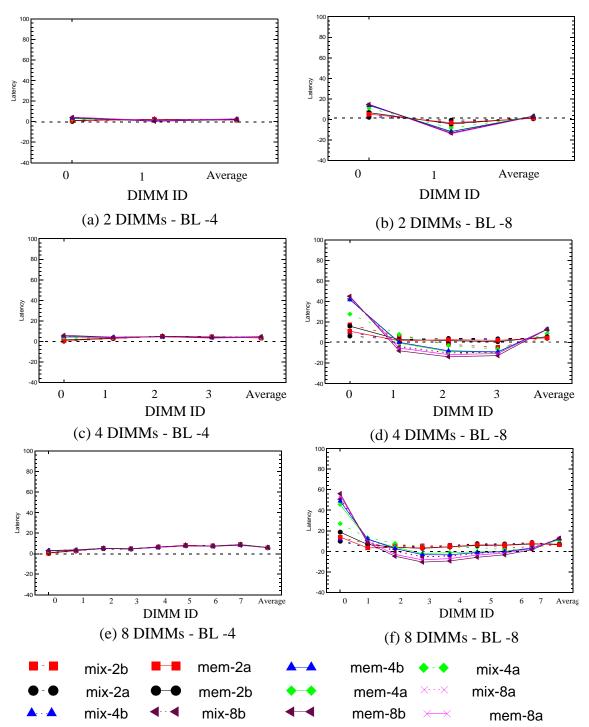

| Figure 5.10. | Per DIMM Average Read Latency for FBD-DDR2 closed page systems 113                                            |

| Figure 5.11. | Per DIMM Average Read Latency for FBD-DDR2 open page systems 114                                              |

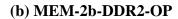

| Figure 5.12. | Per DIMM Average Read Latency for FBD-DDR3 closed page systems 115                                            |

| Figure 5.13. | Per DIMM Average Read Latency Contributors for FBD-DDR3 closed page systems with burst length 8116            |

| Figure 5.9.  | Per DIMM Average Read Latency for FBD-DDR3 open page systems 117                                              |

| Figure 5.14. | Per DIMM Average Read Latency Contributors for FBD-DDR3 closed page systems with burst length 4118            |

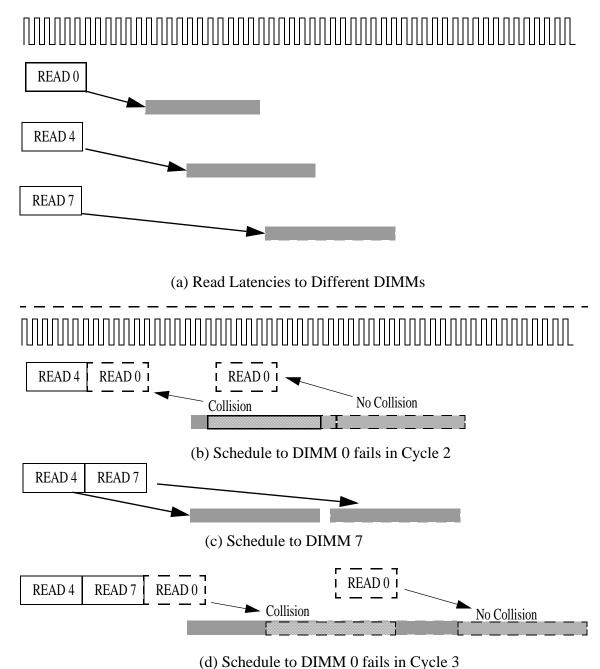

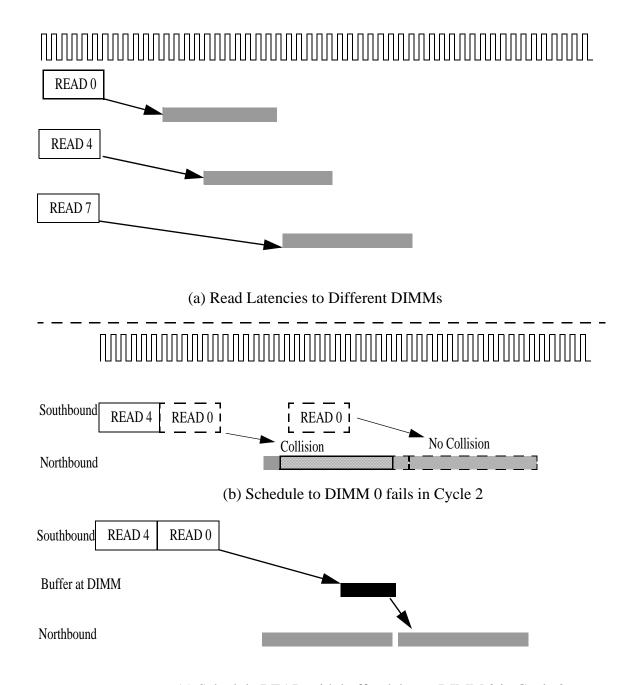

| Figure 5.15. | Why Scheduling to closer DIMMs fails?                                                                         |

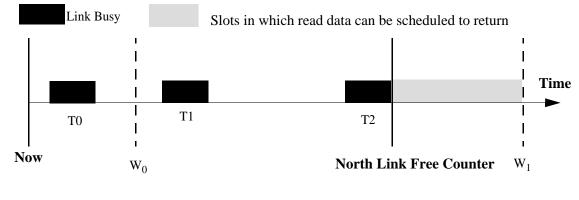

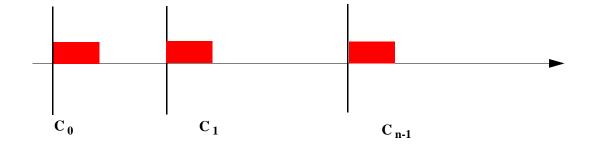

| Figure 5.16. | Monitoring North Link Availability in Scheduling Windows                                                      |

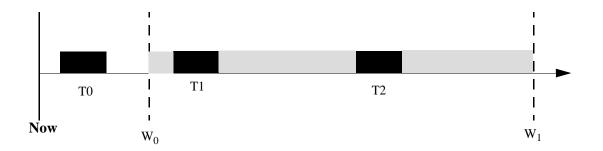

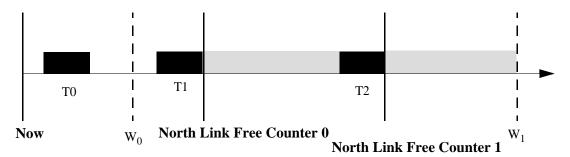

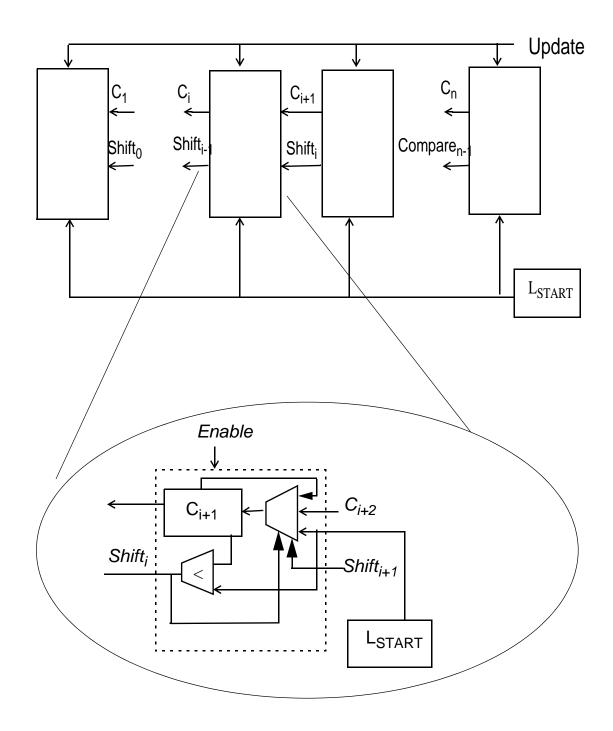

| Figure 5.17. | Counter Mechanism to keep track of North Link Busy Periods                                                    |

| Figure 5.18. | Counter Update Mechanism                                                                                      |

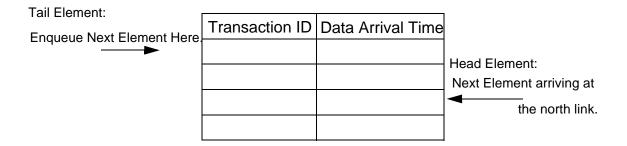

| Figure 5.19. | FIFO Response Queue                                                                                           |

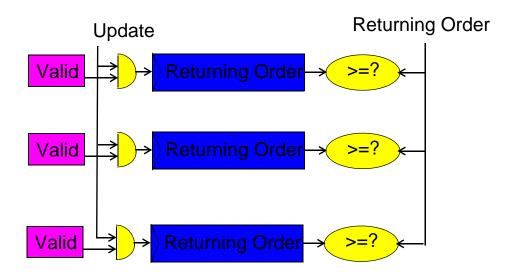

| Figure 5.20. | Self-reordering Queue Logic                                                                                   |

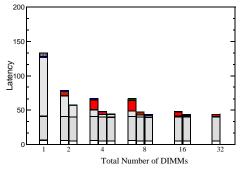

| Figure 5.21. | Impact of permitting out-of-order return on northbound link                                                   |

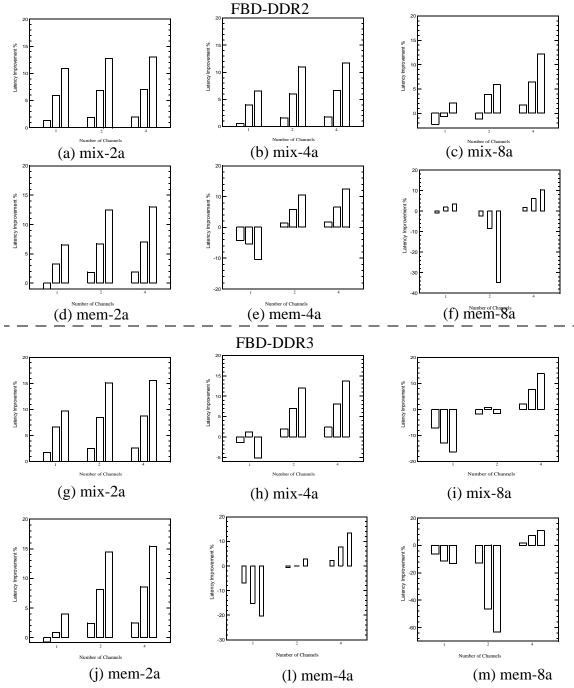

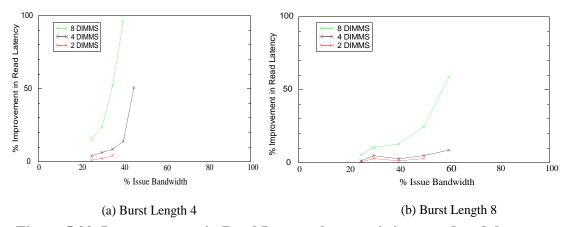

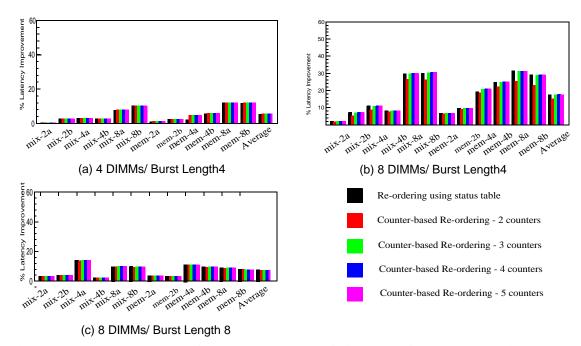

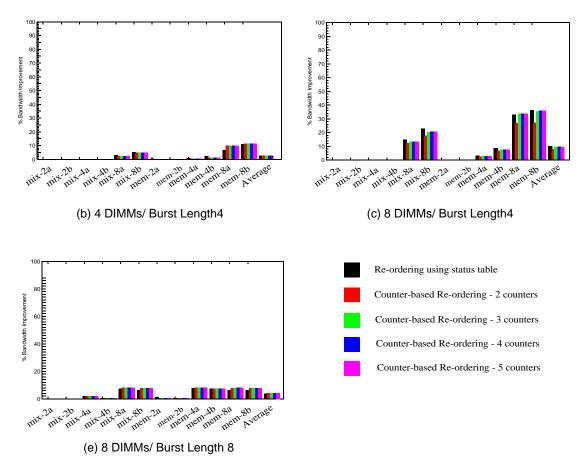

| Figure 5.22. | Improvements in Read Latency by permitting reordered data return of read data134                                                                                                                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.23. | Impact of permitting out-of-order return with different ratio of read traffic 135                                                                                                                                      |

| Figure 5.24. | Latency contributors for system using reordered data return                                                                                                                                                            |

| Figure 5.25. | Impact of different reordering schemes on Latency bandwidth characteristics 137                                                                                                                                        |

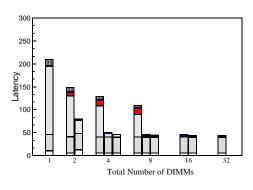

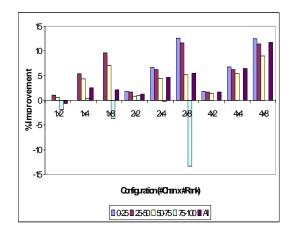

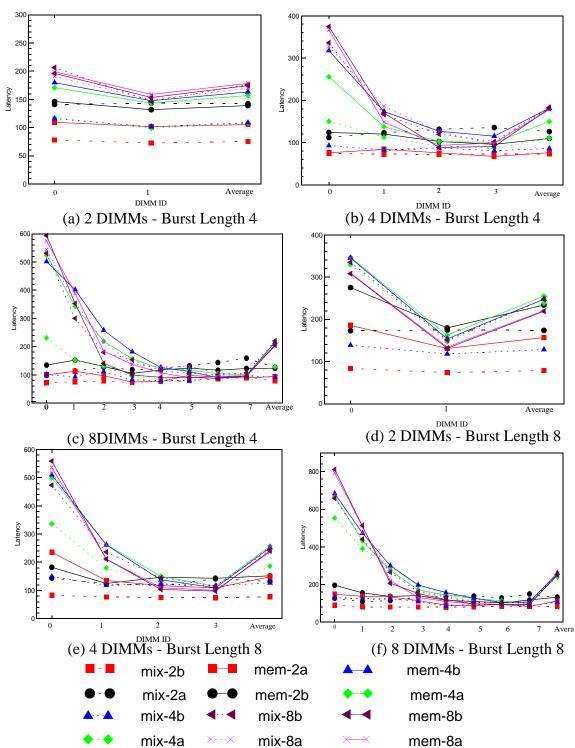

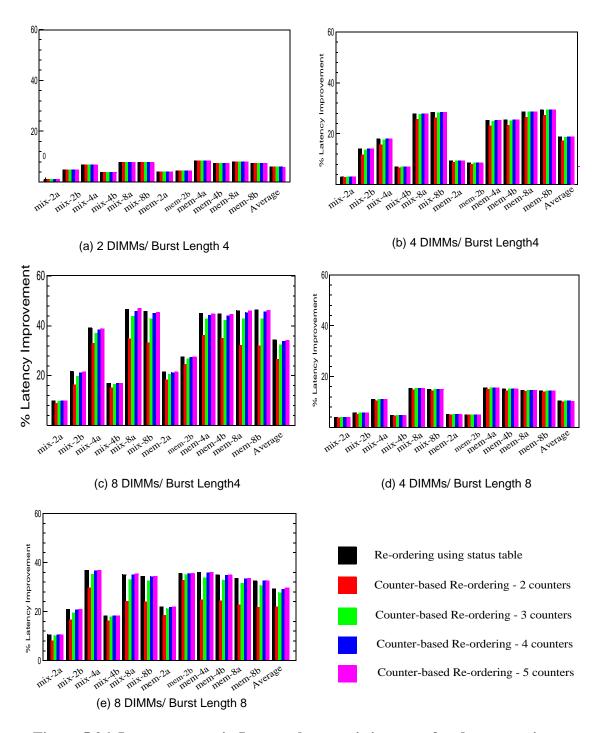

| Figure 5.26. | Improvements in Latency by permitting out-of-order return in FBD-DDR3 system using closed page single channel139                                                                                                       |

| Figure 5.27. | Improvements in Latency by permitting out-of-order return in FBD-DDR3 system using closed page in a two channel system140                                                                                              |

| Figure 5.28. | Improvements in Latency by permitting out-of-order return in FBD-DDR3 system using open page in a single channel system141                                                                                             |

| Figure 5.29. | Improvements in Latency by permitting out-of-order return in FBD-DDR2 system using closed page in a single channel system142                                                                                           |

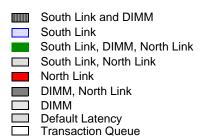

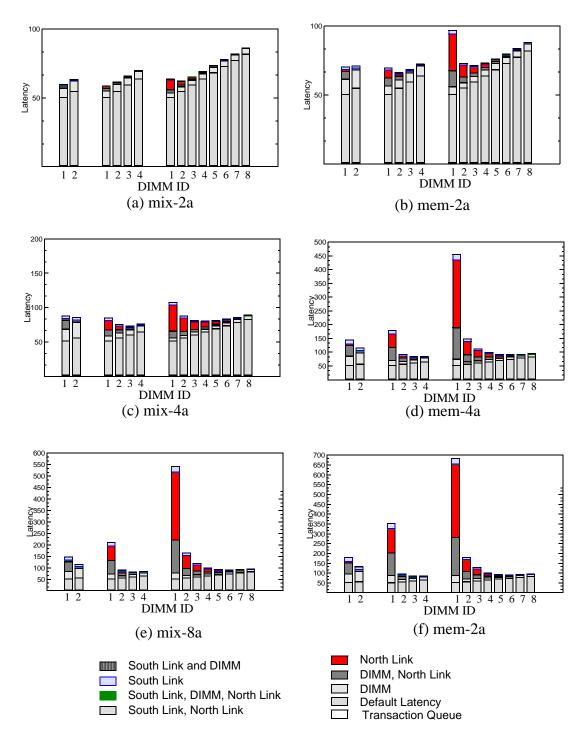

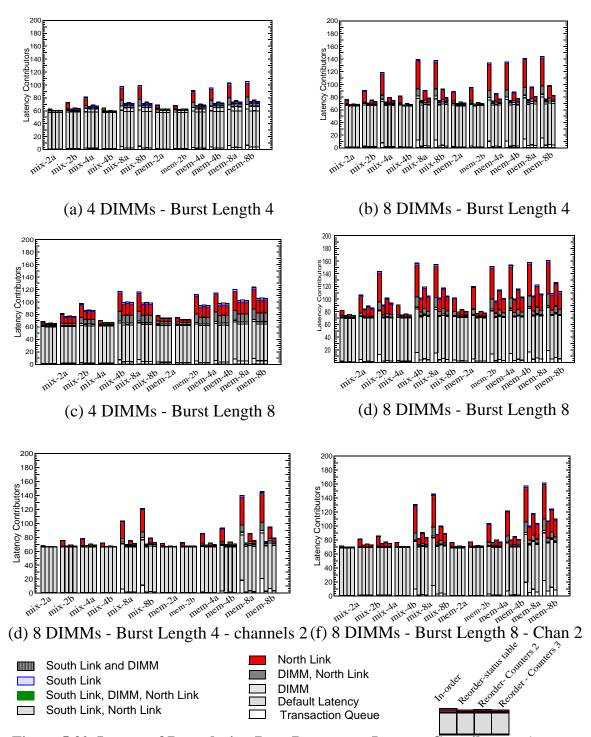

| Figure 5.30. | Impact of Re-ordering Data Returns on Latency Contributors                                                                                                                                                             |

| Figure 5.31. | Per-DIMM Latency Improvements by a Re-ordering Data Returns 147                                                                                                                                                        |

| Figure 5.32. | Impact of Re-ordering Data Returns on Per-DIMM Latency Contributors 148                                                                                                                                                |

| Figure 5.33. | Impact of Re-ordering Data Returns on Per-DIMM Latency Contributors 149                                                                                                                                                |

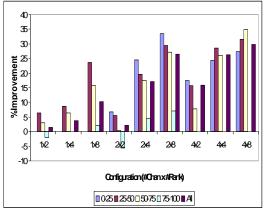

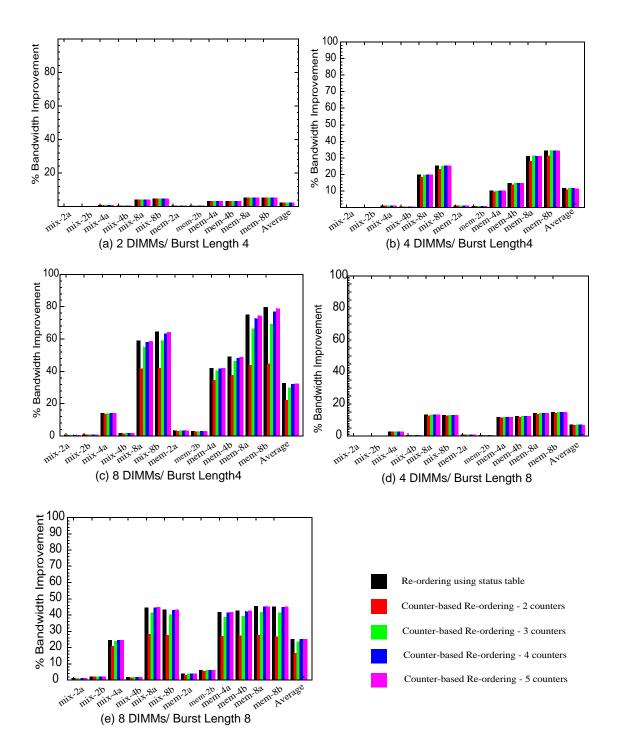

| Figure 5.34. | Improvements in Bandwidth by permitting out-of-order return in FBD-DDR3 system using closed page in a single channel system151                                                                                         |

| Figure 5.35. | Improvements in Bandwidth by permitting out-of-order return in FBD-DDR3 system using closed page in a two channel system152                                                                                            |

| Figure 5.36. | Improvements in Bandwidth by permitting out-of-order return in FBD-DDR3 system using open page in a single channel system153                                                                                           |

| Figure 5.37. | Improvements in bandwidth by permitting out-of-order return in FBD-DDR2 system using closed page in a single channel system154                                                                                         |

| Figure 5.38. | How buffering works                                                                                                                                                                                                    |

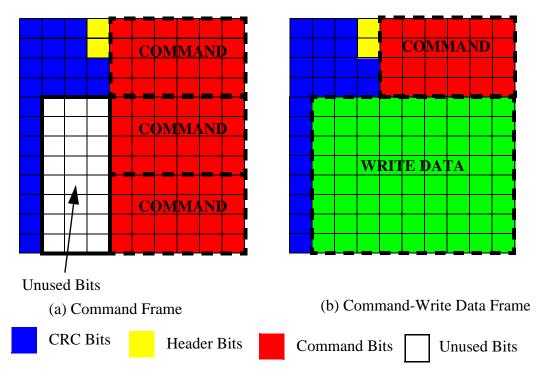

| Figure 5.39. | FBDIMM Southbound Frame Bit Layout                                                                                                                                                                                     |

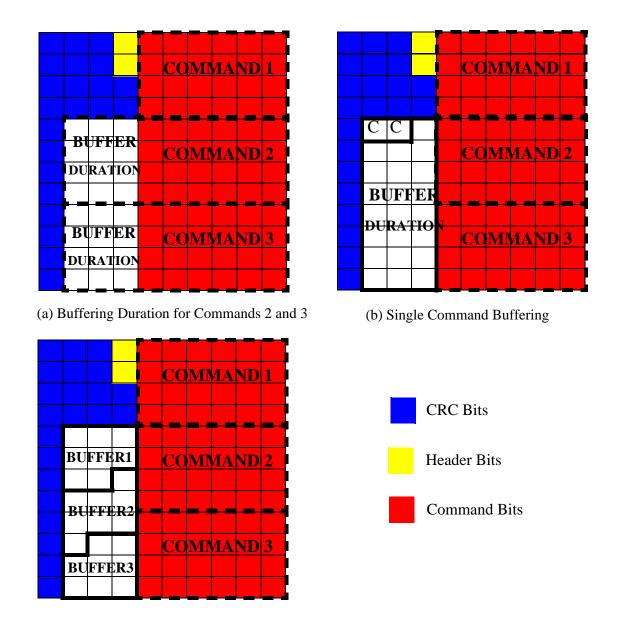

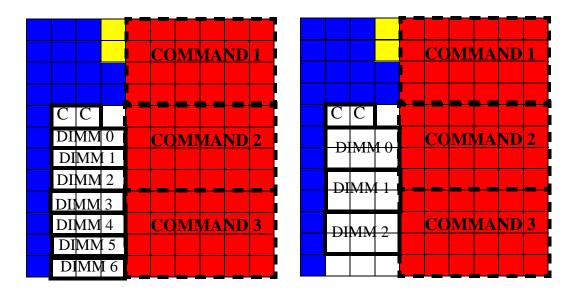

| Figure 5.40. | Command Frame Formats with Buffer Durations Specified                                                                                                                                                                  |

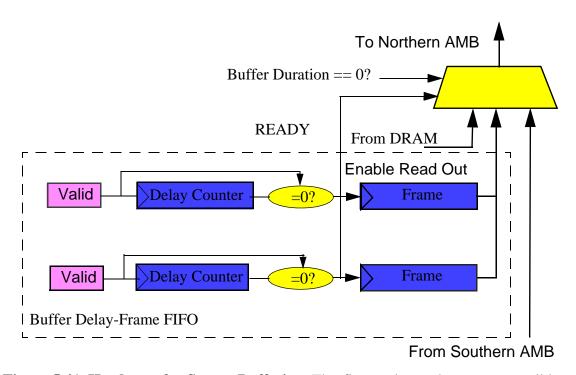

| Figure 5.41. | Hardware for Source Buffering                                                                                                                                                                                          |

| Figure 5.42. | Frames for Global Variable Buffering                                                                                                                                                                                   |

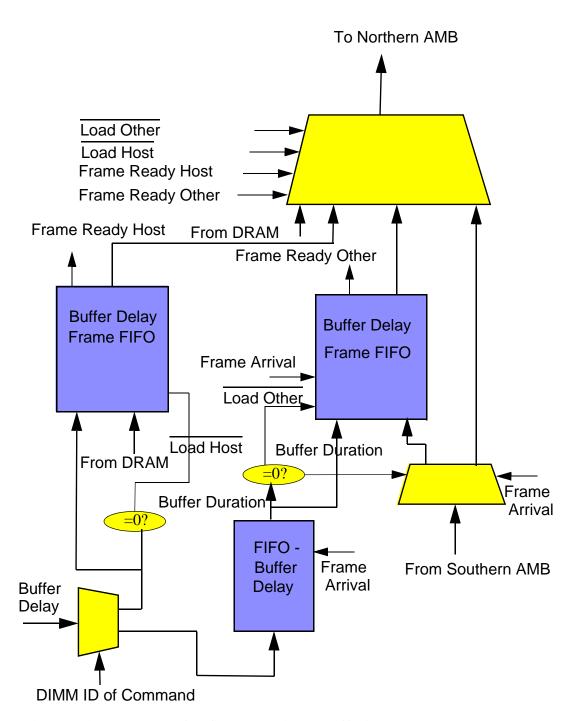

| Figure 5.43. | Hardware for Global Variable Buffering                                                                                                                                                                                 |

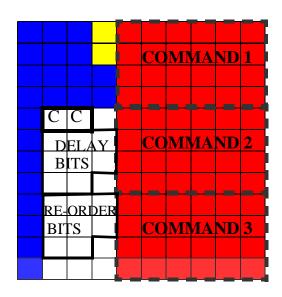

| Figure 5.44. | Frames for Global Binary Buffering                                                                                                                                                                                     |

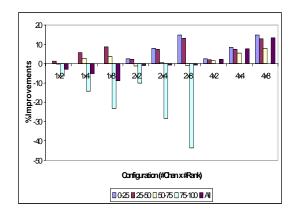

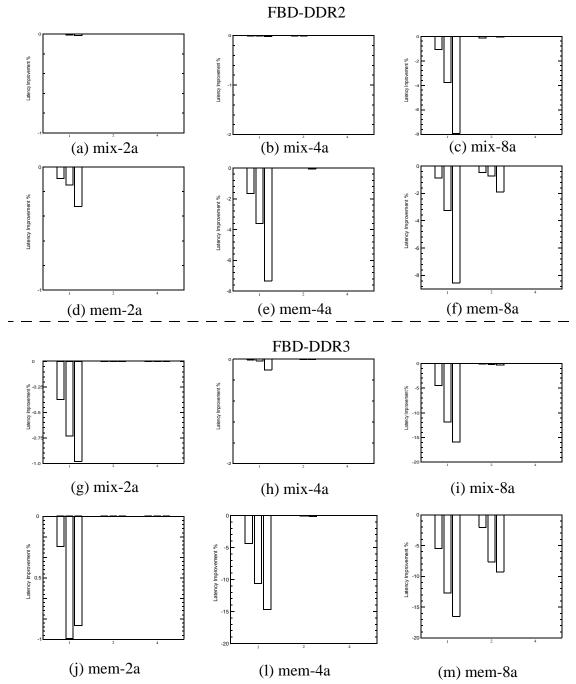

| Figure 5.45. | Latency Improvement by using Source Buffering                                                                                                                                                                          |

| Figure 5.46. | Latency Improvement by using buffer anywhere for variable duration . 168                                                                                                                                               |

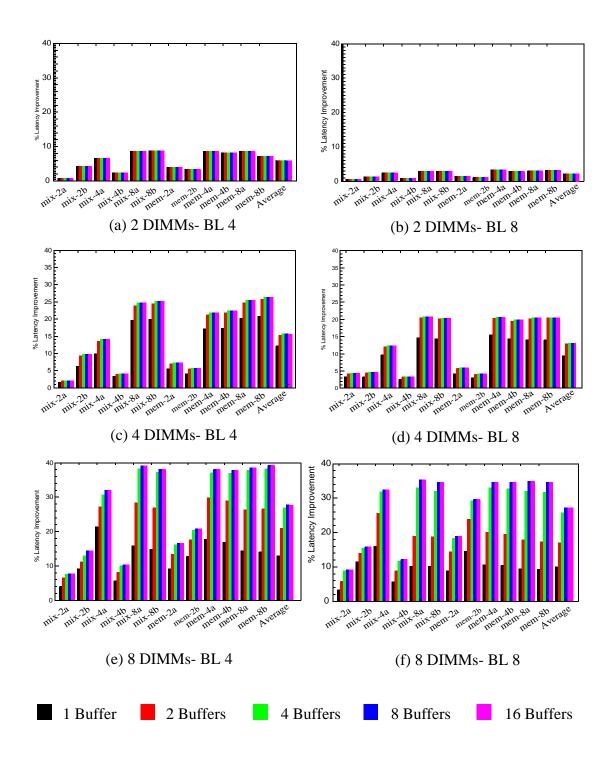

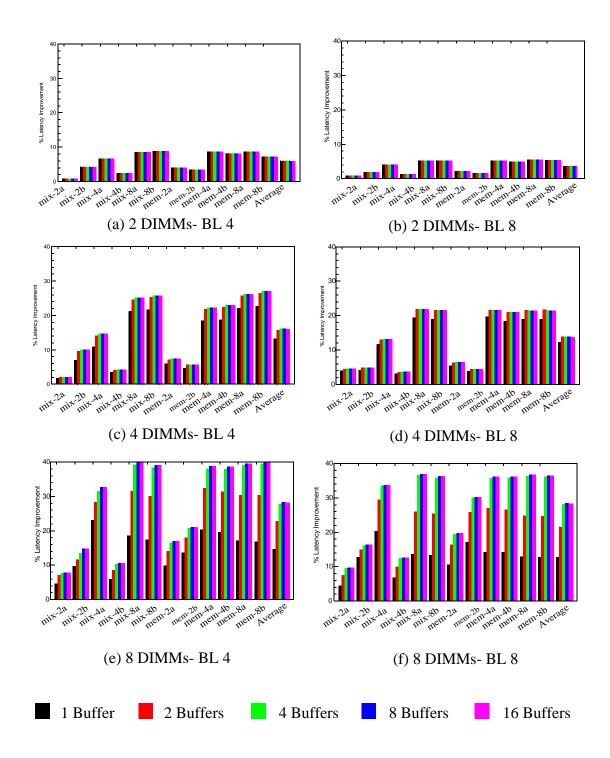

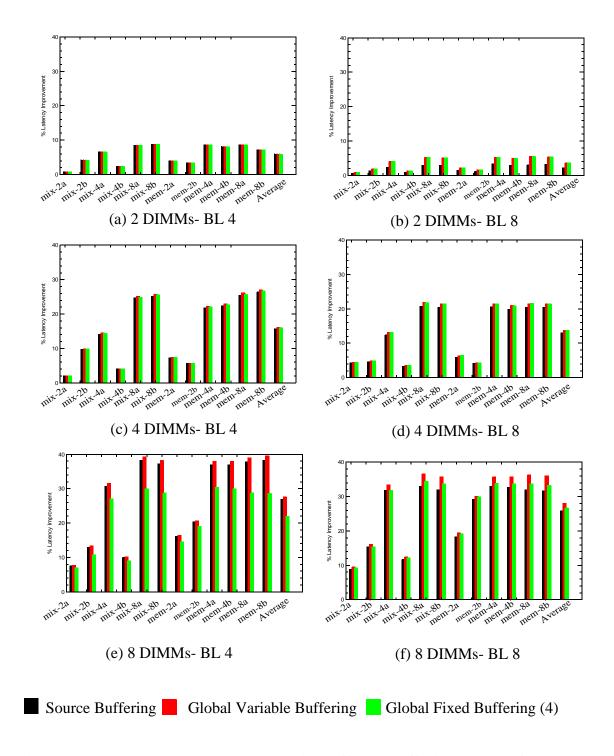

| Figure 5.47. | Latency Improvement by using buffer fixed anywhere - whole burstThe graphs plot the percentage improvements for the average read latency on the v-axis for the different applications at different channel depth. Each |

|              | application's data is grouped on the x-axis with a bar for a different buffer count.169                                                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

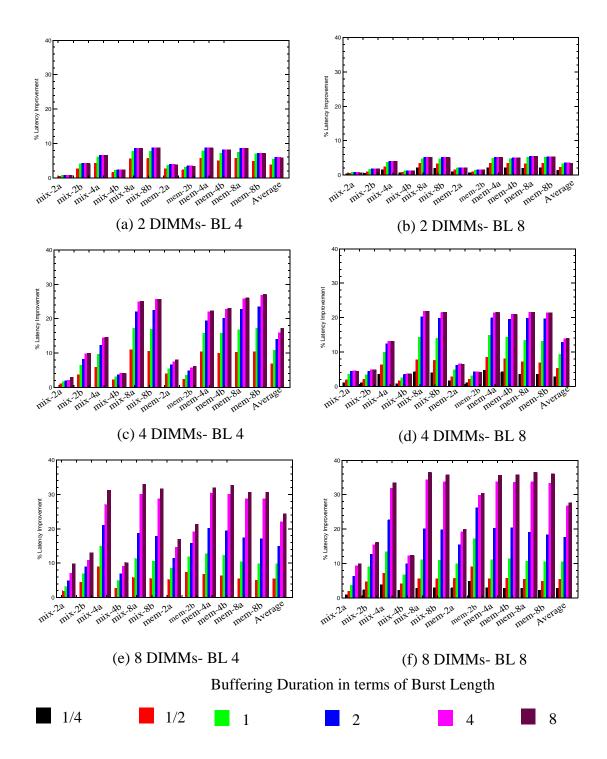

| Figure 5.48. | Latency Improvement by using different durations for Global Binary Buffering170                                                                        |

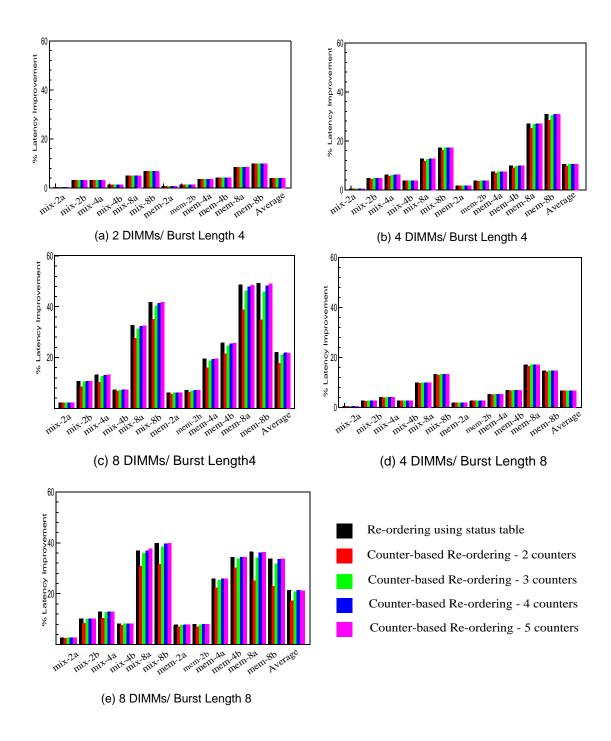

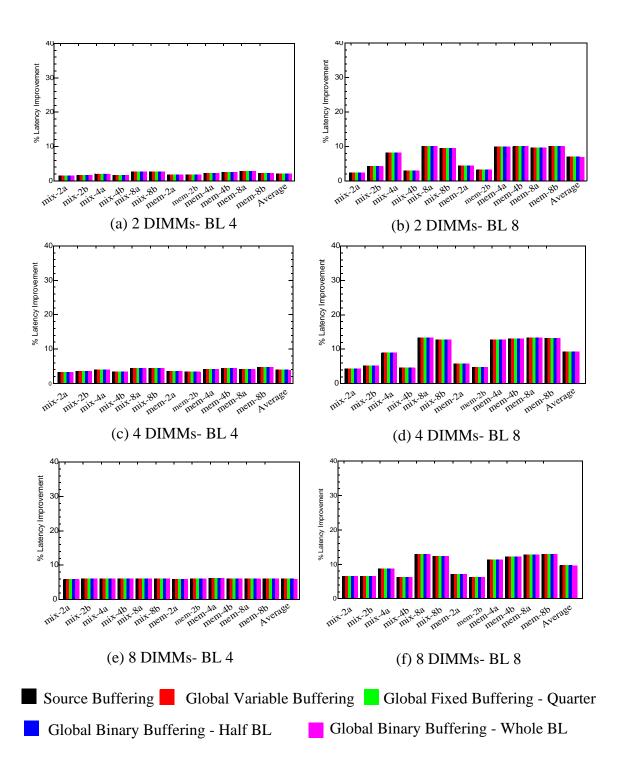

| Figure 5.49. | Latency Improvements by using different buffering schemes for a system using in-order return171                                                        |

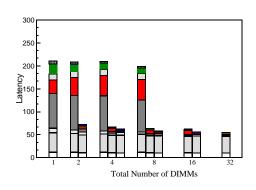

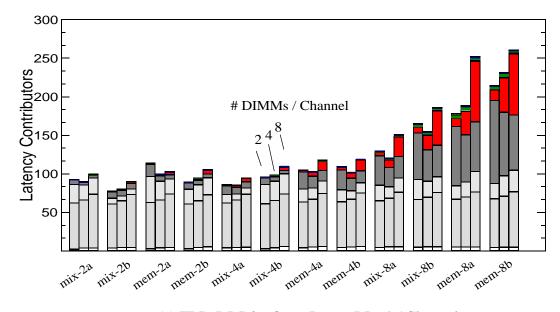

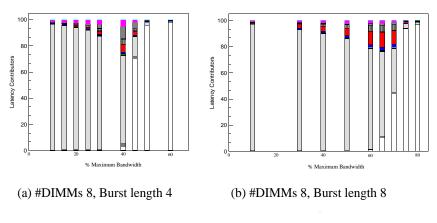

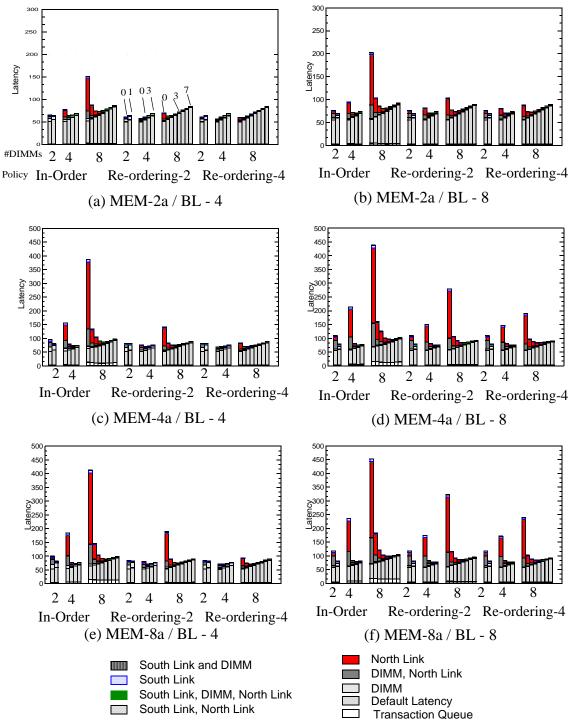

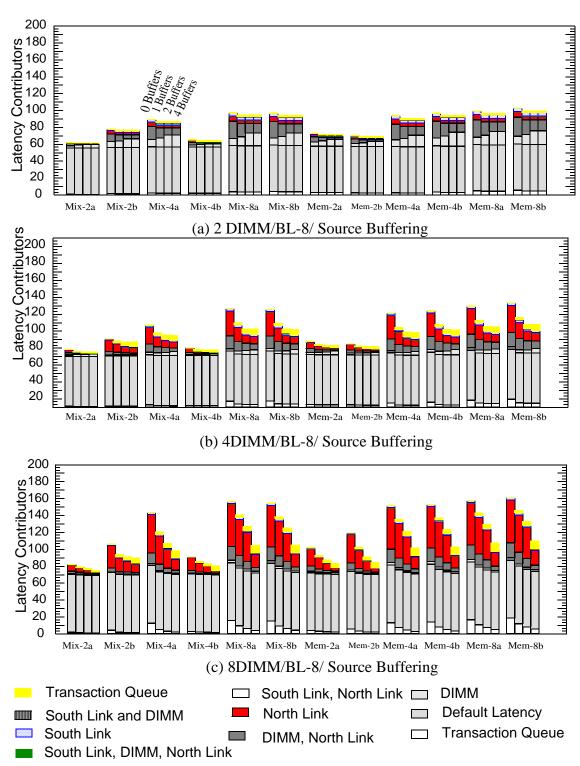

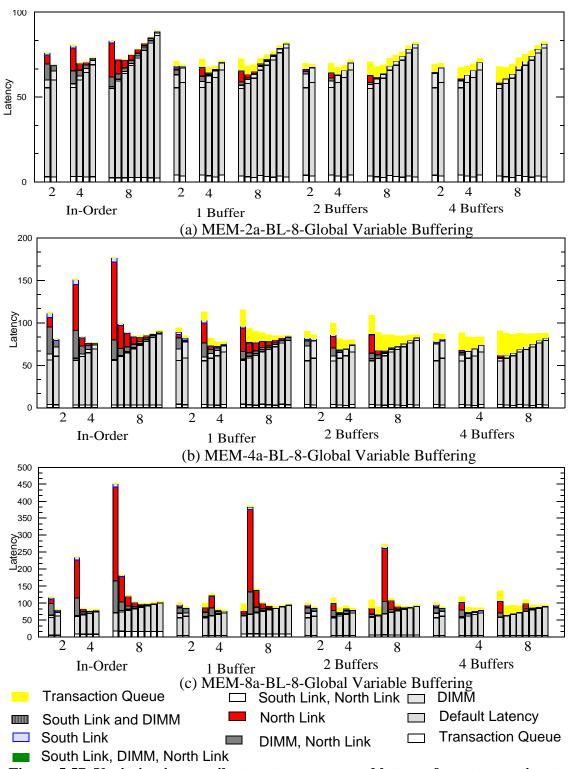

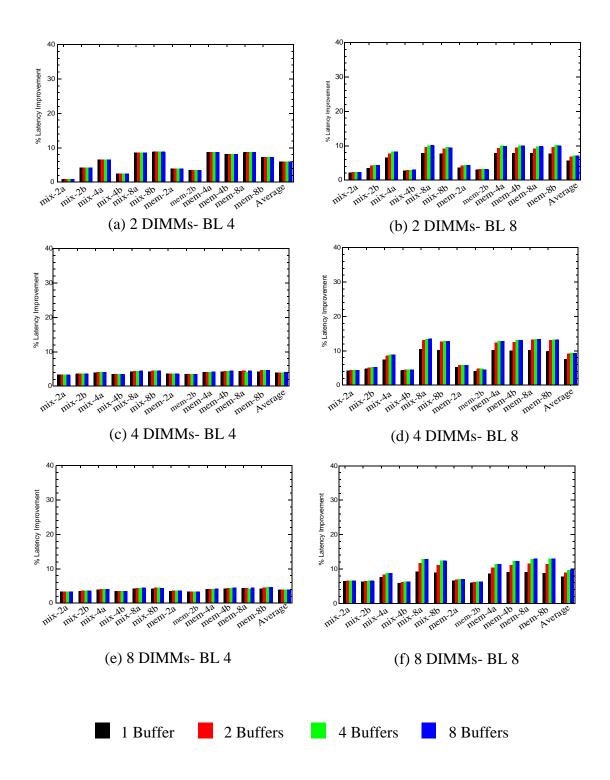

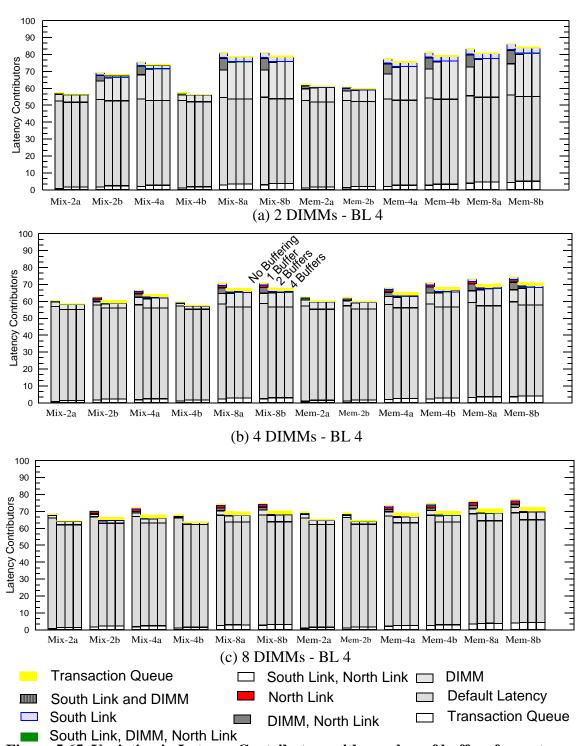

| Figure 5.50. | Impact of number of buffers on read latency contributors for various channel depths 172                                                                |

| Figure 5.51. | Impact of number of buffers on read latency contributors for various channel depths 173                                                                |

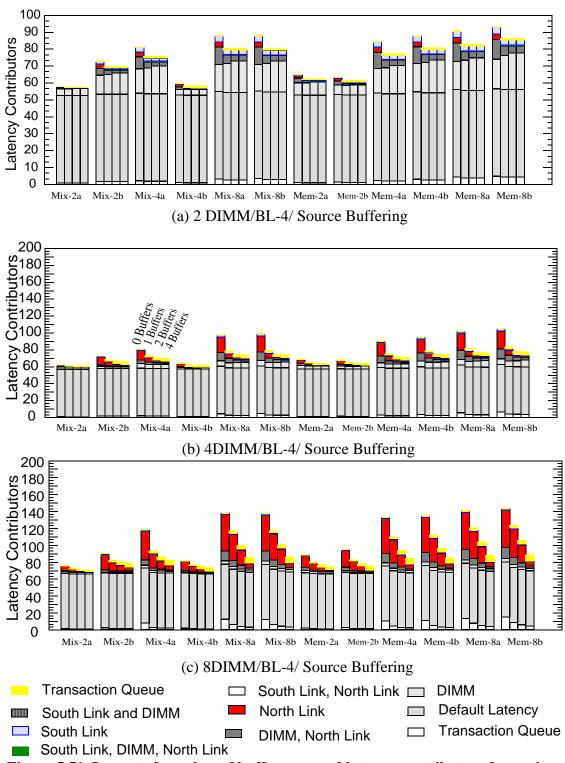

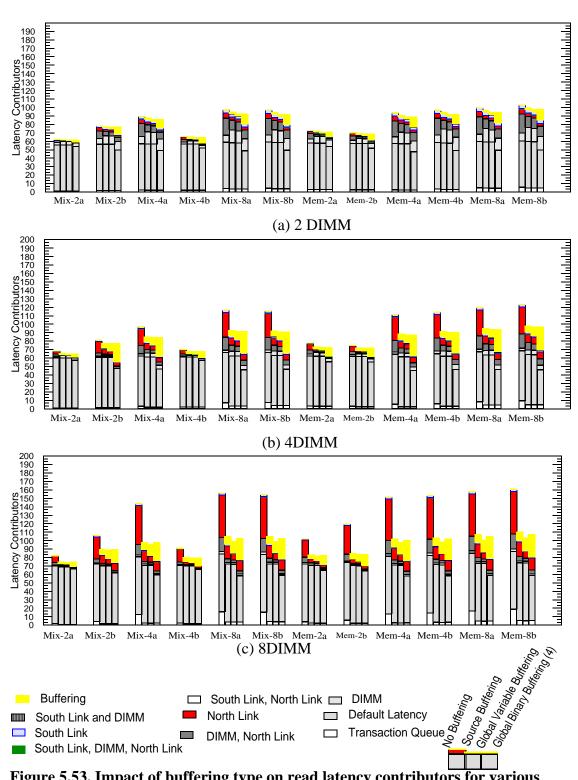

| Figure 5.52. | Impact of buffering type on read latency contributors for various channel depths for burst length 4 systems174                                         |

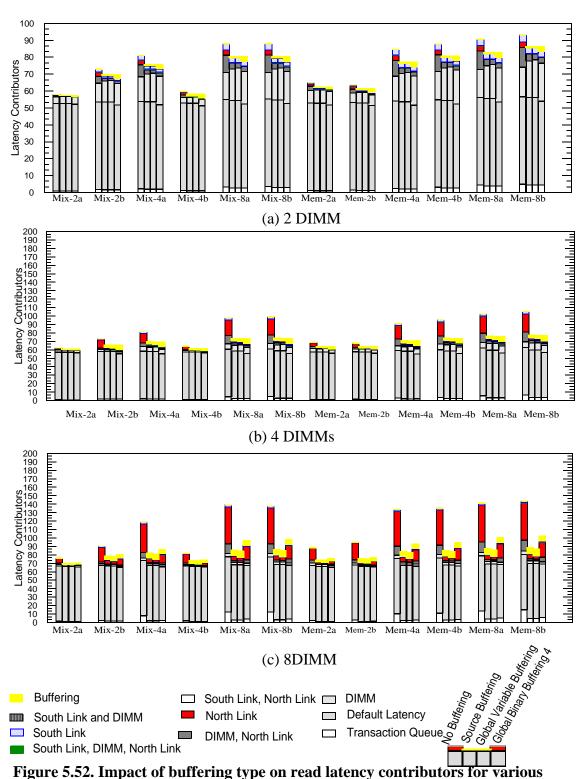

| Figure 5.53. | Impact of buffering type on read latency contributors for various channel depths for burst length 8 systems175                                         |

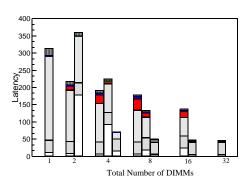

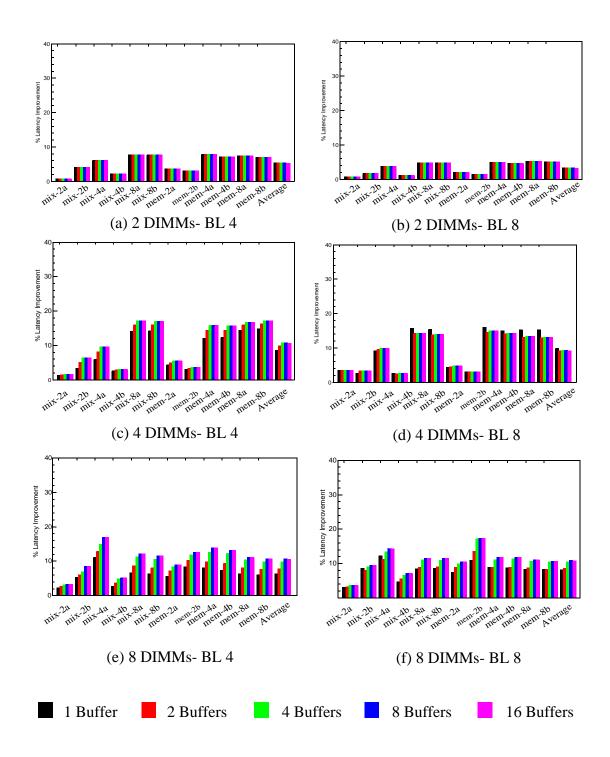

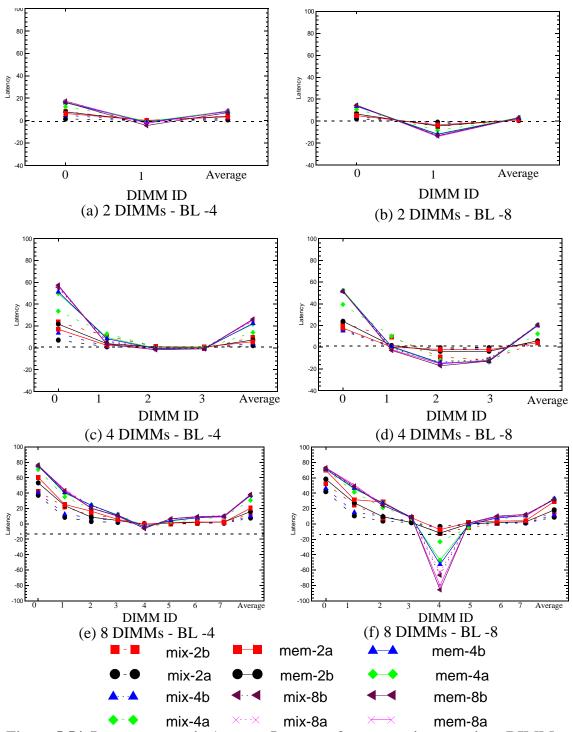

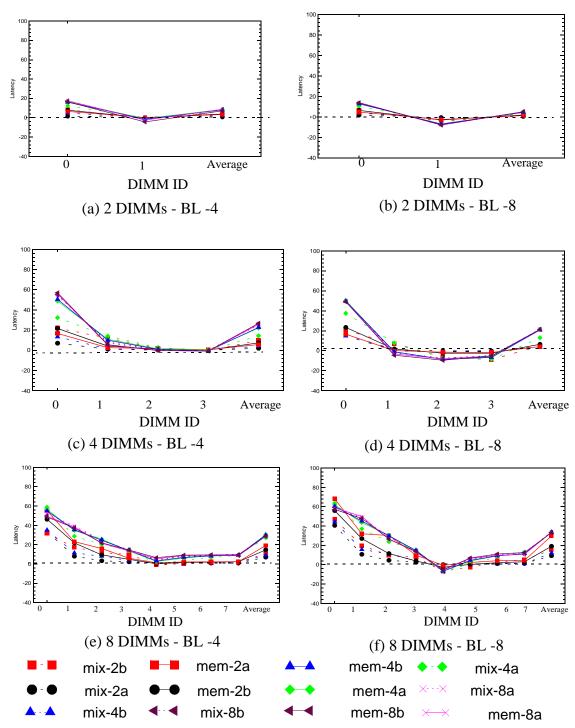

| Figure 5.54. | Improvements in Average Latency of a transaction to a given DIMM using Buffering at Source177                                                          |

| Figure 5.55. | Improvements in Average Latency of a transaction to a given DIMM using Global Variable Buffering178                                                    |

| Figure 5.56. | Improvements in Average Latency of a transaction to a given DIMM using Global Binary Buffering179                                                      |

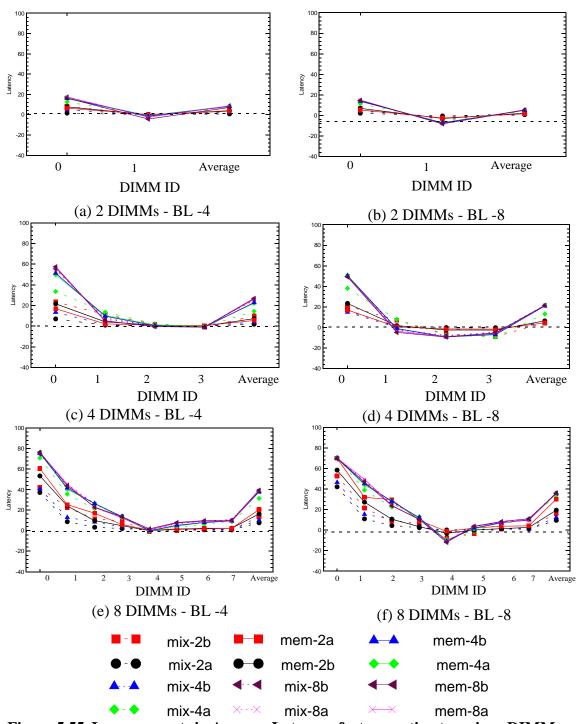

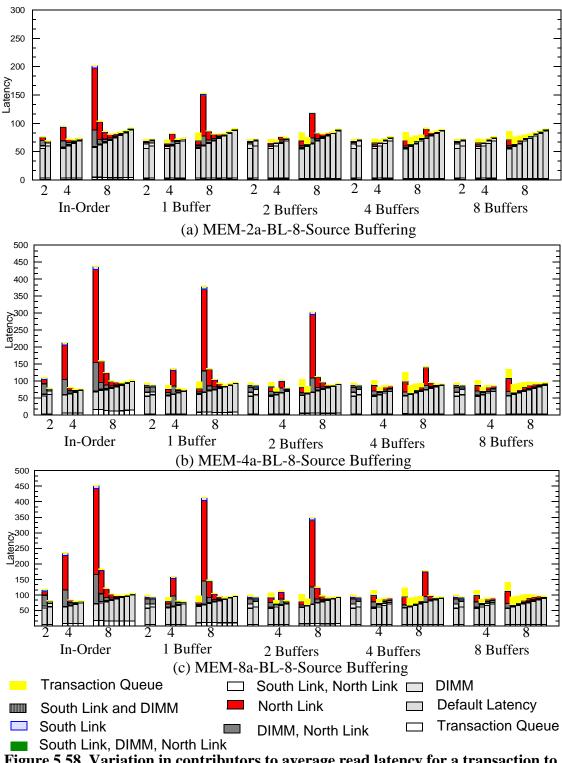

| Figure 5.58. | Variation in contributors to average read latency for a transaction to a given DIMM with number of buffers182                                          |

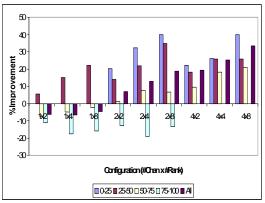

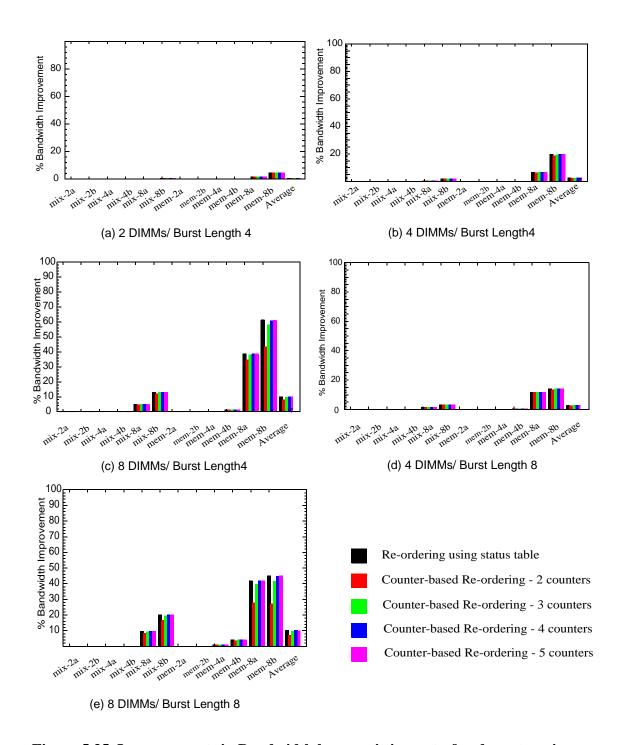

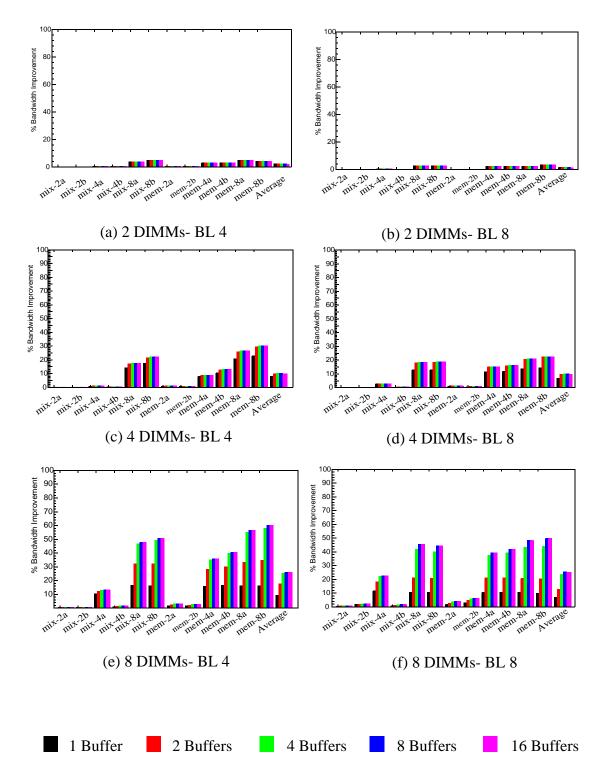

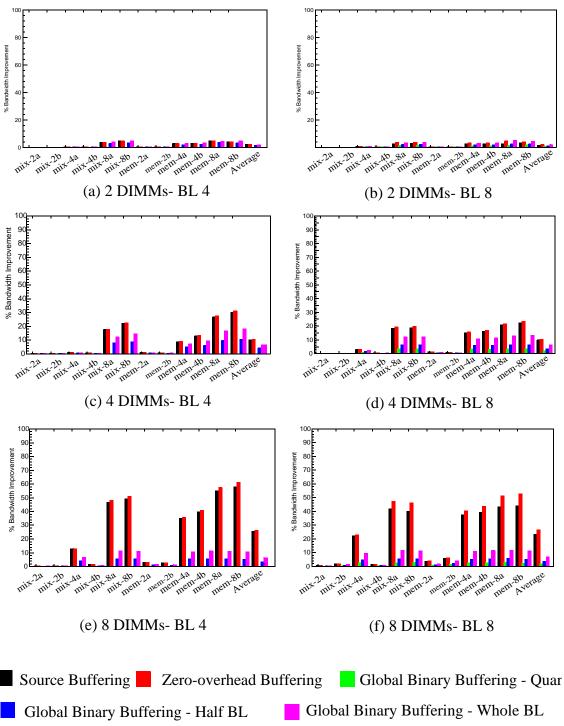

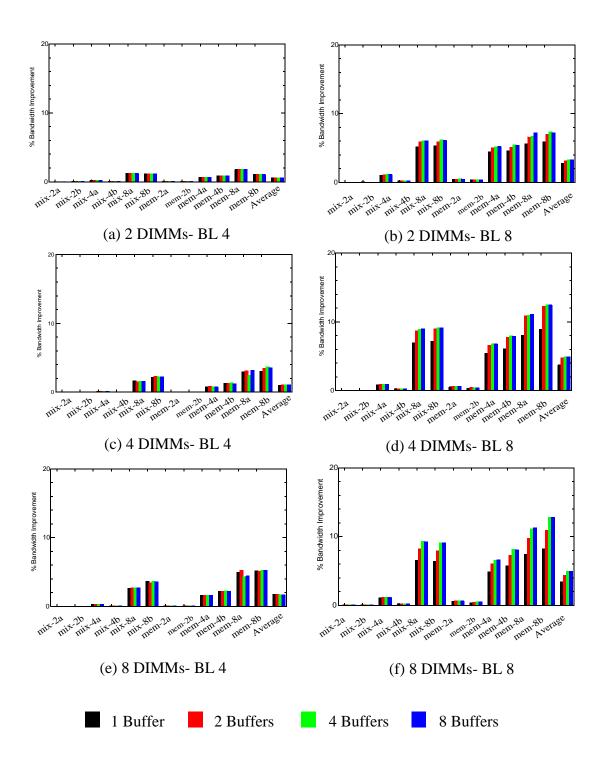

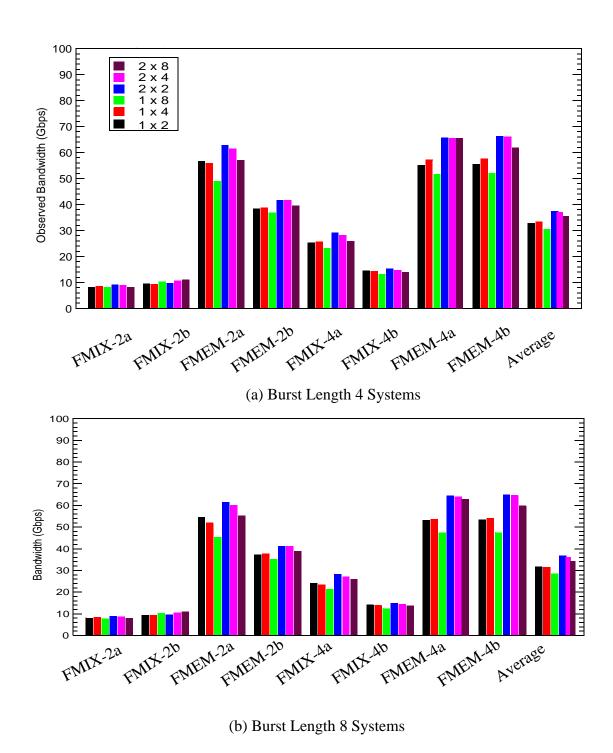

| Figure 5.59. | Bandwidth Improvement by using Source Buffering                                                                                                        |

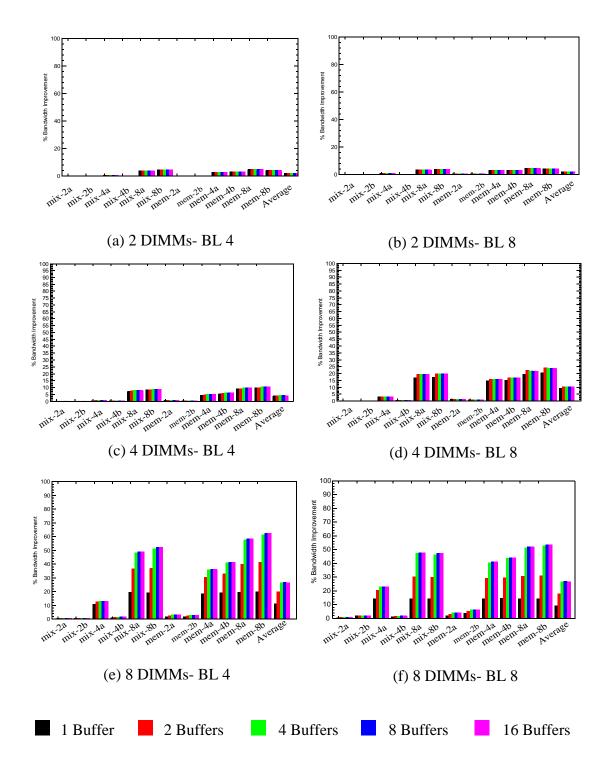

| Figure 5.60. | Bandwidth Improvement by using Global Variable Buffering                                                                                               |

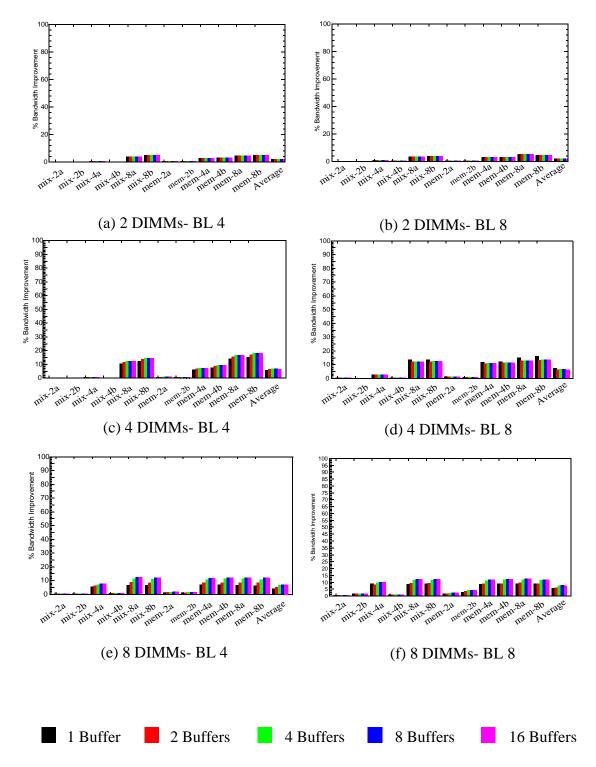

| Figure 5.61. | Bandwidth Improvement by using buffer fixed anywhere - whole 185                                                                                       |

| Figure 5.57. | Variation in contributors to average read latency for a transaction to a given DIMM with number of buffers186                                          |

| Figure 5.62. | Bandwidth Improvements by using different buffering schemes in in-order return system188                                                               |

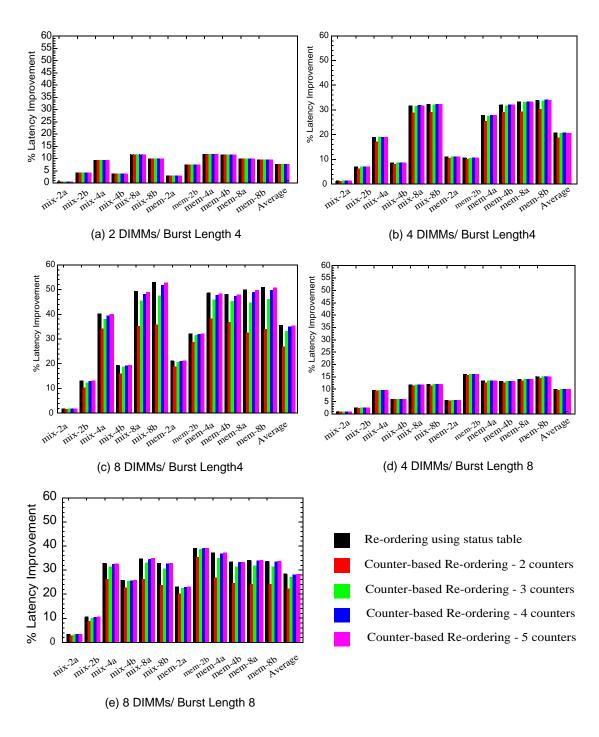

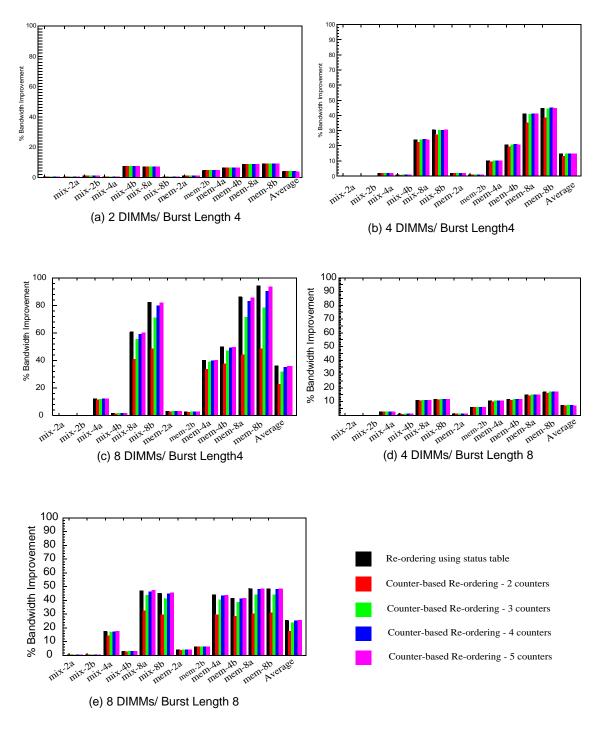

| Figure 5.63. | Latency Improvements by using different buffering schemes in a system permitting re-ordering of data returns 190                                       |

| Figure 5.64. | Impact of number of buffers on AMB on latency improvements by using Source Buffering and re-ordering191                                                |

| Figure 5.65. | Variation in Latency Contributors with number of buffers for system using re-ordering and buffering 192                                                |

| Figure 5.67. | Improvements in Average Latency of a transaction to a given DIMM using Source Buffering in a system that supports re-ordering of read data returns 193 |

| Figure 5.68. | Bandwidth improvements by using different number of buffers in a system permitting re-ordering of data returns and Source Buffering194                 |

| Figure 5.66. | Variation in Latency Contributors with number of buffers for system using re-ordering and buffering 195                                                |

| Figure 5.69. | . Impact of buffering type on bandwidth improvements for a system permitting re-ordering of data returns 196 |         |

|--------------|--------------------------------------------------------------------------------------------------------------|---------|

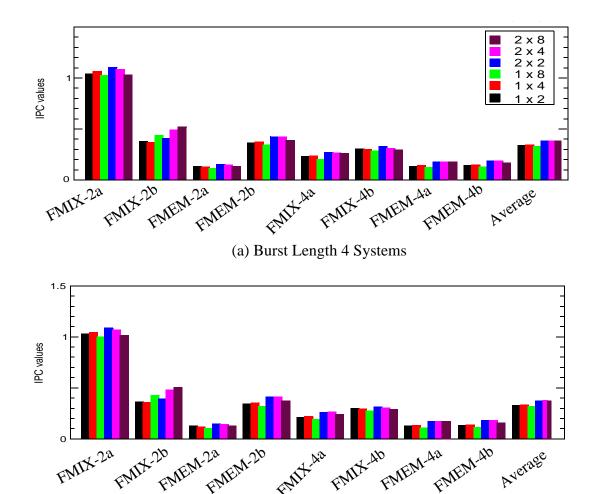

| Figure 5.70. | Default IPC values for Workloads                                                                             | 200     |

| C            | Default Sustained Bandwidth for Workloads                                                                    |         |

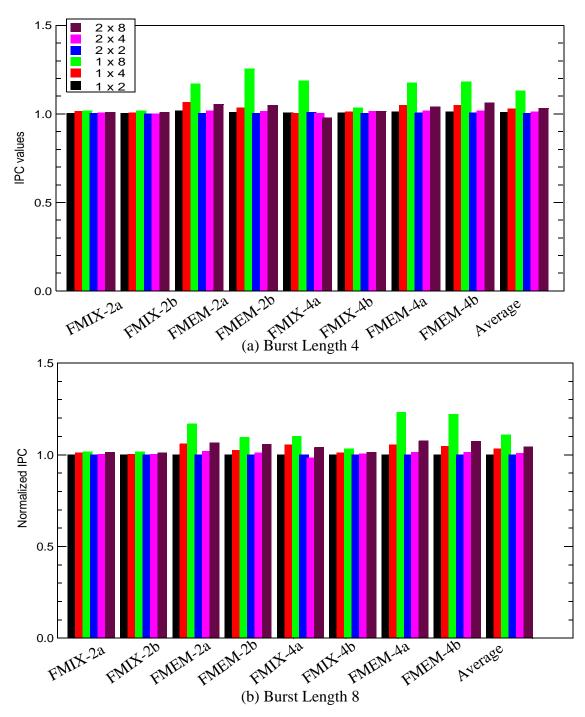

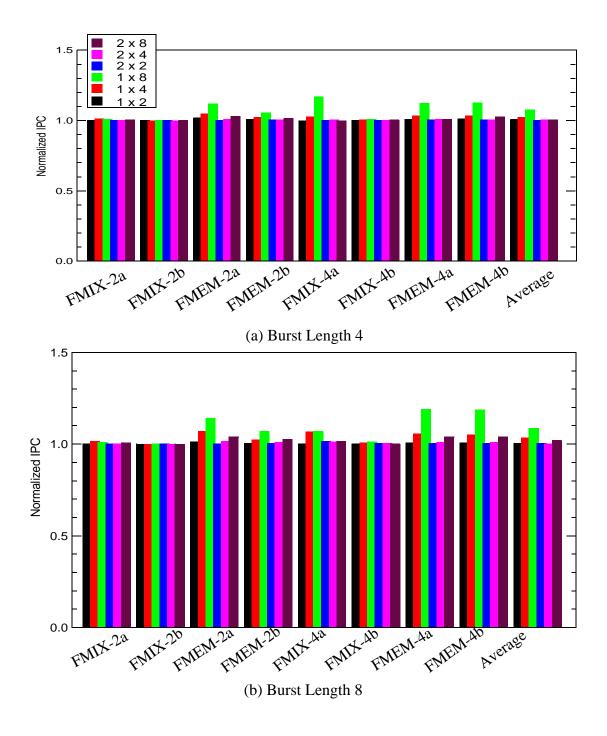

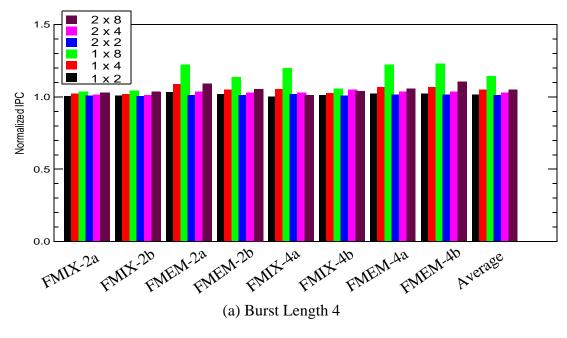

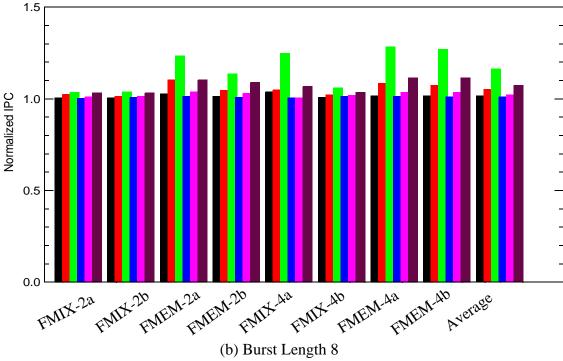

| Figure 5.72. | Improvements in IPC by using Re-ordering of Data Returns                                                     | 202     |

| Figure 5.73. | Improvements in IPC by using Source Buffering                                                                | 203     |

| Figure 5.74. | Improvements in IPC by using Buffering + Re-ordering of Data R 204                                           | Returns |

# **List of Tables**

| TABLE 4.1. | Memory System Parameters          | 47    |

|------------|-----------------------------------|-------|

| TABLE 4.2. | Multi-programming Workloads       | 48    |

| TABLE 5.1. | Memory System Parameters          | 97    |

| TABLE 5.2. | Out of order Processor parameters | . 198 |

| TABLE 5.3. | Workload Combinations Used        | . 199 |

# **Chapter 1: Introduction**

The growing size of application working sets, the popularity of software-based multimedia and graphics workloads, and the increased use of speculative techniques have contributed to the rise in bandwidth and capacity requirements of computer memory sub-systems. Capacity needs have been met by building increasingly dense DRAM chips and bandwidth needs have been met by scaling front-side bus data rates and using wide, parallel buses. However, traditional bus topologies have reached a point where they fail to scale well into the future.

The electrical constraints of high-speed parallel buses complicate bus scaling in terms of loads, speeds, and widths [1]. Consequently the maximum number of DIMMs per channel in successive DRAM generations has been *decreasing*. SDRAM channels have supported up to 8 DIMMs of memory, some types of DDR channels support only 4 DIMMs, DDR2 channels have but 2 DIMMs, and DDR3 channels are expected to support only a single DIMM. In addition, the serpentine routing required for electrical path-length matching of the data wires becomes challenging as bus widths increase. For the bus widths of today, the motherboard area occupied by a single channel is significant, complicating the task of adding capacity by increasing the number of channels. To address these scalability issues, an alternate DRAM technology, the Fully Buffered Dual Inline Memory Module (FBDIMM) [3] has been introduced.

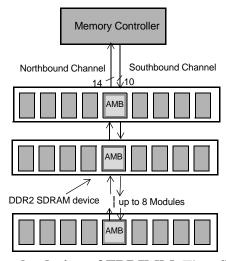

The FBDIMM memory architecture replaces the shared parallel interface between the memory controller and DRAM chips with a point-to-point serial interface between the memory controller and an intermediate buffer, the Advanced Memory Buffer (AMB). The on-DIMM interface between the AMB and the DRAM modules is identical to that seen in

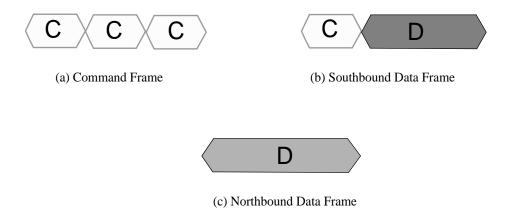

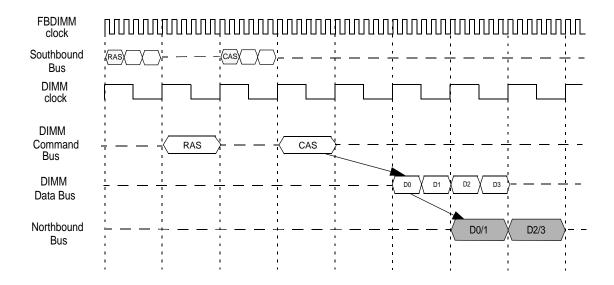

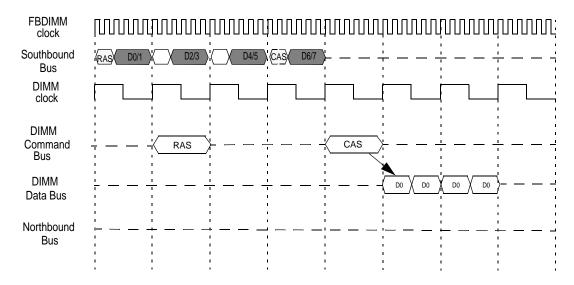

DDR2 or DDR3 systems, which we shall refer to as DDRx systems. The serial interface is split into two uni-directional buses, one for read traffic (northbound channel) and another for write and command traffic (southbound channel), as shown in Fig 1.1. FBDIMMs adopts a packet-based protocol that bundles commands and data into frames that are transmitted on the channel and then converted to the DDRx protocol by the AMB.

**Understanding FBDIMM.** The FBDIMMs' unique interface raises questions on whether existing memory controller policies will continue to be relevant to future memory architectures. In particular in the first part of the dissertation we ask the following questions:

- How do DDRx and FBDIMM systems compare with respect to latency and bandwidth?

- What is the most important factor that impacts the performance of FBDIMM systems?

- How do FBDIMM systems respond to the values of parameters like row buffer management policy, scheduling policy and topology?

To answer these questions, we did an evaluation of the performance of FBDIMM systems and DDRx systems using memory inputs from the SPEC 2000[2] workload suite.

**Figure 1.1. FBDIMM Memory System.** In the FBDIMM organization, there are no multi-drop busses; DIMM-to-DIMM connections are point-to-point. The memory controller is connected to the nearest AMB, via two uni-directional links. The AMB is in turn connected to its southern neighbor via the same two links.

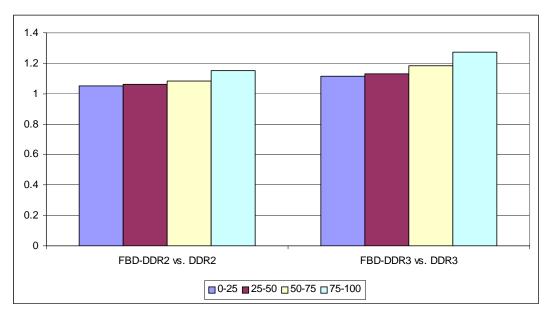

Our study showed that the relative performance of a FBDIMM system and a DDRx system was a strong function of the bandwidth utilization of the input streams. Overall, the FBDIMM system had a 27% average higher latency, which were mainly due to workloads with bandwidth utilizations of less than 50% total DDRx DRAM bandwidth. This latency degradation becomes a latency improvement of nearly 10% for FBD-DDR3 systems as the application bandwidth utilization increased past 75% due to the ability of the FBD memory controller to use the additional DRAM level parallelism, split bus architecture and ability to send multiple DRAM commands in the same clock cycle. However, the additional system bandwidth available in a FBDIMM system resulted in an average of approximately 10% improvement in overall bandwidth with most of the benefits coming again for workloads with higher bandwidth utilization.

More interestingly, we found that the scheduling policies and row buffer management policies used in DDRx systems continued to perform comparably in FBDIMM systems. In both cases, a scheduling policy that prioritizes read traffic over write traffic had the best latency characteristics for both open page and closed page systems. A scheduling policy that prioritized traffic to currently open banks in the system had the best bandwidth characteristics while a greedy approach did very well in closed page systems.

One difference that we found with regard to FBDIMM and DDRx system behavior was their response to the use of posted CAS, a DRAM protocol feature which simplifies memory controller design by allowing the memory controller to bundle a row activation and read/write command in back-to-back command cycles. Unlike DDRx systems, FBDIMM systems using posted CAS had worse latency and bandwidth characteristics than systems which did not use this. This difference arose from the organization and use of the

FBDIMM command frame and the sharing of the FBDIMM southbound bus by commands and write data.

Detailed measurements of the contributors to the read latency of a transaction revealed that a significant factor contributing to the overall latency was delays associated with the unavailability of memory system resources, such as southbound channel, north-bound channel and DRAM. Scaling the memory system configuration, by adding more ranks or channels, resulted in the unavailability of each of these factors varying in a different fashion and interacting in different ways to impact the observed latency. In general, we observed that short channel FBDIMM systems are limited by DRAM availability, while long channel FBDIMM systems are bound by channel bandwidth. This problem is exacerbated in variable latency mode configurations where significant latency and bandwidth degradation occur due to inefficient usage of the northbound FBDIMM channel.

Optimizing FBDIMM Read Latency. The use of serialization and a multi-hop topology in FBDIMM systems has led to increases in the default cost of a read transaction. The FBDIMM protocol allows the channel to be configured in one of two modes, a fixed latency mode where the round-trip latency for a transaction is identical for all DIMMs and is set to the round-trip latency of the last DIMM in the chain. This mode imposes a higher default latency cost which is not desirable. The alternate mode, known as the variable latency mode, has been provided to target this latency cost. In this mode the channel is configured such that the round-trip latency of a transaction is a function of the distance of the DIMM from the memory controller. By allowing this, the FBDIMM protocol hopes to lower overall read latency.

Although the variable latency mode is able to reduce the average read latency for many of the workloads studied, this was not always true for applications executing in longer FBDIMM channels where the latency reductions were most needed. This problem was due to two reasons, one the inefficient utilization of the north link and the second that transactions to closer DIMMs have to often wait for read data from further DIMMs to complete using the north link although the DRAM is ready.

We studied two techniques to improve the latency of an FBDIMM channel using the following techniques

- Out of order return of read data or allowing read data to return out of order,

- Buffers at the AMB for north link data to permit transactions to nearer DIMMs being issued in advance

Like previously defined memory protocols, the FBDIMM specification assumes an omniscient memory controller that manages all system resources, including the DRAM, on-DIMM buses i.e. command and data bus, and on-board links i.e. the south and north links. The memory controller has to guarantee that there are no violations of DRAM timing parameters or any conflicts on any of the various system buses. The default implementation of the protocol assumes that read data returns in the order that it was scheduled. Consequently, the scheduler is unable to take advantage of idle time on the north links which occur prior to the use of the link by a previously scheduled read transaction.

The first optimization that we looked at was to improve latency and bus utilization by relaxing the need for data to return in the same order as the commands. We propose a technique to permit re-ordering of returning read data that can be implemented without modifying the existing FBDIMM memory protocol. Permitting reordering of read data improves

the maximum sustainable bandwidth of the system by 1-2 GBps. Application latency improves in a 4-8 DIMM deep system by an average of 5-25% while bandwidth utilization increased by 5-10%. Multi-program workload runs on a full system simulator demonstrate that this technique improves overall IPC by an average of 5-15%, with the most benefits being seen in a system with longer channels.

The second technique that we explored was focussed on de coupling DIMM availability from north link availability. We proposed using buffers on the northbound channel pat that hold read data frames. Buffering enables the memory controller to read data out of the DRAM rows without having to wait for the north link to become available. We examined several buffering policies including Source Buffering, Global Variable Buffering and Global Binary Buffering. These policies are distinguished by where buffering is permitted, i.e. at the DIMM supplying the data or at any DIMM on the path from the DIMM to the memory controller, and the buffering duration specified, a pre-defined fixed duration or a dynamically determined value. Buffering is managed by the memory controller and all buffering durations are specified by the memory controller in the command frames.

We found that buffering results in a speed-up of 2 to 25% for memory system topologies with 4 and 8 DIMMs per channel. Again, most of these benefits arose from increasing the ability of the memory controller to move data out of the closest DIMM earlier. A memory controller that uses buffering and re-ordering of data returns further reduces memory latency by an additional 10%. The overall speed-up by using both optimizations is on the order of 2-25%, over the baseline system which only allows in order return of data and does not support buffering.

This dissertation is organized as follows. Chapter 2 describes the past work done in the memory system area both in academia and industry. Chapter 3 describes the evolution of memory architectures and describes in detail the FBDIMM memory architecture and protocol. Chapter 4 has a comparison of the characteristics of DDRx and FBDIMM systems. It also has detailed results and analysis of the behavior of FBDIMM memory systems as system configurations are scaled. Chapter 6 describes the optimizations that we explored to improve the average read latency of a FBDIMM memory system. Chapter 7 summarizes the final conclusions of this dissertation.

# **Chapter 2: Related Work**

Microprocessor speeds have tracked Moore's law [1], doubling every eighteen months, while DRAM speeds have increased at a more moderate rate of roughly 7% [2], doubling only every 10 years. The resulting gap, also termed the memory wall, increases at 50% every year. The chief consequence of this has been the development of techniques to reduce or hide memory latency.

At the architectural level these techniques including lock-up free caches [3], hardware and software pre-fetching [4, 5], speculative execution and multi-threading focus on tolerating memory latency. Burger et al. [6] demonstrated that the majority of these techniques lowered latency by increasing bandwidth demands. A later study which examined different DRAM architectures by Cuppu et al. [7] demonstrated that memory manufacturers were able to meet bandwidth demands but had not been able to tackle latency effectively.

### 2.1. Performance Optimizations for the Memory Sub-System

There have been several studies at the controller level which examine how to lower latency while simultaneously increasing bandwidth utilization. The focusses of these techniques have been lowering row-buffer miss rates by employing address mapping, memory request access reordering or split-transaction scheduling. Row-buffer misses are expensive, because conflicts can be resolved only after a precharge-activate sequence. Zhang et al [8] studied how address mapping can be used to lower row-buffer conflicts are reduced. The scheme attempts to distribute blocks that occupy the same cache set across multiple banks in the system, by xoring the lower page-id bits with the bank-index bits. Rixner et al [9]

studied how re-ordering accesses at the controller to increase row buffer hits can be used to lower latency and improve bandwidth for media processing streams. They studied several policies that re-ordered requests based on age, arrival order, type i.e. loads over stores and ratio of column to row accesses. [10] studied how such re-ordering benefitted from the presence of SRAM caches on the DRAM aka Virtual-Channel DRAM for web servers Takizawa et al.[11] proposed a memory arbiter that increased the bandwidth utilization by reducing bank conflicts and bus turnarounds in a multi-core environment. The arbiter reduces bank conflicts by reducing the priority of DRAM accesses that are to the same bank as the previously issued access or if the access direction (read or write) is different from that of the previously issued access.

Natarajan et al [12] studied how memory controller policies for row buffer management policies, including open page, closed page and delayed closed page policies and command scheduling impacts latency and sustained bandwidth. They show that access reordering with a closed page policy provides the best bandwidth and latency for DDR/DDR2 based systems. They also demonstrate in DDR/DDR2 that intelligent read-write switching is influential in reducing bus inefficiencies.

Wang [13] proposed a memory request re-ordering algorithm which focussed on increasing bandwidth utilization. The algorithm attempted to get around bus constraints like bus turnaround time, and DRAM constraints like row-activation windows. Shao et al [14] propose a burst reordering scheduling scheme to improve the system memory bus utilization. The scheme reorders memory requests, such that read accesses, that are addressed to the same row of the same bank are clustered together. Writes are typically delayed until the write queue is either full or hits a particular threshold size. When the latter occurs, the

scheduler piggybacks write transactions onto the ongoing burst by issuing a write transaction which is addressed to the currently open row. When the write queue is full, the scheduler issues the oldest write transaction in the system.

Lin et al [15] studied how memory controller based pre-fetching can lower the system latency in a system with an on-chip memory controller. Zhu et al [16], on the other hand studied how awareness of resource usage of threads in an SMT could be used to prioritize memory requests.

Cuppu et al [17] demonstrated that concurrency is important even in a uni-processor system, but split-transaction support would lower latency of individual operations. [18] studied how split-transaction scheduling in a multi-channel environment could be used to lower latency.

Intelligent static address mapping techniques [15] [8] have been used to lower memory latency by increasing row-buffer hits. The Impulse group at University of Utah [19] proposed adding an additional layer of address mapping in the memory controller. This mapping technique reduced memory latency by mapping non-adjacent data to the same cacheline and thus increasing cacheline sub-block usage. The mapping is handled by the memory controller with information from the operating system. They used this mapping in conjunction with a parallel vector access unit [20], which enabled the memory controller to encode multiple requests in a single command to improve bus utilization.

Shao et al. [21] proposed a bit-reversal address mapping scheme for SDRAM systems. The scheme reverses the 'v' highest address bits and uses these to map the rank bits, bank bits and part of the row address bits. They demonstrate that this scheme improves exe-

cution time by mapping the most likely changing bits to the column, rank and bank bits and by redistributing memory accesses to be equally distributed across all banks.

Mitra et al.[22] characterized the behavior of 3D graphics workloads to understand the architectural requirements for these applications. They explored the impact of using architectural optimizations such as active texture memory management, speculative rendering and dynamic tiling on the performance of graphics applications. In addition they characterized the memory bandwidth requirements for these applications.

Embedded system controllers used in media systems have to provide high bandwidth utilization for the media and signal processing workloads while simultaneously providing low latency service to on-chip processing elements. Harmsze et al [23] proposed a solution to this problem in which they allocate fixed scheduling intervals to continuous streams and any additional slack time at a higher priority to CPUs and peripherals. This scheme was used in conjunction with on-chip buffering to provide compile-time guarantees of performance. This scheme does not take into account the state of the underlying DRAM. Lee et al. [24, 25] proposed a memory controller design that used a layered architecture, with a layer dedicated to DRAM management, QoS scheduling and address generation for continuos streams requestors to solve the same problem. The DRAM management layer generated the DRAM command stream required to process an actual request. As in earlier work, the DRAM layer designed a schedule that takes into account bank conflicts, bus turnaround times etc. In addition, the Quality of Service Access layer provided the DRAM layer with information regarding the priority of a given request which is taken into account to build the schedule. The QoS Access layer sends the DRAM layer information whether a given access is latency-sensitive, bandwidth sensitive or neither. Like Harmsze et al, they provide fixed bandwidth to a bandwidth sensitive stream, but unlike them they build in pre-emptive mechanisms which allows the scheduler to pre-empt a bandwidth-sensitive stream when a latency sensitive requestor makes a request.

Nesbit et al.[26] proposed a fair queueing memory controller scheduling algorithm targeted for CMP systems. The controller allocates memory bandwidth to each thread based on the threads memory utilization. Excess bandwidth is then distributed across threads that have consumed less bandwidth in the past cycle. This guarantees that any malicious thread does not succeed in a denial of service attack on the machine.

#### 2.2. Power Management

System growth in combination with device trends together have led to more and more devices being squeezed together on smaller and smaller areas [1]. This, in combination with speeds of operation etc., has resulted in growing power consumption. To effectively tackle this power consumption, most system components, including processors, disks and memory are capable of switching into low-power modes.

In the case of the memory system, power modes are available in nearly all DRAMs e.g. RDRAM, SDRAM, DDR/2. In DRAMs, a large portion of the power is drawn by the I/O circuitry, PLLs, on-chip registers. The low power modes disable this circuitry. Inter-node transitions take non-zero time, with the transition from low power modes to high power modes taking longer than transitions from high power modes to low power ones.

Rambus' RDRAM, for instance, supports four operating modes, in order of decreasing power consumption, active, standby, nap and idle. The granularity of control for power is at the level of an individual device or chip. The SDRAM family also offers power modes which are activated at the rank level. DDR2 SDRAM has a low power state- power down

that is reached by disabling the clock enable (CKE) input. Depending on whether banks are precharged or active, the power-down savings are different. Additional power consumption determining factors are DIMM activity, such as bank activation, read and write operations, refresh etc.

Delaluz et al [27] also examined how to control DRAM power consumption for an RDRAM system. They examined how the compiler could insert directives to transition the DRAM into the appropriate power state based on profiling information. They also examined how to reorder array accesses and how to cluster arrays with similar access patterns together to reduce power consumption. They studied some hardware-based techniques that were threshold monitoring or history based techniques and found that these performed better because compiler-based techniques tended to be more pessimistic and lacked the detailed runtime information.

In a follow-up paper [28], they examined how operating system directed power management of the memory system could be beneficial. They observed that the OS can keep track of which pages are required by a process, and enable the associated modules prior to its scheduling, while disabling the idle modules. Power savings using this technique did not scale well with the number of modules, because of the uniform distribution of a process' pages across multiple modules. As the number of active threads increased, the returns also diminished.

Lebeck et al [29] examined how software and hardware techniques can be used to reduce power consumption in the memory system. They used both execution-driven and trace-driven simulations to quantify the impact of both hardware-only and software/hardware schemes for a system using RDRAM memory. The hardware based schemes included

static schemes which transition the DRAM from one state to another after certain fixed threshold of time has passed, anddynamic schemes which examined distance between accesses to the same device before making a transitional decision. They studied how page allocation could be combined with the above schemes to improve energy reduction. Page allocation was such that the entire applications' data was allocated to one device at a time. Based on access patterns pages were migrated to the same chip, thereby allowing more devices to be powered down.

Huang et al [30] studied how a virtual memory manager could be used lower DRAM power consumption for a DRDRAM based system. They modified a virtual memory manager in Linux to perform page allocation in a more power efficient manner. The page allocation strategy used was similar to the sequential first-touch scheme used by Lebeck et al [29], but is enhanced to take into account DLL loading and shared pages. Unlike the earlier scheme, the operating system would issue instructions to the memory controller to activate a process' pages prior to its execution. The remainder of the DRAM sub system is kept in Nap mode. In a follow-up paper [31], they studied the impact of using power-aware virtual memory in a server with DDR based memory. Co-operative schemes perform marginally better than hardware-only schemes but use significantly lower resources to track page usage.

### **2.3.** Commercial Memory Controllers

The 21174 memory controller[32], which was designed for the 21164 and 21164PC Alpha workstations[33], was an SDRAM based memory controller. This controller represented the transition from the use of asynchronous DRAM architectures to synchronous DRAM architectures. The goals of the design were to eliminate the latency incurred due to

overheads like having to cross multiple chip domains. To do this, they used a novel memory sub-system design where the CPU was directly connected to the DRAM data bus, but the addressing and control was managed by the memory controller. The controller was designed for an open page system, and had a built-in 4-bit predictor per bank, which was used to determine whether the next access will be a hit or a miss. The prediction for a given predictor state was configured using a 16-bit software controlled register. They noted that the performance improvement by using this predictor is substantial for a few applications.

The Intel 870[34] is a memory controller for the Itanium. It can support up to 4 channels each with 8 DDR ranks. The memory controller chip can be connected to 4 processors simultaneously. It has an on-chip scalability port that enables it to be connected to an additional 12 processors. The chipset supports memory access re-ordering policies which focus on taking advantage of row locality and read/write re-ordering to avoid the impact of bus turn around times. The chipset also has its own read caches that act as prefect buffers for controller level pre-fetching. Being a multi-processor memory controller, it has support for directory level cache coherence. Several chipsets can be connected via the scalability port to form a network of 16-way processor system. Communication on this network is high-speed serial packet based communication.

The Intel front-side bus architecture has the processor communicating to the Northbridge chipset and cores via a fast, wide, shared bus. The northbridge chip, which was mainly the off-chip memory controller and cache coherence controller, is connected to the I/O controller, the AGP and the memory channels. With the trends towards increased integration, Intel first moved the graphics controller onto the chip-set[35]. More recently, the Intel 5000 series memory controller, (code-named *Blackford*), that is designed for dual-core

and quad-core chips, takes this integration process further by moving the PCI Express controller onto the chipset [36]. The Blackford chipset supports 2 logical channels of FBDIMM memory (4 physical channels), that are referred to as "branches". The chipset supports interleaving of cachelines across channels, ranks and banks. To provide increased RAS (Reliability, Availability and Serviceability), the memory is stored with ECC and the memory controller supports scrubbing i.e. periodically reading back memory and checking that it is correct. Both the PCI-express and FBDIMM channel are protected by CRC due to the higher transfer rates.

The increased integration of platform level components has resulted in the moving of the memory controller on-chip for both IBM's Power 5 [37] and AMD Opteron processors [38, 39]. Both these chips support a dual-channel, 16-byte memory channel interface and reduce memory latency by eliminating a chip domain crossing. In the past, on-chip memory controllers have been built for the Sun Sparc 5, which used a simple 1 level caching hierarchy and an on-chip memory controller to reduce memory access overheads. Intel is expected to follow this trend with the *Nehelam* processor.

### 2.4. Processor-in-Memory Architectures

Traditionally complex OOO processors have been built to hide the memory latency. These processors use sophisticated techniques such as out-of-order execution and speculation to hide this latency. One requires large memories to keep these complex OOO processors busy. As the memory hierarchy gets more complex, the distance between the CPU and memory increases. Saulsbury et al.[40] proposed moving away from CPU-centric design to reduce the impact of the memory wall. They proposed bringing the processor and memory closer by moving the processor onto the DRAM chip.

The Berkeley IRAM[41, 42, 43, 44] project studied how to merge the processor and DRAM onto the same chip. They demonstrated how this could improve memory access latency, available bandwidth to the processor, overall energy efficiency and cost savings. Memory latency was reduced by redesigning the memory and allowing the processor to get data from accesses to rows which are closer to the processor earlier than those which were further away. This is unlike what is done in conventional DRAM chips. Energy reductions are achieved at comparable performance due to the lower cost of a DRAM access as compared to the an SRAM access. Further, due to the larger density of DRAM, the number of off-chip accesses are reduced resulting in an additional energy savings [44]. System cost reductions are achieved by reducing the number of chips on a mother board.

Vector IRAM[45, 46, 47] is an architecture that combines vector processing and IRAM to meet the demands of multimedia processing, with high energy efficiency. The vector IRAM processor comprises of an in-order superscalar core with one level of cache, a eight pipeline vector execution unit and several banks of memory. Code written for this architecture had to be compiled by a vectorizing compiler[46, 48] which was designed to compile code such that it took advantage of the on-chip memory bandwidth.

Another approach has been the FlexRAM architecture [49, 50] which is implemented on Merged Logic DRAM chips. The architecture comprises of many simpler processing elements each with a DRAM bank. Each compute element is restricted to access its own DRAM bank and that of its immediate neighbors. A larger processor element on the chip manages the execution of tasks on the simpler compute elements and the communication between non-adjacent members. The FlexRAM chip in turn can be connected onto any commodity memory interconnect. Cache coherence is managed either by the programmer

or by using a directory based shared memory controller[51]. Programming for this architecture is made easier by the use of a special language and compiler support to automatically layout the code across the different compute elements[52, 53].

Some of the issues with building logic on DRAM technology [43] is that the latter has been optimized for small size and low leakage rather than speed. Further, the number of layers available in the two fabrication processes differ. The packaging used in DRAM chips is designed to dissipate significantly lower power (on the order of Watts) than that used by processors (can dissipate on the order of tens of watts). Due to the merging of logic and DRAM on the same chip also increases testing time.

The third approach proposed has been to use active pages[54, 55, 56], a page-based model of computation that associates simple functions with each page of memory. Active Page architectures are different from the previous two proposals since they are used to enhance performance of the conventional processor-memory architecture and not replace them, making it easier to adapt. Using active pages does not require the memory interface to be changed. Active Page data is modified with conventional memory reads and writes; Active Page functions are invoked through memory-mapped writes. Synchronization is accomplished through user-defined memory locations. Finally, Active Pages can exploit large amounts of parallelism by being able to support simultaneous computations to each of the pages in memory.

An alternate approach to reduce the distance between the processor and DRAM is to use a stacked micro-architecture. Black et al.[57] proposed a 3D die-stacked micro-architecture, where the DRAM is stacked on the CPU, thereby reducing memory latency and

increasing bandwidth. Further, they demonstrate that this is a more power efficient architecture since it reduces the off-chip bus lengths.

#### 2.5. Split-Transaction Buses

Shared buses used in multi-processor architectures are either single-transaction or split-transaction buses[58]. A single-transaction bus, also known as a circuit switched bus, permits only a single operation at a time, keeping the bus unavailable during the period when a read request is being serviced by the memory. A split-transaction bus permits multiple transactions to be outstanding by splitting each read request into two parts. First, a read request is followed by a release of the bus. Later, when the memory is prepared to return the result, it again arbitrates for the bus, acquiring it just long enough to send the requested data to the processor.

The split-transaction bus may be further refined by whether or not results are returned in the same order that they are requested. An in-order split-transaction bus always requires that read requests be completed in the same order in which they are initiated, while an out-of-order split-transaction bus places no restriction on the ordering of read requests. Typically, split-transaction buses may have a limit on the number of concurrent outstanding requests permitted

The HP Runaway Bus [59] was a split-transaction, time-multiplexed bus that was used in one-way to four-way SMP systems. It significantly improved bus utilization over a single-transaction bus. The bus supported multiple outstanding split transactions from each bus module, predictive flow control, a pipelined arbitration scheme and a snoopy coherence protocol. The bus protocol used master IDs and transaction IDs to tag every transaction.

These were transmitted in parallel with the address and the returning data, thereby ensuring that tag transmission did not contribute to overall latency.

Bus protocol design is also an important area of study in system-on-chip designs. Several protocols have been proposed to handle this problem including the AMBA bus protocol [60], the CoreConnect bus architecture [61], the Open Core protocol standard [62] by industry and others in academia including the LOTTERY bus [63] and the SAMBA protocol [64]. All these protocols use split transaction buses to improve bus utilization. The Samba protocol [64] attempts to improve fabrication delays in a split transaction bus system by explicitly defining request phases and response phases. The latter can be used by any module which does not share the same bus segment as the arbitration winner.

The concepts of using a split-transaction have also been explored in memory systems by Cuppu et al. [17, 65]. Cuppu et al. demonstrated how interleaving read and write data on the same bus can be used to improve bus utilization and overall system performance. Zhu et al [18] studied how splitting a memory request into multiple DRAM requests can be used to lower overall latency.

# **Chapter 3: Background**

This chapter provides an overview of the workings of the memory system hierarchy and the operational parameters available to the designer. The chapter also delves into the main trends prevalent in the memory system industry. It describes the evolution of DRAM architecture, from asynchronous architectures used in the early 90's to the current day synchronous dual data-rate devices and finally ends up with a detailed description of the FBDIMM memory architecture and protocol.

### 3.1. Memory Request Overview

Figure 3.1 illustrates the life of a memory request, right from its issue at the processor core, to its subsequent dispatch to the memory system and its completion in a uni-processor environment. Memory requests are issued by the core to handle load or store instructions and

igure 3.1. Abstract Illustration of Data being obtained from memory for a Load struction [10].

| Device configuration | 16 Meg x 16        |

|----------------------|--------------------|

| Configuration        | 4 M x 16 x 4 banks |

| row addressing       | 8K (A0 - A12)      |

| bank addressing      | 4 (BA0, BA1)       |

| column addressing    | 512 (A0- A8)       |

32 bit physical address (byte addressable)

**Figure 3.2. Address Mapping.** The figure illustrates the address mapping scheme employed in a memory controller using DRAMs with the configuration in the table above. The device configuration influences how many bits are required to identify the address location. The system has one channel (hence no bits are allocated to the channel), four ranks of memory of the type specified in the table.

ALU instructions which use memory-based operands. If the request cannot be fulfilled from the processor's caches, a request is sent to memory controller.

Address Mapping: One of the first steps in processing a request is to do a mapping from the physical address space to the DRAM layout. The memory controller uses a fixed memory address mapping policy to do this mapping. An address location in DRAM is determined by a channel ID, a rank ID, a bank ID, a row ID and a column ID. The address mapping policy determines which bits of the physical address are used to determine the various DRAM specific IDs mentioned. Figure 3.2 illustrates how a address mapping policy determines the location of a given address in memory. Note, that since the system has only one channel, no address bits are allocated to the channel ID.

Address mapping policies are determined by the device configuration, system topology and row buffer management policies. The device configuration determines how many bits are allocated for the bank, row and column IDs. The system topology determines the layout of the ranks in the system, whether the ranks all exist on a single channel, multiple channels or multiple physical channels which are ganged to behave as a single logical channel.

Row buffer management policies are another important factor to consider when devising an address mapping policy. They influence which portion of the address bits to allocate to the various IDs. Typical row buffer management policies include the open page, closed page and auto page. An open page policy attempts to take advantage of the locality in a DRAM page, while a closed page policy is more common in systems where there is a little or no locality in the address stream. In an open page policy the row is opened and data is retained in the sense amps even after the transaction completes. The row is closed only when a new transaction which goes to another row in the same bank is scheduled. Thus, an address mapping policy for an open page system would try to capture this spatial locality. In a closed page system, the row is closed immediately upon the completion of a transaction and the banks are precharged. In such a system the address mapping policy will distribute adjacent addresses to different banks and ranks.

**Memory Transaction Scheduling:** Once the address translation is completed, the memory controller attempts to schedule the request to the DRAM. The scheduling policy of the controller and the state of the DRAM determines how long this process will take. For instance, the memory controller can select to re-order requests to obtain the most efficient

# Closed Page Policy IFETCH RAS CAS with Open Page Policy - Bank Conflict IFETCH PRECHARGE RAS CAS Open Page Policy - Bank Hit IFETCH CAS

**Figure 3.3. DRAM Commands associated with a transaction.** The figure illustrates the resulting DRAM command stream for an instruction fetch (IFETCH) memory transaction. The commands scheduled are dependent on the state of the DRAM i.e. if the required row is open or not and the row buffer management policy in use.

bandwidth utilization. Based on the reordering policy used, priority can be given to reads over writes or to accesses that are mapped to an open row-buffer or to the oldest transaction etc. The transaction waits in the transaction queue waiting for its turn to be scheduled.

Scheduling to the DRAM: In this stage, the memory controller sends the associated DRAM commands to read or write the data. The transaction is broken down into a sequence of DRAM commands determined by the row buffer management policy and the state of the DRAM. Figure 3.3 demonstrates how these factors determine the exact DRAM command sequence used by an instruction fetch (IFETCH) transaction. In the closed page scheme, where the banks are by default precharged the memory controller has to first open the required row using a row activate command or RAS. The controller than issues a column access command or CAS to the DRAM which initiates a data burst from the DRAM. The controller restores the DRAM to its default state with a precharge command. In a system employing the open page policy, the relevant bank will be open but the open row may or

may not be the row of interest. Depending on whether the relevant row is open (bank hit) or another row is open (bank conflict), the command sequence changes as illustrated.

Following the receipt of the relevant data, the memory controller sends this back to the processor, thereby completing the memory request.

# 3.2. DRAM Architectures over time

This section goes over the various types of DRAM and their features. Performance improvements in DRAM have been less influenced by advances in the speed of DRAM circuitry, than by higher level structural and interface changes. Bandwidth gains have been traditionally achieved by structural modifications to the interface. Recently, several DRAM manufactures have attempted to tackle the latency problem, by proposing radical changes to the underlying core architecture. Figure 3.4 illustrates the evolution in DRAMs, the changes between successive generations and which performance bottleneck the modifications attempt to address [10].

Conventional DRAM: forms the basis of modern day DRAMs with the addressing mechanism still in vogue, with minor changes. The address bus is multiplexed between row and column components. The multiplexed address bus uses two control signals of the row and column address strobe signals, RAS and CAS respectively which cause the DRAM to latch the address components. The row address causes a complete row in the memory array to propagate down the bit lines to the sense amps. The column address selects the appropriate data subset from the sense amps and causes it to be driven to the output pins.

**Figure 3.4. Evolution of the DRAM.** The figure illustrates the trends in DRAM architectures from the basic DRAM to its modern day avatars. It shows the chief factors influencing the trends.

**Fast Page Mode DRAM (FPM DRAM):** Fast-Page Mode DRAM implements *page mode*, an improvement on conventional DRAM in which the row-address is held constant and data from multiple columns is read from the sense amplifiers. The data held in the sense amps form an open page that can be accessed relatively quickly. This speeds up successive accesses to the same row of the DRAM core.

**Extended Data Out DRAM (EDO DRAM):** Extended Data Out DRAM, sometimes referred to as hyper-page mode DRAM, adds a latch between the sense-amps and the output pins of the DRAM. This latch holds output pin state and permits the CAS to rapidly de-assert, allowing the memory array to begin precharging sooner. In addition, the latch in the output path also implies that the data on the outputs of the DRAM circuit remain valid longer into the next clock phase.

Synchronous DRAM (SDRAM): Conventional, FPM, and EDO DRAM are controlled asynchronously by the processor or the memory controller; the memory latency is thus some fractional number of CPU clock cycles. An alternative is to make the DRAM interface synchronous such that the DRAM latches information to and from the controller based on a clock signal. SDRAM devices typically have a programmable register that to specify the burst length. The advantages include the elimination of the timing strobes and the availability of data from the DRAM each clock cycle. The underlying architecture of the SDRAM core is the same as in a conventional DRAM.

Enhanced Synchronous DRAM (ESDRAM): Enhanced Synchronous DRAM is an incremental modification to Synchronous DRAM that parallels the differences between FPM and EDO DRAM. First, the internal timing parameters of the ESDRAM core are faster than SDRAM. Second, SRAM row-caches have been added at the sense-amps of each bank. These caches provide the kind of improved intra-row performance observed with EDO DRAM, allowing requests to the last accessed row to be satisfied even when subsequent refreshes, precharges, or activates are taking place.

**Dual Data Rate Memory (DDR):** DDR has the same basic architecture as SDRAM. To achieve higher bandwidth rates of 200 to 400 Mbps, data is transferred at both edges of the clock. The higher clock speeds are achieved by multi-plexing the I/O buffers and not increasing the core speeds. A source-synchronous signal, DQS is added to enable data transfer. The DQS is generated by the component sending the data i.e. by the memory controller during a write and the DIMM during a read. The DQS is edge aligned for read data and centre aligned for write data.

Dual Data Rate Memory (DDR2): This is the next generation DDR DRAM with a few significant differences. DDR2 achieves higher data-rates lying between 400 to 667 Mbps. The number of DRAM banks is four for all devices except those with capacities greater than 1Gb. The uni-directional DQS signal has been replaced with a differential data strobe. DDR2 also introduces the concept of posted-CAS i.e. the memory controller can issue a RAS and CAS in subsequent cycles. The DRAM processes the CAS only after a fixed programmable period also known as the additive latency. The core operating voltage of DDR2 has been significantly lowered thereby lowering overall power consumption. Finally DDR2 adds on-die termination (ODT) to the data I/O pins. This feature is controlled by the ODT pin and consumes additional power when activated. Typically, on-die termination is only enabled to terminate write data to the DRAM or to terminate read data from a different DRAM.

Virtual Channel SDRAM (VCSDRAM): Virtual Channel SDRAM, designed by NEC, also contains SRAM caches. But the caches are not really buffers for the sense amps like ESDRAM. VC SDRAM contains 16 virtual channels, or 16 1 KB SRAM caches. While the ESDRAM module takes care of the "caching" internally, the VC SDRAM caches are managed by the chipset. This results in two important consequences. First, VC SDRAM will only work properly when paired with a chipset that supports it. Additionally, the performance of VC SDRAM will depend tremendously on the quality of the chipset's implementation.

Fast Cycle RAM (FCRAM): FCRAM (Fast Cycle RAM) was developed by Fujitsu which seeks to lower latency by changing the DRAM core. The process includes core segmentation and pipeline operations. This new structure has some advantages including the