#### ABSTRACT

Title of Dissertation:COMMUNICATION-DRIVEN CODESIGN<br/>FOR MULTIPROCESSOR SYSTEMSDissertation directed by:Neal Kumar Bambha, Doctor of Philosophy, 2004Dissertation directed by:Professor Shuvra S. Bhattacharyya<br/>Department of Electrical and Computer Engineering

Several trends in technology have important implications for embedded systems of the future. One trend is the increasing density and number of transistors that can be placed on a chip. This allows designers to fit more functionality into smaller devices, and to place multiple processing cores on a single chip. Another trend is the increasing emphasis on low power designs. A third trend is the appearance of bottlenecks in embedded system designs due to the limitations of long electrical interconnects, and increasing use of optical interconnects to overcome these bottlenecks. These trends lead to rapidly increasing complexity in the design process, and the necessity to develop tools that automate the process. This thesis will present techniques and algorithms for developing such tools.

Automated techniques are especially important for multiprocessor designs. Programming such systems is difficult, and this is one reason why they are not as prevalent today. In this thesis we explore techniques for automating and optimizing the process of mapping applications onto system architectures containing multiple processors. We examine different processor interconnection methods and topologies, and the design implications of different levels of connectivity between the processors.

Using optics, it is practical to construct processor interconnections having arbitrary topologies. This can offer advantages over regular interconnection topologies. However, existing scheduling techniques do not work in general for such arbitrarily connected systems. We present an algorithm that can be used to supplement existing scheduling techniques to enable their use with arbitrary interconnection patterns.

We use our scheduling techniques to explore the larger problem of synthesizing an optimal interconnection network for a problem or group of problems.

We examine the problem of optimizing synchronization costs in multiprocessor systems, and propose new architectures that reduce synchronization costs and permit efficient performance analysis.

All the trends listed above combine to add dimensions to the already vast design space for embedded systems. Optimizations in embedded system design invariably reduce to searching vast design spaces. We describe a new hybrid global/local framework that combines evolutionary algorithms with problem-specific local search and demonstrate that it is more efficient in searching these spaces.

#### COMMUNICATION-DRIVEN CODESIGN

#### FOR MULTIPROCESSOR SYSTEMS

by

Neal Kumar Bambha

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2004

Advisory Committee:

Professor Shuvra S. Bhattacharyya, Chairman/Advisor Professor Gang Qu Professor K. J. Ray Liu Professor Joe Mait Professor Jeff Hollingsworth © Copyright by

Neal Kumar Bambha

2004

## DEDICATION

To my parents, and to Soraya, Valerie, and Michael

#### ACKNOWLEDGEMENTS

I wish to thank my advisor, Professor Shuvra Bhattacharyya, for his guidance and encouragement in this endeavor. His enthusiasm for research and his insights into many different problems have motivated me greatly during the course of this work.

I would also like to acknowledge the support of the Army Research Laboratory, and to thank Dr. Paul Amirtharaj and Dr. Joe Mait for their encouragement.

It has been a pleasure to interact with many students in the DSPCAD group, including Nitin, Vida, Mukul, Ming-Yung, Bishnupriya, Ozkan, Ankush, and Mainak. Our collaborations and discussions have strengthened this thesis and enriched my experience here.

Finally, I would like to thank my family for their love, support, and patience during these years while I have focused on my studies.

#### TABLE OF CONTENTS

| Li | List of Figures |           |                                                        | ix |

|----|-----------------|-----------|--------------------------------------------------------|----|

| 1  | Introduction    |           |                                                        | 1  |

|    | 1.1             | Multip    | processor Embedded Systems                             | 2  |

|    | 1.2             | Contri    | butions of this Thesis                                 | 4  |

|    |                 | 1.2.1     | Contention Analysis in Shared Bus Systems              | 5  |

|    |                 | 1.2.2     | Architectures Designed for Optically Connected Systems | 6  |

|    |                 | 1.2.3     | Contention Analysis in Optically Connected Systems     | 6  |

|    |                 | 1.2.4     | Scheduling for Arbitrarily Connected Systems           | 6  |

|    |                 | 1.2.5     | Synthesizing an Optimal Interconnection Network        | 7  |

|    |                 | 1.2.6     | Simulated Heating                                      | 7  |

| 2  | Elec            | ctronic l | Design Automation for Embedded Systems                 | 9  |

|    | 2.1             | Datafl    | ow                                                     | 9  |

|    | 2.2             | Archit    | tectural Synthesis                                     | 14 |

|    | 2.3             | Sched     | uling                                                  | 19 |

|    | 2.4             | Model     | ling Self-Timed Execution                              | 22 |

|    | 2.5             | Interco   | onnect Synthesis                                       | 26 |

| 3  | Syst            | tem Arc   | chitectures for Multiprocessor Embedded Systems        | 27 |

|   | 3.1                                                                                                                | Multip                                                                                          | rocessor Program Execution Models                                                       | 28                                                                                                         |

|---|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   | 3.2                                                                                                                | .2 Architectures Based on Dataflow                                                              |                                                                                         |                                                                                                            |

|   | 3.3                                                                                                                | Archite                                                                                         | ectures Utilizing Optical Interconnects                                                 | 32                                                                                                         |

|   |                                                                                                                    | 3.3.1                                                                                           | Optical Interconnect Technology                                                         | 32                                                                                                         |

|   |                                                                                                                    | 3.3.2                                                                                           | Prototype Optically-Connected Systems                                                   | 35                                                                                                         |

|   | 3.4                                                                                                                | Optical                                                                                         | lly Connected System on Chip                                                            | 37                                                                                                         |

|   |                                                                                                                    | 3.4.1                                                                                           | Global/Local Partitioning                                                               | 38                                                                                                         |

|   |                                                                                                                    | 3.4.2                                                                                           | Typical Numbers                                                                         | 42                                                                                                         |

|   | 3.5                                                                                                                | Modeli                                                                                          | ng Optically-Interconnected Systems with Synchronization Graphs                         | 43                                                                                                         |

|   |                                                                                                                    | 3.5.1                                                                                           | SLOT Architecture                                                                       | 44                                                                                                         |

|   |                                                                                                                    | 3.5.2                                                                                           | Dedicated Channel Fiber WDM Architecture                                                | 46                                                                                                         |

|   |                                                                                                                    | 3.5.3                                                                                           | One Wavelength Per Processor                                                            | 47                                                                                                         |

|   |                                                                                                                    |                                                                                                 |                                                                                         |                                                                                                            |

| 4 | Cont                                                                                                               | tention                                                                                         | Analysis in Shared Bus Systems Utilizing the Period Graph                               | 50                                                                                                         |

| 4 | <b>Cont</b><br>4.1                                                                                                 |                                                                                                 | Analysis in Shared Bus Systems Utilizing the Period Graph<br>tion in Shared Bus Systems | <b>50</b><br>50                                                                                            |

| 4 |                                                                                                                    | Conten                                                                                          |                                                                                         |                                                                                                            |

| 4 | 4.1                                                                                                                | Conten<br>Constru                                                                               | tion in Shared Bus Systems                                                              | 50                                                                                                         |

| 4 | 4.1<br>4.2                                                                                                         | Conten<br>Constru<br>Fidelity                                                                   | tion in Shared Bus Systems                                                              | 50<br>52                                                                                                   |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                                                      | Conten<br>Constru<br>Fidelity<br>Using t                                                        | tion in Shared Bus Systems                                                              | 50<br>52<br>58                                                                                             |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                                          | Content<br>Constru-<br>Fidelity<br>Using to<br>Genetic                                          | tion in Shared Bus Systems                                                              | 50<br>52<br>58<br>62                                                                                       |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                                        | Content<br>Constru-<br>Fidelity<br>Using to<br>Genetic<br>Simula                                | tion in Shared Bus Systems                                                              | <ul> <li>50</li> <li>52</li> <li>58</li> <li>62</li> <li>63</li> </ul>                                     |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                           | Content<br>Constru-<br>Fidelity<br>Using to<br>Genetic<br>Simula<br>Results                     | tion in Shared Bus Systems                                                              | <ul> <li>50</li> <li>52</li> <li>58</li> <li>62</li> <li>63</li> <li>64</li> </ul>                         |

| 4 | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | Content<br>Constru-<br>Fidelity<br>Using to<br>Genetic<br>Simula<br>Results<br>Summa            | tion in Shared Bus Systems                                                              | <ul> <li>50</li> <li>52</li> <li>58</li> <li>62</li> <li>63</li> <li>64</li> <li>65</li> </ul>             |

|   | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | Content<br>Constru-<br>Fidelity<br>Using to<br>Genetic<br>Simula<br>Results<br>Summa<br>tention | tion in Shared Bus Systems                                                              | <ul> <li>50</li> <li>52</li> <li>58</li> <li>62</li> <li>63</li> <li>64</li> <li>65</li> <li>70</li> </ul> |

|   |     | 5.1.2    | Synchronization Constraints                          | 73  |

|---|-----|----------|------------------------------------------------------|-----|

|   |     | 5.1.3    | Ordered Transactions Graph                           | 75  |

|   | 5.2 | WDM      | Ordered Transactions                                 | 79  |

|   |     | 5.2.1    | Optical Components                                   | 84  |

|   |     | 5.2.2    | Transaction Ordering                                 | 86  |

|   |     | 5.2.3    | Experiments                                          | 90  |

| 6 | Sch | eduling  | for Arbitrarily Connected Systems                    | 96  |

|   | 6.1 | Implic   | ations of Increased Connectivity                     | 97  |

|   |     | 6.1.1    | Topology Graph                                       | 98  |

|   |     | 6.1.2    | Effect of Connectivity on a Simple Mapping Algorithm | 99  |

|   | 6.2 | Conne    | ction Topologies                                     | 99  |

|   | 6.3 | Conne    | ctivity and Scheduling Flexibility                   | 105 |

|   | 6.4 | Comp     | lexity of the Constraint Algorithm                   | 113 |

|   | 6.5 | Incorp   | orating Feasibility and Flexibility into Scheduling  | 114 |

|   | 6.6 | Schedu   | uling Experiments using Flexibility                  | 115 |

|   |     | 6.6.1    | Power Reduction with Single Hop Communication        | 118 |

|   | 6.7 | Summ     | ary of Flexibility Work                              | 119 |

| 7 | Syn | thesizin | g an Efficient Interconnect Network                  | 120 |

|   | 7.1 | Greed    | y Interconnect Synthesis Algorithm                   | 122 |

|   |     | 7.1.1    | Experiments with TPLA                                | 122 |

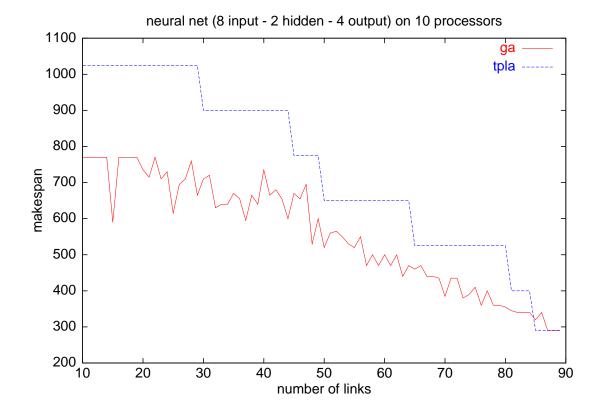

|   | 7.2 | Link S   | Synthesis using Genetic Algorithm                    | 124 |

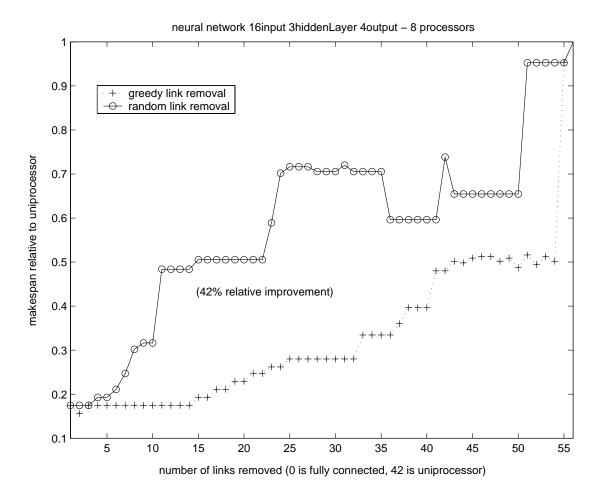

|   |     | 7.2.1    | Genetic Algorithm Overview                           | 124 |

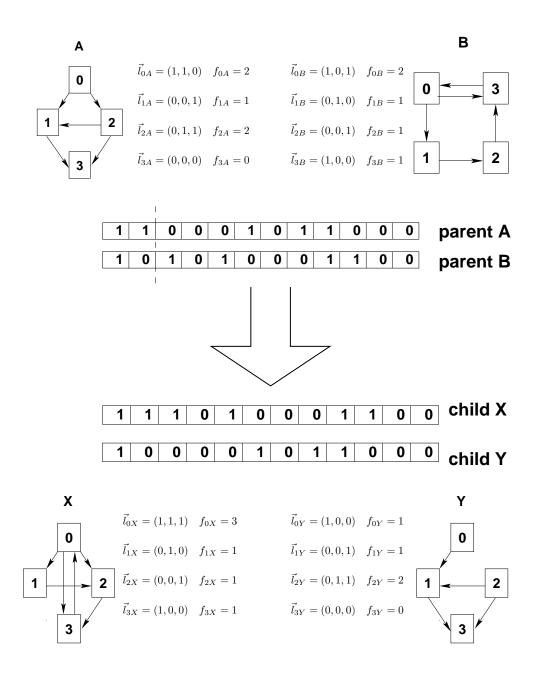

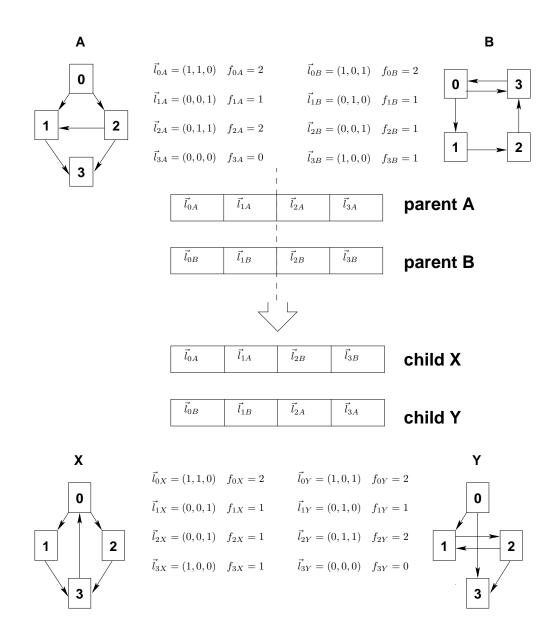

|   |     | 7.2.2    | Problem representation                               | 127 |

|   |     | 7.2.3    | Fanout Constraints                                   | 128 |

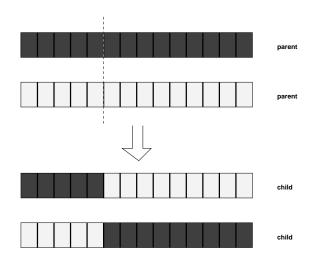

|   |      | 7.2.4    | Crossover and Mutation Operators                | 129 |

|---|------|----------|-------------------------------------------------|-----|

|   |      | 7.2.5    | Experiments                                     | 132 |

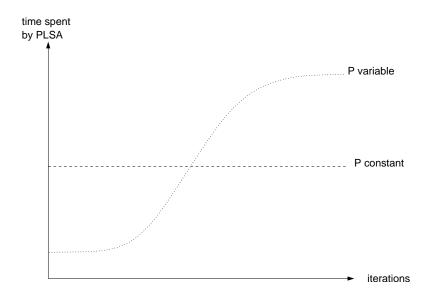

|   | 7.3  | Using    | Graph Isomorphism                               | 134 |

| 8 | Desi | gn Spa   | ce Exploration Using Simulated Heating          | 141 |

|   | 8.1  | Introdu  | uction                                          | 141 |

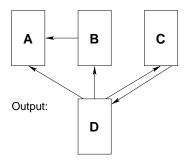

|   |      | 8.1.1    | PLSA for Voltage Scaling                        | 145 |

|   |      | 8.1.2    | PLSA for Interconnect Synthesis                 | 150 |

|   |      | 8.1.3    | PLSA for Ordered Transactions                   | 152 |

|   | 8.2  | Hybric   | d Global/Local Search Related Work              | 153 |

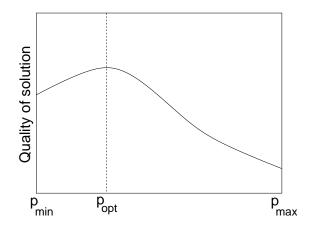

|   | 8.3  | Simula   | ated Heating                                    | 157 |

|   |      | 8.3.1    | Basic Principles                                | 158 |

|   |      | 8.3.2    | Optimization Scenario                           | 159 |

|   | 8.4  | Simula   | ated Heating Schemes                            | 163 |

|   |      | 8.4.1    | Static Heating                                  | 163 |

|   |      | 8.4.2    | Dynamic Heating                                 | 166 |

| 9 | Sim  | ulated I | Heating Experiments                             | 169 |

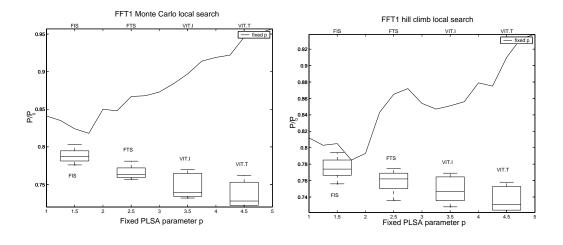

|   | 9.1  | Simula   | ated Heating for Voltage Scaling                | 169 |

|   |      | 9.1.1    | Voltage Scaling Problem Statement               | 170 |

|   |      | 9.1.2    | GSA: Evolutionary Algorithm for Voltage Scaling | 170 |

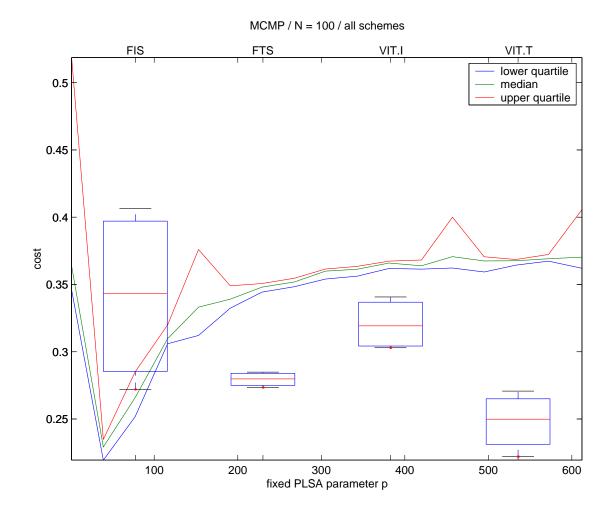

|   | 9.2  | Simula   | ated Heating for Memory Cost Minimization       | 172 |

|   |      | 9.2.1    | Background                                      | 172 |

|   |      | 9.2.2    | MCMP Problem Statement                          | 173 |

|   |      | 9.2.3    | Implementation Details for MCMP                 | 174 |

|   |      | 9.2.4    | GSA: Evolutionary Algorithm for MCMP            | 174 |

|         | 9.2.5           | PLSA: Parameterized CDPPO for MCMP                      | 175 |

|---------|-----------------|---------------------------------------------------------|-----|

| 9.3     | Simula          | ated Heating for Binary Knapsack Problem                | 176 |

|         | 9.3.1           | Implementation                                          | 177 |

| 9.4     | Experi          | ments                                                   | 178 |

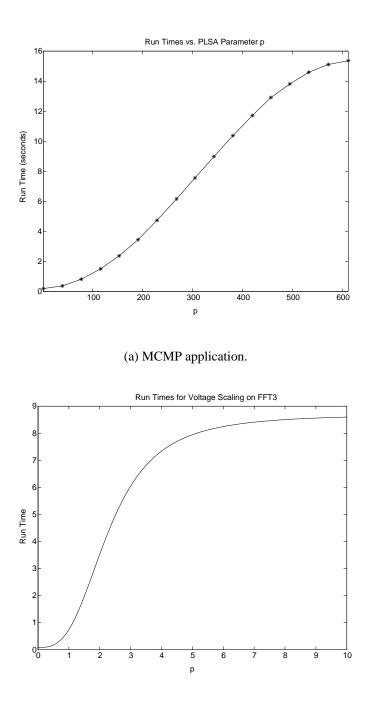

|         | 9.4.1           | PLSA Run-Time and Accuracy for Voltage Scaling and MCMP | 180 |

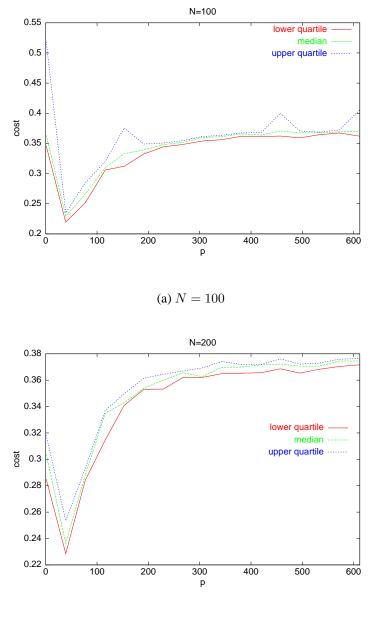

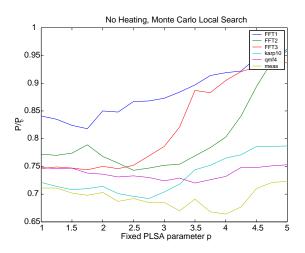

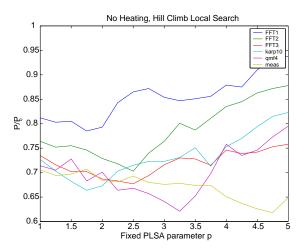

|         | 9.4.2           | Standard Hybrid Approach for Voltage Scaling and MCMP   | 180 |

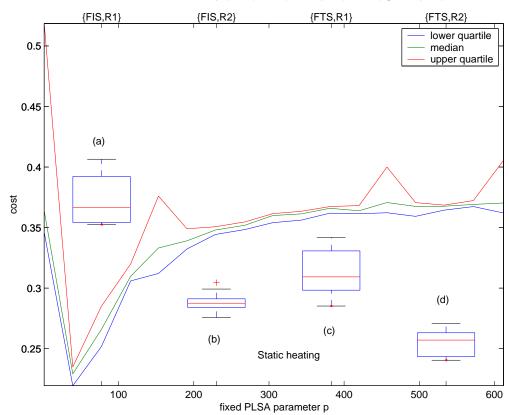

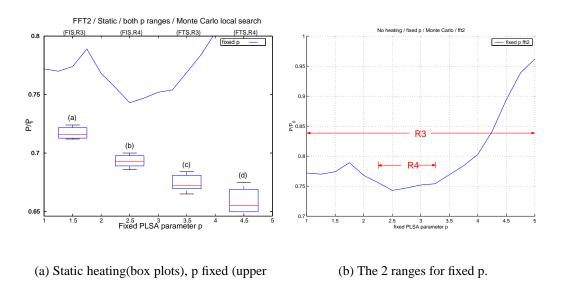

|         | 9.4.3           | Static Heating Schemes for Voltage Scaling and MCMP     | 183 |

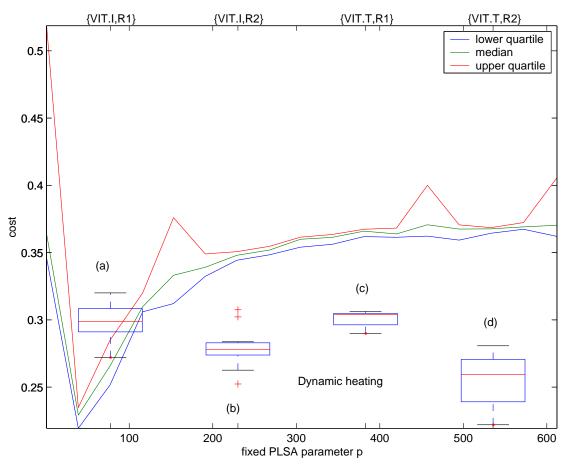

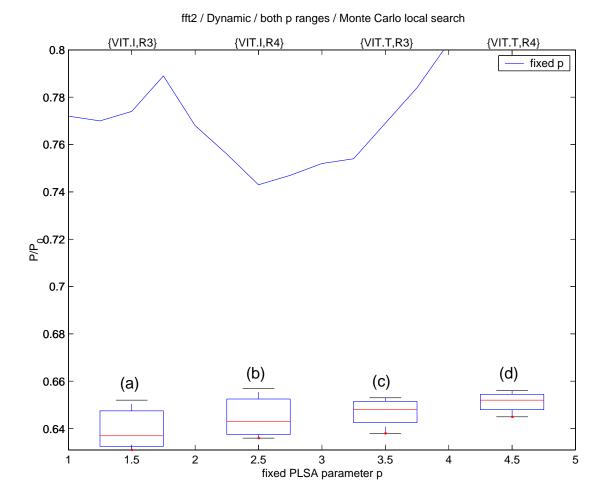

|         | 9.4.4           | Dynamic Heating Schemes for Voltage Scaling and MCMP    | 189 |

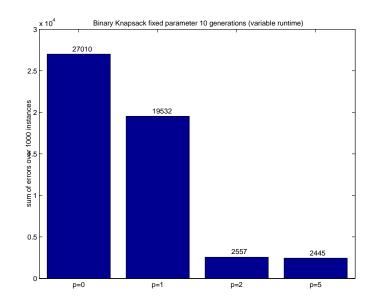

|         | 9.4.5           | Knapsack PLSA Run-Time and Accuracy                     | 189 |

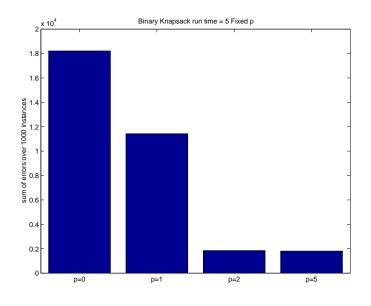

|         | 9.4.6           | Knapsack Standard Hybrid Approach                       | 195 |

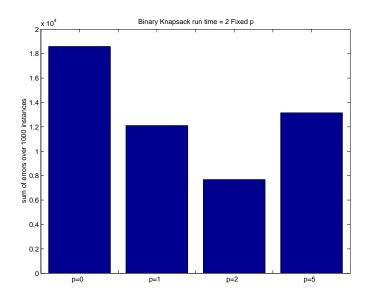

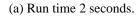

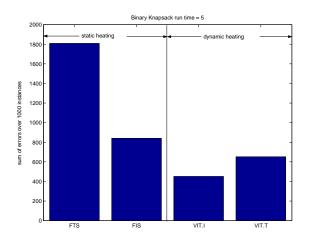

|         | 9.4.7           | Knapsack Static Heating Schemes                         | 195 |

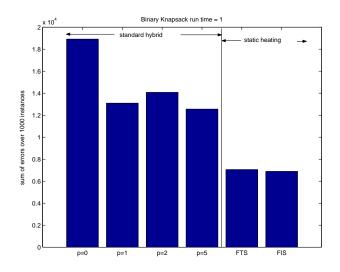

|         | 9.4.8           | Knapsack Dynamic Heating Schemes                        | 195 |

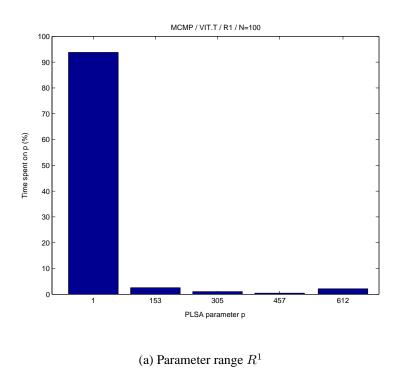

| 9.5     | Compa           | arison of Heating Schemes                               | 199 |

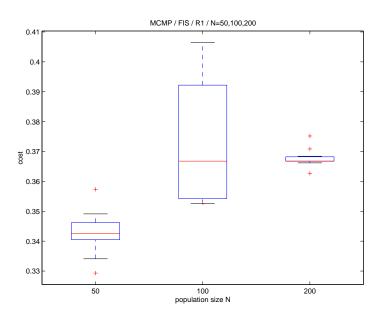

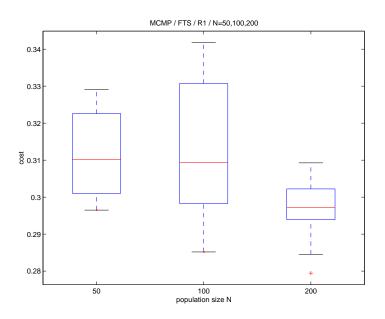

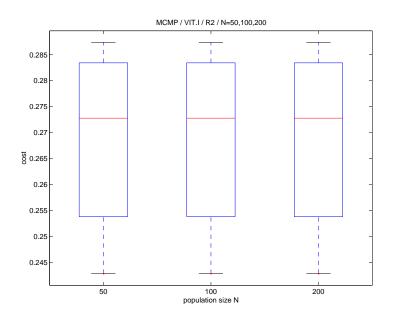

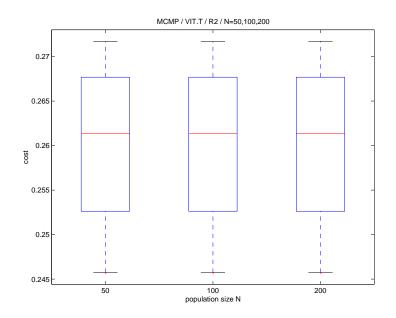

|         | 9.5.1           | Effect of Population Size                               | 201 |

| 9.6     | Discus          | sion                                                    | 206 |

| 9.7     | Conclu          | isions                                                  | 207 |

| 10 Con  | clusions        | s and Future Work                                       | 208 |

| Append  | lix             |                                                         | 212 |

| .1      | Rando           | m Graph Generation Algorithm                            | 212 |

| Bibliog | Bibliography 21 |                                                         |     |

### LIST OF FIGURES

| 2.1  | Marked Petri net.                                                      | 12 |

|------|------------------------------------------------------------------------|----|

| 2.2  | Example of a problem graph, an architecture graph, and a chip graph.   | 16 |

| 2.3  | Specification graph corresponding to example of Figure 2.2             | 16 |

| 2.4  | Example of an application graph and an associated self-timed schedule. | 20 |

| 2.5  | Partition/overhead trade-off                                           | 20 |

| 2.6  | Example of IPC graph                                                   | 24 |

| 3.1  | Shared-memory multiprocessor                                           | 29 |

| 3.2  | Distributed-memory multiprocessor                                      | 30 |

| 3.3  | Coarse-grain dataflow model                                            | 33 |

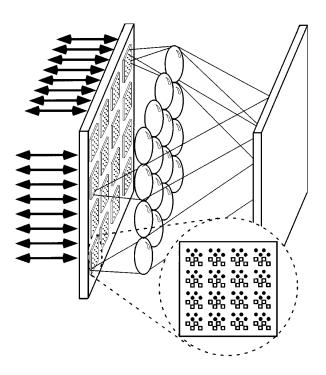

| 3.4  | FASTNet prototype                                                      | 36 |

| 3.5  | Schematic side view of FASTNet                                         | 39 |

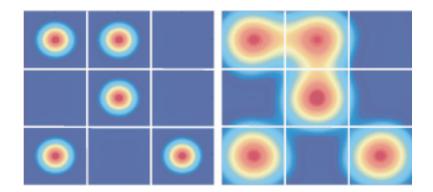

| 3.6  | Array of point source images                                           | 40 |

| 3.7  | Trade-offs in optical SoC                                              | 41 |

| 3.8  | Schematic of SLOT architecture                                         | 45 |

| 3.9  | Architecture for contention-free fiber-based SLOT                      | 47 |

| 3.10 | Architecture for wavelength ordered transactions                       | 48 |

| 4.1  | Schematic of a three processor shared bus architecture                 | 51 |

| 4.2  | Pseudocode for constructing the period graph.                          | 55 |

| 4.3  | An illustration of the period graph construct.        | 56  |

|------|-------------------------------------------------------|-----|

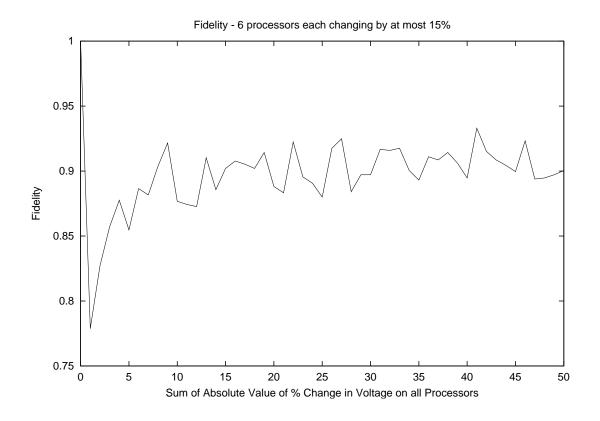

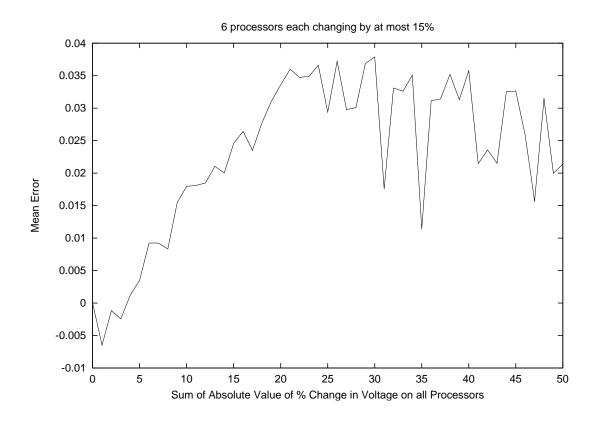

| 4.4  | Plot of fidelity of period graph estimator            | 60  |

| 4.5  | Average error of fidelity estimate                    | 61  |

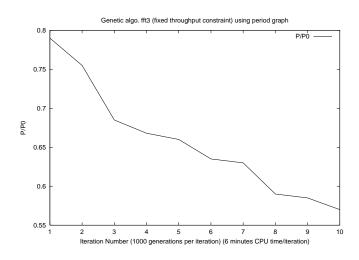

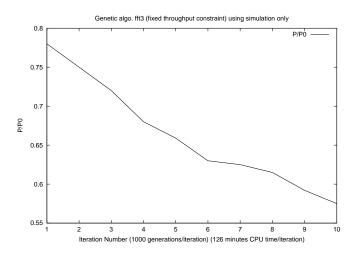

| 4.6  | Optimized power using period graph and simulation     | 66  |

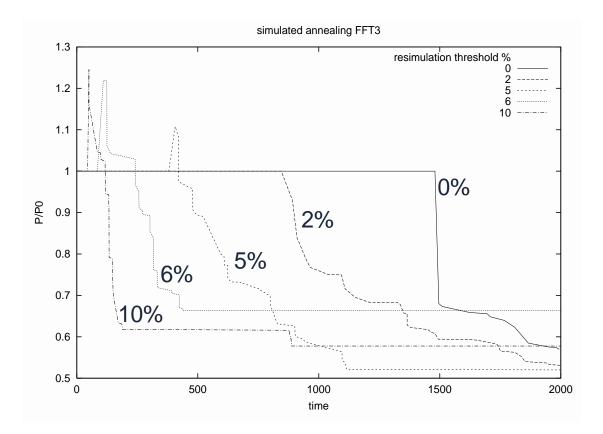

| 4.7  | Optimized power using simulated annealing             | 67  |

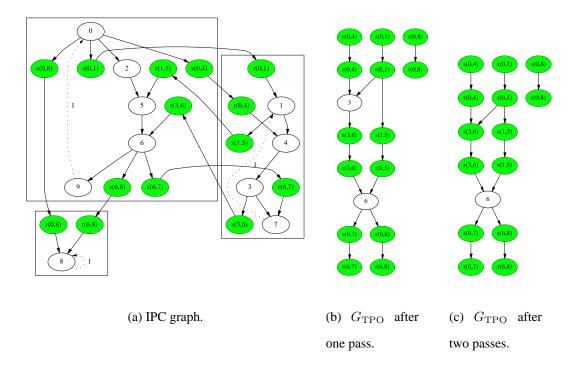

| 5.1  | Pseudo-code for generating TPO graph.                 | 76  |

| 5.2  | $G_{\mathrm{TPO}}$ after one and two passes           | 77  |

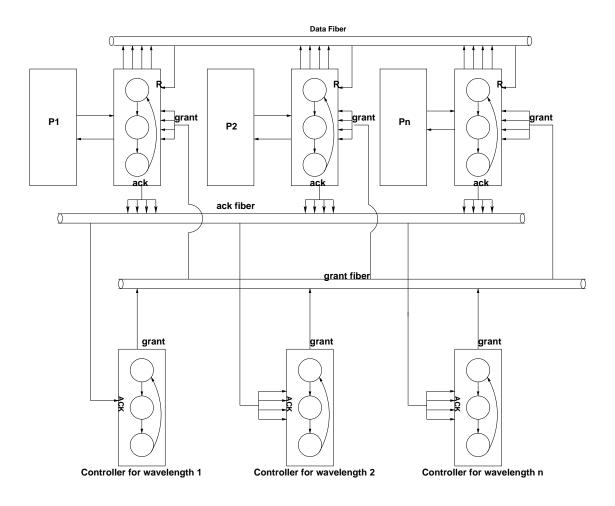

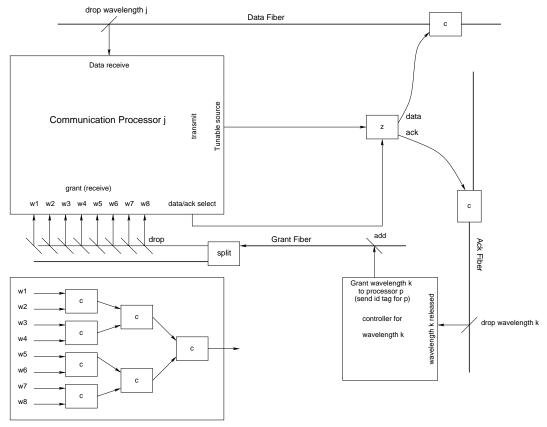

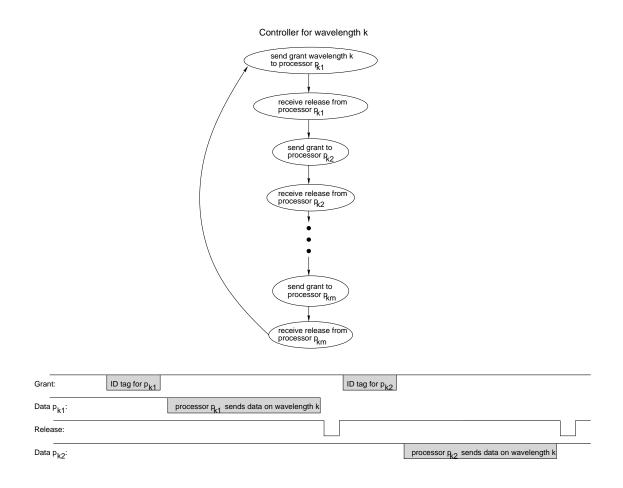

| 5.3  | Architecture for WDM OT                               | 81  |

| 5.4  | Details of WDM OT                                     | 82  |

| 5.5  | WDMOT signals.                                        | 83  |

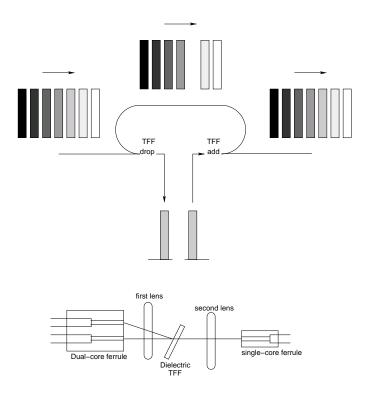

| 5.6  | OADM using thin film filter                           | 85  |

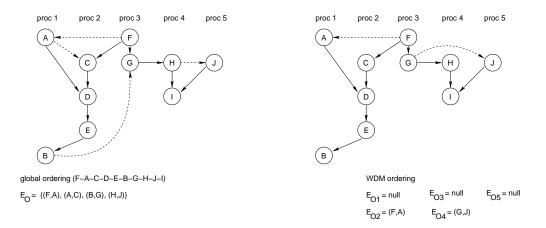

| 5.7  | WDM ordered transaction graph                         | 87  |

| 5.8  | Function chooseCommunicationActor                     | 88  |

| 5.9  | TPO heuristic [62]                                    | 89  |

| 5.10 | WDM ordered transactions algorithm.                   | 90  |

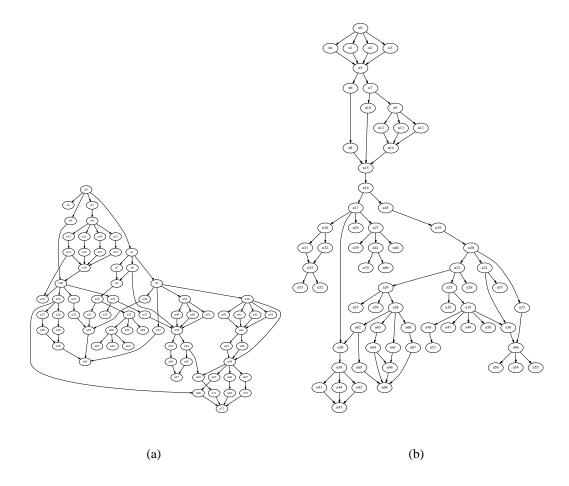

| 5.11 | Example of random graph.                              | 91  |

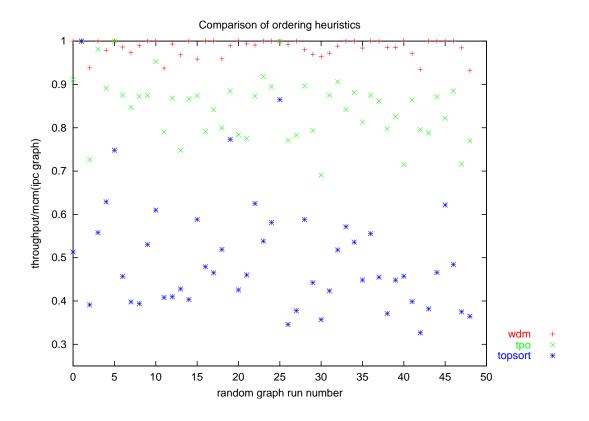

| 5.12 | Experiments with different ordering heuristics        | 92  |

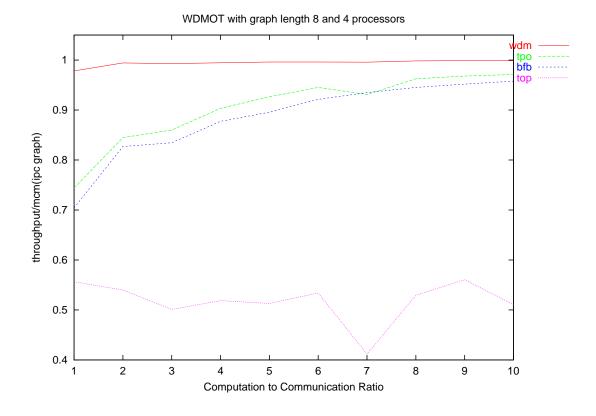

| 5.13 | Experiments with different ordering heuristics        | 94  |

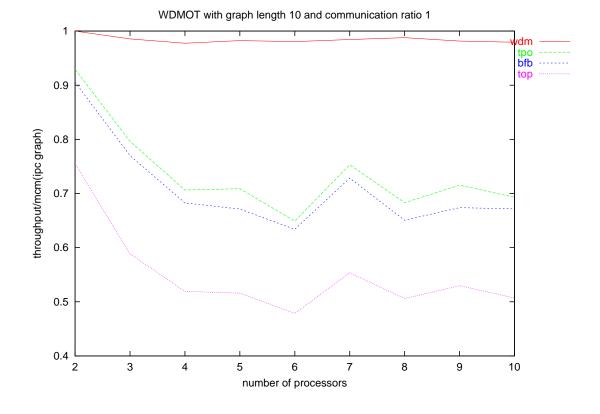

| 5.14 | WDMOT for varying number of processors.               | 95  |

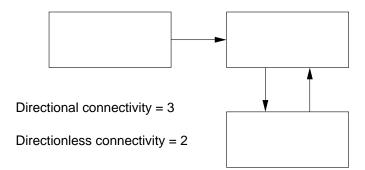

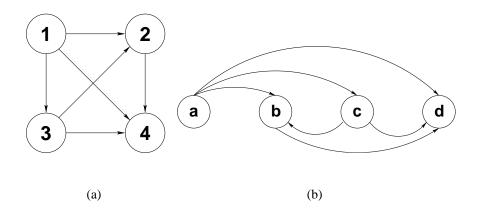

| 6.1  | Example of directional and directionless connectivity | 98  |

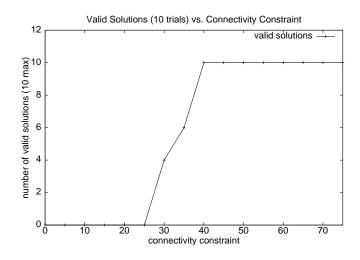

| 6.2  | Impact of Connectivity on Search Efficiency.          | 100 |

| 6.3  | Impact of Connectivity on Performance.                | 100 |

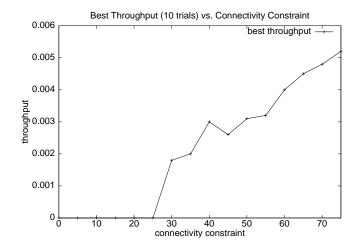

| 6.4  | An irregular topology                                 | 102 |

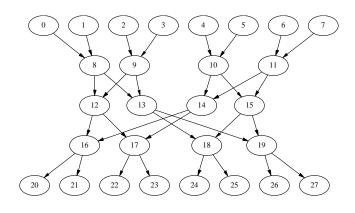

| 6.5  | FFT1 application graph                                | 103 |

| 6.6  | Single-hop topology                                                |

|------|--------------------------------------------------------------------|

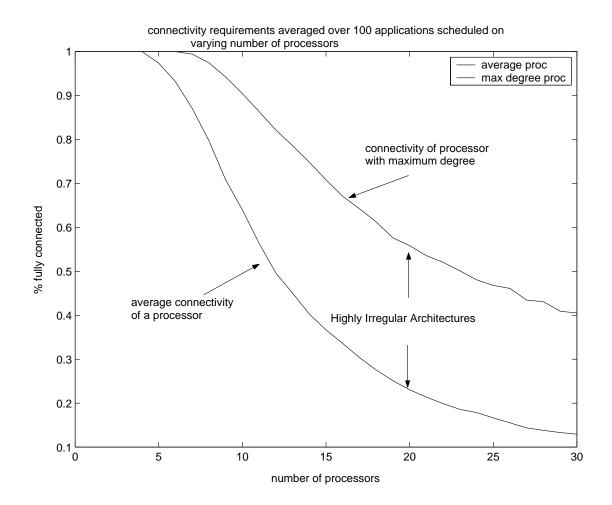

| 6.7  | Connectivity requirements of 100 benchmark applications 104        |

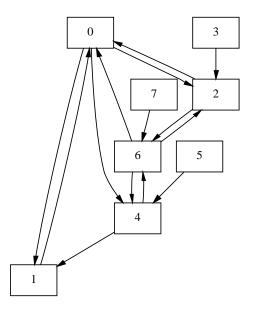

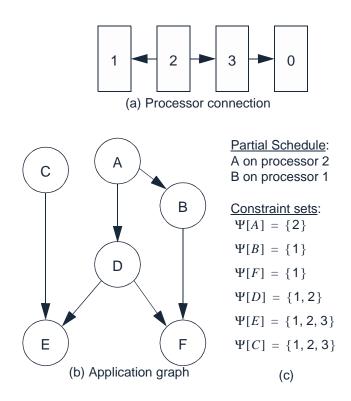

| 6.8  | Demonstrating flexibility metric                                   |

| 6.9  | Function $Rf^1(S)$                                                 |

| 6.10 | Function $Rb^1(S)$                                                 |

| 6.11 | Function bfsForward()                                              |

| 6.12 | Function bfsBackward()                                             |

| 6.13 | Feasibility function                                               |

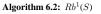

| 6.14 | Makespan of FFT with and without flexibility metric                |

| 7.1  | Link synthesis using the TPLA algorithm                            |

| 7.2  | Basic steps of a GA.                                               |

| 7.3  | Crossover operator applied to array chromosome                     |

| 7.4  | Incorrect crossover for link synthesis                             |

| 7.5  | Correct crossover for link synthesis                               |

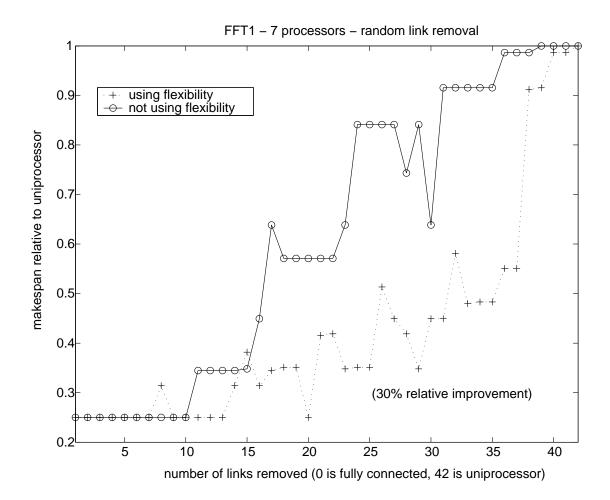

| 7.6  | Comparison of TPLA and genetic algorithm for neural network appli- |

|      | cation                                                             |

| 7.7  | Example of two isomorphic graphs                                   |

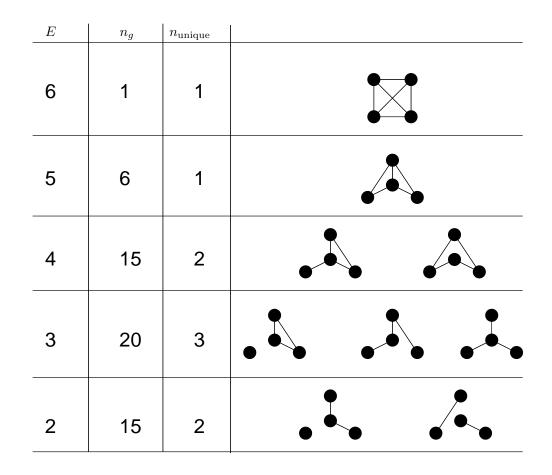

| 7.8  | Isomorphically unique graphs $N = 4$                               |

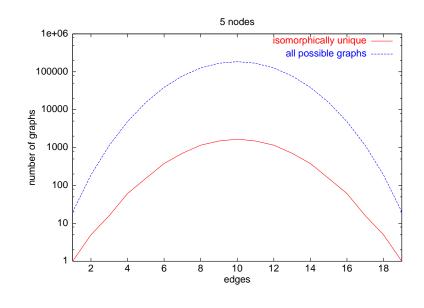

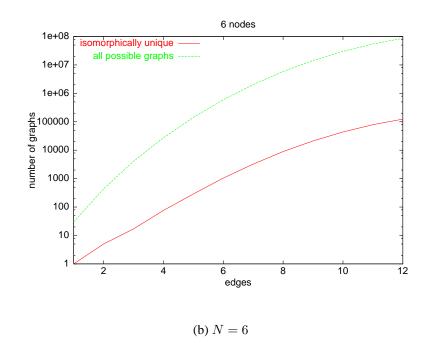

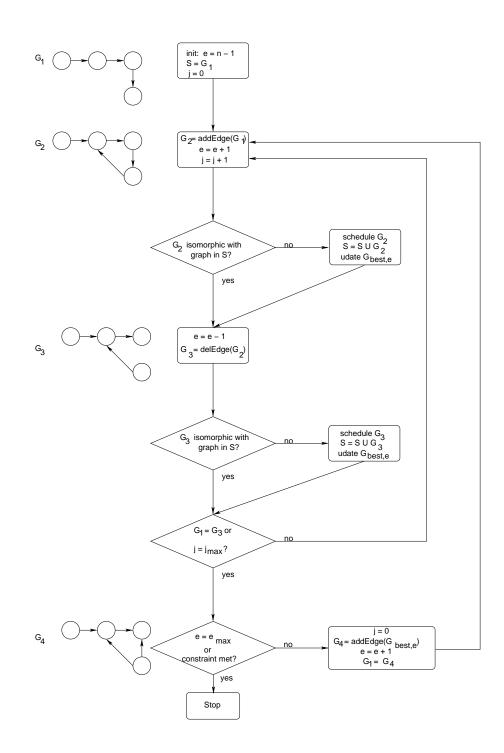

|      | Enumeration of isomorphically unique graphs                        |

|      | Deterministic link synthesis using isomorphism                     |

|      |                                                                    |

| 8.1  | Hill climb local search for voltage scaling                        |

| 8.2  | Monte Carlo local search for voltage scaling                       |

| 8.3  | PLSA for interconnect synthesis                                    |

| 8.4  | PLSA for ordered transactions                                      |

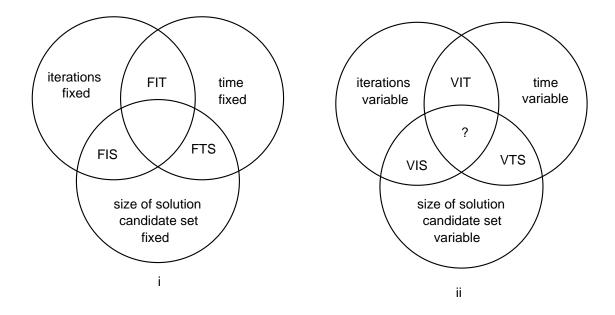

| 8.5  | Simulated heating vs. traditional approach        |

|------|---------------------------------------------------|

| 8.6  | Global/Local Search Hybrid                        |

| 8.7  | Different types of simulated heating 164          |

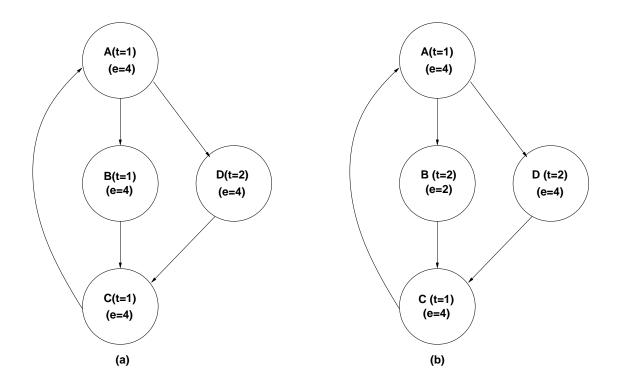

| 9.1  | Voltage scaling the period graph                  |

| 9.2  | Pair swap pseudo-code                             |

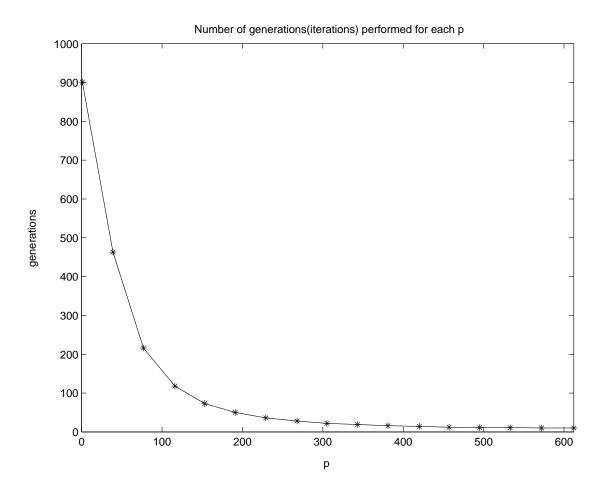

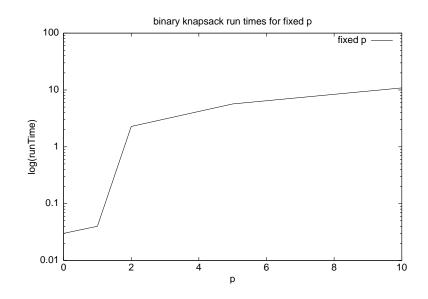

| 9.3  | Local search run times vs. p                      |

| 9.4  | MCMP results for standard hybrid                  |

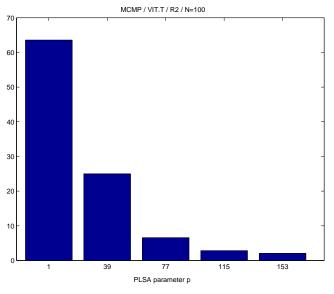

| 9.5  | MCMP number of generations vs. p                  |

| 9.6  | Results for standard hybrid using Monte Carlo     |

| 9.7  | Static heating for MCMP                           |

| 9.8  | Static heating/Monte Carlo for FFT2               |

| 9.9  | Dynamic heating for MCMP                          |

| 9.10 | Dynamic heating/Monte Carlo for FFT2              |

| 9.11 | Time spent in different parameter ranges          |

| 9.12 | Knapsack local search run time                    |

| 9.13 | Error for standard hybrid approach                |

| 9.14 | Knapsack standard hybrid                          |

| 9.15 | Knapsack static heating                           |

| 9.16 | Dynamic heating binary knapsack                   |

| 9.17 | Optimal value of $p$                              |

| 9.18 | Comparison of heating schemes for MCMP            |

| 9.19 | Comparison of heating schemes for voltage scaling |

| 9.20 | Static heating with different population sizes    |

| 9.21 | Dynamic heating with different population sizes   |

|      |                                                   |

| 1 | Random graph algorithm procedures | 213 |

|---|-----------------------------------|-----|

| 2 | Random graph algorithm procedures | 214 |

| 3 | Random graph algorithm main       | 215 |

# **Chapter 1**

# Introduction

The semiconductor industry has demonstrated remarkable progress during the past four decades. For society, this has meant a continual decrease in the cost of electronic devices, from computers to mobile phones to consumer electronics, and their increasing prevalence in our lives. Much of this progress results from the ability to exponentially decrease minimum feature sizes used to fabricate integrated circuits. The most frequently cited trend is Moore's Law, which states that the number of components on a chip doubles every 18 months. The International Technology Roadmap for Semiconductors predicts that by the year 2007, it will be possible to place 800 million transistors in a one square centimeter chip. At the same time, design cycle times have decreased, and interconnects between processing elements are becoming an increasing bottleneck. For a system designer, the biggest challenges involve making effective use of this huge potential functionality, and dealing with the associated complexity. In many ways, time is a much more precious commodity for designers today than is chip area. For this reason, tools that automate the design process are essential for the continued progress of the industry. There has been much research done on lower level design tools which optimize and produce a physical layout for a circuit that has been described in a sufficient amount of detail. Less work has been done on tools for automating the higher levels of design. This thesis will address several issues relating to high level design automation, with a focus on embedded multiprocessor systems.

A central theme in this work is the effect of communication costs and resource contention across processors in the system. We develop techniques and algorithms to deal with these effects in systems whose complexity ranges from low cost shared bus systems to high performance multiprocessor systems utilizing optical interconnects. Communication and contention effects, along with the nature of the application, influence the type of interconnect that is most effective. We discuss different interconnection methods and present algorithms for finding an optimal interconnect topology.

All our optimization problems involve searching large, complex design spaces. Indeed, through our work with a diverse variety of complex optimization problems, we have developed unique insights on general methods for addressing such problems. We present a broadly-applicable framework, which has been derived from these insights, for searching complex design spaces, and we describe how our optimization problems can be solved using this framework.

## **1.1 Multiprocessor Embedded Systems**

An embedded system is a combination of computing hardware and software designed to perform a dedicated function. It is usually part of a larger system, such as the processor in a cell phone. By contrast, a general purpose computing system such as a personal computer is designed to perform many functions. Embedded systems typically offer much higher performance, lower power, and lower cost for their dedicated function than a general purpose system performing the same function. Examples of embedded systems include consumer devices like MP3 players and cell phones, military radar and imaging systems, and processors for automotive engine control.

The processing elements of an embedded system perform two main tasks—control and data stream processing. The control functionality consists of choosing between modes of operation for the device, based on inputs and state information. For example, a simple controller chip on a microwave oven controls the power level and starts and stops the oven based on the keypad inputs. Data stream processing, or digital signal processing (DSP), is required in devices such as cell phones, which must sample data from the radio receiver and convert it into a digital data stream using algorithms which might decrypt the signal and correct for reception errors. In this thesis we will focus on developing tools that optimize the signal processing (DSP) functionality of a system. Processors with architectures that are optimized to provide very powerful digital signal processing functionality are inexpensive, readily available, and prevalent in modern devices.

Applications like video processing and automated target recognition are extremely computationally intensive, and require this processing to be performed in real time. One way to meet these requirements is to design very large scale integrated (VLSI) application-specific integrated circuits (ASIC) that are customized for the specific task. The main problem with this approach is the long design cycle, and the fact that the design is not flexible—if there are changes to the specifications, a new set of ASICs must be designed and tested. Programmable solutions, by contrast, allow changes to be made late in the design cycle by rewriting the software. The use of standard processing cores that have been verified for correctness eliminates much of the error-prone testing and debugging associated with ASIC design. However, it is often the case that a single, standard DSP chip cannot deliver the performance required from the application. In these cases, one attractive solution is to utilize multiple processors. Manufacturers today are able to place several processors on a single die. As the transistor count continues to increase this becomes more cost effective, since it is less expensive to verify and test a number of smaller, standard processing elements than to test a larger, more complicated design. This will make multiprocessor design increasingly important in the future. One trade-off that comes with using multiple processors is that programming them is more complex, since it is necessary to deal with issues such as synchronization, deadlock, interconnect architecture, and interprocessor communication costs. Software tools are needed that allow the designer to specify an application at a high level, and that automate the details like synchronization and code generation. This thesis explores algorithms and techniques to develop such tools.

# **1.2** Contributions of this Thesis

One major theme of this thesis is an analysis of the effect of resource contention in multiprocessor systems. We develop methods to analyze the effects of contention, architectures that are optimized to deal with these effects, and synthesis techniques and algorithms tailored to these architectures.

We consider a variety of systems with different cost/performance tradeoffs. Each successive level of hardware complexity reduces the effects of communication cost and resource contention, allows higher performance, and presents unique optimization challenges for the designer. We present techniques to deal with each of these challenges.

We begin with a shared electrical bus system, which is the simplest, lowest cost solution. The effects of contention are the most pronounced in these systems, and performance analysis is also the most complicated. We present a technique that makes analysis more efficient in these systems. In order to reduce synchronization costs and improve predictability in these systems, researchers have previously developed an *ordered transaction* strategy that adds a hardware controller to the shared bus system [102] and have analyzed the effects of communication costs in these systems [62]. In this thesis we present a modification of this idea that utilizes optical fiber interconnects. This has the effect of dramatically reducing communication resource contention in the system.

The final, most complex architecture we consider is a multiprocessor system utilizing free space interconnects. This can eliminate communication resource contention entirely. One unique challenge for this system is to determine an optimal partitioning of the chip area between regions that are connected electrically and regions that are connected optically.

The optically connected systems offer the the ability to tailor the interconnection network optimally for a specific application. This opens up a vast new design space and poses several interesting challenges in scheduling and interconnect synthesis. We present new scheduling, interconnect synthesis, and optimization techniques to address these challenges.

#### **1.2.1** Contention Analysis in Shared Bus Systems

A critical challenge in synthesis techniques for iterative applications is the efficient analysis of performance in the presence of communication resource contention. To address this challenge for shared bus systems we introduce in Chapter 4 the concept of the period graph. The period graph is constructed from the output of a simulation of the system, with idle states included in the graph, and its maximum cycle mean is used to estimate overall system throughput. We analyze the fidelity of this estimator. As an example of the utility of the period graph, we demonstrate its use in a joint power/performance voltage scaling optimization solution. We quantify the speedup and optimization accuracy obtained using the period graph compared to using simulation only.

#### **1.2.2** Architectures Designed for Optically Connected Systems

In Chapter 3 we will discuss the role that optical interconnects can play in embedded multiprocessor systems, and derive some fundamental equations relating to optically connected systems on chip. We will introduce three architectures on which a broad class of high-throughput, self-timed DSP applications can be analyzed accurately using efficient graph-theoretic algorithms.

#### **1.2.3** Contention Analysis in Optically Connected Systems

Shared bus systems are appealing due to their simplicity and low cost. This is the primary driver for many embedded systems applications. However, a shared bus sometimes cannot meet the performance requirements for systems with significant interprocessor communication. In these cases, a designer may consider using a more expensive optical interconnect. In Chapter 5 we will explain how we modified the IPC graph model [102] and the synchronization graph model [18] to work with the optical architectures developed in Chapter 3.

#### 1.2.4 Scheduling for Arbitrarily Connected Systems

Optics provide the ability to construct highly connected and irregular networks that are streamlined for particular applications. Using these networks, it is possible to implement application mappings that allow flexible, single-hop communication patterns between processors, which has advantages for reduced system latency and power. This flexibility is particularly promising for embedded DSP applications, which are highly parallel and typically have tight constraints on latency and power consumption. In Chapter 6 we discuss the development of scheduling methods for optically connected embedded multiprocessors. We demonstrate that existing scheduling techniques will deadlock if communication is constrained by number of hops. We detail an efficient algorithm for avoiding this deadlock, and demonstrate its performance on several benchmark examples.

#### **1.2.5** Synthesizing an Optimal Interconnection Network

The freedom to optimize interconnection patterns opens up a vast design space, and thus the design of an optimal interconnect structure for a given application or set of applications is a significant challenge. In Chapter 7, we illustrate both probabilistic and deterministic interconnection synthesis algorithms. A key distinguishing feature to our interconnect synthesis algorithms is that they work in conjunction with a scheduling strategy—most existing interconnect synthesis algorithms assume a given schedule.

#### 1.2.6 Simulated Heating

All of the optimization problems we have considered, such as dynamic voltage scaling, scheduling, and interconnect synthesis, involve the search of vast design spaces. Most DSP optimization problems that arise in hardware-software co-design also involve searching large design spaces. For many of these problems, efficient *local search* algorithms exist for refining arbitrary points in the design space into better solutions. In Chapter 8 we introduce a novel approach, called simulated heating, for systematically integrating parameterized local search into global search algorithms. Using the framework of simulated heating, in Chapter 9 we investigate both static and dynamic strategies for systematically managing the trade-off between local search accuracy and optimization effort for the voltage scaling application mentioned earlier, as well as a memory cost minimization problem and a more widely known optimization problem (binary knapsack). We also explain how simulated heating can be used in the transaction ordering optimization problem and the interconnect synthesis optimization problem. The application of simulated heating to these last two problems is the subject of future work.

# **Chapter 2**

# Electronic Design Automation for Embedded Systems

As mentioned earlier, the trend toward increasingly complex designs makes automated design tools very attractive. Ultimately, we would like a single tool that could start with an abstract, system-level design description and produce details of an optimized, hardware implementation. To reach this goal, we must have a suitable framework for describing the system at a high level of abstraction. Automated tools should be able to use this high level specification to generate the details of the design. This chapter will discuss the dataflow specification, and how it can be used for high level design.

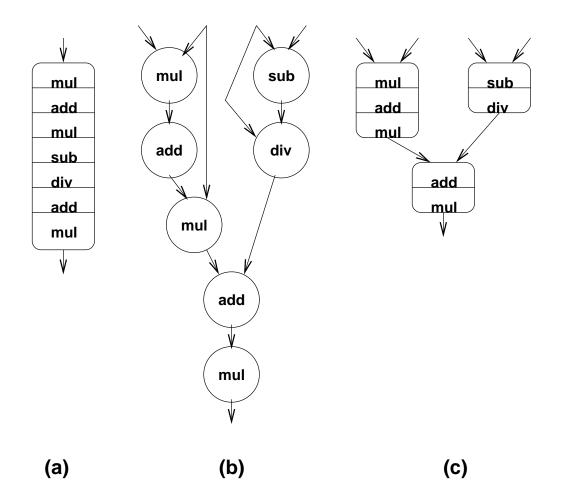

# 2.1 Dataflow

Dataflow graphs have proven to be a very useful specification for signal processing systems for several reasons. First, they support block-diagram based visual programming. Block diagrams (also called signal flow graphs or flow charts), are a versatile and important method for expressing DSP designs. Some of the most powerful DSP design tools use block diagrams as their primary design language. In these tools, the user describes a signal processing system by assembling a block diagram from a library of block functions, such as various types of filters. Examples of commercially available tools using dataflow and visual programming are the Signal Processing Worksystem from Cadence [14] and System Canvas from Angeles Design Systems [82].

A second strength of the dataflow specification is that it effectively exposes the parallelism in the application. It is difficult to compile programs written in imperative programming languages such as C on parallel architectures, since these languages are known to over-specify the control specification and the streaming specification. Parallel languages such as Universal Parallel C [22], are extensions of the serial languages intended to be compiled on parallel machines. However, these languages make certain assumptions about the hardware and are not applicable to a general architecture. They also require the programmer to explicitly handle lower-level details that we would like to avoid. The dataflow model imposes minimal data-dependency constraints in its specification, which allows the compiler to effectively detect parallelism.

A third advantage of the dataflow model is that in certain restricted forms it enables efficient algorithms for determining whether a program will deadlock, and whether it can be implemented in a finite amount of memory. This is not possible in more general computational models, as will be discussed later.

We will focus on applications that can be described by synchronous dataflow graphs (SDF) [69], and its various extensions such as boolean dataflow (BDF) [20]. In the SDF model, streams of data flow through a network of computational nodes. A program is represented as a directed *dataflow graph*. The vertices of this graph, called *actors*, represent computations and the edges represent FIFO buffers that queue the data. The data, represented by *tokens*, are passed from the output of one computation to the input of another. The numbers of tokens produced and consumed by each actor is fixed. The

programmer specifies the function performed at each node. The only constraints that are placed on order of evaluation come from the data dependences in the graph.

Delays on SDF edges represent initial tokens, and specify dependencies between iterations of the actors in iterative execution. For example, if tokens produced by the kth invocation of actor A are consumed by the (k+2)th invocation of actor B, then the edge (A, B) contains two delays.

Actors can be of arbitrary complexity. In DSP design environments, they typically range in complexity from basic operations such as addition or subtraction to signal processing subsystems such as FFT units and adaptive filters.

We refer to an SDF representation of an application as an *application graph*. In this thesis we will mostly concentrate on a form of SDF called *homogeneous* SDF (HSDF) that is suitable for dataflow-based multiprocessor design tools since it exposes parallelism more thoroughly. In HSDF, each actor transfers a single token to/from each incident edge. General techniques for converting SDF graphs into HSDF form are developed in [69]. We represent a dataflow graph by an ordered pair (V, E), where V is the set of actors and E is the set of edges. We refer to the source and sink actors of a dataflow edge e by src(e) and snk(e), we denote the delay on e by delay(e), and we can represent an edge e by the ordered pair (src(e), snk(e)). We say that e is an *output edge* of src(e); e is an *input edge* of snk(e); and e is *delay-less* if delay(e) = 0. The execution time or estimated execution time of an actor  $\nu$  is denoted  $t(\nu)$ .

Fundamental work related to the dataflow model was the work on *computational graphs* by Karp and Miller [59]. In this model, the computation is represented as a directed graph where nodes represent operations and edges represent queues of data. Karp and Miller proved that computation graphs with certain properties are *determinate*, which means that the sequence of data values produced by each node does not depend

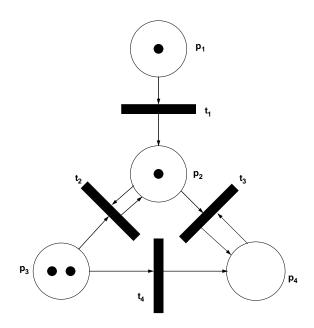

Figure 2.1: Marked Petri net.

on the *schedule*, or order of execution of the actors. They gave conditions to determine graphs whose computation can proceed indefinitely (avoidance of deadlock).

Several forms of dataflow are special cases of *Petri nets*. A general form of Petri nets is discussed in [86]. A Petri net is a directed graph, G = (V, A) where  $V = \{v_1, \ldots, v_s\}$ is the set of vertices and  $A = \{a_1, \ldots, a_r\}$  is a bag<sup>1</sup> of arcs. The set V can be partitioned into two disjoint sets P, representing *places* and T, representing *transitions*. Every arc in a Petri net connects a place to a transition or a transition to a place. Places may contain some number of tokens. A marking of a Petri net is a sequence of nonnegative integers for each place in the net, representing the number of tokens in the place. A Petri net together with a marking is called a *marked Petri net*. An example is given below in Figure 2.1. A Petri net executes by firing transitions. When a transition fires,

<sup>&</sup>lt;sup>1</sup>A bag is distinguished from a set in that a given element can be included n times in a bag, so that the membership function is integer-valued rather than boolean-valued.

one token is removed from each input place of the transition and one token is added to each output place of the transition. A transition that has enough tokens on its input places to fire is *enabled*. Enabled transitions may fire, but are not required to. Firing may occur in any order and may continue as long as at least one transition is enabled. In Figure 2.1, transitions  $t_1$ ,  $t_2$ , and  $t_4$  are enabled. The marking can be represented as a vector  $\{1, 1, 2, 0\}$ . If transition  $t_4$  is fired, the new marking will be  $\{1, 1, 1, 1\}$  and transition  $t_3$  will be enabled.

*Marked graphs* are a subclass of Petri nets. A marked graph is a Petri net in which every place has exactly one input transition and one output transition. A marked graph can be represented by a graph with only a single type of node corresponding to transitions, with the data tokens considered to exist on the arcs. This representation is standard in dataflow. The properties of marked graphs were first investigated in [27].

The application of dataflow to computer architectures and programming languages was pioneered by Dennis [32]. The dataflow model of computer architecture was designed to enforce the ordering of instruction execution according to data dependencies. Execution of instructions is driven by the availability of data, as opposed to the more conventional von Neumann computer where the execution of instructions is controlled by a program counter. In a static dataflow machine, dataflow graphs are executed directly maintaining at the machine level a representation of the program as a dataflow graph and by providing hardware capabilities to detect when an actor has sufficient data to fire. There is a restriction that at most one data value can be queued on an edge at one time. This enables the storage for edges to be determined at compile time. However, this restriction also limits the amount of parallelism that can be extracted from loops. The *tagged-token dataflow model* [2, 47] was created to overcome this restriction. This model supports the execution of loop iterations and function invocations in

parallel. Data values are carried by tokens that include a three-part tag. The first part of the tag marks the current procedure invocation, the second part of the tag marks the loop iteration number, and the third part of the tag identifies the instruction number. Dataflow computers successfully address the problems of synchronization and memory latency, but are not as successful in coping with the resource requirements of large amounts of parallelism in the code. This is due to the overhead in keeping track of the data tags. Although some research continues on dataflow computers, none are in commercial development today. Most research into dataflow today applies to program representation.

Synchronous dataflow (SDF) is a restricted version of dataflow in which the number of tokens produced and consumed by an actor on each edge is fixed and known at compile time. Application of the SDF model to programming of multirate DSP systems was originated by Lee and Messerschmitt [69]. Lee and Messerschmitt provided efficient techniques to determine at compile time whether or not an arbitrary SDF graph has a periodic schedule that neither deadlocks nor requires unbounded buffer sizes. They also presented efficient methods for constructing such a periodic schedule whenever one exists. The SDF model has been successful at describing a large class of DSP applications and has been utilized in numerous design environments. Techniques for compiling general SDF programs for multirate DSP systems into efficient uniprocessor implementations that minimize both code and data memory requirements is presented in [15].

## 2.2 Architectural Synthesis

System-level synthesis requires as a first step the selection of an architecture. In some cases, the designer is given a fixed platform, so the number of computing elements (processors, functional units, etc.) is fixed in advance. More commonly in embedded system

design, there is at least some flexibility to choose the number and types of processing elements and their interconnection. Even with a fixed platform, there can be choices between which tasks are performed by dedicated hardware units and which tasks are performed in software. Modern systems consist of an increasing number of these processing elements, each of which can be highly complex. The design may be realized on a single chip (*system on chip* or SoC), in a multichip design using multi-chip modules (mcm), or on separate circuit boards.

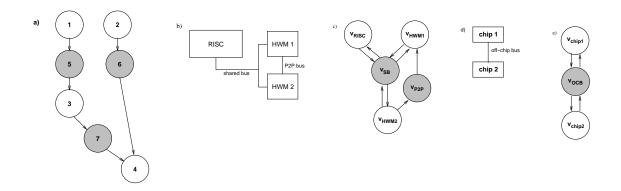

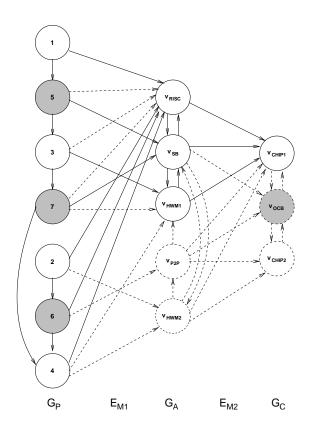

The system synthesis problem can be described formally by means of a specification graph [105], which is a graph  $G_S = (V_S, E_S)$  consisting of D dependence graphs  $G_i(V_i, E_i)$  for  $1 \le i \le D$  and a set of mapping edges  $E_M$ , where  $V_S = \bigcup_{i=1}^D V_i$ ,  $E_S = \bigcup_{i=1}^D E_i \cup E_M$ , and  $E_M = \bigcup_{i=1}^{D-1} E_{Mi}$ . Here,  $E_{Mi} \subseteq V_i \times V_{i+1}$  for  $1 \le i < D$ .

The specification graph consists of layers of dependence graphs, each corresponding to a different level of abstraction. For example, an application graph describes the algorithm, an architecture graph describes the architecture, and a chip graph describes the physical components of the system. An edge in the specification graph between a task and a resource means that task can be implemented by that resource.

This can be better described by considering an example. The example in Figure 2.2 was taken from [105]. Figure 2.2a) depicts an application graph with four computational nodes and three communication nodes (shaded). The architecture, depicted in Figure 2.2b), consists of a RISC processor and two dedicated hardware modules. The hardware modules are connected to each other by a point-to-point bus, and to the RISC processor by a shared bus. The architecture graph corresponding to Figure 2.2b) is shown in Figure 2.2c). The physical implementation consists of two separate chips shown in Figure 2.2d) with a corresponding chip graph depicted in Figure 2.2e). The specification graph is shown in Figure 2.3. The edges  $E_{M1}$  and  $E_{M2}$  describe all possi-

Figure 2.2: Example of a problem graph, an architecture graph, and a chip graph.

Figure 2.3: Specification graph corresponding to example of Figure 2.2.

ble mappings. The edges  $E_{M1}$  describe the possible mappings between the application graph and the architecture graph. We can see that task  $v_1$  can only be executed on  $v_{RISC}$ and task  $v_2$  can be executed on either  $v_{RISC}$  or  $v_{HWM2}$ . Communication task  $v_7$  can be executed on the shared bus  $v_{SB}$ . It can also be executed on  $v_{RISC}$  if tasks  $v_3$  and  $v_4$  both execute on  $v_{RISC}$ , or on  $v_{HWM1}$  if  $v_3$  and  $v_4$  also execute on  $v_{HWM1}$ . The edges  $E_{M2}$  describe the possible mappings between the architecture graph and the chip graph. From these edges we can see that any of the tasks in the architecture graph (the RISC processor, shared bus, point-to-point bus, and both hardware modules) can be implemented inside CHIP1, and that the shared bus  $v_{SB}$  can be handled by CHIP1 or by the off chip bus  $v_{OCB}$ . The dashed nodes and edges in Figure 2.3 are not *allocated* in the implementation. The specification graph allows us to state a formal definition for allocation, binding, and scheduling.

The **activation** of a specification graph  $G_S(V_S, E_S)$  is a function  $a : V_S \cup E_S \mapsto \{0, 1\}$ that assigns to each edge  $e \in E_S$  and each node  $v \in V_S$  the value 1 (activated) or 0 (not activated).

An allocation  $\alpha$  of a specification graph is the subset of all activated nodes and edges of the dependence graphs  $\alpha = \alpha_V \cup \alpha_E$  with  $\alpha_V = \{v \in V_S \mid a(v) = 1\}$  and  $\alpha_E = \bigcup_{i=1}^{D} \{e \in E_i \mid a(e) = 1\}$ . For the example above, the allocation of nodes is  $\alpha_V = \{v_{\text{RISC}}, v_{\text{HWM1}}, v_{\text{SB}}, v_{\text{CHIP1}}\}.$

A binding  $\beta$  is the subset of all activated mapping edges so that  $\beta = \{e \in E_M \mid a(e) = 1\}$ . For the example above, the binding is

$$\beta = \{(v_1, v_{\text{RISC}}), (v_2, v_{\text{RISC}}), (v_3, v_{\text{HWM1}}), (v_4, v_{\text{RISC}}), (v_5, v_{\text{SB}}), (v_6, v_{\text{RISC}}), (v_7, v_{\text{SB}}), (v_{\text{RISC}}, v_{\text{CHIP1}}), (v_{SB}, v_{\text{CHIP1}}), (v_{\text{HWM1}}, v_{\text{CHIP1}})\}$$

so that all the architecture components are bound to CHIP1.

A **feasible binding**  $\beta$  is a binding that satisfies the following criteria:

- 1. Each activated edge  $e \in \beta$  starts and ends at an activated node.

- 2. For each activated node  $v \in \alpha_V$  with  $v \in V_i$ ,  $1 \le i < D$  exactly one outgoing edge  $e \in V_M$  is activated.

- For each activated edge e = (v<sub>i</sub>, v<sub>j</sub>) ∈ α<sub>E</sub> with e ∈ E<sub>i</sub>, 1 ≤ i < D either both operations are mapped onto the same node or there exists an activated edge *ẽ* = (*ṽ*<sub>i</sub>, *ṽ*<sub>j</sub>) ∈ α<sub>E</sub> with *ẽ* ∈ E<sub>i+1</sub> to handle the communication associated with edge e, i.e. (*ṽ*<sub>i</sub>, *ṽ*<sub>j</sub>) ∈ α<sub>E</sub> with (v<sub>i</sub>, *ṽ*<sub>i</sub>), (v<sub>j</sub>, *ṽ*<sub>j</sub>) ∈ β.

It has been shown that the problem of finding a feasible binding is NP-complete [19].

A schedule is a function  $\tau : V_P \mapsto Z^+$  that satisfies for all edges  $e = (v_i, v_j) \in E_P$ the condition  $\tau(v_j) \ge \tau(v_i) + delay(v_i, \beta)$  where  $delay(v, \beta)$  is the execution time delay of node v given a binding  $\beta$ . For the example above a valid schedule is  $\tau(v_1) = 0$ ,  $\tau(v_2) = 1, \tau(v_3) = 2, \tau(v_4) = 21, \tau(v_5) = 1, \tau(v_6) = 21, \tau(v_7) = 4.$

A valid **implementation** is a triple  $(\alpha, \beta, \tau)$  where  $\alpha$  is an allocation,  $\beta$  is a binding, and  $\tau$  is a schedule.

Finally, with the definitions above we can state the problem formally: system synthesis consists of minimizing a function  $h(\alpha, \beta, \tau)$  which describes an optimization goal, subject to

- $\alpha$  is a feasible allocation,

- $\beta$  is a feasible binding,

- $\tau$  is a schedule.

# 2.3 Scheduling

Implementing an algorithm specified as a dataflow graph (DFG) on a multiprocessor system requires "scheduling" the actors. Scheduling was defined formally in Section 2.2. Scheduling involves the tasks of (1) assigning actors in the DFG to processors, (2) ordering the execution of these actors on each processor, and (3) determining the start times of all the actors while maintaining the data precedence constraints of the DFG. Scheduling has been studied extensively in many contexts, and has been classified based on which of the tasks listed above are performed at compile time and which at run time [68].

If all three are performed at compile time, the scheduling strategy is said to be *fully static*. This method requires the least possible runtime overhead. The exact execution times of all the actors are assumed to be given in advance. The processors can run in lock step according to the schedule, and no explicit synchronization is required when they communicate data. However, the exact run times of the actors cannot usually be determined in advance, so the fully static strategy is often not practical.

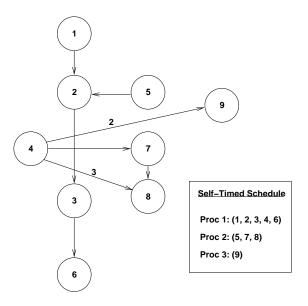

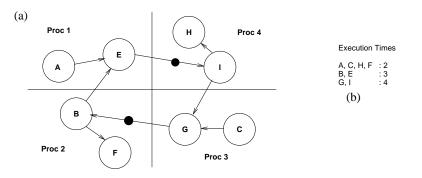

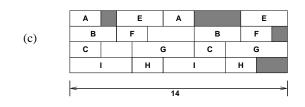

For DSP applications, it is usually realistic to assume that good estimates for the execution times can be determined. Given this assumption, a *self-timed* [68] scheduling strategy can be employed, where the ordering of the actors on each processor is specified, but not the exact start times. Each processor waits for the data needed by an actor before executing that actor. This requires that the processors perform some run-time synchronization when they exchange data, so the run-time overhead is greater for this scheduling strategy. Examples of an application graph and a corresponding self-timed schedule are illustrated in Figure 2.4.

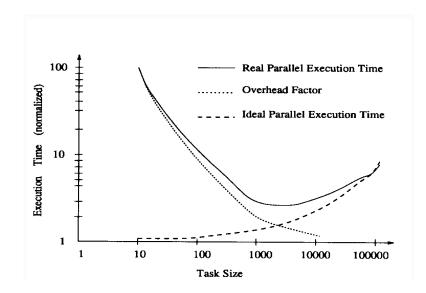

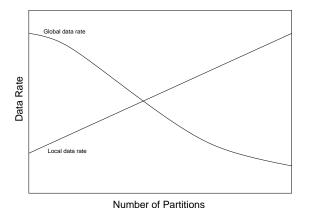

Another consideration in scheduling is the size or granularity of an actor. Figure 2.5 shows a trade-off between parallelism and communication overhead in a heterogeneous DSP system as the size of the actor is varied. It is repeated from the study by Sarkar [93].

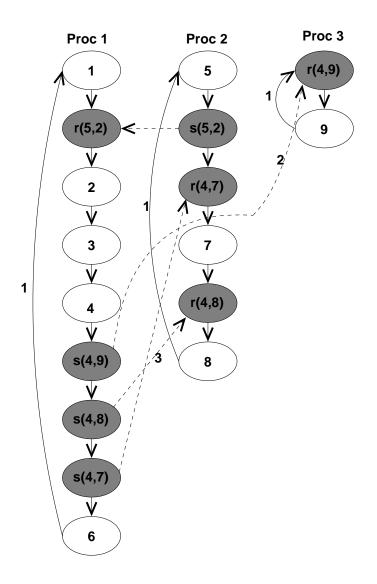

Figure 2.4: An example of an application graph and an associated self-timed schedule. The numbers on edges (4,8) and (4,9) denote nonzero delays.

Figure 2.5: Partition-overhead trade-off [93].

The vertical axis is a measure of performance. As the average actor size is increased, the interprocessor communication (IPC) overhead drops. At the same time, there is a loss of parallelism, so the execution time for an ideal parallel system (with no IPC) increases. Partitioning algorithms try to find the optimal balance between these two factors. Sarkar developed a two-phase scheduling method. The first phase involved scheduling the input graph onto an ideal architecture in which there are no resource constraints or communication costs. This **infinite-resource multiprocessor architecture (IRMA)** consists of an infinite number of processors that are interconnected by a fully-connected crossbar interconnect (an interconnect in which every processor is directly connected to every other processor). The communication in the IRMA architecture is assumed to be simultaneous. In the second phase, the schedule derived for the IRMA architecture is modified to work on the resource-constrained target architecture.

For a system with fixed resource constraints, the multiprocessor partitioning and scheduling problems are NP hard [42], so heuristics must be used. Many such heuristics have been developed. Most existing scheduling heuristics try to minimize the schedule makespan, which is the time it takes for all the tasks to finish the first iteration (execution of one schedule period). However, most DSP applications are non-terminating; an example of a filter operating on an unbounded stream of speech samples. In this case, it is more appropriate to generate schedules that maximize the throughput. Scheduling heuristics can be classified into the following categories: list scheduling heuristics, graph decomposition heuristics, and critical path heuristics.

The most well-studied area in scheduling involves heuristics based on the idea of *priority lists* [31]. These heuristics use a priority list to define an ordering of the nodes in the graph, and use an algorithm that selects each function in order of priority for scheduling on an appropriate resource. In order to compute the priorities, the allocation

and binding steps described in section 2.2 need to be performed in advance.

For DFGs with edge weights and node weights, a path weight can be defined as the sum of the weights of both nodes and edges on the path. A critical path from a source node to a sink node is a path with maximal weight. In the critical path techniques, the graph is partitioned after examining the current critical path, zeroing an edge by combining the incident nodes into a cluster, and repeating the process on the new critical path. In the dominant sequence clustering algorithm by Yang and Gerasoulis [109], the decision to zero an edge is based on the new start time of the node at the beginning of the dominant sequence (the critical path after zeroing of one or more edges) and the start time of an unscheduled node most likely to be affected by the zeroing decision. If either of these start times is increased, the zeroing is not done. Due to the relative simplicity of the zeroing criteria, the complexity of this method is  $O((\nu + e) \log \nu)$ . The modified critical path algorithm by Wu and Gajski [108] considers as-late-as-possible binding, which is found by traversing the graph from the sink nodes to the source nodes and assigning the latest possible start time to each node. A node on the critical path is selected and placed on a different processor. The complexity of this method is  $O(\nu^2 \log \nu)$ .

#### 2.4 Modeling Self-Timed Execution

In relation to the scheduling taxonomy of Lee and Ha [68], in this thesis we focus on the *self-timed* strategy and variations of the closely-related *ordered transactions* strategy optimized for optically-connected multiprocessors. The self-timed and ordered transaction strategies are popular and efficient for the DSP domain due to their combination of robustness, predictability, and flexibility [101]. In self-timed scheduling, each processor executes the tasks assigned to it in a fixed order that is specified at compile

time. Before executing an actor, a processor waits for the data needed by that actor to become available. Thus, processors are required to perform run-time synchronization when they communicate data. This provides robustness when the execution times of tasks are not known precisely or when they may exhibit occasional deviations from their compile-time estimates. Examples of an application graph and a corresponding self-timed schedule are shown in Figure 2.4.

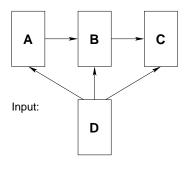

The *ordered transaction* method is similar to the self-timed method, but it also adds the constraint that a linear ordering of the communication actors is determined at compile time, and enforced at run-time [102]. The linear ordering imposed is called the *transaction order* of the associated multiprocessor implementation. The transaction order, which is enforced by special hardware, obviates run-time synchronization and bus arbitration, and also enhances predictability. Also, if constructed carefully, it can in general lead to a more efficient pattern of actor/communication operations compared to an equivalent self-timed implementation [62].

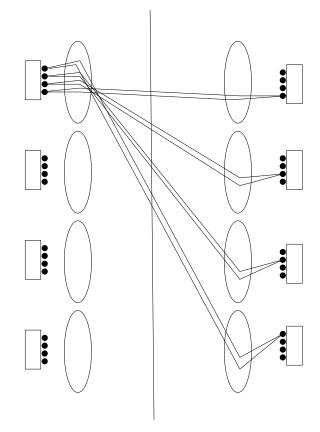

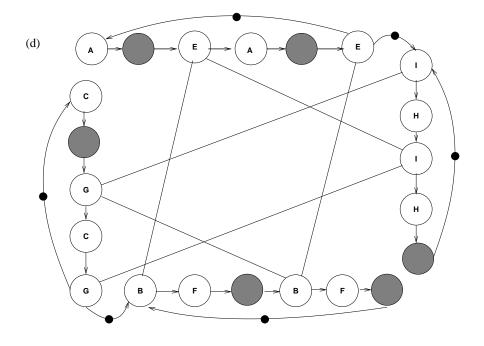

Next we will examine two related graph-theoretic models, the *interprocessor communication graph (IPC graph)*  $G_{IPC}$  [101, 102] and the *synchronization graph*  $G_s$  [102], that are used to model the self-timed execution of a given parallel schedule for a dataflow graph. Given a self-timed multiprocessor schedule for G, we derive  $G_{IPC}$  by instantiating a vertex for each task, connecting an edge from each task to the task that succeeds it on the same processor, and adding an edge that has unit delay from the last task on each processor to the first task on the same processor. Also, for each edge (x, y) in G that connects tasks that execute on different processors, an IPC edge is instantiated in  $G_{IPC}$ from x to y. Figure 2.6 shows the IPC graph that corresponds to the application graph and self-timed schedule of 2.4. In this graph, the nodes labeled with "s" are nodes that send data and the nodes labeled with "r" are nodes that receive data. The numbers in

Figure 2.6: The IPC graph constructed from the application graph and schedule of Figure 2.4. Dashed edges represent IPC edges and shaded actors are communication actors(send and receive actors) that perform interprocessor communication. Numbers next to edges represent delays.

parentheses represent the sending and receiving actors. For example s(5,2) represents a communication actor with data from actor 5 being sent to actor 2.

The non-communication vertices in  $G_s$  and  $G_{IPC}$  correspond to individual tasks of the application being implemented. Each edge in  $G_{IPC}$  and  $G_s$  is either an *intraprocessor edge* or an *interprocessor edge*. Intraprocessor edges model the ordering (specified by the given parallel schedule) of tasks assigned to the same processor. Interprocessor edges in  $G_{IPC}$ , called *IPC edges*, connect tasks assigned to distinct processors that must communicate for the purposes of data transfer, and interprocessor edges in  $G_s$ , called *synchronization edges*, connect tasks assigned to distinct processors that must nicate for synchronization purposes. We will discuss the synchronization graph in more detail in Chapter 5.

Each edge  $(v_j, v_i)$  in  $G_{IPC}$  represents the synchronization constraint

$$\operatorname{start}(v_i, k) \ge \operatorname{end}(v_i, k - \operatorname{delay}((v_i, v_i))) \,\forall k,$$

(2.1)

where start(v, k) and end(v, k) respectively represent the time at which invocation k of actor v begins execution and completes execution, and delay(e) represents the delay associated with edge e.

The IPC graph is an instance of Reiter's *computation graph* model [90], also known as the *timed marked graph* model in Petri net theory [86], and from the theory of such graphs, it is well known that in the ideal case of unlimited bus bandwidth, the average iteration period for the as-soon-as-possible (ASAP) execution of an IPC is given by the *maximum cycle mean (MCM)* of  $G_{IPC}$ , which is defined by

$$MCM(G_{IPC}) = \max_{\text{cycle C in } G_{IPC}} \left\{ \frac{\sum_{v \in C} t(v)}{\text{Delay}(C)} \right\}.$$

(2.2)

The MCM can be computed efficiently—Karp's algorithm [58] runs in  $\Phi(nm)$  time where *n* is the number of actors in the graph and *m* is the number of edges. Dasdan and Gupta [29] describe an algorithm based on Karp's algorithm that runs in (worst case) O(nm), and always faster than Karp's algorithm.

## 2.5 Interconnect Synthesis

SoC design is moving toward a paradigm where reusable components called IP (for intellectual property) from different vendors can be combined to rapidly create a design. IP interface standards are being developed which define the services one IP component (or *IP core*) is capable of delivering, and which enable IP cores to work with on-chip buses and other interconnection networks. The SoC designer's task is then to choose the appropriate IP cores, map the application tasks onto these cores, and to construct a communication network and corresponding glue logic to connect these IP cores.

Interconnect synthesis is becoming an increasingly important part of system-level synthesis, given the larger number of blocks that must be interconnected and the increasing importance of interconnect delay to overall performance. To date, shared bus has been the dominant interconnect. However, researchers are now exploring a richer set of interconnection schemes, including crossbars, meshes, and other point-to-point topologies. We will explore interconnect synthesis in detail in Chapter 7.

## **Chapter 3**

# System Architectures for Multiprocessor Embedded Systems

There has been substantial research work in the areas of multiprocessor hardware and software for high performance, general purpose computing. These machines tend to be big and expensive, and are targeted toward solving large computational problems such as climate simulation. As mentioned in the Introduction, embedded systems can also utilize multiprocessor architectures, and some research work has focused on developing application-specific multiprocessor systems. Since these systems only need to support a limited number of programs, it is often possible to streamline the hardware architecture. We will focus on systems running applications that can be described by dataflow graphs. In these applications, parallelism is easier to identify and exploit because much more is known about the structure of the computation.

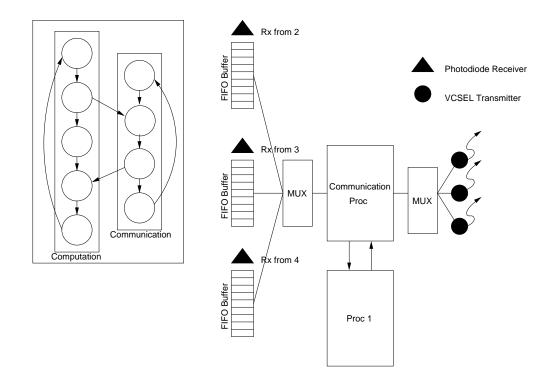

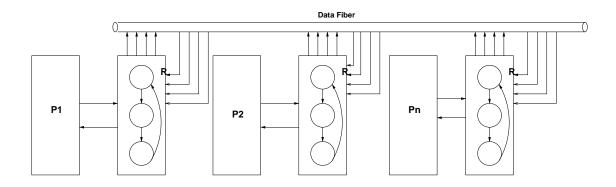

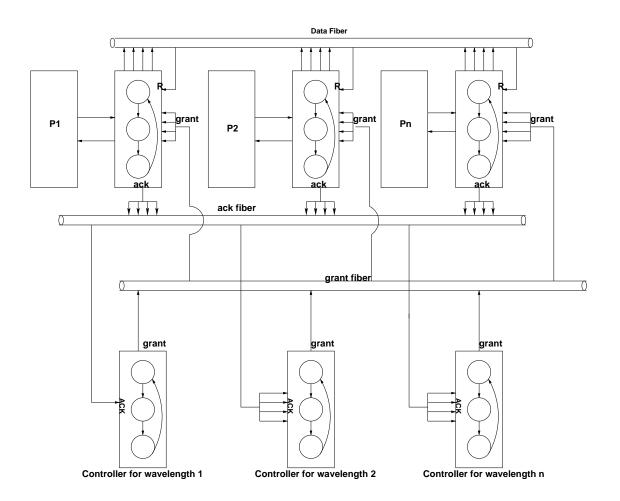

We will discuss the role that optical interconnects can play in embedded multiprocessor systems, and derive some fundamental equations relating to optically connected systems on chip. We will introduce three architectures on which a broad class of high-throughput, self-timed DSP applications can be analyzed accurately using efficient graph-theoretic algorithms.

## 3.1 Multiprocessor Program Execution Models

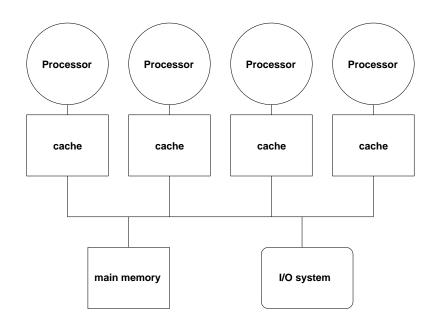

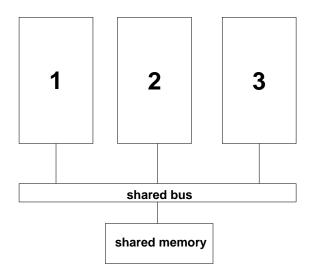

For sequential computers, the principal execution model in use today is the von Neu*mann model* which consists of a sequential process running in a linear address space [45]. In 1966, Flynn [41] proposed a simple model of categorizing multiprocessors using this execution model as either Single Instruction Multiple Data (SIMD) or Multiple Instruction Multiple Data (MIMD) according to how they partition control and data among different processing elements. In a SIMD machine the same instruction is executed by multiple processors using different data streams. Each processor has its own data memory, but there is a single instruction memory and control processor. In a MIMD machine, each processor fetches its own instructions and operates on its own data. Using this terminology, we would call a uniprocessor a single instruction, single data stream (SISD) machine. MIMD machines fall into two categories-centralized shared-memory architectures and distributed memory architectures. Figure 3.1 [85] depicts the basic structure of a centralized shared-memory multiprocessor, where the processors and memory are connected by a shared bus. Processors communicate by writing and reading from locations in memory. In order to reduce the memory bandwidth requirement of the processors, memory cache is used. We may classify the data in the multiprocessor as *private* data if it is only used by a single processor, or shared data if it is used by multiple processors. The communication mechanism utilizes shared data. When data is migrated into a processor's cache, the bus bandwidth is reduced since this processor does not need to access main memory to fetch the data. Also, memory access time to cache is faster than to main memory. When the data is private data, the program execution is not affected. However, when shared data are cached, the data may be stored in multiple caches. This complicates the program execution, since there must be some way to reconcile the different copies of the data. This problem is called *cache coherence*, and

Figure 3.1: Basic structure of a centralized shared-memory multiprocessor. Multiple processor-cache subsystems share the same physical memory, typically connected by a bus.

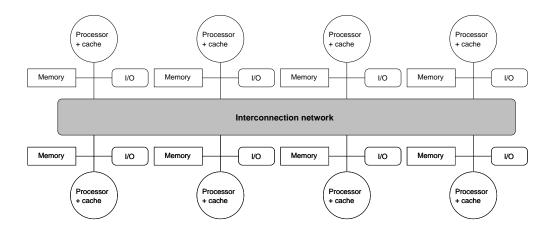

Figure 3.2: Basic structure of a distributed-memory multiprocessor. Individual nodes contain a processor, some memory, and an interface to an interconnection network that connects all the nodes. Individual nodes may themselves contain a small number of processors interconnected via a bus or other interconnect which is often less scalable than the global interconnection network.

has been well studied in general purpose computing [1]. For some embedded systems applications the cache is eliminated in order to reduce complexity and cost.

Figure 3.2 [85] depicts a distributed-memory machine, which has a physically distributed memory. These machines typically have larger processor counts, where a shared bus cannot handle the required communication bandwidth. Distributing the memory reduces the latency for access to the local memory. Compared to the shared-memory architecture, communication between processors is more complex.

## 3.2 Architectures Based on Dataflow

In the von Neumann architecture, all the data, the locations of the data, and the operations to be performed on the data, must travel between memory and CPU a word at a time. This has been termed the "von Neumann bottleneck" [3]. Hardware architectures based on dataflow have been studied in order to avoid this bottleneck. The dataflow model of computation was discussed in Chapter 2. Dataflow models use dataflow program graphs to represent the flow of data and control. In this model an instruction may be executed (or *fired*) as soon as all its input operands are available. When an instruction fires, it consumes its input values and generates some output values. Because of this, the dataflow model is *asynchronous*. In a dataflow architecture the program execution involves receiving, processing, and sending out tokens containing data and a tag. Dependencies between data are translated into tag matching and transformation. Processing occurs when a set of matched tokens arrives at the execution unit. The matching unit and execution unit are connected by queues. Several types of architectures based purely on dataflow have been studied in the past. They differ in how the tokens are handled.

The *single token per arc* dataflow architecture was proposed by Dennis [34]. In this architecture, a dataflow graph is represented by a number of *activity templates*, each containing an instruction and *operand slots* for holding operand values. Only one token is allowed at a time on an arc. Acknowledge signals are used to enforce the single token rule, making it relatively simple to detect when a node is enabled. The *MIT Static Dataflow Architecture* [33] was a direct implementation of this model. One disadvantage of this architecture is that consecutive iterations of a loop can only partially overlap in time. Another is the additional token traffic caused by the acknowledgment tokens.