### **ABSTRACT**

Title Of Dissertation: HIGH-SPEED PERFORMANCE. POWER AND THERMAL

CO-SIMULATION FOR SOC DESIGN

Ankush Varma, Doctor of Philosophy, 2007

Dissertation Directed by: Professor Bruce Jacob

Department of Electrical and Computer Engineering

This dissertation presents a multi-faceted effort at developing standard System Design Language based tools that allow designers to the model power and thermal behavior of SoCs, including heterogeneous SoCs that include non-digital components. The research contributions made in this dissertation include:

• SystemC-based power/performance co-simulation for the Intel XScale microprocessor. We performed detailed characterization of the power dissipation patterns of a variety of system components and used these results to build detailed

power models, including a highly accurate, validated instruction-level power

model of the XScale processor. We also proposed a scalable, efficient and validated methodology for incorporating fast, accurate power modeling capabilities

into system description languages such as SystemC. This was validated against

physical measurements of hardware power dissipation.

Modeling the behavior of non-digital SoC components within standard System Design Languages. We presented an approach for modeling the functionality, performance, power, and thermal behavior of a complex class of non-digital

components — MEMS microhotplate-based gas sensors — within a SystemC design framework. The components modeled include both digital components (such as microprocessors, busses and memory) and MEMS devices comprising a gas sensor SoC. The first SystemC models of a MEMS-based SoC and the first SystemC models of MEMS thermal behavior were described. Techniques for significantly improving simulation speed were proposed, and their impact quantified.

Co-Simulation For SoCs. We adapted the above techniques and used numerical methods to model the system of differential equations that governs on-chip thermal diffusion. This allows a single high-speed simulation to span performance, power and thermal modeling of a design. It also allows feedback behaviors, such as the impact of temperature on power dissipation or performance, to be modeled seamlessly. We validated the thermal equation-solving engine on test layouts against detailed low-level tools, and illustrated the power of such a strategy by demonstrating a series of studies that designers can perform using such tools. We also assessed how simulation and accuracy are impacted by spatial and temporal resolution used for thermal modeling.

# HIGH-SPEED PERFORMANCE, POWER AND THERMAL CO-SIMULATION FOR SOC DESIGN

by

#### Ankush Varma

Dissertation submitted to the Faculty of the Graduate School of the

University of Maryland, College Park in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

2007

## Advisory Committee:

Professor Bruce Jacob, Chair Professor Shuvra Bhattacharyya Professor Neil Goldsman Professor Adam Porter Professor Gang Qu Dr. Yaqub M. Afridi To my loving grandparents

Nana, Nani, Papaji, Dadi and Ammamma

#### **ACKNOWLEDGEMENTS**

The completion of dissertation is not the result of my efforts alone. A number of people are to blame, and I would like to name names. The chief conspirator is, of course, my loving wife, Brinda. She has been my friend, hiking buddy, colleague, proof-reader, and accomplice in most of the adventures I've had.

My parents were involved in this dissertation by proxy. Whether its my genes or my upbringing, its their fault either way. In addition, their unconditional, unshakable faith in me, and their irrational belief that whatever I was doing was really important, were no help at all when I was procrastinating on writing this document. Yes, they rock.

My advisor, Professor Jacob, provided feedback, insights and guidance, taught me how to write well and how to present my ideas cogently. He provided unconditional support and a large helping of patience. He also provided funding, which has been empirically shown to be very important to large percentage of graduate students.

Yaqub Afridi at NIST has been a friend, a mentor and a teacher. He also provided very valuable help and guidance on the black magic involved in MEMS systems. Akin Akturk provided help and guidance on thermal modeling and numerical techniques, and also bravely volunteered to proof-read papers and (gasp!) even this dissertation. Professor Goldsman initially suggested the idea of extending my power modeling techniques to thermal modeling during my Ph.D. proposal examination. This would have been a very different dissertation without their help.

My Ph.D. committee members, Professor Bhattacharyya, Professor Porter and Professor Qu, provided encouragement, support and many suggestions for improvement.

Eric Debes, Igor Kozintsev and Nancy Garrison were kind enough to take me under their wing while I was interning at Intel, and have been friends, mentors and buddies. It was while working with them that many of the ideas presented in this dissertation were first developed. Those were fun times.

Mainak Sen is implicated in the completion of this dissertation on multiple counts. He proofread my papers, continually beat me at racketball, and ungrudgingly shared his stash of lab food. In addition, he graduated before I did, thus setting a bad example and making me aware of the disconcerting fact that there *is* life after grad school. Or is there? Perhaps I should find out for myself.

# *Table of Contents*

| Chapter 1: Introduction                                      | 1  |

|--------------------------------------------------------------|----|

| 1. Motivation                                                |    |

| 2. Problem Description                                       | 4  |

| 3. Contributions and Significance                            | 5  |

| 4. Organization of Dissertation                              | 6  |

| Chapter 2: Background and Related Work                       | 9  |

| 1. Design Flows.                                             | 11 |

| 1.1 The Traditional Design Flow                              | 11 |

| 1.2 The SoC Design Flow                                      |    |

| 2. Performance Modeling                                      | 16 |

| 2.1 The SystemC Language                                     | 20 |

| 3. Power                                                     |    |

| 3.1 Power Dissipation                                        |    |

| 3.2 Microprocessor Power Estimation                          |    |

| 3.3 Power Estimation for Other Components                    |    |

| 3.4 System Power Estimation                                  |    |

| 4. System-Level Modeling of MEMS and Heterogeneous SoCs      |    |

| 5. Thermal Issues                                            |    |

| 5.1 Thermal Impact on Design and Performance Parameters      |    |

| 5.1.1 Impact of Temperature on Subthreshold Leakage Current  | 38 |

| 5.1.2 Impact of Temperature on Performance Characteristics   | 40 |

| 5.1.3 Impact of Temperature on Thermal Conductivity          | 41 |

| 5.1.4 Impact of Temperature on Reliability                   | 41 |

| 5.1.5 Impact of Temperature on Signal Integrity              | 43 |

| 5.1.6 Impact of Temperature on Power/Ground Supply Integrity |    |

| 5.2 Thermal and Power Management Strategies                  |    |

| 5.2.1 System-Level Thermal and Power Management              |    |

| 5.2.2 Chip-Level Static Thermal Management             |               |

|--------------------------------------------------------|---------------|

| 5.2.3 Dynamic Chip-Level Power and Thermal Management. | 46            |

| 5.3 Chip-Level Thermal Modeling                        | 48            |

| 5.3.1 Thermal Simulation                               | 51            |

| 5.3.2 Electrothermal Simulation                        | 53            |

| 5.3.3 Microarchitecture-level Thermal Modeling         | 54            |

| Chapter 3: High-Speed Power-Performance                | Co-Simulation |

| for XScale-Based SoCs                                  | 56            |

| 1. Introduction                                        | 56            |

| 2. Methodology                                         | 59            |

| 2.1 Stimulus-Based Parameter Extraction                | 59            |

| 2.2 Performance Modeling                               | 60            |

| 2.3 Software Architecture for Power Models             | 62            |

| 2.3.1 Interfaces                                       | 63            |

| 2.3.2 Internal Data Structure                          | 64            |

| 3. Power Models                                        | 66            |

| 3.1 The XScale Microprocessor                          | 66            |

| 3.2 The WMMX Co-Processor                              | 72            |

| 3.3 Address and Data Buses                             | 72            |

| 3.4 Caches and SRAM                                    |               |

| 3.5 SDRAM                                              | 74            |

| 4. Experimental Setup                                  | 75            |

| 5. Results                                             |               |

| 6. Conclusion.                                         |               |

|                                                        |               |

| Chapter 4: Modeling Heterogeneous SoCs w               | vith SystemC: |

| A Digital/MEMS Case Study                              | 83            |

| 1. Introduction                                        | 83            |

| 2 The MEMS Gas Sensor SoC                              | 85            |

| 2.1 The MEMS Microhotplate-Based Gas Sensor                      |     |

|------------------------------------------------------------------|-----|

| 2.2 System Architecture                                          | 90  |

| 3. Methodology                                                   | 91  |

| 3.1 Electrical And Thermal Modeling Of MEMS Microhotplates       | 92  |

| 3.2 Integration with SystemC                                     |     |

| 3.3 Simulation Efficiency                                        | 96  |

| 3.4 Component Characterization                                   |     |

| 4. Results                                                       | 100 |

| 4.1 Model Validation                                             | 100 |

| 4.2 Simulation With a Controller Program                         | 102 |

| 4.3 System-Level Effects of Low-Level Design Decisions           | 104 |

| 5. Conclusion.                                                   | 107 |

| Chapter 5: Thermal Modeling                                      | 108 |

| 1. Introduction                                                  | 108 |

| 2. Software Structure                                            | 111 |

| 3. Grid-Based Thermal Modeling                                   | 113 |

| 4. A Limit Study on Spatial and Temporal Granularity             |     |

| 5. Validation                                                    | 120 |

| 5.1 Comparison with Device-Level Thermal Modeling Tools          | 120 |

| 5.2 Validation Against Microarchitectural Power Modeling Tools   | 122 |

| 6. Vertically Integrated Modeling of a Example SoC               | 126 |

| 6.1 SoC Components                                               | 126 |

| 6.2 The Reference SoC.                                           |     |

| 6.3 Benchmarks                                                   | 128 |

| 6.4 Modeling the Temperature-Dependence of Leakage Power         | 130 |

| 6.5 Modeling the Impact of Dynamic Thermal Management Techniques | 131 |

| 7. Conclusion                                                    | 134 |

| Chapter 6: Conclusion                                            | 136 |

| Appendices                                                                  | 140 |

|-----------------------------------------------------------------------------|-----|

| 1. Power and Thermal Characteristics of Contemporary Application Processors | 140 |

| 2. Physical and Thermal Properties of Some Materials                        | 141 |

| References                                                                  | 142 |

## **List Of Figures**

| Figure 1.1.  | Overview of the Integrated Power, Performance and Thermal Modeling Approach                                    |

|--------------|----------------------------------------------------------------------------------------------------------------|

| Figure 2.1.  | A Juxtaposition of Traditional and SoC Design Flows                                                            |

| Figure 2.2.  | Subthreshold Leakage Trends                                                                                    |

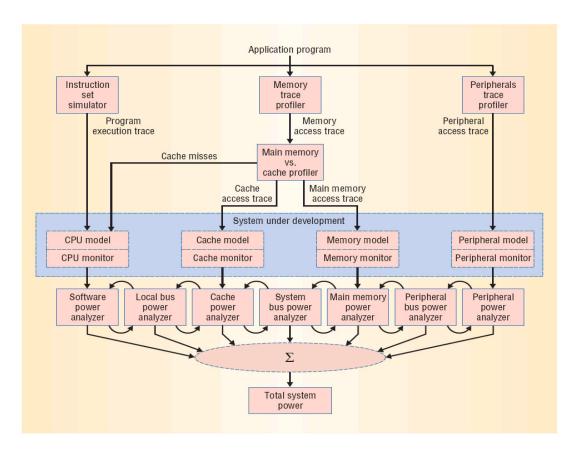

| Figure 2.3.  | System Power Estimation Framework proposed by Talarico et. al. [87] 32                                         |

| Figure 2.4.  | Power Modeling System Architecture proposed by Bansal at. al. [5]33                                            |

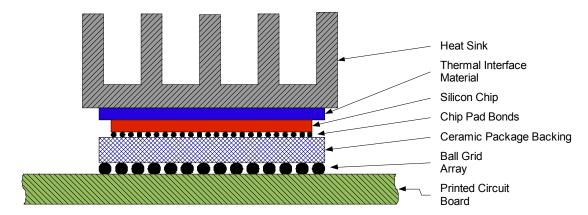

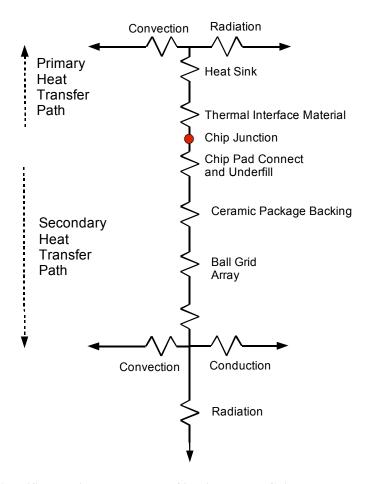

| Figure 2.5.  | Cross-Sectional View of Chip and HeatSink Mounted on a PCB 36                                                  |

| Figure 2.6.  | A Simplified Equivalent Thermal Circuit For The Chip Mount 37                                                  |

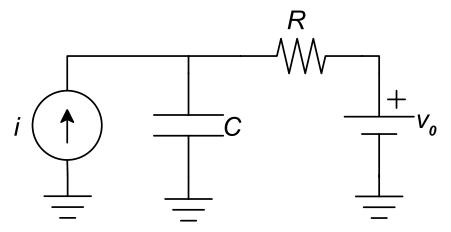

| Figure 2.7.  | The Electrical Analogue Of A Simple Thermal System                                                             |

| Figure 2.8.  | Full-Chip Thermal Modeling                                                                                     |

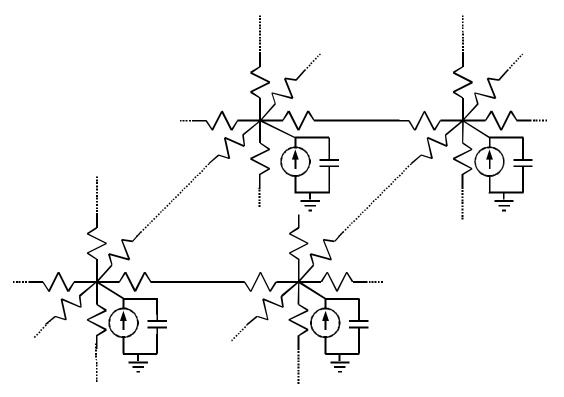

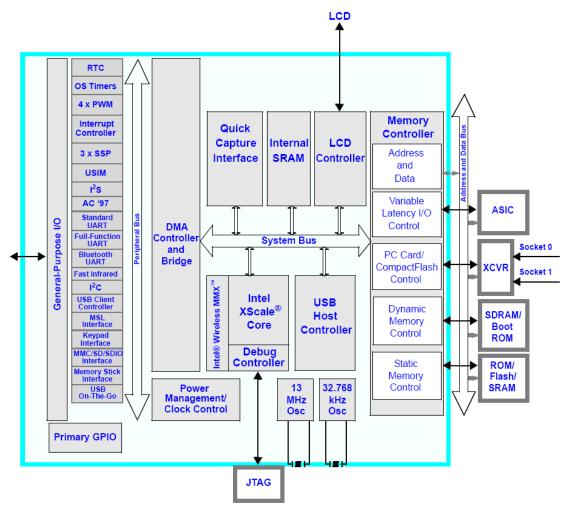

| Figure 3.1.  | The Intel PXA27x Processor Block Diagram for a Typical System [7] 57                                           |

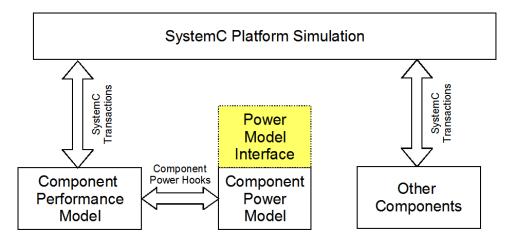

| Figure 3.2.  | Proposed Software Structures for SystemC Power Modeling                                                        |

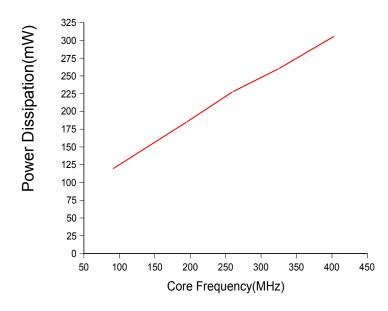

| Figure 3.3.  | Finding Static Power Dissipation and Frequency Scaling Factor for the XScale                                   |

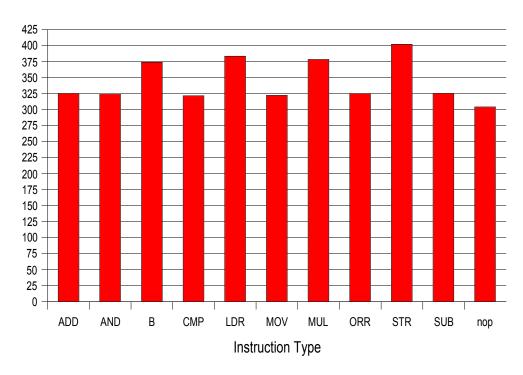

| Figure 3.4.  | Relative Base Energy Costs of Various Instructions                                                             |

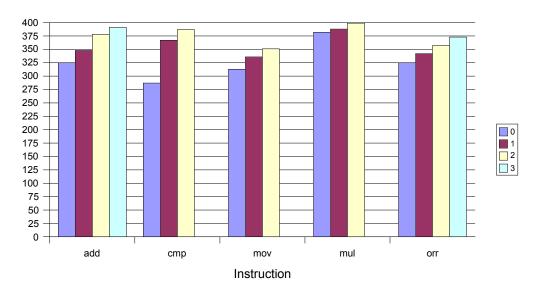

| Figure 3.5.  | Impact of Register Switching on Average Power Dissipation                                                      |

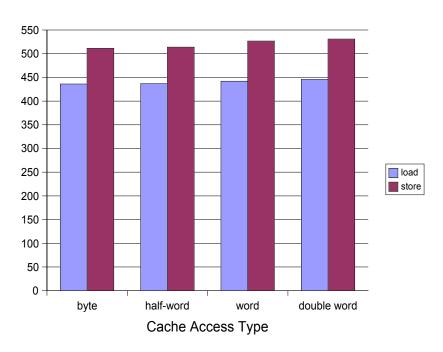

| Figure 3.6.  | The Average Power Dissipation of Various Types of Data Cache Accesses. 70                                      |

| Figure 3.7.  | Average Power Dissipation for various WMMX instruction types72                                                 |

| Figure 3.8.  | The Reference Platform Used for Physical Experiments                                                           |

| Figure 3.9.  | Power Consumed by Various Power Domains at 403 MHz 79                                                          |

| Figure 3.10. | Contributors to Core Power Consumption80                                                                       |

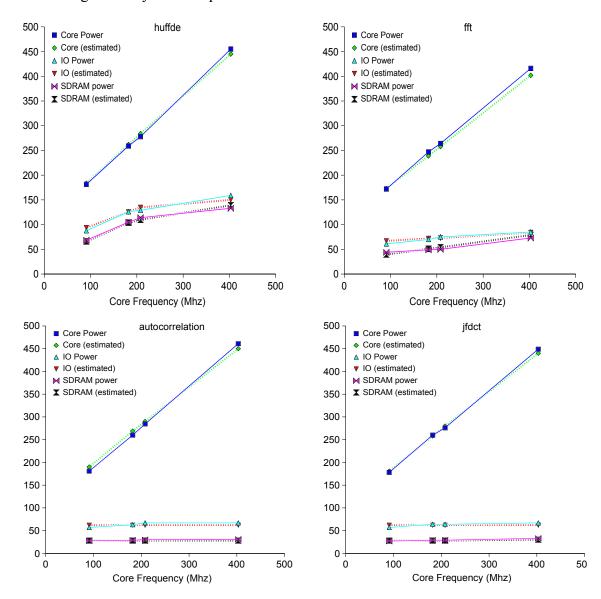

| Figure 3.11. | System Power Consumption at Various Core Frequencies 81                                                        |

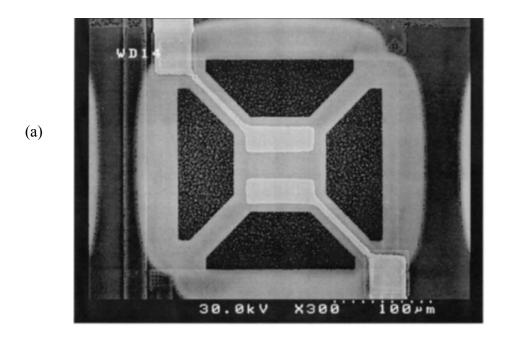

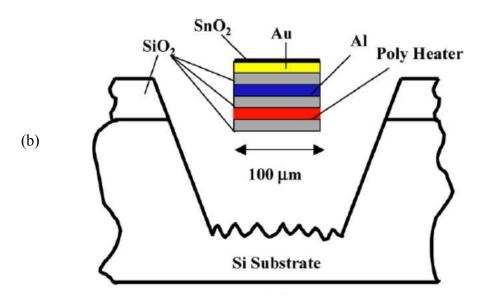

| Figure 4.1.  | The Design of a MEMS Microhotplate based Gas Sensor                                                            |

| Figure 4.2.  | MEMS Microhotplate Gas Sensor Schematics                                                                       |

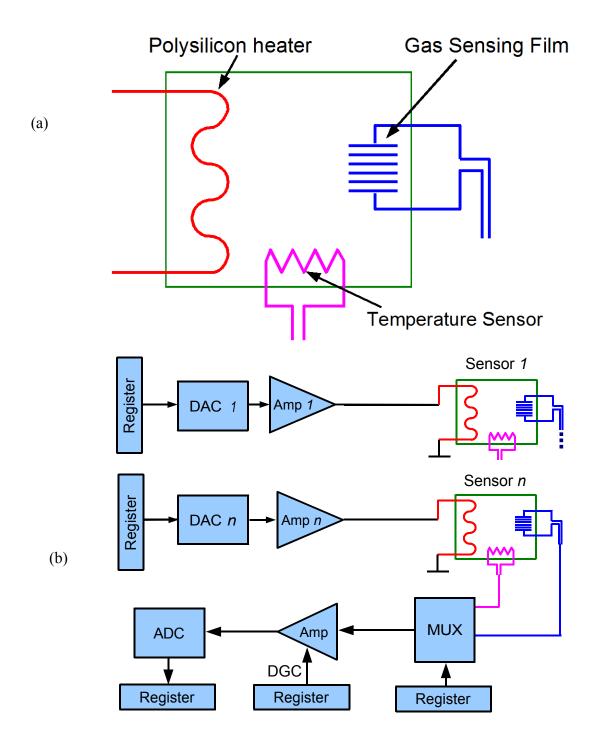

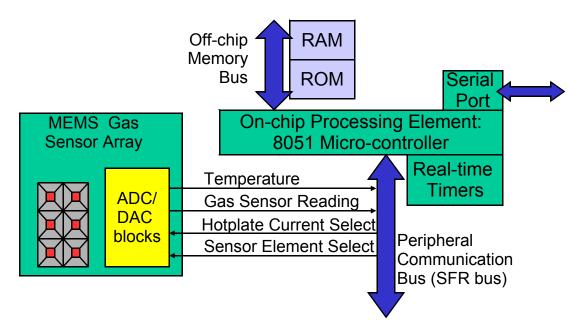

| Figure 4.3.  | System Topology For The Integrated Gas Sensor SoC                                                              |

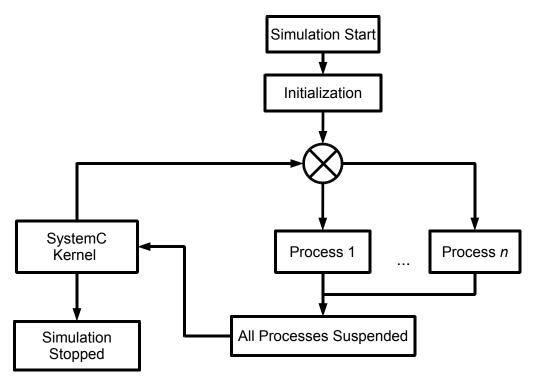

| Figure 4.4.  | The Execution Semantics Of Systemc96                                                                           |

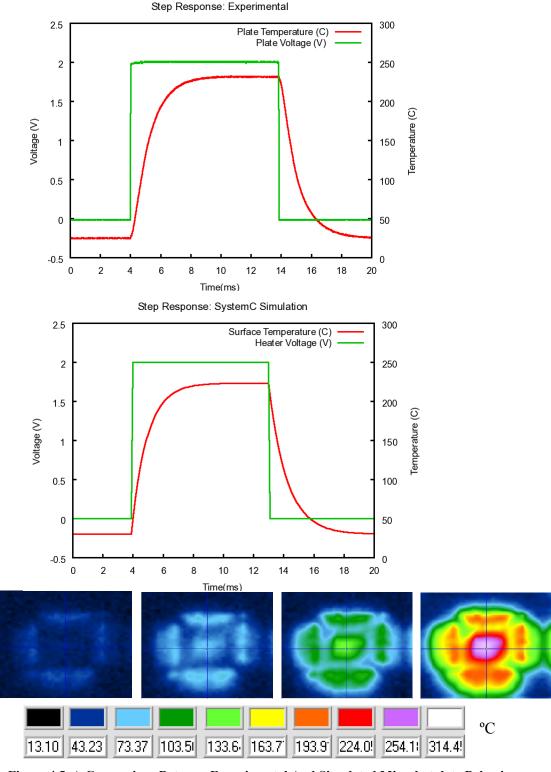

| Figure 4.5.  | A Comparison Between Experimental And Simulated Microhotplate Behavior                                         |

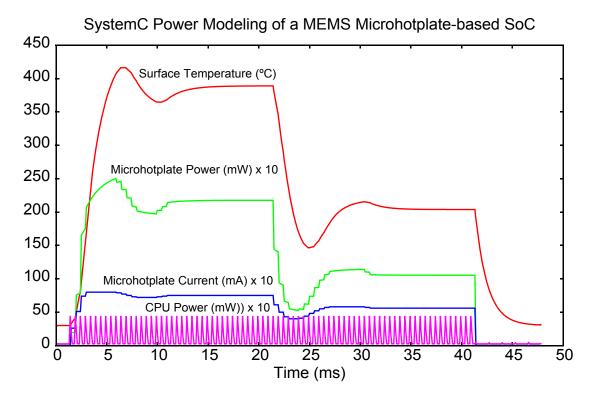

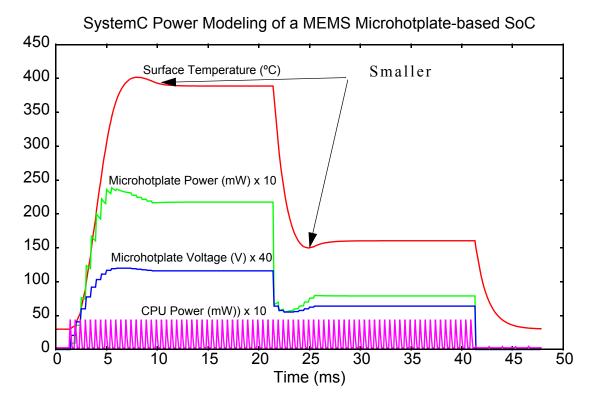

| Figure 4.6.  | An Example Illustrating The Use Of Integrated Functional, Power And Thermal Modeling In A Heterogeneous System |

| Figure 4.7.  | Systemc Power And Thermal Modeling Of A Microhotplate Driven By Controlled-Voltage Source                      |

| Figure 5.1.  | Overall Software Structure for Integrated Power, Performance and Thermal Co-Simulation                         |

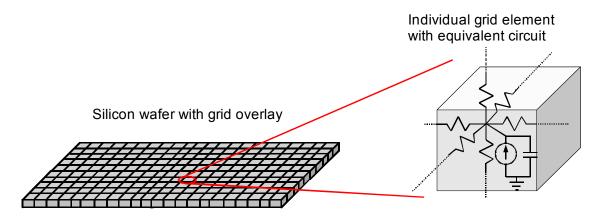

| Figure 5.2.  | Using A Uniform Mesh To Define Thermal Grid Elements                                                           |

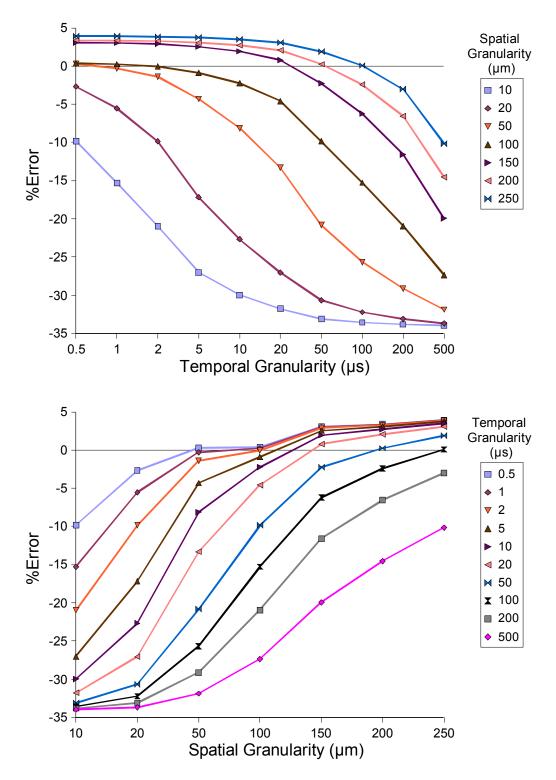

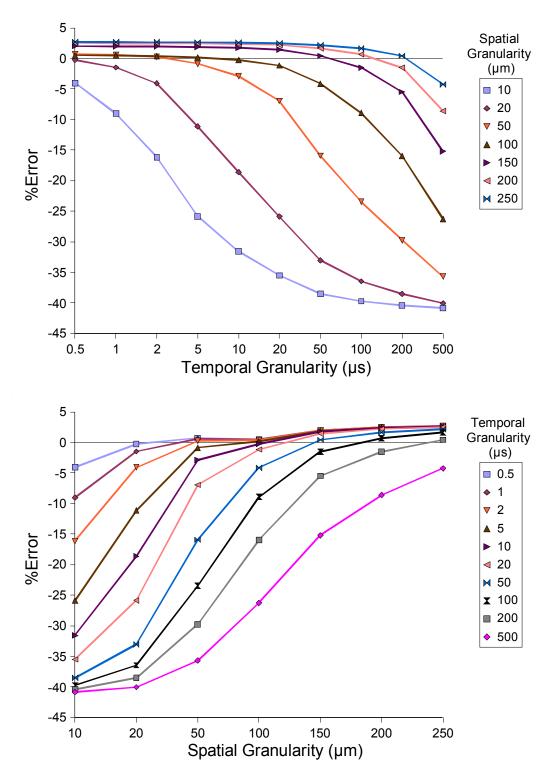

| Figure 5.3.  | Error In Peak Temperature Estimated At 100ms At Various Spatial And Temporal Granularities                     |

| Figure 5.4.  | Error In Peak Temperature Estimated At 200ms At Various Spatial And Temporal Granularities                     |

| Figure 5.5.  | Simulation Speed As A Function Of Spatial And Temporal Granularity.                  |    |

|--------------|--------------------------------------------------------------------------------------|----|

|              | 121                                                                                  |    |

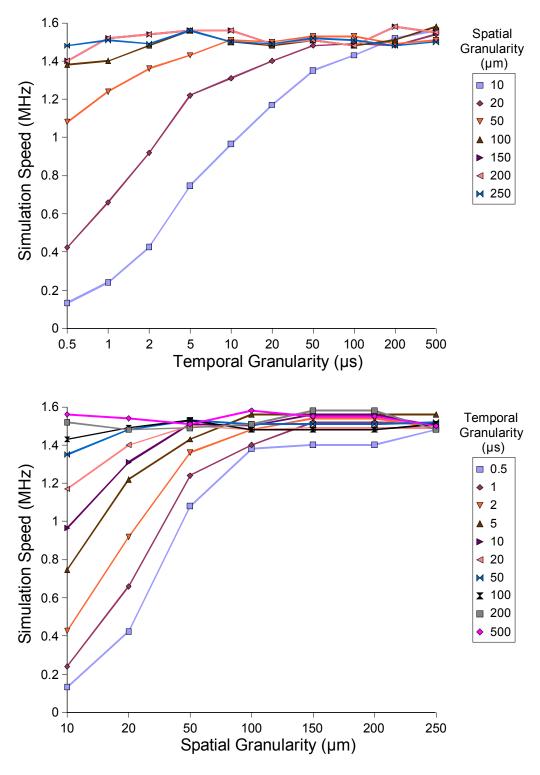

| Figure 5.6.  | Layout And Power Map Used In Reference Chip                                          | 23 |

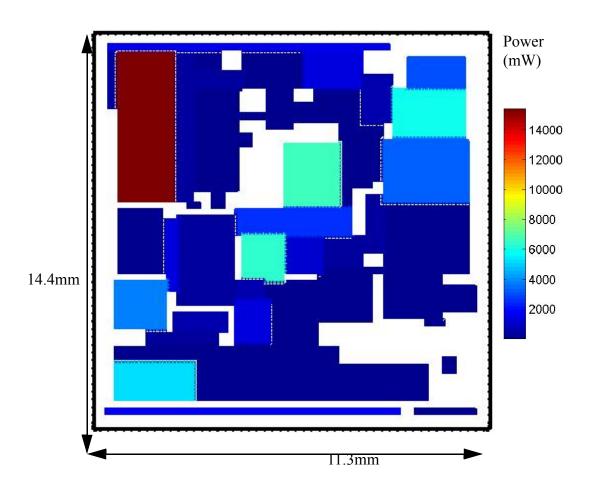

| Figure 5.7.  | Comparison With Device-level Thermal Models                                          | 24 |

| Figure 5.8.  | Validation Against The Hotspot Microarchitectural Thermal Modeling Tool              | 25 |

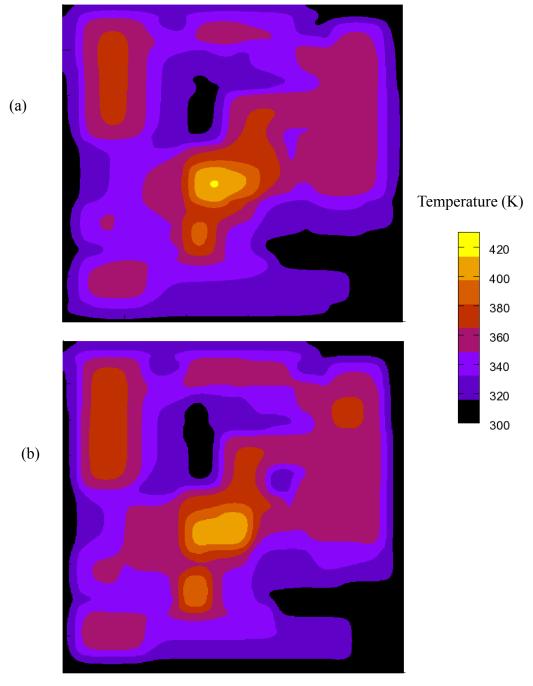

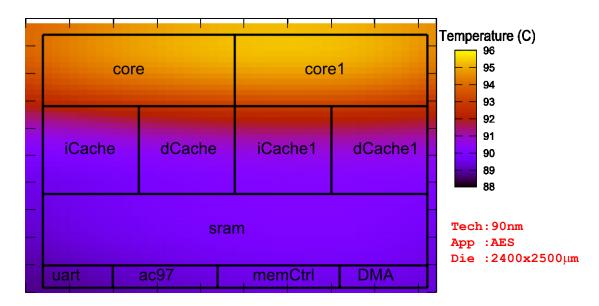

| Figure 5.9.  | Layout Of Reference SoC Used. Showing Components And Their Locations On The Chip     | 28 |

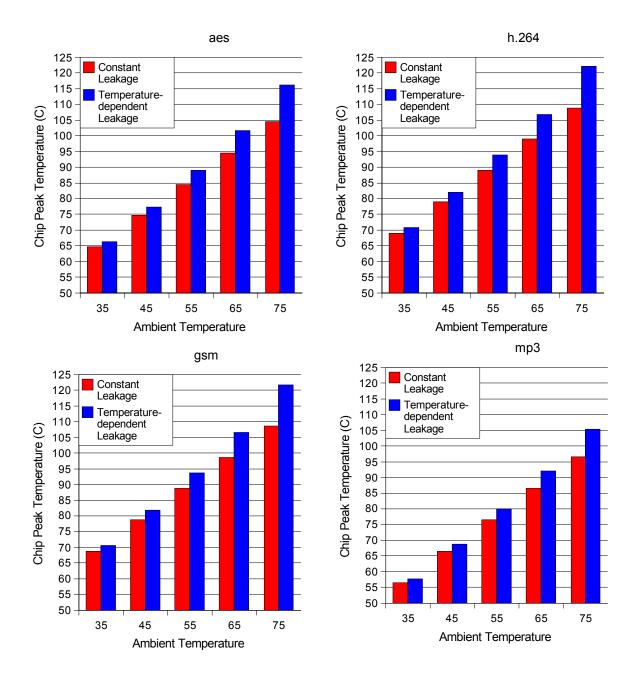

| Figure 5.10. | The Effect of including Temperature-Dependent Leakage Power on peak chip temperature |    |

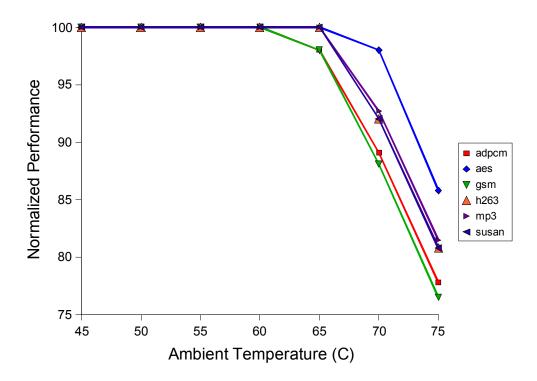

| Figure 5.11. | Evaluating The Degradation Of Performance With Thermal Throttling. 1                 | 34 |

## **List Of Tables**

| TABLE 2.1. | Dualities Between Thermal and Electrical Behavior                                                                                                                      | 50 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| TABLE 3.1. | Using the Power Model Interface                                                                                                                                        | 55 |

| TABLE 3.2. | Observed XScale power dissipation in various low-power modes 6                                                                                                         | 57 |

| TABLE 3.3. | Additional Power Dissipation due to shifts, using stimuli at 403MHz. These are values averaged over all instruction types                                              | 71 |

| TABLE 3.4. | Power dissipation during various stall types, shown here in terms of additional mW of power dissipated at 403 MHz                                                      | 71 |

| TABLE 3.5. | Observed SDRAM Power Parameters (at a memory bus speed of 91MHz 75                                                                                                     | )  |

| TABLE 4.1. | Techniques for enhancing simulation efficiency, and their impact on performance. The exact analytical model for the microhotplates is used unless otherwise specified. | 99 |

| TABLE 7.1. | Thermal Characteristics of Certain Common Embedded Application Processors                                                                                              | 10 |

| TABLE 7.2. | Physical and Thermal Properties of Some Materials at 350K 14                                                                                                           |    |

|            |                                                                                                                                                                        |    |

## Chapter 1: Introduction

### 1. Motivation

Advances in VLSI technology have allowed exponentially increasing numbers of transistors [9] to be crammed onto a single chip. This has led to the advent of System-on-Chip (SoC) designs, which implement all major system components on a single chip to achieve both lower die counts and higher performance. However, the increasing system complexity can make such larger, faster systems increasingly difficult to design, simulate and verify. The classic engineering approach to tackling such complexity is to break the design into sub-modules, so that system design may be tackled in a layered, hierarchical manner, with extensive design re-use. System Description Languages (SDLs) such as SpecC [6] and SystemC [5, 7] have now evolved to provide the high levels of abstraction required for efficient system-level design and high-speed performance modeling, allowing top-level design space exploration to occur very early in the design flow, before resources are invested into a particular system implementation.

The modularity of such a top-down approach for SoCs has led to accompanying changes in the services offered by the EDA (Electronic Design Automation) industry. A variety of vendors now offer microprocessors, memory modules, timers, peripherals, DSPs and hardware acceleration units as pre-designed "shrink-wrapped" IP (Intellectual Property) modules, which system designers can re-use in systems in a standard manner. SystemC-specific programming, synthesis and verification tools are all currently incorporated into the product suites of various EDA vendors. Rather than design each component of a complex system, system designers can now choose components (or *cores*) from a host

of available alternatives, assemble a high-level system model and perform high-speed performance analysis and design space exploration to create an optimized design.

Power is a primary design constraint for a wide variety of systems, especially where battery life or thermal dissipation are critical design parameters. While current SDL-based tools and methodologies provide excellent performance modeling abilities, designers still have to rely heavily on guesswork, simplified spreadsheets and previous experience to estimate power. Inaccurate power estimates have real costs: overestimating power consumption leads to an over-designed, sub-optimal system, while underestimating power causes power issues to emerge late in the design flow, when major design decisions have already been made and resources committed to them. The costs of changing the design late into the design flow can be prohibitively high, and may even cause the entire design to become infeasible. The high penalties for exceeding power budgets also mean that designers must design very defensively, and avoid aggressive designs if there is uncertainty about their power behavior. There is a real need to be able to model and address power issues *early* in the design flow, while there is still scope for design modification.

Thermal dissipation is a major design issue for high-performance systems for a variety of reasons: high costs of chilling server rooms, the rising on-chip heat density, and the physical limitations of air-based cooling systems. In contrast, embedded systems, especially mobile embedded systems, have been historically constrained by battery life (power coming *in*), rather than heat dissipation (power going *out*). However, there are a number of emerging factors that make thermal issues increasingly important for high-end embedded systems:

- A high-end embedded processor for signal or media processing may dissipate as much as 3W of peak power [1, 2].

- Active cooling solutions and even heat sinks are bulky, heavy and expensive, making them unsuitable for embedded systems, mobile embedded systems in particular.

- The infeasibility of cooling solutions means that the junction-to-ambient thermal resistance for an embedded processor package may be 40 60K/W [3], as opposed to ~0.3K/W for desktop processors [8]. This implies that even the relatively modest power consumption of an embedded SoC becomes thermally significant.

- Lastly, embedded systems are often required to operate in harsh and uncontrolled environments. This may include poor ventilation (such as in a utility closet or pocket) which translates into a high effective thermal resistance, as well as elevated environmental temperatures (outdoors operation, locked cars in summer etc.). These serve to exacerbate any existing thermal issues, and reduce the thermal design margins. A report by the CDC, studying fatal car trunk entrapment in children, found that temperatures inside a locked car in summer could reach as high as 78°C [4]. As a result of harsh thermal conditions in everyday environments, embedded system specifications routinely require correct operation at ambient temperatures as high as 85°C.

As a result of these considerations, both power and thermal issues have become major constraints for many embedded systems. The ability to model these issues during system design phases is central to making optimal design choices.

## 2. Problem Description

This dissertation addresses the issues of estimating the power, performance and thermal characteristics of SoCs. This involves answering a number of key questions: What are the power dissipation characteristics of typical embedded systems components? How can power dissipation be modeled using standard SoC design and performance modeling methodologies such as SystemC? Can non-digital components with continuous-time behavior be modeled this way? How can this be extended to modeling chip-level thermal diffusion? And lastly, what are the trade-offs between accuracy and simulation speed involved?

These complexity of these issues is exacerbated by *feedback* behavior in the system. The relationships between performance, power and temperature are not unilateral. While a simplistic view would assume that performance characteristics determine power dissipation, which governs thermal behavior, this is not the complete picture: Temperature, in turn, affects power (for example, through the temperature-dependence of subthreshold leakage current), performance (as in the case of Dynamic Thermal Management strategies) and thermal diffusion itself (through temperature-induced variations in substrate thermal conductivity).

This dissertation is an attempt to answer the questions raised above, and to make system-level power and thermal metrics visible to system designers by augmenting the capabilities of existing SoC performance modeling tools while maintaining the high simulation speeds required for system-level design.

## 3. Contributions and Significance

This dissertation consists of three major inter-related studies. First, we performed a detailed study of the power consumption patterns of the Intel XScale embedded microprocessor and built the most detailed instruction-level power model of such a processor to date [12, 13]. We then showed how an instruction-level power modeling framework can be overlaid on existing SystemC performance modeling frameworks, allowing both fast simulation speeds (over 1 Million Instructions Per Second, or MIPS), as well as accurate power modeling, of the microprocessor, its SIMD co-processor, caches, off-chip bus and on-board SDRAM. We showed that while high-level system modeling languages do not currently model power, they can do so. We explored SystemC extensions and software architectures that enable power modeling and means of obtaining these power models for IP modules so that accurate simulation-based power estimates can be made available to system designers as early as possible. The central problem was that low-level system descriptions can be analyzed for power, but run too slowly to be really useful, while highlevel high-speed system descriptions provide no power modeling capabilities. We developed a system design methodology that bridges this gap, providing both high simulation speed and accurate power estimation capabilities.

Secondly, we showed that such a methodology need not be restricted to pure-digital systems, and we investigated the means to extend it to MEMS devices whose behavior is governed entirely by continuous-time differential equations, which cannot currently be handled by SystemC. To do this, we used SystemC to model an heterogeneous SoC that includes a MEMS microhotplate structure developed at NIST. We demonstrated how equation solvers may be implemented in SystemC, what some of the trade-offs are, and

how high simulation speed may be maintained in the integrated modeling of such devices. We also showed how the integrated modeling of such devices allows implicit feedback behaviors to be modeled at design time [10, 11]. Overlooking such feedback phenomena can frequently lead to suboptimal system designs.

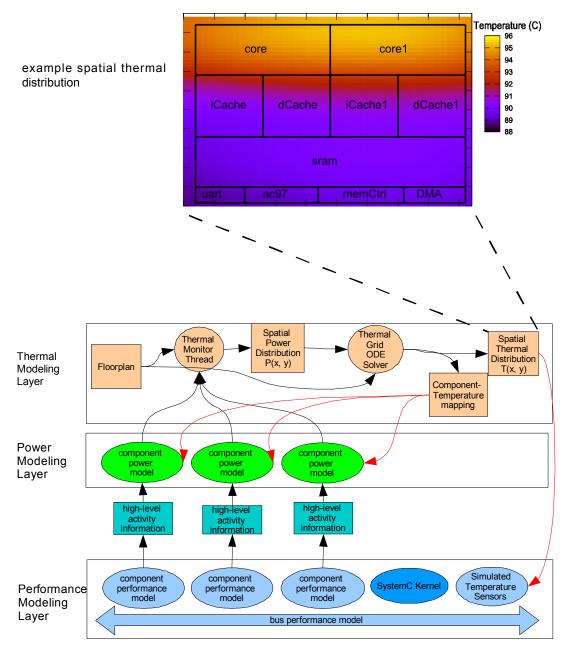

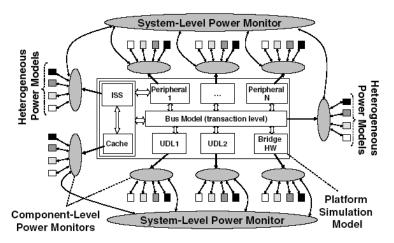

Third, we used the experience gained from the power modeling and mixed-mode modeling study above to extend our SystemC-based modeling infrastructure to the next level: solving the system of tens of thousands of differential equations that govern chip-level thermal behavior. We found that we were able to do so efficiently, while maintaining high simulation speeds, and reasonably accurate temperate estimates. Further, we showed how a vertically-integrated unified modeling tool could model various forms of feedback behavior that is important for accurate thermal modeling, and for estimating the efficacy and performance cost of thermal management techniques. This approach is illustrated in Figure 1.1. We used execution-driven simulation (rather than a trace-driven approach) to enable the modeling of feedback relationships between power, temperature and performance at runtime.

## 4. Organization of Dissertation

The rest of this dissertation is organized as follows. Chapter 2 provides detailed background on the issues involved and discusses related work. Chapter 3 describes a detailed study of the power consumption patterns of the Intel XScale embedded microprocessor and experimentally-validated techniques for power-performance co-simulation in SoC design environments. Chapter 4 shows that such a methodology need not be restricted to pure-digital systems, and explores techniques to extend it to MEMS devices whose behavior is governed entirely by continuous-time differential equations. Chapter 5

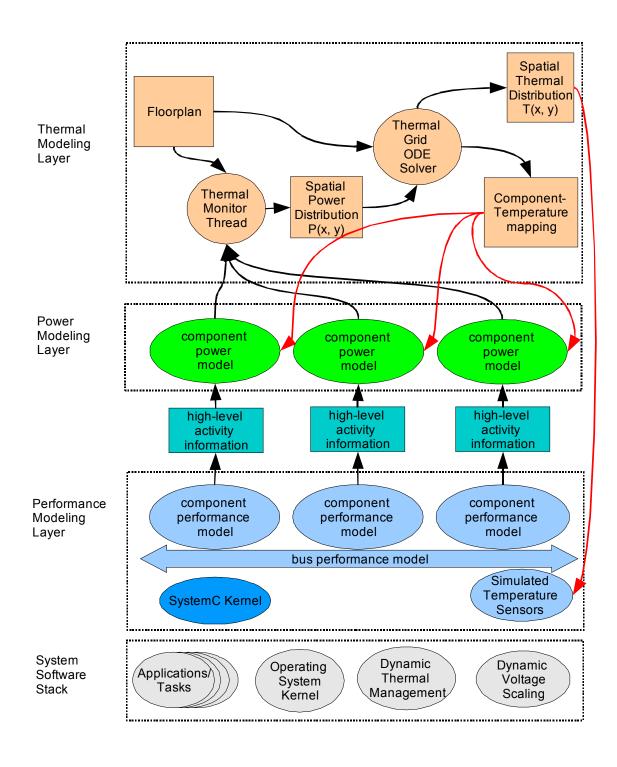

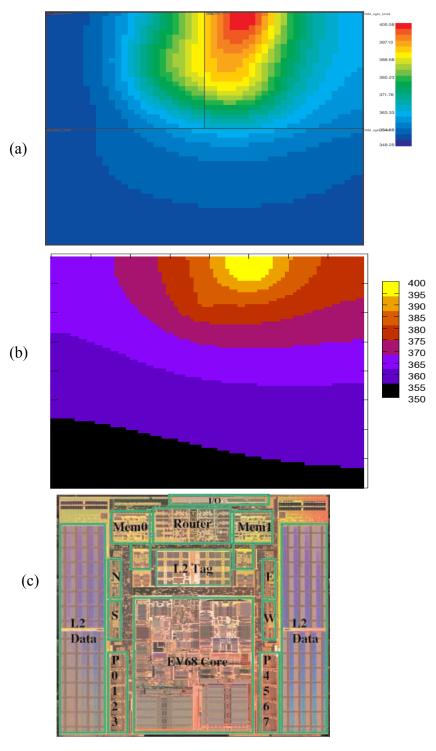

Figure 1.1. Overview of the Integrated Power, Performance and Thermal Modeling Approach. Various component performance models run a standard SystemC-based performance simulation (the bottom layer in the above figure). These performance models are modified to provide high-level activity information to power models, whose output is fed to a thermal modeling infrastructure that uses differential equation solvers to compute the spatial thermal distribution for the SoC studied. An example of this kind of distribution is shown at the very top. The simulation is execution-driven, allowing updated thermal information to be fed back to power models (allowing subthreshold leakage effects to be modeled) as well as to simulated temperature sensor performance models (allowing Dynamic Thermal Management techniques to be evaluated). Details of this approach are discussed in Chapter 5.

The spatial thermal distribution can potentially also be used by a variety of external tools, such automated design space explorers, software optimizers, or thermally-aware floorplanning, layout and routing tools

describes the design, validation and use of an integrated performance, power and thermal co-simulation methodology. Chapter 6 summarizes the findings of these studies, and draws conclusions based on them. This is followed by appendices and references for each chapter.

## Chapter 2: Background and Related Work

This dissertation draws extensively upon a wide variety of previous work in a number of fields, and builds upon it further. Much of the work presented is based on concepts from the following fields:

- Performance Simulation: Performance simulation is a well-studied field, and simulators are used very extensively both for software development and architectural exploration. We build on recent work on System Description Languages (SDLs) as tools for modeling the performance and functionality of complex systems in an efficient manner. In particular, we explore how the simulation infrastructures used for SDL-based performance modeling can be extended to model power as well.

- Power Modeling: This includes work on modeling the power dissipation characteristics of microprocessors and peripherals in isolation, as well as system-level power modeling.

Microprocessor power consumption has been studied for well over ten years now. Microarchitectural power models use an extremely detailed processor model and switching activity information to model power. At a higher level, instruction-level power models assign energy costs to each instruction type to obtain simple but accurate models of microprocessors. Instruction-level power models have been used to successfully model a wide variety of embedded microprocessors. Their main limitation is that they are not known to work for high-performance out-of-order processors, which employ extensive instruction re-ordering and high degrees of speculation. We focus on embedded systems, and build further on work done on

instruction-level power modeling.

Energy consumption patterns of **DRAM**, **SRAM**, **buses and peripherals** have also been the subject of research, although not as much as microprocessors. We draw upon or adapt existing power models of these components where possible. However, we also study some novel components (such as MEMS gas sensors) that have not been studied before, and develop new power models for them.

System-level power modeling encompasses techniques to model an entire SoC, including microprocessors, buses, caches, memory and peripherals. Techniques used in the industry for modeling SoC power are currently ad hoc, based on spreadsheets, guesswork and experience, and there have been only a handful of papers in research that address this issue. This is primarily because methodologies for system-level (as opposed to microarchitectural) power modeling have been developed relatively recently. The research done so far by various groups includes case studies and proposed software architecture solutions to the problem of integrating power modeling into a performance modeling framework. We draw upon this to develop a software architecture that is suited to SDL-based power modeling. However, rather than assume the existence of power models, we address the issue of how such models are created, calibrated and integrated into the framework while simultaneously addressing how the computational overheads of power modeling can be minimized so that high simulation speeds can be maintained.

• Thermal Issues: These include the characterization and modeling of the impact of temperature on circuit correctness and power dissipation, including the impact of

temperature on subthreshold leakage current, performance characteristics, thermal conductivity, reliability, signal integrity and power/ground supply integrity. We also draw upon extensive research on device-level and finite-element modeling of on-chip thermal behavior, as well as some studies on dynamic thermal management strategies.

The rest of this chapter is organized as follows. Section 1 discusses the traditional and SoC design flows, and the differences between the two. Section 2 discusses various approaches to performance modeling and provides an overview of the SystemC system description language. Section 3 discusses power dissipation and provides a literature overview of techniques for estimating the power dissipation of various system components. Section 4 discusses related work on the system-level modeling of MEMS and heterogeneous SoCs. Lastly, Section 5 provides background on chip-level thermal issues, including the impact of temperature on performance and power, thermal and power management strategies and chip-level thermal modeling techniques.

SI units are used for all quantities discussed in all equations and measurements in this dissertation, except where specified otherwise.

## 1. Design Flows

### 1.1 The Traditional Design Flow

Traditionally, designers start with C or C++ simulators to model the components of interest, such as processors, caches, memory systems and so forth. Rather than model the entire system, these typically model the components of interest in detail, and make simplifying assumptions about the rest of the system.

In the design flow, top-level decisions are taken based on simulations using tools such as the ones mentioned above, and then the design is implemented in RTL (Register Transfer Level) in a Hardware Description Language (HDL) such as Verilog [31] or VHDL [50], which can be further synthesized. An intermediate step may be to implement the design in behavioral HDL first, which is higher level than synthesizable HDL and may allow some tweaking of the design, since it is more amenable to simulation.

Synthesis tools then operate on the HDL and a technology-specific library of standard cells to create a gate-level netlist, based on the constraints and operating conditions specified by the designer and on various technology parameters. This netlist is then placed-and-routed on a floorplan of the chip, and finally undergoes layout, where the exact masks of the various layers that will go on silicon is defined. This is then ready for fabrication into silicon.

At each step of the way, lower-level design decisions are taken, optimizations made, and verification performed to ensure that the lower-level implementation indeed conforms to the higher-level specification. The tool flow described above is mature, well-understood and widely used. There exist tools at the circuit, gate and HDL level to model designs in terms of both power and performance. However, these can typically run only at a few thousand instructions per second, making them too slow for system designers to explore power consumption of realistic workloads.

## 1.2 The SoC Design Flow

Both monolithic and SoC designs may incorporate pre-designed modules, commonly referred to as *IP cores*<sup>1</sup>, which provide parameterizable modules such as processors, memory and peripherals for re-use. However, heavy use of modular pre-designed IP cores is the major distinguishing feature of SoC design.

A typical IP core may contain synthesis scripts, documentation and tests, which allow the user to adapt the IP core to arbitrary process technologies (for soft cores) and test the correctness of the implementation. IP cores are typically provided by design companies and other such vendors. In this document, we will use the term "IP core" to refer to any self-contained design intended primarily for re-use in larger systems, regardless of whether is developed by a third party or in-house. For our purposes, it is simply the basic block of design re-use.

IP Cores fall into three broad categories:

- "Hard" IP Cores are provided at the layout level. The SoC designer has little or no flexibility in terms of their configuration, and they are directly plugged into the final design in the design flow back end. Their aspect ratio, size and fabrication technology are fixed.

- "Soft" IP Cores are provided as technology-independent HDL code or netlists.

They are thus extremely flexible and can be synthesized for different technology libraries. However, they may involve an additional investment of effort from the SoC designer, who has to perform synthesis and later design steps for these, rather than just insert the core into a layout. These are the most commonly-available and

<sup>1. &</sup>quot;IP" standing for "Intellectual Property".

most flexible IP cores. Many vendors provide a users a choice of hard or soft IP cores, and charge a premium for the soft version.

"Firm" IP Cores are technology-specific and provide an intermediate degree of

flexibility. They are somewhat configurable but are not provided as high-level

HDL. They typically contain some placement data but allow some degree of

configurability as well.

As the degree of integration increases, the increase in complexity is handled through reuse, and system designers increasingly use IP cores in designs [91] in order to reduce design cost and address time-to-market pressures, to the point where IP Cores comprise the bulk of the chip.

The SoC design flow from HDL onwards falls to the chip designer, and has remained similar the traditional design flow. However, top-level design decisions about which cores to use, what the top-level design parameters of each configurable core should be, and how they should be interconnected are crucial to successful system design, and have an enormous impact on both performance and cost.

Languages to describe hardware at higher levels than current HDLs have evolved to address the increasing complexity of system-level design, since RTL is too low a level of abstraction for efficient design of large multi-million gate systems. These System Description Languages (SDLs) are aimed at extending existing languages to allow high-level hardware description, often while maintaining a C/C++-like syntax. Examples of these include SpecC [38], SystemC [44], SystemVerilog [76], HardwareC [66] and Handel-C [62], among others. A survey of SoC design languages is presented by Habibi and Tahar

[47]. Of these, SystemC has rapidly emerged as a standard for high-level system design, and was approved as IEEE Standard 1666 in December 2005 [51].

Designers first create a very high-level SDL design, make basic design decisions, and *refine* it into successively more detailed SDL designs by adding more detail as design decisions are made. For this purpose, SDLs such as SystemC allow designers to describe designs at a variety of levels of abstraction [17]. In the final step, a sufficiently detailed and low-level SDL model can either be directly synthesized (using newly available SoC design tools) or refined further into an HDL implementation, after which the traditional optimize, place-and-route and layout steps can be followed.

EDA vendors now provide synthesizable, configurable IP cores with SDL models along with HDL implementations so that designers can use the SDL description for high-level design, and plug in the HDL into the final implementation. As system complexity increases, increasing portions of SoC design get replaced by IP cores, much in the same way that chip designers use HDL-based IP cores, and software engineers re-use code libraries. System designers choose, configure and connect IP cores, but typically do not design the innards of the cores [91].

Despite these vast improvements in performance estimation and design re-use, there are still few tools for SoC power estimation, and designers frequently have to depend solely on spreadsheets and previous experience for power estimation until well into the design flow. Even when RTL, netlists, or circuit-level models for IP cores are available, their simulation speeds are orders of magnitude lower than those required for SoC design space exploration, where designers want to simulate many seconds of real time. In addition, there exist no systematic techniques for modeling and integrating analog or

MEMS components into such SDL-based design flows, and these components are often simply treated as black boxes, limiting the accuracy and scope of the system model.

## 2. Performance Modeling

Traditionally, processor designers, programmers and researchers have used specialized processor simulators, typically written in procedural sequential languages such as C and C++. This approach has been around at least since the IBM/360 [16]. While designers use these simulators to explore the microarchitectural space and find the optimal processor designs, programmers use fast, simple instruction-set simulators (also known as *functional* simulators) to quickly check that code behaves as expected, and then use more complex cycle-accurate microarchitectural simulators to analyze performance and optimize code further.

SimpleScalar [4] is a freely available simulator suite and simulation infrastructure that focuses on the microprocessor and cache hierarchy, allowing both software performance exploration and microarchitectural design space exploration. SimpleScalar simulates a MIPS-like architecture at the instruction level. It provides five different simulators that focus on different aspects of the architecture, going from high to low levels of abstraction. At the highest level, Sim-Fast is a functional simulator providing quick results without detailed statistics or timing information. At the lowest abstraction level, Sim-Outorder is a detailed low-level cycle-accurate microarchitectural simulator. The SimpleScalar toolkit provides the basic simulation infrastructure of the type used to evaluate modern processor architectures and memory subsystems. In addition, it also allows designers and researchers to evaluate the impact of specific design choices, such as branch prediction, cache architecture, pipelining etc. SimpleScalar does not directly

### SoC Design Flow Using Soft IP Cores

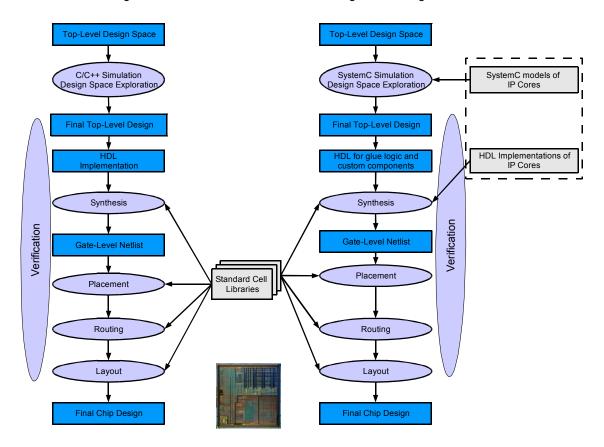

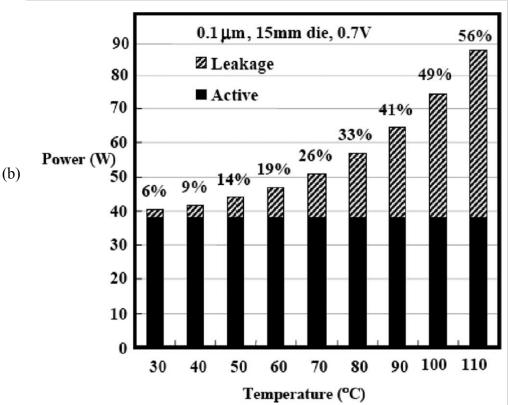

Figure 2.1. A Juxtaposition of Traditional and SoC Design Flows. In a traditional design flow, the HDL is usually written after the top-level design is finalized, while the SoC design flow uses the HDL implementations that are supplied as part of soft IP core components and designers simply connect IP cores and write HDL for "glue logic" that links the cores together. The post-synthesis flow is quite similar in each case. Synthesis, Place&Route and Layout steps all use technology-specific standard-cell library information. Externally-designed supplied components, such as standard-cell libraries and IP cores, are shown in grey in the above figure. The bottom, centre image is a die photograph of an XScale-based SoC.

support power modeling, although there are tools based on it that are used to estimate power.

SimICS [63] is an instruction level functional simulator developed at the Swedish Institute of Computer Science. SimICS aims at being fast and memory-efficient, and achieving a balance between detailed timing simulation and full-featured functional simulation. It supports complex memory hierarchies, and can simulate multi-processor systems. SimICS gathers statistics about memory usage, frequency of various events, and instruction profiling. It allows exploration of the memory hierarchy space, but does not provide power information.

The SimOS simulator [77] is designed to enable the study of operating systems in uniprocessor and multiprocessor systems. The SimOS simulator is capable of simulating the computer hardware in sufficient detail to run a complete operating system. It provides a flexible trade-off between simulation speed and the level of detail and statistics that are collected. However, power consumption is not directly modeled.

Specialized proprietary simulators are also used widely in industry to perform these tasks. Processor manufacturers often have teams aimed specifically at the task of building simulators for these purposes. These are usually performance simulators only, and power budgets are typically calculated based on spreadsheets, experience and conservative design.

As system complexity increases, some drawbacks of *ad hoc* simulators become more apparent. These include:

Simulators written from the ground up are usually cycle-driven. Every subcomponent is triggered on every cycle, even if it does nothing.

- Simulators assume that the processor directs (or "drives") the simulation i.e., it makes the appropriate calls to other components and no higher-level entity makes function calls to the processor model. This often creates scalability issues when going from uniprocessor to multiprocessor scenarios.

- Microarchitectural simulators are written in C, since that is the language most familiar to microarchitects. However, this choice of language has negative implications on scalability since it does not discourage use of static and global variables.

This often prevents multiple-instantiation of components in a design.

- There is no formal model for concurrency, and brute-force cycle-driven simulation is used to ensure synchronicity between components.

- For each new simulator, designers much re-create code for simple functionality such as arbitrary-precision arithmetic, FIFOs, 4-value logic etc.

Traditional simulators were designed to help explore processor microarchitecture, and they have been enormously successful at this job. However, the emerging demands of SoC design demanded that all the problems listed above be solved in a manner that is relatively transparent to the designer. This was addressed by System Description Languages (SDLs), which are aimed at extending existing languages to allow high-level hardware description, often while maintaining a C/C++-like syntax. Examples of these include SpecC [38], SystemC [44], SystemVerilog [76], HardwareC [66] and Handel-C [62], among others. A survey of SoC design languages is presented by Habibi and Tahar [47]. Of these SystemC has rapidly emerged as a standard for high-level system design, and has recently been accepted as an IEEE standard [51]. The SystemC system description language is discussed in detail in Section 2.1.

Given these tools, the job of the SoC designer revolves around choosing preexisting components, connecting them together and configuring the system to find optimal configurations, and these languages have been very successful as tools for aiding this. Examples of using high levels of abstraction for system performance analysis include Conti et. al.'s work on comparing different arbitration schemes for the AMBA AHB onchip bus [29] and Pasricha et. al.'s work on exploring communication architectures [71], among others.

## 2.1 The SystemC Language

SystemC is an ANSI and IEEE standard C++ class library for system and hardware design. Its provides a C++-based standard for designers and system architects who need to design and model complex systems, including systems that are a hybrid between hardware and software.

SystemC is implemented as a C++ class library, and is thus closely related to C++. However, the SystemC language imposes some of its own rules and syntax, and it must be noted that it is possible to create a well-formed C++ program that is legal according to the C++ programming language standard but that violates the SystemC standard [51].

SystemC provides the following facilities to the user:

• The Core SystemC Language: providing primitives such as modules, interfaces, ports, inter-module communication channels (known simply as "channels"), events and so on. At the most fundamental level, a SystemC application consists of a number of modules having ports through which they are attached to channels that enable inter-module communication.

- The SystemC Kernel: an event-driven process scheduler that mimics the passage of simulated time and allows parallel processes to synchronize and communicate in a manner that is useful for modeling a system of hardware and software components. The event-driven, rather than cycle-driven, nature of the simulation kernel allows high simulation efficiency, since synchronization functions need not be invoked for every clock cycle. The SystemC scheduler is non-preemptive, and is deterministic with reference to events occurring and different simulation times. It is not deterministic with reference to events that occur at the same simulation time.

- Data Types: most of which are specifically designed to ease the modeling of commonly used hardware primitives, such as 4-valued logic (0/1/X/Z), bit vectors, finite-precision integers and fixed point types.

- Predefined Channels: representing the common communication types. These include clocks, signals, FIFOs, mutexes, semaphores etc.

- *Utilities*: providing common reporting, tracing and debugging functionality.

- Specialized libraries: Other task-specific libraries built on top of SystemC, such as

the SystemC Verification (SCV) Library, the SystemC Transaction-Level Modeling

(TLM) library, and many bus models.

SystemC provides support for multiple levels of abstraction, going from RTL-like cycle-accurate simulation to pure functional simulation (i.e. no timing) and a variety of highly useful intermediate levels of abstraction [17].

## 3. Power

## 3.1 Power Dissipation

Power Dissipation for CMOS VLSI integrated circuits is dominated by substrate power dissipation, which is the power dissipated in the active devices, rather than by energy losses in the interconnect. Total power dissipation consists of dynamic, static and short-circuit components.

The *dynamic power* (often also referred to as *switching power*) is the power dissipated while charging and discharging the capacitive load at the outputs of each CMOS logic cell whenever a transition occurs. Historically, the dynamic power has been the dominant component of power dissipation. It can be expressed as:

$$P_{dynamic} = \frac{1}{2} \cdot \alpha f V_{dd}^2 C_l$$

(EQ 2.1)

Where

- α is the average number of output transitions in each clock period. α is usually less

than 1, and so is often also defined as the *probability* of an output transition in a

clock period.

- f is the clock frequency.

- $C_l$  is the load capacitance.

The *Static Power* dissipation is the power used by on-chip constant-current sources, and the leakage current, with the latter dominating. The three main components of leakage current are the subthreshold leakage current, the reverse-biased junction leakage current,

and the gate-direct tunneling leakage, with the subthreshold leakage current being the largest of these. According to the BSIM3v3.2 MOSFET model [55, 74], off-state ( $V_{ds} = V_{DD}$ ,  $V_{gs} = 0$ ) subthreshold leakage current can be expressed as:

$$I_{sub} = k_{tech} \left(\frac{W}{L}\right) 10^{-\frac{V_T}{S}}$$

(EQ 2.2)

where

- $k_{tech}$  is a transistor geometry and CMOS technology dependent parameter

- W and L are the transistor width and length

- V<sub>T</sub> denotes the device threshold voltage

- S (the subthreshold swing parameter) is the subthreshold voltage decrease required to increase I<sub>sub</sub> by a factor of ten.

Here, S is given by:

$$S = 2.3nk_bT/q (EQ 2.3)$$

where

- $n \ge 1$  is a device-dependent parameter

- $k_B$  is the Boltzmann's constant

- T denotes the temperature in Kelvin

- q is the electron charge.

Typical values of S are 70-90mV/decade for bulk CMOS devices. In general, the temperature sensitivity of  $I_{sub}$  is 8-12x/100°C [74].

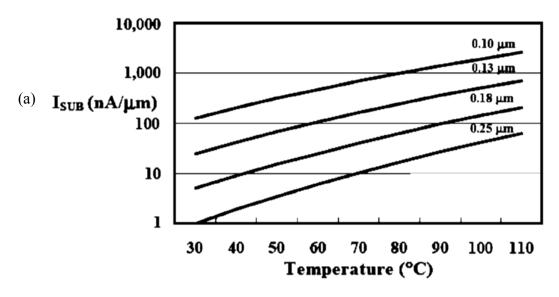

Figure 2.2 illustrates these trends in subthreshold leakage and total power as a function of substrate temperature.

Figure 2.2. Subthreshold Leakage Trends. (a) Subthreshold Leakage Current  $(I_{sub}(V_{gs}=\theta))$  trends as a function of substrate temperature. (b) Total Die Power as a function of substrate temperature. The above figures were taken from work published by Pedram and Nazarian [74], where they were published courtesy Vivek De, Intel.

#### 3.2 Microprocessor Power Estimation

A large amount of research has been done on microarchitectural power analysis, especially for microprocessors. *Wattch* [15] is a widely-used tool built on the SimpleScalar [4] framework that allows power analysis and simulation of microprocessors. It uses capacitance-based analytical power models of regular structures in the processor such as arrays, buses, register files and caches to build up a picture of overall power consumption. *XTREM* [30] is a microarchitectural power model of the XScale [73] based on Sim-XScale, which is in part derived from ARM-SimpleScalar. It uses an approach similar to Wattch to model microarchitectural power. XTREM is not publicly available at the time of writing.

Powell and Chau [75] describe the Power Factor Analysis (PFA) technique, which assigns a fixed *activity factor* to each functional unit inside the processor, and assumes that this does not depend on input signals to the unit. Landman and Rabaey [59, 60, 61] extend this with more powerful statistical tools and allow the power consumption to be a function of the incoming data. They aim at empirically creating statistical power models of functional units, and making power predictions based on certain assumptions about the statistical properties of the inputs. A similar powerful statistical approach is also proposed by Marculescu et. al. [65] who use information theory to create short input sequences that have the same statistical properties as much larger ones, thus allowing for faster analysis. Although these techniques have been applied in large part to processors and DSPs, they are applicable to digital hardware in general.

Chen, Irwin and Bajwa [22] describe a methodology for microarchitectural power estimation and design space exploration based on having a lookup table for each functional unit that maps input signals transitions to power consumption. They also describe a

torially large. However, the level of detail required for accurate modeling makes this approach slow, and they do not demonstrate its applicability on large benchmarks. *SimplePower* [100], also based on SimpleScalar, allows the power models of functional units to be either table-lookups (as described by Chen et. al. [22]) or analytical models. SimplePower models the processor core, instruction and data caches, and the on-chip backend bus between the processor and caches. Intel's Architecture-Level Power Simulator (ALPS) [45] also takes a microarchitectural activity-based approach to power modeling, and is also used to provide power data for subsequent thermal modeling.

While microarchitectural power analysis is aimed at optimizing processor configuration for a set of input programs by predicting power, higher-level power models discard fine-grained microarchitectural information to create a mapping between incoming instructions and power. Tiwari et. al. [88, 89] show how instruction-level power can be characterized from hardware measurements. Sinha et. al. [85] perform energy profiling of ARM processors and also describe how leakage power can be estimated by plotting processor power at various frequencies. Brandolese et. al. [14] propose a generic mathematical model for 32-bit microprocessors which decomposes instructions into *functionalities*, allowing for simpler instruction-level characterization and modeling of 32-bit microprocessors. Chakrabarti and Gaitonde [20] present a simple instruction-level power model based on dividing instructions into categories, and characterizing only representative instructions from each category. Julien, Laurent et. al. study similar instruction-level power models for DSPs [53]. However, they validate their approach only on extremely small programs, not on realistic workloads. Sinevriotis et. al. study [84] low-power optimizations and instruc-

DSP. Zhang [101] and Baynes et. al. [6] create and use similar instruction-level power models of the Motorola M-Core processor in order to study the power consumption of real-time embedded operating systems.

All of these study in-order microprocessor cores, which are typical in embedded systems because of their simplicity, predictability and high energy efficiency. However, instruction-level power models of out-of-order, superscalar high-performance cores have not been widely reported in literature. This is presumably because the added unpredictability of the architecture, through the addition of re-order buffers and speculative execution, decouples microarchitectural energetics from the incoming instruction stream.

Russell and Jacome [78], as well as Sinha and Chandrakasan [85] observe that the power per instruction in embedded processors is a low-variance distribution, suggesting that differences between energy consumption by different functional units are drowned out by the activities common to many instructions. This supports the view that a highly detailed fine-grained power model is only required if microarchitectural parameters within the processor itself need to be tuned, or if extremely accurate power estimates are needed.

#### 3.3 Power Estimation for Other Components

Power models for various kinds of DRAM are provided in technical notes by Micron Technologies [67, 68]. These are *de facto* standard power models used for detailed power modeling of commercial DRAM components. The fundamental aspects of RAM power are discussed by Itoh et. al. [52]. Analytical power models of SRAM and caches are studied by Kamble and Ghose [54]. The CACTI [82], and eCACTI [64] tools also provide accurate

static power estimates of caches and SRAM, and are thus widely used in both industry and academia. We use CACTI 4.0 as a low-level static analysis tools for estimating the energy consumption of various cache operations.

Some work has also been done in modeling peripheral power consumption. Celebician, Rosing and Mooney [19] present simple analytical power models of system components including an I/O controller, FLASH memory, audio CODEC and audio output. Cheng and Pedram [23] present power models of a backlit TFT-LCD display, and how concurrent brightness-contrast scaling (CBCS) can be used to reduce power consumption while reducing the associated degradation in image quality. Choi et. al. [27] and Gatti et. al. [39] discuss system-level strategies for power optimization LCD display schemes. Both of these use simple power models of the display to underpin their work. Givargis, Vahid and Henkel [41, 43], present an instruction-based method for modeling peripheral cores, on the lines of that used for instruction-level microprocessor power modeling, but much simpler. They validate their results for a UART, a DMA controller and JPEG decode accelerator. Fornaciari et. al. [34] present a microarchitectural approach based on the TOSCA hardware-software co-design environment can be applied to a variety of embedded system components, and even to a full control-oriented ASIC.

Bus power has also been studied in some detail. Fornaciari et. al. [35] present an activity-based bus power model and use it to study the effect of bus encoding and cache size on address and data bus power dissipation. Bona, Zaccaria and Zafalon [13] represent one of the first attempts at integrating some power estimation into a SystemC design. They describe how the Siemens' STBus component was adapted to model bus power in a SystemC model of a 4-way ARM multiprocessor system. Caldari, Conti et. al. [18]

describe a similar model for the AMBA AHB on-chip bus, as well as thoughts on how this could be extended to other on-chip components or systems in general. Givargis and Henkel [42] present generic mathematical cache and bus power models while Zhang, Irwin et. al. [103, 104, 105] study on-chip interconnect and its power consumption. This field of research provides the basis for the power models we use.

#### 3.4 System Power Estimation

In contrast, system-level power simulation has been explored in relatively recently. Simunic, Benini and De Micheli [83] present analytical power models for components of a SmartBadge-type embedded system. They use a simplified power model of the ARM processor, which estimates processor power as a simple function of voltage, frequency and idle state (to take into accounted lower power consumption during cache misses). They also describe such analytical power models for a DC/DC converter, on-board bus, caches and memory, and were able to obtain accuracy within 5% of hardware on Dhrystone benchmarks. Early work by Benini, Hodgson and Siegel [8] is based on modeling components as simple state machines. Benini and de Micheli [9] also provide an overview of software and hardware energy minimization approaches typically used by system designers.

Bergamaschi and Jiang [10] present a technique that can be used to create a power state machine for a system, provided that the power model for each component is also a state machine. Bergamaschi et. al.'s SEAS (System for Early Analysis of SoCs) [11] addresses power, along with floorplan and area estimates to enable designers to estimate whether a proposed designs violate area or power budgets. They assume spreadsheet-like or state-machine power models for the core.

Lajolo, Raghunandan, Dey and Lavagno [57, 58] argue that the complexity of model components and software implies that all parts of the system must be simulated together, and trace-based simulation can introduce inaccuracies. They simulate software through *macro-modeling*, where an energy model is created for blocks of software as well as hardware. High-level instruction set simulators simulate functionality, and low-level RTL and gate-level simulators are invoked to calculate timing and energy. To speed up the simulation speed, they use caching and sequence compaction techniques to minimize the number of times low-level RTL energy estimating simulators have to be called. While they too aim at simulation-based execution-driven power simulation, they differ from our work in that they explore ways to tie together different simulators at run-time, while we propose an integrated SDL-based approach that uses lower-level tools only for characterization.

SoftWatt [46] is a system power estimation tool based on SimOS [77]. It estimates software power consumption by analyzing SimOS simulation traces and using simple analytical power models. It can be used to capture the relative power contributions of the user and kernel code, identify the power-hungry operating system services and characterize the variance in kernel power profile with respect to workload.

Givargis and Vahid's *Platune* [40] is a hardware-software co-design tool targeted at tuning SoC design parameters by running small configurable kernels on a number of different configurations to perform automatic design-space exploration. It is suitable for finding the optimum parameters in a fixed system configuration with parameterizable components.

Orion [93, 94, 95] addresses the issue of power-performance estimation on an interconnection network to explore architectural trade-offs using Wattch-like microarchitectural power models [15].

More recently, as system power estimation has become a greater issue, approaches to full-system power estimation have emerged. Beltrame, Palermo, Sciuto, and Silvano [7] describe a plug-in to the StepNP simulation platform [72] that enables power estimation for multi-processor systems on a chip, although they do not describe details of simulation speed or power accuracy achieved.

Talarico, Rosenblit, Malhotra and Stritter [87] present a framework where a simulator is instrumented to produce traces that may be post-processed for power estimation. While this approach is faster than gate-level power modeling, we believe that the huge traces required and the time taken for post-processing limit its scalability and speed. Our experiences show that trace post-processing is an inherently slow activity, since it is almost entirely disk-bound. The results they present have runtimes of a few thousand clock cycles, which is too little to validate full system-level workloads.

Figure 2.3. System Power Estimation Framework proposed by Talarico et. al. [87]. The system relies heavily on execution traces of all components being studied.

Another approach is described by Bansal, Lahiri, Raghunanthan and Chakradhar at NEC Laboratories [5]. They propose a more sophisticated software architecture based on *power monitors*, software plug-ins that monitor component activity at runtime to estimate power. They also allow for different power models for the same component to be swapped in and out at runtime, to minimize the computational overhead of power modeling. They simulate a simple sample architecture in order to demonstrate that system power estimation can be done without significant loss of accuracy. We use a similar software architecture, albeit with a single power model for each component. However, we extend these power

models to account for temperature-dependent power dissipation, and chip-level thermal behavior.

Figure 2.4. Power Modeling System Architecture proposed by Bansal at. al. [5]. This strategy is based on runtime power modeling rather than trace analysis.

# 4. System-Level Modeling of MEMS and Heterogeneous SoCs

There has been relatively little work so far on modeling the behavior of non-digital SoC components within standard SystemC frameworks. Bjornsen et. al. [12] describe using SystemC to model the transient behavior of high-speed analog-to-digital converters. They found SystemC to be an effective modeling tool, with simulation speeds significantly faster than HDL. Zhang et. al. [102] compared Verilog, VHDL, C/C++ and SystemC as candidates for modeling liquid flow in a microfluidic chemical handler, and found SystemC to be the most suitable, since SystemC processes, events and modules are suitable building blocks for expressing fluid flow in a manner analogous to dataflow.

We have published the first SystemC models of a MEMS-based SoC, the first SystemC models of MEMS thermal behavior, techniques for improving simulation efficiency, and a detailed case study of the application of this approach to a real heteroge-

neous SoC. The rest of this section provides background information on related work in literature.

Attempts at generalized modeling of mixed-signal elements for large-scale hardware design include VHDL-AMS [33] and Verilog-AMS [37], aimed at extending the VHDL and Verilog language definitions to include analog and mixed-signal regimes. These have been moderately successful for mixed-domain component modeling; however, they are designed for implementation and end-of-design verification late in the design flow, not for system-level design and verification. Effective system-level design involves representing entire systems at high levels of abstraction and modeling them at high simulation speeds. These requirements are not adequately met by HDL frameworks that primarily target component-level design, creating the need for higher-level techniques and tools that are more efficient at system-level design.

The SystemC 2.0 standard [51, 69] addresses purely digital simulation. However, increasing on-chip heterogeneity has led to the demand for modeling both digital and non-digital components within an integrated framework. Ongoing efforts such as SystemC-AMS [90] and SEAMS [3] propose extensions to the SystemC language definition and additions to the SystemC kernel to incorporate analog and mixed-signal devices into the simulation framework. In contrast, the techniques and models presented in this paper use a standard, unmodified SystemC kernel and library to model non-digital components, and represent the first application of SystemC design to a MEMS SoC.

#### 5. Thermal Issues

With process technologies reaching the nanometer region, chip power density has scaled exponentially across process generations [80]. This has led to increasing die temperatures in modern chips. The exponential dependence of subthreshold leakage power dissipation on temperature aggravates this problem further, potentially affecting correctness of operation, timing closure (and hence speed), as well as reducing reliability and operational lifetime. In addition, the increasing demand for mobile systems has increased the need for low-power designs.

A system or device reaches steady-state thermal equilibrium when the rate of heat transfer out of the system equals the system's net power dissipation. The three key mechanisms involved in heat transfer are radiation, conduction and convection. Cooling systems (heat sinks, heat spreaders, fans etc.) all focus on reducing peak temperatures by increasing the rate of heat transfer. Radiation is the simplest heat transfer mode, involving just a large exposed surface area for transferring heat to the surroundings, often using fins on a heat sink to increase this surface area further. Conduction to the ambient surroundings as well as to cooler nearby components is also achieved by heat sinks, heat spreaders etc.

Figure 2.5 shows a cross-sectional diagram of the mounting of a chip on a printed circuit board. Heat transfer directly away from the chip is primarily conductive. A high-conductivity thermal interface material fills surface imperfections to ensure efficient heat transfer from the chip to the heat sink. Heat transfer away from the heat sink is primarily radiative or convective, since air has a very low thermal conductivity (about four orders of magnitude less than that of aluminum). A secondary heat transfer path also exists downward through the package backing to the PCB. The PCB is in physical contact with

the surroundings, and can conduct heat away (for example, to a case). However, the thermal conductivity along this path is significantly less than that along the primary heat transfer path to the heat sink [97] because of the comparatively low-conductivity materials used and the low cross-sectional area presented to lateral heat flow. In embedded systems, weight/size considerations, as well as the lower dissipated power, neccessitate the use of simple heat spreader (a simple, fin-less, metal sheet of the appropriate dimensions) to often be used instead of the more efficient heat sink.

Figure 2.5. Cross-Sectional View of Chip and HeatSink Mounted on a PCB. The figure shows the typical mounting of a silicon chip and heat sink on a printed circuit board. The fins on the heat sink increase total surface area for better heat transfer outward, and a thermal interface material ("thermal grease") ensures a high thermal contact surface area, and thus better thermal conductivity, between the chip and the heat sink.

Conductive and radiative heat transfer can be improved through purely passive heat transfer systems. However, improving convective-mode transfer usually requires an active cooling solution, of which the CPU cooling solutions of fans and air vents are a common example.

In the past, increasing system power consumption has been address by the use of "bigger fans" as a downstream fix, but this solution is not scalable as power densities increase while components occupy smaller and smaller areas. Further, active cooling

Figure 2.6. A Simplified Equivalent Thermal Circuit For The Chip Mount.

solutions are impractical for use in small form-factor mobile devices, such as smartphones or GPS units. The cost of effective packaging and cooling also increases, since such packages and cooling systems must be designed to address worst-case power dissipation and ambient conditions. Dynamic Thermal Management (DTM) techniques [74], reduce system performance at runtime before excessively high temperatures are reached, allowing the system as a whole to be designed with lower worst-case parameters in mind. Such DTM techniques may include "thermal throttling" (first used on the Pentium 4), where all execution is stopped if the processor nears a thermally unsafe condition. Alternatively, the

processor speed may simply be slowed down, or specific functional blocks disabled to prevent overheating.

The rest of this section is organized as follows. Section 5.1 discusses the impact of temperature on system design and performance parameters, such as leakage current, performance characteristics, substrate thermal conductivity, reliability, signal integrity and power/ground supply integrity. Section 5.2 provides an overview of various thermal and power management techniques. Section 5.3 discusses various chip-level thermal modeling techniques, such as thermal simulation, electrothermal simulation, and microarchitecture-level thermal modeling.

#### 5.1 Thermal Impact on Design and Performance Parameters

#### 5.1.1 Impact of Temperature on Subthreshold Leakage Current

The subthreshold leakage power for a CMOS transistor is given by:

$$I_{subthreshold} = \mu(T)C_{ox}\left(\frac{W}{L}\right)(m-1)\left(\frac{kT}{q}\right)^{2}e^{q(V_{g}-V_{l}(T))/mkT}(1-e^{-qV_{ds}/kT}) \quad \text{(EQ 2.4)}$$

where

- $\mu$  is the mobility.

- $C_{ox}$  is the oxide capacitance.

- m is the body effect coefficient, and has a value in the range of 1.1 1.4.

- W is the channel width.

- *L* is the channel length.

- *k* is the Boltzmann constant.

- *T* is the temperature (in Kelvin).

- q is the electronic charge.

- $V_g$  is the gate voltage.

- $V_t$  is the threshold voltage.

- $V_{ds}$  is the drain-source voltage.

The mobility and threshold voltage in the above equation are also temperature-dependent, and their values are given by:

$$\mu(T) = \mu(T_0) \left(\frac{T}{T_0}\right)^{-1.5}$$

(EQ 2.5)

$$V_t(T) = V_t(T_0) - \kappa(T - T_0)$$

(EQ 2.6)

here,  $T_0$  is room temperature (300K), and  $\kappa$  is the threshold voltage temperature coefficient, with a value around 0.7mV/K [56].

The decrease in threshold voltage and the increase in kT/q (on both of which the current has exponential dependence) dominates the slight decrease in mobility with temperature, and leads to an overall increase in the subthreshold leakage current that is close to exponential.

As described earlier in the chapter, a more directly usable approximation is described by Pedram et. al. [55, 74], based on the BSIM3v3.2 MOSFET model. The subthreshold leakage of a transistor in the "off" state ( $V_{ds} = VDD$ , Vgs = 0) can be expressed as:

$$I_{sub} = k_{tech} \left(\frac{W}{L}\right) 10^{-\frac{V_T}{S}}$$

(EQ 2.7)

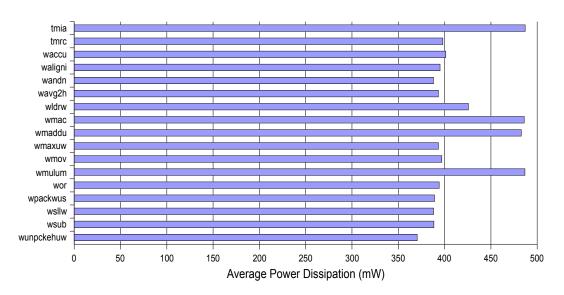

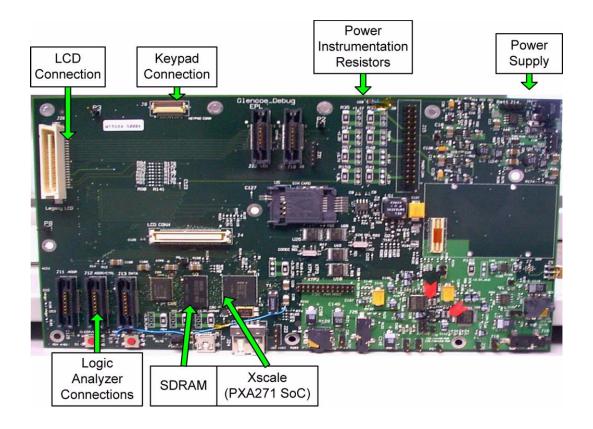

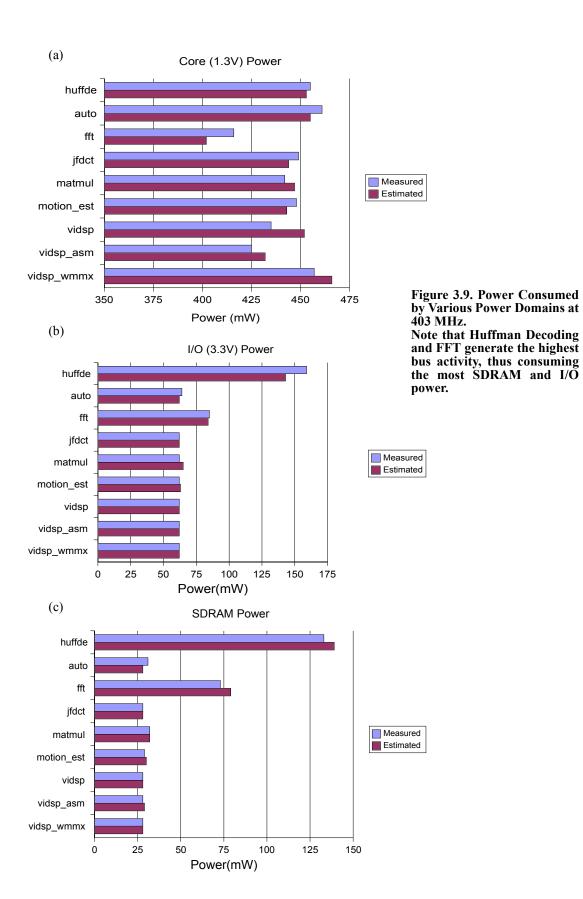

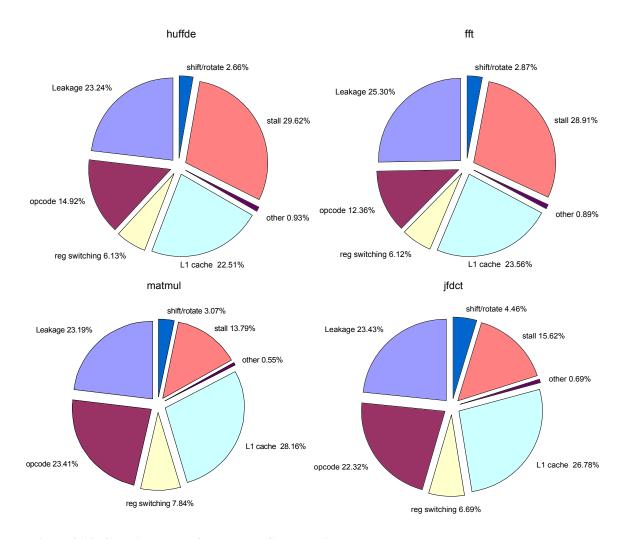

where  $k_{\text{tech}}$  is a transistor geometry and CMOS technology dependent parameter, W and L are the transistor width and length,  $V_T$  denotes the device threshold voltage and S (the subthreshold swing parameter) is the subthreshold voltage decrease required to increase  $I_{sub}$  by a factor of ten. It is  $S=2.3nk_BT/q$  where  $n\geq 1$  is a device-dependent parameter,  $k_B$  is