**ABSTRACT**

Title of Dissertation: RELIABILITY OF COPPER-FILLED

STACKED MICROVIAS IN HIGH DENSITY

INTERCONNECT CIRCUIT BOARDS

Yan Ning, Doctor of Philosophy, 2017

Dissertation directed by: Professor Michael Pecht,

interconnect circuit boards.

Department of Mechanical Engineering

High density interconnect printed circuit boards and substrates are widely used for high-end electronics to meet the demand of greater I/O density and smaller footprint area. Microvias as electrical interconnections between circuit layers have much smaller scale (no larger than 150 µm in diameter) compared to conventional plated-through holes, and require a different fabrication process that introduces unique reliability challenges. Firstly, the copper plating process can easily generate voids in microvias. When voids are present, localized stress concentrations can degrade the reliability of microvias. Secondly, poor quality of electroless copper results in inferior bonding between the base of the microvia and the target pad underneath the microvia. Microvia base and target pad interface separation is a common failure observed in high density

The objectives of this dissertation are to determine the effects of voids on the lifetime of copper-filled stacked microvias, and to develop an analytical model that the electronics industry can use to predict microvia fatigue life. The dissertation also aims to quantitatively address the factors that affect microvia interface separation.

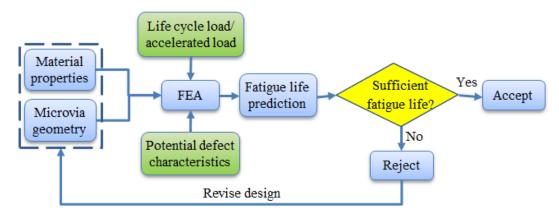

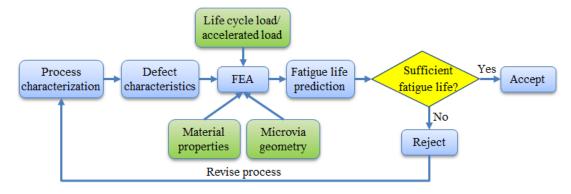

A parametric study was conducted to investigate the effects of voids on the thermomechanical reliability of copper-filled stacked microvias using finite element analysis. Large voids decrease the lifetime of microvias; microvia aspect ratio and *z*-axis coefficient of thermal expansion of the dielectric material are also critical parameters for the lifetime. As an outgrowth of this study, a microvia virtual qualification method was proposed.

A design of experiment (finite element simulation) was performed to quantify the effects of design, material, and defect parameters on microvia lifetime. A second-order strain-based life prediction model was developed using response surface mothed to predict cycles to failure of copper-filled stacked microvias under thermal loading. This is the first known regression model for copper-filled stacked microvia strain life prediction.

Finally, the factors that affect microvia interface separation were quantitatively addressed. Finite element modeling was used to simulate microvias with imperfect electroless copper layers. This study revealed how thermal loadings and structure flaws (in terms of initial crack length) affect the chance of microvia interface separation.

# RELIABILITY OF COPPER-FILLED STACKED MICROVIAS IN HIGH DENSITY INTERCONNECT CIRCUIT BOARDS

by

#### Yan Ning

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2017

Advisory Committee:

Professor Michael Pecht, Chair

Dr. Michael H. Azarian, Co-Chair

Professor Sung Lee

Professor Abhijit Dasgupta

Professor Peter Sandborn

Professor F. Patrick McCluskey

© Copyright by Yan Ning 2017

## Acknowledgements

I would never have been able to finish my dissertation without the guidance of my advisors and committee members, help from my colleagues at the Center for Advanced Life Cycle Engineering (CALCE) and industry partners and sponsors, and support from my family and husband.

I would like to express my deepest appreciate to my advisor, Prof. Michael Pecht, for his visionary guidance and constructive critique. His guidance and advice have allowed me to grow to a stronger researcher and critical thinker.

I would like to express my sincerest gratitude to my co-advisor, Dr. Michael H. Azarian, for his insightful guidance and invaluable advice. He spent enormous time to discuss with me the details of my dissertation research, he always listened and provided excellent advice, and he patiently corrected my writing in papers and presentations. All these helped the success of this dissertation.

I am also very grateful to my committee members, Prof. Abhijit Dasgupta, Prof. Sung Lee, Prof. Peter Sandborn, and Prof. F. Patrick McCluskey for their time spent with me to discuss the research difficulties and their valuable suggestions to help improve the quality of my work.

In addition, I would like to thank all the colleagues at CALCE that helped me on my work toward the dissertation, and CALCE Consortium members and industry sponsors that supported my research and study in the University of Maryland. Special thanks to the industry partners William Bowerman and John Strubbe. They spent a great deal of time to help me understand all aspects of the HDI industry, and we had a lot of great discussions on microvia reliability.

I owe many thanks to my family, including my parents, brother, inlows back in China. Without their constant support, I could not dedicate all my time and efforts to my research and study. Heartfelt thanks to my Husband, Jiachen Li, for his unconditional love, great support, and all sacrifices he made on my behalf. He was always there cheering me up, and stood by me through the good times and bad.

## Table of Contents

| Acknowledgements                                               | ii   |

|----------------------------------------------------------------|------|

| Table of Contents                                              | . iv |

| List of Tables                                                 | . vi |

| List of Figures                                                |      |

| List of Abbreviations                                          | . ix |

| Chapter 1: Introduction                                        | 1    |

| 1.1 Background                                                 | 2    |

| 1.2 Motivation                                                 |      |

| 1.3 Overview of the Dissertation                               |      |

| Chapter 2: Literature Review and Objectives                    |      |

| 2.1 Previous Work and Research Gaps                            | 12   |

| 2.1.1 Reliability Testing on Microvias                         | 12   |

| 2.1.2 Numerical Analysis on Microvias                          |      |

| 2.1.3 Regression Microvia Life Model                           | 17   |

| 2.1.4 IPC Standards on Microvia Voiding                        | 18   |

| 2.1.5 TSV Voiding Research                                     | 19   |

| 2.1.6 Microvia Interface Separation                            |      |

| 2.2 Problem Statement                                          |      |

| 2.3 Objectives of the Dissertation                             |      |

| Chapter 3: Parametric Study on Microvia Voiding Effects        |      |

| 3.1 Finite Element Modeling                                    |      |

| 3.1.1 Microvia Unit Cell                                       |      |

| 3.1.2 Material Properties                                      |      |

| 3.1.3 Thermal Loading Conditions                               |      |

| 3.2 Fatigue Life Prediction                                    |      |

| 3.2.1 Physics-of-Failure Model for Electrolytic Copper Fatigue |      |

| 3.2.2 Total Strain from FEA                                    |      |

| 3.2.3 Application of Miner's Rule                              |      |

| 3.3 Parametric Study                                           |      |

| 3.4 Results                                                    |      |

| 3.4.1 Void Size Effect                                         |      |

| 3.4.2 Void Shape Effect                                        |      |

|                                                                | 39   |

| 3.4.4 Aspect Ratio Effect on Voided Microvias                  |      |

| 3.4.5 Material Property Effect on Voided Microvias             |      |

| 3.4.6 Potential Failure Sites                                  |      |

| 3.5 Discussion about the Voiding Effects                       |      |

| 3.6 Microvia Virtual Qualification                             |      |

| 3.7 Voided Microvias Acceptance Criterion                      |      |

| 3.8 Summary                                                    | 54   |

| Chapter 4: Development of a Regression Microvia Strain Life Model Usi | ing Response |

|-----------------------------------------------------------------------|--------------|

| Surface Method                                                        |              |

| 4.1 Design of Experiments                                             | 58           |

| 4.1.1 Control Variables from Geometric Design                         | 59           |

| 4.1.2 Control Variables from Material Properties                      | 60           |

| 4.1.3 Control Variables from Manufacturing Process                    | 61           |

| 4.1.4 Box-Behnken Design                                              |              |

| 4.2 Finite Element Modeling and Results                               | 65           |

| 4.2.1 Finite Element Models                                           | 67           |

| 4.2.2 Material Properties                                             |              |

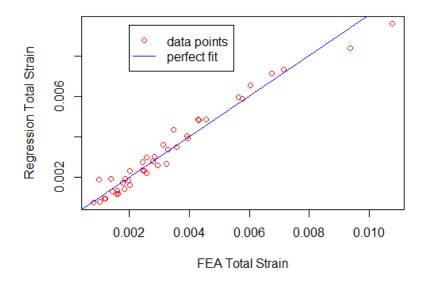

| 4.2.3 Total Strain from the FEA Experiments                           | 69           |

| 4.3 Regression Analysis using Response Surface Method                 |              |

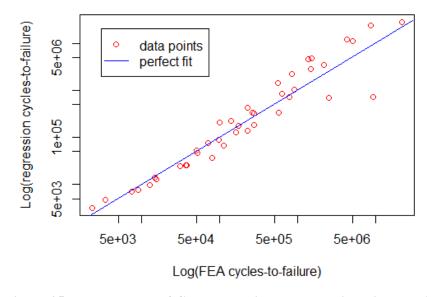

| 4.4 Discussion and Model Validation                                   |              |

| 4.4.1 Model Simplification Using Least Square                         | 74           |

| 4.4.2 Nonlinearity Analysis                                           | 77           |

| 4.4.3 Application Range and Limitations                               | 79           |

| 4.4.4 Validation of the Model                                         | 80           |

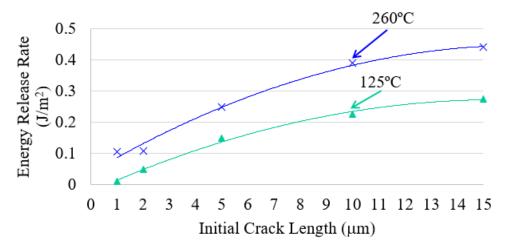

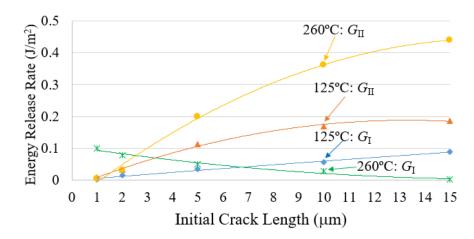

| 4.5 Summary                                                           | 83           |

| Chapter 5: Fracture Analysis for Microvia Interface Separation        | 86           |

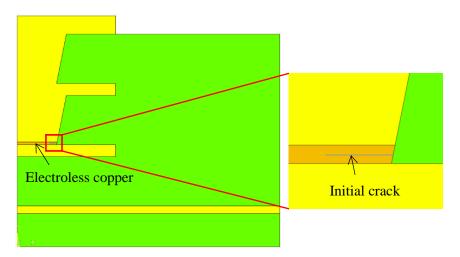

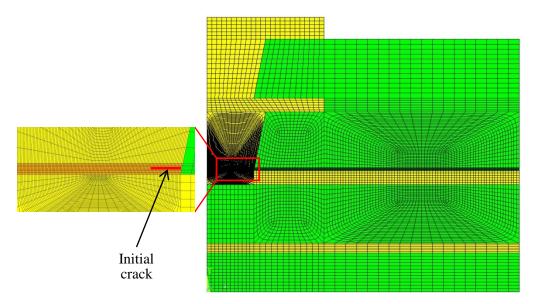

| 5.1 Fracture Analysis and Numerical Calculation                       | 87           |

| 5.2 2D Finite Element Modeling                                        | 90           |

| 5.3 Results and Discussion                                            | 93           |

| 5.4 Summary                                                           | 96           |

| Chapter 6: Contributions and Suggestions for Future Research          | 97           |

| 6.1 Contributions of this Dissertation                                | 97           |

| 6.2 Suggestions for Future Research                                   | 99           |

| Appendices                                                            | 101          |

| Bibliography                                                          | 104          |

## List of Tables

| Table 1: Geometry Dimension of the Microvia Models                   | 25  |

|----------------------------------------------------------------------|-----|

| Table 2: Dielectric Material Properties of the Microvia Models       | 29  |

| Table 3: Total Strains of Microvias with Different MRs               | 62  |

| Table 4: Three Levels of the Factors                                 | 65  |

| Table 5: Dielectric Material Properties                              | 69  |

| Table 6: Response Surface Result with Coded Variables                |     |

| Table 7: Analysis of Variance Table                                  | 71  |

| Table 8: Round 1 Least Square Simplification                         |     |

| Table 9: Round 2 Least Square Simplification                         | 75  |

| Table 10: First-Order Model with No Interactions                     | 77  |

| Table 11: First-Order Model with Pairwise Interactions               |     |

| Table 12: First-Order Model with Pairwise and Three-Way Interactions | 78  |

| Table 13: The Two Models with Highly Over-Predicted Life             | 79  |

| Table 14: Parameters for Model Validation                            | 81  |

| Table 15: Material Properties of Electroless Copper                  | 92  |

| Table A.I: Box-Behnken Design of the Experiments with Five Factors   | 101 |

| Table A.II: Parameters and FEA Results of the 41 Experiments         | 102 |

|                                                                      |     |

# List of Figures

| Figure 1: IC Packaging Feature Roadmap [2]                                          | . 2 |

|-------------------------------------------------------------------------------------|-----|

| Figure 2: Roadmap of HDI Key Attributes [3]                                         | . 2 |

| Figure 3: Diagram of Single Level Microvia                                          |     |

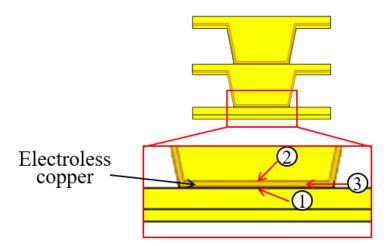

| Figure 4: Illustration of Electroless Copper Layer in a Two-Level Stacked Microvia  | 5   |

| Figure 5: Illustration of Microvia Filling                                          | . 6 |

| Figure 6: Diagram of HDI Board with Various Microvias                               | . 7 |

| Figure 7: Microvia Voiding (Cross-sectional View)                                   |     |

| Figure 8: Microvia Voiding (Top View)                                               |     |

| Figure 9: Stress Distribution in a Voided Microvia                                  | . 9 |

| Figure 10: Crack at Void Border after Thermal Shock Testing [11]                    | . 9 |

| Figure 11: Microvia Interface Separation after Thermal Cycling [12]                 | 10  |

| Figure 12: Microvia Structure Diagram in [22]                                       | 14  |

| Figure 13: Microvia Interface Separation due to Fracture in Electroless Copper [12] | 21  |

| Figure 14: Demonstration of Microvia Aspect Ratio                                   |     |

| Figure 15: Unit Cell and Quarter Model                                              | 27  |

| Figure 16: Microvia Finite Element Model and BCs                                    | 28  |

| Figure 17: Microvia Models of Different Void Shapes                                 | 35  |

| Figure 18: Definition of Void Locations                                             |     |

| Figure 19: Effect of Void Size on Microvia Fatigue Life                             | 37  |

| Figure 20: Effect of Void Shape on Microvia Fatigue Life                            | 39  |

| Figure 21: Effect of Void Location and Minimum Wall Thickness                       | 41  |

| Figure 22: Effect of Microvia Aspect Ratio on Microvia Fatigue Life                 | 42  |

| Figure 23: Effect of Microvia Aspect Ratio with Different Void Size                 | 43  |

| Figure 24: Effect of Dielectric Material Properties                                 | 44  |

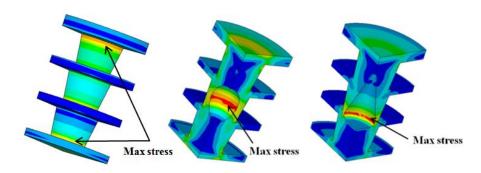

| Figure 25: Sites of Maximum von Mises Stress                                        | 45  |

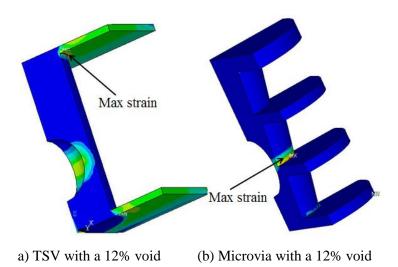

| Figure 26: Maximum Strain Sites in TSV and Microvia                                 | 48  |

| Figure 27: Microvia Virtual Qualification Method                                    | 50  |

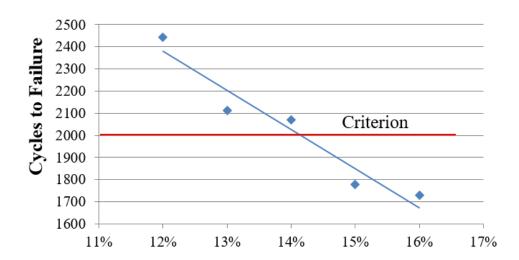

| Figure 28: Cycles to Failure vs. Void Area Ratio for 3-Level Stacked Microvias      | 53  |

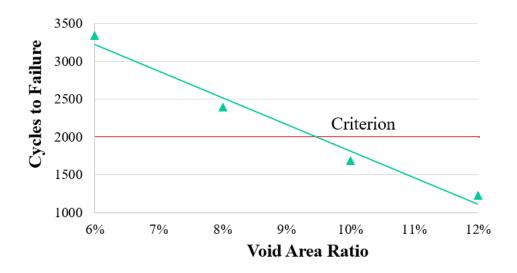

| Figure 29: Cycles to Failure vs. Void Area Ratio for 5-Level Stacked Microvias      | 54  |

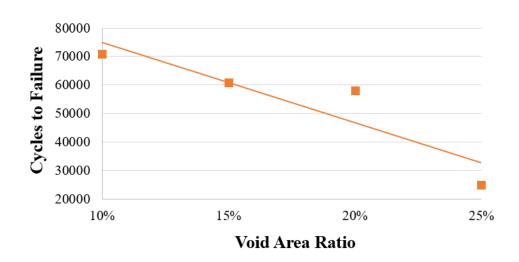

| Figure 30: Cycles to Failure vs. Void Area Ratio for Single-Level Microvias         | 54  |

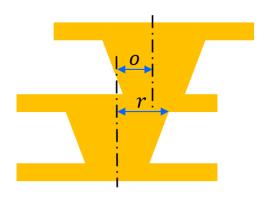

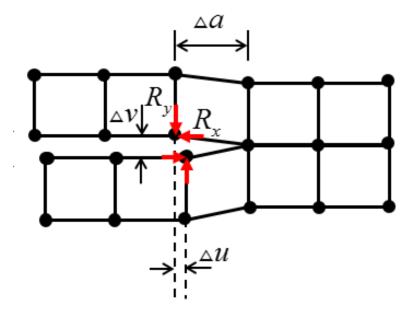

| Figure 31: Definition of MR (MR = $o/r$ )                                           | 62  |

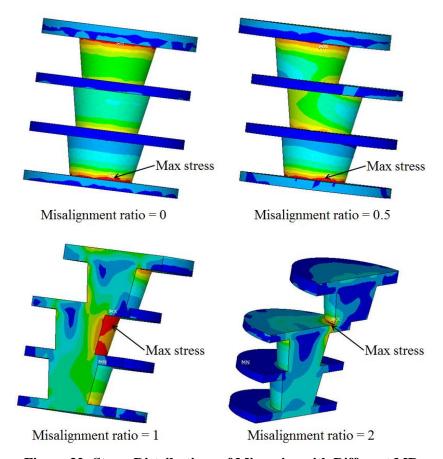

| Figure 32: Stress Distributions of Microvias with Different MRs                     | 63  |

| Figure 33: Voided Microvia Finite Element Model with BCs                            | 68  |

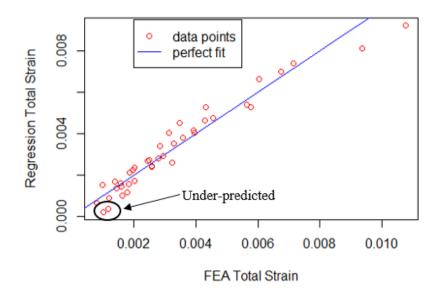

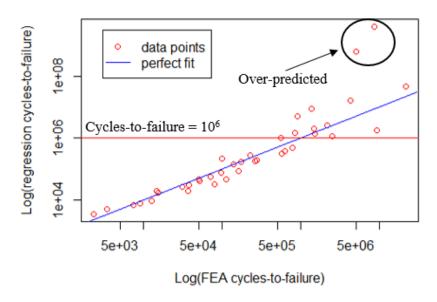

| Figure 34: Regression Model Predicted Strain vs. FEA Strain                         | 73  |

| Figure 35: Log-Log Plot of Cycles-to-Failure: Regression Fit vs FEA                 | 73  |

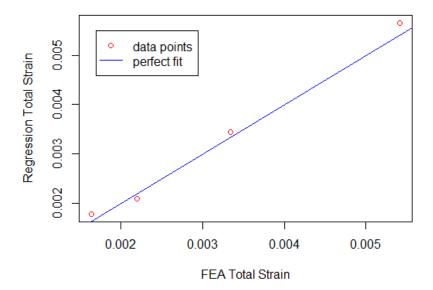

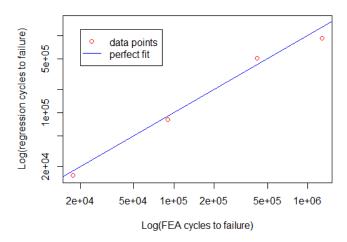

| Figure 36: Predicted Strain vs. FEA Strain                                          | 76  |

| Figure 37: Log-log Plot of Cycles-to-Failure: Final Regression Model vs. FEA        | 76  |

| Figure 38: Model Validation: Regression vs. FEA Strain                              |     |

| Figure 39: Model Validation: Log-log Plot for Regression vs. FEA Life               |     |

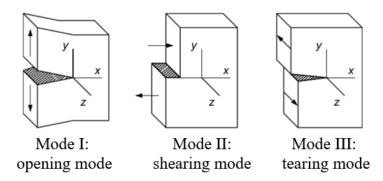

| Figure 40: Three Potential Microvia Interface Separation Locations                  |     |

| Figure 41: Three Fracture Modes [51]                                                |     |

| Figure 42: 2D Crack Geometry Schematic              | 90 |

|-----------------------------------------------------|----|

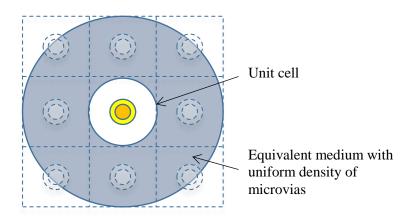

| Figure 43: Cylindrical Unit Cell                    | 90 |

| Figure 44: 2D Axisymmetric Model                    | 91 |

| Figure 45: Meshing Result of the Axisymmetric Model | 92 |

| Figure 46: Total Energy Release Rate                | 94 |

| Figure 47: Mode I and Mode II Energy Release Rate   | 95 |

### List of Abbreviations

ANOVA Analysis of Variance

AR Aspect Ratio

BC Boundary Condition

CALCE Center for Advanced Life Cycle Engineering

CTE Coefficient of Thermal Expansion

DOE Design of Experiment

FEA Finite Element Modeling

HDI High Density Interconnect

IST Interconnect Stress Test

I/O Input/Output

LDP Laser Drillable Prepreg

MCM Multi-Chip Module

MR Misalignment Ratio

MRTV-2.2 Motorola Reliability Test vehicle Version 2.2

NWA Non-Woven Aramid

PCB Printed Circuit Board

PP Prepreg

RCC Resin Coated Copper

RMS Response Surface Method

SBU Sequential Build-Up

TSV Through-Silicon Via

VQ Virtual Qualification

VCCT Virtual Crack Closure Technique

## Chapter 1: Introduction

The continuous increase in component performance and input/output interconnect (I/O) density, reduction in package size, and prevalence of hand-held applications have driven the adoption of high-density interconnects (HDIs) in component subtracts and printed circuit boards (PCBs) that allow a greater number of I/Os with smaller footprint area. (At the electronic component level, the solution is to employ flip-chip packages, chip-scale packages, direct chip attachments, as well as 3D packages using through-silicon vias (TSVs).) HDI substrates and PCBs use finer lines and spaces ( $\leq$ 100  $\mu$ m), smaller vias ( $\leq$ 150  $\mu$ m) and capture pads ( $\leq$ 400  $\mu$ m), and higher connection pad density (>20 pads/cm²) than conventional PCBs [1]. HDI technology makes use of microvias as electrical interconnects among different conductor layers.

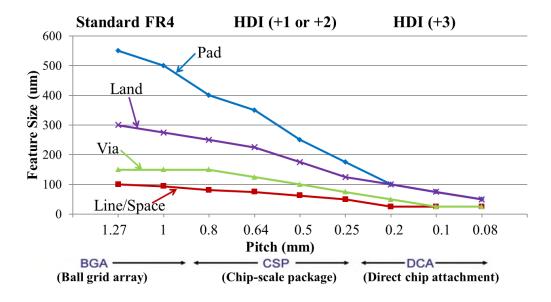

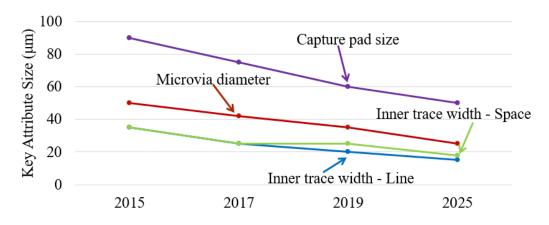

Figure 1 shows an IC packaging feature roadmap with via size, via-pad size, lines and spaces, and surface mount land size [2]. As the pitch of the package gets smaller, the attribute size (size of pad, land, via, and line/space) decreases, and the PCB technology advanced from standard FR4 to HDI circuit boards with increasing HDI layers. In recent years, the attribute size of HDI boards continually decreases. Figure 2 shows the HDI key attribute roadmap [3]. For example, the state of art of the microvia diameter is  $42 \,\mu m$  this year, and would be as small as  $25 \,\mu m$  in 2025. HDI/microvia circuit board has been widely used in the electronics industry. This chapter provides a brief introduction to microvias and presents the motivation of this dissertation.

Figure 1: IC Packaging Feature Roadmap [2]

Figure 2: Roadmap of HDI Key Attributes [3]

#### 1.1 Background

The HDI technology has been used in production of PCB boards since the late 1980s. The use of microvias is the most significant change from conventional PCBs to HDI circuit boards. Microvias play a key role as interconnects between different conductor layers in HDI circuit boards to accommodate the high I/O density of advanced

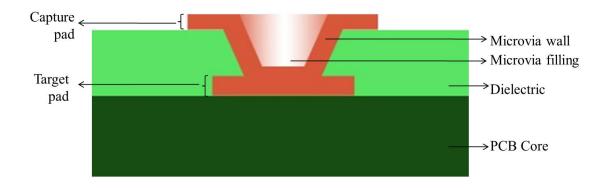

packages. Microvias are defined as blind or buried vias that are equal to or less than 150  $\mu$ m in diameter in IPC standards [4][5]. This definition focuses on single level microvias that transport signal/power between two adjacent conductor layers. Figure 3 shows the diagram of a single level microvia. At the top and bottom of the microvia are the capture pad and target pad, respectively, with the diameter equal to or less than 350  $\mu$ m [4][5].

Figure 3: Diagram of Single Level Microvia

Sequential build-up (SBU) technology is used to fabricate HDI circuit boards. The HDI layers are usually built up from a double-sided core or multilayer PCB ("core substrate" is used in the remaining of this document to refer to the core board or multilayer PCB in the middle of a HDI circuit board). The core substrate is typically manufactured using conventional PCB techniques. Then the HDI layers are built on both sides of the core substrate layer by layer with microvias. The SBU process consists of several steps: layer lamination, via formation, via metallization, copper electrodeposition, and via filling. There are multiple choices of the technologies and materials for each step.

There are a wide range of laminate materials that can be used for build-up layers on HDI boards, including laser drillable prepreg (LDP), resin coated copper (RCC), conventional prepreg (PP), polyimide, non-woven aramid (NWA) epoxy, photo imageable dry films and liquids, etc. [2]. There are many considerations and compromises when it comes to the choice of a dielectric material. For example, the chemical composition of the dielectric must be compatible with that of the resin in the core substrate; the material properties such as the coefficient of thermal expansion (CTE) and glass transition temperature must be sufficiently well-matched between the dielectric and the core substrate; the SBU material must adhere well to the copper on the core substrate; and the construction of the SBU dielectric must compactable with the microvia formation process (e.g. photoimageable materials should be used for the photo-defined microvias). Today, FR4 type of dielectric materials are widely used in the HDI layers.

Depending on the lamination materials and the via formation method, microvia holes are created through the capture pad and the dielectric material either individually or simultaneously. Holes terminate at the target pad. There are four microvia hole formation methods—mechanical drilling, laser ablation, photo imaging, etching including chemical etching and plasma etching [4],[6]. These methods have different limits on the size of the microvias they can form, as well as significant differences in cost efficiency and material selection. Laser ablation is the most widely used via formation methods due to its compatible to most HDI materials.

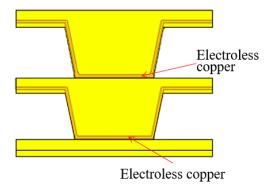

Metallization is a process that renders the microvia hole conductive (known as "making hole conductive" or MHC), and prepares the microvia for copper electrodeposition. There are several processes that can be utilized for microvia metallization [2]: electroless copper, palladium-based direct metallization, graphite, carbon black, and conductive polymer. The microvia is then plated with electrolytic copper at the side wall and the base, or plated closed to fill the microvia. Electroless copper is the most common process for microvia hole metallization. Figure 4 illustrates the electroless copper layer in a two-level stacked microvia.

Figure 4: Illustration of Electroless Copper Layer in a Two-Level Stacked Microvia

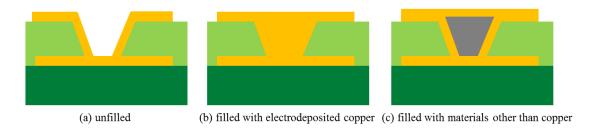

Microvias can be filled with epoxy resin (b-stage) during a sequential lamination process [7], filled with non-conductive paste as a separate process [7], screen printed closed with copper paste [7], filled with solder paste [8][9], or plated closed with electroplated copper [10]. Microvias filled with a non-conductive or conductive fill other than copper require a copper cap to be processed onto the top of the microvia fill material [7]. Blind microvias at the top layer of the PCB could be left unfilled, especially at the early age of microcia application. Figure 5 illustrates different microvia filling results.

Figure 5: Illustration of Microvia Filling

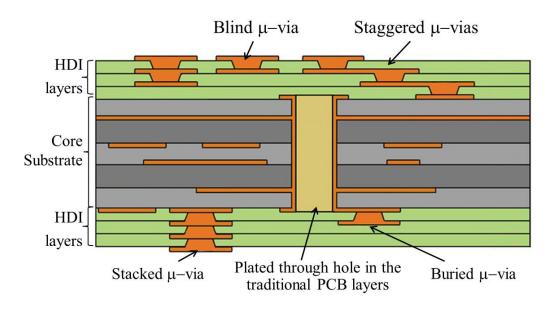

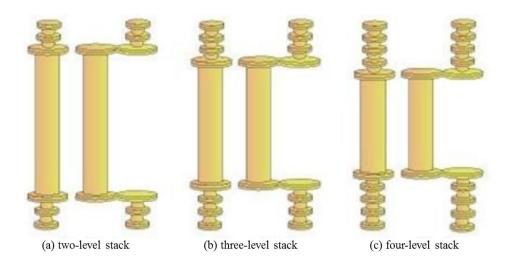

Since the adoption of microvia technology, HDI circuit boards have been widely used in the electronics industry. Advances in miniaturized electronic devices have led to the evolution of microvias from single-level to stacked structures that intersect multiple HDI layers. A stacked microvia is usually filled with electroplated copper to make electrical interconnections between multiple conductor layers and provide structural support for the outer level(s) of the microvia or for a component mounted on the outermost copper pad. Figure 6 shows a schematic diagram of a [3+6+3]-layer HDI board (3 HDI layers on each side of the board, and 6 core substrate layers in the middle) with stacked, staggered, blind and buried microvias. In stacked microvias, the terms of capture pad and target pad are usually used exchangeable. In this dissertation, the researcher takes the original capture and target pad definitions as shown in Figure 3 for each level of microvias in the stacked structures.

Figure 6: Diagram of HDI Board with Various Microvias

#### 1.2 Motivation

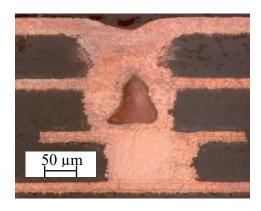

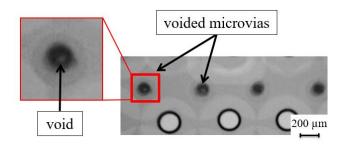

A challenge for HDI circuit board development is to fabricate microvias without generating voids or other defects in the electrodeposited copper structures. The microvia hole is a dead-end structure with a very small diameter. During microvia plating and filling process, voids can be created when gas is trapped in the electrodeposited copper, the exchange of fresh solution is inefficient in the hole due to limitation in throwing power, or improper plating parameters are applied (e.g., improper current density). Figure 7, shows a 3-level stacked microvia with a void in a cross-sectional view. The voiding defect can also be detected using X-Ray. As showed in Figure 8, non-voided microvias are dark dots under X-Ray when looked through the circuit board thickness direction, but voided microvias have a white spot in the center of the dark dot that indicates material missing.

Figure 7: Microvia Voiding (Cross-sectional View)

Figure 8: Microvia Voiding (Top View)

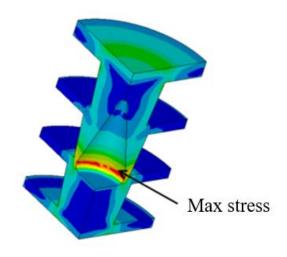

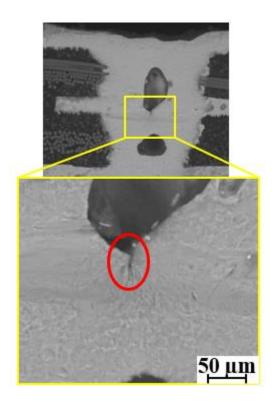

When voids are present, localized stress concentration on the electrodeposited copper structure can degrade the reliability of microvias. Figure 9 shows the stress state in a voided microvia under thermal loading generated using finite element analysis (FEA). The max stress is located on the boarder of the void, and that is the potential failure site of the voided microvia. A thermal shock test of microvias conducted at the Center for Advance Life Cycle Engineering (CALCE) at the University of Maryland shows a crack on the void boarder after the testing (Figure 10) [11]. However, the effect of voids on the lifetime of copper-filled microvias has not been studied.

Figure 9: Stress Distribution in a Voided Microvia

Figure 10: Crack at Void Border after Thermal Shock Testing [11]

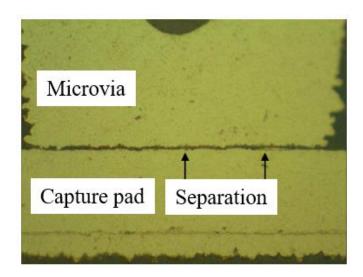

Another defect that affects microvia reliability is the poor quality of electroless copper.

Microvia interface separation is a common failure observed in HDI circuit boards due

to inferior bonding between the microvia base and the target pad [7],[12]-[14]. Figure 11 shows a microvia interface separation failure. However, there is no published study that quantitatively address the factors that result in microvia interface separation.

Figure 11: Microvia Interface Separation after Thermal Cycling [12]

#### 1.3 Overview of the Dissertation

The structure of the remaining of the dissertation is as follows. Chapter 2 presents the literature review on reliability research of microvias, puts forward the problem statement based on the literature review, and provides the objectives of this dissertation. Chapter 3 discusses a parametric study of voiding effects on microvia fatigue life. Development of a second order regression model for microvia life prediction using surface response mothed is presented in Chapter 4. Chapter 5 quantitatively addresses the factors that affect microvia interface separation using fracture analysis. Chapter 6 presents the contributions of this dissertation and suggested future work.

### Chapter 2: Literature Review and Objectives

Microvia reliability studies have been conducted since its invention to determine whether this structure is durable. The reliability studies at the early age of the microvias were basically a go/no-go type of assessment done by the electronics industry. Typically, the same HDI test vehicles were fabricated by different manufacturers using different methods to evaluate the HDI technologies and manufactures' fabrication capacities. Later, industry participants and academic researchers started to conduct reliability data analysis, look into the causes of microvias failures, and predict microvia lifetimes using numerical analysis and fatigue life estimation.

Most of the microvia reliability research in the literature has focused on thermomechanical reliability of single-level flaw-free microvias. Few researchers have studied the reliability of stacked microvias, or addressed the effect of defects introduced during manufacturing processes, such as voids and poor electroless copper quality on reliability of microvias. The current microvia qualification methods and standards lag behind the HDI technologies. The electronics industry does not have a tool to determine the lifetime of copper filled stacked microvias in HDI circuit boards, nor a tool to decide if certain voiding on microvias is acceptable for a field application. In addition, the factors that affect microvia interface separation were not quantitatively studied.

#### 2.1 Previous Work and Research Gaps

In this section, the researcher reviews previous work on microvia reliability, and addresses the gap in the literature regarding the effects of voiding and poor electroless copper qualify on the lifetime of microvias.

#### 2.1.1 Reliability Testing on Microvias

To assess the reliability of microvias, several test methods exist. The most commonly used tests is liquid-to-liquid or air-to-air thermal shock [12][15]–[22]. The thermal shock test is typically carried out to 2000 thermal cycles or to failure on 50% of the microvia coupons, with temperature extremes of –55 °C and +125 °C. Researchers also used interconnect stress test (IST) [23] to evaluate microvia reliability in HDI boards [7][12][24]. Solder reflow simulation test was performed to mimic the temperature excursion in a solder reflow process [25] (e.g., up to 260 °C for lead-free soldering). Solder reflow simulation can be used as an independent test [12], or as preconditioning prior to thermal shock or IST tests [7],[12],[21][22],[24].

Microvia reliability testing has focused on the experimental assessment of reliability of single-level unfilled or epoxy-filled microvias. Davignon [17] overviewed the MRTV-2.2 microvia test vehicle and presented the reliability tests that the test vehicle was subjected to. The test vehicle was a 4 layer circuit board with single level blind microvias. The purpose of this project was to determine the feasibility and ability of each microvia technology in meeting the general and specific requirements of the HDI

applications. Rasul *et al.* [16] reported the test results of the MRTV-2.2 coupon to evaluate different HDI technologies and suppliers' fabrication capacities. Liquid-to-liquid thermal shock test from -55°C to 125°C was used to assess the reliability of the microvias.

Liu et al. [18] conducted liquid-to-liquid thermal shock testing for 2000 cycles to investigate the reliability of photo defined microvias. Cracks were observed at the foot (the joint of microvia base and side wall) of failed the microvias, and the early failures were found due to process-related defects, such as thin electrolytic copper plating at the foot of the microvia. Ramakrishna et al. [19][20] conducted air-to-air thermal shock test for 2000 cycles to study the effects of the geometry and process parameters on HDI yield and reliability. It was concluded that large aspect ratio (AR) tended to cause lower yield and worse reliability. Liu et al. [21] examined low loss thin dielectric laminate and thin core organic systems for use in ultra-high density build up substrates. Three lead-free solder reflow cycles and air-to-air thermal shock test were conducted to examine microvia reliability in the HDI substrate. The authors concluded that the material was reliable up to 1400 thermal shock cycles (a go/no-go test). The microvas tested in [18]-[20] were single level unfilled microvia or filled with epoxy, and [21] involved single-level microvias either unfilled or electrolytic copper filled.

Andrews *et al.* [24] conducted interconnect stress test (IST) with solder reflow preconditions on TV6200 test vehicles to establish criteria for HDI board acceptance and rejection. It was concluded that testing to 1000 cycles at 190°C, IST was capable

of differentiating between good and marginal coupons. This was a go/no-go type of test and acceptance criteria, and the test coupon involves only single-level blind microvias.

Studies on reliability assessment of copper-filled stacked microvias were very limited. In particular, Birch [7] tested multiple-level copper-filled microvias using IST, and Weibull analysis showed that 2-level stacked microvias experienced about 20 times more cycles to failure than 4-level stacked microvias. Heer and Wong [22] found that test coupons (the microvia structure diagram of the test coupons is shown in Figure 12) with 2-level stacked microvias on or off buried vias failed earlier than 3- and 4- level microvias in their IST tests. However, the failure was on the longer barrel of the buried vias.

Figure 12: Microvia Structure Diagram in [22]

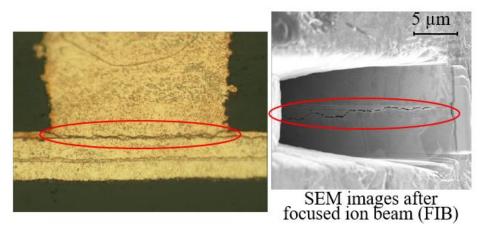

CALCE had the first attempt in the literature to investigate the effect of voiding on microvia reliability. The researcher's colleague, Bakhshi *et al.* [26] took cross-section

of copper-filled microvias from HDI circuit boards. The cross-sections include single-level, 2-level and 3-level microvias; some of the microvias had voids while others did not. Bakhshi *et al.* conducted liquid-to-liquid thermal shock testing (–55 °C to +125 °C) for 500 cycles on the cross-sectioned microvias, and observed microvia degradation (crack formation and void expansion) on 7 voided microvias and 2 non-voided microvias. Therefore, voids accelerated degradation in sectioned microvias.

In summary, most literature on microvia reliability assessment focused on go/no-go type of testing for single level microvias. Only a few researchers examined reliability of stacked microvias. Except Bakhshi *et al.*, there was no effort to investigate the effect of manufacturing defects on reliability of copper-filled microvias. In Bakhshi *et al.*'s study, it was not verified whether sectioned microvias were representative of unsectioned microvias under thermal loading; Bakhshi *et al.* did not test the microvias to failure.

#### 2.1.2 Numerical Analysis on Microvias

Researchers have conducted numerical analyses on microvia structures using FEA. Finite element models were developed to determine the stress or strain state on the microvia under thermal loading. Some researchers further used the total strain from the FEA as input to copper fatigue life models to estimation the cycles to failure of the microvias.

Prabhu *et al.* [27] examined the effect of accelerated temperature cycling and thermal shock on the reliability of single-level epoxy filled microvias using FEA. Stress

distribution on the microvia structure was provided, and fatigue life of the microvias under different thermal loading was estimated.

Ogunjimi et al. [28] conducted FEA for single-level epoxy filled microvias and performed factorial design of experiment (DOE) to investigate the effect of manufacturing and design process variables on microvia fatigue life. The authors ranked the effects of the variables on microvia fatigue life in the order of importance as concentration factor, copper ductility, via wall thickness, wall angle, and epoxy height.

Ramakrishna *et al.* [19][20] conducted FEA for single-level unfilled blind microvias under thermal shock condition to investigate the effects of the geometry and material properties on the reliability of microvias. The parameters they examined included microvia wall thickness, wall angle, diameter, and dielectric thickness and properties.

Wang and Lai [29] investigated the potential failure sites of single-level microvias in the substrate of a multi-chip module (MCM) using submodeling technique in FEA. Both unfilled microvias and electrolytic copper filled microvias were examined. The authors found that unfilled microvias could have a higher stress than copper filled microvias by up to 5%.

Wang *et al.* [30] estimated the fatigue life of single-level unfilled blind microvias with a component assembled to it. In their work, the originally unfilled microvia barrel was

either fully filled with solder or remained completely hollow after assembling the component. They found that a hollow microvia had up to 35% shorter fatigue life than a fully solder-filled microvia.

Ko *et al.* [31] modeled three-level stacked microvias and found that the likely potential failure sites were at the narrow region (the base) of the middle- and lower-level microvias.

Most FEA studies and fatigue life predictions on microvias in the literature focused on single-level defect-free microvias. According to the work of Wang and Lai [29] and Wang *et al.* [30], fully copper or solder filled microvias were more durable than completely unfilled microvias. However, the effect of different void conditions (e.g., different void shapes, sizes, locations) on copper-filled stacked microvias was not studied.

#### 2.1.3 Regression Microvia Life Model

Sexton [32] developed a first order strain life prediction model for single-level epoxy-filled buried microvia. Sexton conducted a two level full factorial DOE using FEA simulation. The DOE factors were microvia design factors, including capture pad radius, microvia hole radius, dielectric thickness, microvia wall plating thickness. By identifying the most significant factors and factor couples using analysis of variance (ANOVA), a first order life prediction model was developed using least square regression.

A regression microvia life prediction model is desirable to quickly qualify an HDI circuit boards. However, Sexton focused on single level epoxy-filled microvias, and his model is not applicable to the more popular copper-filled stacked microvias of today. Also, Sexton's regression model cannot capture higher-order relationship between the microvia design parameter and the model output (total strain, which is directly related to the lifetime). Moreover, Sexton's regression model only considered microvia geometry parameters, but did not take into account material properties and microvia defects.

#### 2.1.4 IPC Standards on Microvia Voiding

In the industry standards, there are regulations on HDI acceptance considering manufacturing defects. IPC standards about copper filling requirements were reviewed.

IPC-6012D-RedLine [33] made the first attempt to specify the copper filling requirement in electrolytic copper filled microias. According to the standard, voids in blind or buried copper-filled microvias are acceptable if they are completely encapsulated and do not exceed 25% of the area of the filled microvia in the central cross-sectional plane.

The IPC standard does not consider the effects of different voiding conditions (e.g. shapes and locations) and microvia design (e.g. material properties and AR), nor do they address the filling requirement in stacked microvias.

#### 2.1.5 TSV Voiding Research

Void-free filling of vias is also a challenge associated with the electroplating of TSVs, which are electrical interconnections through silicon substrates in 3D packages. The effect of voids on thermo-mechanical stress/strain of copper-plated TSVs has been studied using finite element modeling by several researchers. Kinoshita et al. [34],[35] compared the stress in the copper and silicon with and without a void. They concluded that fatigue fracture of TSVs under either operational or reflow conditions was unlikely, although they did not provide justification for their claim. The authors modeled an elliptical void of a fixed size, shape, and location, and did not vary the void characteristics in their study. Sun et al. [36] simulated TSVs containing voids of varying size and location. They presented stress and strain results along the void boundary and the Cu/SO<sub>2</sub> interface, but it was inconclusive how voids affect TSV lifetime. Moreover, the authors did not consider other parameters, such as void shape and TSV AR, on stress and strain in electrodeposited copper structures. Liu et al. [37] modeled different void volume fractions, sizes, and locations in copper TSV structures of a fixed AR. They studied the case of multiple small, spherical voids within a single TSV. While equivalent plastic strain was found to increase with increasing void volume fraction, no clear effect of void size or location was evident. The effect of void shape on thermo-mechanical stress and strain was not studied.

There are three major reasons why the thermo-mechanical stress/strain analysis results of TSVs cannot be adopted for microvias. Firstly, the material properties of dielectrics in microvias are significantly different from those of silicon and silicon dioxide (used

as an insulator between copper and silicon) in TSVs. For example, Young's moduli of silicon and silicon dioxide are about 130 GPa and 70 GPa, respectively; however, Young's modulus of dielectrics in HDI boards is usually less than 30 GPa in the inplane direction (X-/Y-direction), and less than 10 GPa in the out-of-plane direction (Zdirection). The more compliant dielectrics in microvia structures, compared to silicon and silicon dioxide in TSV structures, tend to deform more easily under the applied thermal load, which results in a smaller stress/strain level within the copper in microvias. According to the authors' modeling results, the equivalent plastic strain in a microvia is about an order of magnitude lower than that in a TSV of the same AR. Secondly, the geometry of a TSV is usually a solid cylinder, while the geometry of a microvia consists of several stacked conical structures due to the SBU process. The tapered shape of microvias combined with voids results in stress/strain distributions which differ from those in voided cylindrical TSV structures. Additionally, since the TSV voiding simulation papers in the literature were limited to the analysis of maximum stress/strain in the copper structure, they do not offer a means to estimate the voiding effect on TSV reliability (i.e., the predicted fatigue life of TSVs).

#### 2.1.6 Microvia Interface Separation

Microvia interface separation is a commonly observed failure in HDI boards due to inferior bonding between the microvia base and the target pad [7][12][13][14]. poor quality of electroless copper is recognized to be responsible of the inferior bonding between the base of the microvia and the target pad. There were very limited discussion

in the literature regarding the electroless copper quality and microvia interface separation.

Birch [7] and Reid [13] believed incomplete cleaning of residues from laser drilling or poor micro-etching of the target pad caused poor electroless copper and weak bonding between the microvia base and the target pad. Lesniewski [12] observed that the separation was within the electroless copper layer from his testing result, and the separation was due to brittle fracture of electroless copper. Figure 13 shows the fracture in the electroless copper layer.

Figure 13: Microvia Interface Separation due to Fracture in Electroless Copper [12]

However, there is no published study in the literature that quantitatively addresses factors that result in microvia interface separation. In the FEA studies, the researchers have always modeled all copper layers generated from different manufacturing process as identical electrodeposited copper in the microvia structure for simplification.

#### 2.2 Problem Statement

Microvia technology has evolved from single-level buried or blind structures to copper-filled stacked microvias. However the reliability research and qualification methods on microvias still dwell on assessment and analysis means for single-level microvias. The electronic industry has a big concern on reliability of copper-filled stacked microvias, especially when defects are induced from manufacturing process. There was no sufficient work on copper-filled stacked microvia reliability study, nor did researchers analyze the effect of manufacturing defects of copper-filled microvias, except for the preliminary voiding investigation from CALCE, which was not verified on unsectioned microvias and not tested to failure.

Voids potentially generate stress concentration on microvia structures. However, the effect of different voiding conditions (shapes, sizes, and locations) on the lifetime of copper-filled microvias has not been studied.

A model for microvia life prediction is desired. However, a first-order regression model does not capture needed nonlinear relationship between microvia parameters and total strain. Moreover, there is no life model for copper-filled microvias, and no existing model accounts for voiding effect on microvia fatigue life.

Interface separation is a commonly observed microvia failure. However, no published study quantitatively discusses the factors that affect microvia interface separation.

#### 2.3 Objectives of the Dissertation

The objective of this dissertation is to determine the effects of manufacturing defects, such as voiding and poor electroless copper on reliability of copper-filled stacked microvias.

Firstly, the researcher aims to quantitatively determine the voiding effect on the lifetime (cycles to failure) of copper-filled stacked microvias with different void characteristics, such as different shapes, sizes, and locations. This objective will be achieved through a parametric study using FEA to simulate the void characteristics and microvia design parameters.

Secondly, a regression model will be developed to predict the fatigue life (cycles to failure) of copper-filled stacked microvias under cyclic thermal loading. The inputs of the regression model are microvia geometry, material and defect parameters. Therefore, the microvia life model will take into account the voiding effect. The model will capture second-order relationships between the input parameters and the total strain that is used for fatigue life estimation.

Thirdly, the researcher will quantitatively determine how structure flaw (initial crack length) in electroless copper affects the likelihood of microvia interface separation under different thermal loading conditions.

# Chapter 3: Parametric Study on Microvia Voiding Effects

A parametric study was conducted to investigate the effects of voids on the thermomechanical reliability of copper-filled stacked microvias using finite element modeling and strain-based fatigue life estimation. In this study, different voiding characteristics (size, shape, location) in stacked microvias of different ARs with different dielectric material properties were modeled to investigate how voids affect the reliability of the microvias under cyclic thermal loading.

3D finite element models were created to study the stress/strain state in the microvias under thermal loading and predict the lifetime of microvias in bare HDI PCBs. Although HDI substrates are also used within packaged parts, when a die is attached to an HDI substrate, the stress state in the microvias is different from that in a bare HDI board. This is due to the differences in the boundary conditions between HDI layers constrained on one side by conventional PCB layers as in a bare HDI board, and HDI layers constrained between a die, die attach adhesive, epoxy molding compound, and lead frame structures as in a packaged part. Due to the above differences, and the differences in processing conditions, materials, and qualification requirements for boards as compared to parts, the scope of this study has been limited to modeling microvias in bare HDI boards.

#### 3.1 Finite Element Modeling

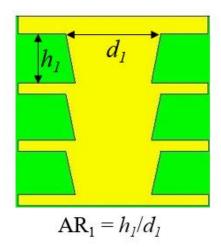

The geometric dimensions of the microvia were based on a [3+6+3]-layer commercial HDI board under study. Without loss of generality, microvias with different ARs were modeled. In the stacked microvias, the center of the microvias were assumed to be perfectly aligned between different levels. The model dimensions are listed in Table 1. AR was defined for each level of the stacked microvias as the ratio of dielectric thickness to the top microvia diameter. Figure 14 demonstrates how the AR of the first level of microvia was defined in the stacked microvia. The AR of the commercial HDI board under investigation was 0.5. The AR of 0.25 was simulated by reducing the dielectric thickness to half and keeping the other parameters the same as the commercial HDI board. The AR of 0.75 was simulated in two ways—by increasing the dielectric thickness to 1.5 times of the commercial HDI board, or by reducing the microvia diameter to 2/3 of the commercial HDI board. The simulation of different microvia geometries was designed to study how geometry influences voided microvia reliability, although some of the dielectric thicknesses or microvia diameters in the table may not be used in practice.

**Table 1: Geometry Dimension of the Microvia Models**

|           |                      | Dimension (µm) |      |       |      |  |  |

|-----------|----------------------|----------------|------|-------|------|--|--|

|           | Element              | AR =           | AR = | AR =  | AR = |  |  |

|           |                      | 0.5            | 0.25 | 0.75  | 0.75 |  |  |

| Thickness | 1st copper layer     | 28             | 28   | 28    | 28   |  |  |

|           | 1st dielectric layer | 75             | 37.5 | 112.5 | 75   |  |  |

|           | 2nd copper layer     | 18             | 18   | 18    | 18   |  |  |

|           | 2nd dielectric layer | 75             | 37.5 | 112.5 | 75   |  |  |

|           | 3rd copper layer     | 18             | 18   | 18    | 18   |  |  |

|           | 3rd dielectric layer | 75             | 37.5 | 112.5 | 75   |  |  |

|           | 4th copper layer     | 18             | 18   | 18    | 18   |  |  |

|           | 4th dielectric layer | 75             | 75   | 75    | 75   |  |  |

|                                      | 5th copper layer        | 12  | 12  | 12  | 12  |

|--------------------------------------|-------------------------|-----|-----|-----|-----|

|                                      | 5th dielectric layer    | 105 | 105 | 105 | 105 |

|                                      | 6th copper layer        | 12  | 12  | 12  | 12  |

|                                      | middle dielectric layer | 80  | 80  | 80  | 80  |

| Microvia                             | Тор                     | 150 | 150 | 150 | 100 |

| diameter                             | Bottom                  | 120 | 135 | 120 | 80  |

| Microvia capture/target pad diameter |                         | 300 | 300 | 300 | 300 |

| Distance between adjacent microvias  |                         | 800 | 800 | 800 | 800 |

Figure 14: Demonstration of Microvia Aspect Ratio

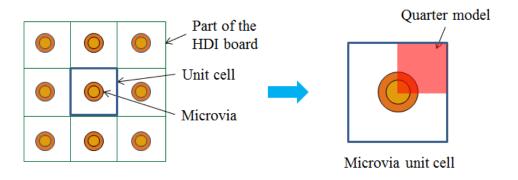

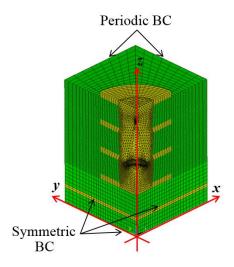

#### 3.1.1 Microvia Unit Cell

The in-plane dimensions of an HDI board are orders of magnitude larger than the height of a microvia, and there can be thousands to millions of microvias in a single HDI board. In this study, a "unit cell" is modeled containing only one microvia structure [38][39][40]. Periodic boundary conditions (BCs) were imposed on the unit cell to simulate the presence of the surrounding microvias and board materials. As shown in Figure 15, the unit cell extends halfway to the neighboring microvias in the same row or column in the periodic arrangement. The periodic BCs permit the unit cell boundaries to deform, but constrain them to remain in-plane and parallel to the original

faces. The constraints of the periodic BCs are tighter than free BCs, which do not constrain the in-plane displacement, but looser than complete constraints of displacement in the PCB plane, which may be overly restrictive and unrealistic. The periodic BCs guarantee the continuity of the unit cell from the rest of HDI board. Therefore, when the unit cell deforms, the entire board is compatible to the deformation.

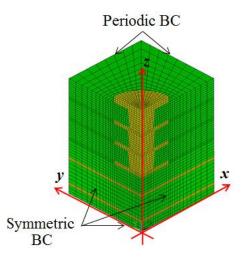

Figure 15: Unit Cell and Quarter Model

Only the top half of the HDI board was modeled due to symmetry to the board midplane; a quarter model was used due to symmetry of the unit cell. Figure 16 shows the 3D quarter model with meshing for the non-voided microvia. The number of divisions of each line of the solid model was specified for meshing. The meshing on and around the microvia was finer, and the meshing of the dielectric far away from the microvia was coarser. The meshing of different microvia models had the same refined level for different voiding conditions, which made the models comparable.

Figure 16: Microvia Finite Element Model and BCs

### 3.1.2 Material Properties

The HDI circuit boards consist mainly of two types of materials—fabric-reinforced dielectric and electrodeposited copper. The dielectric is an orthotropic material with two principal material directions (x- and y-directions) orthogonal to each other in the board plane, and a third direction (z-direction) along the plane normal direction. In this study, the dielectric material properties were based on EM-285 [41] a lead-free and halogen-free material widely used for commercial HDI boards. The dielectric material properties are shown in Table 2. The elastic modulus for the x- and y-directions at different temperatures, and the CTE below and above the glass transition temperature ( $T_g$ ) were measured by the authors and were found to fall within the range of reported FR4 type of material properties in the literature. Other properties in Table 2 were obtained from references [40][42] for equivalent dielectric materials. Through experimental measurement, the authors found that the loss modulus (the ratio of viscous

stress to strain) of the dielectric material below  $T_{\rm g}$  is negligible compared to the storage modulus (the ratio of elastic stress to strain). The temperature excursion of reflow cycles is short, so the viscosity of the material above  $T_{\rm g}$  does not have a significant effect on the copper stress/strain distribution. Therefore, the dielectric was modeled as an elastic material under the loading range of this study. This simplification of the dielectric material model is widely used for PCB modeling in the literature [38][39][40][42][43]. Table 2 lists the dielectric material properties for the majority of microvia models in this study. Besides these properties, two different z-axis CTEs and three different z-axis elastic moduli were used to investigate the effect of material properties on microvia reliability.

**Table 2: Dielectric Material Properties of the Microvia Models**

| Temp                                    | Below T <sub>g</sub> |     |    |    |     |      | Above T <sub>g</sub> |     |     |     |

|-----------------------------------------|----------------------|-----|----|----|-----|------|----------------------|-----|-----|-----|

| (° <b>C</b> )                           | -55                  | -15 | 25 | 65 | 105 | 125  | 145                  | 185 | 225 | 265 |

| $\boldsymbol{E}_{\boldsymbol{x}}$ (GPa) | 27                   | 26  | 25 | 24 | 22  | 20   | 17                   | 12  | 10  | 9.2 |

| $\boldsymbol{E_y}$ (GPa)                | 28                   | 28  | 28 | 27 | 25  | 23   | 20                   | 14  | 12  | 11  |

| $E_z$ (GPa)                             | 7.45                 |     |    |    |     | 1.04 |                      |     |     |     |

| $G_{xy}$ (GPa)                          | 15                   |     |    |    |     |      | 1.35                 |     |     |     |

| $G_{yz}$ (GPa)                          | 2.4                  |     |    |    |     |      | 1.47                 |     |     |     |

| $G_{xz}$ (GPa)                          | 2.4                  |     |    |    |     |      | 1.47                 |     |     |     |

| $ u_{xy} $                              | 0.13                 |     |    |    |     | 0.13 |                      |     |     |     |

| $ u_{yz} $                              | 0.42                 |     |    |    |     | 0.42 |                      |     |     |     |

| $ u_{\mathrm{xz}} $                     | 0.42                 |     |    |    |     |      | 0.42                 |     |     |     |

| $\alpha_x$ (ppm/°C)                     | 16.7                 |     |    |    |     | 7.25 |                      |     |     |     |

| $\alpha_y$ (ppm/°C)                     | 16.7                 |     |    |    |     | 7.25 |                      |     |     |     |

| $\alpha_z$ (ppm/°C)                     | 49.4                 |     |    |    |     | 237  |                      |     |     |     |

Electroplated copper is used for the conductor layers and microvia structures in the HDI boards. The electroplated copper was modeled as an elastic-plastic material with kinematic hardening. The elastic modulus of the copper was measured using

nanoindentation in the authors' lab. To model the plasticity of the copper, the stress-strain relationship is simulated using the well-accepted Ramberg-Osgood model:

$$\varepsilon = \frac{\sigma}{E} + \left(\frac{\sigma}{K}\right)^{\frac{1}{n}} \tag{1}$$

where  $\varepsilon$  is strain,  $\sigma$  is stress, E=127 GPa is the elastic modulus, and K=634 MPa and n=0.15 are material constants. The CTE of copper is 17 ppm/°C, and the Poisson's ratio is 0.34 [40][42].

#### 3.1.3 Thermal Loading Conditions

FEA was conducted to determine the thermo-mechanical stress and strain in microvias under thermal loading. Firstly, a lead-free solder reflow excursion with a peak temperature of 260 °C was simulated on the microvias. The reflow profile complies with that given in IPC/JEDEC J-STD-020D.1 [25]. Three reflow cycles were applied, considering the possibility of rework. Then a cyclic thermal load between –55 °C and +125 °C was simulated. Each thermal cycle consisted of 5-min dwells at the high and low temperatures, with 10-min ramps between the two temperature extremes.

Under the thermal load, the microvia experienced cyclic tensile and compressive stresses. The stresses and corresponding strains were due to CTE mismatch between the dielectric material and copper. In this study, von Mises stress was monitored to determine the location of maximum damage and potential failure site; the total strain generated per load cycle was used to predict the cycles to failure.

#### 3.2 Fatigue Life Prediction

The total strain of the microvias at the potential failure sites is generated from the FEA. Then the microvias fatigue life (cycles to failure) was estimated using a combined Basquin and Coffin–Manson fatigue model. Moreover, Miner's rule was used to take into account the damage accumulation from solder reflow and thermal cycling loading conditions.

#### 3.2.1 Physics-of-Failure Model for Electrolytic Copper Fatigue

The total strain that the electrolytic copper experienced governs the fatigue life of the microvias. The total strain consists of elastic and plastic strains:

$$\Delta \varepsilon = \Delta \varepsilon_{el} + \Delta \varepsilon_{pl} \tag{2}$$

where  $\Delta \varepsilon$  is the total strain, and  $\Delta \varepsilon_{el}$  and  $\Delta \varepsilon_{pl}$  indicate elastic and plastic strains, respectively. The elastic and plastic strains for electrolytic copper derived by Engelmaier [44] are expressed as

$$\Delta \varepsilon_{el} = 0.9 \frac{S_u}{E} \left[ \frac{\exp(D_f)}{0.36} \right]^{0.1785 \log(10^5/N_f)}$$

(3)

and

$$\Delta \varepsilon_{pl} = N_f^{-0.6} D_f^{0.75} \tag{4}$$

where  $S_u$  is the tensile strength of the material, E is the elastic modulus of the material,  $D_f$  is the fatigue ductility coefficient, and  $N_f$  is the number of cycles to failure. Therefore, the total strain is

$$\Delta \varepsilon = N_f^{-0.6} D_f^{0.75} + 0.9 \frac{S_u}{E} \left[ \frac{\exp(D_f)}{0.36} \right]^{0.1785 \log(10^5/N_f)}$$

(5)

Given the material properties of electrolytic copper, once the total strain is obtained from the FEA models, the microvia fatigue life  $N_f$  can be solved from Eq. (5). The elastic modulus, E=127 GPa, was measured at CALCE using nanoindentation for copper in HDI boards. The other constants of the fatigue model can be found from [44] for electrolytic copper:  $S_u=400$  MPa and  $D_f=30.2\%$ . Engelmaier's model, Eq. (5) and the electrolytic copper properties from [44] were widely used to predict microvia fatigue life in the literature [19][20][27][28][32]. Engelmaier used resistance increase as a failure criterion when he derived the fatigue mode and material properties for electrolytic copper in his experiments. By using Engelmaier's model, the same failure criterion in [44] was used for microvia fatigue life prediction.

#### 3.2.2 Total Strain from FEA

To estimate the microvia fatigue life, the input to Eq. (5) is the total strain  $\Delta \mathcal{E}$ , which is obtained from the FEA in this study. In order to minimize the element density effect on the total strain, a group of elements at the neighborhood of the potential failure site of the microvia was used to calculate the weighted average total strain:

$$\Delta \varepsilon_{FEA} = \frac{\sum V^e \Delta \varepsilon^e}{\sum V^e} \tag{6}$$

where  $V^e$  is the element volume, and  $\Delta \varepsilon^e$  is the element total strain. The element group was selected as a circular slice (a quarter of a circle in the quarter model), taking about 1/8 of the single-level microvia height at the maximum von Mises stress location.

## 3.2.3 Application of Miner's Rule

The damage from the sequential loading conditions accumulates for fatigue, according to Miner's Rule [45]:

$$\sum_{i} \frac{n_i}{N_i} = 1 \tag{7}$$

where  $n_i$  is the number of applied cycles and  $N_i$  is the limit number of cycles to failure under loading i.

In this study, three solder reflow cycles were simulated and followed by thermal cycling of -55 °C to +125 °C. The applied number of cycles to failure of the thermal

cycling was predicted. Based on FEA results, the total strain of the first solder reflow cycle was much larger than that of the second and third solder reflow cycles due to hardening of the copper structure. Therefore, the first solder reflow cycle was treated as the first load, the second and third solder reflow cycles as the second load, and the thermal cycling was the third load. In other words,  $n_1 = 1$  and  $n_2 = 2$ , and the aim is to predict  $n_3$ .

The limit number of cycles to failure under each load was calculated using Engelmaier's fatigue life model, Eq. (5) based on the total strain from FEA, that is,  $N_i$  (i = 1, 2, 3) was estimated. From Eq. (7), the applied number of thermal cycles (-55 °C to +125 °C) to failure was derived as

$$n_3 = \left(1 - \frac{1}{N_1} - \frac{2}{N_2}\right) N_3 \tag{8}$$

#### 3.3 Parametric Study

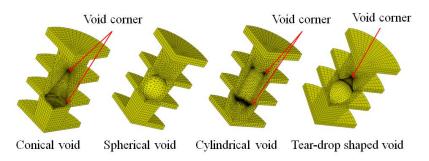

A parametric study of void shape, size, and location, as well as microvia AR and dielectric material properties, was conducted to investigate their effects on the thermomechanical stress distribution and durability of microvias. Based on the examination of the commercial HDI boards, four geometries were extracted from the void shape: conical, spherical, cylindrical, and teardrop-shaped. The conical shape was the most common void shape, representing more than half of the examined voids, followed by the spherical shape.

The four different void shapes simulated in the microvias are shown in Figure 17. It was assumed that the voids were located at the center of the stacked microvias. The same void size was used to examine the microvia fatigue life for all the void shapes. Whenever a void had a corner, where the radius of curvature had a sudden change, the corner was smoothed using tangential surfaces to avoid artificial stress concentration. The corners of the voids are marked in Figure 17.

Figure 17: Microvia Models of Different Void Shapes

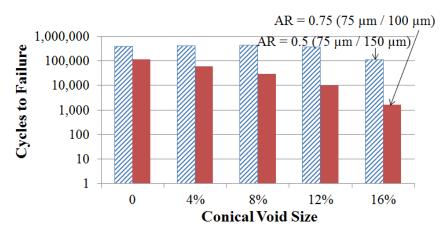

The effect of different void sizes on microvia fatigue life was studied using both conical and spherical voids. The void size was measured by volume ratio, which was defined as the ratio of the void volume to the microvia volume. 4%, 8%, 12%, and 16% voids were modeled for the two shapes.

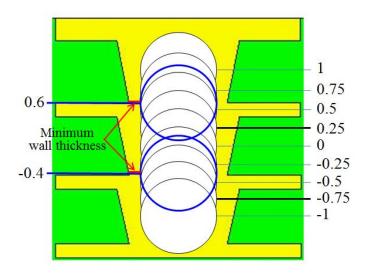

To study the effect of void location, spherical voids of 12% were simulated at different heights throughout the stacked microvia structure. Void locations were defined using numerical data for generalizing the findings. The center of the middle-level microvia is defined as Location 0, and half microvia height (single-level height) above Location 0 is defined as 0.5, half microvia height below Location 0 is defined as –0.5, and so on. The location definitions are shown in Figure 18.

**Figure 18: Definition of Void Locations**

In the above models, the same microvia geometry was used (75  $\mu$ m height/150  $\mu$ m diameter). The AR of the microvias was 0.5 (AR = 0.5 column in Table 1). To investigate the effect of microvia geometry on the fatigue life of voided microvias, microvias with ARs of 0.25 (37.5  $\mu$ m height/150  $\mu$ m diameter) and 0.75 (112.5  $\mu$ m height/150  $\mu$ m diameter and 75  $\mu$ m height/100  $\mu$ m diameter) were simulated for 16% conical voids.

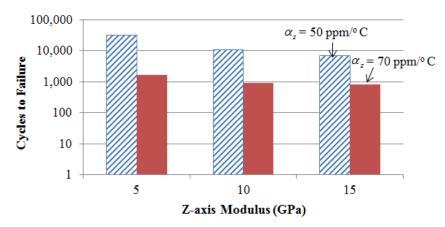

The effect of mechanical properties of the dielectric material of the HDI board on the reliability of voided microvias was also studied. The most important material properties that affect the stress/strain levels and cycles to failure are CTE and *z*-axis modulus of the dielectric material. Thus, two different CTEs, namely, 50 ppm/°C and 70 ppm/°C, and three different *z*-axis moduli, namely, 5 GPa, 10 GPa, and 15 GPa, were simulated

in six microvia models (AR of 0.5 and 16% conical void). The other material properties of these models were the same as in Table 2.

#### 3.4 **Results**

The results of the parametric study of different void shapes, sizes, and locations, as well as different microvia ARs and dielectric material properties, on microvia fatigue life are presented in this section.

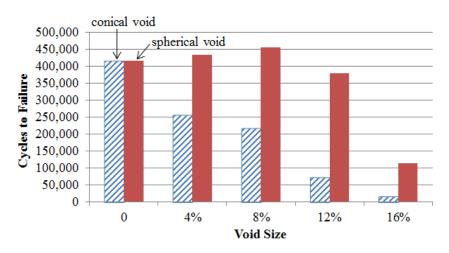

#### 3.4.1 *Void Size Effect*

Figure 19 shows the cycles to failure of microvias with different spherical and conical void sizes. For conical voids, the microvia fatigue life decreased as the void size increased. The number of cycles to failure of a microvia with a 16% conical void was only 5.4% of the cycles to failure of a non-voided microvia.

Figure 19: Effect of Void Size on Microvia Fatigue Life

For a spherical void, the microvia fatigue life first increased and then decreased as the void size increased. When there is a void in the microvia structure, the stress and strain

distributions are different from the non-voided microvia, because the microvia structure surrounding the void (referred to below as the "voided layer") becomes more compliant. For example, the strain increases in the voided layer, while it decreases in the microvia structure above and below the voided layer. For a small void, the strain in the voided layer is still smaller than in the microvia structure above or below the voided layer, and therefore the strain level in the voided microvia is lower than a non-voided microvia, which results in an increased fatigue life. A spherical void was beneficial up to a certain void size (around 8%). When the void became larger than the cross-over point, the thinner microvia wall generated by the void led to a lower fatigue life, because the strain level in the voided layer exceeded that in the structure above or below the voided layer. The fatigue life of a microvia with an 8% spherical void was 10% longer than the fatigue life of a non-voided microvia, while the fatigue life of a microvia with a 16% spherical void was 25% of the fatigue life of a non-voided microvia.

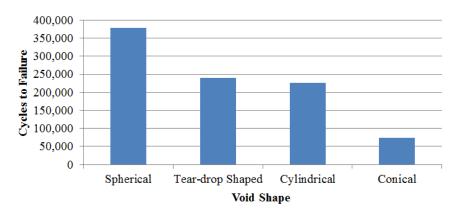

#### 3.4.2 Void Shape Effect

Figure 20 presents the cycles to failure of microvias with four different void shapes of the same size (12% volume ratio). The fatigue life of the microvia was highly dependent on the void shape. The conical void resulted in the shortest fatigue life, while the spherical void resulted in the longest fatigue life. The fatigue life of the conical void was about 19% of that of the spherical void. The fatigue life of microvias with teardrop-shaped and cylindrical voids was 63% and 60% of microvias with spherical voids, respectively.

Figure 20: Effect of Void Shape on Microvia Fatigue Life

The longer fatigue life in the spherical void was due to the uniform radius of the void boundary. The conical void had two corners (Figure 17), which resulted in the greatest local stress concentration and hence the shortest fatigue life. A large region of the teardrop-shaped void boundary had a uniform radius, and there was one corner on the void boundary. In the cylindrical void, the lateral surface of the void boundary had uniform curvature. Although the connection between the lateral surface and the base surfaces formed two corners, the angles of the corners were 90° (not an acute angle). Therefore, the teardrop-shaped and cylindrical voids resulted in longer fatigue life than the conical void and shorter fatigue life than the spherical void.

#### 3.4.3 *Void Location Effect*

Due to the tapered shape of microvias, void location change results in different minimum wall thickness between the void boundary and the outside edge of the microvia. Multiple void locations were simulated in each stack level to capture the fatigue life change along with the changes in the microvia wall thickness. Apparently, the voids located at 0.6 and -0.4 (Figure 18) resulted in the thinnest minimum wall. The

wall thickness at location 0.6 and -0.4 is about 5  $\mu$ m. It is thinner than the minimum copper plating thickness in microvias required by IPC-6012D-RedLine [33]. However, this does not affect our discussion on how microvia wall thickness affects the life time. Moreover, the very thin plating wall was generated due to the specific void locations. On other models in the dissertation, the void was located in the center of the microvia, so other models did not have as thin as 5  $\mu$ m microvia walls.

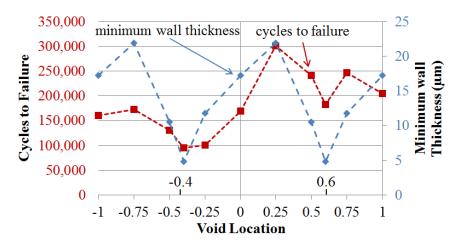

Figure 21 shows the change of minimum wall thickness and cycles to failure of microvias with the varying void location. The void at Locations -0.4 and 0.6 resulted in the thinnest minimum microvia wall thickness and shortest fatigue life (local minimum on the curve). However, the minimum wall thickness at different microvia levels had different effects—for example, the local minimum fatigue life at location 0.6 was actually longer than the fatigue life at locations between -1 and 0 due to the effects of the entire microvia geometry. The lower level minimum wall thickness resulted in shorter microvia fatigue life than the same upper level minimum wall thickness.

Figure 21: Effect of Void Location and Minimum Wall Thickness

The trend of cycles to failure was consistent with that of the minimum wall thickness, except for location 1, which resulted in maximum stress at the top pad corner of the microvia rather than around the minimum wall thickness site for other void locations. The void location 1 was close to the top of the microvia, so the stress distribution on the microvia could be different than other locations. The shortest microvia fatigue life at location -0.4 was 32% of the longest fatigue life at location 0.25.

#### 3.4.4 Aspect Ratio Effect on Voided Microvias

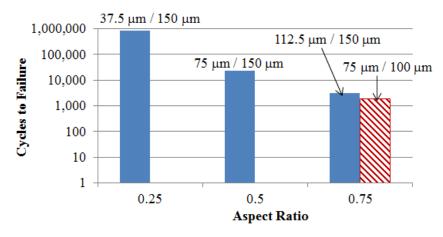

The estimated cycles to failure of voided microvias with different ARs are presented in Figure 22, which shows that smaller ARs are associated with longer microvia fatigue life. The AR of 0.5 (75  $\mu$ m/150  $\mu$ m) was the default microvia geometry for the previous models. The AR of 0.25 was achieved by reducing the dielectric thickness to half; the AR of 0.75 was achieved in two ways—by increasing the dielectric thickness by half or by reducing the microvia diameter by a third.

Figure 22: Effect of Microvia Aspect Ratio on Microvia Fatigue Life

The number of cycles to failure of the microvia (with 16% conical void) with AR of 0.25 was 36 times that of the microvia with AR of 0.5; the number of cycles to failure of the microvia with AR of 0.5 was 7.5 and 12 times that of the microvias with AR of 0.75 for 112.5  $\mu$ m/150  $\mu$ m and 75  $\mu$ m/100  $\mu$ m geometry, respectively. Therefore, a larger AR resulted in shorter microvia fatigue life, regardless of whether the AR was generated by changing dielectric thickness or microvia diameter.

Interestingly, the fatigue life of the voided microvia of 0.25 AR was even longer than that of a non-voided microvia of 0.5 AR—821,000 vs 415,000 cycles to failure. Consequently, it is not sufficient to simply provide a qualification criterion for voided microvias without considering the microvia geometries as in IPC-6012D-RedLine.

To better understand the effect of AR on the reliability of microvias containing conical voids of varying sizes, microvias with an AR of 0.75 and with void size up to 16% were modeled. As shown in Figure 23, the fatigue life of microvias of 0.75 AR had the same

trend as those with 0.5 AR—the fatigue life decreased as the conical void size increased. The microvias of 0.75 AR always resulted in a shorter fatigue life than those with 0.5 AR for the same void size. Moreover, voids had a more significant effect on the fatigue life of microvias with a higher AR—the cycles to failure of the microvia of 0.75 AR with a 16% void was only 1.4% of that of the microvia without a void.

Figure 23: Effect of Microvia Aspect Ratio with Different Void Size

#### 3.4.5 Material Property Effect on Voided Microvias

The effect of dielectric material properties on the fatigue life of voided microvias is shown in Figure 24. A larger *z*-axis CTE or a larger elastic modulus resulted in a shorter fatigue life. As the *z*-axis CTE increased by 40% (from 50 ppm/°C to 70 ppm/°C), the fatigue life decreased by 95%, 92%, and 88% for a *z*-axis modulus of 5 GPa, 10 GPa, and 15 GPa, respectively. As the modulus increased by 100% (from 5 GPa to 10 GPa), the fatigue life decreased by 65% and 44%, respectively, for *z*-axis CTE of 50 ppm/°C and 70 ppm/°C; as the modulus increased by 200% (from 5 GPa to 15 GPa), the fatigue life decreased by 78% and 48%, respectively, for *z*-axis CTE of 50 ppm/°C and 70 ppm/°C. Therefore, the change of *z*-axis CTE had a more significant impact on

microvia fatigue life than elastic modulus. Additionally, the voided microvias with *z*-axis CTE of 70 ppm/°C only lasted for about 1000 cycles under the thermal loading condition.

Figure 24: Effect of Dielectric Material Properties

#### 3.4.6 Potential Failure Sites

The site of the maximum von Mises stress is a potential site for maximum damage and, hence, is a potential fatigue failure site in a microvia. Therefore, the identification of the site is helpful for microvia reliability evaluation and improvement.

As shown in Figure 25, for a non-voided microvia, the site of maximum von Mises stress was at the top and/or bottom pad corner of the microvia due to CTE mismatch in the board thickness direction between the copper material and the dielectric. For conical voids, the maximum von Mises stress was located at the void boundary or microvia outside wall with minimum microvia wall thickness, due to local stress concentration. For spherical voids, when the voids were equal to or less than 8% volume ratio (default

microvia AR and dielectric material properties), the potential site of maximum damage was the same as in non-voided microvias; the major effect of the void was the change of the compliance of the microvia structure, which resulted in an increase in microvia fatigue life. When the spherical void reached 12% or larger, the thin microvia wall generated a greater stress concentration than at the top or bottom pad corner, and the maximum von Mises stress was located at the void boundary with a larger stress level than the non-voided microvia.

Figure 25: Sites of Maximum von Mises Stress

#### 3.5 Discussion about the Voiding Effects

Although voids have been observed in copper-filled microvias, their existence is not always detrimental to microvia reliability. For example, 8% or smaller spherical voids resulted in longer fatigue life than microvias without voids, while larger voids resulted in shorter fatigue life than non-voided microvias. The voided layer in a microvia can be considered as a composite of the copper and the void. In the simplest case of effective material properties (Rule of Mixtures), each component (i.e., copper and void) contributes to the effective modulus in a quantity proportional to its volume fraction. The modulus of the void is considered as zero, and therefore, the effective modulus of