## THESIS REPORT

Master's Degree

Supported by the National Science Foundation Engineering Research Center Program (NSFD CD 8803012), the University of Maryland, Harvard University, and Industry

## A Neural Network Based Approach for Surveillance and Diagnosis of Statistical Parameters in the IC Manufacturing Process

by W. Zhang Advisor: L. Milor

### **Abstract**

Title of Thesis: A Neural Network Based Approach for Surveillance

and Diagnosis of Statistical Parameters in the IC

Manufacturing Process

Name of degree candidate: Wei Zhang

Degree and year: Master of Science, 1992

Thesis directed by: Dr. Linda Milor

Department of Electrical Engineering

Despite advances in integrated circuits (IC) equipment and fabrication techniques, there still exist random fluctuations or statistical disturbances in any IC manufacturing facility, which can adversely affect the production yield. Actually devices and circuits are being designed with increasingly tighter parameter and performance margins. As a result, chip performance becomes even more sensitive to the statistical variations, and this may result in low production yield. Based a statistical process simulator, a methodology of tracking and diagnosing statistical variations of a real manufacturing process in a bid to implement real time statistical quality control of IC manufacturing process is presented in this thesis.

The main contributions of this thesis include the following. A neural network based approach for IC process diagnosis is proposed and has been realized. This approach needs a very short time in diagnosing significant variations of an IC process, hence is practical to be used in real-time monitoring and diagnosing of the process disturbances. Another contributive feature of this approach is that process diagnosis is a high dimension problem, and in our approach all variables are handled simultaneously, instead of eliminating of some variables that may have small but important contributions as in previous approaches. Other contributions include an algorithm to evaluate the fault observability and disturbance diagnosability. In addition, thresholding and coding methods are developed for pattern generation of the neural networks. A special sampling distribution is employed for simulation of samples, in conjunction with latin hypercube sampling techniques. Finally the approach is applied to a general example to show its efficiency with some experimental results.

## A Neural Network Based Approach for Surveillance and Diagnosis of Statistical Parameters in the IC Manufacturing Process

by

#### Wei Zhang

Thesis submitted to the Faculty of the Graduate School of the University of Maryland in partial fulfillment of the requirements for the degree of Master of Science

1992

#### Advisory Committee:

Dr. Linda Milor, Chairman/Advisor

Dr. R. Newcomb

Dr. A. Tits

| ~ |  |   | ~~~ |

|---|--|---|-----|

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  | · |     |

|   |  |   |     |

|   |  |   |     |

| • |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

|   |  |   |     |

## Acknowledgements

I would like to take this opportunity to express my deep appreciation to my advisor, Dr. Linda Milor. Her enlightening guidance, kind help, insightful comments, and encouragement are instrumental for the completion of this work. I want to thank Dr. J. Dayhoff and Mr. A. Teolis for the helpful discussions on neural networks. My appreciation also goes to the members of my advisory committee, Professor R. Newcomb and Professor A. Tits for their valuable help and comments. I would like to acknowledge the financial support from the Institute of Systems Research, University of Maryland at College Park. And finally I want to thank my wife Chien for her years of encouragement and supports.

| • |   |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   | • |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

## Contents

| Li | List of Tables |                                                                    | vi  |

|----|----------------|--------------------------------------------------------------------|-----|

| Li | st of          | Figures                                                            | vii |

| 1  | Intr           | roduction                                                          | 1   |

|    | 1.1            | Overview                                                           | 1   |

|    | 1.2            | Monitoring and Diagnosing of IC Process Variations                 | 3   |

|    | 1.3            | IC Process Control and Yield Optimization                          | 5   |

| 2  | Stat           | tistical Characterization Problem in Integrated Circuit Man-       |     |

|    | ufac           | cturing Process                                                    | 7   |

|    | 2.1            | Introduction to IC Manufacturing Process                           | 7   |

|    | 2.2            | Statistical Characteristics of the IC Process and Distributions of |     |

|    |                | Process Disturbances                                               | 11  |

|    |                | 2.2.1 Process Disturbances                                         | 12  |

|    |                | 2.2.2 Distributions of Process Disturbances                        | 14  |

|    | 2.3            | Analytical Models of IC Process and Computer Simulation            | 16  |

|    | 2.4            | IC Process Characterization Problem                                | 17  |

|    | 2.5            | Previous Approaches for IC Process Characterization                | 19  |

|   | 2.6  | The IC Process Diagnosis Problem and Previous Approaches to                                        |    |  |

|---|------|----------------------------------------------------------------------------------------------------|----|--|

|   |      | the IC Process Diagnosis                                                                           | 21 |  |

| 3 | Sur  | veillance and Diagnosis of Statistical Parameters in IC Pro-                                       |    |  |

|   | cess | 3                                                                                                  | 24 |  |

|   | 3.1  | Introduction                                                                                       | 24 |  |

|   | 3.2  | Statistical Process Control Technique and Its Application in IC                                    |    |  |

|   |      | Yield Optimization                                                                                 | 26 |  |

|   | 3.3  | Design and Application of Control Charts                                                           | 30 |  |

|   | 3.4  | Surveillance and Monitoring of Process Disturbances Using Con-                                     |    |  |

|   |      | trol Charts                                                                                        | 33 |  |

|   | 3.5  | Practical Considerations                                                                           | 36 |  |

| 4 | Ma   | hematical Foundations of the Neural Network Based Method-                                          |    |  |

|   | olog | зу                                                                                                 | 38 |  |

|   | 4.1  | Introduction to Neural Networks [31]                                                               | 38 |  |

|   | 4.2  | The Approximation Capability of Backpropagation Neural Net-                                        |    |  |

|   |      | work [32][33]                                                                                      | 39 |  |

|   | 4.3  | $\label{lem:matter} \mbox{Mathematical Formulation of the Process Surveillance Problem} \; . \; .$ | 42 |  |

| 5 | Rea  | alization of Neural Network Based Approach for IC Process                                          | ŀ  |  |

|   | Sur  | veillance                                                                                          | 46 |  |

|   | 5.1  | Generation of Training Samples for the Neural Network                                              | 46 |  |

|   | 5.2  | Determination of Neural Network Structures and Training of Neu-                                    |    |  |

|   |      | ral Networks                                                                                       | 52 |  |

|   |      |                                                                                                    |    |  |

|   | 5.3  | Training and Testing of Neural Networks                                                            | 54 |  |

| 6                | Des    | ign of | Experiments and Result Analysis                            | 61 |

|------------------|--------|--------|------------------------------------------------------------|----|

|                  | 6.1    | Introd | uction                                                     | 61 |

|                  | 6.2    | Design | of Experiments                                             | 62 |

|                  |        | 6.2.1  | Selection of Parameters to be Monitored                    | 62 |

|                  |        | 6.2.2  | Generation of Thresholds                                   | 72 |

|                  |        | 6.2.3  | Determination of Control Limits for the Control Charts     | 75 |

|                  |        | 6.2.4  | Sample Size Analysis                                       | 77 |

|                  | 6.3    | Experi | imental Results                                            | 79 |

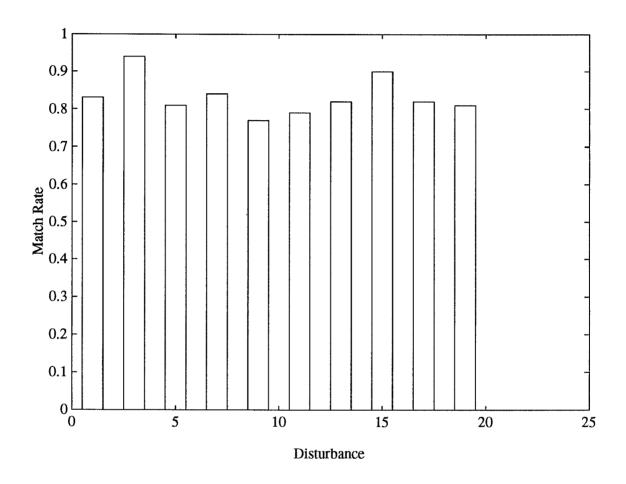

|                  |        | 6.3.1  | Monitoring IC Process Parameters Using Control Charts .    | 79 |

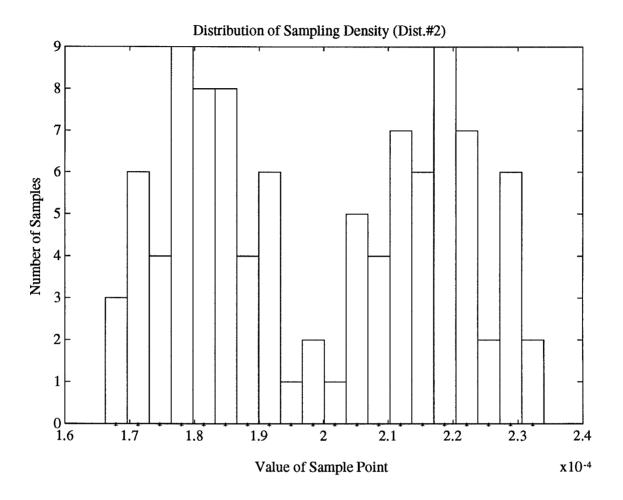

|                  |        | 6.3.2  | Distribution of the Sampling Density in Pattern Generation | 81 |

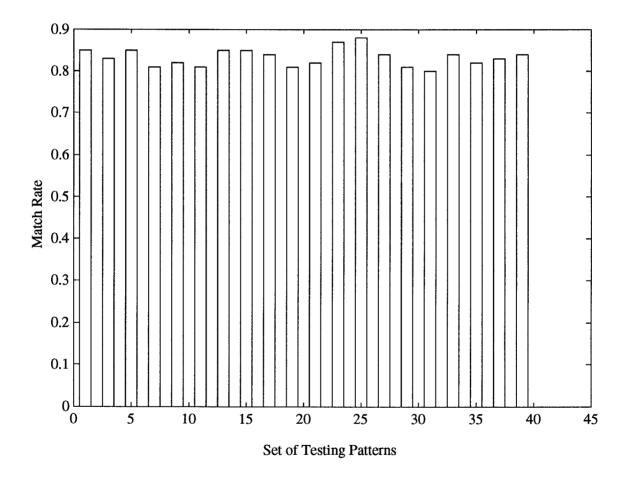

|                  |        | 6.3.3  | Testing Results for the Neural Network                     | 83 |

|                  | 6.4    | Error  | Analysis of the Experiments                                | 87 |

| 7                | Fut    | ure We | ork                                                        | 91 |

|                  | 7.1    | Summ   | ary                                                        | 91 |

|                  | 7.2    | Future | e Research Directions                                      | 92 |

| $\mathbf{B}^{i}$ | ibliog | graphy |                                                            | 94 |

## List of Tables

| 5.1 | Formulation of input vectors using permutation sets             | 49 |

|-----|-----------------------------------------------------------------|----|

| 6.1 | Selected disturbances and their nominal values                  | 63 |

| 6.2 | Selected measurable output parameters                           | 64 |

| 6.3 | Samples of RSH when the correlated disturbance No. 4 shifted to |    |

|     | $3\sigma$                                                       | 66 |

| 6.4 | Samples of RSH when the correlated disturbance No. 4 at nominal |    |

|     | and shifted to $-3\sigma$                                       | 68 |

## List of Figures

| 2.1 | Two level structure of RNG's simulating local and global distur-   |    |

|-----|--------------------------------------------------------------------|----|

|     | bances                                                             | 15 |

| 3.1 | The system of yield optimization                                   | 28 |

| 3.2 | A typical variable control chart                                   | 30 |

| 3.3 | The system of implementing inverse of IC process                   | 35 |

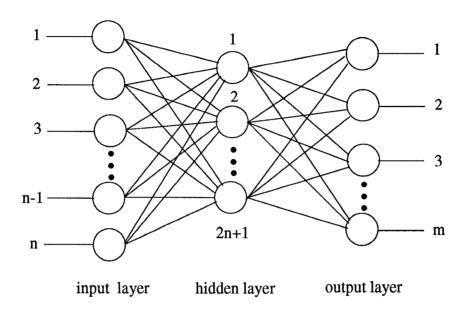

| 4.1 | The typical structure of a backpropagation neural network          | 40 |

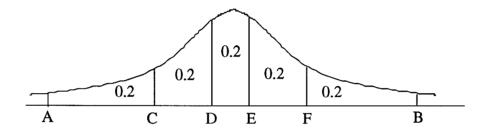

| 5.1 | Evenly divided intervals in probability for $X_1$                  | 48 |

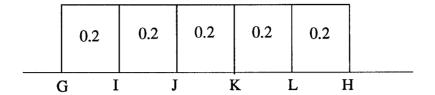

| 5.2 | Evenly divided intervals for $X_2$                                 | 49 |

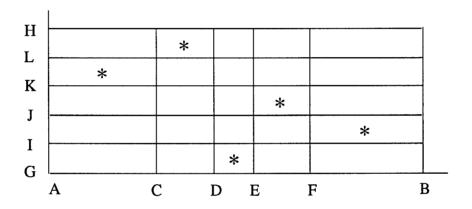

| 5.3 | Two-dimensional representation of sample space                     | 50 |

| 5.4 | Specific distribution for unevenly sampling                        | 52 |

| 5.5 | Function of error vs. weights                                      | 57 |

| 6.1 | An example showing the procedure of determining the distur-        |    |

|     | bances in the same ambiguity group                                 | 71 |

| 6.2 | Procedure of creating thresholds for an output parameter affected  |    |

|     | by two disturbances                                                | 73 |

| 6.3 | An example of the generation of codes for disturbances and outputs | 75 |

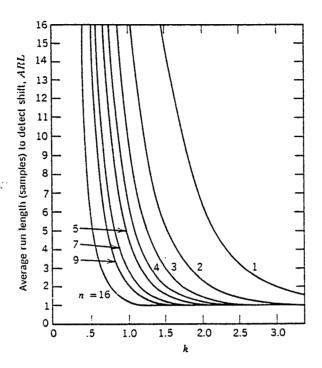

| 6.4  | Average run length (sample) for the $\bar{x}$ chart with $3\sigma$ limits, where |    |

|------|----------------------------------------------------------------------------------|----|

|      | the process mean shifts by $k\sigma$ . (Adapted from Introduction to             |    |

|      | Statistical Quality Control. by D.C.Montgomery, John Wiley &                     |    |

|      | Sons, pp. 230, 1991)                                                             | 78 |

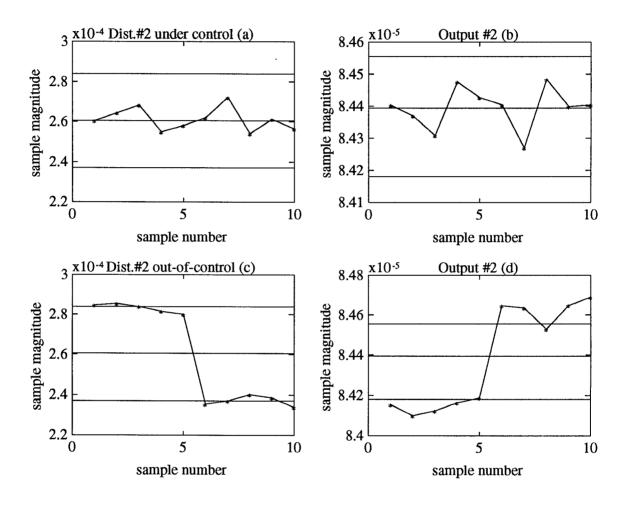

| 6.5  | Control charts for correlated disturbance and output parameter $$ .              | 80 |

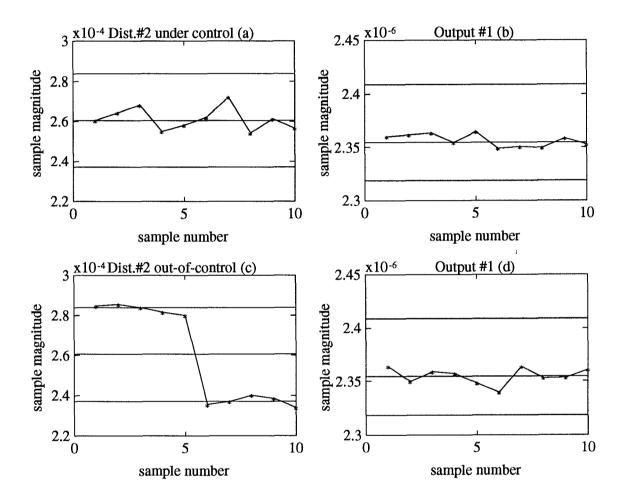

| 6.6  | Control charts for uncorrelated disturbance and output parameter                 | 82 |

| 6.7  | A typical distribution function of sampling density                              | 83 |

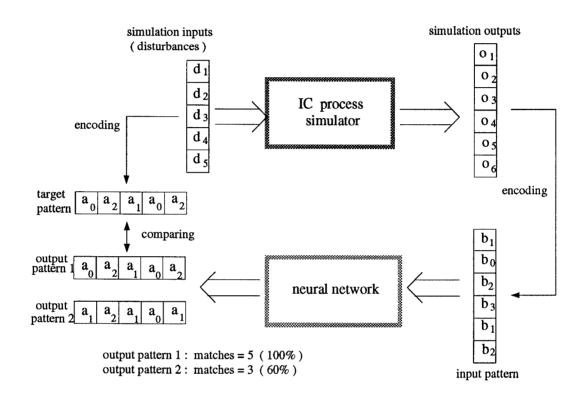

| 6.8  | The testing procedure                                                            | 84 |

| 6.9  | The average match rate for each disturbance                                      | 85 |

| 6.10 | The average match rate for each set of testing patterns                          | 86 |

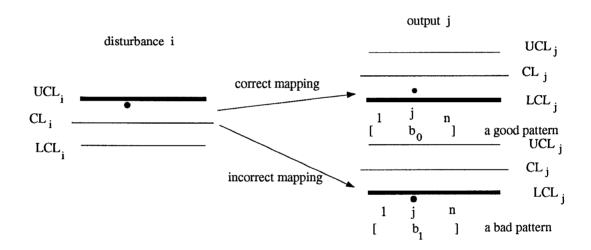

| 6.11 | Creation of "good pattern" and "bad pattern"                                     | 88 |

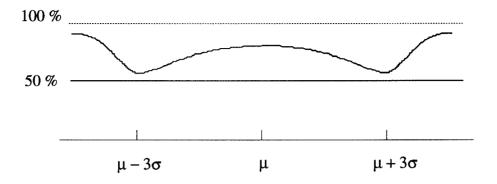

| 6.12 | An approximated probability distribution of yielding "good" pat-                 |    |

|      | terns                                                                            | 89 |

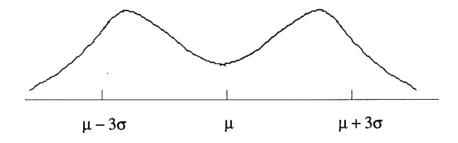

| 6.13 | Probability distribution of sampling density                                     | 89 |

## Chapter 1

## Introduction

#### 1.1 Overview

During the last decade, the feature sizes of VLSI devices have been scaled down significantly, and they are still becoming smaller. Despite advances in integrated circuits (IC) equipment and fabrication techniques, however, there still exist random fluctuations or statistical disturbances in any IC manufacturing facility, which can adversely affect the production yield. And unfortunately, these statistical variations in the critical device parameters, such as the MOSFET channel length and width, and threshold voltage have not been scaled down in proportion to the feature sizes of devices. Actually devices and circuits are being designed with increasingly tighter parameter and performance margins. As a result, chip performance becomes even more sensitive to the statistical variations, and this may result in low production yield.

To achieve an acceptable yield, this random nature of the IC manufacturing line should be taken into consideration during the design procedure. With the variety of CAD tools available nowadays, an accurate model can be established and fine turned to simulate a real manufacturing process [1][2][3]. The process yield can thus be predicted through analyzing the critical process parameters extracted from the simulation process. The extracted process information also makes it possible to implement process control and maintain uniform process condition and high yield [4][5].

In the literature substantial effort has been put on the establishment of statistical models and the optimization of yield [6][7][8]. Based on some of these models and results, a methodology of tracking and diagnosing statistical deviations of a real manufacturing process in a bid to implement real time statistical quality control of IC manufacturing process is presented in this thesis.

The main contributions of this thesis are listed as follows.

- 1. A neural network based approach for IC process diagnosis is proposed and has been realized.

- 2. This approach is practical in real-time monitoring and diagnosis of IC process disturbances

- 3. Process diagnosis is a high dimensional problem and all variables are handled simultaneously, rather than subdividing the problem, which may lead to inaccuracies.

- 4. An algorithm is devised to evaluate fault observability and disturbance diagnosability.

- 5. Thresholding and coding methods are developed for pattern generation of the neural networks.

- 6. A special sampling distribution is employed for simulation of samples, in conjunction with latin hypercube sampling

- 7. The approach is applied to a general example to show its efficiency.

## 1.2 Monitoring and Diagnosing of IC Process Variations

The IC manufacturing process involves a sequence of basic processing steps that are performed on sets of wafers called lots. Each wafer may contain tens to hundreds of chips. Due to the batch character of IC manufacturing, process faults and deviations that may arise in the various steps of an IC process result in a large volume of defective products before they are detected and rectified.

The faults and variations that cause depreciation of process yield come from the deviated process conditions and the unavoidable fluctuations inherent in IC manufacturing process. Although most process conditions, such as temperature, gas flux and pressure can be measured and controlled accurately, the fluctuations, such as the diffusivity of boron and arsenic, variance of implantation profile and surface state density, etc. are generally not directly measurable. Therefore, monitoring the fluctuations, detecting the significant deviations of them from their nominal values and keeping them under control play an important role in stabilizing and improving yields of integrated circuit manufacturing.

An IC fabrication line is characterized by a number of fabrication recipes being used to manufacture different kinds of IC's. In each fabrication recipe there are a large number of process parameters that to different extents affect the output performance and in turn the yield of the process. When some of these parameters depart from their designated values, or nominal values, what follows may be the generation of some functionally defective devices or even a big drop in the yield. Process diagnosis and control are employed, in this circumstance, to identify those shifted parameters and bring them back to their nominals. Due to the quantities of the process parameters, however, it is infeasible and uneconomical to monitor all of them. A much more effective way is naturally to monitor those parameters that have a significant impact on the process yield.

As aforementioned, most process fluctuations or disturbances, which are the main source of the parameters to be monitored, are generally not directly measurable. Hence we have to rely on in-line measurements and electrical measurements of a fabrication line to determine the distributions of the process disturbances. On the other hand, process disturbances provide more useful information if the process is out-of-control. Therefore, we have built control charts for process disturbances, and consequently it has been necessary to map the statistics of a set of observed measurements to statistics of process disturbances. The main thrust of the work is therefore first to find the optimal choice of parameters to monitor with control charts, the main tool used in statistical quality control, which will be introduced in succeeding chapters. Secondly, because a set of measurements may be related to multiple process disturbances, in order to diagnose a fault we have implemented an algorithm that will identify out-of-control process disturbances after a set of measurements have been made.

The relation between process disturbances and observable measurements is modeled by a process simulator. The process simulator will map process disturbances to observable measurements. So what we actually need is the inverse of this map. This problem has previously been studied by Spanos [3], who fits the

map from disturbances to measurements by using polynomial approximation, and then uses nonlinear programming to find the disturbance statistics. The main drawback of the approach lies in the high dimensionality of the problem, since it is very difficult to build accurate polynomial models for a high dimensional problem.

Assuming normal statistics have been determined, our problem is to diagnose major changes in the disturbances. In this paper we solve this problem by fitting a neural network to the map from statistics of measurements to statistics of process disturbances. The motivation behind the idea of using neural networks is based on the extensive applications of neural networks and common belief that neural networks can handle high dimensional problems better than polynomial approximation techniques. Some simplified device models have been used to demonstrate the feasibility and efficiency of this method. Results of the experiments will be provided in chapter 7.

## 1.3 IC Process Control and Yield Optimization

The manufacturing of today's micron and submicron features in integrated circuits requires a tight control of the fabrication process in order to realize the objective of maximizing process yield. In volume production, this means that both the size of these features and its distribution must be well controlled and fall within specifications.

Because of the complexity of the IC fabrication process, identifying those parameters to monitor is a non-trivial task. Some specifically designed experiments, such as a factorial experimental design [9], or the latin hypercube method [10] could be applied to obtain a reasonable choice according to the circuit being manufactured and the specifications it needs to satisfy. Once a set of parameters has been selected, it is possible to choose an optimal set of control limits for the control charts established for these parameters. The choice of control limits should depend on the sensitivity of the yield to a given disturbance, the cost of producing faulty chips, and the cost of halting processing due to a false alarm. Research done in this area is summerized by Montgomery [11].

When a sample in a control chart indicates that the process has gone out of control, an investigation will be initiated for the assignable causes of the problem. This can either be malfunctioning equipment or the conditions need to be adjusted. To find out if it is possible to adjust the conditions to bring the process back into control, the sensitivity of the yield to the conditions at a given (out of control) operating point can be computed. If adjusting the conditions can not bring the process into control, then the source of the problem is likely to be faulty equipment. The use of process disturbance control charts should hence make it easier not only to identify an out of control process, but also find the appropriate actions to correct the process.

We have briefly discussed the background and objective associated with monitoring and diagnosis of the IC process variations. In next chapter, a detailed description about the IC manufacturing process and their statistical characteristics will be provided, and then some previous work relevant to this topic will be summarized.

### Chapter 2

# Statistical Characterization Problem in Integrated Circuit Manufacturing Process

## 2.1 Introduction to IC Manufacturing Process

The manufacturing process of an integrated circuit (IC) consists of a sequence of steps that are carried out in a specific order. These steps generally include mechanical, optical, thermal and chemical operations performed on a silicon substrate, and finally convert the circuit design into a functional silicon integrated circuit chip.

The objective of the IC manufacturing process is to produce IC chips satisfying specific requirements of a design at as small a cost as possible. To achieve this goal, production is traditionally done in batch mode, including processing up to several hundred ICs together on a wafer, and a few dozen wafers in a lot. Hence, several thousand of the same ICs are manufactured together, simply for the purpose of reducing the cost per chip. At the same time, effort has to be

directed towards minimizing the departure of geometrical and electrical features of the processed devices from those specified during design stage. Toward this end, a high degree of control over the parameters of each processing step is required. Equally rigid requirements apply to the physical and chemical properties of materials used for IC fabrication, and also to the cleanliness of the production environment.

The sequence and manner in which individual IC process steps are carried out vary from one IC process to another, and they are crucially important to the outcome of the manufacturing process. Although different techniques make use of different equipment and materials, hence creating different devices, the IC processing steps basically fall into the following six categories [12][13]:

Photolithography: This is a technique used in IC fabrication to transfer a desired pattern onto the surface of a silicon wafer. As such, photolithography is a key step in the entire circuit integration process. Specifically, it is a photochemical process during which the layout is transferred through visible or ultraviolet exposure from a photomask to a photoresist layout, which has been deposited on the wafer. The image is subsequently developed quite similar to the image on a photographic negative using specific chemicals that affect exposed and non-exposed areas differently. The geometry of the regions in which the photochemical reaction in the photoresist takes place corresponds to the pattern on the mask. The accuracy of the pattern transfer from the mask to the wafer is determined by the resolution of the photolithographic process. The higher the photolithographic resolution, the finer the geometrical features that can be patterned onto the wafer.

Oxidation: The oxidation of silicon is necessary throughout the modern

integrated circuit fabrication process. Silicon dioxide has several uses: to serve as a mask against implant or diffusion of a dopant into silicon; to provide surface passivation; to isolate one device from another; to act as a component in MOS structures and to provide electrical isolation of multilevel metallization systems. Several techniques for forming oxide layers have been developed, such as thermal oxidation, wet oxidation, the vapor-phase technique and plasma oxidation. They are employed in different circumstances to generate silicon dioxide layers serving the different purposes mentioned above.

Layer Deposition: The layers of both conducting substances and insulating materials constitute an important part of any semiconductor device. In contrast to the deposition of the silicon dioxide layer by thermal oxidation, the deposition process does not involve a chemical reaction with the substrate. In deposition, all components of layer being grown are independent of the composition of the substrate (deposition of a thin solid layer in this manner does not cause consumption of the silicon substrate as is the case in thermal oxidation of silicon). The configuration of the deposited thin layer reflects the topography of the substrate. This is an important consideration since in the case of high steps patterned on the substrate, coverage of the steps by the deposited material may not be conformal. The resulting non-uniformity of thickness of the deposited layer can cause reliability problems in the final device.

Etching: The process that immediately follows the photolithographic step is removal of the material from areas of wafer unprotected by photoresist. Various etching techniques are used for this purpose. Etching processes are characterized by their selectivity and their degree of anisotropy. Anisotropic etching occurs in one direction only, in contrast to the undesired isotropic etching, in which

material is removed at the same rate in all directions. The etching processes used in IC fabrication can take place either in a liquid (wet etching) or gas (dry etching) phase. They can be purely chemical, purely physical, or a combination of both.

Diffusion: Solid state diffusion is a process which allows atoms to move within a solid at elevated temperatures. Diffusion is a commonly used technique in IC fabrication to introduce dopants into the semiconductor substrate. Dopants affect the conductivity or change the type of conductivity (from n to p type or vice versa) of selected regions within the substrate. The objective is to achieve the desired impurity profiles (concentration of impurities as a function of the distance from the wafer surface) and eventually create junctions (surfaces that separate regions with dopings of alternate polarity on each side at the desired depth beneath the wafer surface.)

Implantation: Ion implantation is the alternative to the diffusion technique of dopant introduction used in IC manufacturing. From the processing point of view, the main difference between these two techniques lies in the significantly lower process temperature in ion implantation. This advantage combined with a much decreased lateral spreading of the doped region as well as overall better control over the dopant profile during ion implantation have led to the preferential use of this technique in high-density microcircuit fabrication.

Based on the above processing steps, various technologies have been developed to produce different kinds of IC components. Among them, NMOS (N-channel Metal-Oxide Semiconductor) and CMOS (Complementary MOS) are extensively used technologies currently.

NMOS technology is characterized by the negative doping of the transistor

channel. There are two main types of transistors produced by NMOS technology, namely depletion and enhancement transistors. The names reflect the effect an increasing effective field has on the concentration of the conducting impurities in the transistor channel. While in CMOS technology, the silicon substrate is selectively doped with negative or positive impurities. Three types of this technology are in use, namely p-well, n-well and twin-tub. Here the names reflect the technique employed to isolate regions with alternate doping. Since CMOS technology employs both NMOS and PMOS transistors to form logic elements, it has an advantage in a sense that the particular logic elements only draw significant current during the transitions, allowing power consumption to be minimized. This accounts for the reason why CMOS technology is recognized as a leading contender for existing and future VLSI systems.

# 2.2 Statistical Characteristics of the IC Process and Distributions of Process Disturbances

It is well known that random fluctuations, or disturbances exist in any IC fabrication process. Due to the existence of these disturbances, each manufactured wafer has a different and unique processing history. Furthermore all fabricated ICs on a wafer are different from one another because of random fluctuations in processing conditions across a wafer. Some of them may be affected by process disturbances in such a way that they do not meet expected specifications. In some cases, process instabilities may even cause only a small fraction of all

fabricated ICs to have an acceptable performance, hence significantly decreasing the manufacturing yield.

In this section, the principal disturbances in IC process and their effects on IC device performances will be classified and described. The distributions behind these disturbances will also be discussed.

#### 2.2.1 Process Disturbances

The statistical variations of an IC process arise from the existence of a set of low level, non-measurable, non-controllable, independently statistically varying physical quantities, called process disturbances[14]. The exact definition of process disturbances will depend on the process model. Some examples of process disturbances include the diffusivity of a dopant, like boron and arsenic, to the substrate, variance of implantation profile spread of a dopant, various silicon dioxide growth rates, mask misalignments and surface state density, etc.[15] Sources of the random disturbances that occur in the IC fabrication process can be classified as two categories, namely global fluctuations and local fluctuations [3].

#### Global Fluctuations in IC Process

Among the sources of process disturbances, there sources of fluctuations affect chip performances in a random but globally homogeneous way. In other words, the effects are independent of the physical location of a particular chip or device on a chip during manufacturing. Although the local fluctuations are also generally characterized by affecting all devices on wafer/chip approximately equally, they are small compared to variances between chips, and in turn between wafers.

The sources of the global fluctuations can be further classified as:

- Instabilities in the process conditions. Although some of the process conditions can be controlled accurately, as mentioned in section 1.2, others such as the turbulent flow of gases used for diffusion and oxidation, furnace temperatures, etc. cannot be controlled as quite accurately. Because of these instabilities, each area of a wafer is exposed to slightly different environmental conditions, and hence no two manufactured chips can possibly have identical performance.

- Material non-uniformities. These are variations in the physical parameters of the chemical compounds and other materials used in manufacturing process. They are independent of the location of a chip on the wafer or the location of a wafer in the lot. Typical examples of material instabilities are fluctuations in the purity and physical characteristics of the chemical compounds, density and viscosity of photoresist, wafer and gas contamination, etc.

- Translational mask misalignments. These are errors in the position of a lithography mask with respect to the features already engraved on the surface of a wafer. They cause all edges defined by the mask to be shifted by the same amount with respect to the boundaries of the regions that already exist on the surface of the wafer. Therefore, the geometry of an IC could be significantly deformed from that of an ideal one, and hence wrong electrical connectivity could result.

- Human factors and equipment failures. These include imprecise equipment settings, imprecise equipment calibrations, etc.

#### Local Fluctuations in IC Process

In contrary to the global fluctuations, local fluctuations tend to affect ICs in some specific locations on a wafer. There are two main sources of spatial fluctuations.

- Substrate inhomogeneities. These are local disturbances in the properties of substrate wafers and are of three types: spot defects, dislocations and surface imperfections. Spot defects are local disorders in the structure of the lattice inside a semiconductor material. Dislocations are geometrical irregularities in the regular structure of the crystal lattice. These factors may cause serious or fatal changes in chip functionality.

- Pattern Transfer. While translational mask misalignments uniformly affect all chips on a wafer, rotational misalignments, pattern shrinkage or bloating and optical aberrations tend to dramatically affect those chips which are closer to the edges of the wafer.

#### 2.2.2 Distributions of Process Disturbances

From the above discussion we can observe that process disturbances can cause either global or local deformations, and process induced deformations of any kind, local or global, geometrical or electrical, are all random.

Usually the variations caused by a global process disturbance that are observed within a single IC chip are small because all devices from a single IC chip are located very close to each other and therefore have very similar "process histories". Thus it can be expected that a specific parameter of all devices within a single chip to be similar and close to a certain mean value. Such is not the case, however, for the devices from different chips, since the mean process conditions for one chip can be quite different from that of another one, especially if they

are on different wafers.

The above discussion suggests that each global process disturbance should have a mean value characterizing average process conditions for some local area. The actual condition for a specific location within this area can be modeled by a variable randomly fluctuating about this local mean value with some local standard deviation. And these local parameters should also randomly change from one local area to another.

To account for local and global variations in device parameters, we can employ a multilevel structure for the random variables that characterize process disturbances [1]. With such a structure, disturbances are generated by a hierarchically defined random number generator (RNG) at levels that correspond to natural divisions, i.e. at the lot, wafer and chip levels.

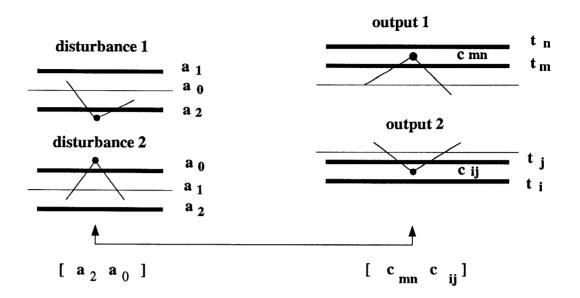

Figure 2.1: Two level structure of RNG's simulating local and global disturbances

Figure 2.1 shows a two-level structure composed of three RNG's. This structure is capable of generating disturbance data for a wafer, and this structure can be easily extended to the lot level.

As introduced in Section 2.2.1, the variations of an IC process are usually caused by a large number of independent physical quantities. Consequently, it is quite reasonable to assume that the random variables representing process disturbances are normally or log-normally distributed based on the Central Limit Theorem in probability [16]. This assumption has proved convenient and realistic in statistical simulation of IC the process. With this assumption, we can completely specify process disturbances by identifying their means and standard deviations.

## 2.3 Analytical Models of IC Process and Computer Simulation

In order to design and simulate an IC process for ideal yield, an accurate and efficient process model is a necessity. Traditional approaches for process simulation, such as that implemented in SUPREM [17], employ numerical models to characterize each fabrication step. These models, which are expressed in terms of partial differential equations (e.g. the diffusion equation), are solved using numerical techniques to produce the nominal profiles of impurities in silicon. The impurity profiles can then be used by device simulators such as SEDAN [18] and MINIMOS [19], in which semiconductor device models are described by a system of partial differential equations, which are solved numerically to produce I-V characteristics from which device parameters can be extracted. While such simulations can produce results that are accurate for a deterministic case, they are prohibitively expensive when used for statistical investigations.

To alleviate this difficulty, some statistical simulators were developed to serve

the purpose of statistical investigations. The statistical simulator FABRICS II is one of them [2]. Instead of using numerical models, FABRICS II employs analytical models which are solutions of the partial differential equations that describe each fabrication step under a set of restricted or simplifying conditions. Reasonable results have been achieved by these models. A detailed description of fabrication steps and analytical models implemented in FABRICS II can be found in [15]. However like other statistical simulators, there are some limitations with it. For example, it can not be used for the short-channel devices.

It should be emphasized that although FABRICS II has been employed to generate simulation data in our experiments, the algorithm presented in this thesis does not depend on any specific statistical simulator. It can be used with any simulator as long as the simulator can provide the required simulation data, or the manufacturing process itself.

### 2.4 IC Process Characterization Problem

The IC manufacturing processes vary from one to another, depending on the devices manufactured and the specific requirements for the devices. Hence, it is not difficult to understand that statistical characteristics are particular to a specific IC process. In order to simulate, monitor and diagnose an IC manufacturing process, we have to obtain sufficient knowledge about the process of interest. Specifically, we need to determine the quantitative effect of the controlled process conditions on the physical properties of various areas of the substrate. We also want to know the electrical characteristics of the manufactured devices after IC process is completed, and dependence of these characteristics on the process

conditions. Due to statistical nature of the IC manufacturing process, determining the statistical distributions and correlations of process parameters is also very important. The procedure of acquiring the above knowledge is usually referred to as IC process characterization.

In the statistical process simulator FABRICS II, an IC manufacturing process is viewed as a deterministic process with statistically varying inputs, i.e., the process disturbances. The deterministic process simulator actually consists of a number of analytical models that can accurately simulate the physics of a fabrication process. These models could be numerical, as with other process simulators. Thus given statistical distributions of the process disturbances, it is possible to simulate statistical variations within any process by means of Monte Carlo techniques [20]. This is accomplished in FABRICS II by using random number generators to generate a population of process disturbance values, which are then used as the inputs to the deterministic process.

A statistical simulator can produce a population of electrical and physical parameters pertaining to the finished ICs. Significant trends on process conditions due to the fluctuations of an actual process can be detected by statistically analyzing the simulated population of parameters.

In order to predict statistical attributes of output population, exact distributions governing the input population, namely process disturbances have to be known. In the literature [21], the task of obtaining probability distribution functions (pdf's) of the process disturbances is accomplished by extracting pdf's of the process disturbances so that joint probability distribution function (jpdf) of the simulated process outputs matches the jpdf of the measured process outputs.

## 2.5 Previous Approaches for IC Process Characterization

Because of the important role IC process characterization plays in modeling, analysis and simulation of the IC process, a lot of effort has been put into this problem. And several approaches have been employed to deal with different aspects of the problem. A brief summary will be given below about some representative approaches that are used extensively.

Worst case characterization [22] determines the extreme fluctuations of a given IC process in a sense that these fluctuations most adversely affect the performance. Once these fluctuations have been determined, simulations or the process can be skewed to worst case conditions. Thus the extreme performance of a population of manufactured ICs can be produced under the worst case. If these extreme simulated performances are within the specifications of design, we can expect that the bulk of performances of actually manufactured ICs to be within the specifications as well.

I-V matching is another technique used for IC process characterization [23]. This is actually a process of extracting some parametric values of the analytical device model, so that the model is in agreement with the measured device. If the device is typical of the process, then in a sense this is considered to be a characterization of the process.

Although these techniques have been extensively used, they have some deficiencies associated with them. One of the inherent deficiencies of these approaches is that the process statistics are modeled with correlated parameters, and an independent set of statistical variables is not determined.

A methodology for statistical IC process characterization was proposed to compensate for the deficiency of the above approaches [3].

In this approach the statistical process characterization problem is first formulated as a set of nonlinear equations of the form:

$$N(d_0 + d_e, p, y_0 + y_e) = 0 (2.1)$$

where  $d_0$  and  $y_0$  are vectors of deterministic values and represent the nominal values of the disturbances and the outputs of an IC process, respectively.  $y_e$  and  $d_e$  are the statistical variations superimposed on the outputs of the process and the process disturbances. p represents the process conditions. Since  $y = y_0 + y_e$  is related to  $d = d_0 + d_e$  by nonlinear functions, the problem can be solved in two steps: first the nominal disturbance vector  $d_0$  can be extracted given the nominal output parameter vector  $y_0$ , and then the statistical distribution of the disturbance variance vector  $d_e$  can be extracted given statistical distribution of the output parameter variance vector  $y_e$ .

Specifically, the nonlinear programming technique has been employed to solve this statistical extraction problem, which can be mathematically represented as follows.

$$\min_{d_0} ||N(d_0, p, y_0)||_2 \tag{2.2}$$

and

$$\min_{\theta^d} \|G(\hat{\theta}^y, \theta^d)\|_2 \tag{2.3}$$

where  $\hat{\theta}^y$  is a vector of moments that characterizes the distribution of  $y_e$ , and  $\theta^d$  is a set of moments that characterizes the distribution of  $d_e$ . The map from

statistical distributions of process disturbances to that of output measurements is approximated by polynomial models. A detailed discussion on this approach can be found in [24].

Based on these models, a computer software PROMETHEUS [21] was developed to diagnose the nominal disturbances using optimization techniques. This approach proves to be efficient when the number of disturbances to be diagnosed is not large, for instance, smaller than 10. It may not be as efficient in the context of high dimensionality, because it is extremely difficult to build an accurate polynomial model for high dimensional cases. Nevertheless, once the nominal disturbances have been determined, they can be used in statistical process control.

# 2.6 The IC Process Diagnosis Problem and Previous Approaches to the IC Process Diagnosis

In the literature the IC process diagnosis is defined as the inference of the changes in the statistics of the process disturbances. As discussed earlier, significant shifts of process disturbances from their nominal statistics will result in process faults. Due to their low level physical nature, however, some of the process disturbances can not be directly measured. They have to be inferred by the measurements obtained on the circuits or test structures, which have been fabricated by the process. This section provides a brief discussion on two previous approaches for the IC process diagnosis problem.

The first approach is a pattern recognition based method which was proposed by Strojwas and Director [46]. The output measurements used in this approach are taken from chip performance testing. Since the performance specifications are employed as the thresholds, only pass or fail data are generated. The drawback of this method is that since the data are taken from chip performance testing which is carried out in the evaluation stage, the method is not very sensitive to the variations in the IC process. In order to diagnose a process fault, a large amount of data is required. Moreover the approach has limited observability, because only the faults already in the data base can be identified.

The second approach is polynomial approximation method proposed by Spanos [14]. The measurements used in this approach are taken from test chips, and therefore are more sensitive to the variations of the IC process. Polynomial models are employed to approximate the relation between the process disturbances and the output parameters in this approach. Then the diagnosis problem is converted to an optimization problem, which is solved iteratively using nonlinear programming techniques. The main drawback of this method is that with the high dimensionality of the problem, it is very difficult to build an accurate polynomial model at each operating point of the process, hence the method is very intensive in computation. Therefore it is impractical for use in real-time diagnosis of large variations of the process disturbances.

The approach proposed in this thesis is based on backpropagation neural networks. The mapping from the process output parameters to the process disturbances is accomplished by fitting a neural network to the IC process of interest. A distinguishing feature of this approach is that the diagnosing of process disturbances is very short once the neural network has been fine tuned to the IC

process. This feature makes it practical to be used in real-time monitoring and diagnosing of process faults. And since the neural networks are much easier to set up than the polynomial models, the difficulty due to the high dimensionality of the problem is alleviated using the neural network based approach. The details of this new approach will be the main subject of the remaining part of this thesis.

#### Chapter 3

## Surveillance and Diagnosis of Statistical Parameters in IC Process

#### 3.1 Introduction

The rapid advances in the miniaturization of today's microchips have resulted in ever-increasing circuit density and complexity. In the fabrication of such microchips, defects in materials, contamination in chemicals and deviations in process parameters can lead to dramatic yield reductions. The fabrication of integrated circuits requires a number of processing steps. If one or more of these steps are incorrect or exceeds certain design limits, the devices fabricated will either fail or not perform as intended. It has therefore become imperative to monitor the IC process continuously at each step in order to take immediate corrective actions in case of a deviation.

To assure that a maximum number of devices will be functional and meet the desired performance criteria, a sample of the wafers is taken for a variety of quality control inspections and also for measurements to determine the effects of any process variation upon the wafer properties. Such an operation is carried out after every major step in an IC fabrication process. For example, after a photolithographic step, the dimensions and the alignment of patterns generated in the photoresist will be checked at perhaps five chip positions on 1 out of 10 wafers. This serves to verify mask performance [25].

The real-time monitoring of equipment and processes in IC fabrication makes it possible to identify and eliminate problems before the yield of fabrication has already been adversely affected.

In practice an integrated circuit production line is monitored by gathering and analyzing information obtained from varieties of sources [26]. For example, the uniformity of various process parameters can be measured from specially designed process monitor chips (PMC's) stepped into product wafers, and from a process validation wafer (PVW) consisting entirely of test patterns [27], the process control data can be obtained from a wafer capable of isolating the behaviors of particular process steps. Additional information may be gathered on the behavior of processing equipment, on various environmental factors, and on a variety of other aspects of IC fabrication. The quantity of data which can be collected is, therefore, virtually unlimited. The real challenge lies in effectively utilizing this information to achieve a high level of control and operation efficiency.

Various techniques have been employed to monitor and detect non-uniformity in the IC process based on the data extracted from it. Among these techniques, the frequency plots (histograms), the two-dimensional contour maps and the three dimensional perspective drawings are extensively used, which have been discussed in the literature [28][29]. These techniques have been proved effective in monitoring and exhibiting variations of some parameters such as sheet resistance

and film thickness in the IC process. To be able to detect or predict a significant trend of device performance in IC process, however, a large number of process parameters need to be monitored and evaluated simultaneously. The statistical process control technique has been proved to be more effective in this case to deal with the problem.

Due to the importance of IC process characterization, a substantial effort has been made to reveal and analyze the statistical nature of the IC process in the literature. As part of this effort, a new approach is proposed in this thesis, which incorporates the application of the statistical process control technique to achieve the goal of monitoring and detecting deviations of IC process parameters based on the measurable outputs of the process.

## 3.2 Statistical Process Control Technique and Its Application in IC Yield Optimization

In any production process there exists a certain amount of inherent or natural variation no matter how well it is designed and maintained. To manufacture products meeting the designed specifications, a production line has to be capable of operating with little variability around the nominal dimensions of the product's quality characteristics. In other words, the production process has to be kept in a stable condition. Statistical process control is a powerful collection of tools useful in achieving process stability and improving capability of the process through the reduction of variability.

The inherent variability in any production process arises from the cumulative effect of many small essentially unavoidable causes. As indicated in Section 2.2,

for example, variations in the IC process are due to the existence of a large number of low level physical quantities. When the inherent variability in a process is relatively small, we usually consider it to be an acceptable level of process performance, or the process is said to be under statistical control.

There are other kinds of variability which may occasionally be present in a process. Such variability is generally large compared to the inherent variability. The sources of such variability in the IC process may include imprecisely adjusted equipment, improperly controlled environmental conditions, defective raw materials and operator mistakes. These sources of variability are referred to as assignable causes in the field of statistical quality control. Occurring in a random mode, the assignable causes result in a shift in the process state and in turn cause a large proportion of the products not to meet the requirements. A process that is operating in the presence of assignable causes is said to be out of control.

A major objective of statistical process control is to quickly detect the occurrence of process shifts or assignable causes so that investigation of the process and corrective action may be undertaken before many nonconforming products are manufactured. Techniques such as the control chart can be used to monitor the process outputs and to detect when adjustments in the inputs are required to bring the process back to an under-control state.

The introducing of statistical process control to IC fabrication is motivated by the objective of optimizing process yield. The manufacturing yield of an IC process is defined as the ratio of the number of chips that successfully pass all of the selection steps in the process with respect to the total number of chips that enter the fabrication process at the very beginning [30]. It can be simply

expressed as:

$$Y_m = \frac{N_f}{N} \tag{3.1}$$

where N is the maximum number of chips that can be fabricated in an ideal IC manufacturing process, and  $N_f$  is the number of chips that have been classified as fault-free after the final selection step.

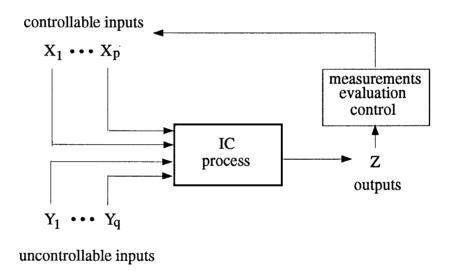

The yield of an IC process depends on many process parameters. In order to optimize yield, all those parameters whose changes have a substantial impact on yield have to be under strict control. The system of using statistical control to optimize process yield is illustrated in Figure 3.1.

Figure 3.1: The system of yield optimization

The inputs  $X_1, \dots, X_p$  are controllable factors, such as process time, environmental temperature and gas flux etc., while the inputs  $Y_1, \dots, Y_q$  are uncontrollable factors, such as raw materials and human (operator) factors. The

manufacturing process transforms these inputs into a finished device which is expected to have specific electrical functions and meet some designated requirements at the same time.

Choosing input variables to perform statistical control is one of the critical steps in yield optimization. The key input variables that significantly influence the yield have to be identified in order to achieve high efficiency in control. Towards this end, first the analysis of sensitivity of yield to process parameters needs to be done to find the best set of input process parameters. Designed experiments proved to be extremely helpful in discovering the key variables. A designed experiment is an approach to systematically varying the controllable inputs and observing the effect these inputs have upon the output device parameters. In the literature [3.9], designed experiments are also referred to as a major off-line quality control tool, because they are often used during development activities and early stages of manufacturing, rather than as a routine on-line or in process control procedure.

Once the best set of inputs has been determined, they will be used as the target of monitoring, and appropriate control charts will be built associated with them. Whenever an out-of-control signal emerges from any of these control charts, an investigation will be initiated to search for the assignable causes behind it. Corrective measures will then be taken if an assignable cause really exists and is found. By continuous surveillance of the entire fabrication procedure, we can expect to keep the fabrication line in a stable condition and therefore achieve a high yield of the process.

#### 3.3 Design and Application of Control Charts

As a main tool of statistical quality control, the control chart is an on-line process control technique widely used for the purpose of detecting the occurrence of process shifts or assignable causes [11]. The control chart may also provide information useful in improving the process. Note that the eventual goal of statistical process control is the elimination of variability in a process. It may not be possible to completely eliminate variability, but the control chart is an effective tool in reducing variability as much as possible.

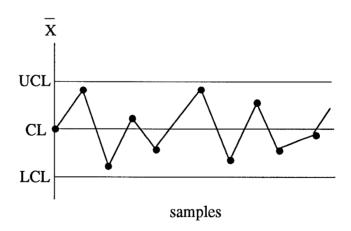

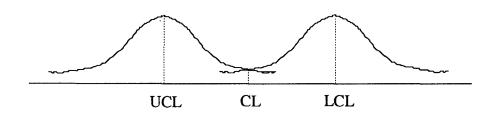

There are several types of control charts built in different cases to detect the potential variability of a process for the best effectiveness. A typical control chart is shown in Figure 3.2, which is a graphical display of a statistical characteristic that has been measured or computed from a sample versus the sample number or time.

Figure 3.2: A typical variable control chart

The control chart shown in Figure 3.2 consists of a center line (CL) and two other horizontal lines that parallel the center line. The line above the center line

shown on the figure is called the upper control limit (UCL) and the line below called the lower control limit (LCL). These control limits are chosen so that if the process is under control, nearly all of the sample points will fall between them. As long as the sample points fall within the control limits, the process is considered to be under control, and no action is necessary. A point that falls outside of the control limits, on the other hand, is interpreted as evidence that the process is out of control; investigation and corrective actions are required in this case.

Figure 3.2 is actually a control chart for the IC device parameter channel length. Each point plotted on the chart is computed from ten consecutive samples from process simulation. Because this control chart utilizes the sample average  $\bar{x}$  to monitor the mean of the channel length, it is usually called a  $\bar{x}$  control chart. Note that all points in the figure fall within the control limits, so the chart indicates that the process is in statistical control.

A general model for a  $\bar{x}$  control chart can be described as follows.

$$UCL = \mu_x + k\sigma_x$$

$$CL = \mu_x$$

$$LCL = \mu_x - k\sigma_x$$

where x is a sample statistic of a process parameter,  $\mu_x$  stands for the mean of x and  $\sigma_x$  for the standard deviation of x. k is the "distance" of the control limits from the center line.

As stated at the beginning of this section, there are various control charts that are employed for the different purposes. But generally control charts can be classified into two types, namely variable control charts and attribute control charts. Following is a brief description of the two types.

If the quality characteristic can be measured and expressed as a number on some continuous scale of measurement, it is usually called a variable. In such cases, it is convenient to describe the quality characteristic with a measure of central tendency and a measure of variability. Control charts for central tendency and variability are collectively called variable control charts. The  $\bar{x}$  chart is the most widely used variable control chart for controlling central tendency, while charts based on either the sample range or the sample standard deviation are used to control process variability.

On the other hand, many quality characteristics are not measured on a continuous scale or even a quantitative scale. In these cases, we may judge each unit of product as either conforming or nonconforming on the basis of whether or not it possesses certain attributes, or we may count the number of nonconformities (defects) appearing on a unit of product. The control charts for such quality characteristics are called attribute control charts.

Since the central tendency is our main concern in IC process surveillance and control,  $\bar{x}$  chart is the appropriate control chart which can serves our purpose. It is actually applied as the main chart in the approach proposed in this thesis, as will be seen in Chapter 6.

Note that due to the statistical nature of the observed parameters, one or more sample points may fall outside of the control limits occasionally even though the process is actually under statistic control. These out-of-control signals result in a "false alarm" that might cause unnecessary cost. By moving the control limits further from the center line, we can decrease the risk of a false alarm. However, widening the control limits will also increase the risk of another type of error, namely the risk of a sample point falling between the control limits when the process is really out of control. Therefore, specifying the control limits is one of the critical decisions that must be made in designing a control chart.

In practice control limits are customarily determined as a multiple of the standard deviation of the statistics plotted on the chart. And the multiple is usually chosen as 3, although a more reasonable choice should be dictated by the economic considerations in a specific process. More complete discussion of this subject can be found in [11].

## 3.4 Surveillance and Monitoring of Process Disturbances Using Control Charts

From discussions in Section 2.2, we know that the reason for a yield drop of an IC process can be attributed to significant variations of the process disturbances in most cases. Obviously, if we can implement real-time monitoring and statistical control of the process disturbances, a great step will be made towards the objective of optimizing manufacturing yield.

Although statistical quality control techniques have been successfully applied to various stages of the IC manufacturing, the idea of establishing control charts for IC process disturbances in order to implement real-time direct monitoring of the process disturbances has not been attempted. The main difficulty lies in the fact that most of the process disturbances can not be observed and measured directly.

Even though a number of approaches have been developed to extract those

unmeasurable process parameters from the measurable outputs, their applications in real-time surveillance and control of IC process are strongly restricted by the intensive computations that they involve. A real-time based approach that is quick and simplistic in computation is needed for this purpose.

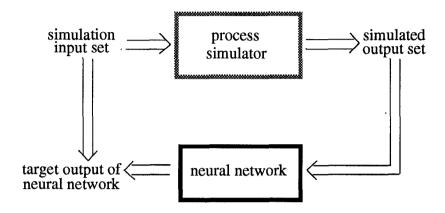

We have been aiming to establish control charts for the process parameters and disturbances that have a significant impact on yield. This idea has been made realistic by a successful algorithm relating the measurable outputs of an IC process to the process disturbances in a timely fashion. Actually, shifts in process disturbances are tracked based on the information provided by the online measurements of process outputs. This task is accomplished by tuning a multilayer neural network to the inverse map of the IC process of interest. In other words, the tuned neural network uses the on-line output measurements of the IC process as its inputs, and its outputs are the process parameters and disturbances we want to monitor. As such it is possible to get a real-time sampling of the process disturbances as long as a continuous sampling of the on-line output measurements are available, which turns out not to be a very difficult task.

The tuning or learning of the neural network employed is carried out after the design or development stage of an IC process, and uses a process simulator that have been tuned to the process of interest. The learning procedure initiates from the generation of simulation data for the process disturbances. Then designed experiments are employed to input a set of simulation data to the fine tuned process simulator, and the corresponding outputs of the simulator are recorded. The next step is to generate training patterns for the neural network. And this is done by using the pair of output and input sets of the process simulator as

the inputs and outputs of the neural network, respectively. Figure 3.3 shows the learning procedure.

Figure 3.3: The system of implementing inverse of IC process

After the learning procedure the neural network is then ready to be used with the real IC fabrication line that has been simulated by the process simulator. The samples taken from the outputs of the real fabrication line thus can be used to obtain real-time samples of the process disturbances through the fine tuned neural network. With real-time sampling of the process disturbances, the control charts can be built to implement real time monitoring of these disturbances.

It is worth mentioning here that in order to minimize the false alarms and "fail to detect" errors that might result from the IC process itself and measuring process, control charts are also established for IC process output measurements. The detailed designing procedure of these control charts will be discussed in Chapter 6.

#### 3.5 Practical Considerations

The main idea of implementing real-time monitoring of the process disturbances by using a neural network in conjunction with a process simulator has been introduced in the last section. The realization of the approach, however, has to be based on some practical considerations which will be discussed below.

As described in Section 2.2, every process disturbance can be represented as a random variable. Hence what we actually deal with is the statistics of these process disturbances. Furthermore, an assumption is made that the process disturbances to be monitored are independent from each other. This simplifies the problem by ignoring the correlations between the disturbances.

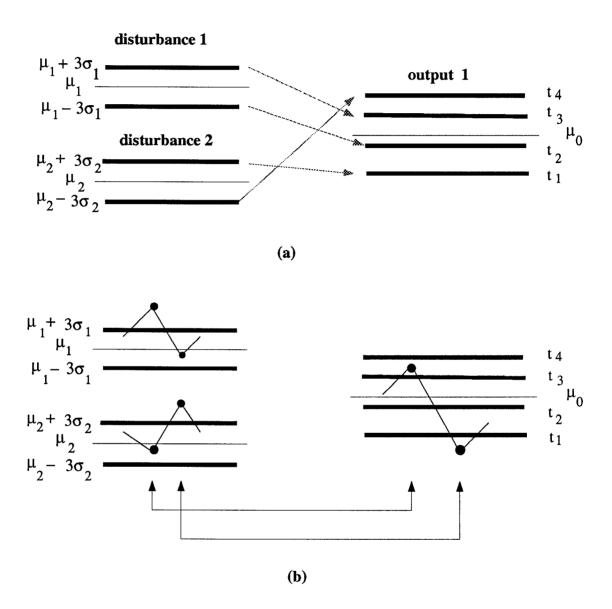

Another important factor that needs to be considered is the fact that the highly nonlinear relationship between the output measurements and the process disturbances makes the tuning of a neural network extremely difficult or even impossible in a global range, if the statistics of the process outputs and disturbances are used directly. In other words, the inverse of the relationship, i.e. from the statistics of outputs to the statistics of disturbances, is not valid over the global range, due to the fact that the functions relating disturbances to outputs are not one-to-one. A practical strategy to deal with this difficulty is to use coding.

Specifically, some properly spaced multiple thresholds in the control charts are first established for the statistics of both outputs and process disturbances. A specific number out of several preselected numbers is assigned to a variable which falls between any two thresholds. An ordered combination of the numbers assigned to all input variables then constitutes a digit string, called a code. The same thing is also obtained from the output variables. These codes will be

employed as the inputs and target outputs of the neural network to be tuned. It will be explained in Chapter 6 that the relationship between the input and output codes can be built on a one-to-one basis as long as no two process disturbances under surveillance affect exactly same set of output parameters.

After a neural network is fine tuned, it can then be used to monitor process disturbances in practice. To keep track of variations of the process disturbances, first of all, the on-line measurements of output parameters are taken from a real production line. These measurements will then be employed to obtain the statistics of the process outputs. The next step is to encode these statistics by the same procedure stated above. The generated code will be used as the input to the fine tuned neural network. And the output of the neural network will be the corresponding code for the statistics of disturbances in the real fabrication line. The decoding will create the samples of disturbance statistics, which will be plotted on their control charts.

The following two chapters will be devoted to the discussion of the theoretical and practical aspects of the neural network based approach.

#### Chapter 4

## Mathematical Foundations of the Neural Network Based Methodology

#### 4.1 Introduction to Neural Networks [31]

Neural networks are massively parallel systems that rely on dense arrangements of interconnections and simple processors. The systems actually consist of many nonlinear computational elements operating in parallel and arranged in patterns reminiscent of biological neural nets. Computational elements or nodes are connected via weights that are typically adapted during use to improve performance.

Neural network architectures are significantly different from traditional single processor computers. Traditional computing machines have a single CPU that performs all of its computations in sequence. In contrast, a neural network consists of a large number of processing units, called neurons which perform simple computations simultaneously. Each processing unit has four important components: input connections, through which the unit receives activation from other units; a summation function that combines the various input activations into a single activation; a threshold function that converts this summation of

input activations into an output activation, and output connections by which a unit's output activation arrives as an input activation at other units in the system. The inter-unit connections in neural networks are typically assigned numeric weights that modulate the activation passing through the connections. The power of the neural network lies in these interconnections.

As a useful computing tool, a neural network has strong capabilities to classify and recognize patterns, to perform pattern mappings, and to recover or complete patterns with missing segments. In this thesis the pattern mapping capability of neural networks will be employed. A further discussion on neural network's mapping capability is provided in the following section.

#### 4.2 The Approximation Capability of Backpropagation Neural Network [32][33]

As one of the paradigms of neural networks, backpropagation is currently the most widely applied neural network architecture. This popularity primarily revolves around the ability of backpropagation networks to learn complicated multi-dimensional mappings.

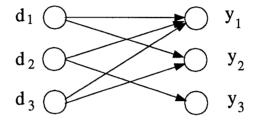

The backpropagation neural network architecture is a hierarchical design consisting of fully interconnected layers of processing units which have been introduced in the last section. Backpropagation belongs to the class of mapping neural network architectures and therefore the information processing function it carries out is the approximation of a bounded mapping of function  $f: A \subset \mathbb{R}^n \longrightarrow \mathbb{R}^m$ , from a compact subset A in n-dimensional Euclidean space to a bounded subset f(A) of m-dimensional Euclidean space, by means of training on examples  $(x_1, y_1), (x_2, y_2), \dots, (x_k, y_k), \dots$  of the mapping, where  $y_k = f(x_k)$ .

It will always be assumed that such examples of a mapping f are generated by selecting  $x_k$  vectors randomly from A in accordance with a fixed probability density function  $\rho(x)$ . A typical structure of backpropagation neural network is shown in Figure 4.1.

Figure 4.1: The typical structure of a backpropagation neural network

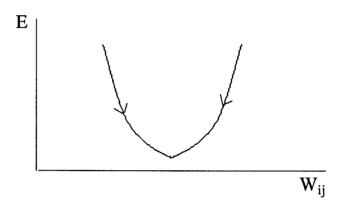

The scheduling of the backpropagation network's operation consists of two stages. The first stage (the forward pass) starts by inserting the vector  $x_k$  into the network's first layer, or the input layer. The processing elements of the first layer transmit all of the components of  $x_k$  to all of the units in the second layer of network. The same operations are performed between the second and third layers, and so on, until finally the moutput units in the output layer emit the components of the vector  $y_k$  (the network's estimate of the desired output  $y_k$ ).

After the estimate  $y_k$  is emitted, each of the output units is supplied with its component of the correct output vector  $y_k$ , starting the second stage (the

backward pass). The output units compute their squared errors,  $\delta_k = ||y_k - y_k t||_2$ , and then transmit them back to their ancestor layer. The ancestor layer updates its weights and transmits its corresponding errors to the layer of a level higher. This process continues until the first hidden layer has been updated.

The two-stage cycle is continued until the network reaches a satisfactory level of performance (the error level is lower than the predesigned). And then the network will be able to implement or approximate the functional mapping  $f: A \subset \mathbb{R}^n \longrightarrow \mathbb{R}^m$ .

The above discussion leads us to come up with a question — what kinds of functional forms can be approximated by the backpropagation neural networks? This problem had drawn a lot of concern and explorations in the past. A clear insight into the versatility of neural networks for use in function approximation came with the discovery of a new explanation to a classic mathematical result of Kolmogorov. The explanation states that for any continuous function  $f:[0,1]^n \subset \mathbb{R}^n \longrightarrow \mathbb{R}^m$ , there must exist a three-layer neural network (having an input layer with n processing elements, a hidden layer with (2n+1) processing elements, and an output layer with m processing elements) that implements function f exactly. This result gave hope that neural networks would turn out to be able to approximate any function that arises in the real world.

Mathematically, this result can be more precisely expressed in the following theorem.

**Theorem:** Given any  $\epsilon > 0$  and any  $L_2$  function  $f:[0,1]^n \subset \mathbb{R}^n \longrightarrow \mathbb{R}^m$ , there exists a three-layer backpropagation neural network that can approximate

$<sup>^{1}</sup>$ An  $L_{2}$  function is a squared-integrable multi-variable function defined in a bounded domain.

function f to within  $\epsilon$  mean squared error accuracy.

A complete proof of this theorem can be found in [32]. It is important to realize that although this theorem proves that a neural network with three layers is always enough in approximating any  $L_2$  function, it is often essential to have more than three layers. This is due to the fact that for many problems, an approximation with three layers would require an impractically large number of hidden units, whereas an adequate solution can be obtained with a tractable network size by using more than three layers.