ABSTRACT

Title of Document: READ-OUT CIRCUITS FOR INTEGRATED

SURFACE ACOUSTIC WAVE SENSORS.

Sambarta Rakshit, Doctor of Philosophy, 2015

Directed By: Agis A. Iliadis, Professor, Electrical and

Computer Engineering

Readout modules for vapor and liquid phase SAW sensors fabricated on piezoelectric films are typically configured as single or dual delay line oscillator loops. Mass loading of the sorbent film realized on the SAW device is detected as a frequency shift which is read externally via a frequency counter. However, this approach is not directly applicable in the development of a monolithically integrated autonomous sensor system suitable for wearable sensor tags and other field applications. In this work we have developed a data measurement topology suitable for monolithically integrated SAW sensors on CMOS chips, a technology that is not fully developed and will significantly increase Si-CMOS functionality. This readout technology achieves closed loop conversion of the SAW frequency response to a well-defined output voltage accurately tracking sensor behavior in real time. The topology is appropriate for thin film, low loss interdigitated (IDT) SAW devices used as mass loading sensors, such as those reported in [1] and [2].

The proposed closed loop system is controlled by a finite state machine (FSM) which forces the system output to oscillate within a narrow voltage range that correlates with the SAW pass-band response. The period of oscillation is of the order of the SAW phase delay. We also use timing information from the FSM to convert SAW phase delay to an on-chip 10 bit digital output operating on the principle of time to digital conversion (TDC). The output voltage range varies with changes in SAW center frequency, thus tracking mass sensing events in real time. This architecture precludes mode jumping issues found in designs incorporating the SAW delay line or the resonator in the feedback loop of an amplifier. It was demonstrated that the system can be adapted to alternate SAW center frequencies and group delays by adjusting the VCO control and TDC delay control inputs. Because of frequency to voltage and phase to digital conversion, this topology does not require external frequency counter setups and is uniquely suitable for full monolithic integration of autonomous sensor systems and tags.

# READ-OUT CIRCUITS FOR INTEGRATED SURFACE ACOUSTIC WAVE SENSORS

By

#### Sambarta Rakshit

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2015

Advisory Committee: Professor Agis A. Iliadis, Chair Professor Robert Newcomb Professor Neil Goldsman Professor Marty Peckerar Professor Aris Christou © Copyright by Sambarta Rakshit 2015

# Dedication

To Mayurika

## Acknowledgements

I am deeply grateful to my advisor, Professor Agis A. Iliadis for his guidance and support during my dissertation research. I would also like to thank the members of my dissertation committee, Professor Robert Newcomb, Professor Neil Goldsman, Professor Marty Peckerar and Professor Aris Christou.

# Table of Contents

| Dedication                                            | 11  |

|-------------------------------------------------------|-----|

| Acknowledgements                                      | iii |

| Table of Contents                                     | iv  |

| List of Tables                                        | vi  |

| List of Figures                                       | vii |

| Chapter 1: Introduction                               | 1   |

| 1.1 Motivation                                        | 2   |

| 1.2 Overview of Dissertation                          |     |

| Chapter 2: Surface Acoustic Wave Device Modeling      | 6   |

| 2.1 IDT Structure                                     |     |

| 2.2 Circuit Models                                    | 7   |

| Section 2.4 Summary                                   |     |

| Chapter 3: Analyte Interaction with Sensitive Film    | 17  |

| Section 3.1 Introduction                              | 17  |

| Section 3.2 Diffusion                                 | 18  |

| Section 3.3 Adsorption                                |     |

| Section 3.4 Sorption/Absorption Mechanisms            | 21  |

| Section 3.5 Summary                                   |     |

| Chapter 4: Sensor Readout Circuit Design              | 23  |

| 4.1 Introduction                                      | 23  |

| 4.2: Network analyzer based readout                   |     |

| 4.3: Oscillator based readout                         | 26  |

| 4.4: Transponder based measurements                   | 33  |

| 4.5: Digital Readout                                  | 34  |

| 4.6: PLL based SAW sensor                             | 35  |

| 4.7: Summary                                          |     |

| Chapter 5: Readout Architecture                       | 40  |

| 5.1 Introduction                                      | 40  |

| 5. 2 Top Level Architecture of Primary Sensor Loop    |     |

| 5. 3 Top Level Architecture of Secondary Sensor Loop  | 42  |

| Section 5.4 Summary                                   |     |

| Chapter 6: Design and Analysis of Primary Sensor Loop |     |

| Section 6.1 Voltage Controlled Oscillator (VCO)       |     |

| 6.2 Surface Acoustic Wave Device Model and Properties |     |

| 6.3: Open Loop Response of SAW-VCO                    |     |

| 6.4; Peak Detecting Comparator                        |     |

| 6.4.1 Input Level Shift:                              |     |

| 6.4.2 Transconductance Stage                          |     |

| 6.4.3 Peak Detection Stage                            |     |

| 6.4.4 Hysteresis Stage                                |     |

| 6.4.5 Buffer                                          |     |

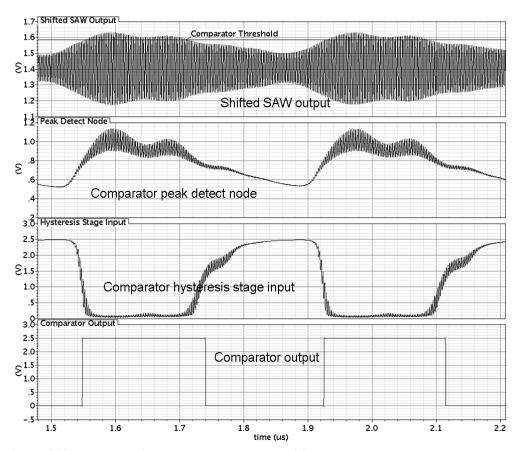

| 6.4.6 Node transitions                                | 56  |

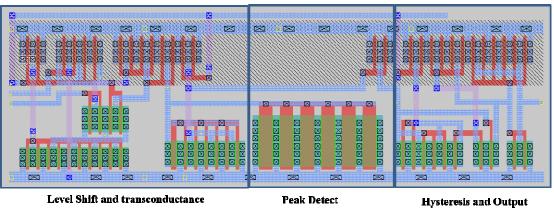

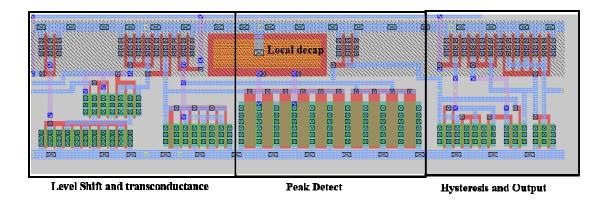

| 6.4.7 Layout                                                                 | 57  |

|------------------------------------------------------------------------------|-----|

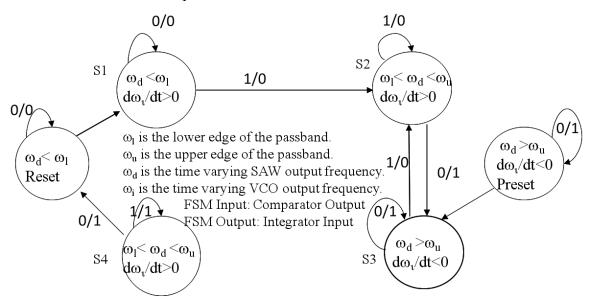

| 6.5: Finite State Machine Implementation                                     |     |

| Chapter 7: Simulation and Experimental Results of Primary Sensor Loop        |     |

| Section 7.1: Introduction                                                    | 72  |

| Section 7.2: Simulations for 374MHz Device                                   | 72  |

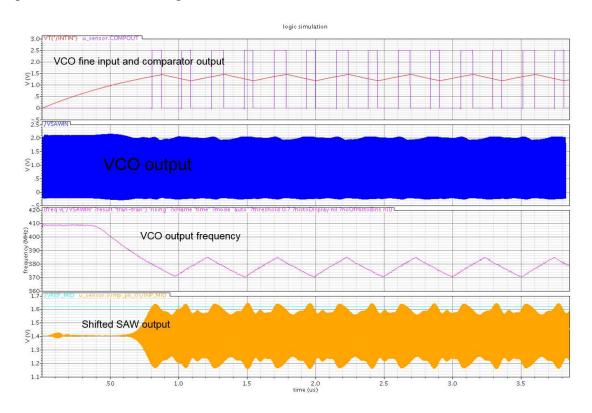

| 7.2.1 Transient Simulations                                                  |     |

| 7.2.2 Transient Simulations with Noise                                       | 74  |

| Section 7.3: Simulations for 140MHz Device                                   |     |

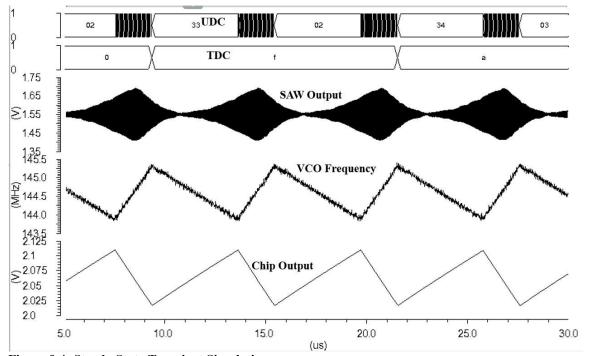

| Subsection 7.3.1: Transient Simulations                                      | 76  |

| Subsection 7.3.2 Transient Simulations with Noise                            | 77  |

| 7.4: Simulations for 70MHz Device                                            | 78  |

| 7.4.1 Transient Simulations                                                  | 78  |

| 7.5: Experimental Results                                                    | 84  |

| 7.5.1: Test results with 140MHz IF SAW device                                | 86  |

| 7.5.2: Test results with 70MHz IF SAW device                                 | 90  |

| Section 7.6: Summary                                                         | 98  |

| Chapter 8: Design and Analysis of Secondary Sensor Loop                      |     |

| 8.1 Introduction                                                             |     |

| 8.2: Control Logic Block                                                     |     |

| Section 8.3: Modified Up/Down Counter                                        |     |

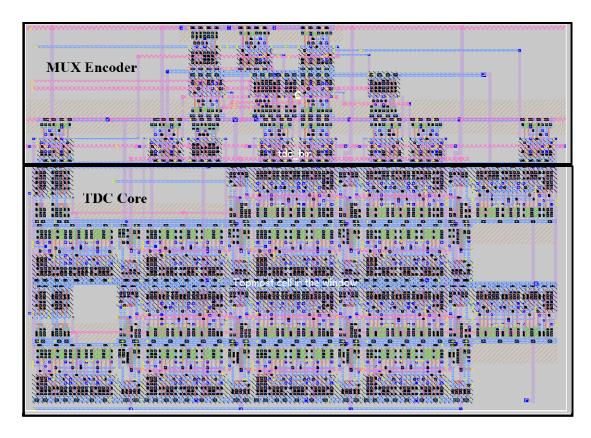

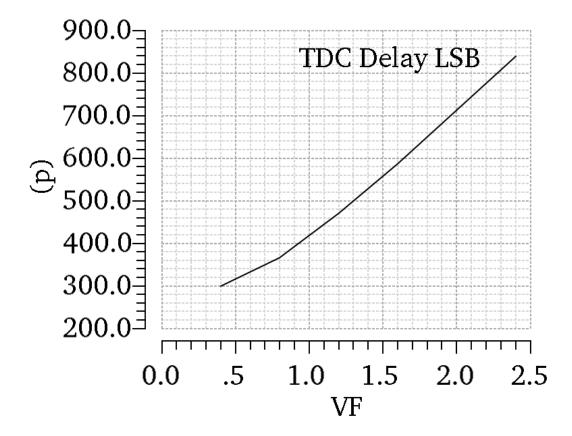

| Section 8.4: Time to Digital Converter                                       |     |

| Section 8.5: Summary                                                         |     |

| Chapter 9: Experimental and Circuit Simulation Results of Secondary Sensor I |     |

|                                                                              | 110 |

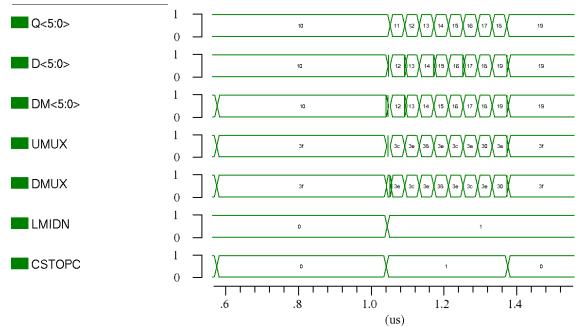

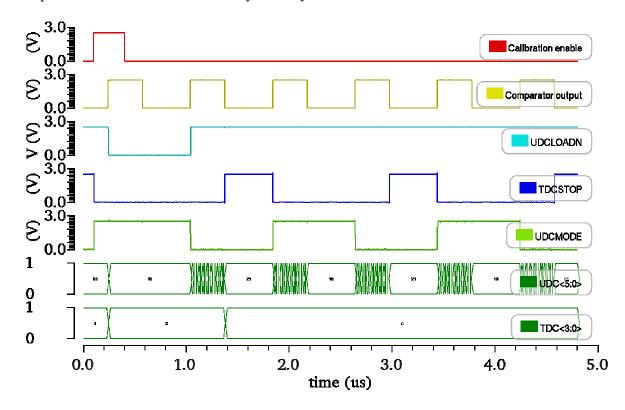

| 9.1 Introduction                                                             | 110 |

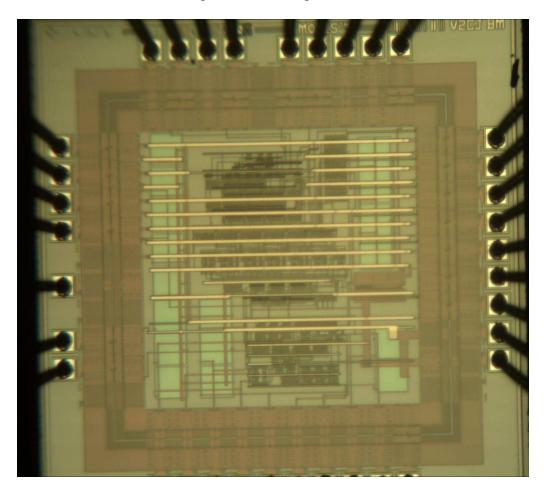

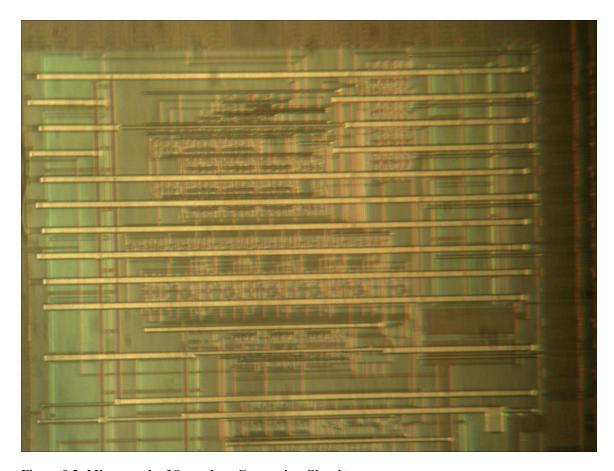

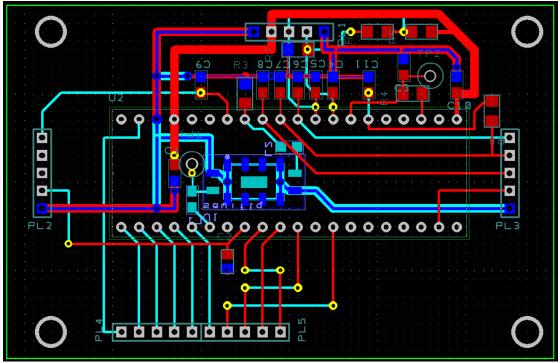

| 9.2 Test Chip Fabrication.                                                   | 111 |

| 9.3 System Test Results                                                      | 113 |

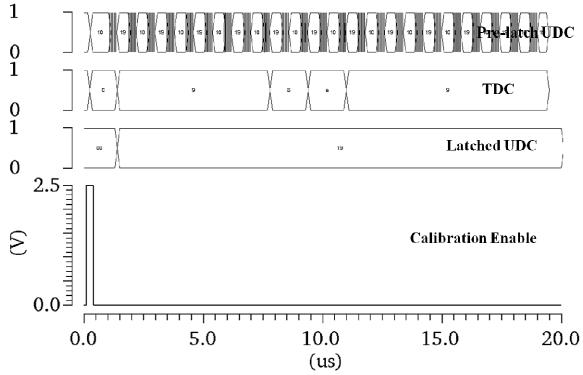

| 9.4 Delay to Digital Conversion test Results                                 |     |

| 9.5 Performance Summary                                                      |     |

| 9.5 Summary                                                                  |     |

| Chapter 10: Conclusions and Future Work                                      |     |

| 10.1 Design Features                                                         |     |

| 10.2 Modeling and Analysis                                                   |     |

| 10.3 Future Work                                                             |     |

| Appendix                                                                     |     |

| A.1 Alternate readout topology                                               |     |

| A.2 MATLAB Code                                                              |     |

| Bibliography                                                                 |     |

# List of Tables

| Table 6.1: Transistor W/L ratios in Peak Detecting Comparator for AMI 0.5µm         |     |

|-------------------------------------------------------------------------------------|-----|

| process                                                                             | 51  |

| Table 7.1: Summary of Simulation Results for 70MHZ SAW device. Ton and Tof          |     |

| represent the high and low durations respectively of the FSM output                 | 84  |

| Table 7.2: Summary of Experimental Results for 70MHZ SAW device. Ton and Table 7.2: | off |

| represent the high and low durations respectively of the FSM output                 | 97  |

| Table 8.1: State transition table of conversion control block                       | 100 |

| Table 9.1: Performance Summary                                                      | 119 |

# List of Figures

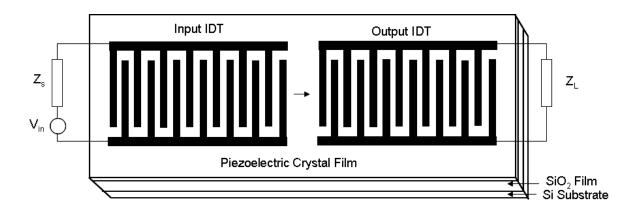

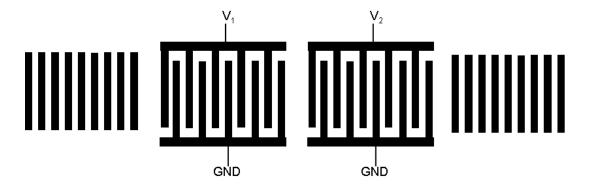

| Figure 2.1: Basic IDT Comb Structure                                            | 6  |

|---------------------------------------------------------------------------------|----|

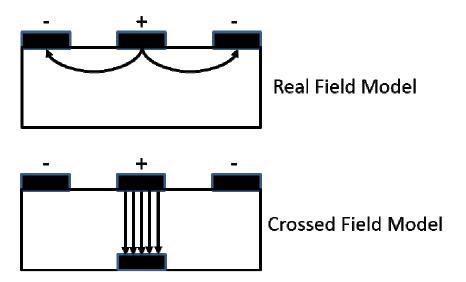

| Figure 2.2: Electric field - Real and approximate                               | 7  |

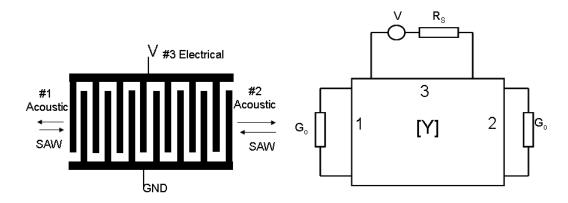

| Fig. 2.3: Equivalent three port representation of a single IDT                  | 8  |

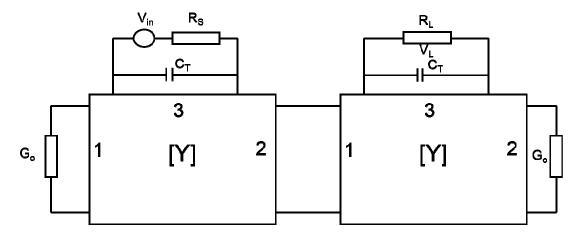

| Figure 2.4: Two-IDT representation using cascaded three port model              |    |

| Figure 2.5: Two Port SAW Resonator                                              |    |

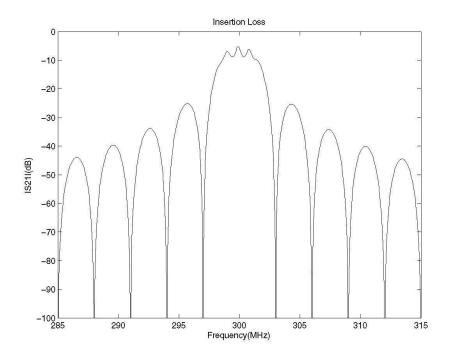

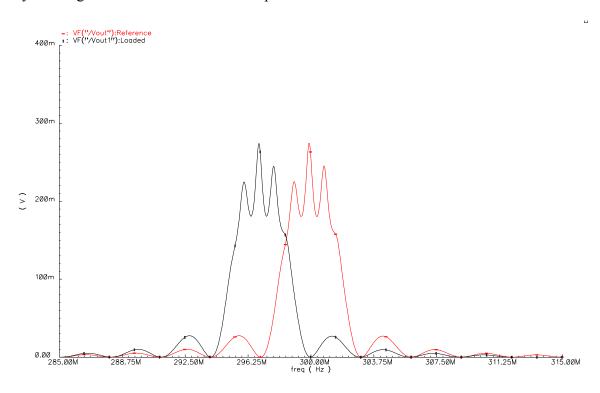

| Fig. 2.6: SAW Delay Line Simulated Response at 300MHz.                          | 14 |

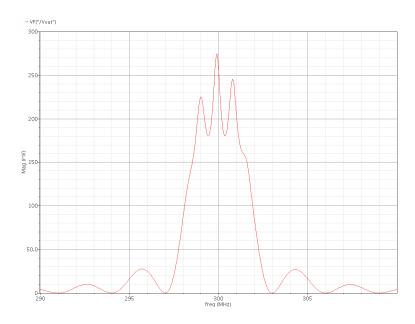

| Figure 2.7: SAW Output Frequency Response of Transfer Function                  |    |

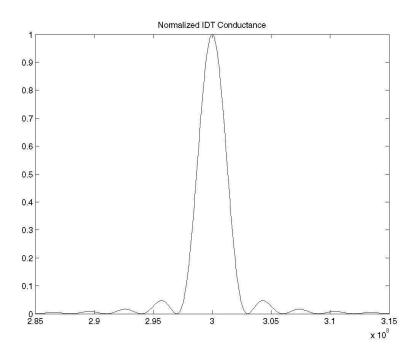

| Fig. 2.8: Frequency Response of Normalized Input Admittance                     | 15 |

| Figure 3.1: Physisorption and Chemisorption Mechanisms                          | 20 |

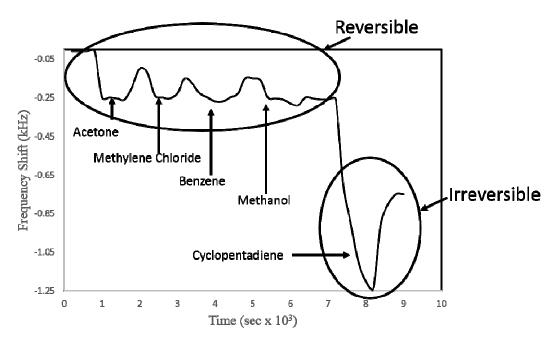

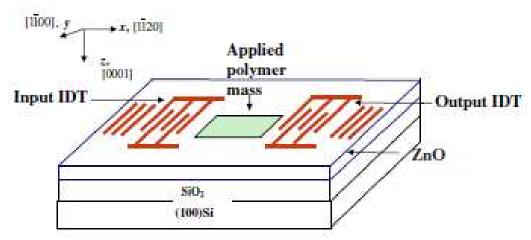

| Fig. 4.1: Polymer mass measurement with Love mode sensor                        | 25 |

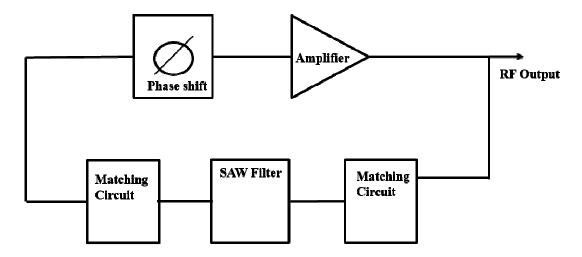

| Figure 4.2: General SAW oscillator block diagram                                | 27 |

| Figure 4.3: Oscillator Based Sensor Example                                     | 27 |

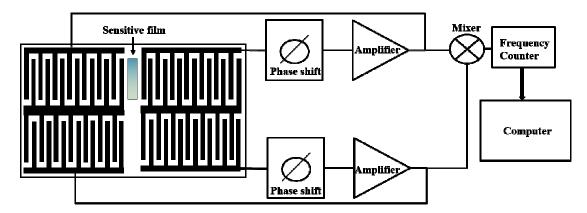

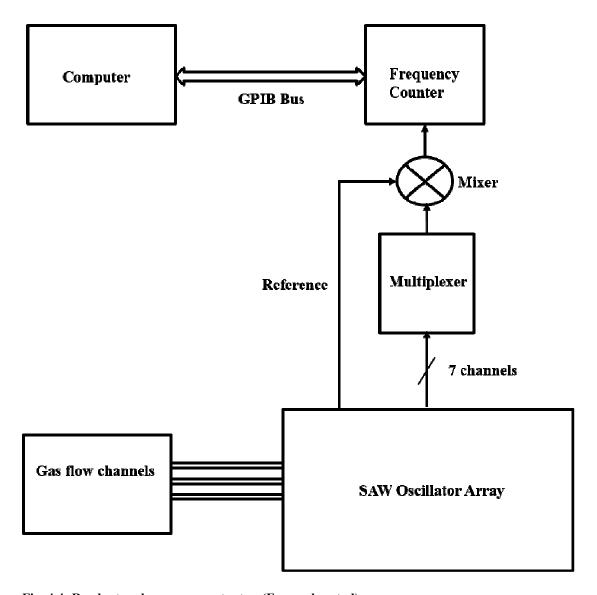

| Fig. 4.4: Readout and measurement setup (Fernandez et al)                       | 30 |

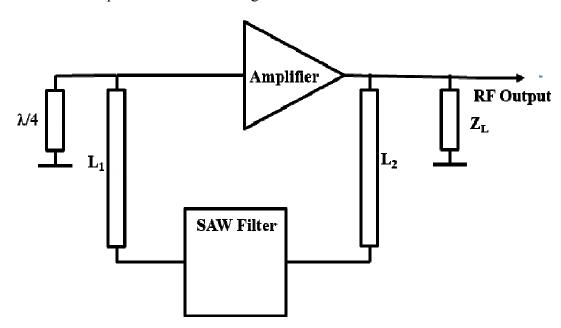

| Fig. 4.5: Oscillator topology with distributed microstrip components.           |    |

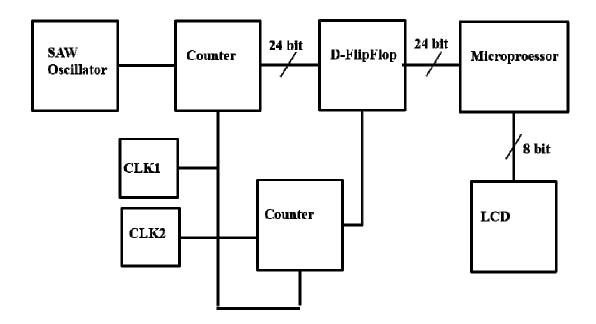

| Figure 4.6: Oscillator topology with digital readout (Hao et al.)               | 35 |

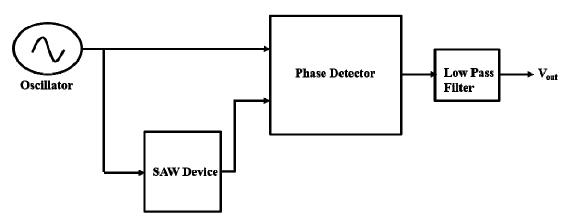

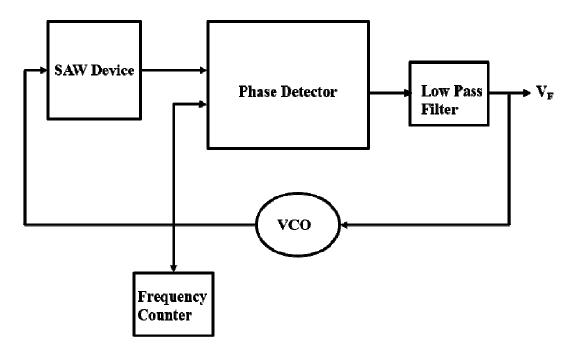

| Figure 4.7: Phase detector based SAW sensor.                                    | 36 |

| Figure 4.8: PLL based SAW sensor                                                |    |

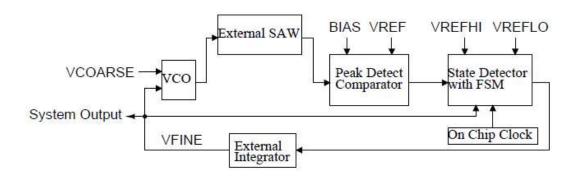

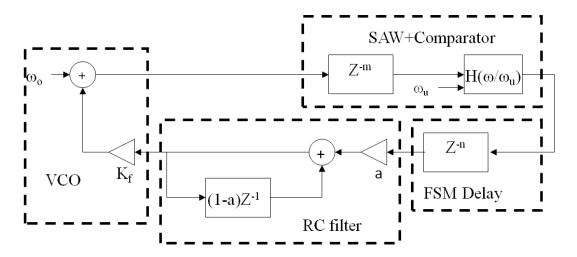

| Figure 5.1: Primary Sensor Loop Block Diagram                                   | 41 |

| Figure 5.2: Digital Conversion of Sensor Output                                 |    |

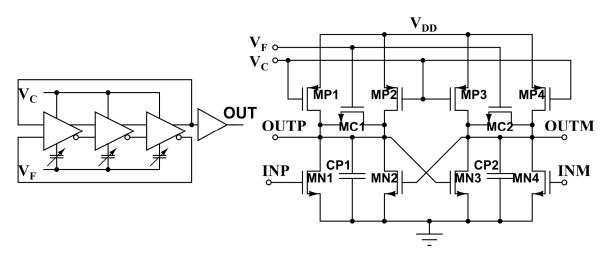

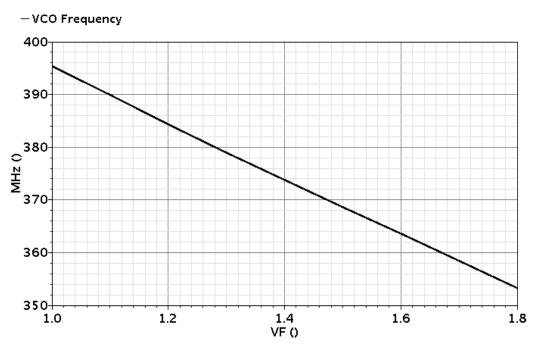

| Figure 6.1: VCO with Coarse and Fine Controls                                   |    |

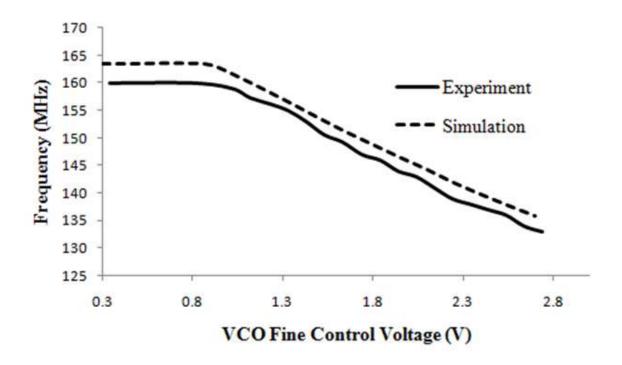

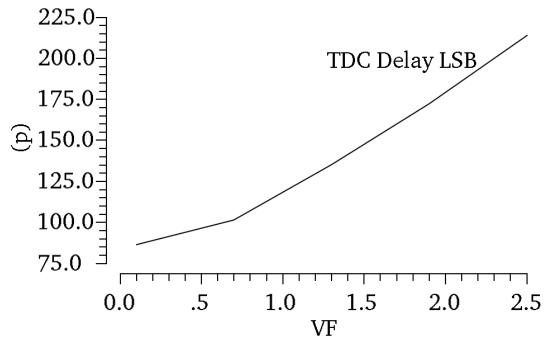

| Figure 6.2: VCO Frequency versus Fine Input Voltage                             |    |

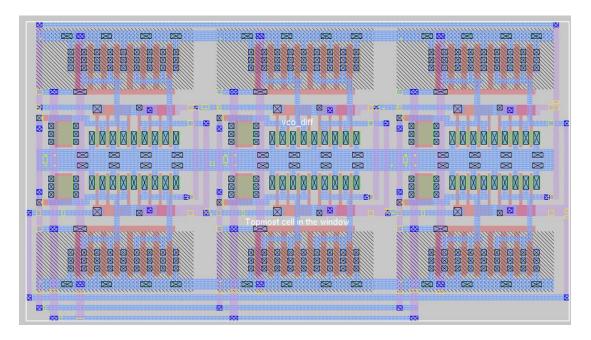

| Figure 6.3: VCO Layout                                                          |    |

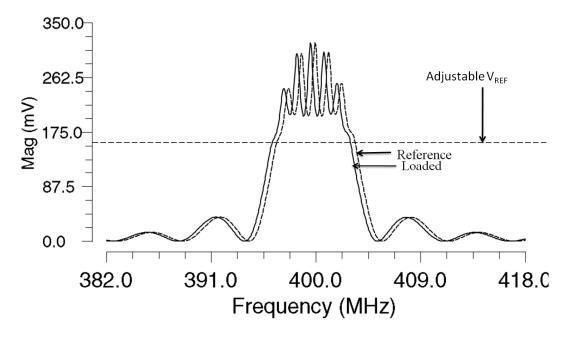

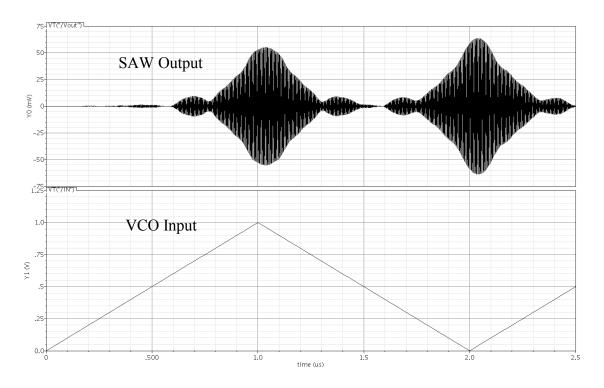

| Figure 6.4: Illustrative response of loaded and unloaded data lines.            |    |

| Figure 6.5: SAW Response to VCO                                                 |    |

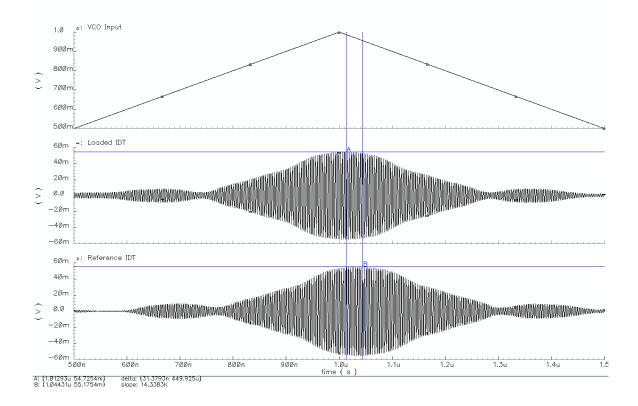

| Figure 6.6: Response of loaded and unloaded IDTs                                |    |

| Figure 6.7: Transient responses of loaded and unloaded IDT                      |    |

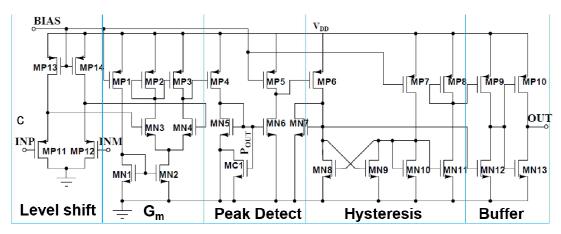

| Fig. 6.8: Peak detecting comparator                                             |    |

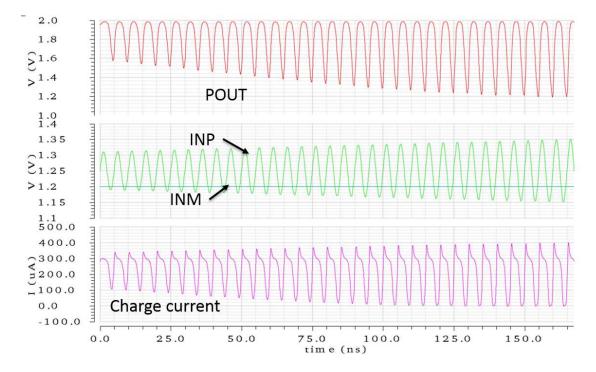

| Fig. 6.9: Peak detect stage waveforms.                                          |    |

| Figure 6.10: Peak detecting comparator node transitions                         |    |

| Fig. 6.11: Layout of peak detecting comparator                                  |    |

| Figure 6.12: Layout of comparator with external common mode                     |    |

| Figure 6.13: Finite State Machine Diagram.                                      |    |

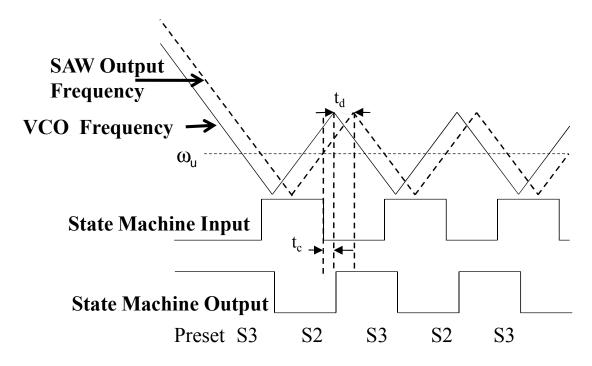

| Figure 6.14: Conceptual Timing Diagram                                          |    |

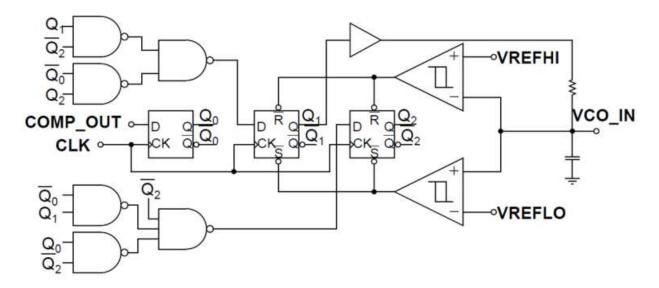

| Fig. 6.15: Finite State Machine Circuit.                                        | 62 |

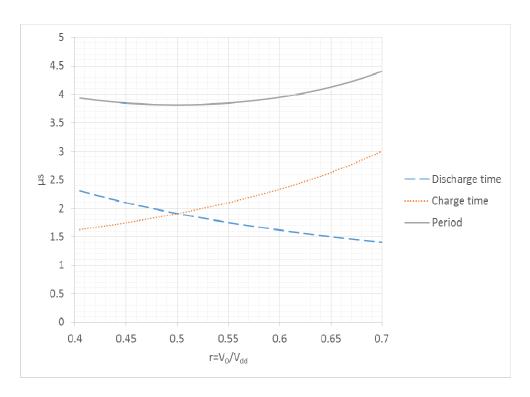

| Figure 6.16 Variation of charge time, discharge time and period with equivalent |    |

| passband threshold                                                              |    |

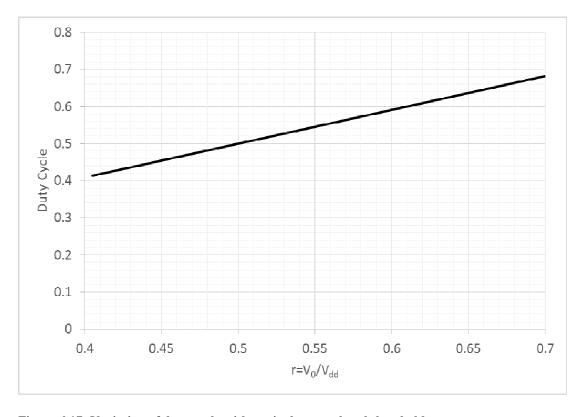

| Figure 6.17: Variation of duty cycle with equivalent passband threshold         |    |

| Fig. 6.18: Behavioral Model Simulation Results.                                 |    |

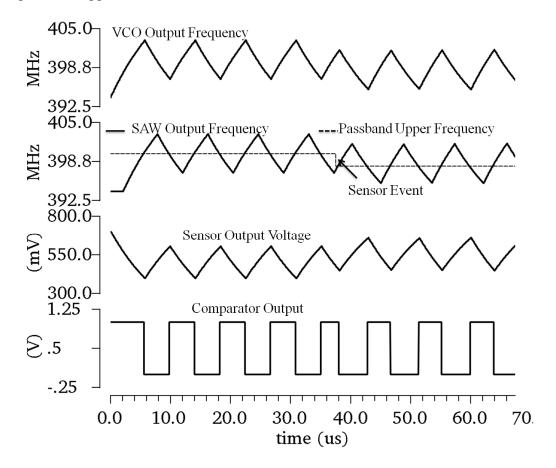

| Figure 7.1: Steady State Transient Simulation                                   |    |

| Fig. 7.2: Startup transient simulation                                          | 74 |

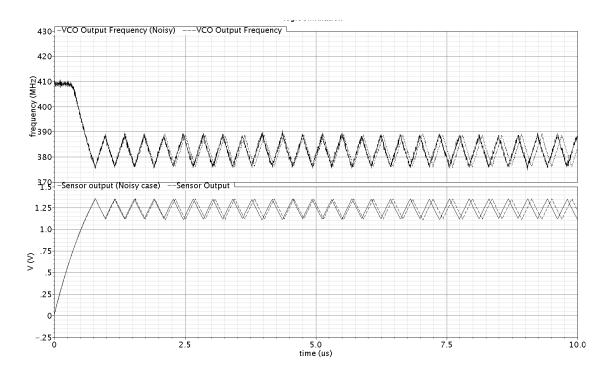

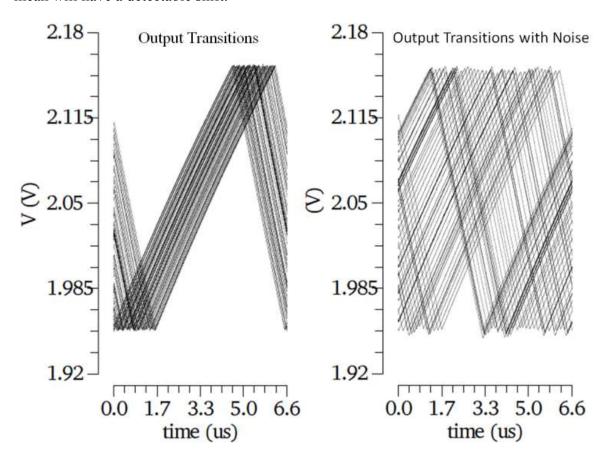

| Figure 7.3: Transient simulation with VCO noise                                 | 75 |

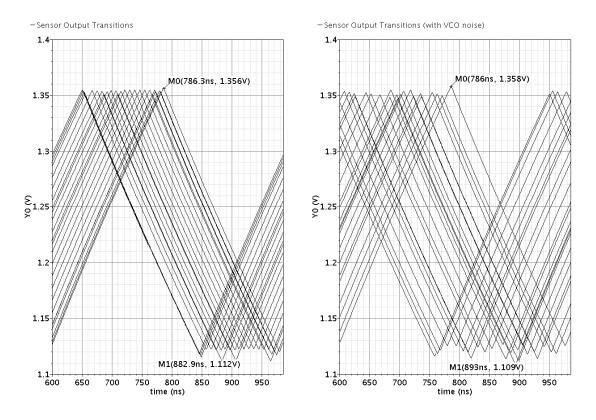

| Figure 7.4: Superimposed Output Transitions within Time Period                  |    |

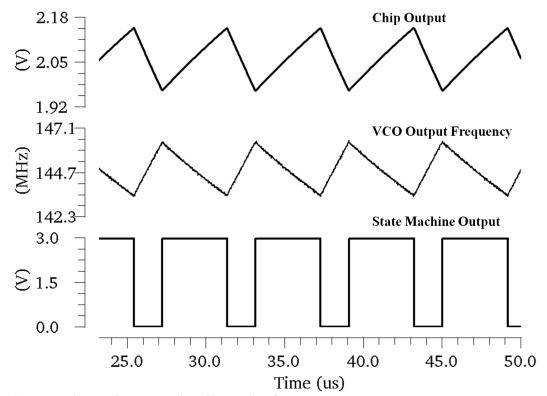

| Figure 7.5: Steady State Transient Simulation Outputs                           | 77 |

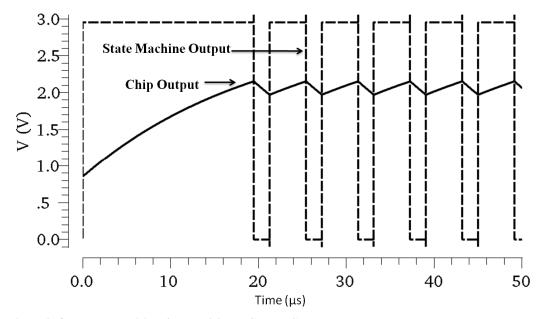

| Fig. 7.6: Output Transition from Initial to Steady State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 7.7: Superimposed Output Transitions within Time Period, 140MHz SAW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

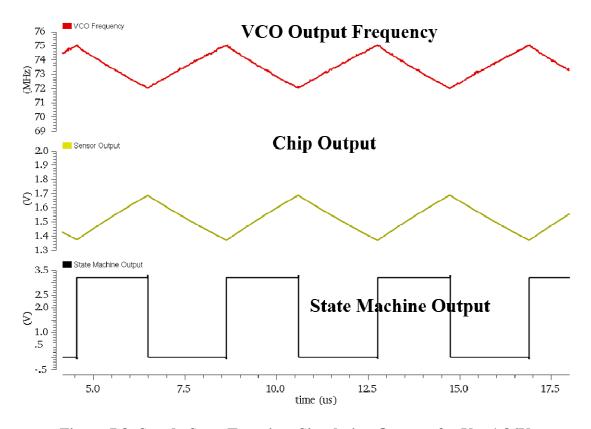

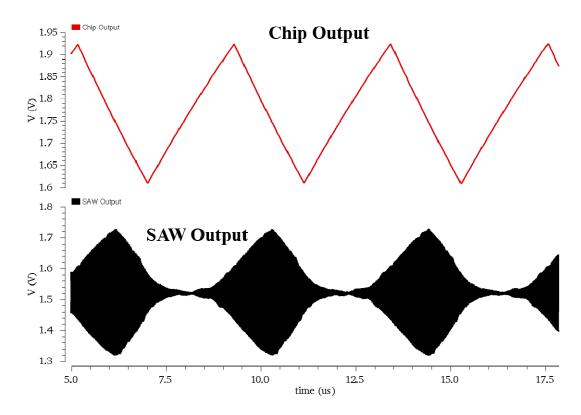

| Figure 7.8: Steady State Transient Simulation Outputs for V <sub>c</sub> = 1.86V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79  |

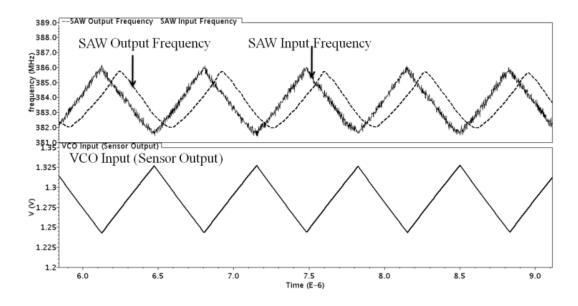

| Figure 7.9: Steady State Transient SAW Output and Sensor Output for V <sub>c</sub> = 1.86V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

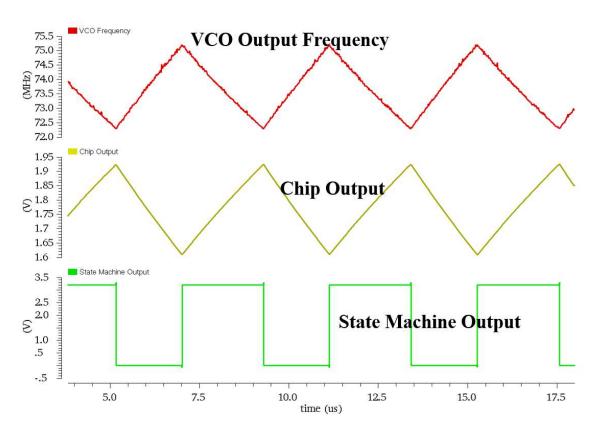

| Figure 7.10: Steady State Transient Simulation Outputs for V <sub>c</sub> = 1.85V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Figure 7.11: Steady State Transient SAW Output and Sensor Output for V <sub>c</sub> = 1.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Figure 7.12: Steady State Transient Simulation Outputs for V <sub>c</sub> = 1.84V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Figure 7.13: Steady State Transient SAW Output and Sensor Output for $V_c$ = 1.84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

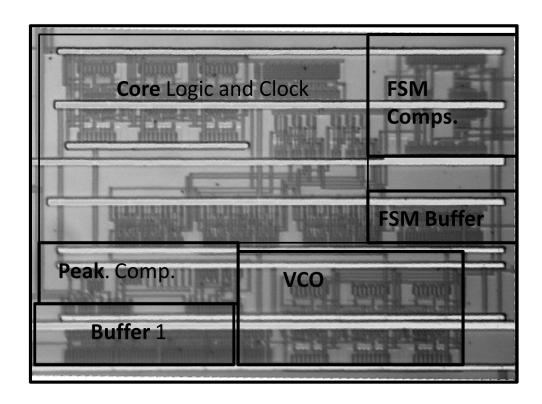

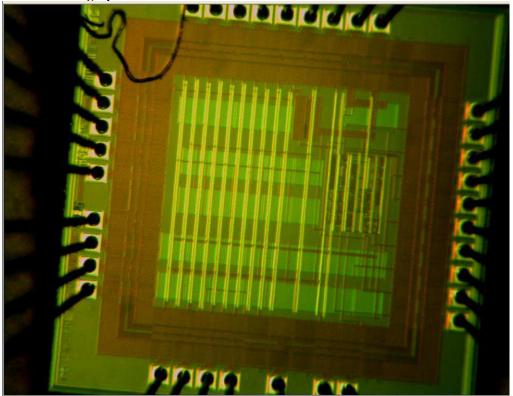

| Figure 7.14: Micrograph of Die Active Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Figure 7.15: Micrograph of Die with Pad Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Figure 7.16: VCO fine input gain: Simulated vs. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

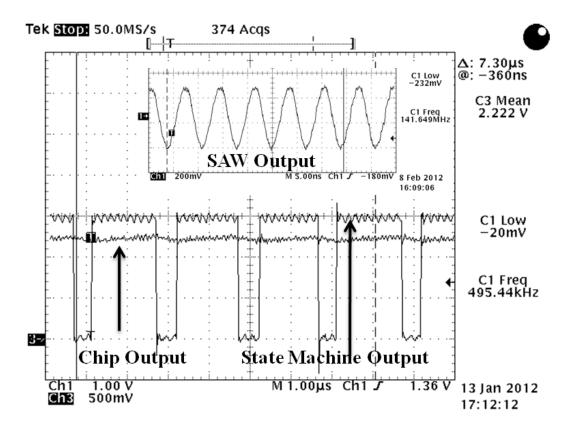

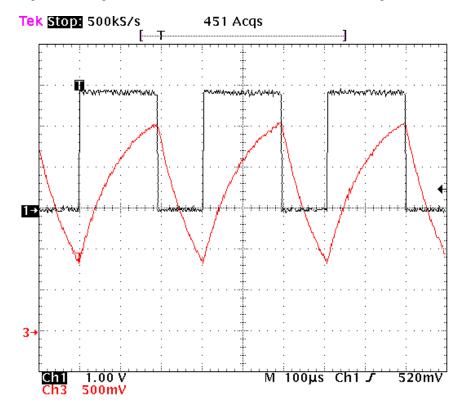

| Figure 7.17: Experimental waveforms of sensor and state machine outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Figure 7.18: Experimental waveforms of alternate mode where comparator thresholds believe and a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| is below range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89  |

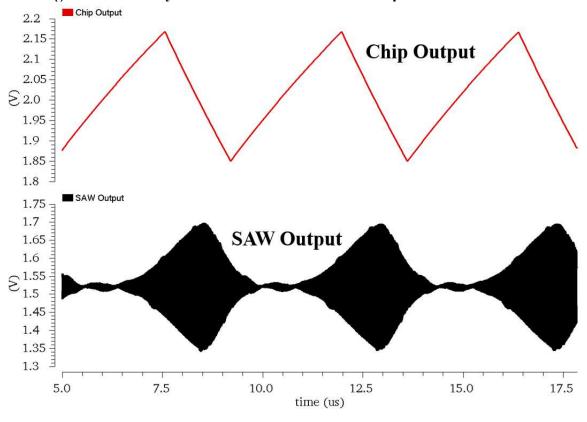

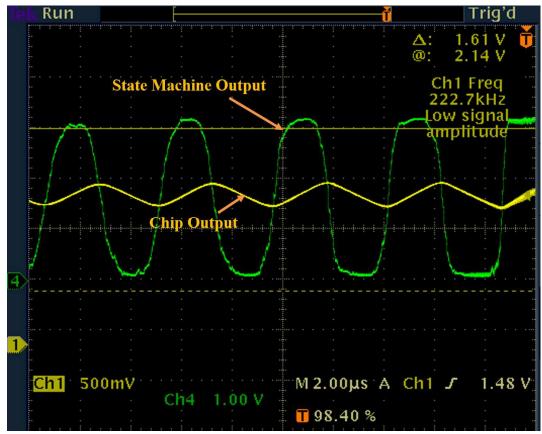

| Figure 7.19: Experimental waveforms of alternate mode where SAW frequency is if range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

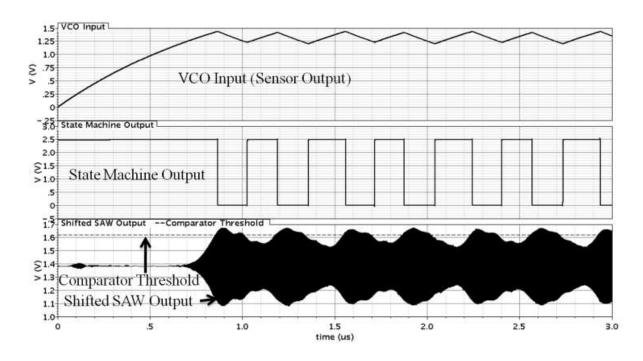

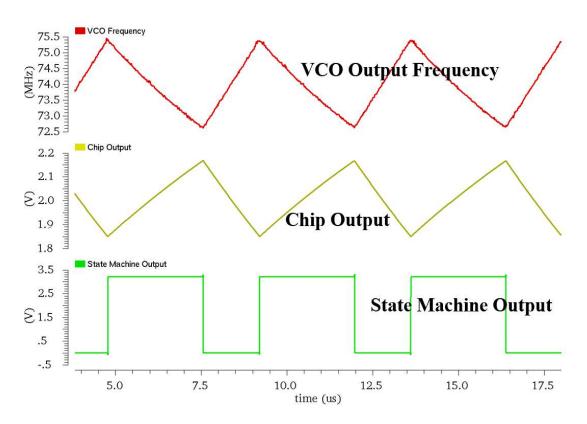

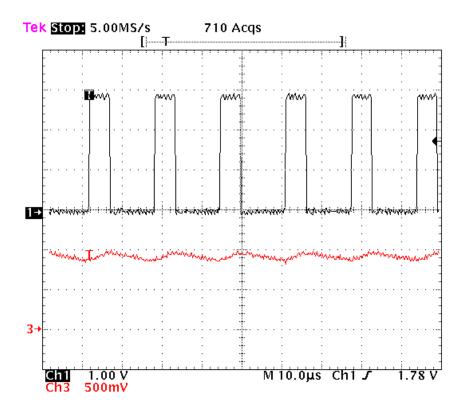

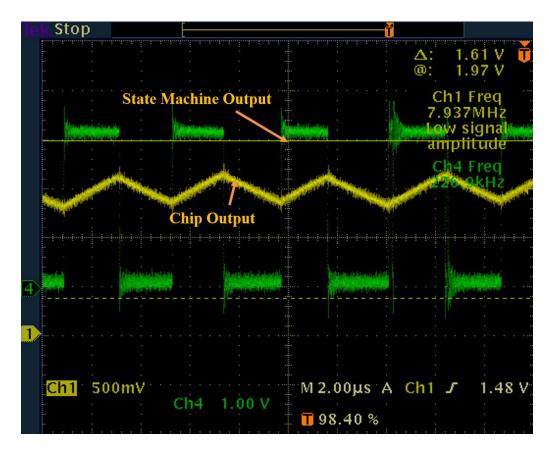

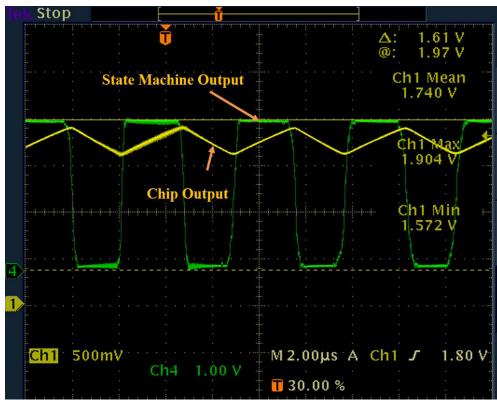

| if range. Figure 7.20: Capture of Chip Output and State Machine Output for $V_c$ = 1.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Figure 7.20. Capture of Chip Output and State Machine Output for $V_c$ = 1.8 | 91  |

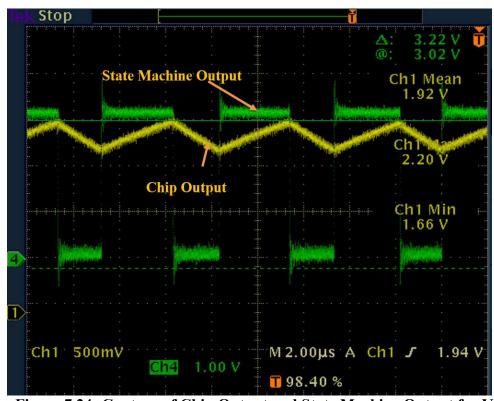

| Averaging Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92  |

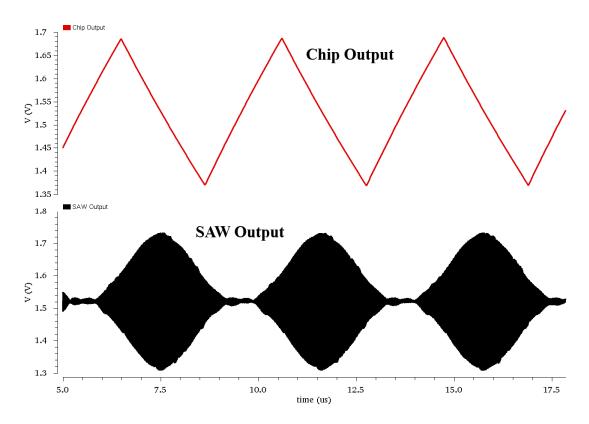

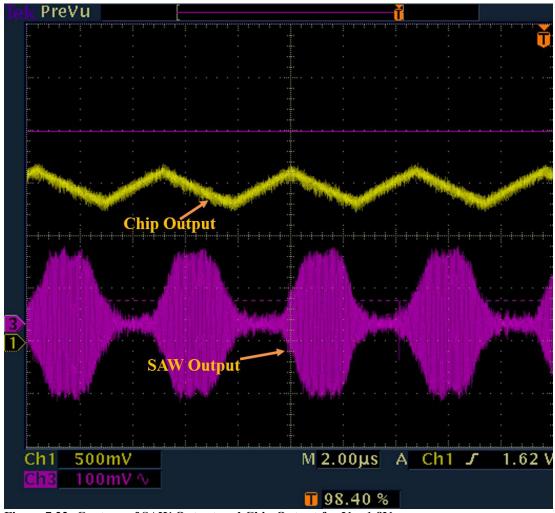

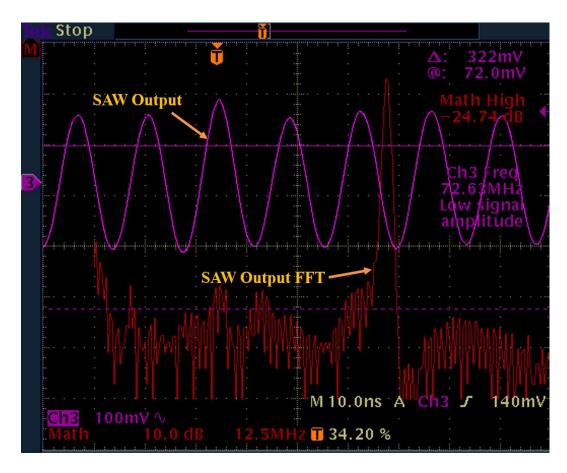

| Figure 7.22: Capture of SAW Output and Chip Output for V <sub>c</sub> = 1.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Figure 7.23: Capture of Chip Output and State Machine Output for V <sub>c</sub> = 1.79V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

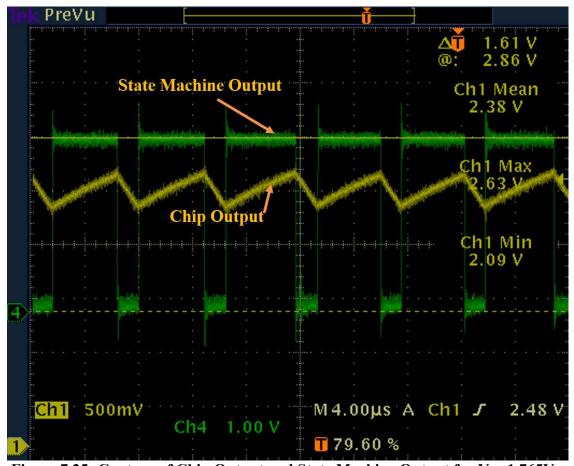

| Figure 7.24: Capture of Chip Output and State Machine Output for $V_c = 1.78V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Figure 7.25: Capture of Chip Output and State Machine Output for $V_c$ = 1.765V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

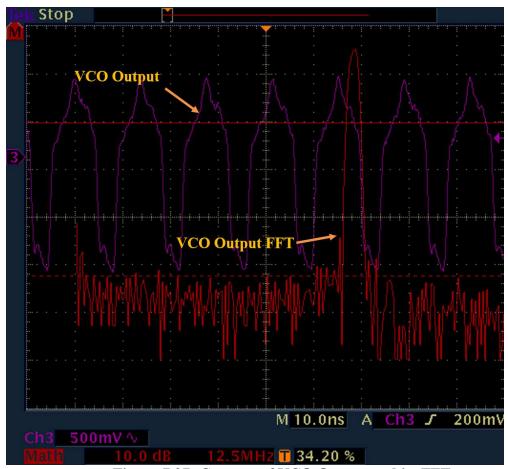

| Figure 7.26: Capture of SAW Output and its FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Figure 7.27: Capture of VCO Output and its FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

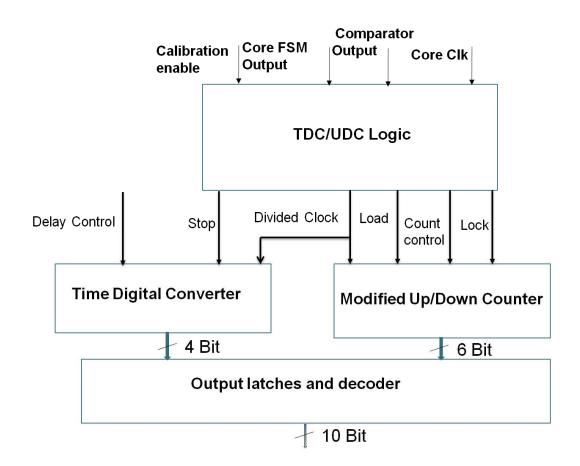

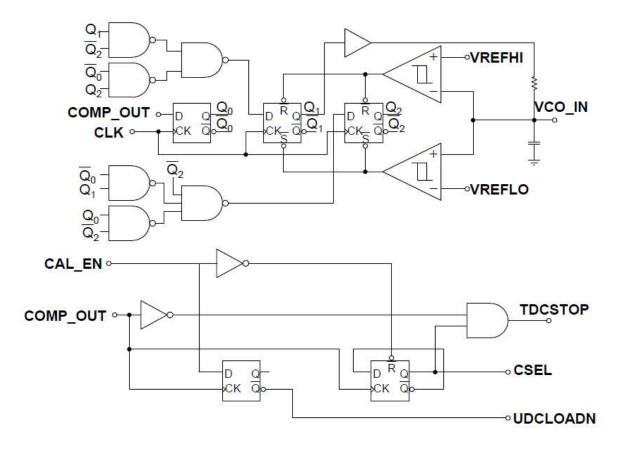

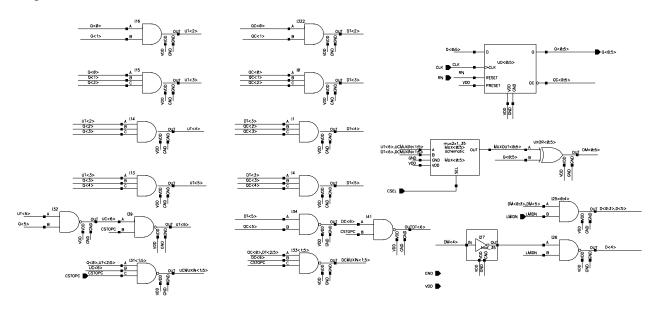

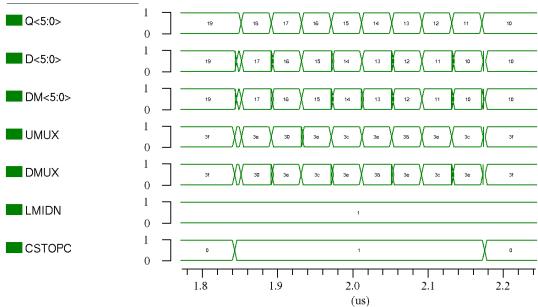

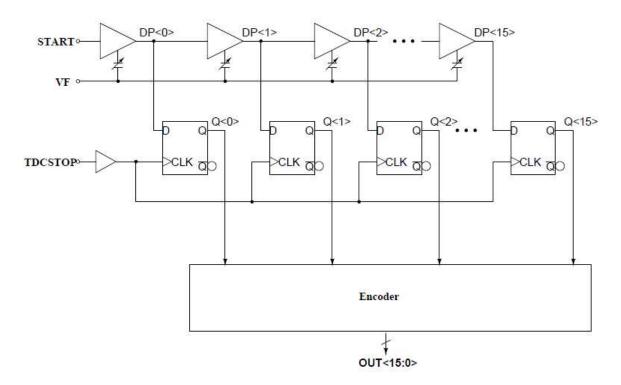

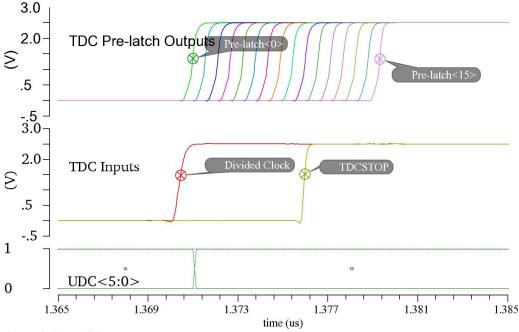

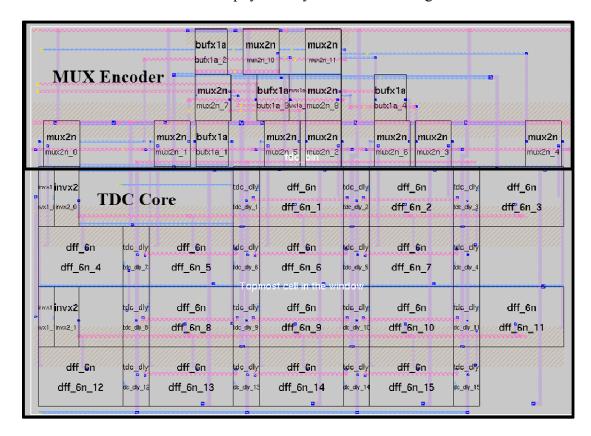

| Figure 8.1: Complete Finite State Machine Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |