ABSTRACT

Title of dissertation: HIERARCHICAL MAPPING TECHNIQUES

FOR SIGNAL PROCESSING SYSTEMS

ON PARALLEL PLATFORMS

Lai-Huei Wang, Doctor of Philosophy, 2014

Dissertation directed by: Professor Shuvra S. Bhattacharyya

Department of Electrical and Computer Engineering

Dataflow models are widely used for expressing the functionality of digital signal processing (DSP) applications due to their useful features, such as providing formal mechanisms for description of application functionality, imposing minimal data-dependency constraints in specifications, and exposing task and data level parallelism effectively. Due to the increased complexity of dynamics in modern DSP applications, dataflow-based design methodologies require significant enhancements in modeling and scheduling techniques to provide for efficient and flexible handling of dynamic behavior. To address this problem, in this thesis, we propose an innovative framework for mode- and dynamic-parameter-based modeling and scheduling. We apply, in a systematically integrated way, the structured mode-based dataflow modeling capability of dynamic behavior together with the features of dynamic parameter reconfiguration and quasi-static scheduling.

Moreover, in our proposed framework, we present a new design method called parameterized multidimensional design hierarchy mapping (PMDHM), which is targeted to the flexible, multi-level reconfigurability, and intensive real-time processing requirements of emerging dynamic DSP systems. The proposed approach allows designers to systematically represent and transform multi-level specifications of signal processing applications from a common, dataflow-based application-level model. In addition, we propose a new technique for mapping optimization that helps designers derive efficient, platform-specific parameters for application-to-architecture mapping. These parameters help to maximize system performance on state-of-theart parallel platforms for embedded signal processing.

To further enhance the scalability of our design representations and implementation techniques, we present a formal method for analysis and mapping of parameterized DSP flowgraph structures, called *topological patterns*, into efficient implementations. The approach handles an important class of parameterized schedule structures in a form that is intuitive for representation and efficient for implementation.

We demonstrate our methods with case studies in the fields of wireless communication and computer vision. Experimental results from these case studies show that our approaches can be used to derive optimized implementations on parallel platforms, and enhance trade-off analysis during design space exploration. Furthermore, their basis in formal modeling and analysis techniques promotes the applicability of our proposed approaches to diverse signal processing applications and architectures.

# HIERARCHICAL MAPPING TECHNIQUES FOR SIGNAL PROCESSING SYSTEMS ON PARALLEL PLATFORMS

by

# Lai-Huei Wang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2014

Advisory Committee:

Professor Shuvra S. Bhattacharyya, Chair/Advisor

Professor Manoj Franklin

Professor Steven A. Tretter

Professor K.J. Ray Liu

Professor Yang Tao, Dean's representative

© Copyright by Lai-Huei Wang 2014

#### Acknowledgments

I would like to express my sincere gratitude to my advisor, Dr. Shuvra S. Bhattacharyya for his academic guidance and financial support throughout my doctoral research work in the DSPCAD research group. He provided me great support to pursue and develop my desired research interests. During my PhD education, he has been the superb mentor whom I have learned a lot from. His expertise in the fields of signal processing and model-based design helps significantly to the critical thinking in my research work. Especially, I am grateful to him for his patience and thoughtful understanding during his guidance to my PhD work. I also thank him for giving me valuable research and teaching opportunities. Absolutely, the experience working with Dr. Bhattacharyya has been one of the most important career experience of my life.

I would also like to thank the members of my dissertation committee, Prof. Manoj Franklin, Prof. Steven Tretter, Prof. Ray Liu, and Prof. Yang Tao for their service and constructive comments and feedback.

The research underlying this thesis was supported in part by the Austrian Marshall Plan Foundation, the Laboratory for Telecommunications Sciences, and the US National Science Foundation. I sincerely thank for their support.

It has been a pleasure to conduct research with the DSPCAD members, including Chung-Ching Shen, William Plishker, Hsiang-Huang Wu, George Zaki, Zheng Zhou, Kishan Sudusinghe, Shuoxin Lin, Inkeun Cho, Scott Kim, and Yanzhou Liu. Among them, I specially thank Chung-Ching and Hsiang-Huang for their assistance

and guidance during my beginning phase of research in the group.

I would like to thank my parents for their love, encouragement, and support during my PhD program. Also, I am grateful to my sisters for their encouragement during these years.

Last, and most importantly, I would like to give my deepest gratitude to my wife, Cindy. Without her constant encouragement, patience, and support throughout my doctoral studies, I would not have been able to successfully complete my PhD program. Her love is the biggest source of inspiration that enables me to overcome the challenges during my PhD pursuit.

# Table of Contents

| List of I | Figures |                                                        | vi |

|-----------|---------|--------------------------------------------------------|----|

| 1         | Introd  | uction                                                 | 1  |

|           | 1.1     | Core Functional Parameterized Synchronous Dataflow     | 3  |

|           | 1.2     | Hierarchical Mapping Approach                          | 5  |

|           | 1.3     | Scheduling Representation                              | 6  |

|           | 1.4     | Organization of the Thesis                             | 7  |

| List of A | Abbrevi | ations                                                 | 1  |

| 2         | Backgr  | round                                                  | 9  |

|           | 2.1     | Dataflow Modeling                                      | 9  |

|           | 2.2     | Multidimensional Synchronous Dataflow                  | 10 |

|           | 2.3     | Parameterized Synchronous Dataflow                     | 10 |

|           | 2.4     | Core Functional Dataflow                               | 11 |

|           | 2.5     | Topological Patterns                                   | 12 |

|           | 2.6     | Generalized Schedule Trees                             | 13 |

|           | 2.7     | General Purpose Graphics Processing Units              | 14 |

| 3         | CF-PS   | DF Modeling and Scheduling                             | 16 |

|           | 3.1     | CF-PSDF Model                                          | 17 |

|           | 3.2     | Multi-Mode Actors                                      | 20 |

|           | 3.3     | Subsystem Modes                                        | 21 |

|           | 3.4     | Scheduling Techniques                                  | 23 |

|           | 3.5     | Case Study: MIMO Detection                             | 25 |

|           |         | 3.5.1 Application Model based on CF-PSDF               | 25 |

|           |         | 3.5.2 Experimental Results                             | 28 |

|           | 3.6     | Related Work                                           | 30 |

| 4         | Hierar  | chical Mapping for Parallel Architectures              | 32 |

|           | 4.1     | PMDHM Framework                                        | 33 |

|           |         | 4.1.1 Multi-level Hierarchical Dataflow Transformation | 34 |

|           |         | 4.1.2 Partitioning of Mapping Cluster Graphs           | 39 |

|           |         | 4.1.3 Deriving Dataflow Rates for Intra-Channel Edges  | 46 |

|           |         | 4.1.4 An Example of Pipelined AMCG Construction        | 48 |

|           |         | 4.1.5 Graph Decomposition Example                      | 50 |

|          | 4.2    | Mapping            | g Process and Optimization                |

|----------|--------|--------------------|-------------------------------------------|

|          |        | 4.2.1              | Overview                                  |

|          |        | 4.2.2              | PMDHM Supernode Transformation 55         |

|          | 4.3    | Related            | Work                                      |

| 5        | PMDF   | HM Case            | Studies                                   |

|          | 5.1    | Case Stu           | idy: LFSD Subsystem for MIMO Detection 63 |

|          |        | 5.1.1              | Application Graph                         |

|          |        | 5.1.2              | DH Exploration                            |

|          |        | 5.1.3              | Experiments                               |

|          |        | 5.1.4              | Summary                                   |

|          | 5.2    | Case Stu           | ıdy: Integral Histogram                   |

|          |        | 5.2.1              | Actor Design                              |

|          |        | 5.2.2              | Application Graph                         |

|          |        | 5.2.3              | Design Hierarchy Exploration 84           |

|          |        | 5.2.4              | Experiments                               |

| 6        | Enhan  | ble Schedule Trees |                                           |

|          | 6.1    |                    | del                                       |

|          | 6.2    | SST Tra            | versal Process                            |

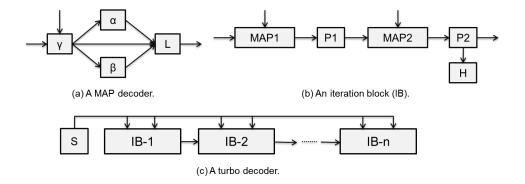

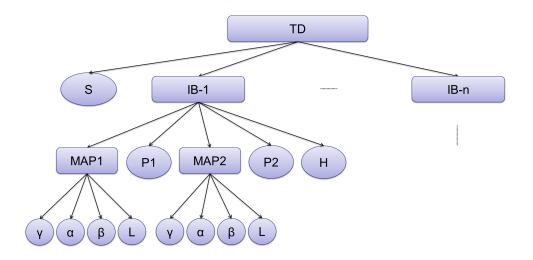

|          | 6.3    | Case Stu           | ıdy: Turbo Decoder                        |

|          |        | 6.3.1              | The Dataflow Interchange Format 93        |

|          |        | 6.3.2              | Turbo Codes                               |

|          |        | 6.3.3              | Exploring Design Trade-offs using SSTs 96 |

|          | 6.4    | Related            | Work                                      |

| 7        | Conclu | isions and         | l Future Work                             |

|          | 7.1    | Summar             | y and Conclusions                         |

|          | 7.2    | Future V           | Vork                                      |

| Bibliogi | aphy   |                    | 108                                       |

| _        |        |                    |                                           |

# List of Figures

| 2.1  | An example of thread hierarchy in CUDA                                            | 15 |

|------|-----------------------------------------------------------------------------------|----|

| 3.1  | An example of a CF-PSDF graph                                                     | 18 |

| 3.2  | Examples of PSDF and CF-PSDF actors                                               | 20 |

| 3.3  | CF-PSDF model of soft MIMO detection application                                  | 26 |

| 4.1  | An example of a three-actor MDSDF graph                                           | 35 |

| 4.2  | An example of a design hierarchy for an MDSDF specification                       | 40 |

| 4.3  | An example of pipelined AMCG derivation                                           | 49 |

| 4.4  | The application graph of (1,2,2,P) LFSD subsystem                                 | 51 |

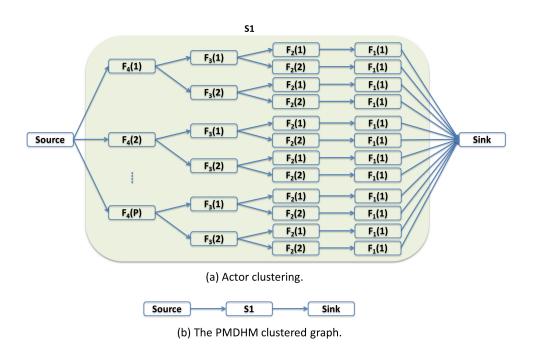

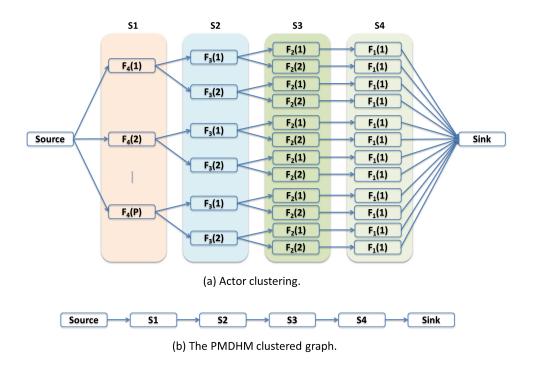

| 4.5  | The actor clustering and the PMDHM clustered graph                                | 51 |

| 4.6  | The AMCG associated with supernode S1                                             | 52 |

| 4.7  | The channel and pipeline partitions for the LFSD mapping cluster                  | 52 |

| 4.8  | The pipelined AMCG associated with supernode S1                                   | 53 |

| 4.9  | An example of the PMDHM supernode transformation                                  | 58 |

| 4.10 | Illustration of our proposed PMDHM-based design methodology for                   |    |

|      | design and implementation of signal processing systems                            | 60 |

| 5.1  | Clustering Approach B                                                             | 66 |

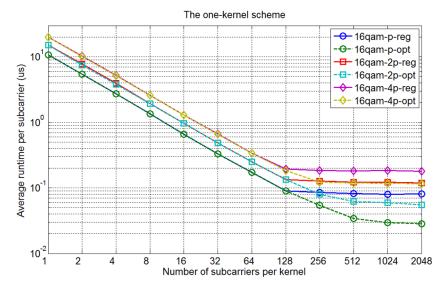

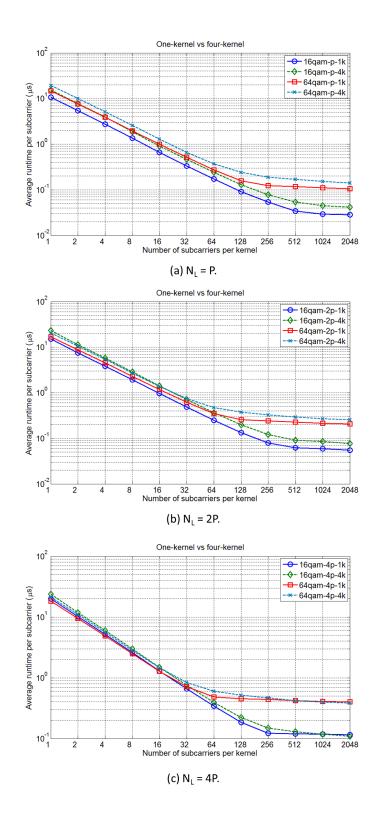

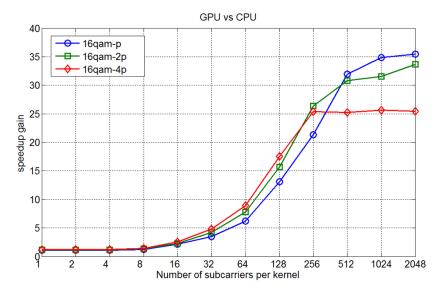

| 5.2  | Performance comparison of Clustering Approach A for 16-QAM with                   |    |

|      | and without PMDHM                                                                 | 71 |

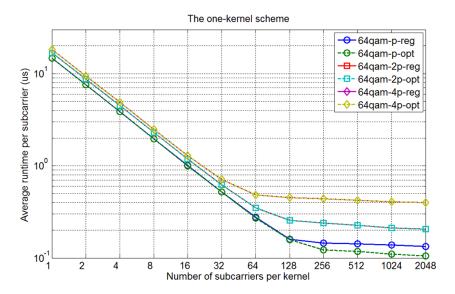

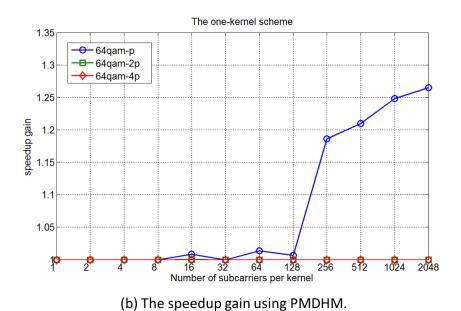

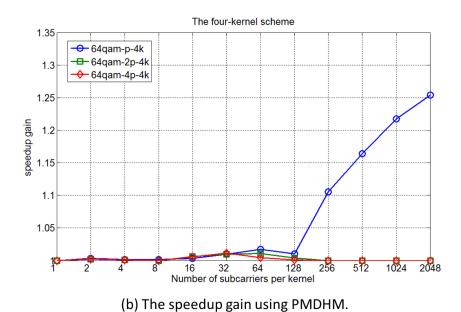

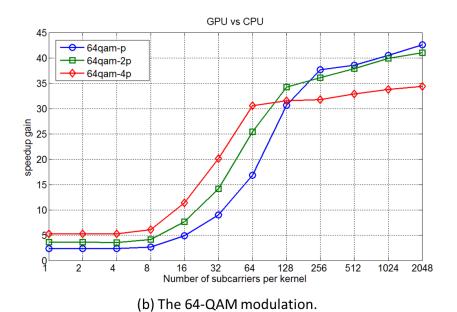

| 5.3  | Performance comparison of Clustering Approach A for 64-QAM with and without PMDHM | 72 |

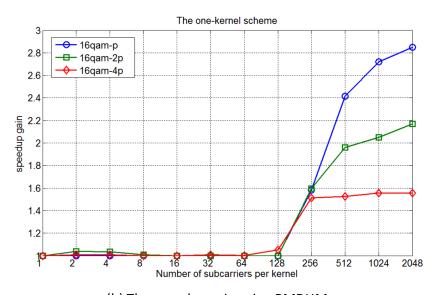

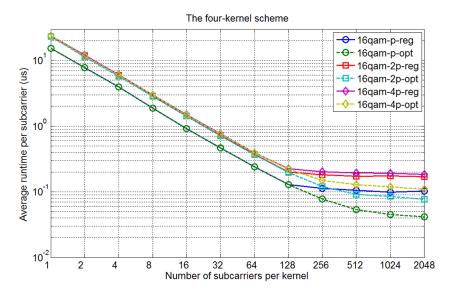

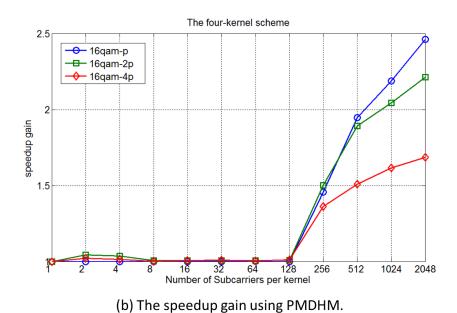

| 5.4  | Performance comparison of Clustering Approach B for 16-QAM with                   |    |

|      | and without PMDHM                                                                 | 74 |

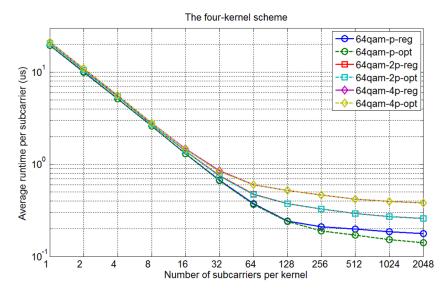

| 5.5  | Performance comparison of Clustering Approach B for 64-QAM with                   |    |

|      | and without PMDHM                                                                 | 75 |

| 5.6  | Performance comparison of Clustering Approaches A and B with the                  |    |

|      | PMDHM framework                                                                   | 76 |

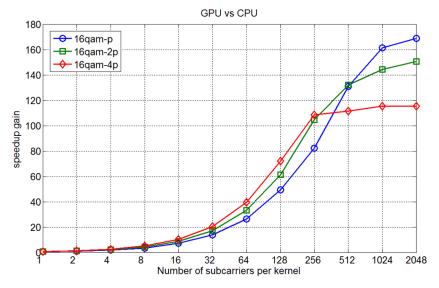

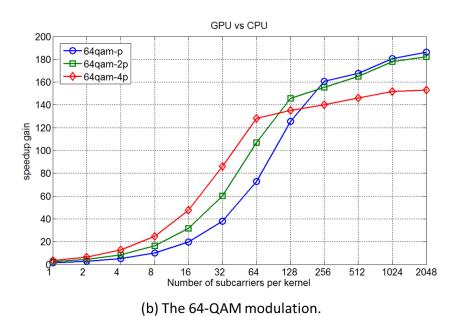

| 5.7  | Performance comparisons for GPU and single-core CPU implemen-                     |    |

|      | tations                                                                           | 78 |

| 5.8  | Performance comparisons for GPU and multi-core CPU implementa-                    |    |

|      | tions                                                                             | 79 |

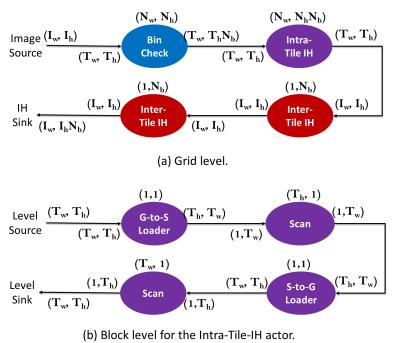

| 5.9  | MDSDF graph for optionally-tiled IH computation                                   | 83 |

| 5.10 | Hierarchical dataflow graphs for cross-weave TIH                                  | 85 |

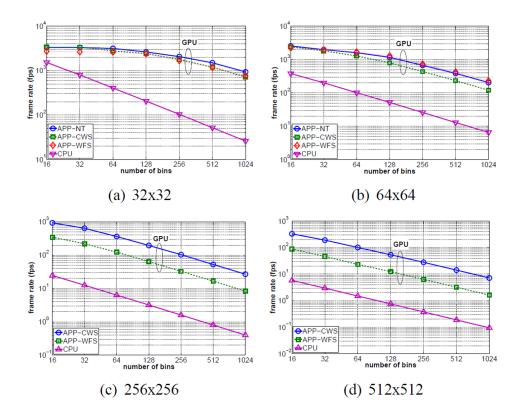

| 5.11 | Performance comparisons for different image sizes                                 | 87 |

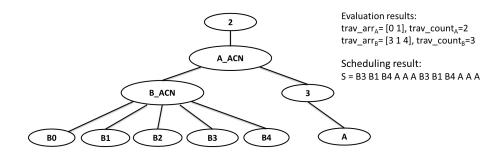

| 6.1 | An example of an SST                                                 |

|-----|----------------------------------------------------------------------|

| 6.2 | A dataflow graph representation of a turbo decoder 95                |

| 6.3 | TDL code for using TPs to specify turbo a decoder 101                |

| 6.4 | SST representation for a schedule of the targeted turbo decoder sub- |

|     | system                                                               |

#### 1 Introduction

Dataflow models are widely used for expressing the functionality of digital signal processing (DSP) applications, such as those associated with audio and video data stream processing, digital communications, and image processing (e.g., see [1]). Dataflow provides a formal mechanism for describing specifications of DSP applications, imposes minimal data-dependency constraints in specifications, and is effective in exposing and exploiting task or data level parallelism for achieving high performance implementations.

In recent years, a variety of computing architectures have been proposed for massively parallel processing (e.g., see [2, 3]). One of the most important classes of parallel computing platforms is the class of multicore processors. Such processors may use hundreds of lightweight cores to achieve application speedup. Graphics Processing Units (GPUs) form one major sub-class of multicore processors. GPUs provide large performance gains for certain types of regularly structured computations that have high degrees of parallelism (e.g., see [4, 5]). However, development of efficient implementations on GPUs requires careful attention to scheduling and resource mapping, and tedious fine tuning may also be required to extract performance gains.

When implementing a dataflow-based signal processing application model on a target platform, scheduling plays an important role (e.g., see [1]). Here, by *scheduling*, we refer to the process of determining which processing resource each actor executes on, and the ordering of execution among actors that share the same re-

source. By affecting key metrics that include performance, and memory usage, scheduling often has significant impact on implementation quality.

For efficient implementation on parallel platforms, it is useful for application developers to perform complex graph analysis, such as parallelism exploration and buffer size estimation, to map a platform-independent application graph into an efficient platform-specific realization. In the mapping process, parameters associated with the targeted parallel platforms, such as the degree of parallelism available for exploiting application components, are useful for scheduling of the applications. Here, by scheduling, we mean assigning application components (tasks) to processing resources and ordering the execution of the application components that share the same resources. The effective configuration of mapping parameters can be critical to optimizing performance. However, such parameter configuration often requires large amounts of human labor — e.g., to acquire profiling-related information for the application with respect to relevant platform properties.

In this thesis, we propose a systematic framework based on dataflow techniques to map signal processing applications onto parallel platforms. Our proposed framework is geared toward achieving optimized performance, and operates using platform-independent application graphs as its starting point. This use of platform-independent specifications helps to promote the retargetability of the proposed methods across different platforms, as well as the lasting utility across multiple generations of the same platform. Our mapping framework employs a form of dataflow modeling called *core functional parameterized synchronous dataflow* (*CF-PSDF*). In our work, CF-PSDF is applied to facilitate efficient scheduling techniques in dy-

namic systems, and to help optimize the exploitation of parallelism in the targeted platforms.

We also develop in this thesis a novel design method for hierarchical exploitation of parallelism in multi-dimensional signal processing applications. The method provides a formal linkage between hierarchical layers of parallelism in a targeted multicore platform and corresponding subsystems of the application. Scheduling can be optimized with the parallelism exposed from our proposed design method by using established techniques for DSP dataflow graph scheduling (e.g., see [1]). In addition, we also present innovative models for schedule representation. These models aid in the development of code generation techniques, as well as in the formal analysis and transformation of schedules to help meet design constraints.

#### 1.1 Core Functional Parameterized Synchronous Dataflow

Due to the increased complexity of dynamics in modern DSP applications, such as wireless communication systems based on LTE and WiMAX, designers need significant flexibility in the types of functional behaviors that they can efficiently specify and implement. To model complex dynamic DSP systems, a variety of dataflow approaches have been proposed (e.g., see [1]). Some of these can model arbitrary dynamic behaviors, but may lead to inefficient schedules. Others allow powerful scheduling and mapping techniques by restricting the range of dynamic applications that they can accommodate.

Core functional dataflow (CFDF), is a dynamic dataflow model that provides highly expressive semantics for the design of applications with structured dynamic behavior [6]. However, this flexibility, especially when high levels of data-dependent dynamics are present, may result in significant run-time scheduling overhead and reduced predictability in scheduling performance.

On the other hand, parameterized synchronous dataflow (PSDF) is a modeling technique that provides for systematic integration of dynamic parameter reconfiguration into synchronous dataflow representations [7]. Such an approach enables flexible parameterized modeling as well as strong support for quasi-static scheduling, which allows efficient and predictable scheduling performance for many kinds of dynamic applications. Here, by quasi-static scheduling, we mean scheduling techniques that fix a significant portion of schedule structure at compile time, while allowing flexibility for run-time adaptation of this statically-constructed structure based on characteristics of input data and operating conditions [8]. To provide support for powerful quasi-static scheduling techniques, expression of dynamics in PSDF is restricted — in particular, dynamic changes to actor and subsystem dataflow properties are disallowed for some kinds of modeling structures [7].

In this thesis, we develop a new dataflow modeling framework, which is based on careful integration of the CFDF and PSDF models. We refer to our proposed model as core functional parameterized synchronous dataflow (CF-PSDF). CF-PSDF provides useful trade-offs between dynamic modeling flexibility, and support for efficient quasi-static scheduling. By applying our proposed design methodology based on CF-PSDF modeling, designers can potentially enhance performance of dynamic

applications by employing efficient static and quasi-static scheduling techniques locally, and reducing the overhead associated with more general dynamic scheduling strategies. We demonstrate the utility of our proposed CF-PSDF based modeling and design techniques using an application case study involving multi-input, multi-output (MIMO) detection.

#### 1.2 Hierarchical Mapping Approach

Synchronous dataflow [9] has been popular in design of DSP applications because of its useful features, including compile-time, formal validation of deadlock-free operation and bounded buffer memory requirements, as well as support for efficient scheduling and buffer size optimization [1]. However, the SDF model is well suited only for one-dimensional DSP algorithms, such as those in the domains of speech, audio, and digital communication. Multidimensional synchronous dataflow (MDSDF) [10] is a generalization of SDF to multiple dimensions. MDSDF provides an effective model for a variety of multidimensional DSP systems that have statically structured dataflow characteristics.

In this work, we develop new methods for efficient implementation of parallel processing solutions for signal processing systems using MDSDF representations. Our proposed design methods apply dataflow transformations to exploit data parallelism hierarchically from multidimensional dataflow graphs. Our design methods provide a systematic approach for exposing and exploiting parallelism from multidimensional dataflow specifications across different levels of the specification hierarchy.

We demonstrate our proposed new modeling techniques and design methods by applying them to optimize implementations developed using the NVIDIA GPU programming environment [11]. Using our new MDSDF-based design techniques, we demonstrate efficient GPU implementations for integral histogram computations, which form an important class of image processing operations for surveillance and monitoring applications. The results of our experiments demonstrate concretely that our proposed design methods are effective in mapping formal design models for multidimensional DSP systems into efficient implementations on complex multicore processors.

## 1.3 Scheduling Representation

For dataflow models of large-scale DSP applications, the underlying graph representations often consist of smaller sub-structures that repeat multiple times. Topological patterns (TPs) have been shown to enable more concise representation and direct analysis of such substructures in the context of high level DSP specification languages and design tools [12]. Furthermore, by allowing designers to explicitly identify such repeating structures, use of TPs provides an efficient alternative to automated detection of such patterns, which entails costly searching in terms of graph-isomorphism and related forms of computation. A TP is inherently parameterized and provides a natural interface for parameterized scheduling, which enables efficient derivation of adaptive schedule structures that adjust symbolically in terms of design time or run-time variations. In [13], a formal design method is presented for specifying TPs, and deriving parameterized schedules from such patterns based on a schedule model called the scalable schedule tree (SST). The method ensures deterministic behavior of the system based on compile-time analysis of its behavior, where the behavior may be expressed in terms of parameterizable patterns of actor and edge instantiations. However, this method enforces certain forms of regularity in executing schedules, which restricts the class of schedule structures that can be expressed, and hence the flexibility with which the method can be applied to the mapping of dataflow graphs.

In this thesis, we introduce a more general traversal method, which allows designers and automated schedulers to programmatically construct solutions from within a broad class of execution sequences. This allows for design and representation of a correspondingly broader range of schedules through the common framework of SSTs. To demonstrate our enhanced SST model, we present a case study involving optimized implementation of turbo decoders, which are important and widely used in wireless communication applications.

## 1.4 Organization of the Thesis

The remainder of this thesis is organized as follows. Background relevant to the research presented in the thesis is discussed in Chapter 2. Chapter 3 presents the CF-PSDF modeling approach for dynamic signal processing applications. Our model for hierarchical representation of DSP flowgraph parallelism is introduced in Chapter 4 through Chapter 5. In Chapter 6, we present our generalized method for managing and traversing dataflow graph schedules. Conclusions and directions for future work are discussed in Chapter 7.

#### 2 Background

#### 2.1 Dataflow Modeling

In dataflow modeling, an application is represented using a directed graph G = (V, E), where V is a set of vertices and E is a set of edges [14]. In the form of dataflow that we employ in this thesis, each vertex (actor)  $v \in V$  represents a computation of arbitrary complexity, while each edge  $e = (v_1, v_2) \in E$  represents a first-in-first-out (FIFO) buffer that provides a logical communication link between actor  $v_1$  and actor  $v_2$ . In dataflow graphs, an actor can be executed (fired) whenever it has a sufficient number of data values (tokens) available on each of its input ports. In the topology of a dataflow graph, an actor with no input edges is called a source actor; an actor that has no output edges is called a sink actor.

A static schedule for a dataflow graph G = (V, E) is a sequence of actors in V that represents the order in which actors are fired during an execution of G. Each actor, when firing, consumes a certain number of tokens at each input port and produces a certain number of tokens at each output port. These numbers of tokens consumed or produced are referred to as dataflow rates of the associated dataflow actors or firings. Various types of dataflow models are formed based on the characterizations of the consumption and production rates of actors. For example, in synchronous dataow (SDF) [9], constant valued rates are used; in cyclo-static dataow (CSDF) [15], the rates are in the form of periodic patterns of constant values; in Boolean dataow (BDF) [16], data-dependent forms of rates are employed

for the support of modeling dynamic behaviors.

#### 2.2 Multidimensional Synchronous Dataflow

Synchronous Dataflow (SDF) [9] is a specialized form of dataflow that is used for an important class of DSP applications. In SDF, actors produce and consume data at fixed rates. Useful features of SDF include compile-time, formal validation of deadlock-free operation and bounded buffer memory requirements; support for efficient static scheduling; and buffer size optimization (e.g., see [1]).

However, SDF is ideally suited only for one-dimensional DSP algorithms. By expressing arrays in terms of 1-D streams, SDF modeling of multidimensional systems may hide potential data parallelism. Multidimensional synchronous dataflow (MDSDF) [10] generalizes SDF to multiple dimensions to provide an effective model for a variety of multidimensional DSP systems. In an MDSDF graph of dimension M, the number of tokens produced and consumed are given as M-tuples. For each edge, there are M balance equations, where the balance equations are used to determine the minimal numbers of actor firings required in each dimension to provide a periodic schedule (i.e., a schedule that can be executed iteratively, as many times as needed, with guaranteed bounded memory requirements for the dataflow graph edges) [10].

#### 2.3 Parameterized Synchronous Dataflow

Parameterized dataflow is a meta-modeling technique that can significantly

improve the expressive power of an arbitrary dataflow model that possesses a well-defined concept of a graph iteration [7]. Parameterized dataflow provides a method to systematically integrate dynamic parameter reconfiguration into such models of computation, while preserving many of the properties and intuitive characteristics of the original models. The integration of the parameterized dataflow meta-model with synchronous dataflow (SDF) provides the model of computation referred to as parameterized synchronous dataflow (PSDF). PSDF offers valuable properties in terms of modeling systems with dynamic parameters, supporting efficient scheduling techniques, and natural integration with popular SDF modeling techniques [7].

A PSDF specification (subsystem) is composed of three cooperating PSDF graphs, the *init*, *subinit*, and *body* graphs of the specification. The init graph is designed to configure the corresponding subinit and body graphs while the subinit graph can only change parameters in the body graph. The body graph, when executed, performs the main functionality of the subsystem based on the updated set of parameters. For more details on PSDF modeling, we refer the reader to [7].

#### 2.4 Core Functional Dataflow

Core functional dataflow (CFDF) is a dynamic dataflow model that provides highly expressive semantics for the design of applications with structured dynamic behavior [17]. In CFDF, an actor is specified as a set of operational modes. In each mode, an actor consumes and produces fixed numbers of tokens on its input and output ports, respectively. These numbers of tokens consumed and produced

are called the consumption and production *rates* of the associated input and output ports, respectively, and the associated modes. Consumption and production rates for CFDF actor modes can be arbitrary non-negative integers.

During execution, a CFDF actor operates in a unique current mode of the actor, which can be maintained as part of the actor state. Each actor has an associated enable function, which can be called by a run-time scheduler. The enable function returns a Boolean value indicating whether or not there is sufficient data available on the actor input ports to fire the actor in its current mode. The invoke function of an actor consumes data for execution based on the associated current mode. When an actor is invoked, it executes its current mode, produces and consumes data, and updates its current mode (i.e., sets the mode to be used in its next firing).

The enable function need not always be called before invoking an actor — in particular, it need not be called if static analysis of the graph can determine that the required data for the given actor mode will be available at the desired point of invocation. On the other hand, dynamic or quasi-static scheduling techniques may make use of the enable function to help ensure data availability in the absence of static guarantees [17].

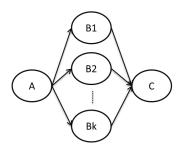

#### 2.5 Topological Patterns

For large-scale models of signal processing applications, the underlying dataflow graph representations often consist of smaller substructures that repeat multiple times. A method for scalable representation of dataflow graphs using topological patterns was introduced in [12]. Topological patterns, such as the ring, butterfly, and chain patterns, are pervasive in signal processing applications, including multi-dimensional signal processing systems, where processing of large scale dataflow structures is common. Topological patterns enable concise representation and direct analysis of sub-structures in the context of high level DSP specification languages and design tools. Modeling based on topological patterns also provides a scalable approach to specifying regular functional structures that is formally integrated with the framework of dataflow. This integration allows not only for specification of functional patterns, but also for their analysis and optimization as part of the larger framework of dataflow. For more details on modeling and design based on topological patterns, we refer the reader to [12].

#### 2.6 Generalized Schedule Trees

The generalized schedule tree (GST) is a compact, tree-structured graphical format that can represent a variety of dataflow graph schedules [18]. In GSTs, each leaf node refers to an actor invocation, and each internal node n (called a loop node) is configured with an iteration count  $I_n$  for the associated sub-tree, where execution of the sub-tree rooted at n is repeated  $I_n$  times. The GST has been demonstrated to represent looped schedules for dataflow graphs effectively in the context of static, non-scalable schedules (e.g., see [18]).

#### 2.7 General Purpose Graphics Processing Units

In recent years, graphics processing units (GPUs) have become increasingly popular in general-purpose computing applications due to their useful features, such as flexible programmability, tremendous computational ability, high memory bandwidth, and large amounts of parallelism [5, 4]. Compared to conventional microprocessors, GPUs are designed such that more hardware resources (transistors) are dedicated to data processing and less are dedicated to data caching and flow control. The result is that GPUs are effective on computations that involve large amounts of data-parallel computing and relatively small amounts of control flow. Significant levels of acceleration from GPUs have been demonstrated in many fields, such as physics, computer vision, signal processing, and wireless communications (e.g., see [19, 20, 21, 22]). Currently, parallel computing on GPUs is supported in a variety of programming models, including CUDA [23], OpenCL [24], and OpenACC [25]. In this thesis, we employ CUDA as the back-end environment for our GPU-targeted design methods.

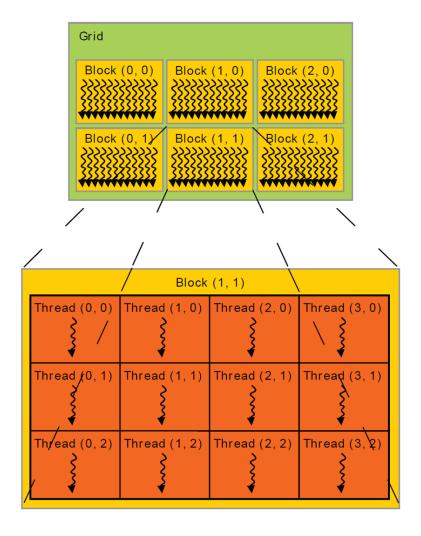

CUDA (Compute Unified Device Architecture) is a software programming model for NVIDIA GPUs. In CUDA, a computational unit is wrapped in a ker-nel function, which, when invoked, is executed N times in parallel by N CUDA threads in a structure called a grid. The CUDA programming model features multidimensional and multi-level thread hierarchies. Threads are organized into multidimensional (up to three dimensions are supported) thread blocks, and multiple

thread blocks are combined together to form grids, as shown in Figure 2.1. As with

Figure 2.1: An example of thread hierarchy in CUDA.

thread blocks, up to three dimensions are supported for the construction of grids in CUDA.

#### 3 CF-PSDF Modeling and Scheduling

In this section, we address challenges pertaining to modeling and scheduling of dynamic signal processing applications. Here, by dynamic signal processing applications, we mean applications in which the underlying dataflow graphs contain actors whose characteristics, such as production and consumption rates and execution times, can exhibit significant run-time variation [26]. Development of efficient scheduling techniques for dynamic signal processing applications is challenging because of the limited information that is available at compile time about actor characteristics, and because of the potential performance overhead and decreased predictability involved in making significant scheduling decisions at run-time.

In this chapter, we address these challenges for a specific class of dynamic signal processing applications. In the targeted application class, actors that exhibit significant dynamics are controlled by common sources that control the actor dynamics at run-time. These *control sources* can be viewed as specific actors whose outputs are used to control the behavior of other actors. We present a new dynamic dataflow model that groups dynamic actors based on their control sources to enable efficient static and quasi-static scheduling approaches for the associated actor groups (subsystems).

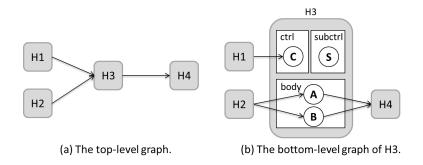

In this chapter, we present an application modeling approach called *core func*tional parameterized synchronous dataflow (CF-PSDF), which integrates the CFDF and PSDF models. In CF-PSDF, an application is represented with a two-level hierarchy, as illustrated in Figure 3.1. In the top level (e.g., Figure 3.1(a)), each node is a CF-PSDF actor (with *enable* and *invoke* functions as a CFDF actor) to model data dependent dynamic behaviors that may change dataflow. The bottom level (e.g., Figure 3.1(b)) is composed of three subgraphs (as in PSDF) to provide flexible dynamic parameter reconfiguration.

This chapter is based on work presented in [27].

#### 3.1 CF-PSDF Model

In CF-PSDF, a DSP application is modeled through a CF-PSDF specification, which is also called a CF-PSDF subsystem. A hierarchical actor that encapsulates a CF-PSDF subsystem S (i.e., for instantiation in a higher level subsystem) is called the CF-PSDF actor associated with subsystem S. A CF-PSDF actor H can be viewed at its interface as a CFDF actor that has a set of modes, and enable and invoke functions, which are fundamental components of the CFDF model [6]. When H is executed in a given mode, a fixed number of tokens is consumed and produced at the input and output ports of H, respectively. Across different modes of H, however, the production and consumption rates at the ports of H can vary.

In a CF-PSDF actor H, the encapsulated specification, which we denote by  $\sigma(H)$ , is decomposed into three cooperating graphs, which we refer to as the  $\operatorname{ctrl}(\phi_c)$ ,  $\operatorname{subctrl}(\phi_s)$ , and  $\operatorname{body}(\phi_b)$  graphs of  $\sigma(H)$  (here, "ctrl" is used as an abbreviation for "control"). The actor H3 in Figure 3.1(b) shows an example of a CF-PSDF actor.

As in PSDF modeling, the body graph of a CF-PSDF specification is intended for use in modeling the core functional behavior of the associated subsystem, while

Figure 3.1: An example of a CF-PSDF graph.

the ctrl and subctrl graphs, which are analogous in some ways to the init and subinit graphs of PSDF, control the dynamic behavior of the body graph. This dynamic body graph control is achieved by appropriately configuring selected body graph parameters. As in PSDF, the subctrl graph of a CF-PSDF specification  $\sigma(H)$  can configure the parameters in the associated body graph in ways that do not change the production and consumption rates at the interfaces (ports) of H.

The ctrl graph of a CF-PSDF subsystem  $\sigma(H)$  is executed once during each firing of H and is allowed to update parameters in the associated subctrl and body graphs. Such parameter configurations may depend on parameters of the enclosing system as well as on run-time data generated from other CF-PSDF actors (i.e., data-dependent parameter updates).

On specific parameter that is configured in the ctrl graph of  $\sigma(H)$  is a special parameter  $\mu(H)$  that controls the execution mode of H. The ctrl graph is the basic mechanism in CF-PSDF for determining this execution mode. After the ctrl graph of  $\sigma(H)$  executes and  $\mu(H)$  is updated, the production and consumption rates at the interfaces of H are fixed until the next execution of the ctrl graph. Furthermore, the

control information processed in the ctrl graph of  $\sigma(H)$  can be shared by "exporting" tokens (through dedicated dataflow graph edges) to ctrl graphs in other CF-PSDF actors within the enclosing application model. This mechanism of "sharing" control information, which represents a departure from the parameterized dataflow metamodel, can facilitate local scheduling and mapping optimization, and help avoid repetitive computation of control information. Additionally, the ctrl graph can process data from input ports of  $\sigma(H)$  and produce data onto the output ports of  $\sigma(H)$ . This is more flexible compared to the init graph of PSDF, where such linkages to the ports of the enclosing PSDF actor are not allowed.

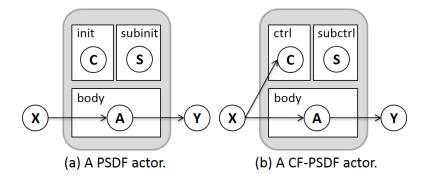

The modeling flexibility of CF-PSDF compared to PSDF is illustrated in Figure 3.2. In the PSDF subsystem shown in Figure 3.2, the production rate of actor A is independent of the output of actor X. However, in some applications it can be useful to model behaviors where the production rate of actor A in this kind of a subsystem structure is dependent on the output of actor X. This kind of data-dependent dynamics, which is not expressed in the more predictable, PSDF-style specification of Figure 3.2, can be useful to model precisely when developing DSP applications. For example, in wireless communications, a turbo decoder with a dynamic iteration count may or may not execute one more iteration according to the run-time output of the current iteration [22]. Another example of this kind of dataflow dynamics is discussed in Section 3.5.

On the other hand, in CF-PSDF, designers can pass control tokens from actor X to the ctrl graph of a CF-PSDF subsystem, as shown in Figure 3.2(b). Then, the ctrl graph can configure the dataflow (production and consumption) rates of A

Figure 3.2: Examples of PSDF and CF-PSDF actors.

through the CF-PSDF mechanism of parameter reconfiguration based on subsystem input tokens (input tokens arriving from actor X in this case). A disadvantage in supporting this kind of dynamics is that the efficient quasi-static scheduling techniques that have been developed for PSDF models (e.g., see [7]) are in general not applicable to CF-PSDF specifications. However, in Section 3.4, we develop new scheduling techniques that exploit the structure of CF-PSDF models, and permit derivation of efficient schedules from such models.

#### 3.2 Multi-Mode Actors

In this section, we develop scheduling techniques for mapping CF-PSDF graphs into efficient implementations.

The hierarchical, mode-oriented structure of CF-PSDF modeling allows designers to specify complex applications with more concise graphs representations, where related functionality can be grouped together naturally under common actors or subsystems. For example, a P-QAM mapper, which maps blocks of  $log_2P$  input bits to P-QAM symbols, consumes P tokens (bits) and produces one token (QAM

symbol). An SDF representation of this functionality would typically require three separate actors for 4-QAM, 16-QAM, and 64-QAM processing, while this entire functionality can be encapsulated within a single, multi-mode CFDF actor. However, in a CFDF graph, additional control modes may be needed to provide for correct transitioning between operational states (e.g., see [6]), which may increase design effort and introduce scheduling overhead. In CF-PSDF, we alleviate these problems by applying a central control mechanism, through ctrl and subctrl graph execution, and a modeling approach based on designer-specified sets of practical mode combinations (functional modes) across body graph actors. This concept of functional modes is discussed next, in Section 3.3.

#### 3.3 Subsystem Modes

In CF-PSDF, it is not possible for one body graph actor to have direct control over the dataflow rates of another actor in the same body graph. For example, in the graph of Figure 3.1(b), the dataflow rates of actors A and B can be varied based on output from H1, but the dataflow rates of A are prohibited from depending on outputs of B, and vice versa. This condition ensures that the mode transitions of all actors in a body graph  $\phi_b$  can be configured centrally from the ctrl graph based on system parameters and run-time data. This centralized, ctrl-graph based control of actor modes can help to eliminate certain local (actor-level) modes and transitions that are employed in pure CFDF models to ensure proper transitioning between processing states.

Each CF-PSDF actor (subsystem) H has a special mode called the *control* mode of H, which is used to execute the ctrl graph of H, and update parameters, including the next mode parameter  $\mu(H)$ . The control mode can in general consume and produce data at the interface ports of H, as described previously.

Apart from the control mode, a CF-PSDF actor H may have any number of additional modes, which are referred to as the functional modes of H. Execution of H proceeds based on alternating sequences of the control mode and a functional mode (i.e., between each pair of successive functional mode executions, there is exactly one execution of the control mode). Each functional mode of H corresponds to a unique set of modes for all actors that are contained in the associated body graph,  $\phi_b$ . That is, for each functional mode m of H and each actor  $\alpha$  in  $\phi_b$ , there is a unique mode  $z(m,\alpha)$  of  $\alpha$  that governs the execution state of  $\alpha$  whenever H executes in functional mode m. Thus, in each functional mode m,  $\phi_b$  can be viewed an SDF graph  $G_{sdf}(m)$ , which can be analyzed and scheduled by leveraging the large body of existing techniques for SDF (e.g., see [1]).

Note that in CF-PSDF, the set F(H) of functional modes of H is defined explicitly by the designer. An alternative approach would be to derive F(H) by enumerating all possible mode combinations across the actors within  $\phi_b$ . However, this approach is clearly not scalable since, for example, there is no polynomial bound on such mode combinations.

Indeed, in practical DSP applications, many mode combinations may be uninteresting (e.g., redundant or simply not useful). In Figure 3.1(b), for example, suppose that actors A and B are both P-QAM mappers with three modes each for

P=4, 16, and 64. The set of all mode combinations for H3 contains  $3\times 3=9$  combinations. However, at any given time during actual execution of the system, the values of P will be identical for both A and B — only three mode combinations are relevant in the design of H3. Thus, H3 is designed such that F(H3) contains only three modes.

In previous work, methods have been developed to detect and eliminate unreachable mode combinations in CFDF graphs [6]. However, in practical scenarios, such as the example of Figure 3.1(b), it can be difficult to detect all unused modes without designer guidance. Automated techniques, such as those developed in [6], can be used in a complementary fashion to the designer-specified approach in CF-PSDF (e.g., to remove unused modes from the specified functional mode set). Integrating such automation into the CF-PSDF framework is an interesting direction for future work.

## 3.4 Scheduling Techniques

In CF-PSDF, dynamically parameterized and dynamic dataflow subsystems are represented with two-level hierarchies, as illustrated in Figure 3.1. In the top level (e.g., Figure 3.1(a)), each actor is a CF-PSDF actor with associated enable and invoke functions, which have similar roles as in the pure CFDF model. The lower level of the subsystem design hierarchy (e.g., Figure 3.1(b)) is composed of three subgraphs to provide flexible dynamic parameter reconfiguration. This structured decomposition into three subgraphs is based on a similar kind of decomposition

provided in PSDF, but with significant adaptations to make the modeling approach more flexible and more coupled to CFDF design techniques.

CF-PSDF provides a natural framework for quasi-static scheduling based on the decomposition of a CF-PSDF subsystem H in terms of it functional modes F(H)and the associated set of SDF graphs

$$S(H) = \{G_{sdf}(m) \mid m \in F(H)\}$$

(3.1)

that characterizes the body graph  $\phi_b$ . Each graph  $\{R \in S(H)\}$  can be scheduled using SDF techniques, and based on specific operational constraints (e.g., constraints on throughput, latency, or buffer memory requirements) that are associated with the corresponding functional mode of H. The resulting set of SDF schedules  $S(R) \mid R \in S(H)$  can then be integrated in a quasi-static, dynamic control-driven manner using CFDF techniques for scheduling H as a component within its enclosing subsystem or application graph model.

For example, for the dataflow graph  $G_{outer}$  that contains H, one can readily apply a CFDF canonical schedule, which is a standard type of schedule for CFDF graphs that can be constructed quickly and is suitable for rapid prototyping and bottleneck identification [6]. Alternatively, existing techniques for CFDF schedule optimization (e.g., see [6]) can be applied to  $G_{outer}$  to help improve system performance or satisfy operational constraints.

#### 3.5 Case Study: MIMO Detection

We demonstrate the utility of CF-PSDF-based implementation with a case study of soft multiple-input, multiple output (MIMO) detection.

## 3.5.1 Application Model based on CF-PSDF

MIMO technology has been adopted in many modern wireless communication standards, such as LTE and WiMAX, due to the significant capacity increases that can be achieved by using multiple antennas in transmitters and receivers [28]. In this case study, we implement an application of  $M \times M$  MIMO detection with a P-QAM constellation. We apply an efficient soft MIMO detection algorithm called the list fixed-complexity sphere decoder (LFSD), which is a list-based version of the fixed-complexity sphere decoder (FSD) [29]. The LFSD generates a list of candidates around the maximum likelihood (ML) solution that can be used to calculate soft-output information for each transmitted bit  $b_k$  in the form of log-likelihoods (LLRs),  $\{L_k\}$ .

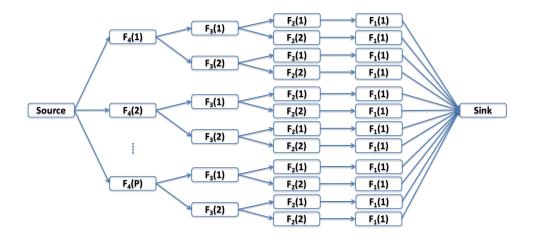

An  $M \times M$  MIMO system is commonly decomposed into M processing layers (in our experiments, we use M=4). In our design, the vector-valued parameter  $\lambda$ , consisting of M-elements, specifies the number of optimal detected results that are generated at each layer. If  $\lambda = (n_1, n_2, \dots, n_M)$ , then the list size can be expressed as  $N_L = \prod_{i=1}^M n_i$ .

In our implementation, the soft MIMO detector takes the received symbol vector y and the channel matrix C as inputs, finds the  $N_L$  candidates for each y and

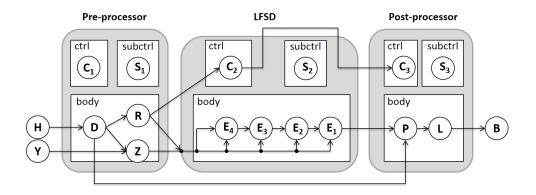

Figure 3.3: CF-PSDF model of soft MIMO detection application.

C, and generates the soft information  $L_k$ . We model the application with our proposed CF-PSDF framework, as illustrated in Figure 3.3. Here, the dataflow graph is composed of three CF-PSDF actors (Pre-processor, LFSD, and Post-processor), two source actors Y (source of y) and H (source of C), and one sink actor B (sink of  $L_k$ ). The soft MIMO detector is divided into three parts: (1) the preprocessing component (Pre-processor actor), which applies QR decomposition on the channel and least squares estimation of the input symbols; (2) the LFSD component (LFSD actor), which generates a list of candidates according to the FSD algorithm; and (3) the postprocessing component (Post-processor actor), which computes the LLRs with the list generated by the LFSD component. On the subsystem corresponding to each CF-PSDF actor, the quasi-static scheduling technique developed in [7] is applied.

In our implementation, the list size  $N_L$  is determined dynamically for each realization (i.e., for each y and C) based on the channel quality. Usually, a large value for  $N_L$  improves the bit error rate (BER), but at the cost of increased complexity. In our design, a realization with better channel quality is processed with a smaller list to reduce computational complexity. On the other hand, a large list is used for realizations in poor channel states to improve the detection accuracy. We consider three different settings of  $\lambda$  in our MIMO system implementation: (1, 1, 1, P), (1, 1, 2, P), and (1, 2, 2, P). These settings result in  $N_L = P$ ,  $N_L = 2P$ , and  $N_L = 4P$ , respectively.

In our CF-PSDF-based design, the LFSD actor includes three modes, MODE-P, MODE-2P, and MODE-4P to output  $N_L=P$ ,  $N_L=2P$ , and  $N_L=4P$  tokens (candidates), respectively. The associated control actor C2 of the LFSD actor, when fired, computes the channel quality (instantaneous channel capacity of C, denoted  $\rho_C$ ) with the input data exported from the Pre-processor actor, and then configures the subsystem mode parameter  $\mu$  (i.e., selects a list size) based on the current channel quality indicator  $\rho_C$ . In the cases of  $\rho_C > \rho_{TH1}$  ("good quality") and  $\rho_C < \rho_{TH2}$  ("bad quality"), MODE-P and MODE-4P are selected, respectively, while in all other cases, the mode is set to MODE-2P. Here,  $\rho_{TH1}$  and  $\rho_{TH2}$  are two system parameters that determine the thresholds to use for determining good and bad channel quality, as described above.

The designer-provided specification of functional modes in CF-PSDF provides significant streamlining in the space of mode combinations that need to be handled during the implementation process. The body graph of the LFSD actor contains four actors —  $E_1$ ,  $E_2$ ,  $E_3$ , and  $E_4$  — which, respectively represent the FSD processing elements for layers 1 through 4. Each  $E_i$  has four operational modes — a LOAD mode for reading input tokens, and three processing modes, denoted M-1, M-2, and M-P, to process data for  $n_i = 1$ ,  $n_i = 2$ , and  $n_i = P$ , respectively. The total number of actor

mode combinations in the body graph is therefore  $4^4 = 256$ . However, it is easy for the designer to understand and specify that only three of these combinations, which correspond to MODE-P, MODE-2P, and MODE-4P of the LFSD subsystem, are relevant. Thus, including the required control mode, the total number of operational modes for the LFSD subsystem is reduced from 256 to only 4 using the CF-PSDF convention of designer-specified functional modes.

### 3.5.2 Experimental Results

Our experiments on this MIMO detector case study are performed on a PC with an Intel 3GHz CPU and 4GB RAM. First, we compare the performance of the detector modeled in pure CFDF and CF-PSDF for a 4 × 4 MIMO system with QPSK, 16-QAM, or 64-QAM modulation. In the experiments, both implementations apply the canonical CFDF scheduler [6]; however, for the CF-PSDF-based implementation, the results of this scheduler are integrated with SDF schedules for individual functional modes, as described in Section 3.4.

Table 1 lists experimental results for this comparison. From the results, we see that compared to CFDF, CF-PSDF modeling can significantly reduce the number of average visited actors per realization (shown in the row labeled *Visited node count*). Here, by a "visit", we mean a basic dataflow scheduling operation that involves assessing whether an actor has sufficient input data, firing the actor if it has sufficient data, or both. This reduction in visited node count, which can be viewed as a reduction in schedule execution overhead, arises because of the novel

Table 1: Performance comparison between CFDF- and CF-PSDF-based implemen-

tations. Run time is in microseconds.

| Modulation         | 4-QAM |       | 16-QAM |       | 64-QAM |       |

|--------------------|-------|-------|--------|-------|--------|-------|

| Dataflow model     | CF    | CF-PS | CF     | CF-PS | CF     | CF-PS |

| Visited node count | 272.6 | 68.7  | 1012   | 151.9 | 3972   | 484.4 |

| Improvement        | 74.8% |       | 85.0%  |       | 87.8%  |       |

| Run time           | 0.11  | 0.10  | 0.19   | 0.15  | 0.50   | 0.33  |

| Gain               | 9.1%  |       | 21.1%  |       | 34.0%  |       |

support in CF-PSDF for efficient quasi-static scheduling (i.e., in terms of local SDF schedules for individual functional modes). The overall performance of the CF-PSDF implementation is correspondingly improved as well. As we see from the row labeled "Run time", the average execution time is improved by 9.1%, 21.1%, and 34.0%, respectively, for QPSK, 16-QAM, and 64-QAM.

As P increases, the run time improves more since in CFDF, more non-firing node visits occur while in CF-PSDF, such overhead is avoided through efficient quasi-static scheduling.

Next, we compare the performance of our dynamic MIMO detector against a conventional static detector with a fixed list size  $N_L = 4P$  for a 64-QAM 4x4 MIMO system (i.e., P = 64). To evaluate the coded BER performance, we feed the soft output of the detectors to a length 3600, rate 1/2 turbo decoder with eight iterations [30]. Our experimental results show that to achieve the target BER

Table 2: Experimental comparison between the SS and DS. Run time is in microseconds.

| SNR (dB)           | 19.0  | 19.5  | 20.0  | 20.5  | 21.0  |

|--------------------|-------|-------|-------|-------|-------|

| Run time (static)  | 0.425 | 0.425 | 0.424 | 0.426 | 0.425 |

| Run time (dynamic) | 0.370 | 0.353 | 0.339 | 0.327 | 0.318 |

| Gain               | 12.9% | 16.9% | 20.0% | 23.2% | 25.2% |

(assume 10<sup>-4</sup>), the static system (SS) and dynamic systems (DS) require at least 19.84dB and 19.90dB signal to noise power ratio (SNR), respectively. In exchange for this small (0.06dB) degradation, the DS provides a significant improvement in run time (RT), as shown in Table 2. As expected, the RT of the SS at various SNRs is almost uniform. By contrast, the RT for the DS improves as SNR increases. This is because higher SNR provides more opportunities for use of smaller list sizes, which results in lower computational cost.

#### 3.6 Related Work

In addition to CFDF and PSDF, there is a variety of other models that support dynamic dataflow modeling, design, and implementation. Wiggers, Bekooij, and Smit [31] present variable rate dataflow (VRDF) to model systems with data-dependent communication, and develop techniques to compute buffer sizes for VRDF specifications for given throughput constraints. Eker et al. [32] present a hierarchical approach for modeling of heterogeneous embedded systems, including systems

that incorporate dataflow behaviors. In this approach, designers employ modeling constructs called *directors* to control the communication and execution schedules for associated application subsystems. The *stream-based functions* (SBF) model of computation combines the semantics of dataflow and process network models for design and implementation of embedded signal processing systems [33]. An actor in SBF contains a set of operational functions, along with a controller, state, and a transition function. The use of operational functions and the transition function in SBF is analogous in some ways to the modes and next mode determination functionality in the CFDF model. Given this relationship, an interesting direction for further study is the adaptation of the techniques introduced in this thesis to SBF specifications (i.e., an integrated SBF-PSDF modeling framework).

The dataflow-based modeling and design techniques presented in this chapter differ from the related work discussed above in that our framework generalizes the CFDF and PSDF models to provide systematic, mode-based, dynamic modeling together with flexible dynamic parameter reconfiguration. Our emphasis on support for localized use of optimized static and quasi-static schedules further distinguishes our contribution in this chapter from related work in this area.

Furthermore, the CF-PSDF modeling approach proposed in this chapter can potentially reduce scheduling overhead and also provide opportunities for powerful dataflow analysis and transformation techniques. We discuss these advantages further in Chapter 4.

## 4 Hierarchical Mapping for Parallel Architectures

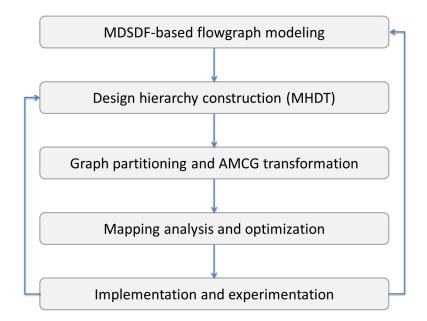

In this chapter, we present a structured design method based on MDSDF graphs for hierarchical mapping of DSP systems onto parallel architectures. Material in this chapter was published in partial, preliminary form in [34] and [35]. In various forms of data parallel programming, programmers can define functions, and have multiple calls to the functions execute in parallel on different data sets (e.g., see [11, 24]). Recent data parallel programming environments emphasize support for exploiting multi-level or hierarchical parallelism, where parallelism is exploited programmatically at multiple levels of granularity. For example, CUDA [11] provides a two-level thread hierarchy, where a set of threads makes up a thread block, and multiple thread blocks form a grid.

Such hierarchical support for representing parallelism is important for multidimensional signal processing applications, where parallelism exists in different forms at different levels of the design hierarchy (DH) (e.g., inter-frame, inter-block, and inter-pixel parallelism in video processing). In this chapter, we build on the MDSDF and CF-PSDF models of computation, and develop a design method to represent and apply parallelism hierarchically for multidimensional dataflow graphs. We refer to the proposed method as the parameterized multidimensional design-hierarchy mapping (PMDHM) framework.

Currently, the class of directed acyclic graphs (DAGs), i.e., directed graphs with no directed cycles [36], is targeted in this work. In other words, we assume that application dataflow graphs that are provided as input to the PMDHM framework

are DAGs. A large class of useful signal processing applications conforms to the structure of DAGs. The extension of the PMDHM framework to handle classes of graph structures that include cycles is a useful topic for further investigation.

#### 4.1 PMDHM Framework

In this section, we present our proposed PMDHM framework for dataflowbased design, which is targeted to the flexible, multi-level reconfigurability, and intensive real-time processing requirements of emerging dynamic signal processing systems.

A CF-PSDF specification is composed of three cooperating CF-PSDF graphs, the *ctrl*, *subctrl*, and *body* graphs of the specification. Actors and edges in CF-PSDF graphs can be annotated with arbitrary parameters, which can be changed at runtime. Such actors and edges correspond, respectively, to functional components and intra-component connections in signal processing flowgraphs (see Chapter 3).

The ctrl graph of a CF-PSDF subsystem  $\sigma(H)$  is executed once during each firing of H and is allowed to perform data-dependent parameter updates in the associated subctrl and body graphs as presented in Chapter 3. The subctrl graph of  $\sigma(H)$  can configure the parameters in the associated body graph in ways that do not change the dataflow rates at the interfaces of H.

For selected subsystems in a CF-PSDF-based system design, a new design transformation called the *multi-level hierarchical dataflow transformation (MHDT)* can be employed to efficiently map the subsystem to a given target platform that

employs parallelism at multiple levels of platform architecture. Designers can thus select subsystems that have critical constraints (e.g., on performance, energy efficiency or resource utilization) for application of the MHDT.

For each alternative body graph that results from different sets of parameter configurations (e.g., application or subsystem modes) in the ctrl graph, the MHDT approach transforms an application graph with parameterized production and consumption rates (i.e., dataflow rates that are represented as functions of system parameters) into a hierarchical organization of graphs such that the structure of the hierarchy helps the designer to map the design onto the hierarchical parallel structures in the target platform.

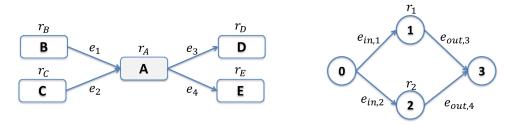

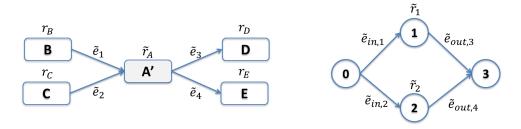

#### 4.1.1 Multi-level Hierarchical Dataflow Transformation

Let G = (V, E) denote an MDSDF graph where  $V = \{v_1, v_2, \dots, v_L\}$  is a set of vertices (actors), and  $E = \{e_1, e_2, \dots, e_K\}$  is a set of directed edges, which represent communication between actors according to MDSDF semantics. In MDSDF graphs, actor firings are indexed (in their associated "firing spaces") by n-dimensional vectors, where the values of n depend on the dimensions of the data that are produced and consumed  $(n = 1 \text{ corresponds to conventional single-dimensional, SDF-like firing sequences) [10].$

Suppose that v is an MDSDF actor with a firing space of M dimensions, and let  $r_{v,i}$ , for i = 1, 2, ..., M, denote the size of the ith dimension of the firing space for v in a given periodic schedule S for G. A periodic schedule is a sequence of

Figure 4.1: An example of a three-actor MDSDF graph.

actor firings that executes each actor at least once and produces no net change in the numbers of tokens queued on the edges of G [9, 10]. We refer to the M-vector  $r_v = [r_{v,1}, r_{v,2}, ..., r_{v,M}]$  as the firing vector for actor v associated with S. The product of the M elements of this vector gives the total number of firings of v within S. For a properly constructed MDSDF graph,  $r_v$  can be computed by solving a system of equations called the balance equations for the graph [10].

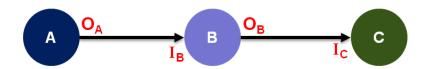

Consider, for example, the 3-node graph illustrated in Figure 4.1. The firing vectors  $r_A$ ,  $r_B$ , and  $r_C$  can be found by solving the following balance equations for i = 1, 2, ..., M:

$$r_{A,i}O_{A,i} = r_{B,i}I_{B,i}, \quad r_{B,i}O_{B,i} = r_{C,i}I_{C,i},$$

(4.1)

where  $I_X = [I_{X,1}, I_{X,2}, \dots, I_{X,M}]$  and  $O_X = [O_{X,1}, O_{X,2}, \dots, O_{X,M}]$  are the *M*-dimensional consumption and production rates, respectively, for actor *X*.

Now suppose that we have an N-level hierarchical parallel programming model (platform hierarchy) P, which we want to use to implement a given MDSDF graph G. For example, such a parallel programming model could be used as a target for code generation or could be used for an implementation that is derived from hand based on a functional reference ("golden model") that is based on the MDSDF specification. We develop an N-level hierarchical dataflow graph transformation approach to achieve such a mapping from an MDSDF-based application graph to

#### P. We refer to N in this context as the platform depth.

First, we introduce some definitions and notation related to hierarchical dataflow graphs. For a dataflow graph G = (V, E), let  $P_i(V)$  and  $P_o(V)$  be the sets of input and output ports of all actors in V, respectively. A supernode s in G is an actor (i.e.,  $s \in V$ ) that is associated with a "nested dataflow graph" H(s), where execution of s in G corresponds to execution of H(s). In general, not all actor ports in H(s) are connected in H(s) (i.e., not all of them connect to edges within H(s)). The "unconnected actor ports" are referred to as the interface ports of H(s), and these ports are in one-to-one correspondence with ports of actor s.

If G is the "top" of the design hierarchy (i.e., G is not encapsulated by a supernode in another graph), then we say that the *nesting level* (or simply *level*) of G, denoted  $\lambda(G)$ , is 1. Similarly, for each supernode s in G,  $\lambda(H(s)) = 2$ ; for each supernode t in any of these H(s)'s,  $\lambda(H(t)) = 3$ , and so on.

The design hierarchies in our model are non-overlapping, which means that for all supernodes within a design hierarchy (i.e., across all levels), their corresponding nested dataflow graphs do not share any actors or edges. Furthermore, we assume that these design hierarchies are finite, which means that the levels ( $\lambda$  values) are all bounded.

We refer to the maximum  $\lambda$  value in a design hierarchy D as the depth  $\delta$  of D. For each  $i \in \{1, 2, ..., \delta\}$ , we denote by  $L_i$  the set of all actors that are "at level i". That is,  $L_1 = V$ , and for  $i = 2, 3, ..., \delta$ ,

$$L_i = \bigcup \{V_h(s) | \lambda(H(s)) = i\}, \tag{4.2}$$

where  $V_h(s)$  denotes the set of actors in the nested dataflow graph H(s).

Design hierarchies in our decomposition approach can be constructed by designers as they explore alternative methods to structure the hierarchies such that they map efficiently into the parallelism hierarchy supported by the targeted platform. The key constraint in the construction of a design hierarchy D is that the depth of each candidate design hierarchy should equal the platform depth. In Section 5.1 and 5.2, we illustrate how a design hierarchy can be constructed naturally from understanding of the flowgraph structure of an application. However, design hierarchies can also be targeted by automated tools. Exploration of such automated design hierarchy construction tools is a useful topic for future work.

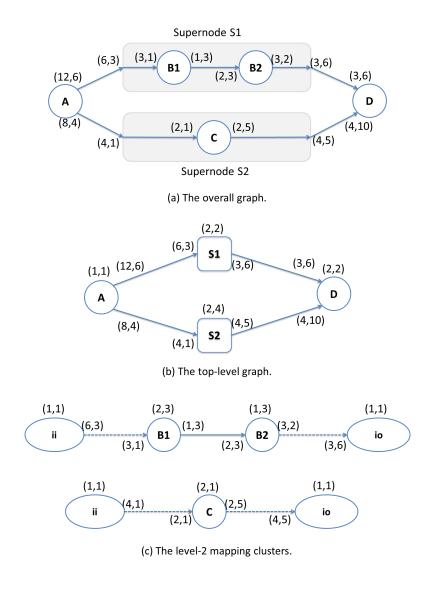

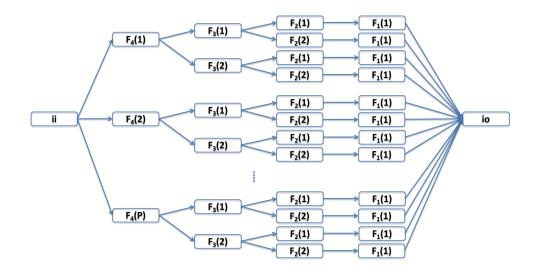

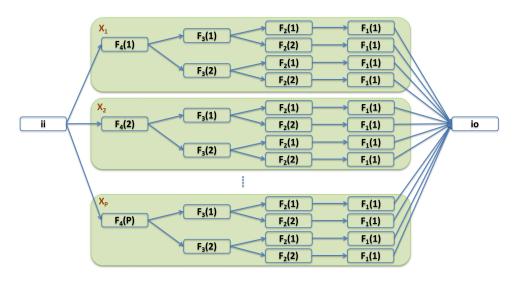

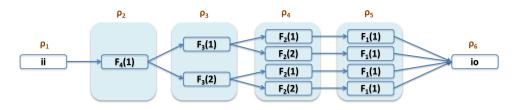

We have developed a systematic method, called the multi-level hierarchical dataflow transformation (MHDT), to specify and map design hierarchies into hierarchies of smaller graphs, which can in turn be mapped to successively lower levels of the targeted platform hierarchy. Figure 4.2 illustrates this approach for an MDSDF graph. The designer can construct the design hierarchies in a bottom-up or top-down fashion. At each ith level (i > 1) of the design hierarchy, one or more groups (clusters) of connected actors are combined into units that are viewed as individual supernodes from level (i - 1). Groups of actors, including supernodes, that are contained within such clusters are then scheduled together by adapting techniques for SDF- and MDSDF-based clustered graph analysis and scheduling [37, 10].

When applying the MHDT, each supernode s at each level i is transformed into a corresponding "standalone" dataflow graph, which is referred to as a mapping cluster. The transformation of a supernode into a mapping cluster is performed

through the following process.

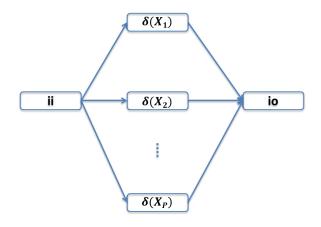

In each mapping cluster, two special interface actors, ii (interface input) and io (interface output) actors, are inserted. These actors represent interfaces to the enclosing supernodes and serve to inject data from input edges and to output edges of the supernodes, while providing standalone dataflow graph representations for each level of the design hierarchy. Using these standalone representations, buffer management and scheduling can be performed to ensure correct, consistent execution while mapping the actors in each design hierarchy level  $L_i$  into the corresponding ith level of the targeted parallel platform.

Each mapping cluster, when executed, is assumed to fire the interface actors only once. The derivation of the production and consumption rates associated with the interface input and output actors, in general, depends on the characteristics of supernodes (subsystems). Nevertheless, the valid values of the rates should satisfy the condition that there exists a non-trivial solution of the balance equations for the associated mapping cluster given that the ii and io actors only fire once. This condition is important since it guarantees that a valid period schedule can be found for the mapping cluster.

Presently, we compute these rates by hand, as our emphasis in this work is on demonstrating the overall design methodology and its utility on practical case studies. However, the process can readily be automated since it is based on formal dataflow principles. Development of automated tool support for the design methodology proposed in this chapter is a useful direction for further work.

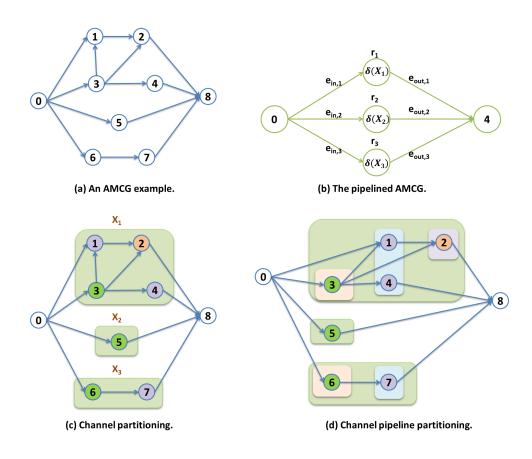

For a mapping cluster C, virtual edges (edges with zero rates of consumption

and production) are added between source (sink) actors and the ii (io) actor to connect these actors with the interface actors, where the source (sink) actors are those actors without input (output) edges. For each source actor  $\operatorname{src}$  in C, a virtual edge is created to connect  $\operatorname{src}$  from the ii actor; Similarly, for each sink actor  $\operatorname{snk}$  in C, a virtual edge is created to connect  $\operatorname{snk}$  to the io actor. The original mapping cluster together with the actors ii and io, and the corresponding set of virtual edges is referred to as the augmented mapping cluster graph (AMCG). Given a mapping cluster C, the corresponding AMCG is denoted as  $\operatorname{AMCG}(C)$ .

The virtual edges are added to augment the mapping cluster such that for each actor  $\alpha$  in C, there exists a path in the AMCG from ii to io that traverses  $\alpha$ . This condition is important for further partitioning and transformation techniques, which are introduced in Section 4.1.2.

The mapping clusters constructed using this process are used for efficient mapping of flowgraph structures into architectures that employ multi-level parallelism. Such architectures, such as graphics processing units (GPUs) and CBEA-compliant processors [38], are becoming increasingly important in the realization of computationally-intensive signal processing systems.

# 4.1.2 Partitioning of Mapping Cluster Graphs

In this section, we present techniques for graph partitioning that use the mapping clusters generated by the MHDT approach described in Section 4.1.1. These partitioning techniques provide further transformations to the application dataflow

Figure 4.2: An example of a design hierarchy for an MDSDF specification.

graph that facilitate analysis and exploitation of parallelism across different levels of the targeted platform hierarchy.

Let V(C), E(C) denote, respectively, the sets of actors and edges in AMCG(C). The graph AMCG(C) is partitioned through the following process.

First, AMCG(C) is partitioned into n channels  $X_1, X_2, \ldots, X_n$ , where  $n \geq 1$ . Each channel X is an ordered pair X = (actors(X), edges(X)), where  $actors(X) \in V(C)$  and  $edges(X) \in E(C)$ , and actors(X), edges(X) are mutually connected. A set P of actors and a set Q of edges are mutually connected if for each  $e \in Q$ , we have that  $src(e) \in P$  and  $snk(e) \in P$ , where src(e) represents the source actor of edge e and snk(e) represents the sink actor of edge e. For the partition into channels  $X_1, X_2, \ldots, X_n$  to be valid in this context, the edge sets  $edges(X_1), edges(X_2), \ldots$ ,  $edges(X_n)$  must be disjoint. Furthermore, in a valid partition  $X_1, X_2, \ldots, X_n$ , each channel contains both ii and io (i.e., each  $actors(X_i)$  contains both of these actors), and beyond these two common actors, no other actor in AMCG(C) is contained in multiple channels.

Thus,

$$\bigcap_{i=1}^{n} \{edges(X_i)\} = \{\emptyset\}, \tag{4.3}$$

and

$$\bigcap_{i=1}^{n} \{actors(X_i)\} = \{ii, io\}. \tag{4.4}$$

We refer to this kind of graph partition as a channel partition of the associated

AMCG. By definition, a channel partition ensures that, except through the interface actors, there is no path that connects any pair of distinct channels, and therefore, all channels can be executed in parallel once the input tokens of the associated supernode are injected into the associated mapping cluster. We refer to each  $X_i$  as a *channel* of the mapping cluster C (or of AMCG(C)).

Algorithm 1 outlines a partitioning process, which we refer to as the *AMCG* partitioning algorithm, that we have developed for strategic derivation of channel partitions.

After channel partitioning, the actors in each channel X are further partitioned into  $\rho_1(X), \rho_2(X), \ldots, \rho_{parts(X)}(X)$  in such a way that all actors in each  $\rho_i(X)$  are ready to fire (i.e., all input tokens are available for a given iteration of the associated mapping cluster) immediately after all actors in the preceding partition components  $(\rho_1(X), \rho_2(X), \ldots, \rho_{i-1}(X))$  have fired completely. In this context, by firing completely, we mean that the associated actor A has finished  $\nu(A)$  firings (i.e., a single-or multi-dimensional "volume" of firings as represented by the vector  $\nu(A)$  in the current iteration of the enclosing mapping cluster, where  $\nu(A)$  represents the firing vector of the actor A. At the beginning of this partitioning process, the interface input actor ii is initialized as being fired completely.

This process results in a unique partition  $\rho_1(X), \rho_2(X), \dots, \rho_{parts(X)}(X)$  of each channel X, which we refer to as the *pipeline partition* of the channel. The pipeline partition provides a decomposition of a channel into a flowgraph pipeline consisting of parts(X) "stages", where all actors within a given pipeline stage  $\rho_i(X)$  can be fired simultaneously for a given mapping cluster iteration once the previous stages

#### Algorithm 1 Outline of the AMCG partitioning algorithm.

```

// The AMCG partitioning process for a mapping cluster C = (V, E).

// This process generates a finite sequence of channels \{X(i) = (V(i), E(i))\}.

Vb = V.Remove(ii,io); // The set of all non-interface vertexes in V.

Eb = E;

i = 1;

while (Vb is non-empty) {

v = Vb[1];

// The first vertex in Vb.

V(i) = \{v\};

// Initialize the vertex set for a new channel.

Vb.Remove(v);

// Remove v from Vb.

E(i) = {};

EC = \{\};

EC = The set of all edges in Eb that are incident to any vertex in V(i);

while (EC is non-empty) {

VC = {all vertexes in Vb that are incident to edges in EC};

V(i).Add(VC);

// Add all vertexes in VC to V(i).

Vb.Remove(VC);

// Remove all vertexes in VC from Vb.

E(i).Add(EC);

// Add all edges in EC to E(i).

// Remove all edges in EC from Eb.

Eb.Remove(EC);