ABSTRACT

Title of dissertation: MODEL-BASED DESIGN AND

IMPLEMENTATION OF DEEP

WAVEFORM ANALYSIS SYSTEMS

Yanzhou Liu

Doctor of Philosophy, 2018

Dissertation directed by: Professor Shuvra S. Bhattacharyya

Dept. of Electrical and Computer Engr., and

Institute for Advanced Computer Studies

Analysis of signals of relatively long duration, an area that is referred to as

deep waveform analysis, is of increasing importance in instrumentation systems for

wireless communications. For example, jitter measurement of deep waveforms must

be performed during design and manufacturing tests for complex communications

circuitry or equipment. As requirements for bit error rate performance become more

stringent and data volumes increase, it becomes increasingly important and inter-

esting to perform deep waveform analysis computations in long, or even temporally

unbounded, waveforms.

Real-time response and limited hardware resources challenge the design meth-

ods of deep waveform analysis systems. Previous methods for deep waveform anal-

ysis required storage and computation across all samples of the waveform at once.

However, as the amount of data in the waveform grows, and especially if the wave-

form is unbounded, storage of the waveform in its entirety becomes impractical.

The need to satisfy stringent real-time constraints, handle large volumes of data at high sample rates, and operate on resource-constrained platforms result in challenging problems in the development of advanced systems for deep waveform analysis. In this thesis, we have developed new design methodologies and design optimization methods to address these problems. The contributions of the thesis are geared toward handling large, possibly unbounded, signal data sets, and providing novel trade-offs among measurement accuracy, memory constraints, and real-time performance. Motivated by performance bottlenecks that we observed in our experimentation with deep waveform analysis, we have also developed a new model of computation for representing signal processing applications in a way that improves the efficiency of data communication between computational modules.

The main contributions of this thesis are summarized in the following.

(1). Design methodology for deep waveform analysis systems. We have developed a new design methodology for deep waveform analysis under limited resources. The methodology builds on the formalisms of dataflow-based design and implementation of signal processing systems. Our proposed methodology is shown to help significantly advance the prior state of the art in jitter measurement system design, and it forms an important foundation for later contributions that are presented in the thesis. Our approach is demonstrated through extensive experiments using actual measured data. Through its incorporation of high-level dataflow principles, the approach is suitable for efficient mapping to a variety of platforms, including multicore processors and graphics processing unit (GPU) devices for high performance signal processing.

- (2). Design optimization for gapless deep waveform analysis. We have developed novel models and design optimization methods for addressing the real-time processing challenges of gapless deep waveform applications. A gapless signal processing application is characterized by one or more continuous streams of input data, where the data must be processed reliably without dropping any of the input samples. The strict real-time processing requirements for gapless deep waveform applications can be very challenging when input data rates are high, processing requirements are intensive, or the target platform is significantly resource constrained. The methods developed in this part of the thesis focus on optimizing the throughput of deep waveform analysis subject to the on-board memory constraints of a given data acquisition system interface, processor memory constraints, and the constraint of gapless processing.

- (3). Passive-active flowgraphs for dataflow-based implementation. We introduce a new model of computation called passive-active flowgraphs (PAFGs), which complement conventional dataflow-based application representations. We have developed PAFGs to address important bottlenecks in dataflow graph implementation associated with communication between computational modules (dataflow graph vertices). We demonstrate the use of PAFGs as an intermediate representation for refining dataflow graphs into efficient implementations. We develop formal underpinnings of the PAFG model of computation, and introduce systematic transformation techniques for deriving and optimizing PAFG representations.

# MODEL-BASED DESIGN AND IMPLEMENTATION OF DEEP WAVEFORM ANALYSIS SYSTEMS

by

# Yanzhou Liu

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2018

Advisory Committee: Professor Shuvra S. Bhattacharyya, Chair/Advisor Professor Manoj Franklin Professor Sennur Ulukus Doctor Lee Barford Professor Mihai Pop © Copyright by Yanzhou Liu 2018

# Dedication

To my parents and all of my friends, thank you for everything.

#### Acknowledgments

Firstly I would like to sincerely express my gratitude to my research advisor Professor Shuvra Bhattacharyya for his invaluable support, guidance, patience and encouragement throughout my Ph.D. study. His continuous support and instructions helped me a lot in my research and thesis preparation. His technical advice and motivation and enthusiasm to research are indispensable to my completion of research and dissertation. I could not have imagined having a better research advisor for my Ph.D. study.

I also want to thank my committee members, Professor Franklin, Professor Ulukus, Doctor Barford, Professor Pop and Professor Goldsman for providing useful and insightful feedbacks and suggestions to my research.

I am grateful to Professor Rong Chen, Doctor William Plishker, Doctor Laihuei Wang, Doctor Kishan Sudusinghe, Doctor Shuoxin Lin, Ms. Lin Li, Mr. Jiahao Wu, Mr. Honglei Li, Mr. Jing Geng, Mr. Kyunghun Lee and other colleagues and research project collaborators for their generous help and support. I would also like to thank Marshall Plan Foundation and Fachhochschule Salzburg for providing a great opportunity for research and study in Austria.

Finally I give my special thanks to my great parents for their love and support during my study.

The research underlying this thesis was supported in part by U.S. National Science Foundation, Agilent Technologies and Keysight Technologies.

# Table of Contents

| Dedication                                                                                                                                                                                                   | ii                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Acknowledgements                                                                                                                                                                                             | iii                        |

| List of Tables                                                                                                                                                                                               | vii                        |

| List of Figures                                                                                                                                                                                              | viii                       |

| List of Abbreviations                                                                                                                                                                                        | X                          |

| 1 Introduction 1.1 Jitter Measurement                                                                                                                                                                        |                            |

| 2 Background 2.1 Synchronous Dataflow 2.2 Core Functional Dataflow 2.3 LIDE — The DSPCAD Lightweight Dataflow Environment 2.4 Jitter Measurement                                                             | 9<br>11                    |

| 3 Dataflow Design for Deep Waveform Analysis Systems 3.1 Introduction 3.2 Proposed method 3.2.1 Dataflow Modeling 3.2.2 Implementation in LIDE-C 3.2.2.1 DVL 3.2.2.2 LFT 3.2.3 Scheduling the Dataflow Graph | 20<br>21<br>24<br>25<br>26 |

| 3.3 Results                                                                                                                                                                                                  |                            |

| 4 | Dee  | p Wave   | form Analysis with Parallelization and Constant Memory | 35   |

|---|------|----------|--------------------------------------------------------|------|

|   | 4.1  | Jitter   | Measurement System Design                              | . 37 |

|   |      | 4.1.1    |                                                        |      |

|   |      | 4.1.2    | Window-based Signal Analysis                           | . 38 |

|   |      | 4.1.3    | System-Level Model                                     |      |

|   |      |          | 4.1.3.1 Actor Descriptions                             |      |

|   |      | 4.1.4    | Actor Implementation                                   |      |

|   |      |          | 4.1.4.1 Jitter Measurement Optimization using LIDE-OCL |      |

|   |      |          | 4.1.4.2 DVL and RE                                     |      |

|   |      |          | 4.1.4.3 RRE and LFT                                    |      |

|   |      |          | 4.1.4.4 TRT                                            |      |

|   |      | 4.1.5    | Schedule for Dataflow Graph Execution                  |      |

|   | 4.2  |          | imental Verification                                   |      |

|   | 4.3  |          | nary                                                   |      |

|   | 1.0  | Sami     |                                                        | . 01 |

| 5 | Desi | ign Met  | thods for Gapless DSP Applications                     | 54   |

|   | 5.1  | Introd   | luction                                                | . 55 |

|   | 5.2  | Backg    | round                                                  | . 58 |

|   | 5.3  | Syster   | m Design                                               | . 59 |

|   |      | 5.3.1    | Window-based Analysis                                  |      |

|   |      | 5.3.2    | DAQ Interfacing                                        |      |

|   |      |          | 5.3.2.1 DAS Actor Implementation                       |      |

|   |      |          | 5.3.2.2 DAT Actor Design                               |      |

|   |      | 5.3.3    | Dataflow Graph for Deep Jitter Measurement             |      |

|   | 5.4  | Perfor   | rmance Optimization                                    |      |

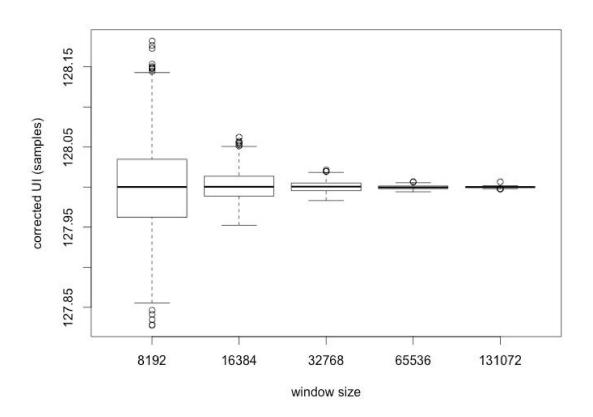

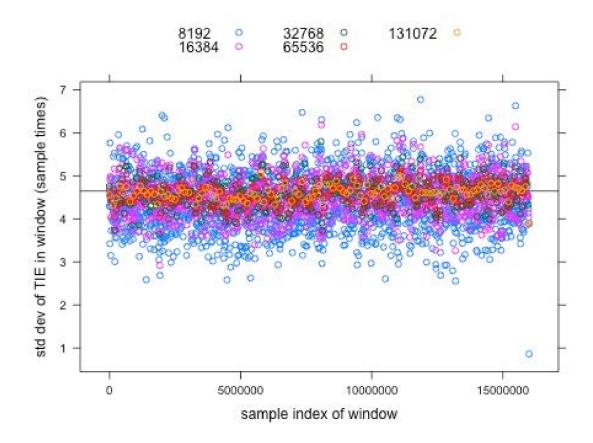

|   |      | 5.4.1    | Window Size Optimization                               |      |

|   |      | 5.4.2    | Sorting Optimization                                   |      |

|   |      | 5.4.3    | Throughput Optimization                                |      |

|   | 5.5  | Exper    | riments and Analysis                                   |      |

|   |      | 5.5.1    | Sorting in the Optimized DVL and RE Actors             |      |

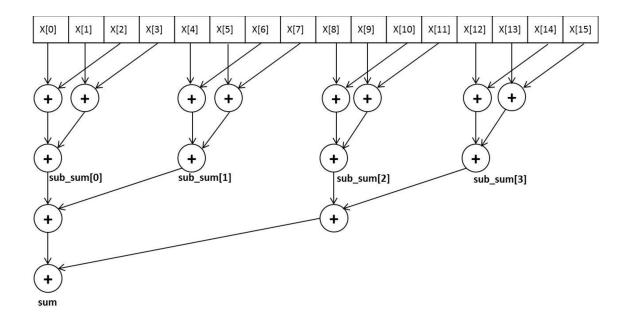

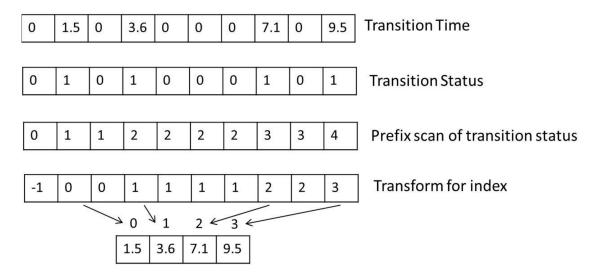

|   |      | 5.5.2    | Optimization of Reduction and Prefix Sum Operations    |      |

|   |      | 5.5.3    |                                                        |      |

|   |      | 5.5.4    | Overhead Analysis for Dynamic Adaptation               |      |

|   |      | 5.5.5    | System Throughput                                      |      |

| 6 | Gen  | eralizeo | d Graph Connections for Dataflow Modeling              | 83   |

|   | 6.1  | Introd   | luction                                                | . 84 |

|   | 6.2  | Relate   | ed Work                                                | . 87 |

|   | 6.3  | PAFC     | Representations                                        | . 89 |

|   |      | 6.3.1    | PAFG Blocks                                            | . 91 |

|   |      | 6.3.2    | Coordination Functions and Alternating PAFGs           | . 93 |

|   |      | 6.3.3    | Alternating PAFGs                                      | . 94 |

|   |      | 6.3.4    | Direct PAFGs                                           | . 94 |

|   |      | 6.3.5    | Association between Dataflow Graphs and PAFGs          | . 97 |

|   | 6.4  | Passix   | vization Transformation                                | . 98 |

|    | 6.5    | Appl     | ication Examples and Experiments                    | <br>. 101 |

|----|--------|----------|-----------------------------------------------------|-----------|

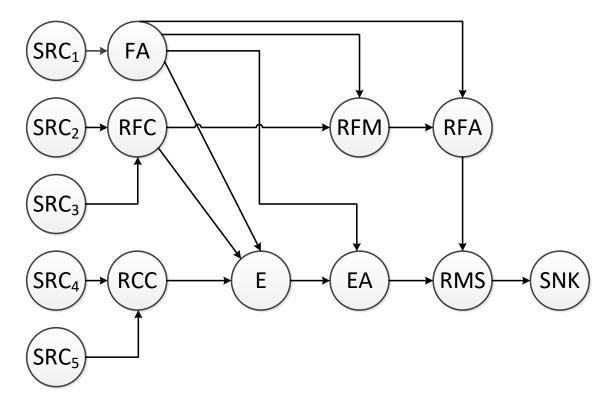

|    |        | 6.5.1    | Error Vector Magnitude Computation                  | . 101     |

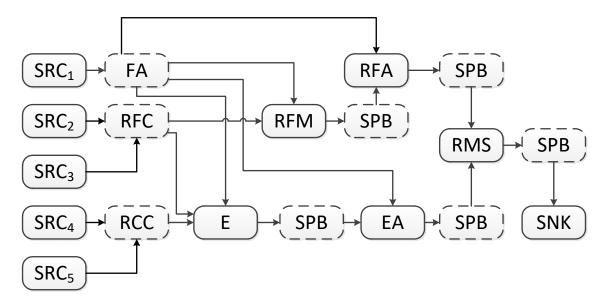

|    |        | 6.5.2    | Jitter Measurement Application                      | . 104     |

|    | 6.6    | Summ     | nary                                                | <br>106   |

| 7  | Con    | clusions | s and Future Work                                   | 108       |

|    | 7.1    | Concl    | $\operatorname{usions}$                             | . 108     |

|    | 7.2    | Future   | e Work                                              | . 110     |

|    |        | 7.2.1    | Parallelization of Deep Waveform Analysis Systems   | . 110     |

|    |        | 7.2.2    | Future Work on PAFG-Based Design and Implementation | <br>. 111 |

| Bi | bliogi | raphy    |                                                     | 113       |

# List of Tables

|     | Summary of actors in the dataflow graph of signal frequency recovery Obtained jitter standard deviation, by method |     |

|-----|--------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Standard deviation of TIE: Accumulated variant                                                                     | 51  |

| 5.1 | Actors in the dataflow graph of Figure 5.2                                                                         | 66  |

| 5.2 | Throughput speedup for TRT, RRE and LFT actors                                                                     | 77  |

| 5.3 | Adaptation overhead in gapless jitter measurement system                                                           | 80  |

| 6.1 | Coordination function for the direct PAFG of Figure 6.6                                                            | 96  |

| 6.2 | Coordination function for the PAFG in Figure 6.7                                                                   | 100 |

| 6.3 | Results for the EVM application                                                                                    | 104 |

| 6.4 | Results for the jitter measurement application                                                                     | 106 |

|     |                                                                                                                    |     |

# List of Figures

| 2.1                                                                         | A simple synchronous dataflow graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                              |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                      | An illustration of typical input signals that are analyzed in this chapter. Dataflow model for signal frequency recovery and jitter computation. Measurement apparatus used to verify the proposed method Recovered clock period in different windows                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22<br>30<br>31<br>31<br>32                                     |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                      | Dataflow model for real-time jitter measurement system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39<br>44<br>46<br>51<br>52<br>53                               |

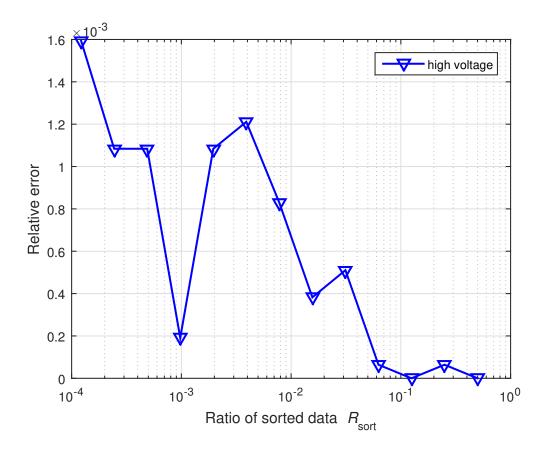

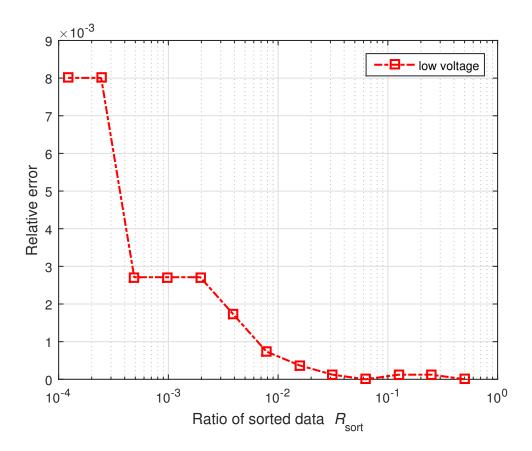

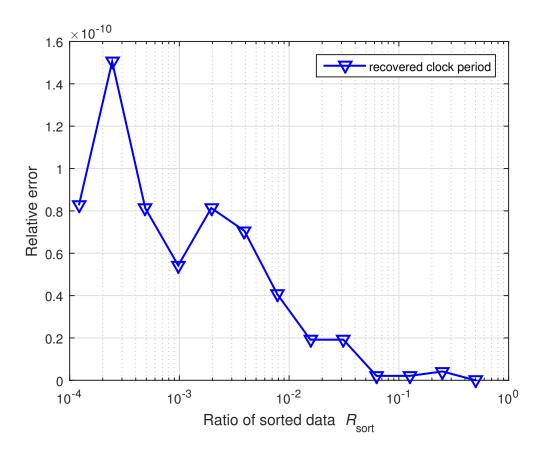

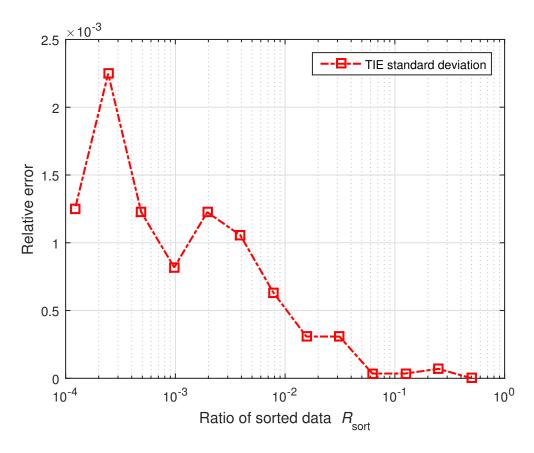

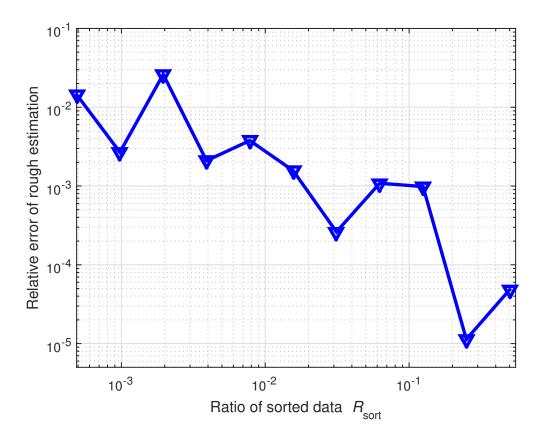

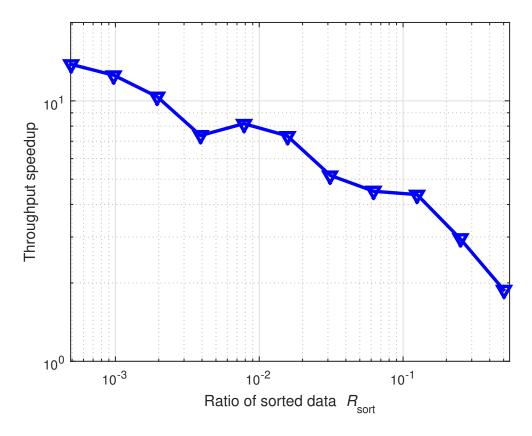

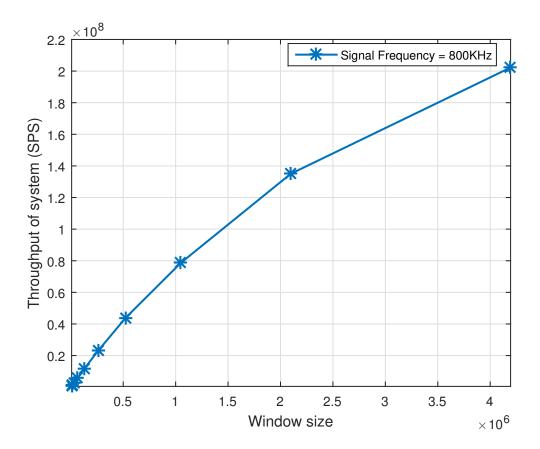

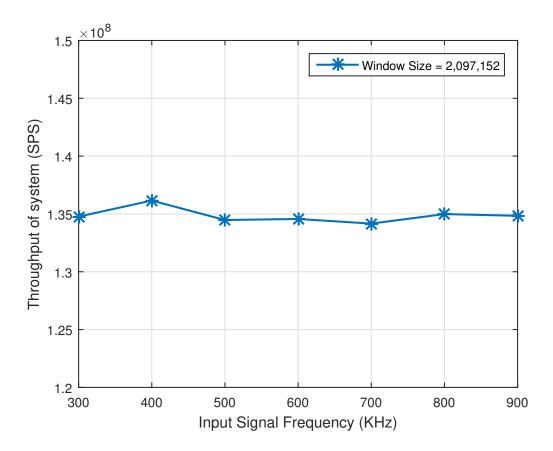

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | Subgraph for acquiring data. Dataflow graph for deep jitter measurement system. Throughput speedup for the DVL actor for varying values of $R_{\rm sort}$ . Relative error of high voltage threshold for various $R_{\rm sort}$ in DVL actor. Relative error of low voltage threshold for various $R_{\rm sort}$ in DVL actor. Relative error of recoved clock period for various $R_{\rm sort}$ in DVL actor. Relative error of TIE standard deviation for various $R_{\rm sort}$ in DVL actor. Relative error of rough estimation for various $R_{\rm sort}$ in RE actor. Throughput speedup for the RE actor for varying values of $R_{\rm sort}$ . System throughput versus window size. | 61<br>64<br>73<br>74<br>75<br>76<br>77<br>78<br>79<br>81<br>82 |

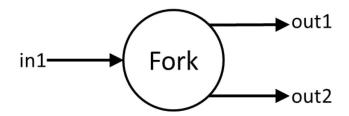

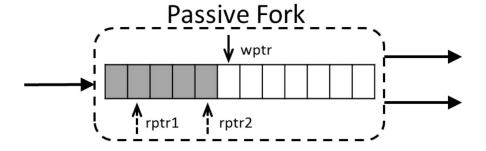

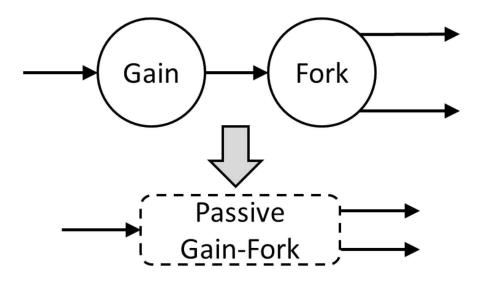

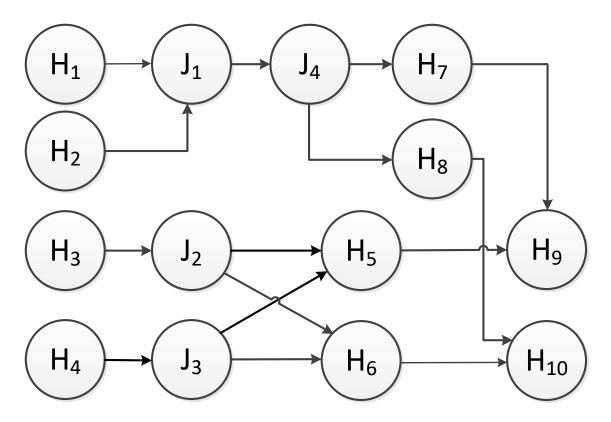

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                             | Fork actor illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85<br>85<br>86<br>87<br>96                                     |

| 6.6  | The direct PAFG that is derived from Figure 6.5                | . 97  |

|------|----------------------------------------------------------------|-------|

| 6.7  | Resulting PAFG after applying the passivization transformation | . 100 |

| 6.8  | Dataflow graph for EVM measurement                             | . 102 |

| 6.9  | Optimized PAFG for EVM measurement                             | . 103 |

| 6.10 | Dataflow graph for jitter measurement application              | . 105 |

| 6.11 | Optimized PAFG for jitter measurement application              | . 106 |

#### List of Abbreviations

ABC Adjacent Buffer Coordination

API Application Programming Interface

BER Bit Error Rate

BMR Buffer Memory Requirement

CDF Cumulative Distribution Function

CFDF Core Functional Dataflow CPU Central Processing Unit

DAQ Data acquisition

DSP Digital Signal Processing

EVM Error Vector Magnitude

FCFS First Come First Serve FFT Fast Fourier Transform FIFO First-In, First-Out

FIR Finite Impulse Response

GEMS Graph Elements

GPU Graphics Processing Unit

HEFT Heterogeneous Earliest Finish Time

IIR Infinite Impulse Response

LIDE The DSPCAD Lightweight Dataflow Environment

OpenCL Open Computing Language

PAFG Passive-active Flowgraph

PDF Probability Density Function

PRBS Psuedo-random binary signal

RMS Root mean square

SDF Synchronous Dataflow Graph SISO Single-Input, Single-Output SMSS Single-mode steady state  $\operatorname{SSE}$  Streaming Single instruction multiple data Extensions

SPS Samples per second

$\begin{array}{ll} {\rm TDD} & {\rm Targeted~DAQ~Device} \\ {\rm TIE} & {\rm Time~Interval~Error} \end{array}$

UI Unit Interval

## Chapter 1: Introduction

In the information era, more and more data needs to be processed in daily life, which greatly challenges the ways in which people store data, as well as the methods for processing and managing data efficiently and accurately. Our increasing ability to acquire data in the real world has resulted in continually escalating requirements for higher throughput and optimized memory management in design and implementation of embedded signal processing systems.

Many embedded signal processing applications involve the continuous acquisition and sampling of data, and the management of signals that have long duration. The time spans of continuous signal acquisition for such applications range from minutes, hours to days or even longer. Often, there is no well defined bound on the input signal duration that is known in advance.

Signals with long, possibly indefinitely-long durations and high sample rates are referred to as *deep waveforms*. Deep waveforms present major challenges for resource-constrained embedded implementation due to the large volumes of samples that need to be processed, and the need for reliable, real-time performance to avoid "falling behind" in the processing of the continuously-arriving input samples. This thesis is concerned with developing new models and methods for addressing the chal-

lenges of deploying deep waveform applications on resource-constrained platforms.

#### 1.1 Jitter Measurement

As a concrete example of an important deep waveform application, we focus on *jitter measurement*, which has important uses in instrumentation for electronic system design, such as in measurement equipment for communication systems. Although we focus on jitter measurement for a significant part of this thesis, the core approaches developed in the thesis are not specific to this application, and can be adapted to other relevant deep waveform applications.

The jitter of a signal is defined as the short-term deviation of the signal's transition time from its ideal position in time [1]. Continuous, accurate evaluation of jitter is useful, for example, in computing the Bit Error Rate (BER) of a communication system. The BER is a widely-used performance metric for quality evaluation in communication systems. It is defined as the ratio of the number of bits received or transmitted in error to the total number of bits received or transmitted in the system [2]. BER can be estimated from the statistics of the jitter of eye crossings in the input signals (e.g., see [1]).

### 1.2 Dataflow Modeling

We employ dataflow-based modeling and analysis extensively in this thesis, and make new contributions to the application of dataflow methods in deep waveform applications. *Dataflow models of computation* are widely-used in the design

and implementation of signal processing systems. While dataflow represents a broad spectrum of models and methods that are used in many types of computer hardware and software systems, we focus specifically on dataflow as it relates to model-based design of embedded signal processing systems (e.g., see [3]). In this form of dataflow, signal processing applications are represented as directed graphs, where vertices (actors) represent computational tasks, and edges represent first-in, first-out (FIFO) buffers that store data that is communicated between actors [4]. Dataflow techniques are used in a wide variety of commercial tools for design and implementation for signal and information processing systems. Prominent examples include LabVIEW (National Instruments), MATLAB (MathWorks), SystemVue (Keysight Technologies), and Tensor Flow (Google).

#### 1.3 Contributions of This Thesis

In this thesis, we develop new methods for dataflow-based design and implementation of deep waveform applications on resource-constrained platforms. Our methods are demonstrated on multicore platforms and hybrid CPU-GPU platforms, which integrate central processing unit (CPU) and graphic processing unit (GPU) devices. As mentioned previously, our methods are demonstrated concretely in the context of an advanced system for jitter measurement.

The contributions of this thesis involve three main parts. The first involves a new design methodology for deep waveform analysis under limited resources using dataflow graph techniques. This methodology is shown to help significantly advance

the prior state of the art in jitter measurement system design, and it forms an important foundation for later contributions that are presented in the thesis. Details and demonstrations of the methodology are presented in Chapter 3. This chapter is based on a paper that we have published in the Proceedings of the 2015 IEEE International Instrumentation and Measurement Technology Conference [5].

The second main contribution in this thesis addresses the problems of gapless deep waveform analysis, and systematic integration of data acquisition devices and their associated real-time constraints into model-based design and implementation of deep waveform applications. A gapless signal processing application is characterized by one or more continuous streams of input data, where the data must be processed without gaps. In this context, by "without gaps", we mean continuous processing without dropping any of the input samples. The strict real-time processing requirements for gapless deep waveform applications can be very challenging when input data rates are high, processing requirements are intensive, or the target platform is significantly resource constrained.

In the second part of this thesis, we present novel models and design optimization methods for addressing the real-time processing challenges of gapless deep waveform applications. Details of these models and methods are presented in Chapter 4 and Chapter 5. We have published a preliminary version of this work in the Proceedings of the 2016 IEEE International Instrumentation and Measurement Technology Conference [6].

The third main contribution of this thesis addresses a fundamental limitation of dataflow semantics in design and implementation of signal processing systems. This limitation involves inter-actor communication patterns that depart from the single-input, single-output (SISO) interface and FIFO behavior that are defined for dataflow edges (e.g., see [7]). When these types of communication pattern are mapped into hardware or software using pure dataflow semantics, the resulting implementations can be very inefficient. At the same time, these types of communication patterns are important in deep waveform applications.

To address this problem, we introduce a novel application modeling concept called *passive blocks*, which generalize the FIFO buffers of dataflow graphs. Like dataflow buffers, passive blocks are used to store data during the intervals between its generation by producing actors, and its use by consuming actors. However, passive blocks can have multiple inputs and multiple outputs, and can incorporate operations on and rearrangements of the stored data subject to certain constraints.

We introduce a new model of computation called passive-active flowgraphs (PAFGs), which complement conventional dataflow-based application representations. We demonstrate the use of PAFGs as an intermediate representation for refining dataflow graphs into efficient implementations. We develop formal underpinnings of the PAFG model of computation, and introduce transformation techniques for deriving and optimizing PAFG representations. We demonstrate the utility of PAFG-based modeling and optimization through application case studies involving jitter measurement and error vector magnitude monitoring, which are two important deep waveform applications used in instrumentation for communication system design.

Details on the PAFG model of computation and its application to signal pro-

cessing system design are presented in Chapter 6. This chapter is based on a paper that has been accepted for publication and is to appear in the Proceedings of the 2018 IEEE Workshop on Signal Processing Systems [8].

#### 1.4 Outline of Thesis

The remainder of this thesis is organized as follows. Chapter 2 introduces background on the different research topics discussed in the thesis. The chapter covers fundamentals of dataflow models for signal processing system design; background on specific software tools that we have used for prototyping and experimentation; and background on the jitter measurement application that we study in depth throughout the thesis. As described in Section 1.3, the three main contributions of the thesis are presented in Chapter 3, Chapter 4/Chapter 5, and Chapter 6, respectively. Chapter 7 concludes with a summary of the contributions of this thesis, and discusses directions for future work that are motivated by these contributions.

### Chapter 2: Background

In this chapter, we introduce background on core concepts that are applied to the work in this thesis.

### 2.1 Synchronous Dataflow

Dataflow is a form of model-based design that is employed for design and implementation in many areas of signal processing [3,4]. By providing formal methods to represent and analyze the flowgraph structures within signal processing applications, dataflow methods help to enhance the efficiency and reliability of implementations, and assist in the retargeting of designs across different hardware platforms.

A dataflow graph is a directed graph in which vertices, called actors, represent computational tasks, and edges represent the communication of data between actors. More specifically, each edge e = (u, w) in a dataflow graph represents a first-in, first-out (FIFO) buffer that stores data as it passed from the output of actor u to the input of actor v. Actor u is referred to as the source actor of edge e, and actor w is referred to as the sink actor of e.

Ports connect actors and edges. A port can be either an input port or an output port, depending on whether the actor consumes data from the incident edge or

produces data on it, respectively. Each unit of data that passes along a dataflow edge edge is referred to as a *token*. Tokens can have arbitrary data types. The execution of an actor in a dataflow graph is decomposed into discrete units of execution, which are referred to as *firings* of the actor.

Synchronous dataflow (SDF) is a restricted form of dataflow in which the number of tokens produced on each output edge is constant across all firings of a given actor, and similarly, the number of tokens consumed from each input edge is constant [9]. SDF graphs are widely used in the design and implementation of signal processing applications, and many kinds of useful analysis and optimization techniques have been developed for this class of graphs [3]. An important property of SDF graphs is that, if certain well-defined consistency properties hold, they can be implemented to operate on unbounded-length input streams with deadlock-free execution, and bounded memory requirements that can be determined at compile-time [9].

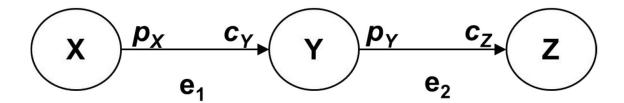

Figure 2.1 shows an example of a simple SDF graph. The annotations on the edges represent the production and consumption rates of the actors — that is, the constant numbers of tokens that are produced and consumed on each firing. For example, when actor Y is fired,  $c_Y$  tokens are consumed from edge  $e_1$ , and  $p_Y$  tokens are produced onto edge  $e_2$ . The production and consumption rates of an actor are collectively known as the dataflow rates of the actor.

An important task involved in implementing a dataflow graph is the task of scheduling the graph — that is, the process of determining the assignment of actor firings to processors and the order in which multiple firings assigned to the same pro-

Figure 2.1: A simple synchronous dataflow graph.

cessor will execute [10]. Scheduling techniques can be distinguished based on when the assignment and ordering tasks described above are performed (e.g., at compile time versus at run time). This leads to important classes of scheduling strategies, including static, dynamic, quasi-static, and static assignment strategies [11]. Various useful abstractions have been developed for representing dataflow graph schedules, and providing a basis for analysis, transformation, and software synthesis of schedules [12, 13].

#### 2.2 Core Functional Dataflow

In this thesis, we build on the methodology of dataflow-based design and implementation of signal processing systems, and we apply a specific form of dataflow-based design referred to as core functional dataflow (CFDF). In this section, we will provide background on CFDF graph.

Core functional dataflow (CFDF) is a form of dataflow that is useful for applying dataflow-based design methods to a wide variety of signal processing applications [14]. In CFDF, the behavior of an actor is decomposed into a set of modes such that any given firing corresponds to a single mode, and in each mode, the number of tokens consumed from each input edges is constant, and similarly, the

number of tokens produced on each output edge is constant. These numbers of tokens consumed and produced by the actor in each mode are consumption rates and production rates, respectively. More specifically, given a mode m of a CFDF actor A, the consumption rate associated with m and input edge  $e_i$  is the number of tokens consumed by A during m from  $e_i$ . Similarly, if  $e_o$  is an output edge of A, then the production rate associated with m and  $e_o$  is number of tokens produced by A during m on  $e_o$ .

As part of execution of a given mode m, a CFDF actor must determine the next mode in which the actor will operate. The next mode determines the mode that will be active during the next firing of the actor. Although production and consumption rates for any given mode are constant, the rates can vary across different modes, which allows for modeling and design of  $dynamic\ dataflow$  behavior. Additionally, the next mode of an actor can be data-dependent — i.e., it is not necessarily a function only of the current mode.

Implementation of a CFDF actor requires implementation of two specific functions, which are called the *enable* and *invoke* functions of the actor. Each of these functions take as an argument in the *actor context*, including the *mode state*, and the current values of all parameters of the actor. Here, by the mode state, we mean the current mode of the actor if the actor is currently firing or the next mode of the actor (as determined by the previous mode or an initialization process) if the actor is currently dormant (not firing). The enable function returns a Boolean value indicating whether or not there is sufficient data on the input edges and sufficient empty space on the output edges to allow the actor to fire based on the mode specified by the mode state. On the other hand, the invoke function executes a single firing of the associated actor in the mode specified by the mode state, and changes the value of the mode state based on the next mode that is determined as part of the firing.

The separation of enable and invoke functions helps to modularize the design of CFDF actors, and to implement more efficient and predictable scheduling techniques. It is also important to note that it is not always necessary to call the enable function at run-time prior to executing the invoke function. Compile-time analysis of dataflow properties may provide guarantees about data and output space availability for some proper subset of an actor's firings or for all firings. In such cases, the invoke function can safely be executed without first using the enable function to validate fireability. For example, when implementing static scheduling techniques (e.g., see [3,9]) for CFDF graphs (when such schedules exist), there is no need to use the enable function at all.

In addition to applying CFDF semantics as a specific form of dataflow in this thesis, some of the techniques that we apply are related to parametric dataflow modeling techniques, such as parameterized dataflow [15]; parameterized sets of modes [16]; and parameterized and interfaced dataflow meta-model [17].

### 2.3 LIDE — The DSPCAD Lightweight Dataflow Environment

LIDE, which stands for the DSPCAD *LIghtweight Dataflow Environment*, provides a flexible and lightweight software environment for dataflow-based design and

implementation of DSP applications [18]. LIDE contains collections of pre-designed libraries for dataflow graph elements, including actor and edge implementations. These existing graph elements or *gems*, which stands for "Graph EleMentS", provide useful building blocks for constructing dataflow graphs, and also provide examples that designers can use as references or templates when extending LIDE with their own custom-designed actor and edge implementations.

A core part of LIDE is a compact set of abstract application programming interfaces (APIs) for implementing, integrating, and scheduling dataflow actors based on CFDF semantics. These APIs are abstract in the sense that they are defined in terms of mathematical dataflow principles, and are independent of any particular language for programming the actors (actor design language). The compact and abstract nature of this set of APIs makes it easy to map it into a wide variety of actor design languages. Presently, the set of actor design languages supported in LIDE includes C, CUDA, OpenCL and Verilog.

An actor in LIDE can be viewed as an abstract data type or a class (if an object oriented language is employed as the actor design language). Four interface functions are used in LIDE in the implementation of each actor — the construct, enable, invoke, and terminate functions. The construct function is used to create an instance of the actor, including all of the associated memory allocation and initialization. The enable and invoke functions implement their counterparts as defined by CFDF semantics. The terminate function is used to carry out any tasks, such as deallocation of memory, that are appropriate when an actor is no longer needed — e.g., if the enclosing application has terminated or if the dataflow graph

is being reconfigured in such a way that the actor will not be used any more.

#### 2.4 Jitter Measurement

In this thesis, we investigate a jitter measurement system as a case study for dataflow-based design and implementation of real-time deep waveform analysis. Jitter is defined as the deviation of a timing event in a signal from its ideal appearance in time [1]. We specifically study jitter measurement in the context of wireless communications, where bit error rate (BER) is an important metric for assessing overall system performance.

Previous work on jitter measurement has been performed in conjunction with use of clock recovery algorithms, and measurement based on a reference clock signal (e.g. see [19]). Loken presents a fixed-frequency clock recovery algorithm for jitter measurement [20]. This work assumes a two-state digital signal and a duty cycle that is approximately equal to 50%. We maintain these assumptions in our research, as they are applicable in our primary application context of deep waveform analysis for wireless communication systems.

There are various limitations in state-of-the-art methods for jitter measurement that our proposed research seeks to overcome. For example, some of the previous research on jitter measurement relies on a stable reference clock period. This limits applicability of the approaches since a stable reference clock period is not always available for measuring jitter. We overcome this limitation in our proposed research by integrating clock period estimation with jitter measurement analysis

— that is, our proposed analysis system first estimates the clock period, and then estimates the jitter in the input signal based on the estimated clock period.

Loken has developed an algorithm for jitter measurement from fixed-frequency signals that does not require a reference clock [20]. However, this algorithm has the limitation of being a "swallow and wallow" technique for signal analysis. This swallow and wallow characteristic requires all of the signal data to be stored in memory before the computation for jitter measurement is initiated. Such swallow and wallow approaches require large amounts of memory to analyze long signals, and limit the length (number of samples) or "depth" of deep waveform signals that can be handled.

In this thesis, we have demonstrated new window- and dataflow-based design and implementation techniques for jitter measurement that overcome this swallow and wallow limitation, while also maintaining the feature that a reference clock is not needed for the underlying measurement algorithm. We apply a windowing method that partitions the signal to be analyzed into multiple subsets, and allows processing of windows to proceed in real-time without need for all of the signal data to be available at once. We apply dataflow methods to model the signal flow characteristics of the algorithm that analyzes the signal windows, and develop efficient design transformations using the dataflow model to optimize memory cost and real-time performance.

# Chapter 3: Dataflow Design for Deep Waveform Analysis Systems

Deep waveform analysis applications are increasingly important in signal processing application areas, such as wired and wireless communication and biomedical instrumentation. In this chapter we begin to examine system design challenges for a specific deep waveform analysis application, jitter measurement, that we use throughout the thesis as a concrete case study to develop and demonstrate our research contributions.

The measurement of jitter is key when verifying the design or performing manufacturing test of ever more complex digital communications circuitry or equipment. As the requirements for bit error rates (BER) become more stringent and data volumes increase, it becomes increasingly important and interesting to measure timing jitter in long, or even temporally unbounded, waveforms.

Previous methods for doing constant rate clock recovery and jitter measurement required storing and computing all samples of the waveform at once. As the waveform grows, and especially if the waveform is unbounded, this storage of the waveform in its entirety becomes impractical. In this chapter, we demonstrate the transformation of the previous methods to a dataflow method where the entire waveform need never be stored.

The new method has been tested on actual measured data. Through its incorporation of dataflow principles, the new method is suitable for efficient mapping to a variety of platforms, including multicore and field programmable gate array platforms for high performance signal processing. Intermediate measurement results converge toward those obtained in the original method. The final measurement result, the jitter standard deviation, agrees with the original method to within well under one percent. Thus, a small amount of additional measurement error is added in order to remove the restriction that the entire waveform fit into memory.

Material described in this chapter has been published in [5].

#### 3.1 Introduction

Complex systems often include or are connected to other complex systems by ever faster communications links with lower rates of error. Communications errors are often due to timing errors or jitter. Thus, the measurement of jitter is key when verifying the design or performing manufacturing test of digital communications circuitry or equipment. As the requirements for bit error rates (BER) become more stringent and data volumes increase, it becomes increasingly important and interesting to measure timing jitter in signals of longer duration (that is, of so-called "deep waveforms"). Measuring deep waveforms both (1) increases the chances that rare events leading to communications errors will be captured and identified [21], and (2) allows the statistical estimation of the tails of jitter probability distributions, which in turn permits better extrapolation of BER. [22]

Commercially available instrumentation is capable of measuring communications and/or timing signal waveforms containing billions of samples. Here, we are concerned with constant rate clock recovery, where the clock is assumed not to change its period during the course of the measurement. Any deviation of the timing of the communication signal being measured from that constant rate clock is to be considered jitter. This is the case for many communications physical layers. (Exceptions include example in designs utilizing spread spectrum clocks.) Clock recovery and computation of jitter statistics are straightforward and computationally inexpensive when considered on a per-sample basis.

As discussed in Chapter 2, performing these tasks on deep waveforms takes considerable computing time. One way to address this computation speed issue is through parallel computing. Previous work [20] described and demonstrated the measurement capability and computational performance of a parallel algorithm for constant rate clock recovery from a two-logic state digital waveform.

That method is suitable for implementation on multicore central processing units (CPUs) and graphics processing units (GPUs). The resulting computational speedups permits its use on waveforms with millions of samples. However, that algorithm must store not only the entire waveform in memory but also a number of working arrays with lengths comparable to that of the number of samples in the waveform. As a result, even a multi-gigabyte memory is inadequate to do constant rate clock recovery on more than a few hundred million samples.

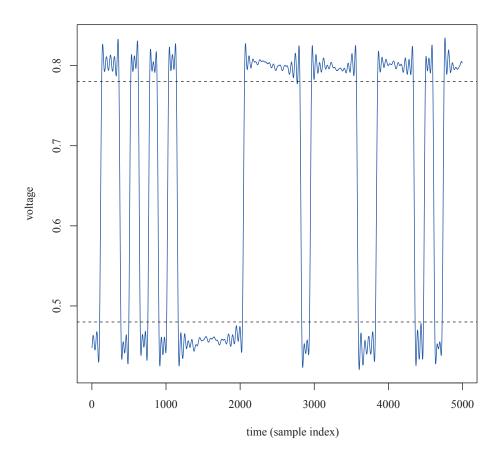

Figure 3.1 demonstrates typical input signals that are analyzed in this chapter.

The figure shows a small portion of a waveform with two logic states including high

Figure 3.1: An illustration of typical input signals that are analyzed in this chapter.

and low states. The two dashed horizontal lines indicate the thresholds l = 0.48 and h = 0.78 of the low and high logic states, respectively.

An alternative to storing a large waveform in memory is to use a dataflow approach. That is, a programming model is used where samples and intermediate results move on the edges of a directed graph and computations on these data occur at the graph vertices, called actors. Languages commonly used in measurement that provide variants of a dataflow framework include LabVIEW [23], VEE Pro [24], and Simulink [25]. When using a dataflow programming tool, the signal is processed sequentially. Neither it not intermediate computations are not (and typically can not be) stored in their entirety. This feature is attractive when analyzing deep

waveforms, when all such data will not fit into the available memory. Another important advantage of the dataflow formalism is that the dataflows exactly specify the data dependencies between computations, and so the computations of the actors can in many cases automatically be scheduled on multicore processors [3], yielding a parallel implementation without the need for explicitly parallel programming. Vector-mode computation is sometimes still possible inside actors [26], yielding a second level of parallel speed-up.

Despite such advantages, there is a subtle incompatibility between the data flow approach and that of storing and computing on the entire waveform. When the whole waveform is available, measurements can be made of the waveform based on its entirety that are used in later measurement stages. Sometimes this sort of design is referred to as the "swallow and wallow" approach, because the entire waveform is stored (or "swallowed") and then computed on (or "wallowed over"). For example, in the present case, the voltage statistics of the whole waveform can be used as recommended by the relevant IEEE standard [27] to arrive at the voltage thresholds used to determine the low and high voltage levels of the signal and the timing of the signal for purposes of clock recovery and then jitter measurement. When using the dataflow paradigm, it is no longer possible to take measurements of the entire signal and use them in computing derived measurements.

Thus, a measurement algorithm designed for the swallow and wallow approach can not in general produce identical results when modified to be used with the dataflow paradigm. It would seem that the best that can be done is to design a dataflow algorithm that closely approximates the behavior of the swallow and

wallow algorithm. Note that this must be a dynamic approximation. Suppose that the dataflow algorithm has fully processed the first n samples of the waveform. The best it can do is to approximate the measurement results of the swallow and wallow algorithm if it were applied to the same n samples. Since differences between the "swallow and wallow" and dataflow measurement results are inevitable, the differences should be categorized and documented.

In this chapter we present a case study of creating such a dataflow algorithm from a swallow and wallow algorithm, where the measurement problem being solved is constant-rate clock recovery. First, we present the proposed dataflow method along with a discussion of how and where that method must deviate from the swallow and wallow algorithm of [20]. Then we present the results of a study comparing the measurement results of the two methods in the light of the approximation criterion of the previous paragraph.

# 3.2 Proposed method

The swallow and wallow algorithm takes considerable computing time and requires a large amount of memory. As we discussed in Section 3.1, application of the dataflow paradigm can help to reduce memory requirements significantly. In this section, we take the case of clock recovery [20] as an example to discuss how to develop a dataflow method, based on the swallow and wallow algorithm, that approximates the measurement results of that algorithm in the sense described above.

#### 3.2.1 Dataflow Modeling

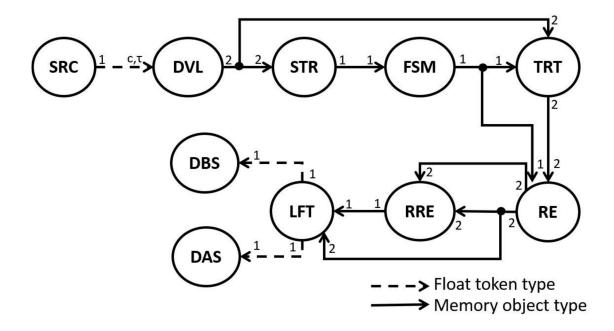

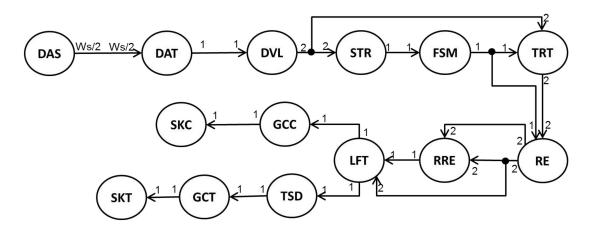

To create a dataflow model for the clock recovery application, we analyze the application to extract its high-level signal flowgraph structure. The basic steps for clock recovery [20] can be summarized as follows. The first step is to determine the voltage thresholds that correspond to high and low signal levels. The next step is to determine the complete set of transitions across these thresholds in the input signal. The third and last step is to estimate, from this set of transitions, the clock period; refine this estimate by rounding the differences of neighboring transitions in terms of the estimated clock period; and apply linear fitting to further refine the result. The input signal to this three-step clock recovery process is decomposed into a sequence of overlapping windows, where the three processing steps are applied iteratively to successive windows.

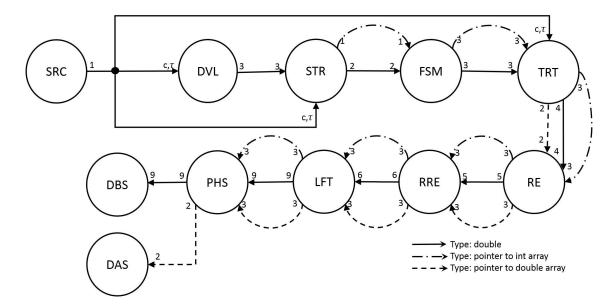

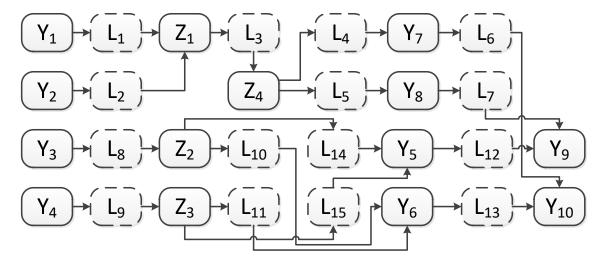

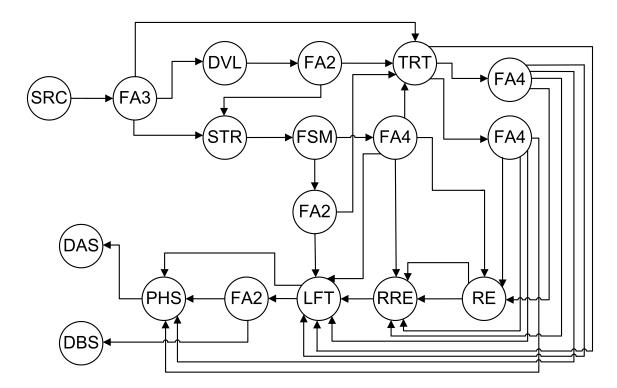

The resulting dataflow graph is shown in Figure 3.2. It is a dataflow model of the swallow and wallow algorithm for clock recovery. Table 3.1 lists the actors employed in the dataflow graph of Figure 3.2, and briefly summarizes the functionality of each one. The dataflow graph in Figure 3.2 is annotated with the production and consumption rates of the edges (flowgraph connections) in the graph. Such dataflow properties associated with edges are important when analyzing dataflow graphs to construct schedules and derive other parts of implementations. Given a dataflow edge e that is directed from an actor x to an actor y, the production rate of e is the number of tokens (data values) that is produced onto e in each firing of x, and similarly, the consumption rate of e is the number of tokens consumed from e during

Figure 3.2: Dataflow model for signal frequency recovery and jitter computation each firing of y.

The input port p of the DVL actor is annotated with two values  $[c, \tau]$ , where c is the consumption rate of the DVL actor from the input edge associated with p, and  $\tau$  is another dataflow-edge-related attribute called the *threshold* of the edge [28]. The threshold specifies the number of tokens that must be present on the corresponding input FIFO before the actor can fire. In general, the consumption rate of a port is less than or equal to the threshold. Consumption rate / threshold pairs are also indicated at certain input ports of the STR and TRT actors in Figure 3.2. In Figure 3.2, the consumption rates and thresholds for all edges are equal except for the input edges of the DVL, STR and TRT actors that are annotated with pairs of values on the associated input ports. More details about the key actors in Figure 3.2, including the DVL actor, are discussed in Section 3.2.2.

Table 3.1: Summary of actors in the dataflow graph of signal frequency recovery

| Actor | Description                                                                                                                                  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SRC   | Source. Load data from input file.                                                                                                           |  |  |  |  |

| DVL   | Determine Voltage Level. Sort the input data in the current window and determine the high and low voltage thresholds.                        |  |  |  |  |

| STR   | State Representation. Perform analog-to-digital conversion; assign state to data in the current window of the input signal.                  |  |  |  |  |

| FSM   | Finite State Machine. Determine transitions from high to low voltage states or low to high states.                                           |  |  |  |  |

| TRT   | Compute Transition Time. Compute the transition time for each transition in the current window.                                              |  |  |  |  |

| RE    | Rough Estimation. Derive an preliminary estimate of the clock period.                                                                        |  |  |  |  |

| RRE   | Refine Rough Estimation. Refine the rough estimation of the clock period to improve its accuracy.                                            |  |  |  |  |

| LFT   | Linear Fitting. Further refine the estimated clock period by linear fitting.                                                                 |  |  |  |  |

| PHS   | Phase. Compute the phase and time interval errors at the current transition using the refined clock period estimate.                         |  |  |  |  |

| DBS   | Double Sink. Store double precision numeric data to an output file; each input token encapsulates a scalar, double precision value.          |  |  |  |  |

| DAS   | Double Array Sink. Store double precision numeric data to an output file; each input token encapsulates an array of double precision values. |  |  |  |  |

#### 3.2.2 Implementation in LIDE-C

In this section, we discuss our implementation of the dataflow graph (Figure 3.2) for clock recovery. To develop this implementation, we have used *LIDE* (*Lightweight Dataflow Environment*) [18,29]. In our implementation of clock recovery, we employ *LIDE-C*, which provides APIs for implementing signal processing dataflow graphs using the C language. In general, a LIDE-C implementation includes C implementations of actors, edges, and a schedule to execute the overall dataflow graph.

Next, in Section 3.2.2.1 and Section 3.2.2.2, we discuss details of two of the most critical actors in our implementation.

#### 3.2.2.1 DVL

Each firing of the DVL actor examines a window of samples from the input signal, sorts the values of these samples, and determines high and low voltage thresholds based on the results of this sorting operation. The parameters of the DVL actor include the window size  $W_s$ , and the amount of overlap  $O_p$  between successive windows. The consumption rate and threshold for this actor are, respectively,  $W_s \times (1 - O_p)$ , and  $W_s$ . Intuitively, this means that before the actor can fire, a full window of data must be available at the input, but only part of this input is consumed during the firing — the rest remains in the input FIFO to be processed as part of the next (overlapping) window during the subsequent firing.

Since the applied voltage thresholds will influence the value of the estimated

clock period, it is essential to determine an appropriate voltage threshold. In our implementation, we consider two alternative methods for determining the voltage threshold. Selection between these two alternative methods is controlled by a third parameter Y of the DVL actor. The first method (Y = 1) is to use the sorted result from the current window to dynamically determine the voltage threshold associated with the current firing of the DVL actor. The second method (Y = 2) is to fix the voltage thresholds across all iterations based on the sorted result from the first window. We experiment with both of these methods, and results of this experimentation are discussed in Section 3.3. From these experiments, we find that the accuracy for Y = 2 is slightly better than that for Y = 1; however, the difference is so small for the examined application scenarios that it is not worth the added complexity to implement and apply the Y = 2 case.

#### 3.2.2.2 LFT

This actor optimizes (further refines) the result of clock period estimation by linear least square fitting. The sequences of transition times and phases at the transition times are the two data streams used in this linear fitting operation. The phase at a given transition time t depends on t and the estimated clock period. Since the total number of transitions is proportional to the number of windows processed, performing linear fitting across all transitions computed is computationally very expensive. To make this process more efficient, we select a subset of data for linear fitting. We allocate a buffer in the LFT actor to store the selected transition times,

and the corresponding phases to be used for linear fitting. There is a variety of methods to select data for linear fitting (e.g., see [30]). In our design of the LFT actor, we apply a rule for selecting data in which the selected data is composed both of data from previous transitions and from the current input signal window.

#### 3.2.3 Scheduling the Dataflow Graph

As discussed in Section 3.2.1, scheduling is an important step in simulating or implementing a dataflow graph application model. There are many possible schedules for our dataflow model of the clock recovery application. For the experiments in this chapter, we use a relatively simple, sequential (single-processor) schedule since the main objective in this chapter is to validate and study functional properties of the proposed clock recovery system. Applying the developed dataflow model to derive fast implementations (with correspondingly fast schedules) is a useful direction for future work that builds naturally on the developments of this chapter.

The specific schedule that we used in our experiments is

$$SRC~(W_s~DVL)~STR~FSM~TRT~RE~RRE~LFT~PHS$$

$DBS~DAS$

where the parenthesized term  $(W_s \ DVL)$  represents a schedule loop that executes actor DVL a number of times in succession that is determined by the window size  $W_s$ . In addition to providing a simple execution pattern that is suitable for rapid prototyping, this schedule is efficient in terms of buffer memory requirements —

i.e., the amount of memory required to implement the dataflow graph edges. This buffering efficiency is useful for our computations because our experiments involve input signals that contain large numbers of samples (in the range of  $10^7$  to  $10^9$  samples in each experiment).

#### 3.3 Results

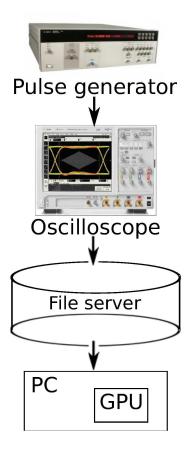

The above dataflow implementation was tested using actual measured data acquired and processed using the apparatus in Figure 3.3. Two waveforms were used for testing. One is the signal used in [20] to test a GPU implementation of the swallow and wallow algorithm for the present measurement. That waveform comprises approximately  $1.6 \times 10^7$  samples of a pseudo-random binary (PRBS) signal. The first few thousand samples of that signal are shown in Figure. 3.1. That waveform was chosen for testing because the outputs of the dataflow method, especially the corrected clock period and phase, could be directly compared with those obtained by the previous swallow and wallow implementation in [20].

A second PRBS waveform comprising approximately  $2 \times 10^9$  samples was used to test that dataflow implementation's ability to operate on waveforms too large to process in memory all at once. The proposed method produced the expected results.

As was discussed in the introduction, a difficulty of modifying a swallow and wallow measurement algorithm into a dataflow on is the presence in the original algorithm of intermediate measurement results that depend on the entire acquired waveform. In the dataflow algorithm such intermediate measurement results can

only depend on the prefix of the waveform that has previously been processed. Thus, these intermediate measurement results in the dataflow method can only approximate those of the swallow and wallow method. The question therefore arises as to whether this approximation is sufficiently good or whether it negatively influences the accuracy of the final measurements.

Here, in the swallow and wallow algorithm percentile levels of all the sample voltages are used to compute the low, medium, and high voltage thresholds used to determine the locations of the state transitions. In the dataflow method this is done in the actor DVL. In that actor, two different methods were tried to obtain the thresholds. One was to use the voltages of the first window to compute the thresholds and then use those thresholds for all succeeding windows. The second approach was to re-compute the thresholds for each window. In order to investigate the sensitivity of the measurement results to the choice between these methods, processing of the measured signals was done twice, one using each of these methods.

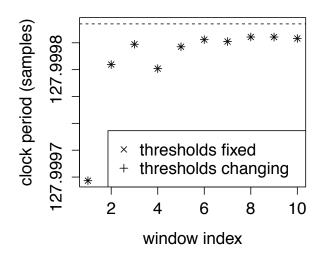

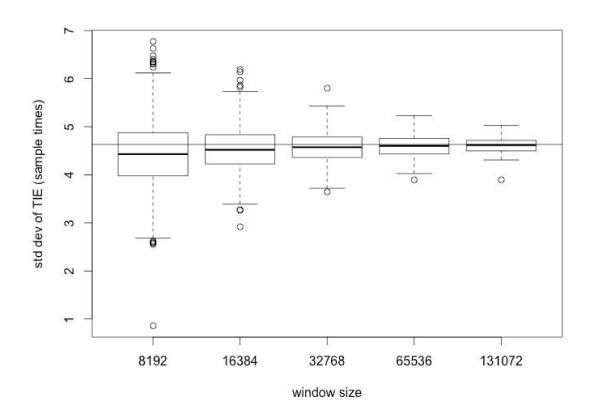

The result of using the proposed method with 10 windows on the signal with  $1.6 \times 10^7$  samples is shown in Figure 3.4 and Figure 3.5. Figure 3.4 shows evolution of the measured value of the clock period from the waveform with  $1.6 \times 10^7$  samples. Its beginning is shown in Figure 3.1. The dashed, horizontal line in Figure 3.4 indicates the clock period measured in [20] as a reference for accuracy comparison.

Figure 3.5 demonstrates evolution of the measured value of clock phase offset from the waveform with  $1.6 \times 10^7$  samples using the same input data as in Figure 3.4. The dashed, horizontal line in Figure 3.5 shows the phase offset found in [20]. Both Figure 3.4 and Figure 3.5 compare results with the results reported in [20].

Clock recovery was not sensitive to whether or not the voltage thresholds were fixed or varied according to each window's voltage statistics. Both the clock period and phase offset converge toward the values obtained from the swallow and wallow algorithm, as was desired. The final measurements from the dataflow algorithm are not identical to those obtained by the swallow and wallow algorithm. Some difference is expected because the two methods use slightly different voltage thresholds and perform the final correction by linear fitting using different time interval errors. However, the final clock periods and phase offsets produced by the two methods have absolute relative differences of under  $1 \times 10^{-8}$  samples per clock cycle and  $1 \times 10^{-2}$  samples, respectively.

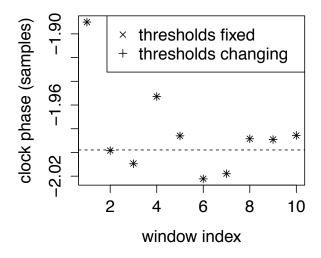

Figure 3.6 is a scatter plot matrix [31] that shows the correlations of the time interval errors (TIEs) measured using each of the two tested variants of the proposed method and the method of [20]. Here, we index the three different methods under investigation as 1, 2, 3. Index 1 corresponds to TIEs obtained using the method of [20] (labeled "SW"). Index 2 represents TIEs obtained using the proposed method with voltage thresholds fixed ("DF (fixed thresh)"). Index 3 represents TIEs obtained using the proposed method with flexible thresholds ("DF (flexible thresh)"). For each  $i \neq j$ , the subfigure of Figure 3.6 in row i and column j shows the correlation of TIEs measured using the methods with indices i and j. All axes in the subfigures show time, as a multiple of the sample time of the measured signal.

Both of the proposed methods increase the measurement uncertainty of the TIE by 0.39 sample times over the prior method. This increase is less than the inherent timing accuracy of the measurements, which is one sample time. However,

Figure 3.3: Measurement apparatus used to verify the proposed method

there is no discernible difference in the added uncertainty between the two variants of the proposed method.

To quantify further this added uncertainty, the key metric of jitter, the jitter standard deviation (that is, the standard deviation of the TIE), was computed for the three methods (Table 3.2). The absolute relative error between each of the two variants of the proposed method and the prior method are also tabulated there. Both variants of the proposed method increase the measured jitter standard deviation by roughly 0.1 sample or well under one percent. Thus, a small amount of additional measurement error is added in order to remove the restriction that the entire waveform fit into memory.

Figure 3.4: Recovered clock period in different windows.

Figure 3.5: Clock phase in different windows.

Figure 3.6: Scatter plot matrix for correlation of TIEs using different methods.

Table 3.2: Obtained jitter standard deviation, by method

| Method                      | TIE standard deviation | Absolute relative error |  |  |

|-----------------------------|------------------------|-------------------------|--|--|

| Method of [20]              | 4.630                  | _                       |  |  |

| Proposed, fixed threshold   | 4.647                  | 0.00378                 |  |  |

| Proposed, threshold updated | 4.646                  | 0.00351                 |  |  |

# 3.4 Summary

In this chapter, we considered the problem of transforming an algorithm for extracting the parameters (period and phase) of a fixed frequency clock from one based on computing from all available measured samples to a dataflow algorithm that can only base its results at any time on a prefix of the samples that have already been processed. One novel contribution of this chapter is the proposed dataflow method for modeling and design of the application. This method provides a formal connection to a wide variety of dataflow-based techniques for deriving efficient implementations on high performance signal processing platforms.

Another novel contribution arises from consideration of the question: how does one tell if such a transformation has adequately been performed? That is, what results of the original and dataflow methods should be compared in order to establish that the dataflow method is approximating well the results of the original method. We propose and demonstrate that two kinds of results should be compared. Firstly, intermediate values computed in the original method on all samples and used in later computational phases should in the dataflow method converge toward the values obtained in the original algorithm. For the proposed dataflow method, these values

are the recovered clock period and phase. In the present example, these do converge. Secondly, the final measured quantities of the original and dataflow methods should differ by a small amount relative to the uncertainty of the measurement results of the original method. Here, the final measured quantity is the jitter standard deviation, which is found by either variant of the dataflow method to with about one third of a percent.

# Chapter 4: Deep Waveform Analysis with Parallelization and Constant Memory

In Chapter 3, we presented a novel jitter measurement algorithm that significantly improved measurement response time compared to previous work. The algorithm achieves its efficiency by partitioning the overall data set into windows and allowing jitter measurement results to be reported for earlier windows before later windows are received. This re-formulation of jitter measurement eliminates the swallow and wallow characteristic, and provides improved speed.

However, a memory requirement limitation still remains: the memory required (like the method of [20]) is unbounded. In other words, the memory requirement grows without bound as the size of the data set is increased. This characteristic again limits the amount of signal data that can be measured, which is problematic, for example, in measuring relatively long signals or signals with high sample rates with limited memory resources.

In this chapter, we improve the algorithm of Chapter 3 to overcome its limitation of having unbounded memory requirements. In the jitter measurement approach proposed in this chapter, the memory requirements are fixed for a given system design configuration — in particular, the memory requirements are inde-

pendent of the amount of data that is processed when the system operates. This allows processing of unbounded signal streams: the measurement system can process as much data as it receives during a given execution of the system. At the same time, the method proposed in this chapter provides significantly faster response time compared to previous work, and is capable of delivering measurement results in real time.

For design and implementation of the jitter measurement system presented in this chapter, we integrate the application of Graphics Processing Units (GPUs) [32], the Open Computing Language (OpenCL) [33], and dataflow-based modeling of signal processing systems [3]. GPUs are massively parallel processors that execute large numbers of specialized computational modules, called *kernels*, concurrently to achieve improved performance in terms of throughput and latency. OpenCL is an open standard for programming applications, and executing programs on heterogeneous computing platforms, including platforms that integrate CPU and GPU devices. Dataflow-based modeling provides representations for signal processing application design that help to formally capture high level algorithmic and computational structure in a systematic way. The structure exposed by well-designed dataflow models can help to significantly enhance the reliability and efficiency of derived implementations.

In summary, the novel contributions of this chapter are three-fold. First, we present the design and implementation of a jitter measurement system that jointly provides (a) constant-memory requirements (independent of the amount of data processed) and (b) potential for real-time response. Second, we investigate

fundamental trade-offs among accuracy, processing speed, and memory requirements in the implementation of jitter measurement systems. Third, we demonstrate the integrated application of GPU, OpenCL and dataflow technologies to address design challenges of high speed signal measurement applications.

Material described in this chapter has been published in [6].

#### 4.1 Jitter Measurement System Design

In Chapter 3, we developed dataflow modeling methods and window-based signal analysis methods to improve the efficiency of jitter measurement. In Section 4.1.1 and Section 4.1.2, we provide a brief review of these methods in the context of the objectives in this chapter. We then present the main contributions of this chapter, which enable real-time jitter measurement by (1) significantly improving response time, and (2) providing bounded memory requirements that are dependent on the window length rather than on the overall duration across which the jitter measurement is performed. We discuss novel GPU implementation techniques that we have applied to improve the efficiency of jitter measurement in these dimensions of response time and memory requirements.

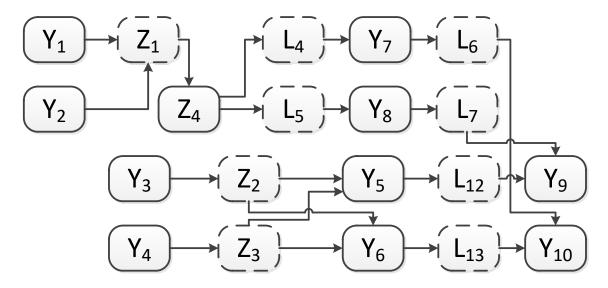

### 4.1.1 Dataflow Modeling

Our jitter measurement system design takes the form of a *computation graph* [28]. Computation graphs are similar to SDF, except that the consumption rate of a port can be different from the number of tokens from the associated input edge that

is accessed during a firing. Tokens that are accessed but not consumed during a firing remain in the associated FIFO so that they can be accessed or consumed in subsequent firings. The number of tokens that is accessed from an edge is referred to as the *threshold* for the associated actor port.

An important step in the implementation of a dataflow graph is the assignment of actors to processing resources, and the ordering of actors that share the same processor. This step is referred to as dataflow graph *scheduling*. The result of the scheduling step is a design component called a *schedule*, which is used to execute the actors in the graph. A wide variety of scheduling techniques have been developed based on specific constraints and objectives in different signal processing application areas (e.g., see [3]).

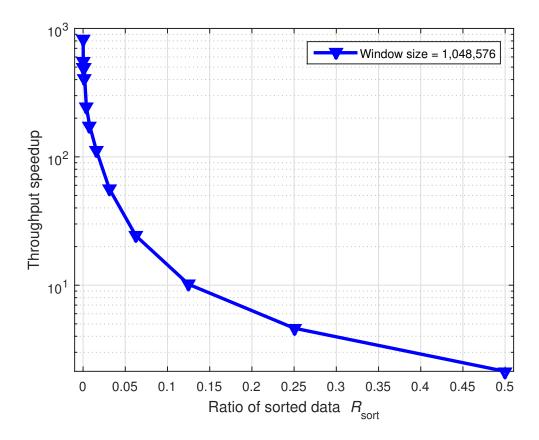

# 4.1.2 Window-based Signal Analysis

To help reduce memory requirements for jitter measurement computations on large input data sets, we have developed a windowing method that decomposes the jitter analysis process into fixed-size blocks of successive samples, where the block ("window") size  $W_s$  is relatively small compared to the size of the overall data set (see Chapter 3). The dataflow graph can then be executed repeatedly on successive windows of the input data stream. The measurement system designer can set the window size  $W_s$  to influence an underlying trade-off between jitter measurement accuracy and memory requirements. Larger window sizes generally provide increased accuracy at the expense of increased memory cost.

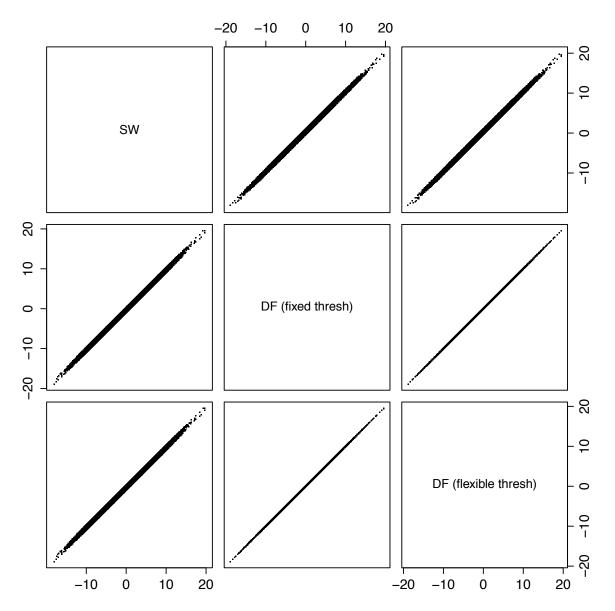

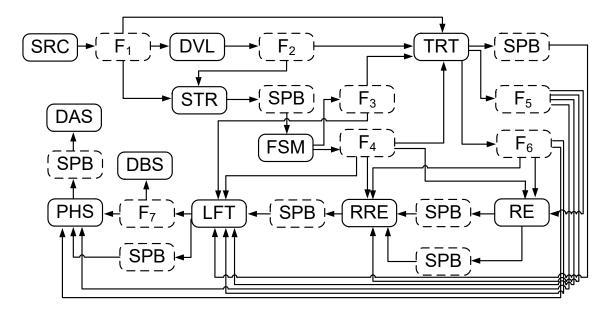

Figure 4.1: Dataflow model for real-time jitter measurement system.

# 4.1.3 System-Level Model

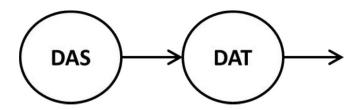

The dataflow (computation graph) model of our jitter measurement system is illustrated in Figure 4.1. We implement the individual dataflow modeling components (actors and edges) in OpenCL. Details on these implementations are discussed below. The integers next to the actor ports represent the production and consumption rates associated with the ports. For all input ports except one (the input port of the DVL actor), the consumption rate and threshold are equal, so they are not shown separately. The dataflow behavior of the input port of the DVL actor is represented by the parameter pair  $[c, \tau]$ , where c is the consumption rate and  $\tau$  is the threshold of the port. The parameter  $\tau$  is the window size for the actor, and satisfies  $\tau \geq c$ .

#### 4.1.3.1 Actor Descriptions

Here, we briefly summarize selected actors that are employed in Figure 4.1. The actors summarized here are those whose implementations have changed (compared to the system presented in Chapter 3) due to our use of a GPU for the new measurement system.