**ABSTRACT**

Title of dissertation: INTEGRATED SINGLE-PHOTON SENSING

AND PROCESSING PLATFORM IN

STANDARD CMOS

Babak Nouri, Doctor of Philosophy, 2013

Dissertation Advisor: Dr. Pamela Abshire

Electrical and Computer Engineering Department

Practical implementation of large SPAD-based sensor arrays in the standard CMOS process has been fraught with challenges due to the many performance trade-offs existing at both the device and the system level [1]. At the device level the performance challenge stems from the suboptimal optical characteristics associated with the standard CMOS fabrication process. The challenge at the system level is the development of monolithic readout architecture capable of supporting the large volume of dynamic traffic, associated with multiple single-photon pixels, without limiting the dynamic range and throughput of the sensor.

Due to trade-offs in both functionality and performance, no general solution currently exists for an integrated single-photon sensor in standard CMOS single photon sensing and multi-photon resolution. The research described herein is directed towards the development of a versatile high performance integrated SPAD sensor in the standard CMOS process.

Towards this purpose a SPAD device with elongated junction geometry and a perimeter field gate that features a large detection area and a highly reduced dark noise has been presented and characterized. Additionally, a novel front-end system for optimizing the dynamic range and after-pulsing noise of the pixel has been developed. The pixel is also equipped with an output interface with an adjustable pulse width response. In order to further enhance the effective dynamic range of the pixel a theoretical model for accurate dead time related loss compensation has been developed and verified.

This thesis also introduces a new paradigm for electrical generation and encoding of the SPAD array response that supports fully digital operation at the pixel level while enabling dynamic discrete time amplitude encoding of the array response. Thus offering a first ever system solution to simultaneously exploit both the dynamic nature and the digital profile of the SPAD response. The array interface, comprising of multiple digital inputs capacitively coupled onto a shared quasi-floating sense node, in conjunction with the integrated digital decoding and readout electronics represents the first ever solid state single-photon sensor capable of both photon counting and photon number resolution. The viability of the readout architecture is demonstrated through simulations and preliminary proof of concept measurements.

.

# INTEGRATED SINGLE-PHOTON SENSING AND PROCESSING PLATFORM IN STANDARD CMOS

By

#### Babak Nouri

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment

Of the requirements for the degree of

Doctor of Philosophy

2013

Advisory Committee: Professor Pamela Abshire, Chair/Advisor Professor Neil Goldsman Professor Timothy Horiuchi Professor Marty Peckerar Professor Isabel Lloyd © Copyright by Babak Nouri 2013

## **Table of Contents**

| List of Figures                           | V                                                |

|-------------------------------------------|--------------------------------------------------|

| Chanter 1: Rackground & Overv             | ew1                                              |

| -                                         |                                                  |

|                                           | Photon Detection Technologies                    |

|                                           | 8                                                |

|                                           | Area Vs Performance8                             |

| _                                         |                                                  |

|                                           | - Readout Challenge                              |

| •                                         | mager Array                                      |

|                                           | etector                                          |

| •                                         | eture                                            |

| • •                                       |                                                  |

| e <b>.</b>                                | ation                                            |

|                                           |                                                  |

| 1.9 Significance to the Scientific F      | ield20                                           |

| <b>Chapter 2: Performance Oriented</b>    | <b>Device Design</b> – A Modified p-n Junction21 |

| 2.1 CMOS SPADs                            | 21                                               |

| 2.1.1 Gain Uniformity – Full PE           | B Suppression24                                  |

| 2.1.2 Noise – DCR Minimization            | 26                                               |

| 2.1.3 Low DCR Pixel Geometry              | 30                                               |

| 2.1.4 Exprimental Results                 |                                                  |

| 2.2 Summary                               | 41                                               |

| Chapter 3: Pixel Level Performan          | ce - Front-end Electronics                       |

| 3.1 External Gating Signal – Hybri        | d Design43                                       |

| 3.2 Integrated Electronics – <i>Monol</i> | ithic Design45                                   |

|                                           | with Active Device                               |

|                                           | 48                                               |

|                                           | 56                                               |

| 3.4 System Interface - Event pulse Generator                         | 60                 |

|----------------------------------------------------------------------|--------------------|

| 3.5 Summary                                                          | 65                 |

| Chapter 4: Analytical Performance Characterization                   | 67                 |

| 4.1 Ultra-low intensity Optical Sensing – Dual Detection Paradig     | <i>m</i> 68        |

| 4.1.1 Multiple Single Shot Measurements – Photon number mo           | ode68              |

| 4.1.1.1 Detection System – Silicon PhotoMultiplier (SiPM)            | 69                 |

| 4.1.1.2 SiPM Non-linearity characterization                          | 69                 |

| 4.1.2 Continuous Measurement – Photon Counting Mode                  | 71                 |

| 4.1.2.1 Detection System – Digital SPAD Array                        | 72                 |

| 4.1.2.2 Non-linearity characterization                               | 73                 |

| 4.1.3 Proposed Analytical Model – Theoretical Dead Time corn         | rection74          |

| Chapter 5: CMOS Photon-Counting Detector Array                       | 78                 |

| 5.1 Digital Readout – SPAD Image Sensor Array                        | 78                 |

| 5.1.1 Synchronous Readout – Serial Access                            | 80                 |

| 5.1.1.1 Sequential Processing and Readout - Chip Level               | 80                 |

| 5.1.1.2 Semi-Parallel Processing and Readout – Column Para           | allel81            |

| 5.1.1.3 Fully Parallel Processing with Serial Readout – In Pix       | rel81              |

| 5.1.2 Asynchronous Readout – Event Driven Access                     | 82                 |

| 5.1.3 Inherent Limitations of Digital Readout                        | 84                 |

| 5.1.3.1 Architectural Trade-Offs – Application Specific Design       | gn84               |

| 5.1.3.2 Ineffective Parallel Pattern Detection                       | 85                 |

| 5.2 Analog Readout – The Silicon PhotoMultiplier (SiPM)              | 87                 |

| 5.2.1 Information Extraction Electronics – Associated Design T       | Fradeoffs88        |

| 5.2.1.1 Pre-amplification                                            | 88                 |

| 5.2.1.2 Pulse Shaping                                                | 90                 |

| 5.2.1.3 Signal Sampling                                              | 92                 |

| 5.2.2 Inherent Limitation of Analog Readout                          | 93                 |

| 5.2.2.1 Charge Signal as a Sub-optimal Counting Index                | 93                 |

| 5.2.2.2 Signal Amplitude Distortion – Sensitivity & Dynamic          | Range Limitation94 |

| 5.2.2.3 Signal Time-Response Distortion                              | 95                 |

| 5.2.2.4 Static Integration Window – <i>Limited Applicability No.</i> | Adaptability96     |

| 5.2.2.5 Design Complexity and Performance Trade-off                  | 97                 |

| 5.3 Digital SiPM – Displaced Complexity                              | 100                |

| 5.4 General Summary and Critique of the Existing Readout Paradigm   | 101 |

|---------------------------------------------------------------------|-----|

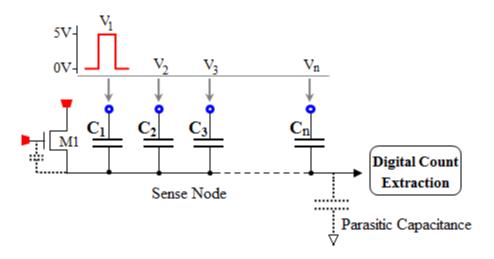

| 5.5 Proposed Readout Architecture – A New Encoding Paradigm         | 103 |

| 5.5.1 Discrete-Time Representation of Digital Data                  | 103 |

| 5.5.1 Quantized Detector Response – Performance Aspects             | 109 |

| 5.5.2 Adjustable Measurement Window – Utility Aspect                | 110 |

| 5.6 Summary                                                         | 112 |

| Chapter 6: Fully Integrated Asynchronous Digital Decoding System    | 113 |

| 6.1 System Architecture Overview                                    | 113 |

| 6.2 System Electronics                                              | 118 |

| 6.2.1 High Speed Comparator                                         | 118 |

| 6.2.2 Discrete-Signal Pulse Adder (DSPA)                            | 125 |

| 6.2.3 SPAD Signal Path Configuration                                | 128 |

| 6.2.4 Highly Compact Digital Counter with Dynamic Readout and Reset | 134 |

| 6.3 Integrated Readout System                                       | 137 |

| 6.3.1 Experimental Results – Proof Of Concept                       | 140 |

| 6.4 Summary                                                         | 145 |

| Chapter 7: Conclusion                                               |     |

| Appendix A: SPAD Device Modeling1                                   |     |

| Ribliography                                                        | 160 |

# List of Figures

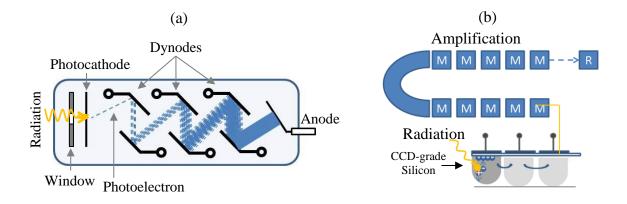

| 1.1 | (a) Structure of a PMT, the resistive divider circuit distributes the optimum voltage to each node to induce the charge acceleration required for impact ionization. (b) EMCCD structure consisting of the CCD part and electron multiplying readout component                                                                                                                                                                                                                                                                                      |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

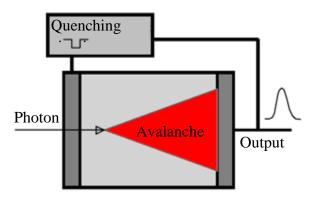

| 1.2 | SPAD pixel consisting of the above breakdown biased pn junction coupled to a quenching circuit for active control of the avalanche process                                                                                                                                                                                                                                                                                                                                                                                                          |

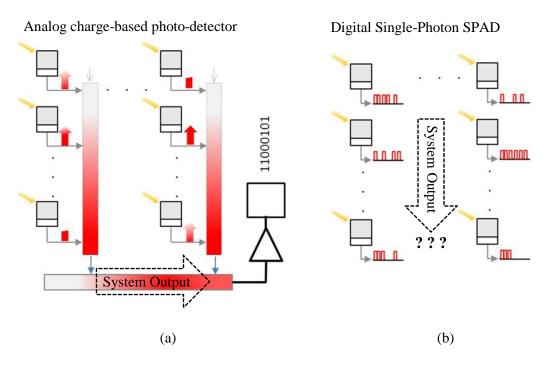

| 1.3 | (a) Photo-signal statically stored in the pixel until it is sequentially readout and processed during the readout cycle. (b) Photo-signal must be dynamically processed in real time with each photon arrival making local storage difficult                                                                                                                                                                                                                                                                                                        |

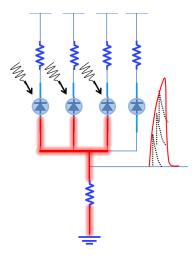

| 1.4 | Current signal summation at the common readout node of the set of parallel connected individually quenched SPAD elements forming a single SiPM macro-pixel                                                                                                                                                                                                                                                                                                                                                                                          |

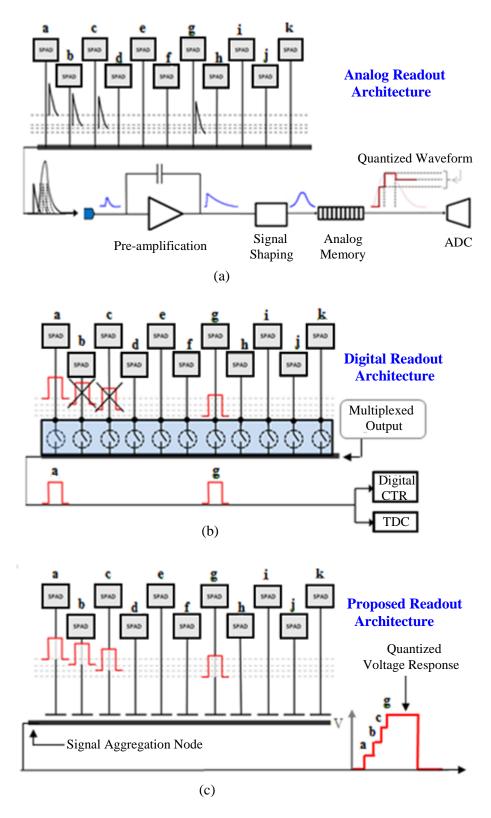

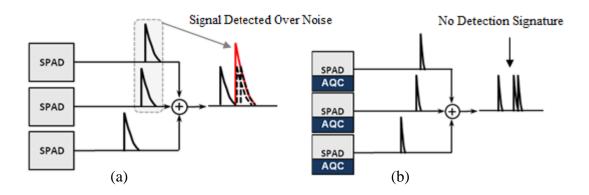

| 1.5 | (a) SiPM analog readout based on dynamic current signal summation requires complex analog readout chain. (b) Multiplexed digital readout results in loss of overlapping pulses. (c) Proposed readout based upon digital readout at the pixel level and dynamic voltage division at the readout interface                                                                                                                                                                                                                                            |

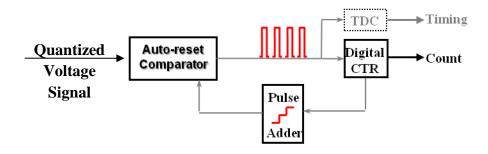

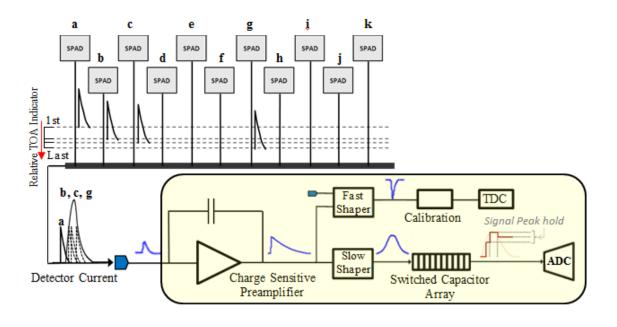

| 1.6 | Signal processing system for the SPAD sensor array interface of Fig. 1.5 c                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

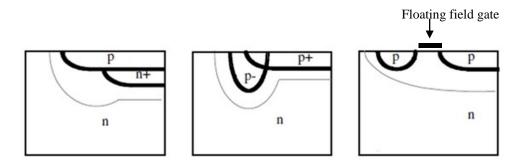

| 2.1 | Different methods of isolating the high field region. (a) Center Field concentration. (b) Sidewall-Edge isolation (c) Low dope p adjacent ring                                                                                                                                                                                                                                                                                                                                                                                                      |

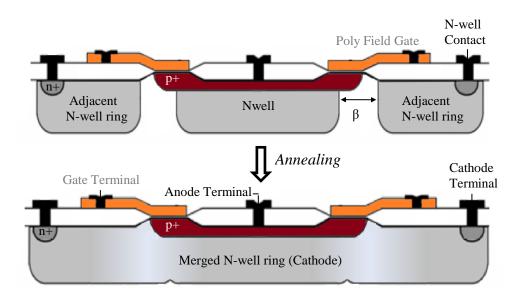

| 2.2 | Formation of the diffused guard ring during the annealing process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

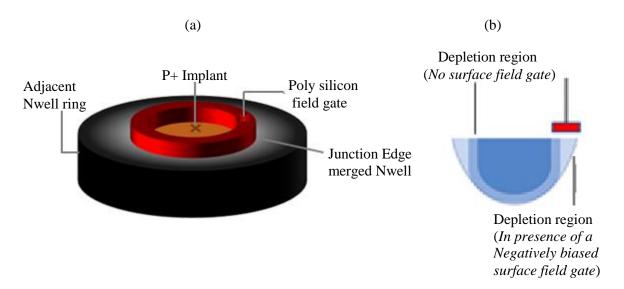

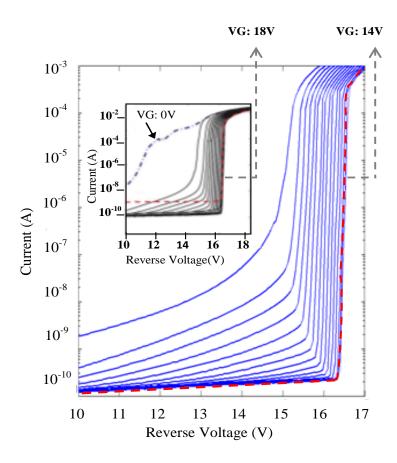

| 2.3 | (a) Drawn layout of the device demonstrating the adjacent n-well ring that will form the diffused ring about the p-n junction and the surface field gate. (b) Cross-sectional view after implant diffusion fabrication process. (c) Three dimensional view of the device illustrating its ring-like structure. (d) Conceptual illustration of the control gate effect in altering the shape of the depletion region around the junction perimeter and modulating the local electric field intensity at the surface and along the curved junction 27 |

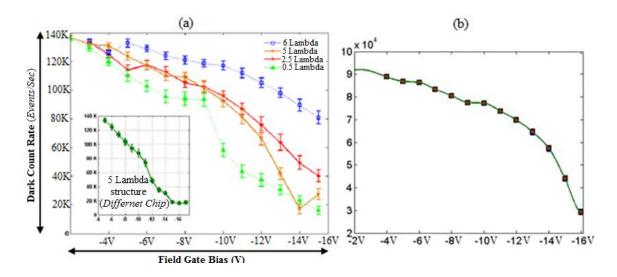

| 2.4 | (a) Measurement of DCR for various gate bias values. The data was recorded for 3 different SPAD structures. In all cases, the DCR was observed to drop substantially with increasing the negative bias of the gate terminal. At starting voltage as low as -4V the effect of the gate becomes dominant over the diffusion ring. (b) DCR measured as a function of the field gate bias for the SPAD structure with $5\lambda$ ring gap from a separate die.                                                                                          |

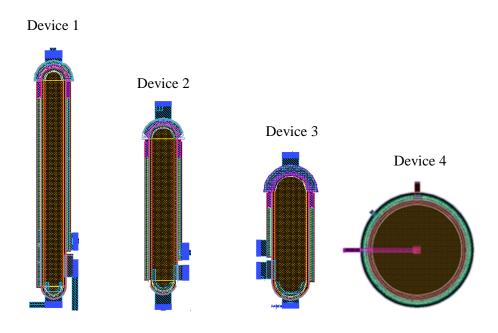

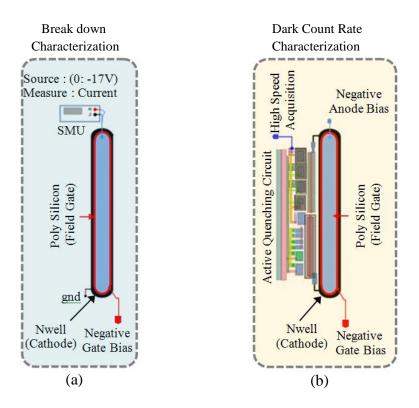

| 2.5 | New SPAD pixel design utilizing special geometry to minimize defect density. (a) SPAD unit with in-pixel active quenching electronics for DCR characterization. (b) Stand-alone SPAD unit for breakdown characterization—active front-end electronics 33                                                                                                                                                                                                                                                                                            |

| 2.6 | (a) Device 5 represents the largest perimeter to area ratio, expected to produce the best DCR characteristics. (b) Device 8 represents an intermediate perimeter to area ratio. (c) Standard circular design. (d) The breakdown voltage as a function of the gate bias is measured. Device 5 and 8 show similar breakdown characteristics in terms of magnitude and rate of change of the breakdown voltage with respect to the fate bias value. The performance is superior to that of the circular SPAD in terms of both the magnitude and the rate of change. (e) The I-V characteristics for device 8 is compared to that of the circular device whose I-V characteristics appear as an inset | 34   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

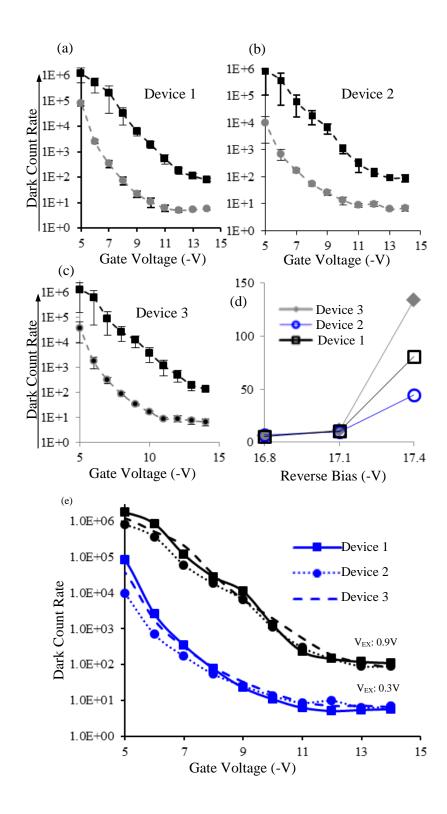

| 2.7 | Red trace represents the graph of DCR as a function of gate voltage for Device 11 measured at 3 different reverse bias values. The Blue trace represents the same for Device 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 35 |

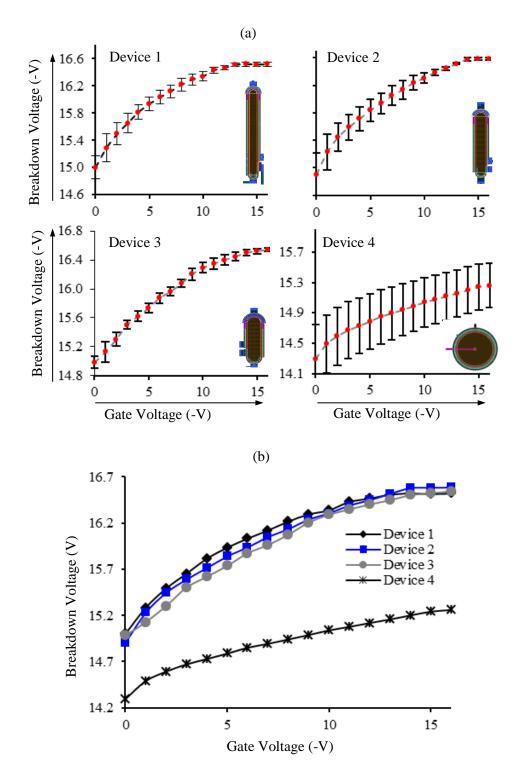

| 2.8 | Mean breakdown voltage as a function of the perimeter field gate bias measured for devices 1, 2 and 3 representing the high gettering efficiency structures and device 4 representing the round SPAD structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .36  |

| 2.9 | Measured DCR as a function of the perimeter field gate bias for devices 1, 2, and 3 operated at two different excess bias levels (0.3V and 0.9V). (d) DCR vs. device reverse bias at -14V field gate bias. (e) DCR vs. perimeter field gate bias for devices 1, 2, and 3 at excess bias of 0.3V and 0.9V.                                                                                                                                                                                                                                                                                                                                                                                         | .40  |

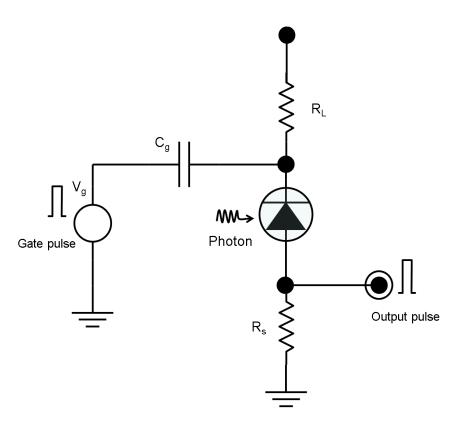

| 3.1 | Schematic of Passive-quenched SPAD in gated-mode operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 44 |

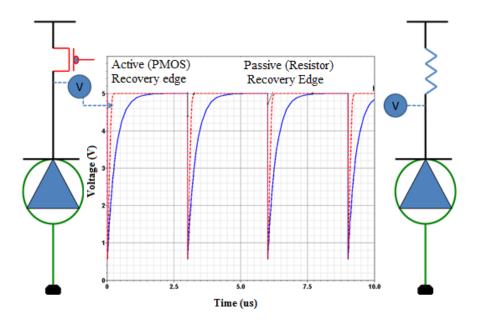

| 3.2 | Red dotted waveform represents the Cathode voltage during normal avalanching operation of PMOS quenched model. Blue waveform is the cathode voltage of resistor quenched model. Recharge time of 220 ns is achieved with the PMOS component compared to 1.67 µs achieved with a ballast resistor of minimum size for complete quenching. Total SPAD capacitance was set to 3pF                                                                                                                                                                                                                                                                                                                    | . 47 |

| 3.3 | The dashed waveform represents the cathode terminal voltage during normal avalanching operation of PMOS quenched model. Solid waveform represents the cathode terminal voltage of the resistor quenched model. Recharging time of 220 ns is achieved with the PMOS component compared to 1.67 µs achieved with the ballast resistor of minimum size. The total SPAD capacitance was set to 3 pF in the simulation model                                                                                                                                                                                                                                                                           | . 48 |

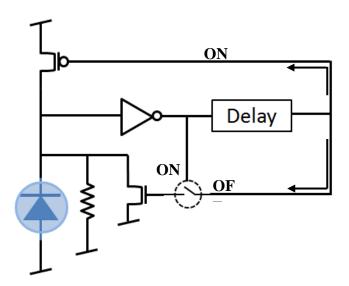

| 3.4 | Input stage of the Active Q/R (Control) circuit ,Sfeedback switch ensure exclusive charging (Sreset) and quenching (Squench) operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 49 |

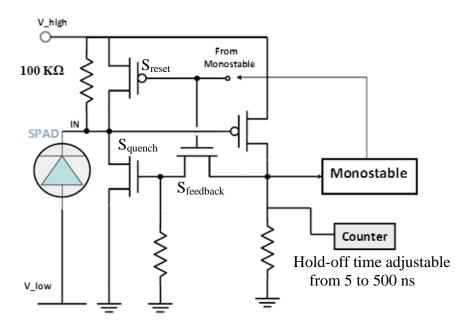

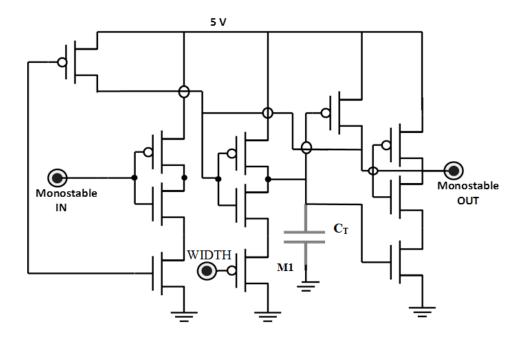

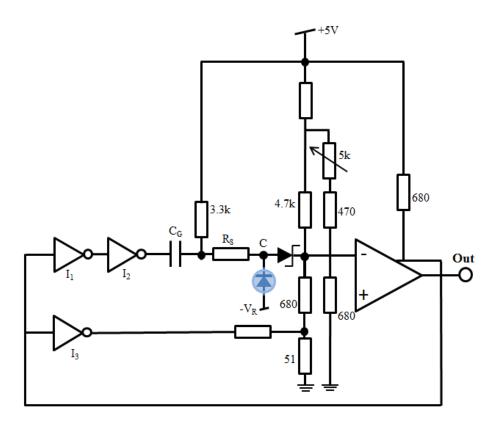

| 3.5 | circuit diagram of a basic hold-off time generating monostable circuit. This monostable circuit is able to set a delay time of 500ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 50 |

| 3.6 | Schematic drawing of variable load AQC. Transistor Ms, provides initial quenching through operation mode shift from triode to saturation; full quenching by cutting of the Avalanche current when I2 goes low; Recovery through discharge of Anode capacitance CA when I2 goes high                                                                                                                                                                                                                                                                                                                                                                                                               | 53   |

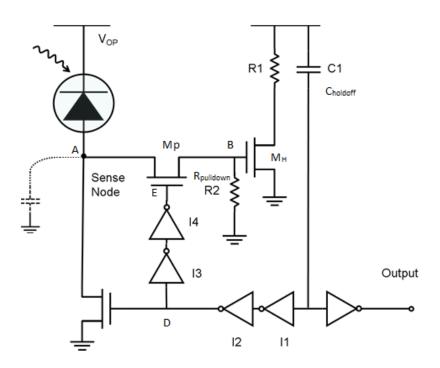

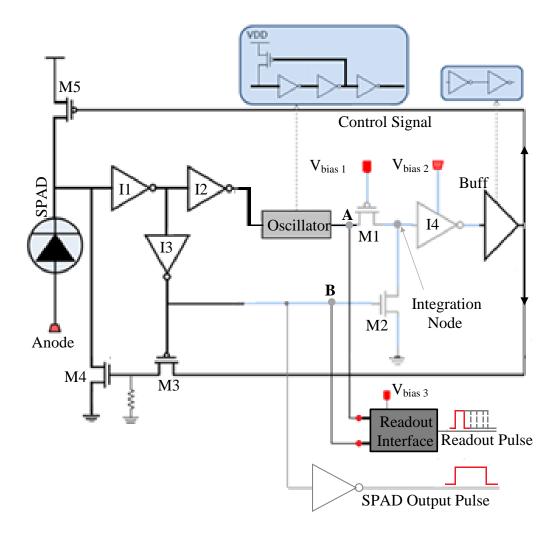

| 3.7  | System schematics. Control signal for adjusting the hold off time and the readout pulse width are shown as grey shaded terminals                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

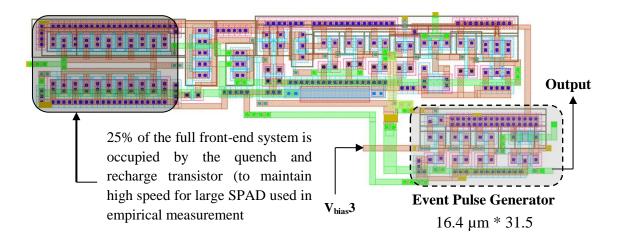

| 3.8  | Layout of the active quenching circuit. Third of the area is taken up by the two transistors used as Quench and Recharge switches. The large size is charging and discharging                                                                         |

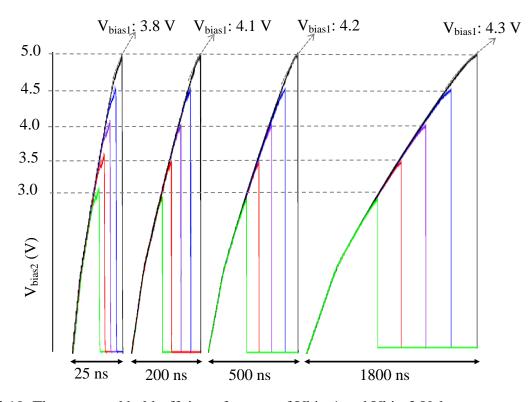

| 3.9  | Post-layout simulated waveform representing the transient voltage at the integration node for different slew rate and amplitude threshold levels determined by Vbias1 and Vbias2 values respectively                                                  |

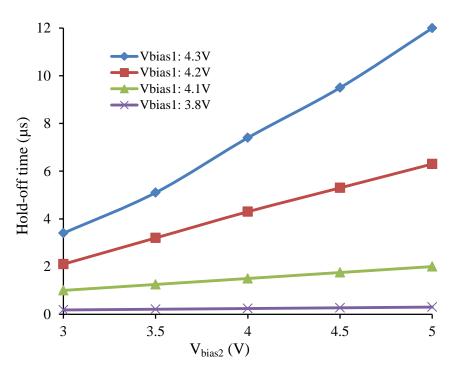

| 3.10 | The measured hold-off times for a set of Vbias1 and Vbias2 Values                                                                                                                                                                                     |

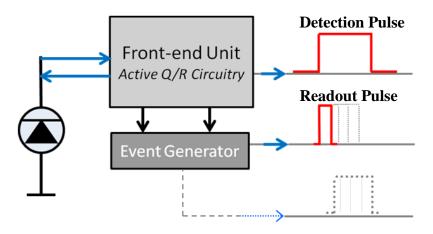

| 3.11 | Block diagram showing the relationship between the detection and the readout pulse 62                                                                                                                                                                 |

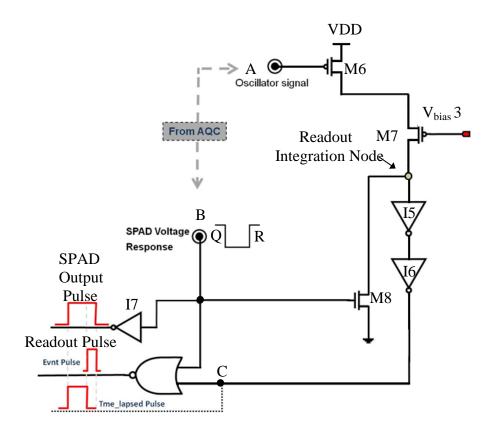

| 3.12 | 2 Readout interface (Event generator). The leading edge of the readout pulse is simultaneous with that of the detector pulse, its trailing edge is set by propagation delay through Vbias3 if it is set to be shorter than the detection pulse period |

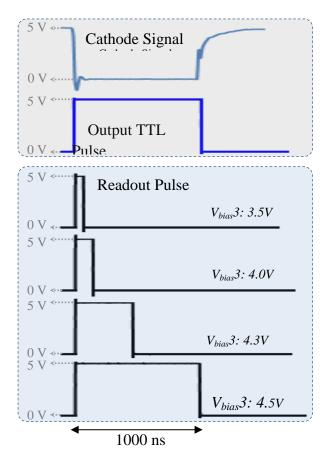

| 3.13 | 3 Experimental measurement of the readout pulse with different pulse width parameters recorded at different Vbias3 values without altering the activity pulse duration                                                                                |

| 3.14 | Layout for the front-end system integrated with each SPAD detector                                                                                                                                                                                    |

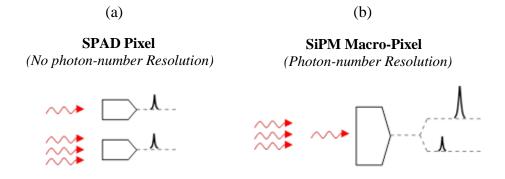

| 4.1  | (a) Multi-photon response of single-element SPAD detector is not differentiable from its single photon response. (b) SiPM macro-pixel has linearly proportional photoresponse cable of discriminating between single photon and multi photon events   |

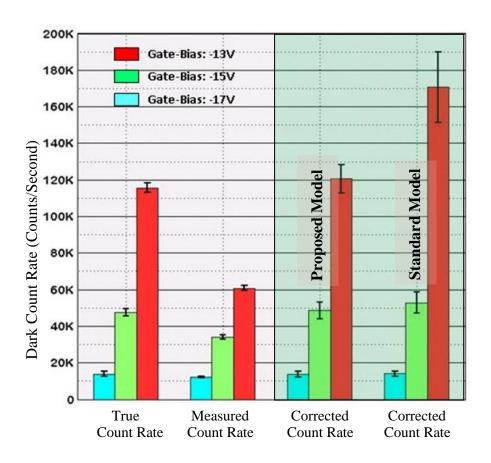

| 4.2  | Performance comparison between the proposed and the standard model                                                                                                                                                                                    |

| 5.1  | Conceptual difference in data readout requirement between standard semiconductor imagers and SPAD detector                                                                                                                                            |

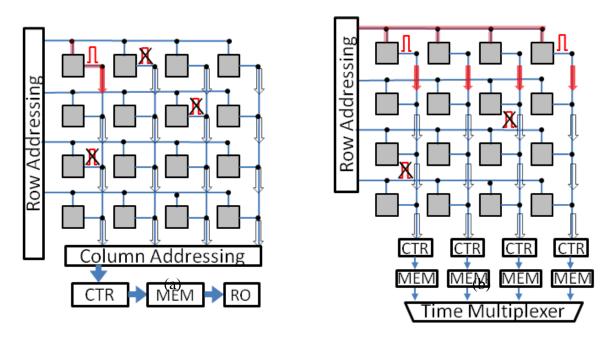

| 5.2  | (a) Sequential architecture: offers the best power and area utilization, but the worst bandwidth and detection efficiency. (b) In-Column architecture improves the readout bandwidth but degrades the fill-factor                                     |

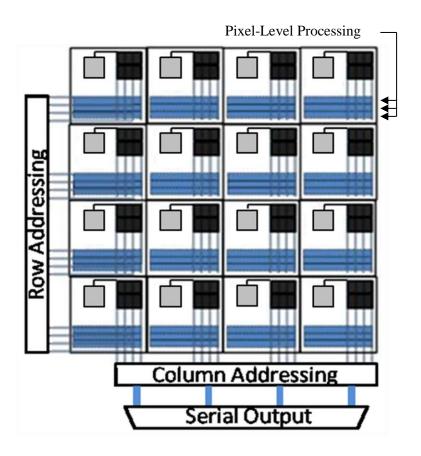

| 5.3  | Fully parallel In-pixel processing offers the best detection bandwidth but the worst fill factor performance                                                                                                                                          |

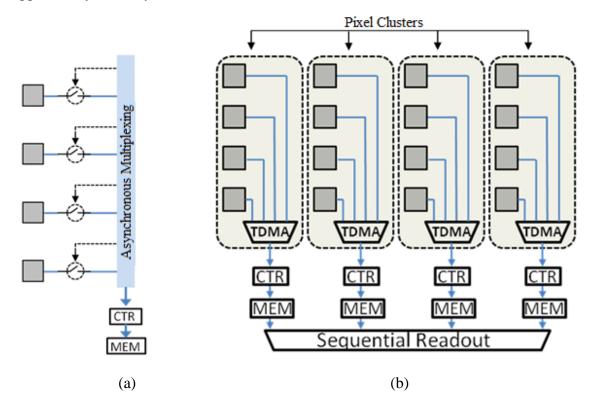

| 5.4  | (a) Collision is avoided by verifying the state on the shared medium prior to initiating access. (b) Time division Multiplexing randomizes the transmission time window of the signals converging onto a common resource                              |

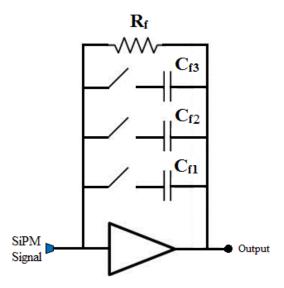

| 5.5  | Variable Gain Charge Sensitive Preamplifier                                                                                                                                                                                                           |

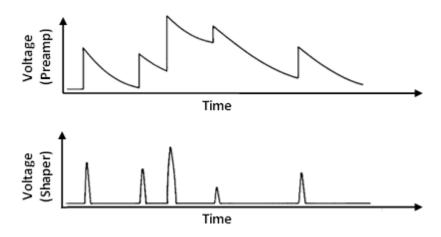

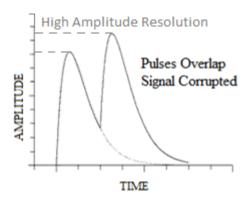

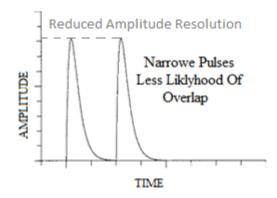

| 5.6  | The effect of pulse shaping on the output of the preamplifier91                                                                                                                                                                                       |

| 5.7  | Effect of shaping time on pulse-pair resolution of the readout system                                                                                                                                                                           | 92  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

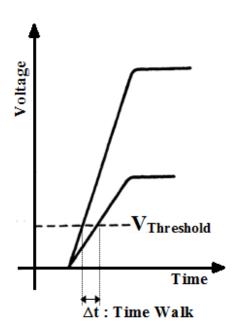

| 5.8  | Time walk effect demonstrated for two simultaneously arriving detection events with different amplitudes                                                                                                                                        | 95  |

| 5.9  | Shortening the avalanche pulse, through active quenching is highly desirable due to its enhancing effect on SNR and active range performance of the device. However such pixel-level improvements interfere with the detection criteria in SiPM | 97  |

| 5.10 | Typical Analog readout chain used in conjunction with SiPM detectors                                                                                                                                                                            | 98  |

| 5.11 | General representation of the detector readout interface                                                                                                                                                                                        | 105 |

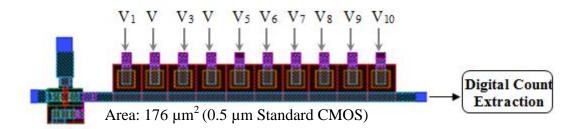

| 5.12 | 2 Compact layout structure of a ten input readout interface                                                                                                                                                                                     | 106 |

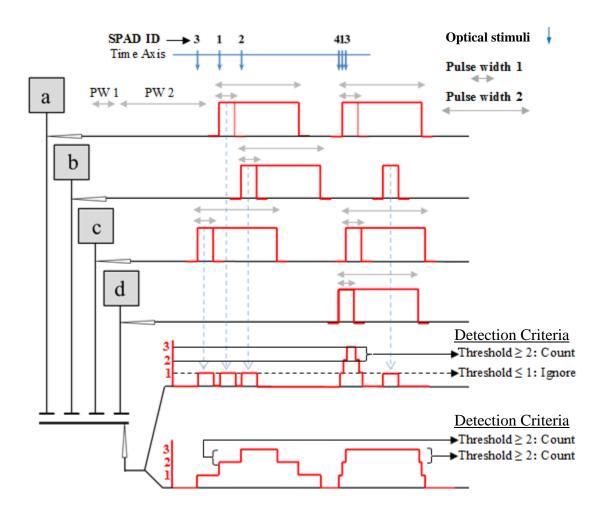

| 5.13 | Simulation results showing the response at the output port of a 4-input interface for two different input pulse widths PW1 and PW2                                                                                                              | 111 |

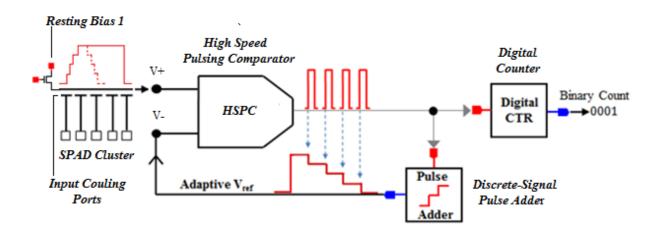

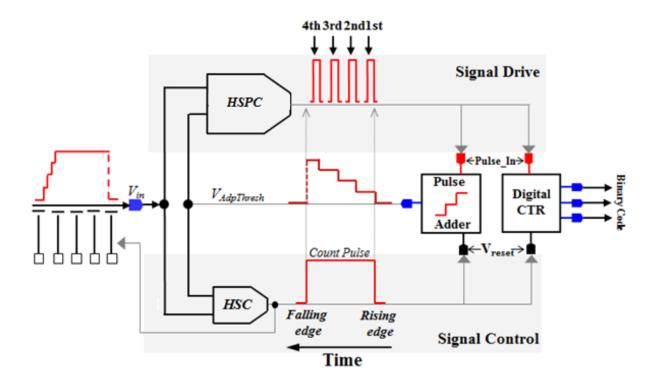

| 6.1  | Conceptual signaling block diagram of the readout system showing the primary internal signal and the operational flow of the overall system                                                                                                     | 114 |

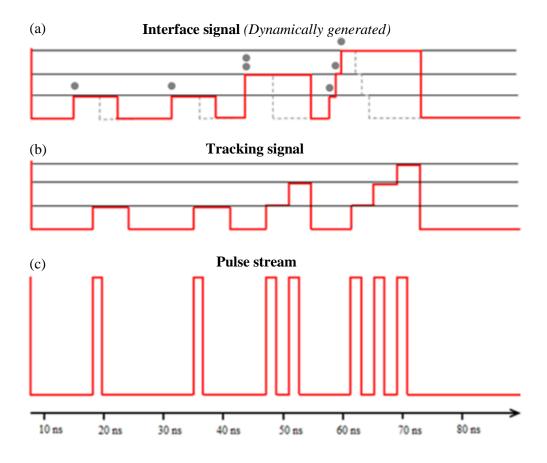

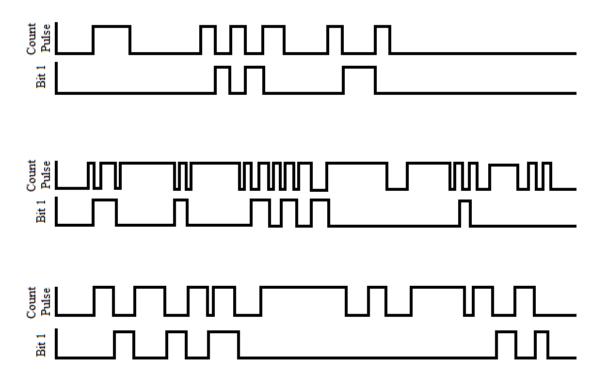

| 6.2  | Primary system internal signals. (a) Dynamic signal on the output port of the main interface. (b) Tracking signal at the output of the DSPA module. (c) Serial pulse stream.                                                                    | 117 |

| 6.3  | Conceptual block diagram of the complete readout system, featuring the drive signaling portion and the control signaling portion of the overall architecture                                                                                    | 118 |

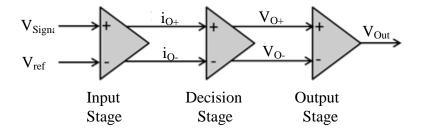

| 6.4  | Conceptual block diagram of the standard three stage high speed comparator                                                                                                                                                                      | 119 |

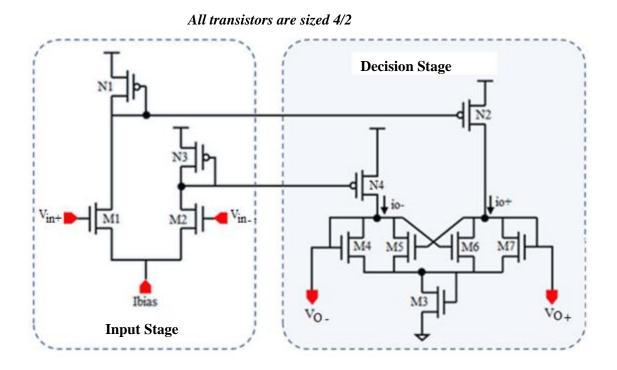

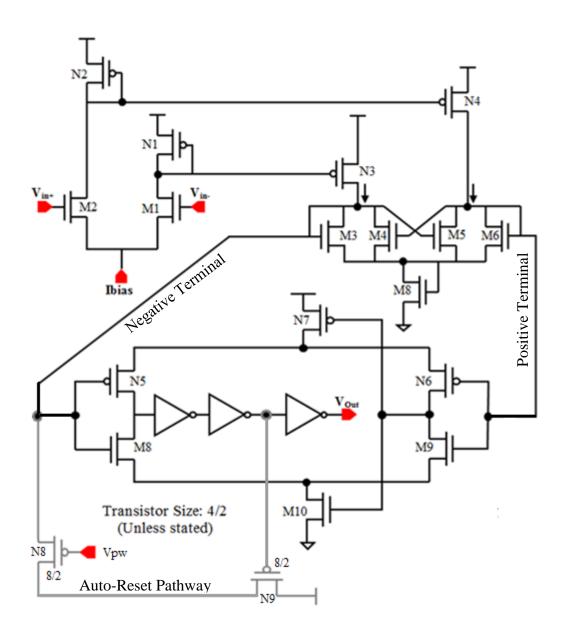

| 6.5  | Input and the decision stage of the High Speed Comparator                                                                                                                                                                                       | 119 |

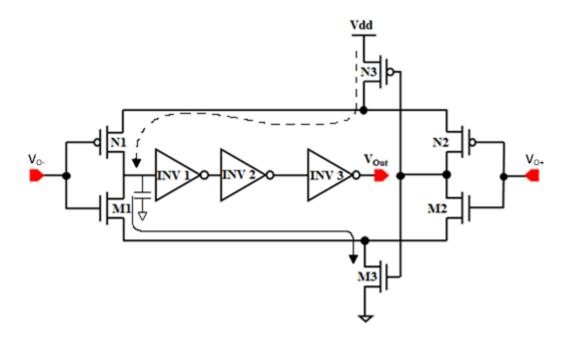

| 6.6  | Output buffer stage of the High Speed Comparator, generally deployed for slew rate improvement and generation of an output response with a digital signal profile                                                                               | 122 |

| 6.7  | Schematic diagram of the complete High Speed Comparator with the auto pulsing feature                                                                                                                                                           | 123 |

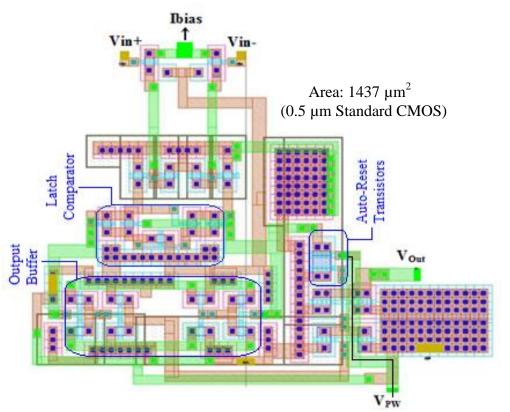

| 6.8  | Layout diagram of the High Speed Comparator, highlighting the compact electronic footprint of the module                                                                                                                                        | 124 |

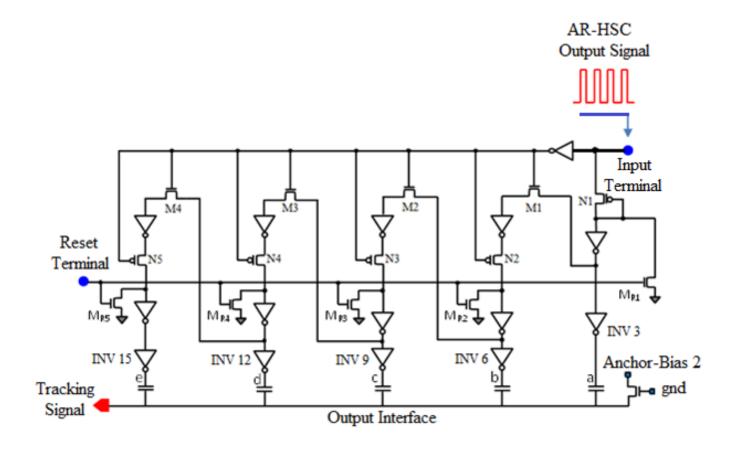

| 6.9  | Schematic diagram of the Discrete-Signal Pulse Adder                                                                                                                                                                                            | 126 |

| 6.10 | Schematic diagram of the edge-driven Discrete-Signal Pulse Adder featuring improved operational speed and a more compact structure                                                                                                              | 127 |

| 6.11 | Layout diagram of the 10-Count pulse-driven Discrete-Signal Pulse Adder                                                                                                                                                                         | 128 |

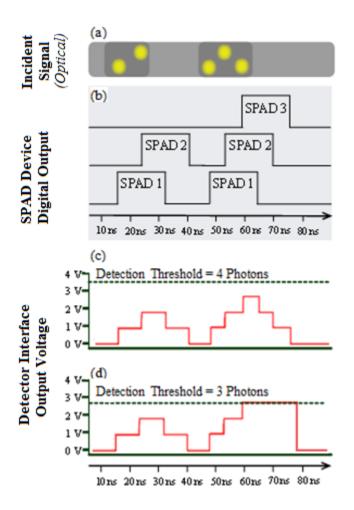

| 6.12 | Simulation of the interface signal response. (a) Optical input stimuli used for the simulation. (b) SPAD device digital output. (c) Interface response for a 4-photon detection threshold. (d) Interface response for a 3-photon detection threshold                                                                                                                                                                        | 129 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

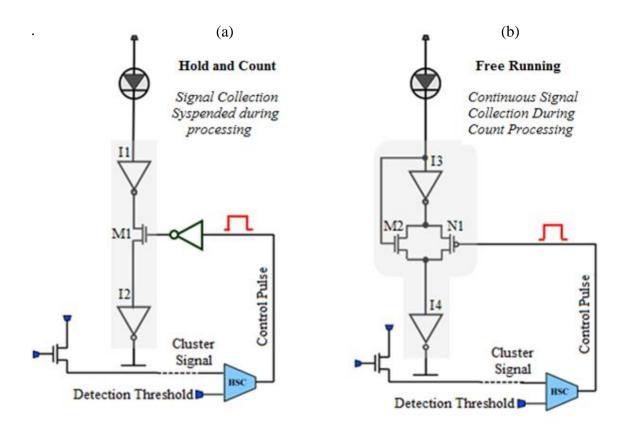

| 6.13 | SPAD Signal path electronics. (a) Hold and Count Mode electronics. (b) Free Running Mode electronics                                                                                                                                                                                                                                                                                                                        | 130 |

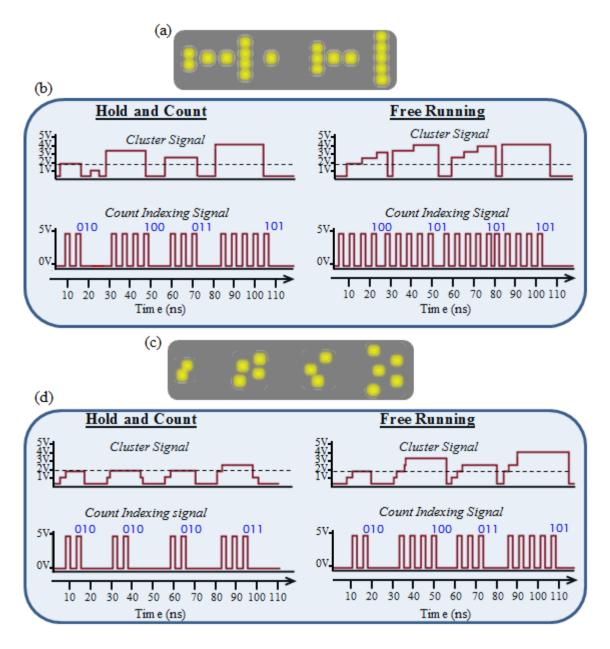

| 6.14 | Simulation results of primary internal signals. (a) Optical stimuli representing short multi-photon optical pulses. (b) Internal system response to short multi-photon stimuli profile under both signal path configuration. (c) Optical stimuli representing longer optical pulses or a continuous photon stream. (d) Internal system response to continuous optical stimuli                                               | 132 |

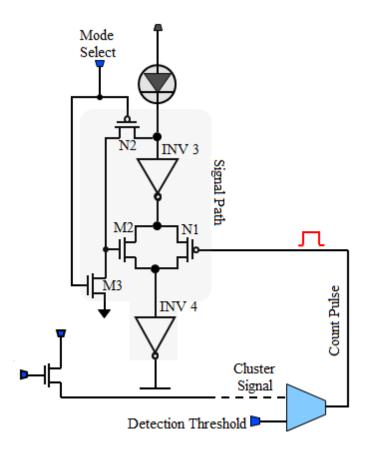

| 6.15 | The schematics for the Configurable signal path electronics                                                                                                                                                                                                                                                                                                                                                                 | 133 |

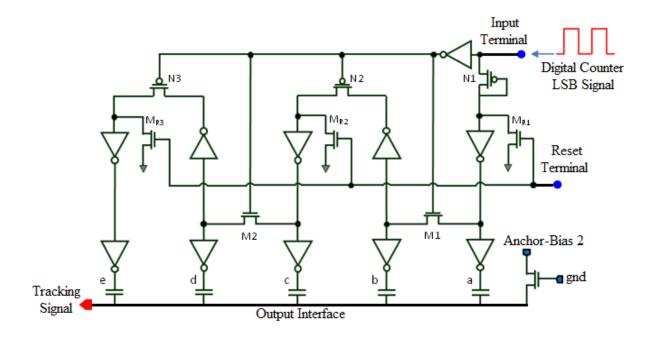

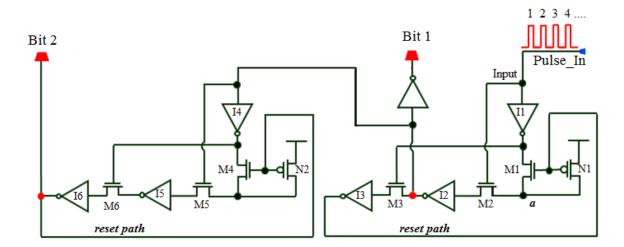

| 6.16 | Schematic diagram showing the compact structure for a 2-bit Digital counter                                                                                                                                                                                                                                                                                                                                                 | 134 |

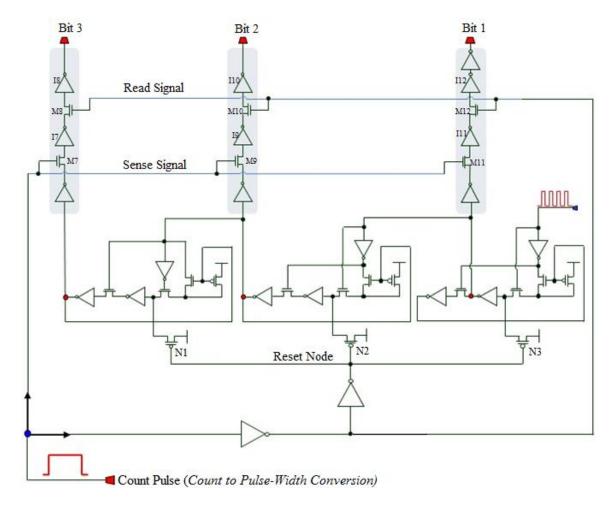

| 6.17 | Schematic diagram of the 3-bit compact digital counter with active reset                                                                                                                                                                                                                                                                                                                                                    | 136 |

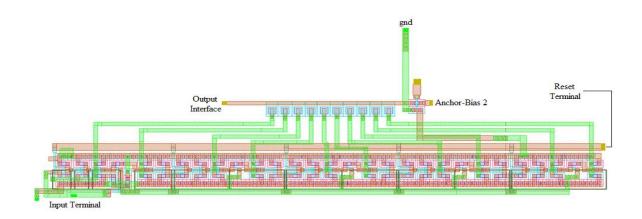

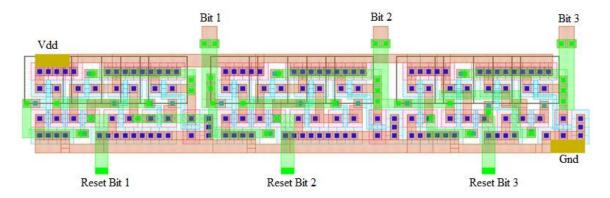

| 6.18 | Layout diagram of the 3-bit compact digital counter with active reset                                                                                                                                                                                                                                                                                                                                                       | 136 |

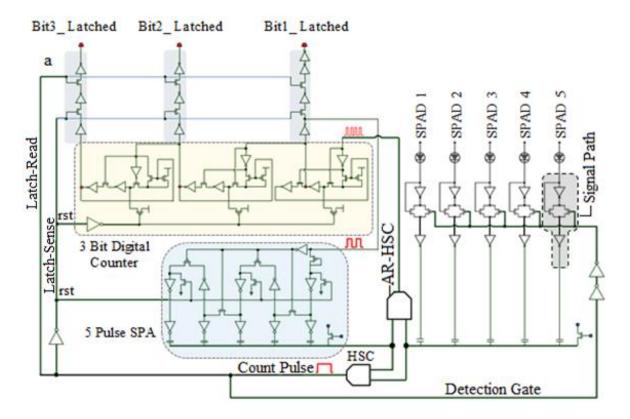

| 6.19 | The schematic diagram of the readout system using free-running architecture                                                                                                                                                                                                                                                                                                                                                 | 137 |

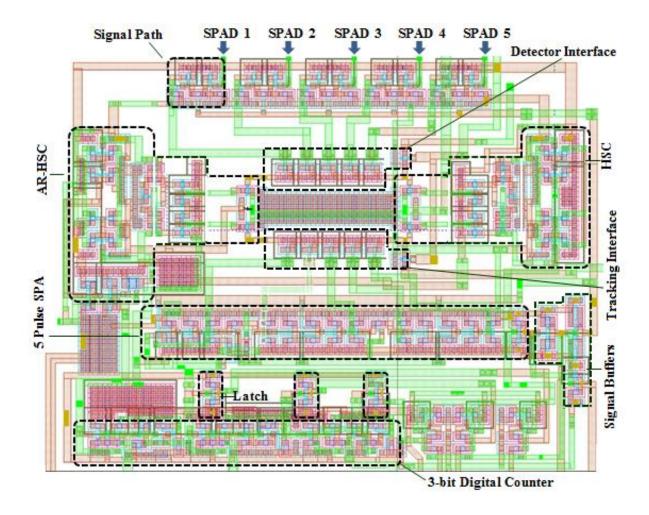

| 6.20 | Layout diagram of the full readout architecture for a 5-SPAD cluster                                                                                                                                                                                                                                                                                                                                                        | 138 |

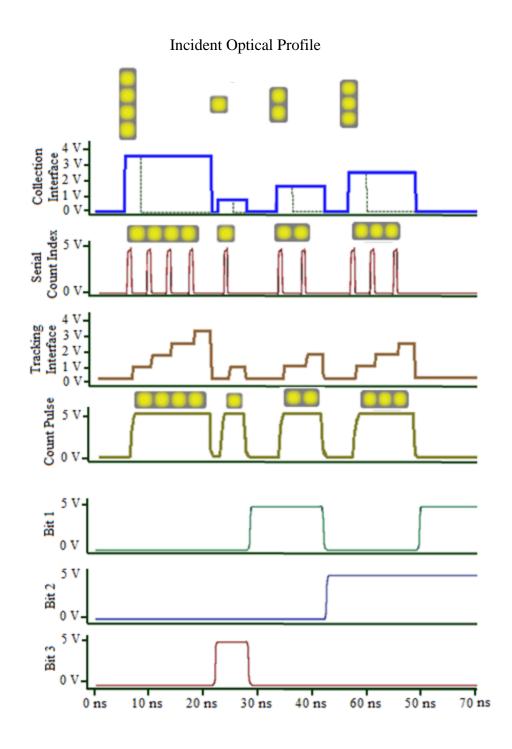

| 6.21 | Post-layout simulation results showing the primary internal and the external signals                                                                                                                                                                                                                                                                                                                                        | 139 |

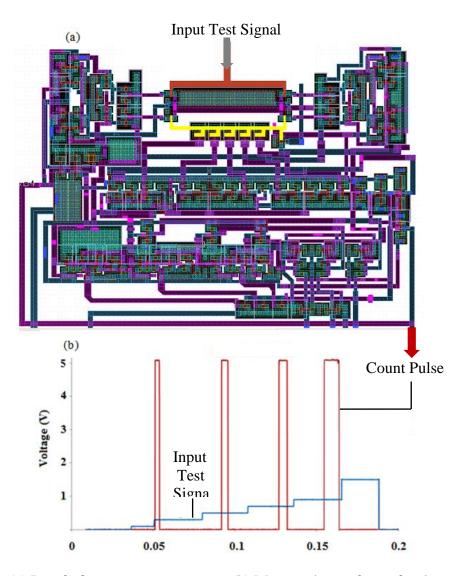

| 6.22 | (a) Proof of concept test structure. (b) Measured waveforms for the user-defined input test signal and the generated count pulse response of the test system                                                                                                                                                                                                                                                                | 140 |

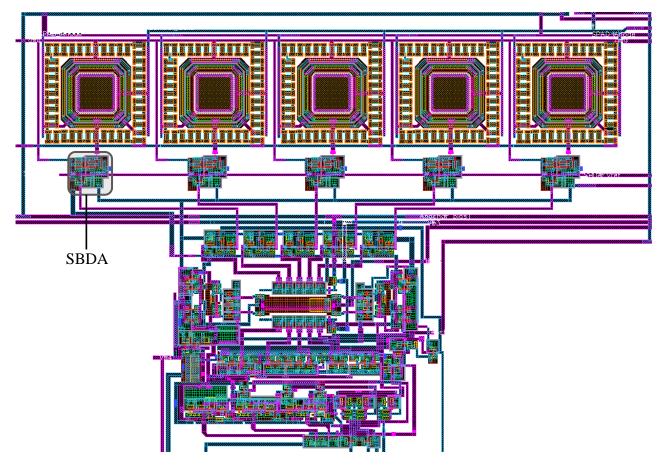

| 6.23 | Test Structure showing a full cluster system for 5 passively quenched SPADs                                                                                                                                                                                                                                                                                                                                                 | 142 |

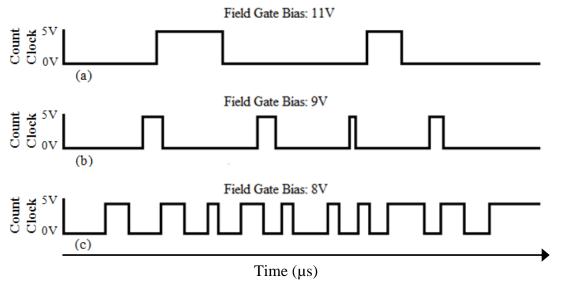

| 6.24 | Representative snapshot of Count_Clock signal captured for Proof Of Concept demonstration. (a) Count_Clock signal (cluster activity) measured at Field gate bias of 11V corresponding to low overlap probability thus resulting in fewer detection events. (b) Cluster response measured at field gate bias of 9V showing increase in detection event count. (c) Lowest gate bias leading to highest measured combined rate | 142 |

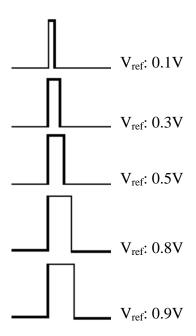

| 6.25 | Count Clock Pulse for various integration intervals determined by the value of the Vref signal                                                                                                                                                                                                                                                                                                                              | 143 |

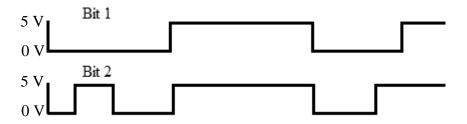

| 6.26 | Digital decoding of the pulse-width modulated Count_Clock signal for optical event measurement. Trace above shows the Least Significant Bit transition at the end of each counting cycle as implemented by the Passive cluster readout system shown in Fig. 6.22                                                                                                                                                            | 144 |

| 6.27 | Digital representation of photon count associated with an optical event, determined through simultaneous measurement of the latched Bit 1 and Bit 2 signal                                                                                                                                                                                                                                                                  | 145 |

| A.1 | SPAD device model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 153 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

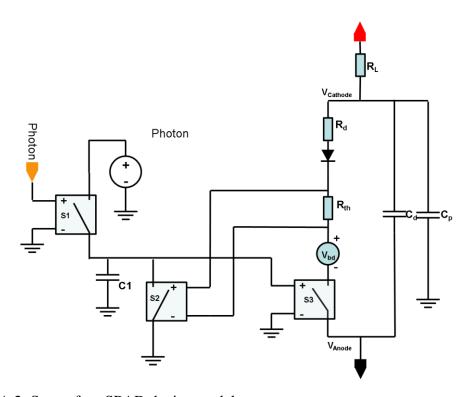

| A.2 | State of art SPAD device model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 154 |

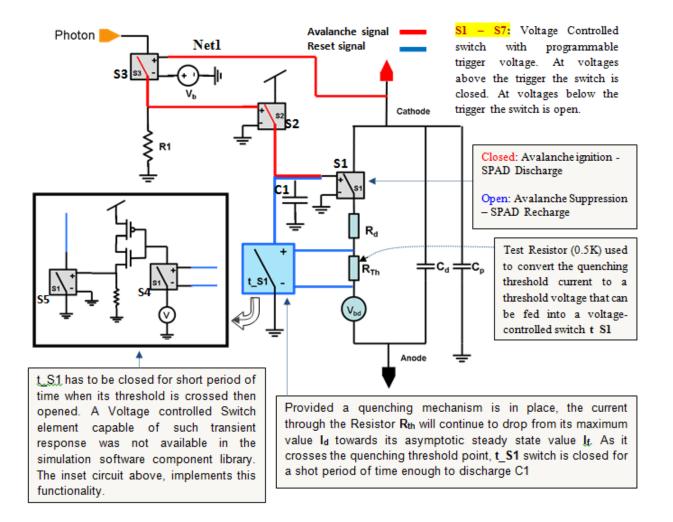

| A.3 | Proposed SPAD device model with embedded text box describing the functionality of select components. The inset shows the actual circuit implementation of t_S1 component                                                                                                                                                                                                                                                                                                                                          | 156 |

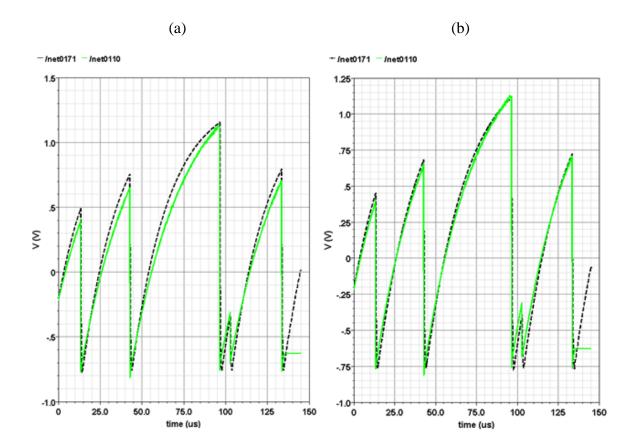

| A.4 | (a) Solid Green trace represents the measured waveform using data acquisition system. The black trace is the simulation out using the SPAD model in Figure 4.3. Depletion Capacitance was set at its quiescent value. (b) Solid green trace represents the measured waveform using data acquisition system. The black trace is the simulation out using the SPAD model in Figure 4.3. Depletion Capacitance was set to change according to the time varying SPAD terminal voltage (depletion region voltage drop) | 159 |

## Chapter 1

## **Background & Overview**

#### 1.1 Introduction

A photon is the ultimate limit of sensitivity in optical sensing. The rise of high performance single photon detectors has led to the emergence of many new scientific fields, while enabling the continued progress of many other existing ones [1-3]. The broad spectrum of applications for this technology extends from high energy particle detection at the Large Hadron Collider to DNA sequencing and gene-associated protein detection for the human genome project.

Photons are very useful as probes for medical/biomedical imaging applications. They can travel safely through tissues, interact with them and carry environmental information from the sample back to the outside world for subsequent processing and interpretation [2]. Since the amount of light emitted from micro-scale biological structures is extremely small the optical properties of biological sample can only be exploited with optical detectors of sufficient sensitivity [3]. The set of techniques that exploit the photon-based biological interactions in order to extract specific information about the biological matter is collectively defined as Bio-photonics [4-8]. Bio-photonics constitutes a major area of advanced optical imaging. Previously the only means of

observing cellular behavior was to view a frozen stained and sliced sample of the organism under a microscope. This provided no information about the active internal process of the cells and the dynamics of its interactions with the cells surrounding it [5]. Bio-photonics allows dynamic observation of biological events at the micro-scale level thus enabling real time study of biological functions at the cellular or sub-cellular levels. The granularity of such real-time observation extends to the level of a single molecule within an active cell. Ultra-sensitive optical methods are also widely utilized to identify and quantify DNA, mRNA or protein content within biological matter [6, 7].

In the clinical field, single photon sensitive imaging has enabled the study of the mechanisms involved in human health and disease at the cellular and molecular level. Optical properties of tissue such as fluorescence reveal valuable information regarding its pathology and composition [7]. The fluorescence property of biological matter is also modulated by disease-related abnormalities in the organic structure of tissues. Discerning the resulting shift in the optical properties for micro-scale biological structures would require contrast resolution on order of single photon. This marks the maximum resolution limit for optical intensity measurements.

Another major area of impact is the Imaging of extremely fast transient events such as spike-based neural signals characterized by microsecond-long action potentials travelling through neural pathways at speeds of up to 112 mph [8]. Effective imaging of such high speed phenomena requires optical detectors with a very high frame rate capability or equivalently very short integration window (small exposure time) single-photon sensitivity yields the shortest possible integration window of one photon.

Essentially the challenge for the detection system utilized in biomedical imaging application is the speed and sensitivity requirement for detection of ultra-low intensity bio-reporter signal (optical) emitted as result of bio-photonic processes [8].

LiDAR (Light Detection and Ranging) is a technology that utilizes light to probe the atmosphere in order to retrieve information about atmospheric properties such as temperature, humidity, pollution, weather pattern and the trace gases present. The detection of changes in properties of the emitted light pulse after it has interacted with the atmosphere allows for the measurement and mapping of atmospheric parameters [9]. LiDAR can also be used as Laser range finders. It can determine the distance to a remote object by detecting the reflected pulse and measuring the round trip flight time. Consideration of Cost, portability and eye safety necessitates the use of low power source for laser generation which proportionally lowers the intensity of the reflected signal. Due to the limitation of the detector active area only a small fraction of this reflected signal is captured by the detector. The low back-scattering coefficient of atmosphere also attenuates the reflected optical signal. As the result of these restrictions, LiDAR applications are critically dependent upon the ability for efficient ultrasensitive photon detection [9].

## 1.2 Assessment of Existing Single Photon Detection Technologies

The underlying process in signal detection is the electro-transduction of the incident energy signal into a representative electrical signal at the output. The function of a photo-detector is to convert the optical energy of light into an analog electrical signal whose magnitude is proportional to the incident intensity. The challenge presented

involves fast and reliable detection of ultra-faint signals. In conventional optical detectors the free carriers generated due to the absorption of incident photons are passively integrated until the resulting electrical signal exceeds the baseline noise of the external amplification and read out electronics [10]. This method is inherently ill suited to meet the stringent sensitivity and speed requirement for detection of Ultra-weak optical signals that occur on a time scale from hundreds of nanosecond to milliseconds. The detection of such signals is contingent upon the presence of an intrinsic internal amplification mechanism that is as noiseless as possible [11-13].

The gold standard in single photon detection, for the past several decades has been the PhotoMultiplier Tube (PMT). The internal amplification process in PMT occurs on time scale of tens of nanosecond. Within that time period a single photo-generated carrier pair is converted into a pulse of current which can be directly read out. However, due to their internal mechanism for signal transduction and amplification, PMTs have high power consumption (large operating voltage) and are operationally sensitive to the presence of external magnetic field. Additionally, due to their bulky packaging, they offer poor detection granularity, and are mainly used as stand-alone point detectors. Although these limitations have been partially over come through introduction of multi-anode PMT and Micro Channel Tube, these devices still fall short of meeting the growing technological demand for greater system integration and miniaturization [14]. Many applications on the cutting edge of technology such as Lab on Chip (LoC) and Micro Total Analysis System (µTAS) must deliver ultra-sensitive and high speed integrated functionality across an implementation platform capable of very high levels of miniaturization, reliability and low power operation [14, 15]. Semiconductor technology

can offer a robust implementation platform for such high performance single photon detection, provided that the speed and sensitivity performance of PMT can be realized in silicon. A basic illustration of PMT appears in Fig. 1.1a.

A modified version of the standard semiconductor CCD called Electron Multiplying CCD is capable of achieving single photon sensitivity by incorporating an amplification stage directly into the readout architecture thus eliminating the external noisy amplification step. A notable advantage over PMT is that EM-CCD devices can be manufactured into high density detector arrays capable of parallel detection. However, due to the intrinsic gradual amplification process through several stages of high voltage multiplication registers, they suffer from long response times and cannot match the detection speed of PMT device. Fig. 1.1b illustrates the basic readout architectural enhancement required to upgrade a CCD detector to an EM-CCD.

Figure 1.1 (a) Structure of a PMT, the resistive divider circuit distributes the optimum voltage to each node to induce the charge acceleration required for impact ionization. (b) EMCCD structure consisting of the CCD part and electron multiplying readout component.

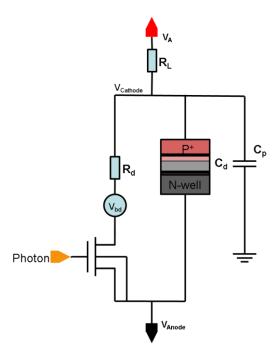

Another solid state alternative for single photon detection is Single Photon Avalanche Diode (SPAD) in custom CMOS process. SPAD is essentially a p-n junction reverse-biased at above breakdown level with the maximum electric field uniformly distributed across the depletion region of the planar p-n junction, which constitutes the device multiplication region [15]. Photo-generated carriers within this region are accelerated by the high electric field and undergo a rapid multiplication process through repeated high speed collisions with the lattice atoms, resulting in successive impact ionization. The result is an avalanche current generated on picosecond time scale [16]. The charge multiplication process is driven by the high lateral electric field and occurs in a single turn. Due to the large number of electrons in the high filed region during the avalanche build up, there will be multiple impact-ionization events occurring in parallel. According to the law of large numbers, at any given time, there will be a large number of carriers working to reduce the variance of the gain within the high field region. If one electron fails to fulfill its average number of ionizations, another is likely to exceed it. Consequently the amplification noise in SPAD is negligible [17]. The rapid internal amplification by means of a run-a-way avalanche process completely eliminates many of the traditional sources of noise such as (read noise, amplification noise) typical in analog optical detectors. The main source of noise in SPADs is the Dark Count Rate (DCR), which is the rate of dark (photon unrelated) avalanche events. These non-photon related pulses can be due to thermal generation of carriers, band to band tunneling, field assisted tunneling, after pulsing or crosstalk [18]. Basic depiction of SPAD operation appears in Fig. 1.2.

Custom SPADs are capable of matching the single photon detection speed and sensitivity of PMT, however they requires front-end electronic support to enable their rapid reset and recovery for continuous operation. Since electronics components cannot be easily integrated in the custom CMOS process, hybrid systems have been proposed whereby the SPAD detectors on custom substrate are externally coupled to an electrically active standard CMOS substrate containing the necessary front end electronics.

Fig 1.2: Single Photon Avalanche Diode (SPAD

The down-side is the increase in cost and complexity that results from bonding incompatible technologies. Furthermore, parasitic introduced by the external connections bring about degradation of system performance in terms of diminished sensitivity and speed [17]. Since standard CMOS offers an ideal platform for seamless integration of processing and readout electronics, it would seem that integration of SPAD in standard CMOS could offer significant advantages towards the implementation of compact high performance optical sensing systems.

#### 1.3 CMOS Compatibility

There has been interest in a semiconductor replacement for the PMT since the 1960's [18-24]. However CMOS process is not optimized for high field conditions required for SPAD operation. The single photon electrical response of SPAD is contingent upon the volumetric breakdown of the planar depletion region. This requires effective isolation of the maximum electric field to the planar multiplication region, while counteracting the effect of electric field crowding around the curved edges of the device. Otherwise excessive electron tunneling and premature breakdown associated with the corners and curved edges will introduce noise and uncertainty in the operation of the device [25, 26]. In standard CMOS, custom features required for selective tailoring of the electric field distribution are not directly available to the designer.

An innovative layout design, introduced in [27], enabled Premature Edge Breakdown (PEB) suppression in standard CMOS by utilizing a diffused guard ring to modulate the high electric field at the periphery of the SPAD device. Despite the fill factor penalty associated with the diffused guard ring this was a breakthrough step, as it enabled, for the first time, the development of SPADs in conventional CMOS process [27-28]

## 1.4 CMOS Single-Photon Pixel – *Area Vs. Performance*

Implementation in conventional CMOS has opened the way for low cost development of SPAD pixels with increasing performance levels. However the added performance requires more integrated electronics which takes up additional silicon real

estate resulting in a reduced fill factor. If the photosensitive area is kept constant, the loss in pixel fill factor will increase in direct proportion to its performance. The trade-off between performance and fill factor can be resolved if the active area is allowed to increase proportionally with the level of integrated functionality. However, in standard CMOS a linear increase in the SPAD active area leads to an exponential increase in its Dark Count Rate (DCR) [6]. The resulting loss in device Signal to Noise Ratio (SNR) makes the design of large active area SPADs not feasible in standard CMOS. Consequently, in practical applications, the active area of CMOS SPADs is ideally restricted to below  $100~\mu m^2$ . This nonlinearity severely restricts fill factor in high performance SPAD pixels, often resulting in fill factors as low as 2 - 6% [30, 31].

The current trend is towards higher performance SPAD pixels and thus greater integration of functionality on pixel and on chip. The DCR imposed limitation on the active area creates a major tradeoff between performance and fill factor, preventing the full exploitation of the potential offered by CMOS-based SPAD detectors. The DCR associated active area constraint also presents a serious limitation for SPAD-based application as practical detection tasks often require a large photon collection surface [32].

Individual SPADs are characterized by their fill factor, bandwidth (maximum count rate), and DCR. Design methods capable of easing the trade-offs parameters at the device level would make for a more robust SPAD pixel which would naturally assemble into more robust arrays. So the first task in high performance SPAD array design must be performance optimization at the device level. This is the purpose behind the research work discussed in Chapter 2 and Chapter 3

## 1.5 CMOS Single-Photon System – *The Readout Challenge*

Under current implantation strategies, the effective performance of single SPAD Pixel within an array assembly is substantially lower, depending on the array size, than the performance of single standalone SPAD pixel. Due to the resulting degradation of effective single pixel response, when realized within larger multi-pixel assemblies, the development of a robust integrated large SPAD array with high performance is yet to be accomplished in CMOS and remains the primary area of research in the field [33]. The fundamental challenge has been the developments of an appropriate readout architecture that can effectively handle the massive amount of dynamic data generated by multiple SPAD elements without imposing significant bottleneck effects on the operation of the system. The conceptual illustration of the readout challenge appears in Fig. 1.3.

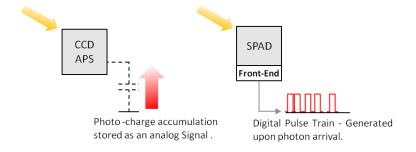

Figure 1.3: (a) Photo-signal statically stored in the pixel until it is sequentially readout and processed during the readout cycle. (b) Photo-signal must be dynamically processed in real time with each photon arrival, thus making local storage difficult

#### 1.5.1 Digital Readout – SPAD Imager Array

The hall-mark of SPAD cutting edge operation is its single-photon sensitive digital response that can be generated with a simple in-pixel digital buffer and directly read out without amplification or pre-processing. Unlike CCD or Active Pixel Sensors, the dynamic response of SPAD cannot be statically stored as photo charge and must be processed instantaneously as either digital count value or Time Of Arrival (TOA) value, or both, before it can be stored. The otherwise excellent signal characteristics of a SPAD device pose a significant architectural challenge when it comes to reading out large arrays of such devices. The primary difficulty is characterized by the achievable efficiency in accessing pixel information as it is dynamically generated in large pixel arrays. One solution that enables massive operational parallelism and offer the best detection efficiency, is in-pixel processing of SPAD response [1, 34]. However large-area in-pixel counters or timing circuits significantly reduce the fill factor of the pixel and can prohibitively limit its photon-collection efficiency [1]. Simpler pixel-level processing improves fill factor and enable larger arrays, but would require a degree of resource sharing. Resource sharing involves multiplexing several signal paths within the same sharing group. This inhibits the dynamic operation of SPADs as digital pulses cannot share the same transmission/processing medium during overlapping time windows. The resulting performance trade-offs impose limitations on the size of the array. The fundamental challenge, and hence the bulk existing research, associated with the readout of large array of digital SPADs is fundamentally driven by the central tradeoff between efficient utilization of Silicon real estate (resource sharing) and throughput (effective transmission bandwidth per pixel).

#### 1.5.2 Analog Readout – SiPM Detector

The severe bandwidth limitations (high rate of pulse pile up) associated with the dynamic readout of multiple digital SPAD pixels onto a common channel, described above, is eliminated by operating the array in what is known as the Silicon Photo-Multiplier (SiPM) mode. In this configuration individual current-mode pixel are parallel-connected to a common load As a result, when simultaneously fired, their signal will combine to produce an analog sum of all the avalanche signals [35-38]. Basic operation of a 4 cell SiPM macro-pixel is shown in Fig. 1.5.

Figure 1.4: Current signal summation at the common readout node of the set of parallel connected individually quenched SPAD elements forming a single SiPM macro-pixel

In SiPM detectors, the asynchronous characteristic of analog operation enables large grouping of multiple SPAD elements without introducing performance constraints. The SiPM signal can be discerned from the background dark noise by amplitude thresholding of the summed current signal (signal amplitude) [39]. Therefore only photons that arrived within the summation window (avalanche current pulse-width) can

be identified and quantified. The avalanche-gated analog summation represents the functional foundation of SiPM detector and ultimately limits the applicability of the technology. Furthermore the SiPM response signal is a faint analog current pulse with rapid transience and large active range. Digital extraction of count and TOA value room such a signal is no trivial task, involving multiple levels of signal processing [40]. The electronic noise added in the process reduces the single-photon sensitivity of the detector while the foot-print area and power dissipation involved with the analog signal processing makes integrated readouts impractical.

#### 1.5.3 Proposed Readout Architecture

SPADs are digital dynamical devices and they must be treated as such in order for their full potential as high speed single-photon detectors to be realized. The readout interface must preserve the advantage from both the dynamical (Asynchronous, high speed) and digital (noise free, direct readout) nature of SPAD response. The existing digital readout architectures preserves the digital characteristic of the SPAD device at the cost of its dynamic characteristics, while the automatically asynchronous behavior of the analog readout, preserve the dynamic nature of SPAD response at the cost of the digital feature of its operation. Chapter 5 presents a design for a novel array readout architecture that preserves both the digital and dynamical aspects of the SPAD operation. Fig. 1.5 compares the basic architecture of the analog, digital and the proposed readout architectures.

An integrated signal processing and digitization system has been designed to interface with the signal aggregation node in Fig. 1.5 c. The purpose is to establish free-

Figure 1.5: (a) SiPM analog readout based on dynamic current signal summation requires complex analog readout chain. (b) Multiplexed digital readout results in loss of overlapping pulses. (c) Proposed readout based upon digital readout at the pixel level and dynamic voltage division at the readout interface.

running dynamic digitization and readout of the detector output signal, not currently possible with the standard ADC digitization system deployed as part of SiPM analog readout chain. Fig. 1.6 illustrates the basic architecture of this integrated signal processing unit.

Figure 1.6: Signal processing system for the array detector interface of Fig. 1.5 c

## 1.6 Primary Objective and Goal

The over-arching goal for both single photon imagers and Silicon Photo-Multiplier is high sensitivity and high resolution solid state optical detection. The potential of SPAD arrays towards realization of this breakthrough seems obvious when considering the excellent single photon performance of a SPAD detector and the feasibility of their implementation in CMOS,. However, this potential is yet to be fully realized. The structure and operation of SPAD introduces several performance trade-offs and conflicting design objectives. The Development of large-scale SPAD arrays capable of reproducing the excellent performance of a single SPAD detector on a larger scale is contingent upon minimization of trade-off parameters associated with the single pixel operation and system-level operation of multi-pixel array. This feat is the primary challenge confronting research in the field. The advent of ultra compact and versatile

process technologies will perhaps one day bring this goal closer to fruition – However for now the effort is in the direction of novel design concepts and new configuration techniques within the context of current low-cost, standard fabrication to realize large, high speed array of compact photon counters in a dense spatial arrangement.

## 1.7 Research Strategy and Organization

The focus of this thesis is to investigate a design approach to merge the best performance aspects of SPAD and SiPM design paradigm into an integrated high speed single photon counting system with greater detection sensitivity than either technology. The strategy involves a hierarchical approach to performance improving with operational requirement and performance of the next stage in mind. This means starting from the semiconductor junction level, moving up to the SPAD pixel eventually leading up to novel system design that can serve as a blue print for development of high speed SPAD array detectors featuring a scalable low-power integrated readout system with an unrestricted dynamic range, high fill factor and low noise operation.

The following brief summary of the upcoming chapters offer a conceptual organization of main research themes.

**Chapter 2:** This work centered around investigation of methods to improve DCR and fill factor by modifying the structure of the p-n junction. In conventional CMOS SPAD design, the fill factor degradation results from the un-scalable dead area taken up by the diffused guard ring. The alternative approach involved covering the perimeter of the junction with a poly gate, appropriately biased to deplete the area underneath it. PEB in

the resulting SPAD device was achieved through reduction of the field at the curved edges or corners that constitute the periphery of planar p-n junctions, without increasing the dead area within the footprint of the SPAD pixel. We experimentally verify the effect of this field gate on lowering the DCR of the device. In addition geometrical modification of the p-n junction towards stated performance improvement has been studied and experimentally verified. Large-area SPAD pixels in standard CMOS have not been possible due to prohibitively large DCR. The purpose of this chapter is to demonstrate a large—area SPAD device in standard CMOS.

Chapter 3: This chapter focuses on performance enhancement at the pixel level which constitutes the next architectural layer in the system hierarchy. This work involved the development of front-end electronics capable of high speed quenching and recovery operation required to maximize pixel bandwidth. Towards this purpose a novel timing and logic circuit was designed to generate precisely matched and optimally synched quench and recharge signals with controllable delay between the two operations. Linearly variable delay enables fine tuning of the hold-off time required to determine the setting that optimizes the SNR (bandwidth Vs DCR). In order to standardize the readout pulse of the pixel so as to optimize the resource sharing requirement of the eventual system. For the first time an in-pixel tunable Event Pulse Generator (EPG) was integrated with the front-end electronics to act as the pixel interface. The pixel interface allows the output pulse-width of the pixel to be actively modified without affecting device operation. In clustered topology where multiple pixels use the same readout resource, the independent control of the pixel-level pulse width can improve system-level dynamic range,

throughput and noise thresholding capability. The design of the Event Pulse Generator (EPG) involves re-using sections of the hold-off generation electronics in the primary AQC circuit, thus recycling some of the functionality already implemented in the primary circuit. This strategy enables a more compact design.

**Chapter 4:** The finite hold-off time separating the quench and recharge halves of the detection cycle introduces a non-linearity condition in the photon counting operation. In light of the associated performance non-linearity, empirically measured count rate data must be supported with an accurate theoretical description of non-linearity condition, associated with the counting process, before the measured data can be reliably interpreted. Towards this goal an analytical model describing the photon detection statistics for a detector with non-paralyzable dead time was derived. The proposed theoretical model can be used for any system that involves discrete detection of randomly arriving event in presence of a fixed dead time such as service time of a server in network traffic modeling or the refractory period of neurons in synaptic network simulation. The model was then used to theoretically predict the true count from a set of experimentally obtained corrupted counts that were measured in presence of a known dead time. The proposed model was compared against the standard model of count correction often used in the literature and shown to be more accurate, especially at higher count rates. The validity of the analytical model was experimentally verified.

**Chapter 5:** A novel signal collection mechanisms for a cluster of digital SPAD is introduced in this chapter. The signal accumulation scheme is based on voltage division

across a floating array of minimum sized capacitors. The footprint of the interconnect interface is negligible relative to the area of the pixels. Signal accumulation scheme is architecturally simple and compact with an intrinsic asynchronous behavior and a dynamic range that is inherently matched to the number of pixels it supports. It is comparable to SiPM interconnect configuration in terms of simplicity and dynamical behavior without being marred by the SiPM associated readout obstacles and challenges.

Chapter 6: The charge redistribution principle, used in the signal collection phase to generate the quantized profile of the interface output response signal from a set of asynchronously arriving input digital pulses, is now implemented in a reverse operational order so as to bring about the disintegration of the discrete analog signal into its constituting stream of digital pulses. By sequentially processing the pulse stream with a compact digital counter, a binary code which represents the amplitude of the interface output signal, directly in terms of incident photon count can be generated and stored. Effectively a novel design for a highly compact and free running on-chip digital pulse counting system capable of sequential photon counting and photon number resolution is demonstrated

#### 1.8 Contributions

This section will list the original contributions in the presented body of work.

- a) Fill factor enhancement in standard CMOS SPAD device (Chapter 2)

- b) DCR improvement in SPAD cell without area penalty, or additional processing cost.

- c) New compact design for SPAD pixel front-end circuitry capable of high bandwidth operation and linear delay generation.

- d) Introduction of a novel array coupling interface to the front-end electronics, The pixel interface features an independently adjustable event pulse generator and could potentially enhance the operational flexibility of the array system.

- e) Derived a mathematical model for accurate prediction of fraction of measured count lost as a result of performances non-linearity in the courting process. The proposed model was able to accurately map the measured count data to the actual incident count even at high arrival rates where the standard mapping expression grossly overestimates the true count.

- f) Introduced a new acquisition interface for dynamic collection of logic pulses over a common interface method to simplify readout system for SPAD array detectors but can just as easily be used for any system requiring readout or communication of digital voltage pulses over a single transmission line.

## 1.9 Significance to the Scientific Field

The proposed structural design lead to performances enhancement for large Area CMOS SPAD arrays operated at temperature. This will greatly benefit biological detection application like DNA sequencing and proteomics. SPAD-based single-photon sensing solution can be implemented with reduced constraint on the detection sensitivity due to dark count rates, and architectural design with significantly relaxed performances tradeoff and constraints. The implication of proposed sensing platform is expansion of the application scope for analog SiPM detectors and greatly reduced noise susceptibility. In the digital domain operation associated with photon-counting SPAD array SPAD the implications are lossless dynamic resource sharing without introducing additional readout complexity and throughput constraints.

#### Chapter 2

## **Performance Oriented Device Design**

The photon counting efficiency of the CMOS SPAD is characterized by its fill factor, operational speed (maximum counting bandwidth) and Dark Count Rate (DCR). The Combination of these parameters determines the photon detection efficiency of the SPAD pixel in terms of its photon-collecting efficiency and Signal to Noise Ratio (SNR). The primary goal of this section is to investigate structural modifications at the device level that may lead to enhanced sensitivity and SNR. The process leading to the ignition of the characteristic avalanche phenomena starts with the absorption of a photon by the semiconductor material. Photon absorption depends on the semiconductor band structure and the wavelength of the incident light. Spectral selectivity and absorption efficiency is primarily determined by the choice of the material [41]. For electrical detection to become possible the photo-absorption process must be followed by a rapid multiplication of the generated carrier pair. It is essential therefore, that the photon is absorbed within or in the vicinity of the high field multiplication region (depletion region surrounding the on junction). Successful absorption of a photon also depends on the depth it has to penetrate before it is expected to be absorbed. The absorption efficiency of a photon as the function of the penetration depth is shown in the equation 2.1 where  $\alpha$  represent the absorption coefficient of the material and L is the penetration depth.

$$\eta = (1 - e^{-\alpha L}) \tag{2.1}$$

As the depth and the width of the depletion layer are determined by the parameters of the foundry process, the choice of fabrication process becomes an important consideration in meeting the spectral requirement of the application. Deep junctions are more efficient for absorption of longer wavelengths.

Another key characteristic informing the choice of the SPAD material is the Dark Rate. Impurities in the silicon create deep energy levels within the band gap structure and act as carrier trapping sites. The concentration of deep levels within the multiplication region determines the degree of after-pulsing effect as carriers, trapped in the high filed depletion region during an avalanche event are subsequently released after a statistical time delay, thus triggering false detection events [45].

When reverse biasing a basic p-n photodiodes at above the breakdown voltage, electric filed uniformity becomes an issue. Electric filed flux lines will crowd around curved surfaces and corners increasing the local electric field intensity at these regions. This effect leads to premature junction breakdown at the device edge, resulting in an uneven gain which is unsuitable for single photon detection. Suppression of premature edge breakdown (PEB) involves the reduction of electric field at the edge of the p-n junction. An effective solution to this is the localized reduction of doping concentration gradient at the susceptible regions. In dedicated CMOS process, thanks to availability of low-doped n/p well, selective shaping of the electric filed profile can be effectively achieved. One approach is based on implanting a highly doped disc at the center of the diode. The highest electric field is confined at the center of the diode for proper avalanche operation. [27]. The Same effect can be accomplished through decreasing the doping concentration at the periphery of the diode. A low doped p- region implanted at