**ABSTRACT**

Title of Thesis: SECURITY THROUGH OBSCURITY:

LAYOUT OBFUSCATION OF DIGITAL

INTEGRATED CIRCUITS USING DON'T

CARE CONDITIONS

Sana Mehmood Awan, Master of Science, 2015

Directed By: Professor Gang Qu, Department of Electrical and

Computer Engineering and Institute for Systems

Research, University of Maryland

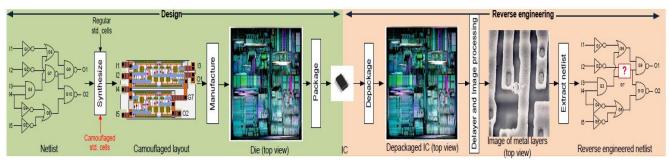

Contemporary integrated circuits are designed and manufactured in a globalized environment leading to concerns of piracy, overproduction and counterfeiting. Contemporary integrated circuits are designed and manufactured in a globalized environment leading to concerns of piracy, overproduction and counterfeiting. One class of techniques to combat these threats is circuit obfuscation which seeks to modify the gate-level (or structural) description of a circuit without affecting its functionality in order to increase the complexity and cost of reverse engineering. Most of the existing circuit obfuscation methods are based on the insertion of additional logic (called "key gates") or camouflaging existing gates in order to make it difficult for a malicious user to get the complete layout information without extensive computations to determine key-gate values. However, when the netlist or the circuit layout, although camouflaged, is available to the attacker, he/she can use advanced logic analysis and circuit simulation tools and Boolean SAT solvers to reveal the unknown gate-level information without exhaustively trying all the input vectors, thus bringing down the complexity of reverse engineering. To counter this problem, some 'provably

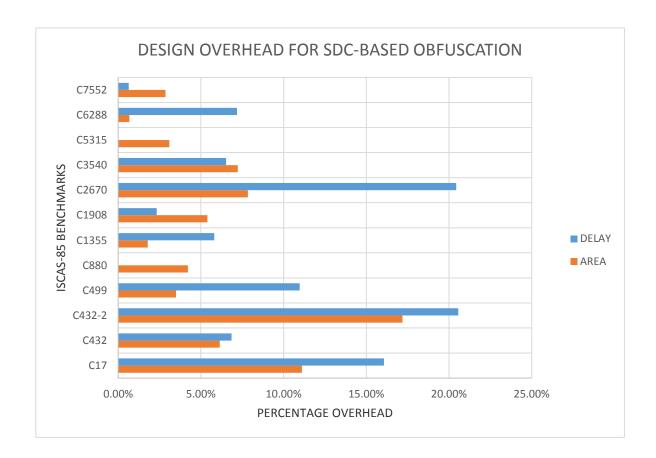

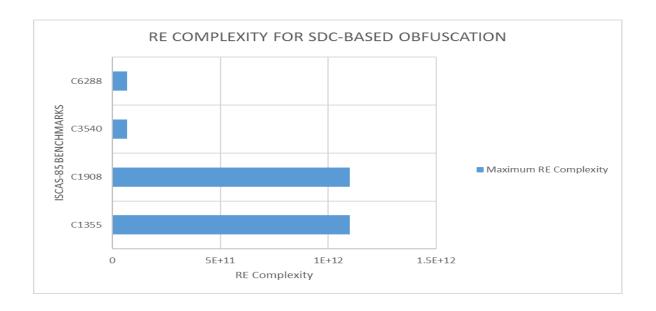

secure' logic encryption algorithms that emphasize methodical selection of camouflaged gates have been proposed previously in literature [5, 6, 15]. The contribution of this paper is the creation and simulation of a new layout obfuscation method that uses don't care conditions. We also present proof-of-concept of a new functional or logic obfuscation technique that not only conceals, but modifies the circuit functionality in addition to the gate-level description, and can be implemented automatically during the design process. Our layout obfuscation technique utilizes don't care conditions (namely, Observability and Satisfiability Don't Cares) inherent in the circuit to camouflage selected gates and modify sub-circuit functionality while meeting the overall circuit specification. Here, camouflaging or obfuscating a gate means replacing the candidate gate by a 4X1 Multiplexer which can be configured to perform all possible 2-input/ 1-output functions as proposed by Bao et al. [16]. It is important to emphasize that our approach not only obfuscates but alters subcircuit level functionality in an attempt to make IP piracy difficult. The choice of gates to obfuscate determines the effort required to reverse engineer or brute force the design. As such, we propose a method of camouflaged gate selection based on the intersection of output logic cones. By choosing these candidate gates methodically, the complexity of reverse engineering can be made exponential, thus making it computationally very expensive to determine the true circuit functionality. We propose several heuristic algorithms to maximize the RE complexity based on don't care based obfuscation and methodical gate selection. Thus, the goal of protecting the design IP from malicious end-users is achieved. It also makes it significantly harder for rogue elements in the supply chain to use, copy or replicate the same design with a different logic. We analyze the reverse engineering complexity by applying our obfuscation algorithm on ISCAS-85 benchmarks. Our experimental results indicate that significant reverse engineering complexity can be achieved at minimal design overhead (average area overhead for the proposed layout obfuscation methods is 5.51% and average delay overhead is about 7.732%). We discuss the strengths and limitations of our approach and suggest directions that may lead to improved logic encryption algorithms in the future.

## SECURITY THROUGH OBSCURITY: LAYOUT OBFUSCATION OF DIGITAL INTEGRATED CIRCUITS USING DON'T CARE CONDITIONS

By

Sana Mehmood Awan

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science 2015

Advisory Committee: Professor Gang Qu, Chair Associate Professor Mark Austin Assistant Professor Dana Dachman-Soled © Copyright by Sana M. Awan 2015

## Dedication

This work is dedicated to my *Baba Jan* who gave me my life's greatest lesson in optimism, courage and faith.

## Acknowledgements

I would like to thank my advisor, Dr Gang Qu for his insightful guidance, support and help throughout the completion of this work, and for being not just a great teacher but also a wonderful person. I am also grateful to Mingze Gao for his help and for all the fruitful discussions we had on the topic.

Additionally, I would like to thank the Fulbright Program for their financial support over the course of my graduate studies.

Finally, I would take this opportunity to express my gratitude to my mother whose constant love and encouragement mean the world to me.

### TABLE OF CONTENTS

| Cha | pter 1: The Need for Hardware IP Security                                                   | 1  |

|-----|---------------------------------------------------------------------------------------------|----|

| 1.1 | Introduction                                                                                | 1  |

| 1.2 | The Emergence of Re-use based System-on-Chip Devices and their Supply Chain Security        |    |

| Imp | lications                                                                                   | 2  |

| 1.3 | Security Threats to IC Supply Chain                                                         | 5  |

| Cha | pter 2: Survey of Existing Hardware IP Security Solutions                                   | 12 |

| 2.1 | Hardware IP Protection Approaches                                                           | 17 |

|     | 2.1.1 Authentication based IP Protection                                                    | 18 |

|     | 2.1.2 Obfuscation based IP Protection                                                       | 22 |

|     | 2.1.3 Mixed or Combined Approaches                                                          | 36 |

| 2.2 | Motivation for this research                                                                | 36 |

| 2.3 | Dissertation Outline                                                                        | 37 |

| Cha | pter 3: Layout Obfuscation: Motivations, Assumptions and Techniques                         | 40 |

| 3.1 | Example of Gate Camouflaging: The Attack Model                                              | 41 |

| 3.2 | The Attacker's Goals                                                                        | 42 |

| 3.3 | Some Observations from the Analysis of RE Attack Strategy                                   | 44 |

|     | 3.3.1 Lemma 1: Simply hiding the configurable cells deeply inside the IC will not increase  |    |

|     | the RE attack complexity, if the camouflaged gates are on the path from primary inputs to   |    |

|     | known gates, SAT Solvers can be used to control the inputs to these unknown gates           | 44 |

|     | Lemma 2: Isolated camouflaged gates can be solved individually in linear time. Interference | of |

|     | these gates will increase the complexity to exponential time.                               | 45 |

|     | Lemma 3: Don't Care Conditions in the Circuit Lower the Complexity of RE Attac<br>Lemma 4: Cone splitting, if possible in the circuit, lowers down the complexity of RI       | E attacks |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|     | Lemma 5: The complexity of circuit for Goal-1 (determining input-output relationship limited by the number of inputs of the largest cone. The largest cone is the cone that h | ps) is    |

|     | primary inputs                                                                                                                                                                |           |

| 3.4 | Recommendations for a Smarter Obfuscation Strategy                                                                                                                            |           |

|     | Pick the gates that belong to the same fan-in cone for obfuscation                                                                                                            | 56        |

|     | Pick the gates that are in a common subset of several fan-in cones and do not belong to                                                                                       | to any    |

|     | other cones.                                                                                                                                                                  | 57        |

|     | Increase the size of fan-in cones                                                                                                                                             | 58        |

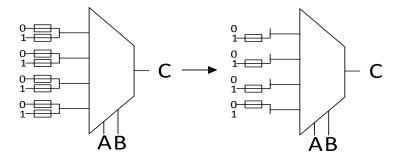

|     | Using the 4x1 Universal Multiplexer for Gate Camouflaging                                                                                                                     | 58        |

| Cha | pter 4: Hardware Obfuscation using Don't Cares                                                                                                                                | 62        |

| 4.1 | Introduction to Satisfiability Don't Care (SDC) based Obfuscation                                                                                                             | 62        |

|     | Boolean Formulation to determine Satisfiability Don't Cares                                                                                                                   | 65        |

| 4.2 | The SDC-based Obfuscation Problem                                                                                                                                             | 66        |

|     | 4.2.1 Layout Obfuscation Method 1:                                                                                                                                            | 66        |

|     | 4.2.2 Layout Obfuscation Method 2                                                                                                                                             | 70        |

| 4.3 | Pseudocode for SDC-based Obfuscation                                                                                                                                          | 72        |

|     | Correctness of the heuristics                                                                                                                                                 | 74        |

|     | Complexity of the heuristics                                                                                                                                                  | 75        |

| 4.4 | Gate Camouflaging Scheme                                                                                                                                                      | 75        |

| 4.5 | Security Analysis of Functional Obfuscation                                                                                                                                   | 77        |

|     | 4.5.1 Valid Function Detection                                                                                                                                                | 77        |

|     | Simple Removal Attack                                                    | 78  |

|-----|--------------------------------------------------------------------------|-----|

|     | Simple Modification Attack                                               | 78  |

| 4.6 | Simulation Results and Discussion                                        | 79  |

|     | 4.6.1 Design Overhead                                                    | 84  |

|     | Other overhead considerations                                            | 86  |

| 4.7 | Conclusion                                                               | 88  |

| Cha | apter 5: Observability Don't Care-based Obfuscation                      | 91  |

| 5.1 | Introduction to ODC-based Obfuscation                                    | 91  |

|     | Observability Don't Cares                                                | 93  |

| 5.2 | ODC-based Obfuscation Methodology                                        | 95  |

|     | 5.2.1 Finding Locations for Circuit Modification based on ODCs           | 96  |

|     | 5.2.2 Determining Potential ODC Modifications                            | 98  |

| 5.3 | ODC-based Modification Methodology                                       | 102 |

|     | 5.3.1 Method 1                                                           | 102 |

|     | 5.3.2 Method 2                                                           | 106 |

| 5.4 | Security Analysis                                                        | 106 |

| 5.5 | Experimental Setup                                                       | 108 |

|     | Pseudocode for ODC-based Obfuscation                                     | 110 |

| 5.6 | Functional Obfuscation for Incompletely Specified Circuits with Examples | 122 |

| 5.7 | Conclusion.                                                              | 128 |

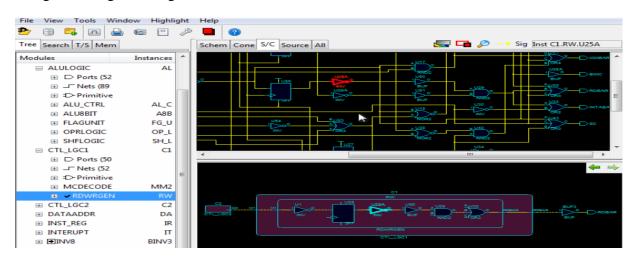

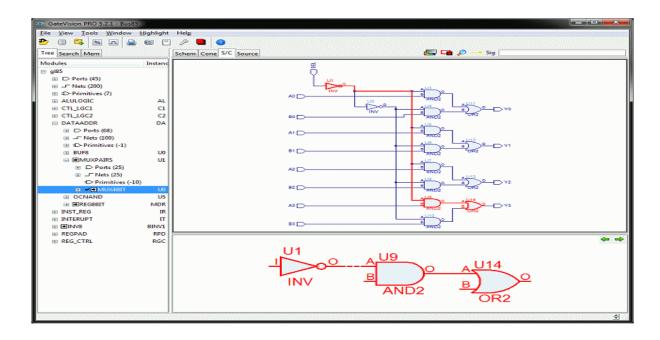

| Cha | apter 6: Netlist Debugging and Viewing using GateVision PRO              | 130 |

| 6.1 | Waveform Viewer and Signal Tracing                                       | 131 |

| 6.2 | Logic Cone Extraction Feature                                            | 132 |

| 6.3 | Path extraction and Verilog Simulation                                   | 132 |

| 6.4 | Debugging Views                                                                      | 133 |

|-----|--------------------------------------------------------------------------------------|-----|

| 7   | CONCLUSION                                                                           | 135 |

|     | Comparison of Don't Care-based Obfuscation with Existing Hardware IP Security ations | 137 |

| APP | PENDIX-1: Taxonomy of Hardware IP Protection Techniques                              | 143 |

| REF | FERENCES                                                                             | 144 |

## LIST OF TABLES

| Table I: Possible Effects of Counterfeit ICs [ 15]                                                                                                            | 15    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

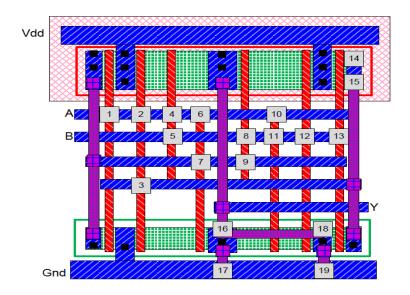

| Table II: List of true and dummy contacts to realize different functions using the camouflaged                                                                |       |

| layout shown in Figure 2.13 (from [15])                                                                                                                       | 33    |

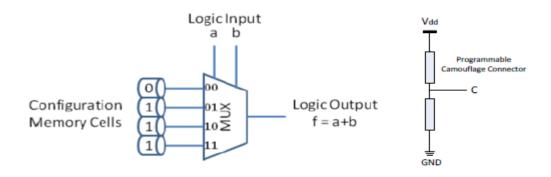

| Table III: 16 Boolean Logic Functions f (a,b) that can be performed by a 4x1 multiplexer dependent                                                            | ıding |

| on the configuration bits.                                                                                                                                    | 60    |

| Table IV: ISCAS-85 Benchmark Circuits                                                                                                                         | 81    |

| Table V: Results of Satisfiability Don't Care-based Obfuscation methodology applied on ISCA                                                                   | S-85  |

| benchmarks                                                                                                                                                    | 81    |

| Table VI: ODC Calculations for the Library Cells (from [20])                                                                                                  | 95    |

| Table VII: ISCAS-85 Benchmark Circuits                                                                                                                        | 114   |

| Table VIII: Results of Observability and Satisfiability Don't Care-based Obfuscation methodology                                                              | ogy   |

| applied on ISCAS-85 benchmarks                                                                                                                                | 114   |

| Table IX: Results of Observability and Satisfiability Don't Care-based Obfuscation methodolog applied on ISCAS-85 benchmarks Method 1 combined with Method 2) |       |

| Table X: Functional Obfuscation of some selected Benchmarks                                                                                                   | 125   |

| Table XI: Summary of Simulation Results of different Don't Care-based Obfuscation Methods applied to ISCAS-85 Benchmarks                                      | 129   |

| Table XII: GateVision PRO features                                                                                                                            | 134   |

## LIST OF FIGURES

| Figure 1.1: Vulnerabilities in the IC Design Cycle for IP Vendors                              | 5  |

|------------------------------------------------------------------------------------------------|----|

| Figure 1.2(a): Electronic Component Supply-chain Vulnerabilities                               | 8  |

| Figure 1.2 (b): Activity Diagram showing IP Design Flow.                                       | 8  |

| Figure 2.1: Taxonomy of Hardware IP Security Issues (from Narasimhan et al.2012)               | 12 |

| Figure 2.2: Taxonomy of Counterfeit Types.                                                     | 14 |

| Figure 2.3: Classical bathtub curve, illustrating typical device failure characteristics[19]   | 14 |

| Figure 2.4: Taxonomy of Hardware IP Protection Techniques (see Appendix-1)                     | 18 |

| Figure 2.5: A delay-based Arbiter PUF.                                                         | 21 |

| Figure 2.6: Circuit Obfuscation techniques (a) Layout Obfuscation, and (b) Functional or Logic |    |

| Obfuscation                                                                                    | 22 |

| Figure 2.7: Key-gate Insertion: Motivation Example                                             | 24 |

| Figure 2.8: A smarter key insertion strategy                                                   | 25 |

| Figure 2.9: (a) Concurrently mutable key-gates (b) Sequentially mutable keygates               | 26 |

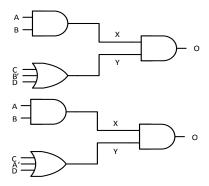

| Figure 2.10: Don't care conditions in the circuit lower RE Complexity                          | 27 |

| Figure 2.11: Overview of Key Insertion based Approach                                          | 28 |

| Figure 2.12: Some simple key-insertion examples                                                | 29 |

| Figure 2.13: A generic camouflaged layout that can perform either as an XOR, NAND or NOR       | 33 |

| Figure 2.14: Camouflaged Circuit Design Flow.                                                  | 34 |

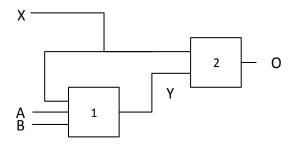

| Figure 3.1: Two interfering camouflaged gates                                                  | 45 |

| Figure 3.2: Isolated camouflaged gates                                                         | 46 |

| Figure 3.3: Interference between camouflaged gates                                             | 47 |

| Figure 3.4: Presence of Don't Care conditions lowers RE complexity                             | 48 |

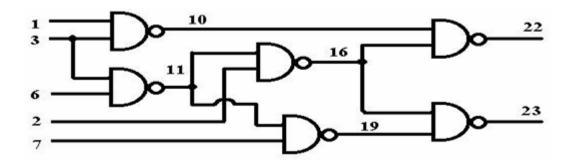

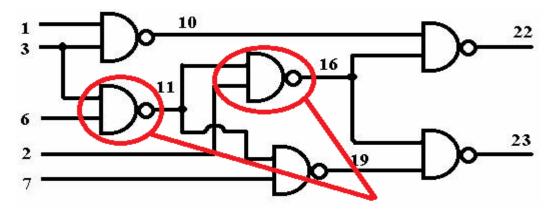

| Figure 3.5: C17 Benchmark Circuit from ISCAS-85 family                                            |

|---------------------------------------------------------------------------------------------------|

| Figure 3.6: Motivation Example demonstrating (a) cone-splitting and (b) the use of interference   |

| graphs (taken from [15])                                                                          |

| Figure 3.7: Complexity Analysis for Goal-1 (determining high level circuit functionality or truth |

| table)                                                                                            |

| Figure 3.8: MUX-based 2x1 OR gate proposed in [16] and a programmable connector proposed in       |

| [17]                                                                                              |

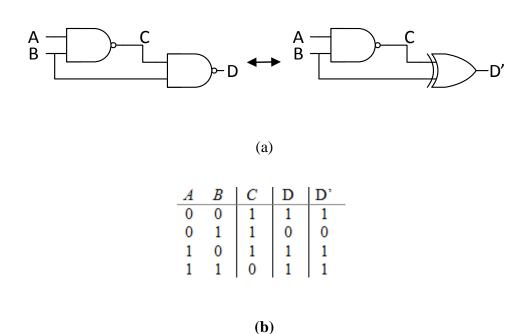

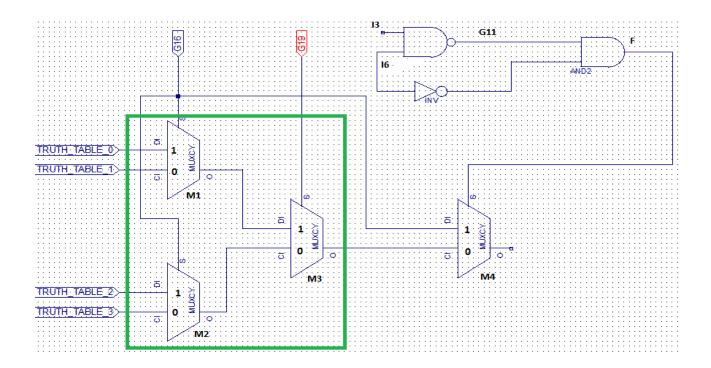

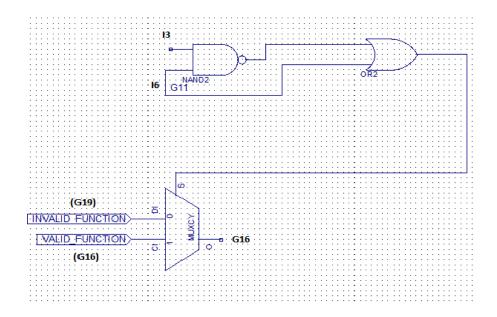

| Figure 4.1: Example SDC modification (a) Gate Replacement (b) Truth table for both circuits 63    |

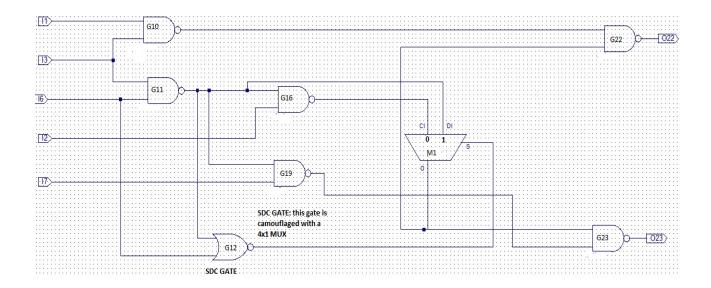

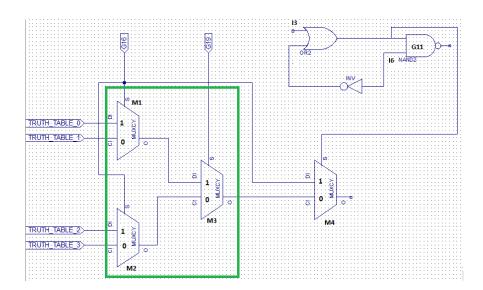

| Figure 4.2 (a) C17 Benchmark from the ISCAS-85 family                                             |

| Figure 4.2 (b) Output Logic Cone Intersection and Valid Function Location                         |

| Figure 4.2 (c) Illustration of SDC-based obfuscation for C17 benchmark                            |

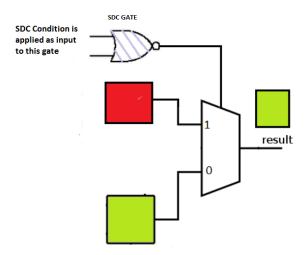

| Figure 4.3: Essential Ingredients of SDC-based Layout Obfuscation                                 |

| Figure 4.4: A second method of Layout Obfuscation of G16 in C17 benchmark                         |

| Figure 4.5: Multiplexer replacement technique                                                     |

| Figure 4.6: Satisfiability Don't Care-based Obfuscation: Overhead results for ISCAS-85 Benchmark  |

| Family85                                                                                          |

| Figure 4.7: SDC-based Obfuscation: RE Complexity for some selected benchmarks                     |

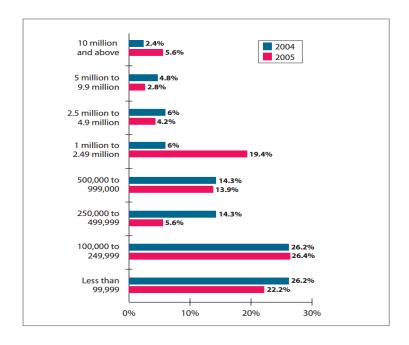

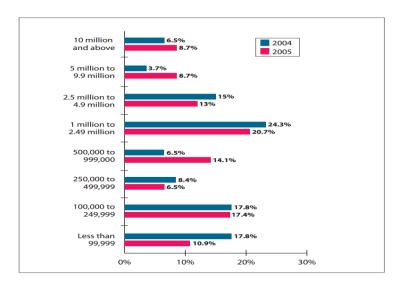

| Figure 4.8. From 2005, (a) ASIC gate counts in Taiwan (b) ASIC gate counts in China [41] 87       |

| Figure 4.9: Secure "Split Manufacturing" Approach in IC Design                                    |

| Figure 5.1: Two 4-input circuits that implement the same function                                 |

| Figure 5.2: Two more implementation of the same function                                          |

| Figure 5.3: ODC on the AND gate                                                                   |

| Figure 5.4. Generic ODC modification                                                              |

| Figure 5.5. ODC change that reroutes earlier signals                                              |

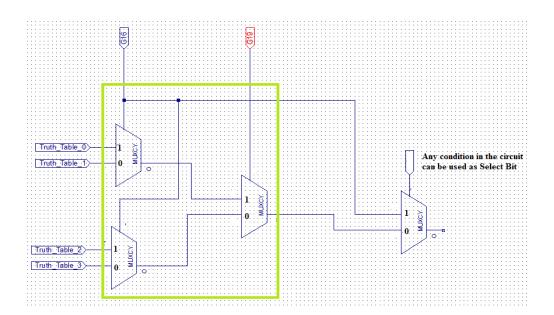

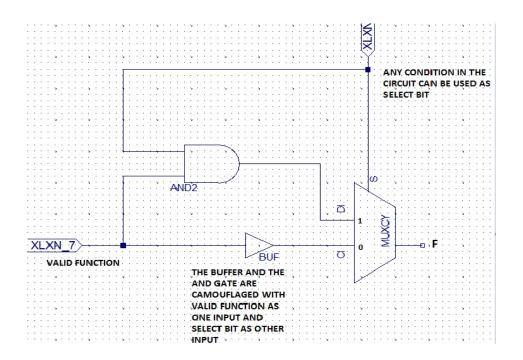

| Figure 5.6: Essential Ingredients of ODC-based Layout Obfuscation                                     | . 103 |

|-------------------------------------------------------------------------------------------------------|-------|

| Figure 5.7: Layout Obfuscation using ODCs (Method 1)                                                  | . 104 |

| Figure 5.8: Layout obfuscation using SDC-like gate                                                    | . 105 |

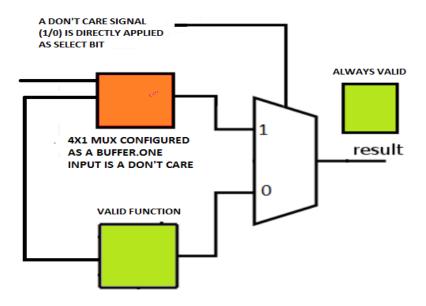

| Figure 5.9: A don't care, such as input X from Figure 5.1 (right), is used as select bit for the 2x1  |       |

| multiplexer. Both the inputs to this multiplexer are the same 'valid function' but they are           |       |

| camouflaged so an attacker cannot directly observe them.                                              | . 105 |

| Figure 5.10: Making inputs to the 2x1 MUX symmetric for don't care-based obfuscation                  | . 107 |

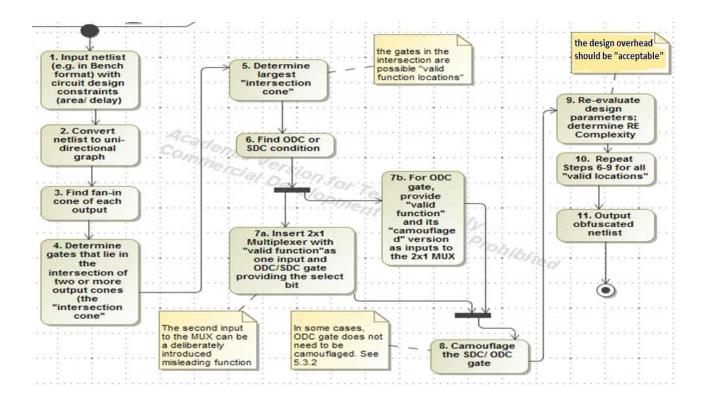

| Figure 5.11: Activity Diagram of Obfuscation Methodology (ODC Method 1 and SDC)                       | .113  |

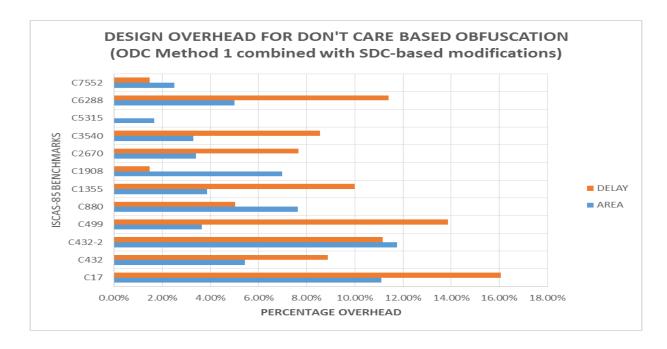

| Figure 5.12: Don't Care-based Obfuscation (Method 1 combined with SDC modifications):                 |       |

| Overhead Results for ISCAS-85 Benchmarks                                                              | . 119 |

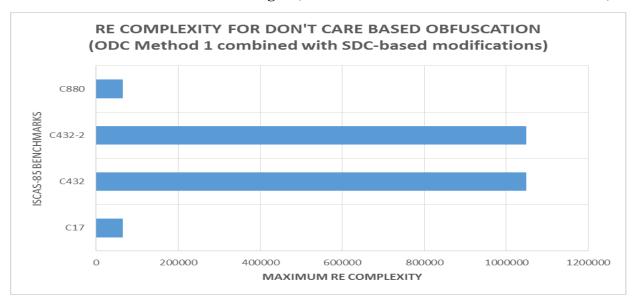

| Figure 5.13: RE Complexity for some selected benchmarks (using a combination of Method 1              |       |

| combined with SDC modifications)                                                                      | . 119 |

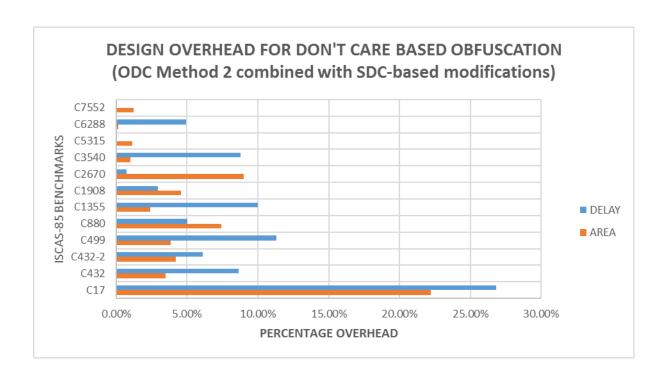

| Figure 5.14: Don't Care-based Obfuscation (Method 2 combined with SDC modifications):                 |       |

| Overhead results for ISCAS-85 Benchmark Family                                                        | . 121 |

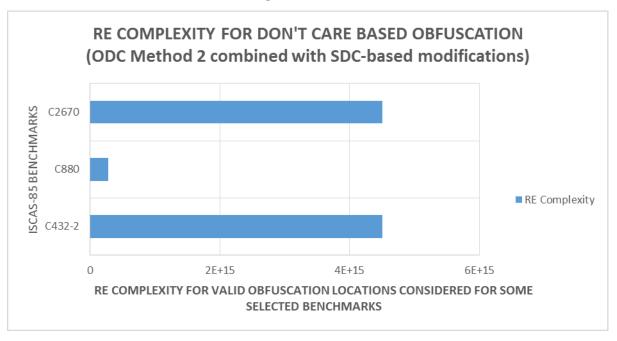

| Figure 5.15: RE Complexity for some selected Benchmarks: ODC Method 2 combined with SD0 Modifications |       |

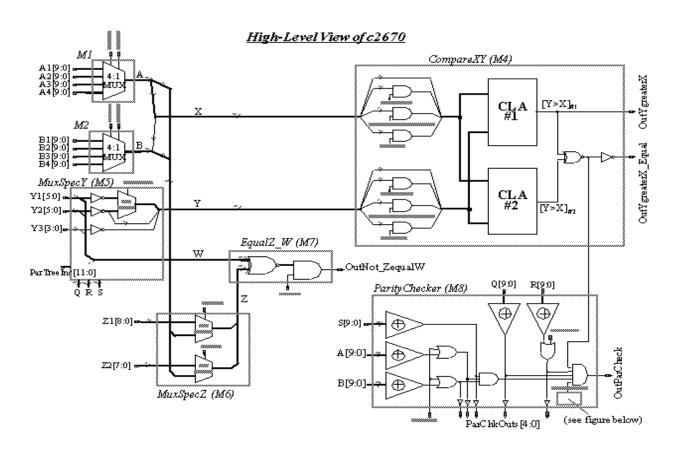

| Figure 5.16: High-level Cicuit Model of C2670.                                                        | .124  |

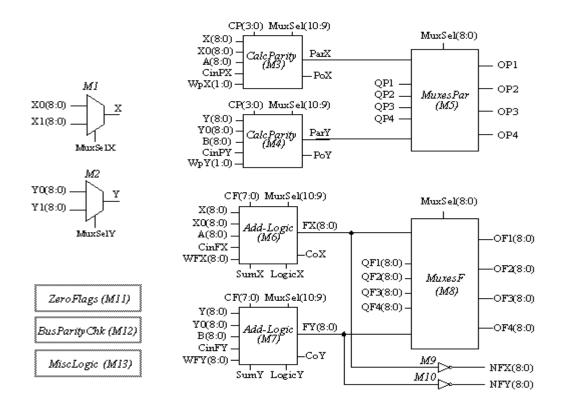

| Figure 5.17: High-level Circuit Model of C5315.                                                       | .127  |

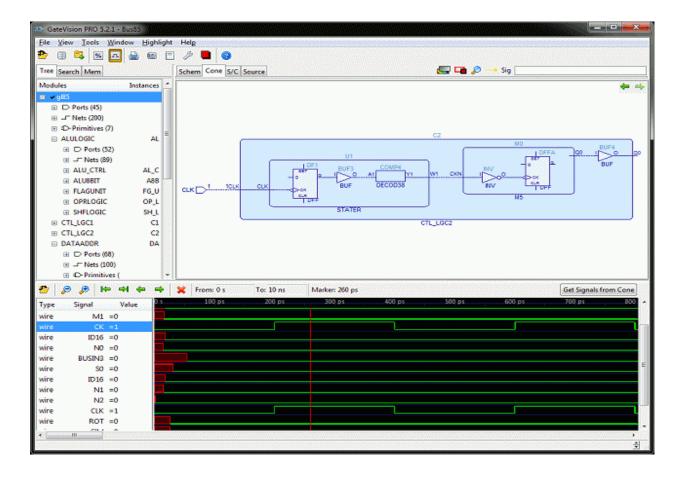

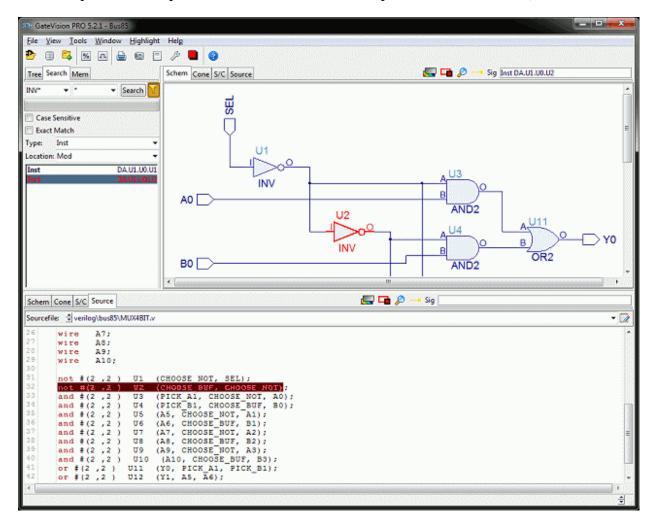

| Figure 6.1 (a): Gate-level Description of an example circuit in GateVision PRO                        | .130  |

| Figure 6.1(b): Cone Extraction Feature of GateVision PRO                                              | . 131 |

| Figure 6.2: Waveform Viewing using GateVision PRO                                                     | . 132 |

| Figure 6.3: Source code and Schematic views (viewable side-by-side)                                   | . 133 |

#### CHAPTER 1: THE NEED FOR HARDWARE IP SECURITY

#### 1.1 Introduction

The dynamic and rapidly evolving field of electronics has changed our lives immeasurably and irrevocably since the invention of the transistor in 1948. The power, speed and availability of information will continue to define our social, political and economic landscape. The all-pervasive nature of Electronics can be felt in every aspect of human life in this "silicon age". Starting from 1960 when commercial semiconductor manufacturing became a viable business, the industry has grown with a prodigious average annual growth rate of 16.1% between 1975 and 2000 [1, 2]. According to the Semiconductor Industry Association (SIA), representing U.S. leadership in semiconductor manufacturing and design, worldwide semiconductor sales for 2013 reached \$305.6 billion, the industry's highest-ever annual total and an increase of 4.8 percent from the 2012 total of \$291.6 billion. The industry saw strong demand in several product segments during 2013, especially logic and memory. Logic was the largest semiconductor category by sales, reaching \$85.9 billion in 2013, a 5.2 percent increase compared to 2012 while memory was the fastest growing field recorded, increasing 17.6 percent in 2013 [3]. The key to this rapid advancement in electronics is the aggressive reduction in device dimensions in integrated circuits (ICs) over generations, along with scaling of supply voltage (VDD) and transistor "threshold voltage" (Vth), a phenomenon known as "technology scaling". Device integration density (the number of devices per unit area in an IC) has roughly doubled every two years over the last five decades, a trend first predicted in [4], and now famously termed as "Moore's Law". This has enabled a corresponding exponential increase in computing capabilities and functionality of ICs.

With the rapid development of embedded systems, application specific integrated circuits (ASICs) of small and medium size are playing a more and more important role in the electronics market. Under the umbrella of Systems Engineering, new and pre-existing devices are being connected in novel ways over different forms of communication channels to facilitate increasingly connected system-of-systems. However, with rapidly increasing computing power and integration density, several issues in design, performance and manufacturing of these ICs have come to surface. Increasing power consumption (both due to higher integration density and increasing "leakage" power consumption in the off-state) increased cost of testing and verification of complex integrated circuits and photolithographic complexities in manufacturing nanometer devices (with feature sizes much smaller than the smallest wave-length of light that are used for patterning) are the some of the major issues with IC design and manufacturing in the nanometer regime.

# 1.2 The Emergence of Re-use based System-on-Chip Devices and their Supply Chain Security Implications

To overcome some of the challenges mentioned above and meet design and testing costs and aggressive time-to-market targets effectively, re-use based System-on-Chip (SOC) design using hardware Intellectual Property (IP) cores has become a pervasive practice in the industry to realize bug-free complex System-on-Chip (SoC) devices. System designers can pick integrated circuits (ICs), considered as intellectual property (IP), that are produced for specific functionality and fit them together to achieve a specific goal. This leads to a culture of re-use based design. As a result, IP theft has become profitable as well as a threat to IP developers, vendors, and the SoC industry in general, which motivates the IP protection problem [18].

Considerations of capital costs and economies of scale dictate that semiconductor manufacturing is now reliant on offshore or contract foundries that are organizationally separate and geographically distant from the design houses that design and validate integrated circuits. Qualcomm became the first fabless semiconductor company to rank among top 10 IC producers worldwide and even AMD has been

outsourcing some of its production to foundries throughout the world. However, with the growth of manufacturing potential in Asia, piracy has become rampant, thanks to loose IP protection policies and weak enforcement of IP anti-piracy laws. To make such design and manufacturing feasible, an IC design house is commonly aided by the following external agencies [5]:

- (i) Electronic design automation (EDA) companies that supply the sophisticated software tools that facilitate design, verification and testing of modern ICs.

- (ii) Intellectual property (IP) and standard cell library vendors, who supply pre-verified, high performance, functional hardware IPs or library cells to the IC design facilities. These help to reduce the design time drastically, improve reliability and yield, and enable meeting hard time-to-market targets.

- (iii) Semiconductor manufacturing companies, which provide the fabrication facilities ("fabs") where the design is actually manufactured and sometimes tested, before being sent back to the design house. The cost of maintaining a cutting edge fab runs into billions of dollars every year, encouraging most IC vendors (over 250 strong in 2009 [8]) to follow a "fabless" business model where the design database is outsourced to the fabs for manufacturing [7].

From the above description of prevalent industry practices, it is evident that the control exercised by the IC vendors over the design and manufacturing of their own products is decreasing. The increasing complexity and cost of modern nanometer scale ICs are the main drivers behind this trend. Reduced control on the IC life-cycle accentuates various security issues associated with ICs. Hence, security of hardware IPs and ICs has emerged as a major challenge in nanometer IC design and test.

These IP cores usually come in the form of synthesizable Register Transfer Level (RTL) descriptions (Soft IP), or gate-level designs directly implementable in hardware (Firm IP), or GDS-II design database (Hard IP).

As electronic design automation (EDA) tools and semiconductor technology continues to evolve rapidly, a company will not typically have all the expertise and capability to do in-house design and to fabricate the system it wants to build. If the system is designed and fabricated by others, "how can the company be convinced that the system is trusted, that is, the delivered system does exactly what the company wants, no more and no less?" This is known as the trusted IC design challenge, particularly for military and civilian systems that require security and access control [Defense Science Board 2005; Cohen 2007; Irvine and Levitt 2007; Trimberger 2007; Suh and Devadas 2007; Roy et al. 2008; Rajendran et al. 2012; Gu et al. 2009].

When the company gives the system's specifications to a design house for layout verification or simulation and synthesis, and then gives the layout information to a foundry for manufacture, the company will lose full control of the system's functionality and specifications. An adversary can simply add additional circuitry, such as hardware or software Trojan horses, to maliciously modify the system. For example, a Trojan can disable or destroy system components, perform incorrect or unwanted computation, or leak sensitive information [11].

Another issue is the widespread use of **Design for Testability (DfT)** practices that add certain testability features to a hardware product design. The premise of the added features is that they make it easier to develop and apply manufacturing tests for the designed hardware and reduce time-to-market. These added features, such as scan-chains for sequential circuits, facilitate validation that the product hardware contains no manufacturing defects that could otherwise adversely affect the product's correct functioning.

In addition, IP vendors also allow evaluation versions of their IPs to be downloaded and evaluated by the IC designers. This is an important part of their business because it enables wide publicity of their product leading to increased market share. It also helps them to get feedback about their product from potential customers. From the designers' perspective, IP evaluation is an important step as well since it helps them

explore alternative IP cores with regard to correctness, quality (power, performance, die-area), configurability, testability, and compatibility with other modules in a SoC design.

In the following section, we formally describe different security threats associated with IC design and test cycle introduced due to current industry practices some of which are mentioned above, which will justify our need for effective hardware security solutions.

#### 1.3 Security Threats to IC Supply Chain

The active participation of various external agents in the design and manufacturing process of ICs, as indicated in section 1.2, has made the entire process highly vulnerable to various security threats.

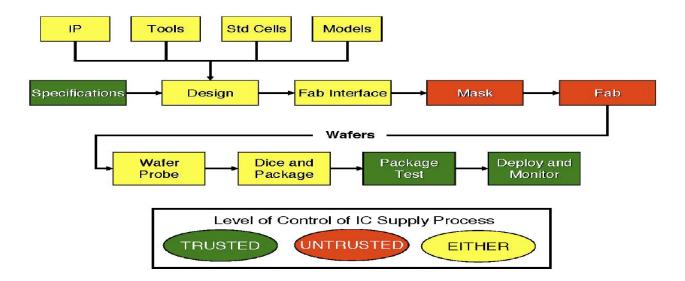

Fig. 1 shows the level of "trust" that can be assigned to the various stages of a typical modern IC design flow [5]. The design life-cycle of IPs shows that these IPs are highly vulnerable to piracy issues at different stages. As a result, the security of integrated circuits supply chain and the reliability of IC functionality in the face of supply chain threats have emerged as a major concern at different stages, spanning design, test, fabrication and deployment.

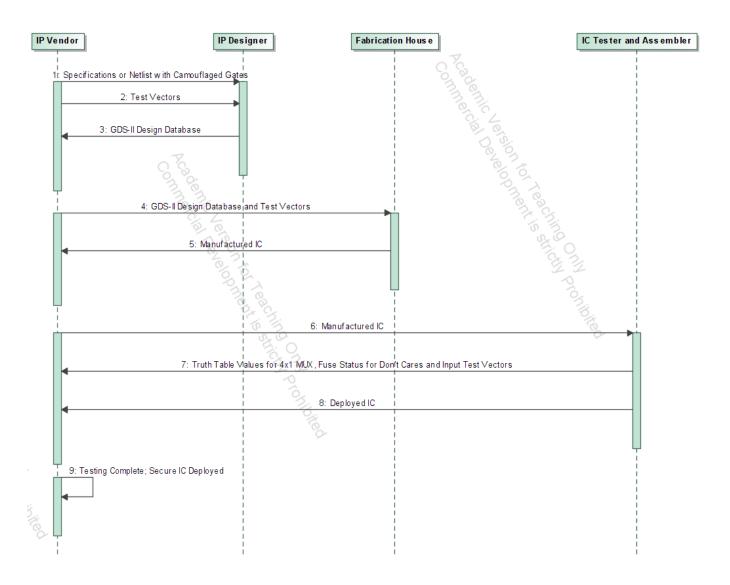

Figure 1.1: Vulnerabilities in the IC Design Cycle for IP Vendors [5], [26]

These security threats include reverse-engineering efforts to facilitate cloning, counterfeiting, unauthorized overproduction by the contract foundry or remarking of ICs as well as malicious alterations by untrusted third-party vendors. It is worth noting that the "design" stage itself is designated as one of the partially insecure stages of the entire flow. This takes into consideration the possible presence of untrusted personnel in the design house with access to the design, who might sabotage the design to serve other interests. Additionally, if the specifications for the proposed design are not complete so that there are unused states in the resulting design (for example a specification for two-bit multiplication table implemented using a 4-bit multiplier) then the inherent redundancy introduced in the circuit by such an implementation can be exploited by a malicious fabrication house to make the circuit have additional unwanted functionality or potentially expose "safe" states. This has been demonstrated in [11] with solutions to counter the problem.

Foundries with access to layout and mask information can easily extract the gate-level netlist and compare circuit simulation results with the responses obtained from an activated IC that has been purchased off the market or provided by the vendor for testing purposes. Thus, a malicious foundry with a means for applying arbitrary input patterns and observing the resultant outputs on an activated IC can easily extract and/or modify circuit functionality. Similarly, package testing may or may not be trusted, depending on who it is contracted out to.

In addition to the above, more critical threats come from the supply chain and compromise hardware integrity. In today's global IC industry, a supply chain adversary, such as an IP provider, an IC design house, a CAD company, or a foundry may have access to the source code of the design, and may easily tamper a hardware system by planting time bombs which compromise hardware computation integrity, or create back doors which enable information leak, or bypass access control mechanisms at higher (e.g., OS and application) levels. The recently released Comprehensive National Cyber Security Initiative has identified this supply chain risk management problem as a top national priority. The issue of malicious modifications

to the design, particularly by the use of hardware Trojans and hardware time bombs has emerged recently due to the widely prevalent industrial practice of fabrication of ICs in potentially untrusted foundries. Hardware Trojans are malicious modifications of a circuit that can cause it to fail during deployment, with potentially disastrous consequences. These Trojans would typically evade detection during conventional post-manufacturing test because they trigger malfunction only under extremely rare conditions unlikely to be exercised during test. Moreover, the Trojans can be tiny relative to the original circuit which makes them difficult to detect by side-channel measurements. Some Trojan circuits, referred to as sequential Trojans, represent FSM structures, which go through a sequence of state transitions before getting activated. On activation, they trigger malfunction, typically by altering logic values at some payload nodes or by leaking secret information.

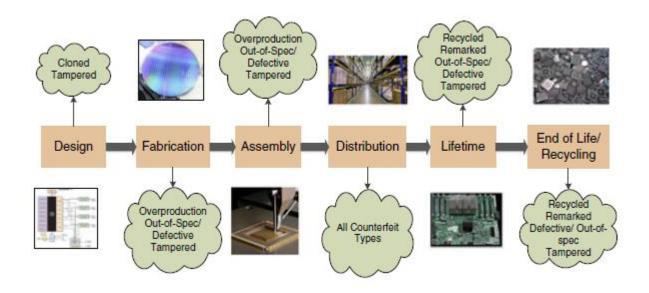

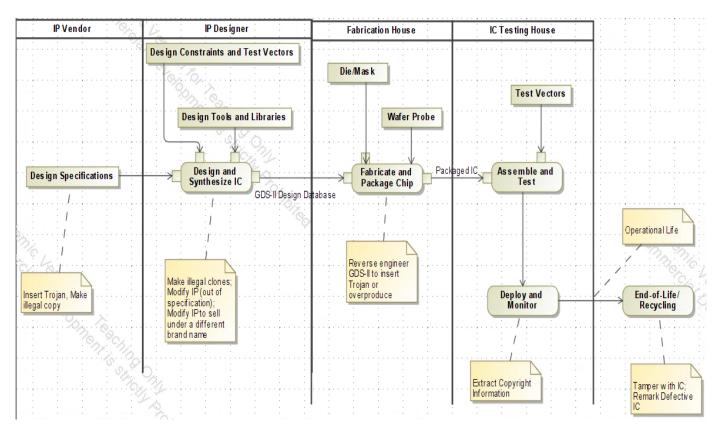

Figure 1.2 (a) details some of the vulnerabilities of the IC design flow which involves design, fabrication, assembly, distribution, usage in the system, and finally end-of-life. As seen, there are vulnerabilities associated with each step in this supply chain. In design stage, an IP may be stolen or a hardware Trojan may be inserted into the design. An untrusted foundry or assembly can insert a hardware Trojan or produce different types of counterfeits. The design house can use illegally obtained IPs in their designs. Overproduced and out-of-spec/defective parts can be entered into the supply chain in the fabrication stage. Untrusted foundries can potentially sell these parts in the open market. They can also tamper with the design to create a backdoor for getting secret information from the field. These parts also get into the supply chain in the assembly phase. An untrusted assembler can possibly sell these parts or tamper with the designs. Illegal activities during distribution, during the IC lifetime, and even at end of useful life may bring different types of counterfeits back into the supply chain (recycled, remarked, etc.) [14].

Figure 1.2(a): Electronic Component Supply-chain Vulnerabilities (Tehranipoor et al. 2014 [14]). "All counterfeit types" indicated in the Figure are detailed in Figure 2.2

Figure 1.2 (b): Activity Diagram showing IP Design Flow. Examples of Security Threats from the perspective of the IP vendor in various stages of IP Design are shown in text boxes corresponding to the different stages.

The main mechanisms and motivations behind the threats in Figure 1.2 can be broadly classified as follows [5]:

- (i) IP piracy: This is a scenario where the IP is illegally used and/or copied without paying the lawful royalty to the IP vendor.

- (ii) IC piracy: In this scenario, the manufacturing fab illegally copies and reverse engineers the design database of an IC sent for fabrication to manufacture illegal copies ("clones") of the IC.

- (iii) Hardware Trojan insertion: The design can be modified in the design house or in the fab by malicious insertion, deletion or modification of circuits, referred to as Hardware Trojans, which cause the IC to deviate from its intended functional behavior during deployment. Typically, these Trojan circuits are stealthy by design, which makes it extremely challenging to detect them by traditional post-manufacturing testing.

- (iv) Secret information leakage: Although the "deploy and monitor" step of the design flow has been shown to be completely trustable in Figure 1.1, in reality, it has been shown that secret information can be extracted by an adversary from secure ICs with cryptographic functionality in this stage (for example, by side-channel analysis). Such threats increase with increasing controllability and observability of the internal nodes of the circuit as a result of widespread adoption of "Design for Testability" (DfT) techniques in modern ICs.

As a result of more recent advances in computation, malicious foundries and fabrication houses may also use satisfiability checking tools such as *binary SAT solvers* along with state-of-the-art circuit simulation tools to find hidden copyright information such as keys belonging to the holder of IP rights. This powerful logic decryption technique has been recently demonstrated in [9].

In the face of these vulnerabilities, an IP Vendor may have the following validation questions about the security of the IC design cycle:

- (i) Is the design true to specifications?

- (ii) Does the IC perform its intended functions and nothing more? If not, how to check for unknown behaviors or additional unwanted/unintended functionality?

- (iii) For reconfigurable devices, does the configuration data accurately represent the specification, design, and synthesis?

- (iv) How to check for inserted circuits or hardware time bombs during fabrication?

- (v) How to check for authentication post-fabrication?

These are important questions. To complicate matters, modern ICs consist of over 20 patterned layers of metals, insulators and semiconductors, with smallest feature sizes at 45nm and decreasing. The patterns are "burned in" by shining a 193-nm ArF laser through chromium-quartz masks in a tightly controlled process at fabrication facilities. A mask set contains a complete physical representation of an IC. Contract fabs produce masks from large computer files supplied by their clients. The IC descriptions given to fabs are often customized to satisfy a fab's specific requirements, but if stolen, they may conceivably be adjusted to another fab, and leading-edge fabs are concerned about this. Another form of piracy is for the contracted fab to produce more chips than authorized, at a very small additional cost, and sell them on the black market. A simple anti-piracy measure is wafer banking, also called split fabrication, i.e., contracting out different layers of a chip to different manufacturers. Not only is this expensive, but it prevents fabs from testing ICs which hampers yield analysis and improvement. Fabricating features smaller than half of 193nm (the ArF laser's wavelength) is increasingly difficult, and no viable replacements to ArF lasers are expected in the near future.

To compensate for optical diffraction, mask patterns are much more complex than the manufactured patterns and may be harder to reverse-engineer by delamination or otherwise. Physically modifying fine-grain features of ICs after manufacturing, to defeat anti-piracy measures, is very difficult.

The Focused Ion Beam (FIB) technique is sometimes used to reconnect wires during post-silicon debugging, but remains too slow and expensive for mass production, and will likely be infeasible for ICs with 32nm features [6].

The mechanisms employed in pirating IP designs demonstrate that the threat to the IP vendor is very real, with many untrustworthy components in the global supply chain. This has huge implications for the semiconductor industry, where Reverse Engineering has become a powerful tool for intellectual property (IP) piracy, in which the attacker analyzes the design and reproduces it with no or much less investment in research and development. These low cost illegitimate products can be sold at a much lower price, giving them an unfair competitive edge against the authentic products. Moreover, when the high level functionality of the target circuit is extracted, the attacker can redesign the circuit to obtain a new design that will appear different from the target circuit in order to avoid the infringement of copyright. The financial risk alone due to counterfeit and unauthorized ICs was estimated to be over \$169 billion a year by IHS Technology in 2012 [10]. Besides financial losses, this issue potentially has national security implications. The Semiconductor Industry Association (SIA) estimates that 15% of all spare and replacement semiconductors purchased by the Pentagon are counterfeit with a large contribution coming from hardware IPs [9].

Having established the importance of, and need for secure hardware IP design, devising an effective circuit obfuscation methodology that mitigates the effects of the security vulnerabilities in the IC design cycle with minimal overhead on design, fabrication and testing of ICs is the main motivation for this research.

--Jodi Rell

#### CHAPTER 2: SURVEY OF EXISTING HARDWARE IP SECURITY SOLUTIONS

From the discussion in Chapter 1, it is clear that hardware IP has become the foundation and the root of trust of any security system. In recent years, a growing number of software-based security solutions have been migrated to hardware-based security solutions for much enhanced resistance to software-based security threats. Such systems range from smartcards to specialized secure co-processing boxes, wherein hardware provides the source of security and trust for a number of security primitives. Examples include Trusted Platform Module (TPM) and Physical Unclonable Function (PUF) applications.

As previously mentioned, a supply chain adversary's capability is rooted in his knowledge of the hardware design. Successful hardware design obfuscation would severely limit a supply chain adversary's capability if not prevent all supply chain attacks. However, not all designs are obfuscatable in traditional technologies.

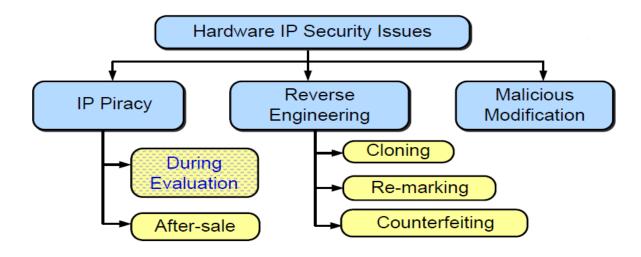

Figure 2.1: Taxonomy of Hardware IP Security Issues (from Narasimhan et al.2012)

Evaluation of hardware Intellectual Property (IP) cores is an important step in an IP-based system-on-chip (SoC) design flow. From the perspective of both IP vendors and Integrated Circuit (IC) designers, it is desirable that hardware IPs can be freely evaluated before purchase, similar to their software counterparts. However, protection of these IPs against piracy during evaluation is a major concern for the IP vendors. Existing solutions typically use encryption and vendor-specific toolsets, which may be unacceptable due to lack of flexibility to use in-house or third-party design tools. To prevent IP piracy, the IP vendors traditionally enforce a binding licensing agreement with the design house. Alternatively, they provide an IP in encrypted form. The decryption process is accomplished with a vendor-specific design platform for simulation and synthesis. The latter approach is prevalent in field programmable gate array (FPGA)-based design framework. On the other hand, some IP vendors allow simulation of the downloaded IP, but do not allow it to be synthesized to gate-level designs or bit streams (for FPGA platforms). Such practices, however, force a SoC designer to evaluate only the IP's functional behavior, but not the important quality parameters. To overcome the shortcomings of existing IP evaluation practices, a recent industry initiative has resulted in a design platform, which allows designers to download and use encrypted IPs from vendor websites. The synthesis and simulation tools in this design platform are capable of working in a user transparent manner based on a technology undergoing IEEE standardization. However, it mandates the use of a particular design platform throughout the design flow, which may not be acceptable for modern SoC designers, who typically use different software tools from diverse vendors as well as in-house design tools [12].

Post evaluation, and after-sale, the threat to IP security grows with increased exposure to market elements. A counterfeit component (i) is an unauthorized copy; (ii) does not conform to the Original Component Manufacturer (OCM) design, model, and/or performance standards; (iii) is not produced by the OCM or is produced by unauthorized contractors; (iv) is an off-specification, defective, or used OCM product sold as "new" or working; or (v) has incorrect or false markings and/or documentation [14].

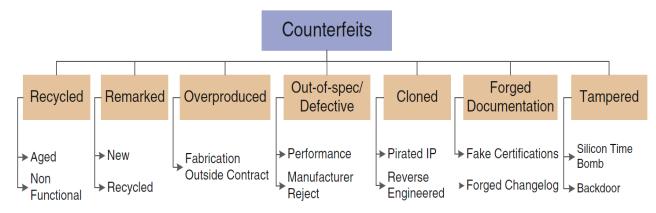

Based on the definitions above and analyzing supply chain vulnerabilities, we classify the counterfeit types into seven distinct categories shown in Fig. 2.2.

Figure 2.2: Taxonomy of Counterfeit types (from Tehranipoor et al. 2014 [14])

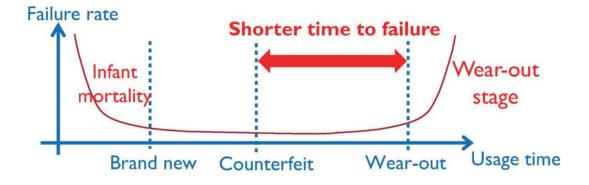

As recently as 2011, it was estimated that counterfeit circuits make up approximately 1% of the market with a financial loss of approximately \$100 billion worldwide [5]. In addition, the number of reported counterfeiting incidents quadrupled between 2009 and 2011 [6]. Many of these counterfeit devices find their way into mission critical devices for the military and aerospace. These ICs can be of poorer quality and fail quicker than brand new devices from a trusted seller, as seen in Figure 2.3. A quicker fail time may lead to a number of ill-effects as specified in **Error! Reference source not found.**

Figure 2.3: Classical bathtub curve, illustrating typical device failure characteristics[27]

**Table I: Possible Effects of Counterfeit ICs [15]**

| Government                                  | Industry                                     | Consumer                                                      |

|---------------------------------------------|----------------------------------------------|---------------------------------------------------------------|

| National security or civilian safety issues | Costs to mitigate this risk                  | Costs when products fail due to lower quality and reliability |

| Costs of enforcement                        | Costs to replace failed parts                | of counterfeit parts                                          |

| Lost tax revenue due                        | Lost sales                                   | Potential cofety                                              |

| to illegal sales of counterfeit parts       | Lost brand value or damage to business image | Potential safety concerns                                     |

With this increasing vulnerability of hardware IPs to piracy, investigation of IP protection techniques has become an emerging area of research. Recent investigations have targeted hardware IP protection benefiting IP vendors, IC designers, or both.

Existing solutions to protect IPs from piracy and reverse-engineering both in the evaluation phase and after sale, include passive defenses like *digital watermarking* which incorporates a hard-to-remove *digital signature* in an IP; wherein the designer embeds additional features (e.g. in the form of design constraints) into the Finite State Machine (FSM) which is similar to hardware Trojan insertion. It helps to establish the author's ownership in case of litigation. However, the added information is for proof of authorship, and does not carry any malicious functionality (as a hardware Trojan does). There is a rich body of research work on FSM watermarking for the protection of FSM design intellectual property. These techniques usually rely on the modification of the state transition graph at the behavioral synthesis level to embed a watermark related to user-specific information for identification purposes. Oliveira, in his famous paper, proposes creating watermarks based on a set of redundant states that can only be traversed when a user-specific

input sequence is loaded [Oliveira 2001]. Others have proposed watermarking schemes based on state encoding, or by introducing extra state transitions in the FSM to produce output that carries the watermark. An improvement on this method was suggested by utilizing the existing transitions for watermarking to successfully reduce the high-overhead caused by extra state transitions. These approaches are referenced in [9]. Additionally, some *soft IP* protection methods perform string modifications of the RTL plain-text to obfuscate it by affecting its human comprehensibility. However, they do not affect the *black box functionality* of the IP.

Other prevalent techniques to counter hardware IP Piracy incorporate active defenses like encryption (coupled with requirement to use vendor-specific tools), hardware metering, and layout level circuit obfuscation. In [6], an IC protection technique ensures that every instance of an IC manufactured in the foundry requires an instance-specific enabling pattern from the IC designer to be operational. It prevents the manufacturing of illegal clones of an IC in a fabrication house. In [5], a gate-level IP obfuscation technique has been proposed that allows the IP to be used only after a pre-defined *initialization key* (sequence of input vectors) is applied.

Note that these IP protection techniques are not directly applicable for protecting evaluation versions of an IP. Passive techniques for IP protection do not prevent a SoC designer from stealing the IP, cloning it, or performing illegal fabrication. For example; the digital watermark does not affect the functionality and usability of a stolen IP. The techniques in [5] and [6] which involve key insertion are only useful for protection of an IP post-evaluation, because the *initialization key is* provided to a trusted design house after legal purchase.

At a closer analysis, all the existing cryptographic primitives have proofs of security based on two broad assumptions:

(1) **Read-proof hardware**; that is, hardware that prevents an enemy from reading anything about the information stored within it, e.g. due to the computational complexity of the task; and

(2) **Tamper-proof hardware;** that is, hardware that prevents an enemy from changing anything in the information stored within it. In particular, existing cryptographic schemes consist of an algorithm which the adversary knows, but cannot change, (i.e., the key is stored in tamper-proof hardware), and a secret key, which the adversary does not know and cannot change (i.e., stored in hardware which is both read-proof and tamper-proof).

#### 2.1 Hardware IP Protection Approaches

Hardware IP protection has been investigated earlier in diverse contexts, addressing licensed as well as the pre-license evaluation version of an IP. Previous work on IP protection can be broadly classified into two main categories:

(i) Authentication based protection, and

(ii) Obfuscation based protection

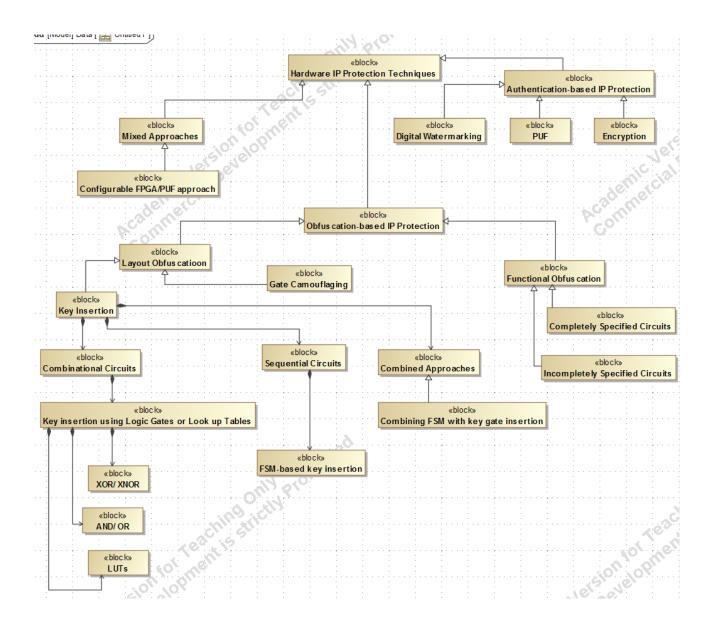

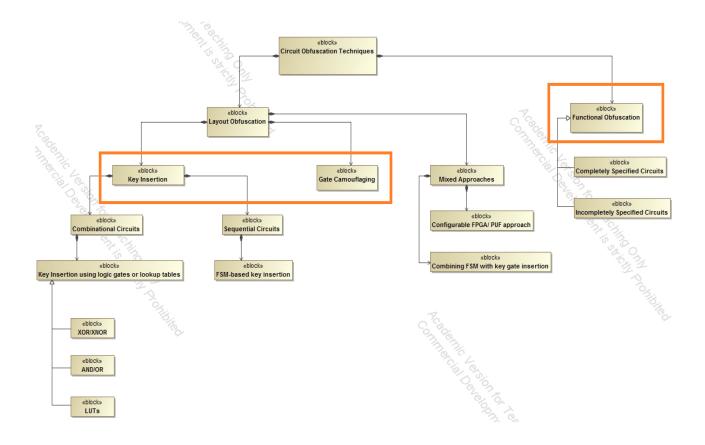

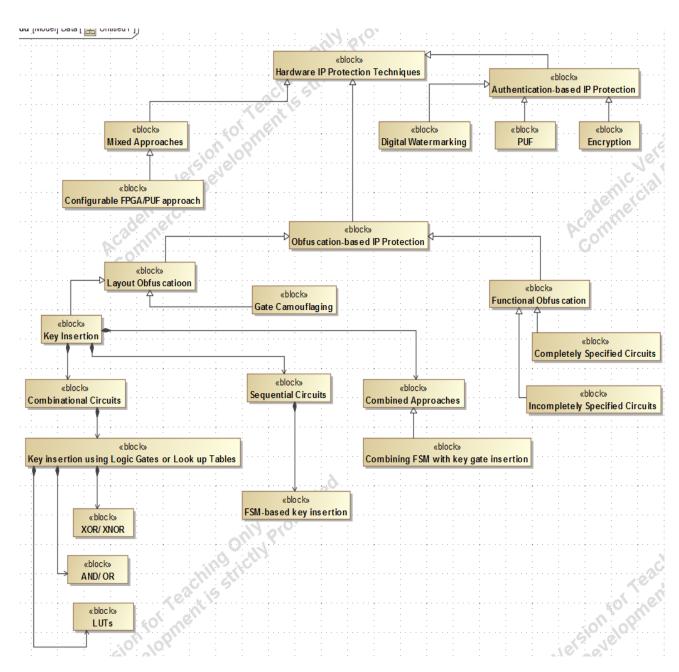

Figure 2.4 shows the taxonomy of hardware IP protection techniques which are broadly classified into authentication-based IP protection and obfuscation-based IP protection.

Figure 2.4: Taxonomy of Hardware IP Protection Techniques (see Appendix-1)

These two approaches are briefly explained next.

#### 2.1.1 Authentication based IP Protection

To protect the rights of the IP vendor through authentication, the approaches proposed are directed towards embedding a Digital Watermark or identifier in the design which helps to authenticate the design at a later stage or in case of litigation. Since a digital copy of data is the same as the original, digital watermarking is a passive protection tool. It just marks data, but does not degrade it or control access to

the data. One application of digital watermarking is *source tracking* in a commercial enterprise (such as movie distribution). A watermark is embedded into a digital signal at each point of distribution. If a copy of the work is found later, then the watermark may be retrieved from the copy and the source of the distribution is known. This technique reportedly has been used to detect the source of illegally copied movies, and is now being applied to hardware design. Typically this is inserted by design modifications which result in one or multiple input-output response pair(s) which do not arise during the normal functioning of the IP. Such digital signatures are known only to the IP vendor. Since this digital watermark (or signature) cannot be removed from the IP, it helps to prove an illegal use of such a component in litigation. However, the effectiveness of authentication-based IP protection schemes is limited by the fact that these techniques are passive and hence they cannot prevent the stolen IP from being used as a black box.

The approaches directed towards protecting the rights of the IC designer, on the other hand, ensure that the design house has knowledge of every IC instance manufactured and sold in the market using a technique called 'IC fingerprinting' which ensures that a unique identifier is associated with every instance of the IC sold in the market. A recent IC fingerprinting technique has made use of observability and satisfiability don't care conditions inherent in the circuit to hide fingerprinting information which is essentially a unique ID for the integrated IC or batch of ICs. (Carson Dunbar and Gang Qu, 2014).

It is interesting to note that the need of obfuscation to protect ICs against possible reverse-engineering and copy was investigated long back in the mid-1970s, coinciding with the commercial release of the first generation microprocessors. However, the scalability of the technique to larger designs by adopting a systematic approach of hardware obfuscation was not explored. Usually, this is implemented by including a locking mechanism in the IC. The fabrication facility would require a unique bit sequence provided by the design house to "unlock" the IC. However, such approaches cannot prevent the possibility of reverse-engineering a design to expose its functionality as well as the security scheme. Moreover, they do not

address protecting the right of an IP vendor because illegal copies of the device can be used as a black box after the key has been revealed to the design house. In this case, a PUF-based approach is more authentic compared to a key-based encryption technique as it uniquely identifies each instance of the IC.

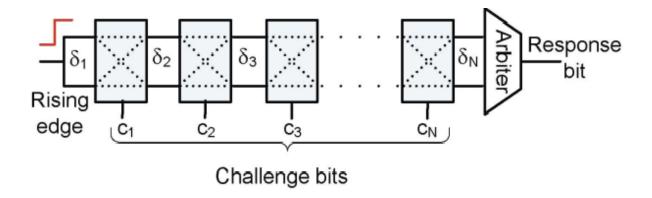

#### **Authentication based on Physical Unclonable Function (PUF)**

Physical Unclonable Function (PUF) is a multi-input hardware device that produces difficult to predict outputs that are unique to each instantiation of identical devices by extracting a silicon chip's inherent fabrication variability. When a physical stimulus is applied to the structure, it reacts in an unpredictable (but repeatable) way due to the complex interaction of the stimulus with the physical microstructure of the device (see Figure 2.5). This exact microstructure depends on physical factors introduced during manufacturing which are unpredictable (like a fair coin). The applied stimulus is called the challenge, and the reaction of the PUF is called the response. A specific challenge and its corresponding response together form a challenge—response pair or CRP. For example, in Figure 2.5, challenge bits C1,C2,C3,...CN are applied to the PUF at the rising edge of the clock. Each block in the PUF is a multiplexer that dictates the path of the bits through the structure. Analog timing difference on the two paths determines the response bit of the PUF, as determined by the Arbiter, which may be a D flip-flop. The device's identity is therefore established by the properties of the microstructure itself. As this structure is not directly revealed by the challenge-response mechanism such a device is resistant to spoofing and piracy attacks. These variability-induced delays or switching thresholds can be conveniently used for authentication as a PUF response will be unique and reliable even for chips manufactured from the same wafer.

Due to these features, PUF is one of the most popular and widely-used hardware security primitives. It is used in a variety of hardware-based security protocols ranging from generation of random numbers to secure storage of privileged information and public key cryptography.

Figure 2.5: A Delay-based Arbiter PUF

However, until recently all PUFs have been analog devices and therefore greatly influenced by operational and environmental conditions and subject to change of their mapping function due to device aging. Very recently, digital PUFs have been developed that eliminate all these drawbacks of analog PUFs. Even more importantly, they are faster, require less energy, and can be easily integrated within conventional digital logic.

However, digital PUFs still face certain limitations. Of most importance are potential susceptibility to sidechannel attacks and a relatively small number of challenge-response pairs. When using a PUF, particularly a delay based arbiter PUF as shown in Figure 2.5, the delay overhead will increase dramatically. More importantly, PUF has an inherent defect: reliability. If the reliability is not guaranteed, that is when the bit flips happen, the circuit will output wrong result.

The second kind of IP Protection approach is based on obfuscation, i.e. modifying the layout (structure) or functionality (behavior) of a circuit so as to make it difficult to reverse engineer i.e. more time-consuming or computationally expensive.

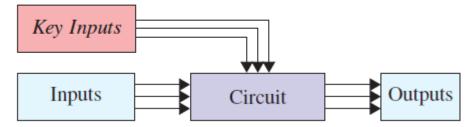

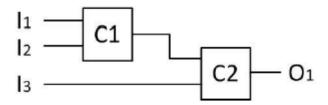

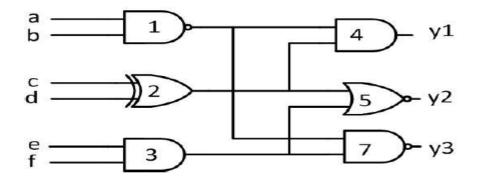

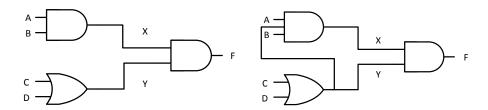

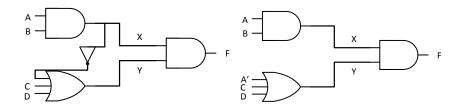

Figure 2.6: Circuit Obfuscation techniques (a) Layout Obfuscation, and (b) Functional or Logic Obfuscation

#### 2.1.2 Obfuscation based IP Protection

Hardware obfuscation is a technique by which the structure or the functional description (behavior) of electronic hardware is modified to intentionally conceal its functionality, which makes it significantly more difficult to reverse-engineer. In essence, it is different from digital watermarking (where proof of ownership is concealed in the digital content itself), or from hardware intellectual property (IP) watermarking where the ownership information is embedded and concealed in the description of a circuit. Hardware obfuscation aims at minimizing the threats at IP or chip level discussed earlier, such as IP infringement, reverse engineering of the manufactured ICs (in fabrication facilities) to produce counterfeit or clone ICs; and malicious modifications of an IP through the insertion of hardware Trojan to cause in-field functional failure by making it difficult for an adversary to comprehend the actual functionality of a design through structural or behavioral modifications. Hardware obfuscation techniques can be classified into two main categories:

(a) the techniques like structural or layout-level modifications, which do not directly affect the functionality of the electronic system, and (b) those techniques which directly alter the functionality of the system.

#### 2.1.2.1 Layout or Structural Obfuscation

This approach modifies the circuit layout without affecting its functionality. Layout-level or structural obfuscation is performed in two ways: (a) key insertion and (b) gate camouflaging.

### 2.1.2.1.1 Key insertion based approach

Key insertion based approaches insert the so-called key-gates (usually XOR and XNOR) to lock the circuit such that normal functionality of the obfuscated design can only be enabled by the successful application of a single pre-determined key (or a key from its equivalent class of keys) or a sequence of secret keys at the input; otherwise the circuit operates in a mode, which exhibits incorrect functionality. This can be done by embedding a well-hidden finite state machine (FSM) in the sequential circuit or by introducing key gates in a combinational circuit to control the functional modes based on application of key. One input of the key-gate will come from the primary input of the circuit so that the user can enter the key, the other input is a circuit node. The circuit will be unlocked when the inputs to the key gates are fed with a valid key. Otherwise the circuit will not perform the desired functionality. Multiplexers and LUTs have also been used to provide a logic barrier between normal and obfuscated modes of circuit.

The technique of key-based, active hardware obfuscation is similar in principle to private-key cryptographic approaches for information protection, since the "key sequence" for the obfuscated design plays a similar role as the cryptographic key. The technique can be applied at different levels of hardware description, namely gate-level or register transfer level (RTL) design and hence can be used to protect soft, firm or hard IP cores. In a practice widely adopted by the industry, the HDL source code is encrypted and the IP vendor provides the key to decrypt the source code only to its valid customers. However, this technique may enforce the use of a particular design platform, a situation that might be unacceptable to many SoC

designers who seek the flexibility of multiple tools from diverse vendors for design and evaluation purposes.

Moreover, none of these techniques prevent possible reverse-engineering effort at later stages of the design and manufacturing flow.

#### **Key Insertion Mechanism and Attack Strategy**

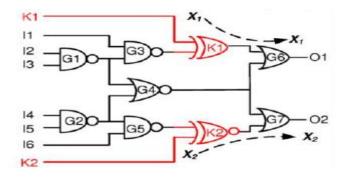

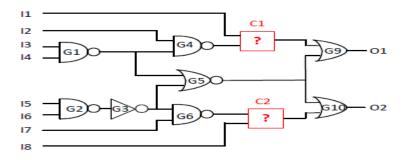

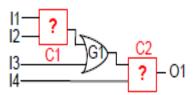

The first and one of the most well-studied key insertion approach is the "EPIC" mechanism ("Ending Piracy in Integrated Circuits") proposed by Roy et al. in 2008 [6]. Figure 2.7 is a motivation example of their approach. It shows a circuit with two key-gates K1 and K2 with key values K1=0 and K2=1. We can see that with incorrect key values, the obfuscated circuit will not function correctly. Therefore, the success of this approach relies on the assumption that RE attackers can only study the input-output behavior revealing the functionality of the circuit. The weakness of EPIC, as pointed out in [15], is that: when an attacker opens up the chip and learns particulars of the design, he can use deliberately selected input signals to control the circuit such that the secret keys will be exposed at the output pins (for example, by setting I1=1, I2=0, and I3=0 in Figure 2.7 the value of K1 is sensitized to output O1). Therefore, the complexity of obfuscation can be reduced to linear time rather than the exponential time as expected. Even if brute forcing the circuit is not computationally feasible due to a large number of key gates, other logic decryption techniques have been proposed that use Boolean SAT solvers to resolve the key gates in the circuit, no matter how numerous [9].

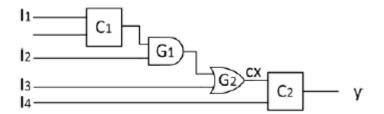

Figure 2.7: Key-gate Insertion: Motivation Example in [6]

Rajendran et al. [21] propose an enhanced obfuscation method to prevent the key values from being propagated to the output (as shown in Figure 2.8).

Figure 2.8: A smarter key insertion strategy to thwart key propagation to the output. K1 cannot be determined without knowing K2 and vice versa

They partition the circuit into the following categories:

- 1) **Runs of key-gates:** A set of key-gates connected in back-to-back fashion. They can be replaced by a single key gate, reducing the complexity of brute force.

- 2) **Isolated key-gates:** A gate that has no path from it to all the other key-gates. In this case, resolve the key gate individually, without considering the other key gate.

- 3) **Dominating key-gates:** Gate K2 is the dominating key-gate of K1 if K2 lies on every path between K1 and the outputs. In this case, the strategy is to "divide and conquer", i.e. by muting the gate K1 and simultaneously sensitizing the value of the dominating key gate to an output, to resolve key gate K1.

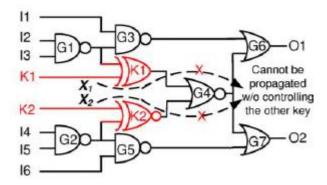

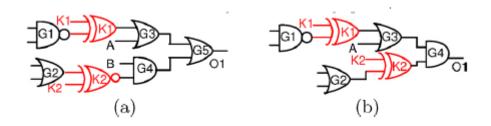

- 4) **Convergent key-gates:** Even if there are no paths between two key-gates, the sensitization paths might interfere. Such scenarios happen if these two or more key-gates converge. Depending upon the type of convergence, key-gates can be classified into 1) concurrently mutable, 2) sequentially mutable, and 3) non-mutable key-gates.

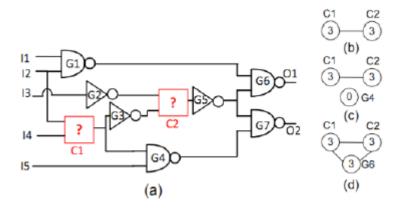

Figure 2.9: (a) Concurrently mutable key-gates: K1 and K2 converge at G5 and can be muted. (b) Sequentially mutable key gates: K1 and K2 converge at G4, but only K1 can be muted [15].

If two key-gates K1 and K2 converge at some other gate, such that neither of the key bits can be muted, then K1 and K2 are called non-mutable convergent key-gates. The only way to resolve such gates is through brute force [21]. Therefore, a designer would want to maximize the number of non-mutable key gates in the circuit.

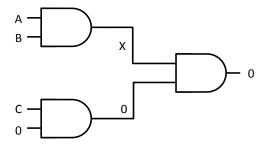

The authors in [21] therefore recommend an insertion strategy to maximally reduce the probability of finding golden patterns (patterns that simultaneously sensitize the target key to the output while muting the other keys) and to increase the brute force search efforts. Their idea is to let the inserted key-gates interfere with each other. One has to try all the combinations of the keys rather than isolating, muting or sensitizing them. The weakness of this recommended approach is that a SAT solver can be used to reduce the effort required to brute force the circuit and extract the keys by controlling the inputs to the key gates. Another potential weakness is that don't care conditions inherent in the circuit can be used to effectively isolate the key gates from each other, reducing RE complexity. Once this occurs, it may be possible to find more golden patterns in the circuit and resolve the functionality of key gates (see section 3.3.3).

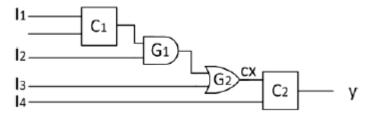

Figure 2.10: Don't care conditions in the circuit lower RE Complexity; C2 can be resolved easily by setting I3=1 and controlling I4, essentially making it an isolated key-gate

Finally, another defect is that the fan-in cone of different outputs will break the interference of key-gates, making RE attacks much easier than anticipated. A key gate that falls outside of the intersection of two or more outputs can be easily isolated and sensitized to its output. Locating such gates will bypass the influences from other key-gates in other cones (see 3.4.2). We use this observation to come up with an arguably stronger encryption strategy in Chapter 3. Next, we mention an emerging technique for logic decryption using Boolean SAT solvers. This technique is very effective against encryption algorithms that do not judiciously select key gates and that do not camouflage the said key gates. Judicious selection here means selecting gates that are non-mutable and cannot be isolated from each other.

#### **Logic Decryption Attacks using SAT Solvers**

The attacker's goal is to determine the key values to unlock the circuit. Once the attacker unlocks the circuit, he/she can extract the functionality for some malicious usage. The key insertion based obfuscation approach illustrated in Figure 2.8 is not very effective against such an attacker, even if brute forcing the circuit is computationally infeasible. An explanation of the weakness of the approach follows.

## Tamper-Proof Memory

Figure 2.11: Overview of Key Insertion based Approach

Key insertion approach rests upon the assumption that *the foundry does not know and cannot compute* the correct values of the key inputs. Otherwise, the foundry could just program these values and overproduction could not be prevented.

**Attack Model:** Considering a malicious foundry, we assume the attacker has access to layout and mask information. The gate-level netlist can be reverse-engineered from this.

We also assume that the attacker has access to an activated IC on which to apply input patterns and observe outputs. This could be obtained by purchasing an activated IC from the open market. The components of our attack model are therefore: (i) a gate-level netlist of the encrypted IC and (ii) a means for applying arbitrary input patterns and observing the resultant outputs on an activated IC.

**Potential Attacks:** Given the above attack model, an attack is possible when an attacker can determine the correct values of the key inputs. Let us consider potential attacks.

The naive idea of brute-force search does not work. If the circuit has M inputs and L key inputs, this requires 2M observations from an activated IC and O(2M+L) computations on the encrypted design. Clearly, this is not practical.

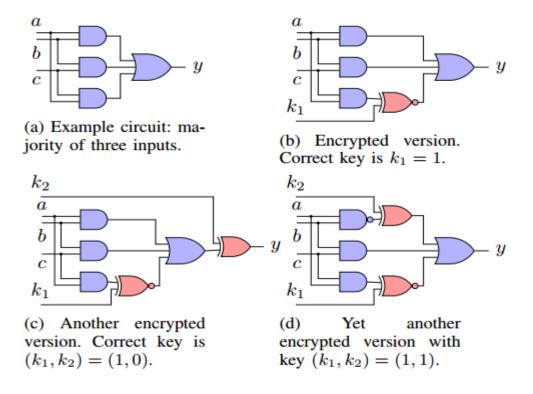

Figure 2.12: Some simple key-insertion examples [9]

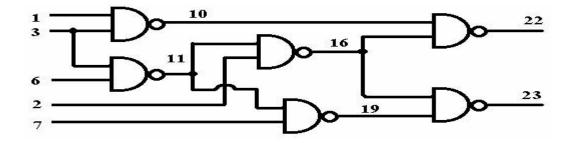

Rajendran et al. [15] propose using automatic test pattern generation (ATPG) tools to generate input

patterns that expose the value of a key input. In Figure 2.12(b), when the input is a = b = c = 0, the output is y = -k1. Therefore, an ATPG tool can find such patterns to reveal keys. But in Figure 2.12(c), no input pattern can expose k1 if k2 is also unknown. The solution is to first attack k2 with the pattern a = b = c = 1. From this we deduce k2 = 0. Now attacking k1 is possible. But even this strategy does not guarantee a successful attack. For the circuit in Figure 2.12(d), there is no single input pattern that can reveal the value of either k1 or k2. Therefore, if logic encryption is done carefully, the fault-analysis attack is ineffective [9]. Formal analyses can potentially be used to attack logic encryption. It is possible to formulate the attack as a solution to a Quantified Boolean Formula (QBF). Suppose the original circuit is represented by the Boolean function  $C_0(X)$ , and its encrypted version is represented by C(X, K). Here X and K are the circuit's primary inputs and key inputs respectively. We can retrieve the key by solving the QBF:

$\exists K \ \forall X \ C(X, K) = C_o(X)$

In plain English, the QBF attempts finds an assignment to the key inputs K such that for all values of the

primary inputs X, the functions C and Co are equal. While we do have relatively efficient algorithms to solve

this particular type of QBF, the formulation itself is moot. The attacker does not have access to the

unencrypted IC's gate-level netlist and cannot construct the formula  $C_o(X)$ .

The attacker can only observe the outputs for a small set of input patterns on the activated IC and must

somehow determine the key values from these observations. Given a set of input/output observations, a

SAT solver can determine a key value that is consistent with these observations. But this key value may not

be correct. For example, suppose we make the observation y = 1 when a = b = c = 1 in Figure 2.12(b). Given

this information, a SAT solver may assign k1 = 0 since this value is consistent with the above observation.

Even if we provide additional observations to the solver, e.g., (a, b, c, y) = (1, 1, 0, 1) and (a, b, c, y) = (0, 1, 1, 1, 0, 1)

1), k1 = 0 is still a valid solution. While we are guaranteed that the solver returns a key value that yields the

correct output for the input patterns observed thus far, there may be other input patterns for which this key

value produces incorrect output. Furthermore, even if the SAT solver returns the correct key, verifying its

correctness seemingly requires evaluation of outputs for all possible input patterns ( $2^M$  in a circuit with M

inputs). Clearly, it is impractical to apply these many input patterns and so a simple SAT formulation is not

enough.

Malik et.al. [9] provide interesting insights to resolve this SAT problem. First, instead of considering key

values individually, they consider equivalence classes of keys. They define two keys K1 and K2 to be

equivalent, denoted as  $K1 \equiv K2$ , if and only if for each input value Xi, the encrypted circuit produces the

same output value *Yi* for both keys *K*1 and *K*2. Precisely stated:

$K1 \equiv K2 \text{ iff } \forall Xi : C(Xi, K1, Yi) \land C(Xi, K2, Yi).$

30

The intuition is that instead of finding the correct key, they are looking for a member of the equivalence class of keys which produces the correct output for all input patterns. To "zero-in" on the correct equivalence class, they iteratively rule out equivalence classes which produce the wrong output value for at least one input pattern. Given two key values K1 and K2, define the input pattern Xd as a distinguishing input pattern if the encrypted circuit outputs different values Yd1 and Yd2 when the key inputs are set to K1 and K2 respectively. More precisely, Xd is a distinguishing input pattern for K1 and K2 iff C(Xd,K1,Yd1) A C(Xd,K2,Yd2) A  $(Yd1 \neq Yd2)$ .

The second insight is that if a distinguishing input pattern Xd is found, then they could examine the output of the activated IC for input Xd and use this to rule out one (or both) of K1 and K2 as not being in the equivalence class of correct keys. This suggests Algorithm 1 which repeatedly finds distinguishing inputs (line 4) for some two keys K1 and K2, while asserting that the encrypted circuit must have outputs consistent with the input/output patterns observed thus far on the activated IC (line 6). The loop ends when no distinguishing inputs can be found. The correct key value is any assignment to K1 or K2 that satisfies the formula Fi (line 9).

```

Algorithm 1 Logic Decryption Algorithm

```

```

Function: decrypt.

Inputs: C and eval.

Output: \vec{K_C}.

1: i := 1

2: F_1 = C(\vec{X}, \vec{K_1}, \vec{Y_1}) \wedge C(\vec{X}, \vec{K_2}, \vec{Y_2})

3: while sat[F_i \wedge (\vec{Y_1} \neq \vec{Y_2})] do

4: \vec{X}_i^d := sat\_assignment_{\vec{X}}[F_i \wedge (\vec{Y_1} \neq \vec{Y_2})]

5: \vec{Y}_i^d := eval(\vec{X}_i^d)

6: F_{i+1} := F_i \wedge C(\vec{X}_i^d, \vec{K_1}, \vec{Y}_i^d) \wedge C(\vec{X}_i^d, \vec{K_2}, \vec{Y}_i^d)

7: i := i+1

8: end while

9: \vec{K_C} := sat\_assignment_{\vec{K_1}}(F_i)

```

Logic Decryption Algorithm suggested in [9]: the algorithm uses SAT solvers to resolve key gates and reduce complexity of brute force. Here C is the Boolean formulation of the gate-level circuit and eval is the output from the legitimate activated IC.