#### ABSTRACT

Title of dissertation: PERFORMANCE EXPLORATION OF

THE HYBRID MEMORY CUBE

Paul Rosenfeld, Doctor of Philosophy, 2014

Dissertation directed by: Bruce Jacob

Department of Electrical Engineering

The Hybrid Memory Cube (HMC) is an emerging main memory technology that leverages advances in 3D fabrication techniques to create a memory device with several DRAM dies stacked on top of a CMOS logic layer. The logic layer at the base of each stack contains several DRAM memory controllers that communicate with the host processor over high speed serial links using an abstracted packet interface. Each memory controller is connected to several memory banks in the DRAM stack with Through-Silicon Vias (TSVs), which are metal connections that extend vertically through each chip in the die stack. Since the TSVs form a dense interconnect with short path lengths, the data bus between the controller and memory banks can be operated at higher throughput and lower energy per bit compared to traditional Double Data Rate (DDRx) memories, which uses many long and parallel wires on the motherboard to communicate with the memory controller located on the CPU die. The TSV connections combined with the presence of multiple memory controllers near the memory arrays form a device that exposes significant memorylevel parallelism and is capable of delivering an order of magnitude more bandwidth than current DDRx solutions.

While the architecture of this type of device is still nascent, we present several parameter sweeps to highlight the performance characteristics and trade-offs in the HMC architecture. In the first part of this dissertation, we attempt to understand and optimize the architecture of a single HMC device that is not connected to any other HMCs. We begin by quantifying the impact of a packetized high-speed serial interface on the performance of the memory system and how it differs from current generation DDRx memories. Next, we perform a sensitivity analysis to gain insight into how various queue sizes, interconnect parameters, and DRAM timings affect the overall performance of the memory system. Then, we analyze several different cube configurations that are resource-constrained to illustrate the trade-offs in choosing the number of memory controllers, DRAM dies, and memory banks in the system. Finally, we use a full system simulation environment running multi-threaded workloads on top of an unmodified Linux kernel to compare the performance of HMC against DDRx and "ideal" memory systems. We conclude that today's CPU protocols such as coherent caches pose a problem for a high-throughput memory system such as the HMC. After removing the bottleneck, however, we see that memory intensive workloads can benefit significantly from the HMC's high bandwidth.

In addition to being used as a single HMC device attached to a CPU socket, the HMC allows two or more devices to be "chained" together to form a diverse set of topologies with unique performance characteristics. Since each HMC regenerates the high speed signal on its links, in theory any number of cubes can be connected together to extend the capacity of the memory system. There are, however, practical limits on the number of cubes and types of topologies that can be implemented.

In the second part of this work, we describe the challenges and performance impacts of chaining multiple HMC cubes together. We implement several cube topologies of two, four, and eight cubes and apply a number of different routing heuristics of varying complexity. We discuss the effects of the topology on the overall performance of the memory system and the practical limits of chaining. Finally, we quantify the impact of chaining on the execution of workloads using full-system simulation and show that chaining overheads are low enough for it to be a viable avenue to extend memory capacity.

# PERFORMANCE EXPLORATION OF THE HYBRID MEMORY CUBE

by

# Paul Rosenfeld

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2014

Advisory Committee:

Professor Bruce Jacob, Chair/Advisor

Professor Manoj Franklin

Professor Gang Qu

Professor Donald Yeung

Professor Jeffrey Hollingsworth, Dean's Representative

© Copyright by Paul Rosenfeld 2014 To my wonderful parents, Simon and Olga Rosenfeld

Without their support, none of this would have been possible.

#### Acknowledgments

First and foremost, I would like to acknowledge my family who has done everything in their power to support me in both my academic and personal life. My father's brilliance and boundless curiosity, my mother's encouragement and ability to ward off any oncoming panic attack with a few words, and my brother's unique perspective and guidance have all helped me focus on what is important. Their support underlies everything that I do, and I am thankful to have such wonderful people in my life.

I owe a special thanks to my girlfriend, Ivy Liu, who has had to endure a disproportionate number of computer references over the years. I imagine that she will forever think "memory fragmentation problem" when looking at a suboptimal seating arrangement (and for that, I apologize). She has helped me through several graduate school existential crises and has always been there for me—for that I am grateful.

Thanks to Elliott Cooper-Balis for being a friend and sounding board for ideas throughout my graduate school career. I wish all the best to the DRAM Ninjas past and present (Mu-Tien Chang, Ishwar Bhati, Jim Stevens, Paul Tschirhart). Avadh Patel who contributed so much of his time and effort furthering the open source and academic research communities and enabling our group's work. Arun Rodrigues for pulling us into the world of supercomputers. Finally, I would like to thank my advisor, Dr. Bruce Jacob, for his leadership and for always being our biggest proponent.

# Table of Contents

| Li | st of ' | Tables                                                 | vi |

|----|---------|--------------------------------------------------------|----|

| Li | st of I | Figures                                                | vi |

| Li | st of . | Abbreviations                                          | ix |

| 1  | Intro   | oduction Status Quo: Current Generation Memory Systems | 1  |

|    | 1.2     | Synchronous DRAM                                       | 2  |

|    | 1.3     | Currently Proposed Solutions                           | 6  |

|    |         | 1.3.1 DDR4                                             | 7  |

|    |         | 1.3.2 LRDIMM                                           | 8  |

|    |         | 1.3.3 Fully Buffered DIMM                              | 9  |

|    |         | 1.3.4 Buffer-on-Board                                  | 11 |

|    | 1.4     | Discussion of Proposed Solutions                       | 13 |

| 2  | Hyb     | rid Memory Cube Architecture                           | 16 |

|    | 2.1     | HMC Architecture                                       | 16 |

|    | 2.2     | Benefits of the HMC                                    | 23 |

|    |         | 2.2.1 Capacity                                         | 23 |

|    |         | 2.2.2 Parallelism and Aggregate Bandwidth              | 24 |

|    |         | 90 v                                                   | 25 |

|    |         | 2.2.4 Device Process Heterogeneity                     | 26 |

|    |         |                                                        | 26 |

|    |         | 2.2.6 Near-Memory Computation                          | 29 |

| 3  | Rela    | ated Work                                              | 30 |

|    | 3.1     | DRAM on CPU Stacking                                   | 30 |

|    | 3.2     | System Level Studies                                   | 31 |

|    | 3.3     |                                                        | 33 |

|    | 3.4     | Serially Attached Stacked DRAM                         | 34 |

| 4  | Met     | hodology                                               | 36 |

|    | 4.1     | HMC Simulator                                          | 36 |

|    | 4.2     | HMC Parameters                                         | 37 |

|    |         | 4.2.1 DRAM Timing Parameters                           | 37 |

|    |         | 4.2.2 Switch Interconnect                              | 38 |

|    |         | 4.2.3 Vault Controller                                 | 39 |

|    | 4.3     | Random Stream Methodology                              | 41 |

|    | 4.4     | Full System Simulation Methodology                     | 44 |

|    |         | $\Theta$                                               | 44 |

|    |         |                                                        | 48 |

|    |         | 4.4.3 Comparison Systems                               | 50 |

| 5  | Sing   | tle Cube Optimization                            | 52    |

|----|--------|--------------------------------------------------|-------|

|    | 5.1    | Motivation                                       | . 52  |

|    | 5.2    | Link Bandwidth Optimization                      | . 53  |

|    |        | 5.2.1 Link Efficiency and Read/Write Sensitivity |       |

|    |        | 5.2.2 Selecting Link/TSV Bandwidth               |       |

|    | 5.3    | Switch Parameters                                |       |

|    | 5.4    | Queuing Parameters                               |       |

|    |        | 5.4.1 Vault Command Queue Depth                  |       |

|    |        | 5.4.2 Vault Read Return Queue Depth              |       |

|    | 5.5    | Constrained Resource Sweep                       |       |

|    |        | 5.5.1 Vault/Partition Organization               |       |

|    |        | 5.5.2 Impact of Total Banks                      |       |

|    | 5.6    | Full System Simulation                           |       |

|    | 0.0    | 5.6.1 Memory Bandwidth Exploration               |       |

|    |        | 5.6.2 Workload Selection                         |       |

|    | 5.7    | Full System Results                              |       |

|    | 0.1    | 5.7.1 DRAM Sensitivity                           |       |

|    | 5.8    | Address Mapping                                  |       |

|    | 9.0    | 5.8.1 Single Cube Address Mapping Results        |       |

|    | 5.9    | Memory Performance Comparison                    |       |

|    | 5.5    | Memory 1 errormance Comparison                   | . 100 |

| 6  | Mul    | tiple Cube Topologies                            | 114   |

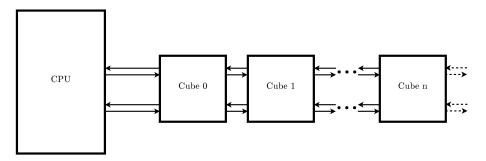

|    | 6.1    | HMC Chaining Background                          |       |

|    | 6.2    | Routing Background                               |       |

|    | 6.3    | Route Selection Algorithms                       |       |

|    | 0.0    | 6.3.1 Link Choosers                              |       |

|    |        | 6.3.1.1 Random                                   |       |

|    |        | 6.3.1.2 Address-based                            |       |

|    |        | 6.3.1.3 Buffer Space                             |       |

|    |        | 6.3.1.4 Read/Write Ratio                         |       |

|    |        | 6.3.2 Route Choosers                             |       |

|    |        | 6.3.2.1 Random                                   |       |

|    |        |                                                  |       |

|    |        |                                                  |       |

|    | 6.1    | 8                                                |       |

|    | 6.4    | Topologies                                       |       |

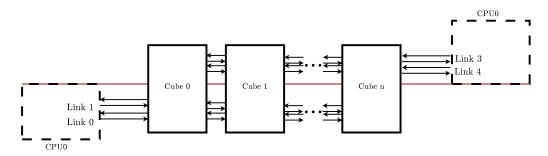

|    |        | 6.4.1 Chain                                      |       |

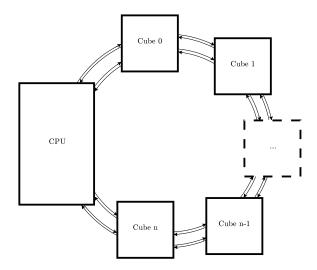

|    | CF     | 6.4.2 Ring                                       |       |

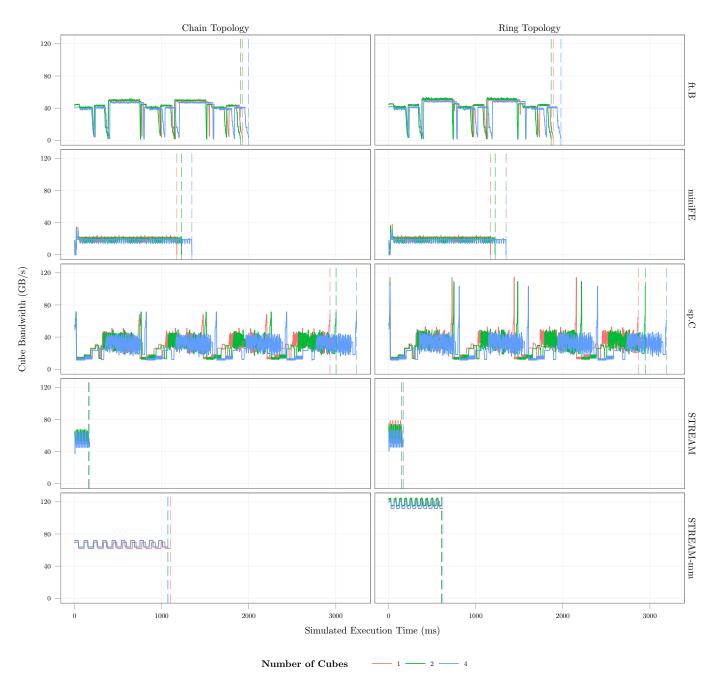

|    | 6.5    | Cube Topology Random Stream Results              |       |

|    |        | 6.5.1 Route Heuristics                           |       |

|    |        | 6.5.2 Full System Performance Impact             | . 134 |

| 7  | Con    | clusion                                          | 141   |

| Bi | bliogr | raphy                                            | 143   |

|    |        | - ·                                              |       |

# List of Tables

| $4.1 \\ 4.2$ | DRAM timing parameters used in simulations                                                                                                                  |   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

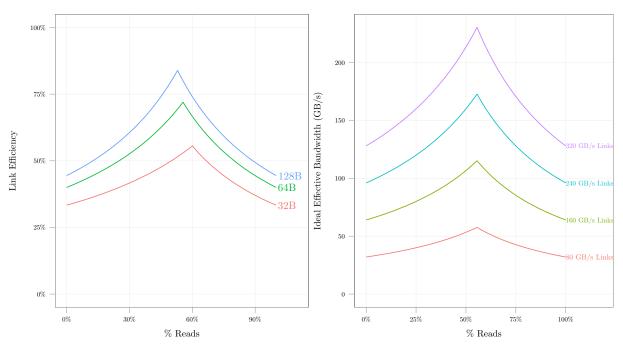

| 5.1          | Effective link bandwidth for various request sizes and a 16 byte overhead. Larger requests achieve higher effective bandwidth on the links. 50              | 6 |

| 5.2<br>5.3   | Effective theoretical peak link bandwidths for different read/write ratios 55 Speedup of workloads when increasing core count and changing coherence scheme | 8 |

| 6.1          | Memory bandwidth and execution time impact of cube chaining 13                                                                                              | 8 |

|              | List of Figures                                                                                                                                             |   |

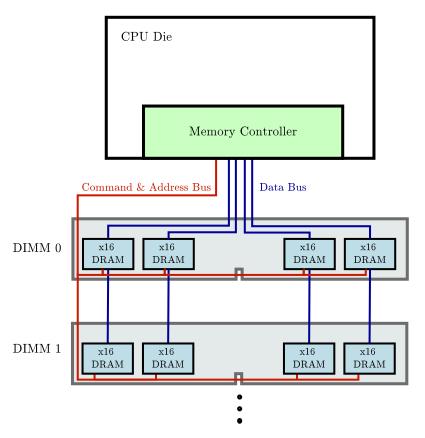

| 1.1          | One channel of a traditional DDRx memory system                                                                                                             |   |

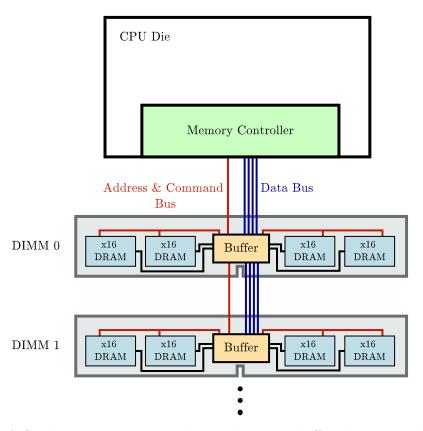

| 1.2<br>1.3   | A Single LRDIMM channel                                                                                                                                     |   |

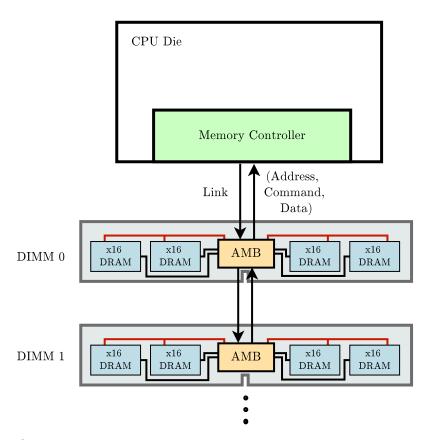

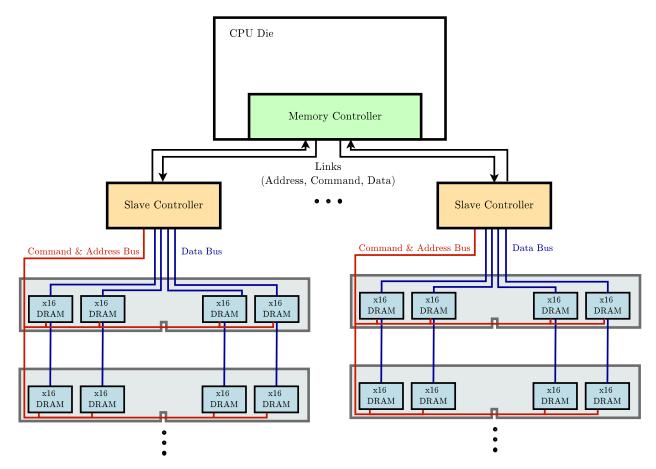

| 1.4          | A Buffer-on-Board memory system                                                                                                                             |   |

| 2.1<br>2.2   | A closeup of an HMC stack                                                                                                                                   |   |

| 2.2          | An artist's rendering of the HMC                                                                                                                            |   |

| 2.4          | A cross section of an HMC device                                                                                                                            |   |

| 2.5          | Comparison of HMC and DDRx DRAM dies                                                                                                                        |   |

|              | 2.5a Single HMC DRAM die                                                                                                                                    |   |

| 2.6          | 2.5b Samsung 2Gb DDR3 DRAM die                                                                                                                              |   |

| 3.1          | Two possible 3D rank organizations                                                                                                                          | 2 |

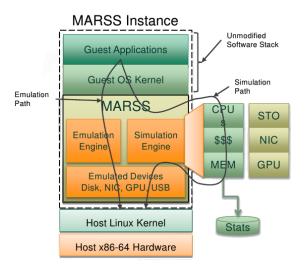

| 4.1          | A block diagram of the MARSSx86 simulator                                                                                                                   | 9 |

| 5.1          | Link efficiencies                                                                                                                                           |   |

|              | 5.1b Effective link bandwidth for 64 byte requests for different link speeds                                                                                |   |

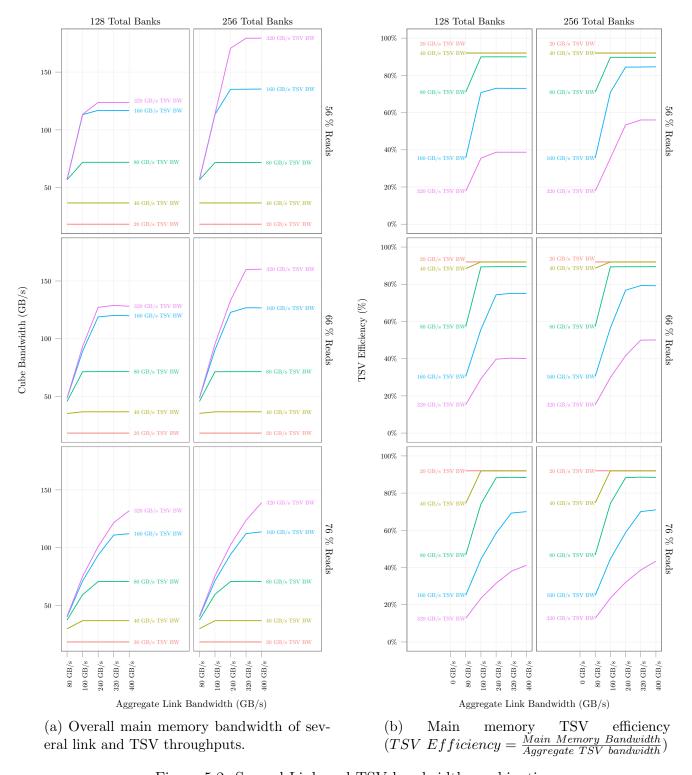

| 5.2          | Several Link and TSV bandwidth combinations 6                                                                                                               |   |

|              | 5.2a Overall main memory bandwidth of several link and TSV throughputs                                                                                      | 0 |

|              | 5.2b Main memory TSV efficiency 60                                                                                                                          | 0 |

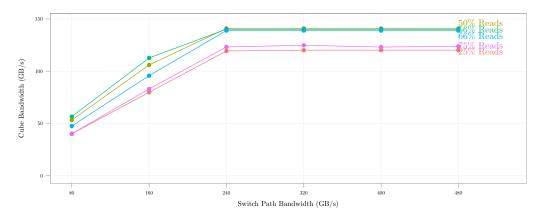

| 5.3          | Main memory bandwidth with several different data path widths and                                                                                           | า |

| 5.4          | read/write ratios                                                                                                                                           |   |

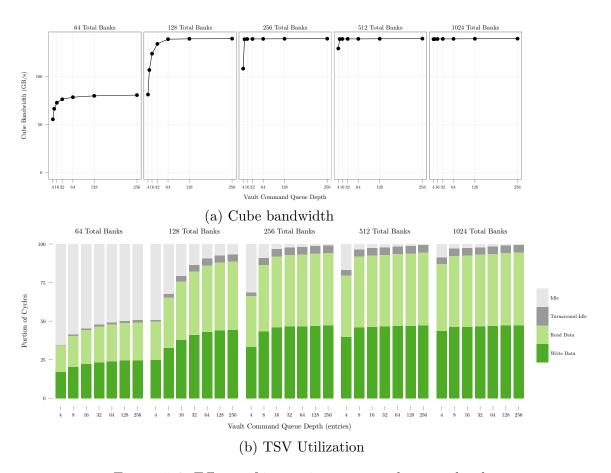

| J.T          | 5.4a Cube bandwidth                                                                                                                                         |   |

|      | 5.4b TSV Utilization                                                       | 65  |

|------|----------------------------------------------------------------------------|-----|

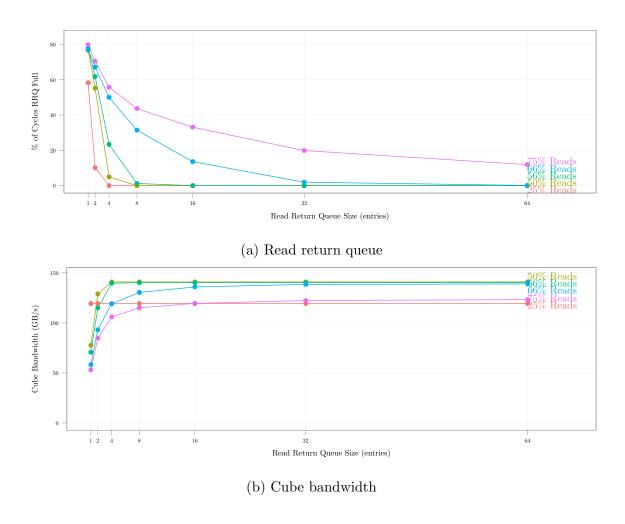

| 5.5  | Impact of increasing read return queue size                                | 67  |

|      | 5.5a Read return queue                                                     | 67  |

|      | 5.5b Cube bandwidth                                                        | 67  |

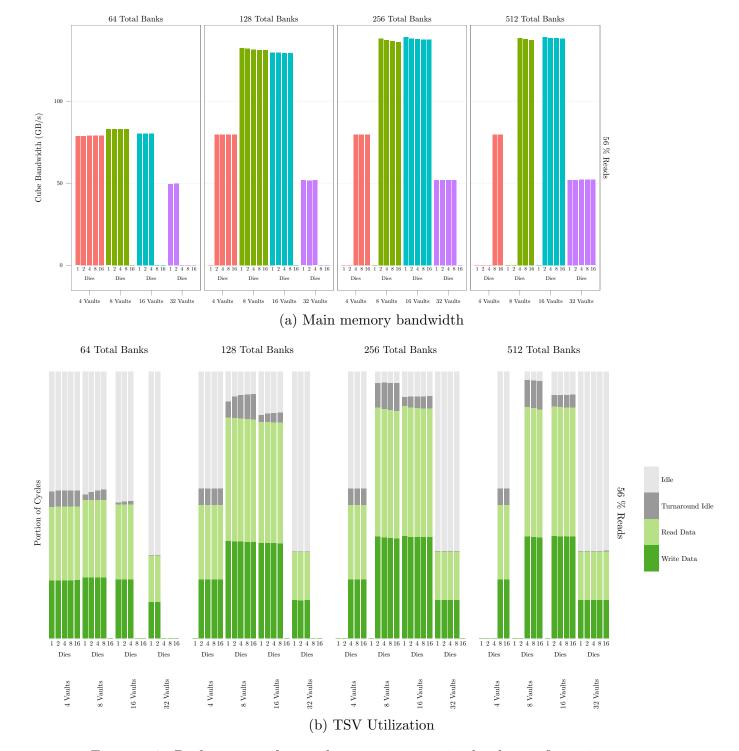

| 5.6  | Performance of several resource constrained cube configurations or-        |     |

|      | ganized into different numbers of vaults, partitions, and total banks.     | 71  |

|      | 5.6a Main memory bandwidth                                                 | 71  |

|      | TOTAL TOTAL TANK                                                           |     |

|      | 5.6b TSV Utilization                                                       | 71  |

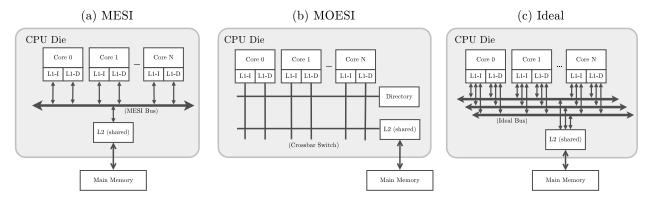

| 5.7  | Comparison of coherence schemes                                            | 78  |

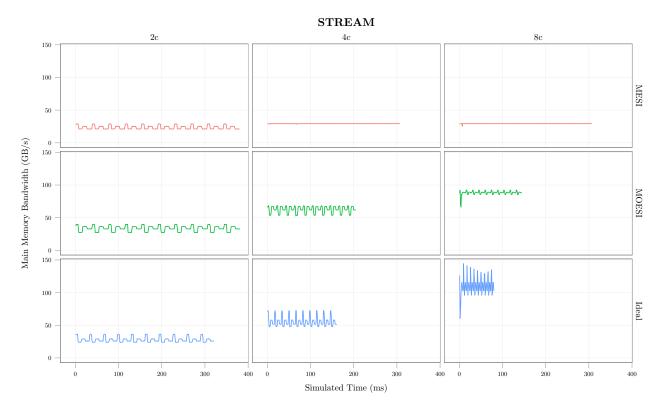

| 5.8  | Core scaling of the STREAM benchmark with various coherence                |     |

|      | schemes                                                                    | 79  |

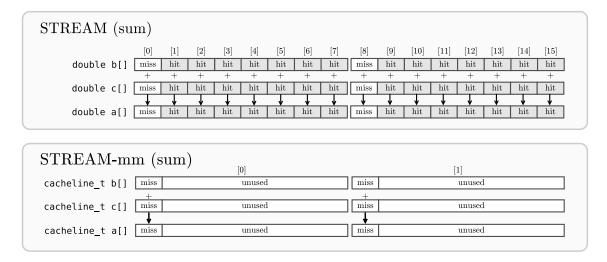

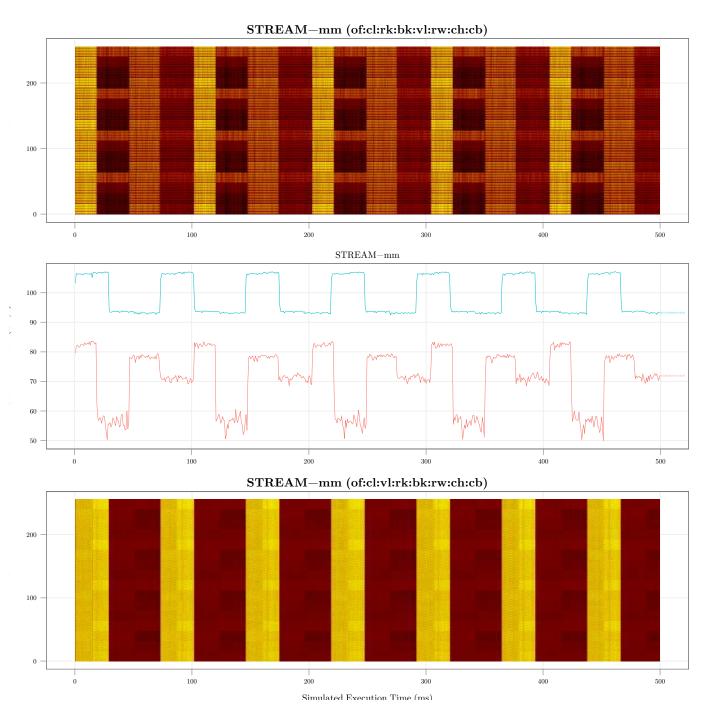

| 5.9  | Comparison of the access patterns of STREAM and STREAM-mm .                | 81  |

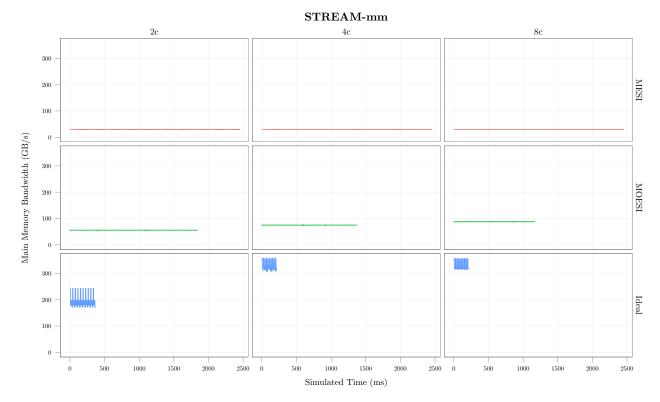

| 5.10 | Core scaling of the STREAM-mm benchmark with various coherence             |     |

|      | schemes                                                                    | 82  |

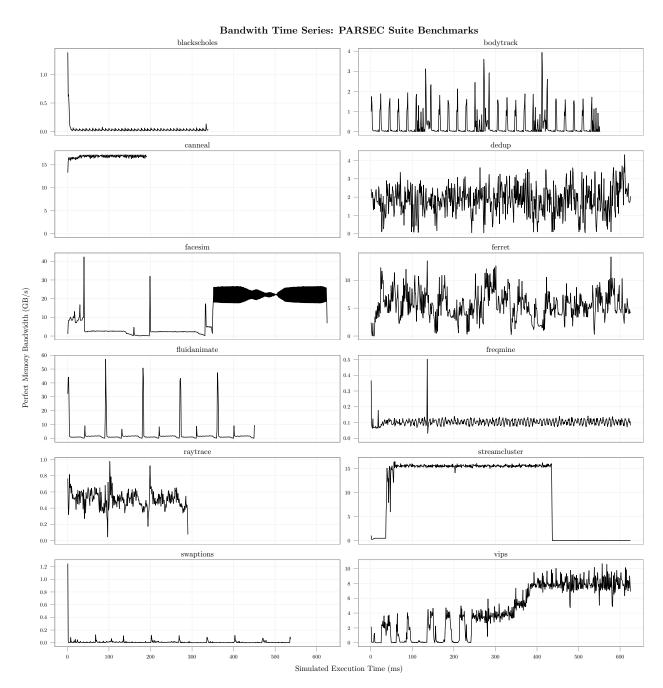

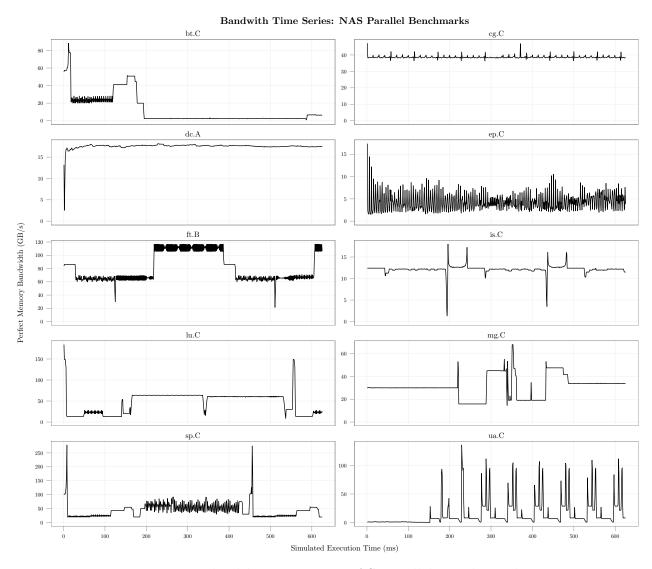

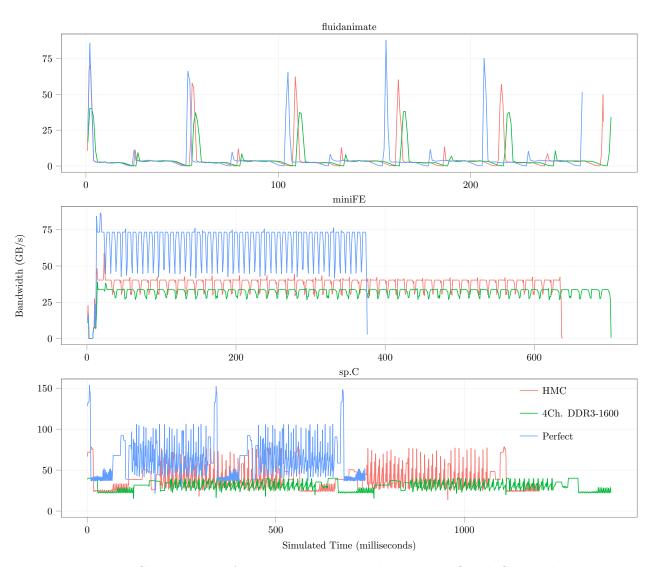

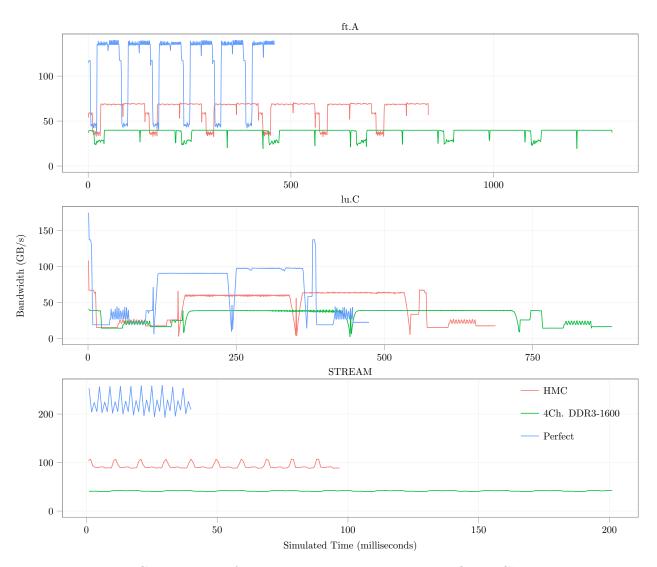

|      | Bandwidth time series: PARSEC suite                                        | 85  |

|      | Bandwidth time series: NAS Parallel Benchamark suite                       | 86  |

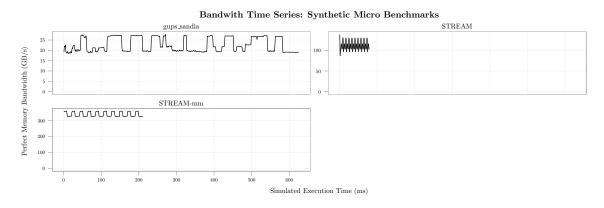

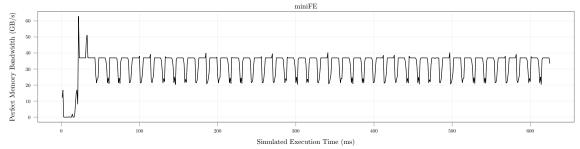

|      | Bandwidth time series: synthetic micro benchmarks                          | 86  |

|      | Bandwidth time series: MANTEVO mini application (MiniFE)                   | 87  |

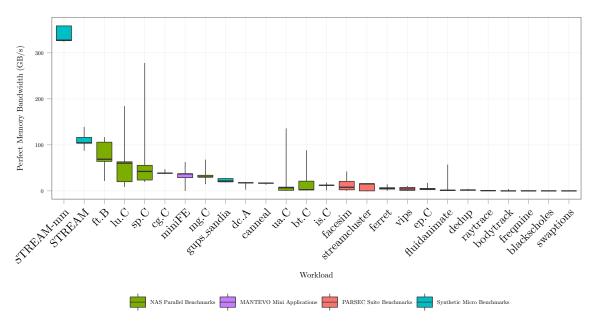

| 5.15 | Box plot summary of the bandwidth characteristics of all workloads .       | 88  |

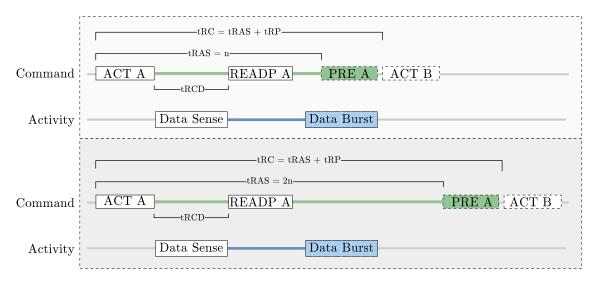

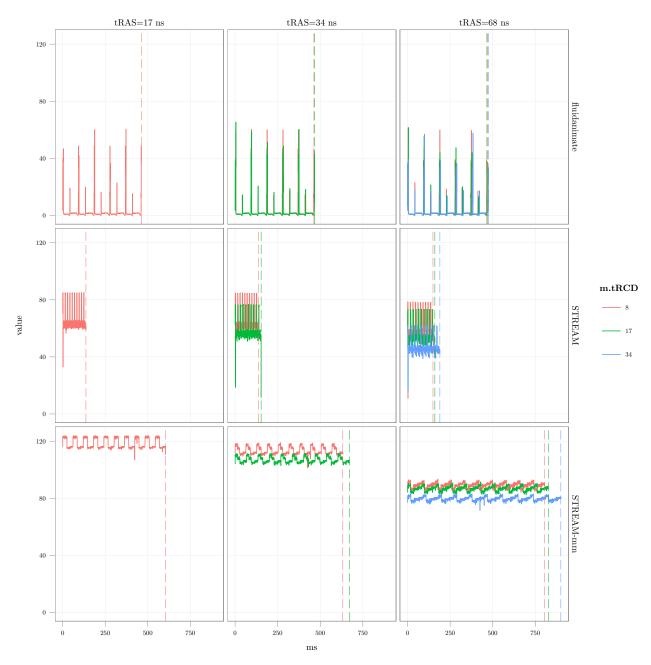

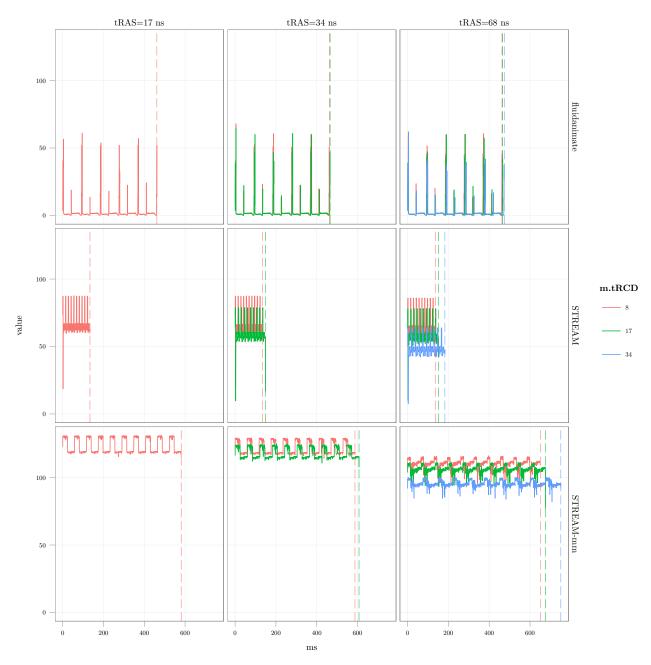

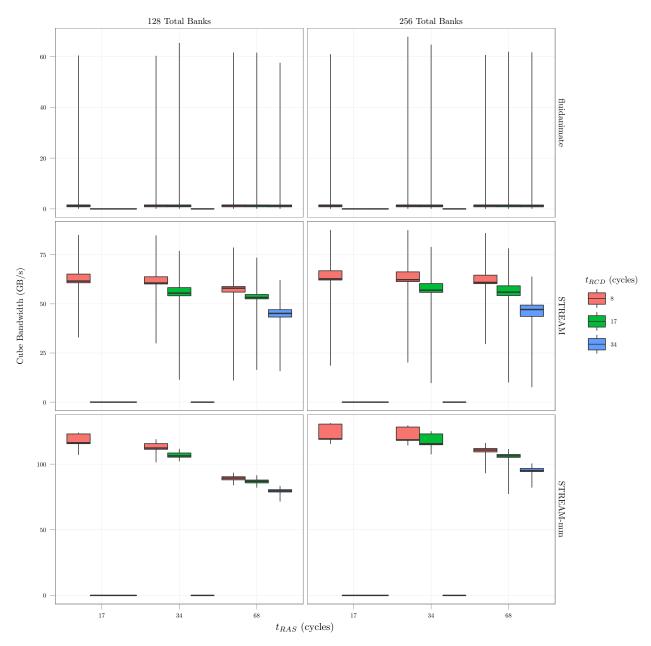

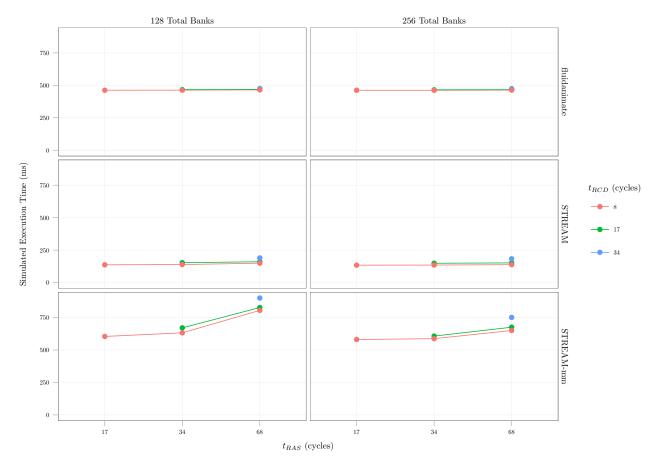

| 5.16 | Effects of doubling the $t_{RAS}$ DRAM timing paramter                     | 90  |

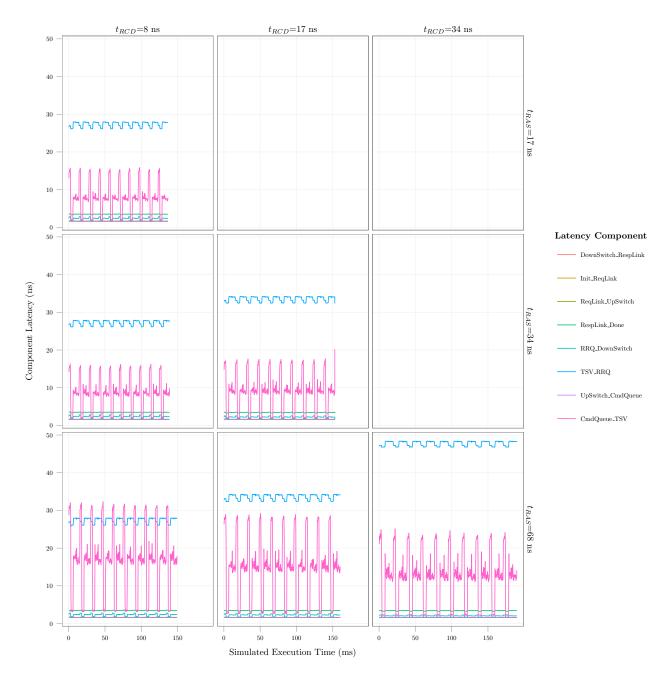

| 5.17 | Effects of doubling the $t_{RCD}$ DRAM timing paramter                     | 90  |

| 5.18 | Effect of varying $t_{RAS}$ and $t_{RCD}$ on bandwidth over time in a 128  |     |

|      | bank HMC                                                                   | 92  |

| 5.19 | Effect of varying $t_{RAS}$ and $t_{RCD}$ on bandwidth over time in a 256  |     |

|      | bank HMC                                                                   | 93  |

| 5.20 | Distribution of bandwidths for varying $t_{RAS}$ and $t_{RCD}$ DRAM timing |     |

|      | parameters                                                                 | 94  |

| 5.21 | Time-varying latency components for various workloads                      | 95  |

| 5.22 | The impact of DRAM timing parameters on workload execution time            | 97  |

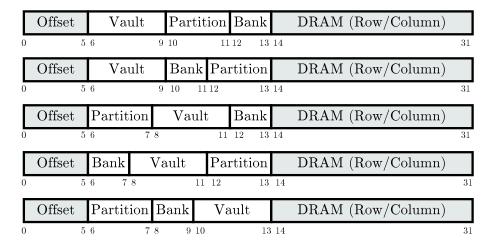

| 5.23 | Single cube address mapping schemes                                        | 99  |

| 5.24 | Performance of various workloads under various address mapping             |     |

|      | schemes with a single cube                                                 | 101 |

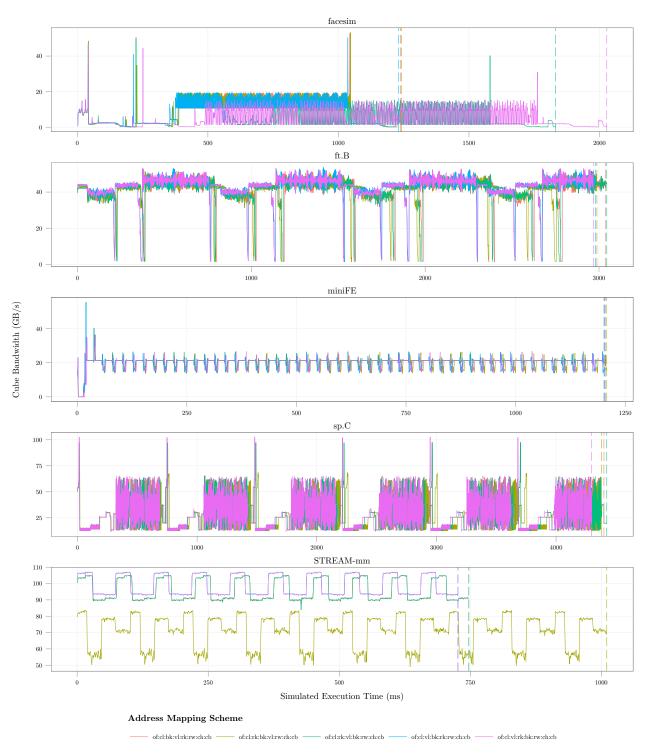

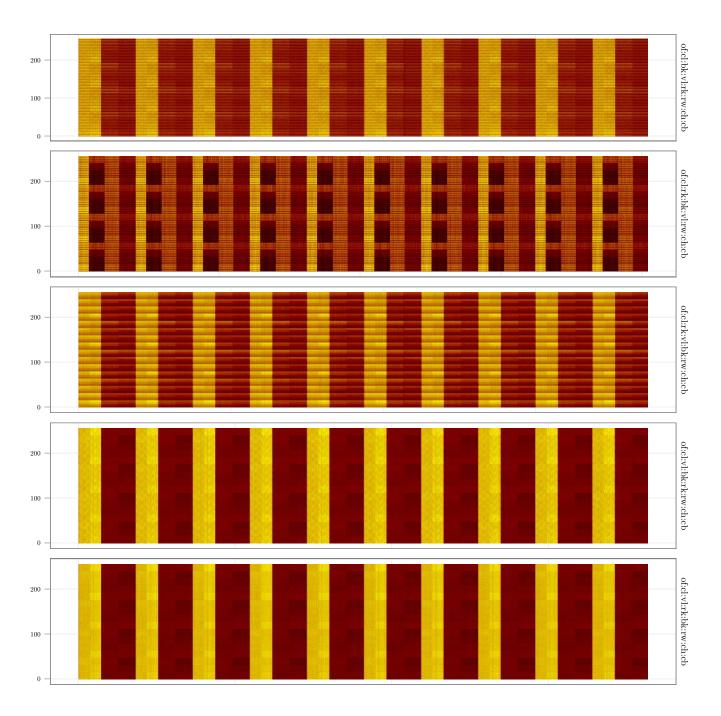

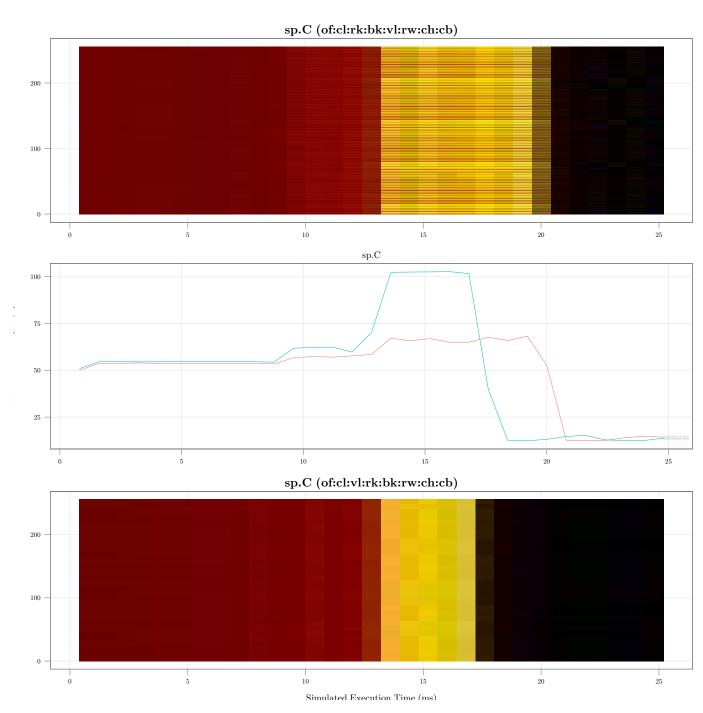

| 5.25 | Heatmaps for five address mapping schemes for the STREAM-mm                |     |

|      | workload over time                                                         | 104 |

| 5.26 | Address mapping scheme comparison for the STREAM-mm workload               | 106 |

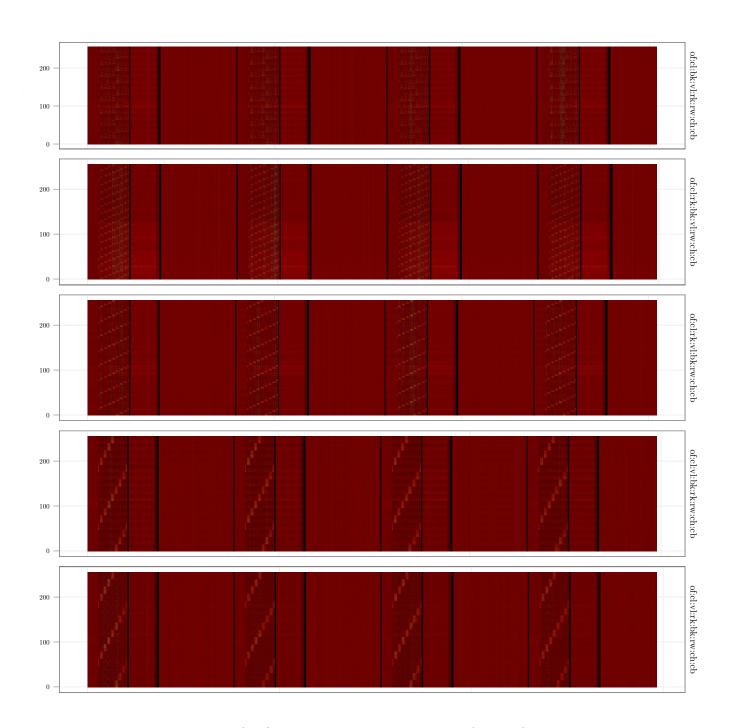

|      | Heatmaps for five address mapping schemes for the ft.B workload            |     |

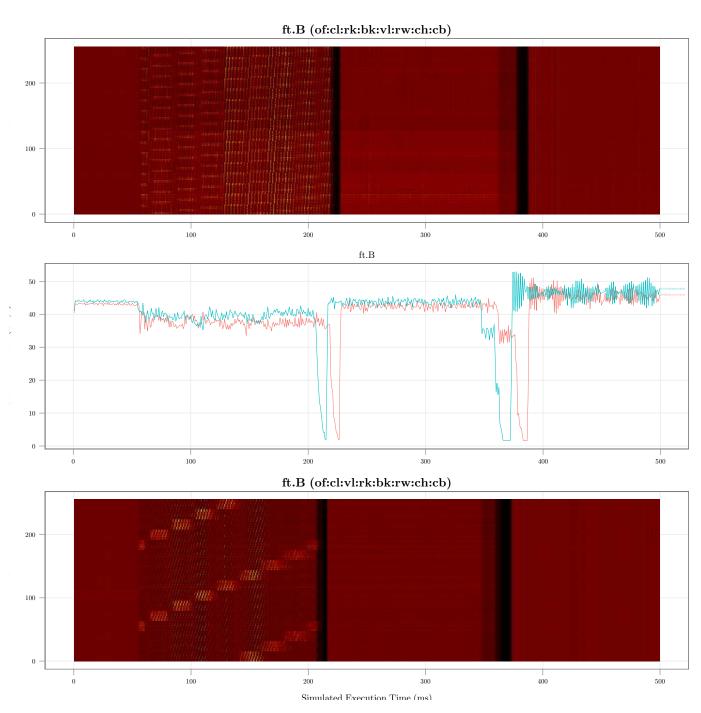

|      | over time                                                                  | 107 |

| 5.28 | Address mapping scheme comparison for the ft.B workload                    |     |

|      | Address mapping scheme comparison for the sp.C workload                    |     |

|      | Comparison of memory system technologies: Quad Channel DDR3,               |     |

| - 55 | HMC, and perfect. (1)                                                      | 111 |

| 5.31 | Comparison of memory system technologies: Quad Channel DDR3,               |     |

|      | HMC, and perfect. (2)                                                      | 112 |

| 6.1  | A linear chain topology                                                    |

|------|----------------------------------------------------------------------------|

| 6.2  | Block diagram of a ring topology                                           |

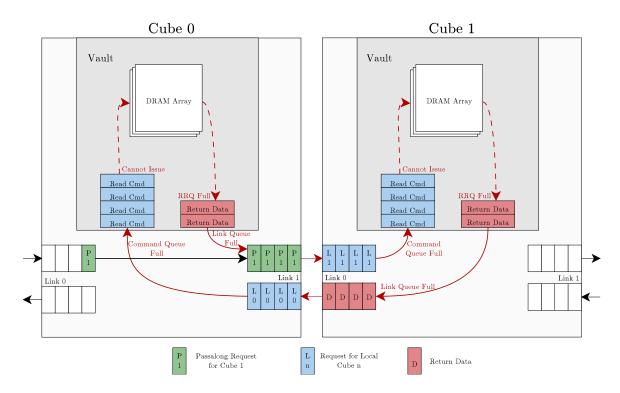

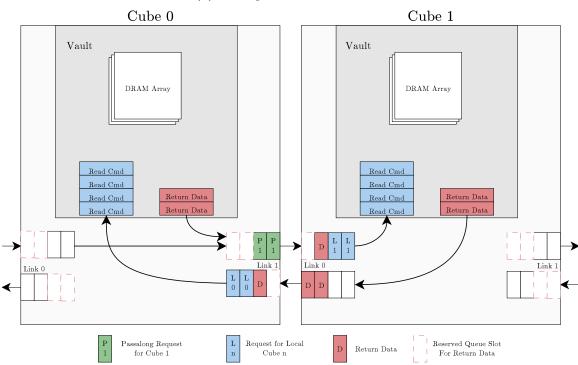

| 6.3  | Deadlock in a ring topology                                                |

|      | 6.3a Example of deadlock case                                              |

|      | 6.3b One strategy to avoid deadlock                                        |

| 6.4  | Logical representation of a ring topology                                  |

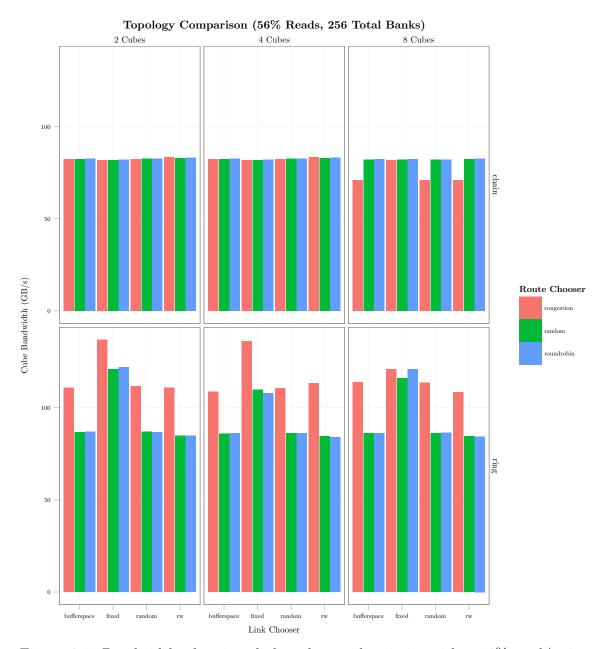

| 6.5  | Bandwidth of various link and route heuristics with a 56% read/write       |

|      | ratio stream                                                               |

| 6.6  | Bandwidth of various link and routing heuristics for a chain topology 132  |

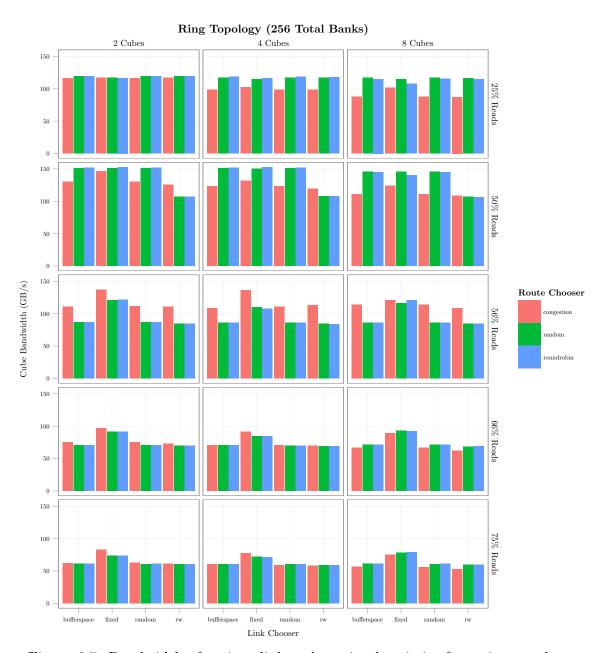

| 6.7  | Bandwidth of various link and routing heuristics for a ring topology . 133 |

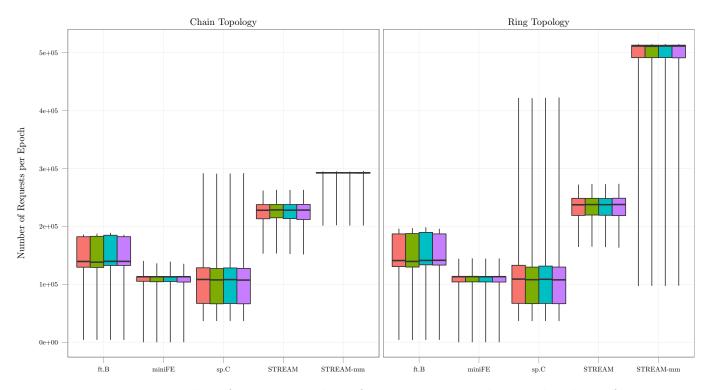

| 6.8  | Box plot of average number of requests per epoch to each cube in           |

|      | four cube topologies                                                       |

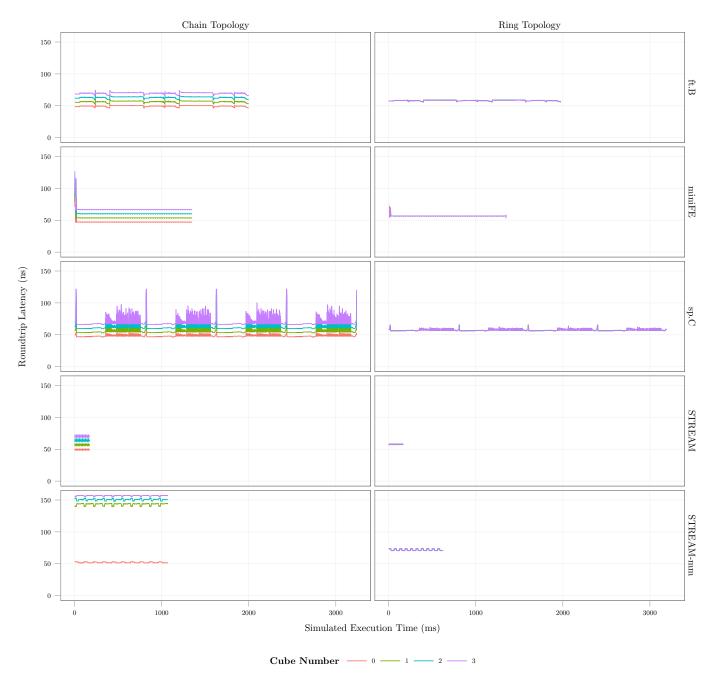

| 6.9  | Round trip latency to different cubes in four cube topologies 137          |

| 6.10 | Memory bandwidth as seen from the CPU over time for topologies of          |

|      | varying size                                                               |

# List of Abbreviations

DRAM Dynamic Random Access Memory

DDR Double Data Rate

DIMM Dual Inline Memory Module

HMC Hybrid Memory Cube

NUMA Non-Uniform Memory Access

RRQ Read Return Queue TSV Through-Silicon Via

# Chapter 1

#### Introduction

# 1.1 Status Quo: Current Generation Memory Systems

The original "Memory Wall" [1] paper was published well over a decade ago and the authors expressed horror at the idea that a memory access could take "tens or hundreds of" CPU cycles in a decade's time. Soon after their paper was published, synchronous DRAM began its slow march toward ubiquity after its standardization JEDEC in 1993. What is remarkable about this situation is that while researchers have been sounding the alarm about the memory bottleneck for nearly two decades, today's DDRx memory systems look largely identical to the SDRAM systems from two decades ago.

With today's multi-core processors containing aggressive pipelines, superscalar execution, and out of order scheduling, the demands on the memory system are more stringent than ever. There are three major problems that today's systems encounter:

- Memory bandwidth per core is insufficient to meet the demands of modern chip multiprocessors

- Memory capacity per core is insufficient to meet the needs of server and high performance systems

- Memory power consumption is beginning to dominate large systems (i.e., high

# 1.2 Synchronous DRAM

The original SDRAM standard was adopted by JEDEC in 1993 and the vast majority of today's computers are still using updated variants of the original SDRAM: DDR1, DDR2, or DDR3. Although these subsequent improvements to the original standard allowed the devices to achieve higher bandwidth through signaling and timing improvements (such as the inclusion of On Die Termination, DLLs, doubling the data clock rate, etc.), the underlying architecture has barely changed since the original SDRAM standard.

A modern DDRx memory system consists of a memory controller that issues commands to a set of DRAM devices that are soldered to a *Dual Inline Memory Module* (DIMM) that is plugged into the motherboard. Each DIMM is made up of one or more *ranks* that are comprised of several DRAM devices connected to a common set of control and address lines (i.e., all of the devices in a rank operate in lockstep to perform the same operation on their local memory arrays). Within each device, there are multiple *banks* of memory each of which contains the circuitry required to decode an address and sense data from the DRAM array. A DDR3 device has eight banks per rank. The bank is the smallest independent unit of memory operations: commands destined for different banks can execute completely in parallel with respect to one another. A schematic image of the DDRx memory system can be seen in figure 1.1.

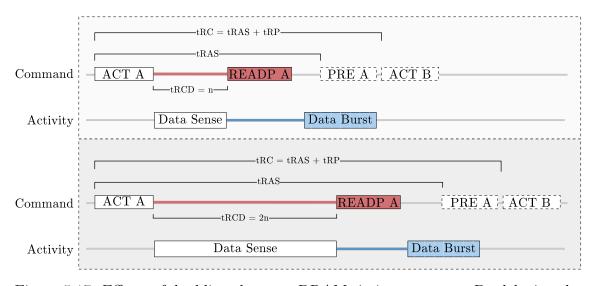

In order to reduce the number of address pins required, DDRx addresses are split into separate row and column addresses. The DRAM array inside of each bank is subdivided into rows of bits which are connected to a wordline driver. In the first phase of a data access, a row activation command (RAS) causes all of the devices in a particular bank to activate a wordline that contains an entire row of bits. Sense amplifiers detect the value of each DRAM cell and store the values in a row buffer. After the data has been stored in the row buffer, a column access command (CAS\_W/CAS) drives data into or out of the DRAM array for a write or a read, respectively. Before a different row can be activated, a precharge command (PRE) must be issued to ready the sense amplifiers to sense a new row. The DRAM protocol also allows for a row to be implicitly precharged after a column access without having to send an explicit precharge command in order to reduce command bus contention.

The DRAM devices are designed to be "dumb" in that the memory controller is responsible for keeping track of the state of each bank in the memory system and guaranteeing that all device timing constraints are met. The device has no ability to detect timing violations; the data will simply become corrupt if the memory controller issues a command at the wrong time. Additionally, the memory controller must schedule all transactions such that there are no collisions on the shared data bus. In addition to avoiding collisions on the bus, the controller must also account turnaround time when the direction of the direction of the shared data bus changes.

In order to keep the core memory clock low with respect to the data bus clock, the DDRx standard specifies a minimum "burst length" for transactions to

Figure 1.1: One channel of a traditional DDRx memory system. All of the ranks share common address, command, and data buses. The destination rank is chosen by a chip select line. The memory controller is responsible for ensuring all DRAM device timing constraints are met.

the DRAM array. Data is transferred to and from the memory controller over a wide 64-bit bus (or a 72-bit bus when ECC DRAM is used) in a series of "bursts". A DDR3 DIMM has a "burst length" of eight: a CAS triggers eight data transfers of 64 bits each for a total of 64 bytes. This corresponds to the size of a typical cache line fill (although a burst length of 4 can be requested for a 32 byte granularity). Data transfers happen on both the rising and falling edges of the I/O clock (hence the term Double Data Rate).

In non-embedded devices, a DIMM contains several individual DRAM devices that operate as a single logical device (see 1.1). The DRAM device width specifies

the number of bits that the device will drive out onto the data bus during each data burst. For example, a DDR3 DIMM that uses x8 width DRAMs will contain eight devices per rank that are connected to the 64 bit data bus. Each CAS command selects a set of columns from the row and these bits are driven out of the I/O pins onto the shared data bus on each burst. That is, on each rising and falling edge of the I/O clock, each device will output a certain number of bits which are aggregated together onto the data bus.

Each device contains rows with 1K columns of 8 bits each for a total of 8 Kb per device [4]. On a row activation, all eight DRAM devices will activate 8 Kb for a total of 8 KB across the DIMM. This situation is even worse for a DIMM consisting of x4 parts where a full 16 KB is activated across the DIMM. Before a row is closed (precharged) any number of column activations can be sent without having to re-issue a RAS command. For a detailed description of DRAM protocol and operation see [5].

This multiplexed addressing scheme, however, results in an efficiency problem: a row access activates 8-16 KB while a CAS only drives 64 bytes of data into or out of the DRAM array. In a "close page" row buffer policy (where a row is closed immediately after every column activation), less than 1% of the activated bits are actually read or written. This is known as the "overfetch" problem [6] and results in one source of energy inefficiency in DDRx DRAM. Memory controllers may implement an "open page" row buffer policy which attempts to exploit spatial locality in the request stream to send multiple column access commands to an open row and thus increase the row utilization. However, this comes at the cost of logic

complexity and queue space overhead in the controller. Even so, it is unlikely that a normal access pattern can exploit more than a few percent of the bits in an open row.

The wide parallel data bus in DDRx systems also creates a scaling problem. As the DRAM clock rates increase to try to keep pace with CPU bandwidth demand, the signal integrity becomes significantly degraded due to crosstalk and signal reflection. This problem is also exacerbated by the fact that electrical contact to the DIMMs is maintained by physical pressure from the DIMM slot contacts and not a permanent electrical connection such as with solder. As more DIMMs are added to the wide multidrop DDRx bus, the resulting capacitance increase and signaling problems create a situation where the data clock rate must be lowered in order to maintain signal integrity. This means that in order to achieve higher bandwidths, system designers typically reduce the number of DIMMs per channel and increase the clock rate. This, in turn, leads to a capacity problem since the number of CPU pins devoted to the memory system and the capacity of a single DIMM are not growing very quickly.

# 1.3 Currently Proposed Solutions

Recently, industry has come up with several solutions to try to address the various shortcomings of DDRx.

#### 1.3.1 DDR4

Recently, JEDEC has completed the DDR4 standard that is slated to replace current DDR3 devices. DDR4 introduces advanced I/O technology such as Dynamic Bus Inversion, Pseudo Open Drain, along with new On Die Termination techniques to reduce bus power consumption and increase signal integrity. DDR4 devices will operate at 1.2V, resulting in a substantial energy savings over current DDR3 devices which run at 1.35V. The use of shorter rows in the DRAM array (512B per row compared to a typical 2048B per row in DDR3) results in a lower activation energy as well as a lower row cycle time.

DDR4 is expected to provide data rates from 1.6 GT/s all the way up to 3.2 GT/s (2x the data rate of DDR3-1600 [7][8]) in future parts. DDR4 devices will contain 16 banks organized into four bank groups (compared to DDR3's 8 independent banks) that result in a higher level of memory parallelism and higher throughput at the cost of increasing scheduling complexity [9]. Consecutive accesses to the same bank group will incur a longer access time than accesses to different bank groups. This means that consecutive requests must go to different bank groups in order to avoid idling the data bus and reducing throughput [10].

Since no systems yet support DDR4, there is no clarity on how many DDR4 DIMMs per channel will be supported. Intel's upcoming Haswell-E CPU is reported to feature four DDR4 channels each supporting only a single DIMM per channel [11] as discussed by previous sources [12]. However, other sources refer to DDR4 configurations with up to three DIMMs per channel at reduced data rates [13]. It

is unclear from this document whether a three DIMM per channel configuration requires LRDIMM technology to be used (see section 1.3.2).

To overcome the potential capacity limitation due to single channel depth, the DDR4 standard contains TSV stacking extensions to create 3D stacked DIMMs containing up to 8 DRAM dies [8]. Currently, Samsung has announced Registered DIMMs with capacity of up to 32 GB per DIMM (and LRDIMMs with capacity of up to 128 GB per DIMM) [13].

#### 1.3.2 LRDIMM

Figure 1.2: A Single LRDIMM channel. By placing a buffer chip on each DIMM to latch the control, address, and data lines, LRDIMM is able to reduce the loading on the DRAM bus. This enables faster clock speeds with higher channel depths as compared to a standard DDRx channel.

Load Reduced DIMM (LRDIMM) takes the approach of reducing the capacitive load on the memory buses by adding latching registers to the control, address, and data lines<sup>1</sup>. In a traditional unregistered or registered DIMM, each rank on a DIMM is its own electrical load on the bus. In an LRDIMM, however, multiple ranks are connected to the buffer chip that appears as a single electrical load on the bus. This means that a 32 GB quad rank LRDIMM results in a 4x load reduction compared to a normal Registered DIMM (RDIMM) [14]. The load reduction mitigates the capacity problem by allowing more DIMMs to be placed per channel than traditional DDRx systems while maintaining reasonably high clock speeds. For example, LRDIMM allows three DIMMs per channel at 1333 MT/s at 1.5 V whereas RDIMM only allows two [15]. Recently, Inphi and Samsung demonstrated a quadsocket server system containing 1.5 TB DRAM running at 1333MT/s (4 sockets x 4 channels per socket x 3 32GB DIMMs per channel) [16].

The LRDIMM load reduction technique can be utilized with DDR3 as well as upcoming DDR4 devices.

# 1.3.3 Fully Buffered DIMM

signals, but not the data bus.

In 2007, JEDEC approved a new memory standard called Fully Buffered DIMM (FB-DIMM). FB-DIMM places a buffer chip called an Advanced Memory Buffer (AMB) on each memory module. The modules communicate with the memory controller using a high speed, full-duplex point-to-point link instead of a wide

1 Note that this differs from a Registered DIMM that only latches the control and address

Figure 1.3: One FB-DIMM channel. The wide DDRx data bus is localized to a single DIMM. The Advanced Memory Buffer on each DIMM translates the high speed link protocol into DRAM protocol.

parallel bus. Since all connections between modules are point-to-point, each memory module must capture the data from the link and either process the request locally or forward the request to the next module in the chain.

By replacing the wide DRAM buses with high speed, point-to-point links, many more DIMMs can be placed in a channel while maintaining high data rate. Though FB-DIMM addressed the bandwidth and capacity problems of the memory system, it was never widely adopted. The power consumption of the AMB proved to be the biggest problem with FB-DIMM since it added a non-trivial power overhead to each DIMM. FB-DIMM allowed approximately 24x the number of DIMMs in the

memory system [17] as compared to a DDR3 system while adding approximately 4 W of power overhead per DIMM [17][18] resulting in power overheads that could reach nearly 100 W. The power overhead of the memory was on par with CPU power consumption at the time.

In the end, FB-DIMM was abandoned by vendors and taken off industry road maps altogether.

#### 1.3.4 Buffer-on-Board

Yet another approach to increasing capacity and bandwidth is the "Buffer-on-Board" (BOB) memory system. This type of memory system has been implemented by the major vendors (Intel, IBM, etc.) for their high end server systems. The BOB memory system is comprised of a master memory controller on the CPU die communicating with several slave memory controllers over high speed, full-duplex serial links. Whereas the CPU communicates with each slave controller using a packet-based protocol, the slave controllers communicate with commodity DDR3 DIMMs using a standard DDR3 memory protocol. To amortize the cost of each high speed link, each slave controller can control more than one DRAM channel.

By splitting off each slave controller and allowing it to act as a buffer between the wide DRAM channel and the CPU, the BOB memory system can achieve high bandwidth and large capacity. The capacity is increased because the serial interface requires far fewer CPU pins per channel as compared to a DDR3 channel. A large number of memory channels can use the same number of CPU pins as just a few

Figure 1.4: A Buffer-on-Board memory system. In the Buffer-on-Board memory system the main memory controller communicates with slave memory controllers over high speed links which then drive their own DDRx channels. By amortizing the cost of the slave memory controller over several DIMMs (instead of a single DIMM as in FB-DIMM), Buffer-on-Board is more cost and power efficient than FB-DIMM while maintaining its capacity and bandwidth.

#### DDR3 channels.

The high level of memory level parallelism enables better spread of memory requests to independent resources to shorten access time by avoiding conflicts. The independent, high speed, full-duplex links stream the data back to the CPU with minimal latency overhead. Overall, the system can achieve high bandwidth and high capacity with reasonable latency overheads. For example, [19] shows that a particular buffer on board configuration with 256 GB of memory connected to an

eight core CMP is able to achieve sustained bandwidth of about 35G B/s with about a 110 ns latency (limit case simulations using random address streams show sustained bandwidths of around 60 GB/s).

While the performance of BOB systems is significantly higher than a regular DDRx system, a BOB system introduces a significant power penalty. Unlike the FB-DIMM memory system that requires a buffer for each memory module, the BOB system only requires a single buffer for one or more channels of memory. Although this cuts down on the number of buffers required in the system, there is still a significant power penalty for running the slave memory controllers. In addition to driving a standard DRAM bus, the slave controllers must send and receive data over high speed I/O links to the CPU. Since these links don't exist in a traditional DDRx memory system, they represent yet another power overhead. Finally, since the BOB memory system allows expanded capacity, the number of DIMMs in the memory system is higher, adding further to a typical system power budget.

# 1.4 Discussion of Proposed Solutions

All of the solutions discussed in the previous section address various shortcomings of the current DDRx memory system. The common theme among all of the proposed solutions is that they maintain the standard DDRx technology at their core. Most of these solutions use a standard DDRx DRAM device and improve it externally by adding extra circuitry (and DDR4, while redesigned, keeps most of the core DDRx technology intact). From a cost and business perspective, this is a

lower risk approach: fabrication facilities do not need to be retooled to build exotic new memory technologies that may fail to gain widespread adoption. However, by keeping the core DDRx technology in place, the solutions only make incremental progress in increasing bandwidth, capacity, and energy efficiency. DDR4 doubles throughput and lowers power consumption, but may potentially suffer from capacity limitations due to the large CPU pin requirement and potential single channel depth. LRDIMM increases capacity while changing power and performance only nominally. FB-DIMM and Buffer on Board offer capacity and performance increase, but with a power penalty.

The longer term problem with these solutions is the widely predicted end of DRAM scaling. Current generation DDR devices are manufactured in a 20 nm process [20], but it is unclear how much further the DRAM technology process will be able to scale downwards while still being able to produce a device that can hold charge without having to be incessantly refreshed. Currently, technology node scaling allows for improvements in power consumption and density of the memory system. However, after the predicted end of DRAM scaling, there is no clear path to continue increasing density and lowering power.

In the long run, some form of 3D stacking will become necessary to keep pushing the performance, capacity, and power advancements in the main memory system. 3D stacking can be used to eliminate long, problematic wires (both going to the chip on the motherboard and the global wire length on a chip), to increase density by allowing more devices per package and per CPU pin, and to decrease power consumption through better electrical characteristics and shorter wires. In

this dissertation, we will examine one such implementation of a 3D stacked DRAM system: the Hybrid Memory Cube.

### Chapter 2

## Hybrid Memory Cube Architecture

One of the recently proposed solutions to the bandwidth, capacity, and power problems of the main memory system is a new memory device called *Hybrid Memory Cube* (HMC) [21][22]. The HMC technology leverages advances in fabrication technology to create a 3D stack of dies that contains a CMOS logic layer with several DRAM dies stacked on top. While the idea of stacking memory on top of logic is not a new one, only recently has research into advanced fabrication techniques allowed for such a device to start becoming commercially viable.

#### 2.1 HMC Architecture

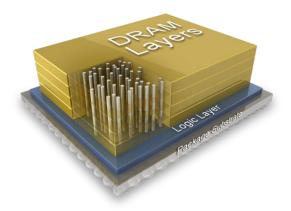

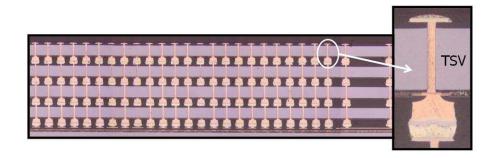

The Hybrid Memory Cube proposes to combine several stacked DRAM dies on top of a CMOS logic layer to form a *cube*. The term "hybrid" is used to describe the fact the device contains both DRAM dies as well as logic dies combined into a single stack. The dies in the 3D stack are connected through a dense interconnect of *Through-Silicon Vias* (TSVs), which are metal connections that extend vertically through the entire chip stack. A cross section of the dies and TSVs can be seen in figure 2.4.

To create these vertical connections, the device wafers are first thinned and then etched to form holes that completely penetrate the wafer. The holes are then

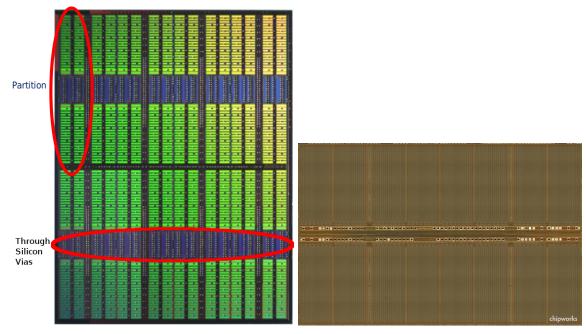

Figure 2.1: A closeup of an HMC stack.

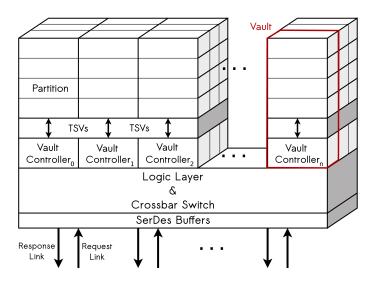

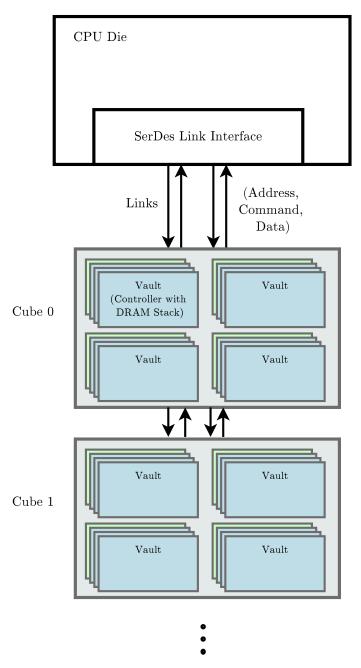

Figure 2.2: The architecture of an HMC cube. High speed serial links bring data into the cube which is routed to one of the vault controllers. Finally, the vault controller issues DRAM commands to the DRAM vaults. Read data flows from the vault controller through the interconnect and back out of the high speed links.

Figure 2.3: An artist's rendering of the HMC. Several DRAM dies are connected to a CMOS logic layer by vertical metal Through Silicon Vias (TSVs)

Figure 2.4: A cross section of an HMC device. A thinned wafer is perforated with vias that are filled with metal. Several wafers are bonded together to form a stack of devices connected with vertical metal connections.

filled with metal to form an electrical connection vertically through the entire wafer. Finally, several wafers are bonded together to form a 3D stacked device that can be packaged (see figure 2.1 for a close up of the HMC device before it is packaged).

The result is a permanent dense metal interconnect between the DRAM dies and the logic die that contains thousands of TSVs [23]. Unlike a typical DDRx DIMM which maintains electrical contact through the pressure of the pin slot, the TSV process forms a permanent metal connection between the dies. Because the TSVs provide a very short interconnect path between dies with lower capacitance than long PCB trace buses, data can be sent at a reasonably high data rate through the stack without having to use expensive and power hungry I/O drivers [24]. Furthermore, smaller I/O drivers and simplified routing allow a high interconnect density between the dies.

In order to increase the parallelism of the architecture, the dies are segmented vertically into *vaults*. Each vault contains several *partitions* that each contain several banks. A single DRAM die within the stack contains several different partitions as shown in figure 2.5.

The base of each vault contains a *vault controller* which takes on the role of a traditional memory controller in that it sends DRAM-specific commands to the DRAM devices and keeps track of DRAM timing constraints. The vault controller communicates with the DRAM devices through the electrical connections provided by the TSVs. A vault is roughly the equivalent of a traditional DDRx channel since it contains a controller and several independent ranks (partitions) of memory on a common bi-directional data bus. However, unlike a traditional DDRx system, these

(a) Single HMC DRAM Die (source: Micron) (b) Samsung 2Gb DDR3 DRAM die (source: chipworks)

Figure 2.5: Comparison of HMC and DDRx DRAM dies. Each DRAM die in the HMC stack contains several partitions each with several banks. The areas between the DRAM devices are taken up by the TSVs while the DDR3 die is almost entire devoted to memory arrays.

Figure 2.6: The architecture of an HMC memory system. The CPU communicates with cubes over a high speed packet interface. Cubes can connect to other cubes to form networks of memory.

connections are vastly shorter than the DDRx bus traces on a motherboard and have much better electrical properties. An illustration of the overall cube architecture can be seen in Figure 2.2.

In addition to containing several vault controllers, the logic layer interfaces with other cubes or hosts (e.g., CPUs) through a high speed link interface. Each link is comprised of several high speed lanes that typically run at several gigabits per second per lane. Although each individual lane is unidirectional and differentially signalled, each link is comprised of several lanes that run in both directions, making the link full-duplex. The link interface is responsible for serializing packets for transmission on the link's lanes by serializing them into the minimal transmission unit known as *flits* (as per the HMC specification, a flit is 16 bytes wide). When receiving packets, the link interface must de-serialize individual flits back into packets. Each packet contains metadata required for routing, error correction, and flow control.

The logic layer also provides a switch interconnect that connects the links to local vaults as well as to other links. The HMC specification states that any link must be able to access any local vault. Similarly, in order to support chaining of HMC cubes together, a packet from any link should be able to access pass-through links. There are two interconnect structures that are mentioned by the specification. The first is a full crossbar switch in which any link can transmit to any vault. The second is a segmented structure in which each link connects to a quadrant that services several local vaults. If a request arrives at a quadrant which does not contain the target vault, it can be forwarded to the appropriate quadrant

that can service the request. However, details of the switching structure are not dictated by the HMC specification as the switching is completely hidden from the host controller. This is a major benefit to vendors as it allows them to optimize the switching structure without affecting the host protocol. This type of encapsulation is a feature of the HMC that will be described further in the next section.

#### 2.2 Benefits of the HMC

The HMC architecture provides several key benefits over traditional DDRx memories that solve key problems plaguing current and future memory systems.

## 2.2.1 Capacity

One of the benefits of an HMC architecture is that it addresses the capacity and density problems of current DRAM technology. The capacitors inside of a DRAM die must maintain a minimum capacitance in order to be able to store charge long enough to avoid corruption or constant refreshing. It is difficult to shrink the DRAM cell size while keeping the same capacitance and thus improvements in DRAM density have slowed in recent years. Furthermore, it is unclear how much longer DRAM can continue to scale down to improve density. By leveraging Through-Silicon Vias, multiple DRAM dies can be stacked together (currently demonstrated parts have 4 dies, but 8 dies have been mentioned). With stacked dram dies, a single cube can contain a multiple of 4 or 8 times the storage in the same package footprint as a single DRAM device. In addition to decreasing footprint, the amount of ca-

pacity accessible per active CPU pin is increased as compared to a planar DRAM device. Note that the application of 3D stacking techniques to increase capacity is not unique to HMC. For example, as discussed in section 1.3.1, the DDR4 standard has 3D stacking extensions in order to help increase density without increasing pin count.

## 2.2.2 Parallelism and Aggregate Bandwidth

As previously mentioned, the TSVs are able to provide a high bandwidth connection between layers of the 3D stack. This high bandwidth is achieved through a combination of the density of the TSVs (there can be thousands of TSVs per cube) as well as the ability to transfer data at a high frequency. As TSVs are a short vertical path between dies, it is possible to transmit data at a high frequency without the signalling problems of many parallel long wires associated with PCB traces on a motherboard (as in DDRx systems). Furthermore, each cube has several high speed serialized links which achieve high bandwidth by using unidirectional differentially signalled lanes.

Since there are many independent vaults, each with one or more banks, there is a high level of parallelism inside of the cube. Each vault is roughly equivalent to a DDRx channel since it is comprised of a controller communicating with several independent DRAM devices sharing a data bus. With 16 or more vaults per cube, this means that each cube can support approximately an order of magnitude more parallelism within a single package. Furthermore, the vertical stacking of DRAM

devices allows for a greater number of banks per package which is also beneficial to parallelism.

The architecture of the cube leverages many relatively slow DRAM devices put together in parallel to take advantage of the enormous bandwidth provided both by the TSVs that connect them to the controller as well as the high speed links that ultimately connect them to the CPU. Overall, depending on the particular cube configuration, tests on real hardware [25] and simulations in later chapters show that the HMC can deliver aggregate memory bandwidth of over 100 GB/s.

## 2.2.3 Energy Efficiency

By radically decreasing the length and capacitance of the electrical connections between the memory controller and the DRAM devices, the HMC is more energy efficient compared to DDRx memory devices. As previously mentioned, this also allows for the I/O driver circuitry to be simplified, making it more power efficient. Additionally, since much of the peripheral circuitry is moved into the logic layer, the power cost of this circuitry is amortized over a large number of DRAM devices, saving on overall power consumption. That is, each DRAM device is only responsible for reading the DRAM array and sending the data over a very short TSV bus, but unlike a traditional DDRx DRAM device, it does not need to communicate data all the way back to the CPU. Claims about energy efficiency range anywhere from 7x [26] to 10x [27] over current generation memory systems. Current estimates of HMC

energy usage range from 10.48 pJ/bit [23] to 13.7 pJ/bit [21]. At peak utilization<sup>1</sup>, it is estimated that DDR3 and LPDDR2 devices use approximately 70 pJ/bit and 40 pJ/bit, respectively [28]. Academic investigations also claim that a 3D stacked architecture like the HMC can be up to 15x more energy efficient than an LPDDR memory part [29].

## 2.2.4 Device Process Heterogeneity

Since a TSV process allows for heterogeneous dies to be stacked together, each die can be optimized for a specific purpose without having to sacrifice performance. The logic layer is optimized for switching and I/O while the DRAM dies are optimized for density and data retention. If these two dies were to co-exist in a single fabrication process, they would both suffer (i.e., DRAM built in a logic process cannot be dense; switching logic built in a DRAM process cannot switch at a high frequency). As a result of the stacking, each die achieves good performance and energy efficiency while retaining almost all of the benefits of being on the same die.

### 2.2.5 Interface Abstraction

The original SDRAM standard purposely created many generations of "dumb" memory devices; the memory controller was in full control of the memory devices and was responsible for ensuring all timing constraints were met. This enabled DRAM devices to contain a minimal amount of circuitry that wasn't related to ma-

<sup>&</sup>lt;sup>1</sup>Note that "peak utilization" represents the most energy efficient scenario; "typical utilization" has a higher energy per bit.

nipulating the DRAM array and driving the data on the data bus. While this was a rational design decision at the time, it had the effect of curtailing innovation in the memory system. Once the standard was written, nothing could be done to change the protocol. Any deviations from the standard DRAM protocol required the agreement of DRAM manufacturers, motherboard manufacturers, CPU manufacturers, etc. As modern CPUs began to incorporate the memory controller onto the CPU die for performance reasons, the problem became even worse: every processor model could only work with a single type of DRAM and would have to be intimately aware of every timing constraint of the memory system. These two factors together meant that any attempt at innovation in the memory system would usually take the form of adding external logic that was invisible to the host (ex: LRDIMM) or used commodity parts with a change to the host (ex: Buffer on board). Nothing could be done inside of the actual memory device itself.

Furthermore, the commodity economics of DRAM further stifled attempts at innovation. Even if improvements could be made inside of a DIMM that did not modify the DRAM protocol, they would largely be ignored as such improvements would add to the cost of a product in a commodity market where consumers make their decisions based largely on cost.

In the Hybrid Memory Cube, however, the memory device at the end of the communication link is no longer "dumb". That is, the CPU can communicate with the cube (or topology of cubes) over a general protocol that is then converted into device-specific commands within the vault controller. This allows for innovation in a number of different ways. The first improvement is that the DRAM timing inside

of the cube can be changed without changing the CPU interface. Since the CPU has to simply operate at the read/write level and not at the DRAM protocol level, it no longer has to be intimately aware of every timing parameter associated with the memory device. This means advances in a DRAM can be integrated into the HMC without having to design an entirely new memory controller or CPU.

A second benefit of an abstract interface is that it allows any communication medium to be used as long as it is capable of delivering packets between a CPU and memory cube. Already researchers are thinking about how to replace electrical SerDes with high speed optical interconnects [30][3][31] to decrease power consumption.

Finally, an abstract interface provides a method of future-proofing the memory system. The authors of [3] point out that in the past, the CPU had to control hard disks at a very low level until the serial ATA (SATA) interface came along and pushed all of the control details into the disks themselves while only exposing an abstract interface to the CPU. This change enabled a painless transition from spinning disks to solid state disks by allowing vendors to conform to the high level SATA interface while managing the details of their own device. The same line of reasoning can be applied to the HMC: if the internal details of the memory technology are the responsibility of the cube and not the CPU, then it would be easy to change the underlying memory technology seamlessly if something came along to replace DRAM. There is an entire field of research into emerging memory technologies such as Spin-transfer Torque RAM (STT-RAM) and Phase Change Memory (PCM) that have a different set of trade-offs and access characteristics as

compared to DRAM. An abstract protocol would enable them to migrate into an HMC-like device without exposing the change to the CPU. Furthermore, one could imagine heterogeneous memory stacks where DRAM dies and non-volatile memory dies co-exist in the same cube and are intelligently and transparently managed by the logic inside of an HMC.

## 2.2.6 Near-Memory Computation

Having a memory device with logic nearby opens the possibility of performing near-memory computations. Certain types of computations and operations could take operands from memory, perform some computation in the logic layer, and put the result back in memory or return it to the CPU. Although this idea is not new, there has never been such a convenient platform for implementing these operations since, as discussed in section 2.2.4, DRAM and logic can easily co-exist in an optimal way.

Already the HMC specification defines several commands that can be used for operations such as locking and read-modify-write that are best done near the memory instead of in the CPU. By executing these memory intensive operations near the memory, the HMC is able to reduce the amount of data that must be transferred back and forth between the memory and the processor.

## Chapter 3

#### Related Work

The idea of stacking the memory hierarchy on top of the processor has been around for over a decade. Shortly after the "memory wall" paper was published, Kleiner et al. [32] proposed the idea of stacking the L2 cache (which was off-chip at the time) and DRAM on top of a RISC CPU and connecting the two chips using vias. They showed that such a stacked processor could perform instructions 25% faster. However, only recently has the fabrication technology progressed to the point where through silicon vias are actually feasible on a commercial scale. Buoyed by forward progress in TSV technology, there has been a recent surge of academic and industry research about possible applications of the technology.

# 3.1 DRAM on CPU Stacking

One of the biggest research directions for the utilization of 3D stacking has been the case where DRAM is stacked directly on top of the processor. This is a natural approach since the TSV process allows for heterogeneous dies to be stacked together (i.e., a CMOS logic CPU die with a DRAM die). This approach also provides the highest bandwidth and lowest latency path to the main memory, which leads to an effective way of bridging the performance gap between the processor and the memory.

### 3.2 System Level Studies

Liu, et al. [33] look at the advantages of stacking various memories (L2 cache or DRAM) directly on top of the CPU as well as the effects of deepening the cache hierarchy to include an L3 cache. Although they use a single core CPU model with dated benchmarks, they conclude that bringing the memory closer to the CPU via stacking can improve performance almost to the same level as having a perfect L2 cache.

In a similar but more recent study, Black, et al. [34] examine the performance and power implications of stacking either an SRAM or DRAM cache on top of a dual core CPU (unlike other studies, they do not assume the entire main memory will fit on top of the CPU). They show that using a 32MB stacked DRAM results in an average reduction of off-chip traffic by a factor of three, which translates to a 13% average reduction in memory access time and a 66% average reduction in bus power consumption. Their thermal modeling also shows that the temperature increases from stacking a single extra die are negligible and unlikely to impact the feasibility of stacking.

Kgil, et al. [35] show that stacking the main memory on top of a slow and simple multi-core CPU without an L2 cache can increase the network throughput for web server applications while achieving a 2-4x energy efficiency compared to more complex conventional CPUs. Their decision to use many simple cores with no L2 cache is motivated by their target workloads, which exhibit low locality and high thread level parallelism. The authors state that 3D stacking allows their chip to run

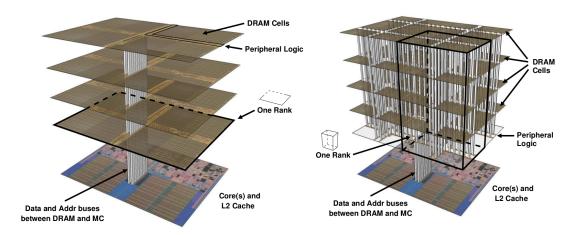

Figure 3.1: Two possible 3D rank organizations. Ranks are either split (a) horizontally ("3D") or (b) vertically ("true 3D"). The HMC model presented in this dissertation is more akin to the horizontal "3D" model in (a). (Image source: [37])

at a slower clock rate but still perform similar to a Pentium 4-like CPU at 1/10th of the power cost.

Loi, et al. [36] demonstrate that there is a 45% performance benefit to stacking memory on top of the CPU while maintaining a 64-bit bus width (same as conventional DRAM). Further utilizing the density of the TSVs to increase the memory bus width improves performance by up to 65% over conventional DRAM. Additionally, the authors show that even when taking into account the clock speed limitations imposed by thermal constraints of 3D stacked devices, these clock-limited stacked devices perform better than higher clocked 2D devices because of their ability to overcome the memory bottleneck with short, high density interconnections. There is, however, one shortcoming to this work as it only considers a 64 MB main memory size despite being a reasonably recent publication.

Loh [37] evaluates different organizations for 3D stacked DRAM. He shows that 3D organizations where each die contains a single rank (figure 3.1a) are not able to utilize the full bandwidth potential of the TSVs. The alternative approach of organizing the ranks in vertical slices (such that the banks are spread vertically among the dies; see figure 3.1b) results in the greatest performance increase. Stacking dies rank-wise yields a 35% performance increase (over a conventional off-chip DRAM configuration); further increasing the bus width to 64 bytes (so a cache line can be transferred in a single cycle) results in a 72% performance increase. Finally, going to a "true 3D" implementation with vertical ranks generates an impressive 117% performance increase. The work also contains a parameter sweep with varying numbers of memory controllers and ranks and shows that increasing the number of memory interfaces has better performance characteristics than increasing the number of ranks. The HMC model presented in this dissertation has an organization closer to figure 3.1a (i.e., the lower performing configuration): banks are contained within partitions located on a single DRAM die.

### 3.3 Low Level Studies

Facchini, et al. [24] develop a model for computing TSV power and use it to explore the energy-saving potential of stacking a DRAM die on top of a logic die in the context of mobile applications. They show that due to the improved electrical characteristics of the TSVs, simpler CMOS transceivers can be used to eliminate a significant portion of the bus power as compared to conventional DRAM.

CACTI-3DD [38] is an extension to CACTI-D to model the power, performance, and die area of 3D stacked DRAM. The authors also show, similarly to [37],

that a "coarse-grain" stacking for each rank is unable to take full advantage of the TSV bandwidth, whereas a fine-grain "vertical rank" (where banks are spread vertically through the stack as opposed to horizontally on a single die) is able to achieve better performance and power characteristics.

Weis, et al. [29] explore the design space for how best to stack commodity DRAM dies for mobile applications with a focus on the internal structure (ex: number of banks per layer, number of data I/O TSVs). They find that a 1 Gbit 3D stack has 15x energy efficiency compared to LP-DDR devices when using a 64 Mbit tile size with x128 I/O.

### 3.4 Serially Attached Stacked DRAM

Udipi, et al. [3] examine how the use of emerging silicon photonics can be efficiently utilized to connect a CPU to an off-chip 3D stacked memory. Unlike much of the other related work in this area, their main memory is not stacked directly on top of the CPU. They propose an interface die that sits below the memory dies and converts the photonic packet interface into electrical signals and handles the low-level memory scheduling details. They examine various configurations of photonic stops in order to most effectively amortize the photonics power costs. Finally, they propose an "unscheduled" interface policy between the CPU memory controller and the DRAM to try to reduce complexity.

The work in [3] builds on their previous work [39] that proposes to alleviate the "overfetch" problem (i.e., bringing an enormous number of bits into the row buffers

but only using a tiny fraction of them) by making DRAM rows much shorter. One of the biggest challenges they cite in this work is the lack of throughput between the smaller banks and the main memory controller. In their new work, the TSVs provide the low latency and high bandwidth path from the banks to the interface die, thereby eliminating the bottleneck. They are able to take advantage of the parallelism of a large number of banks through the usage of the TSVs.

Although the architecture presented in their work is very similar to the HMC (high speed links providing an abstract memory interface connected to an interface die with multiple memory controllers), their paper focuses more heavily on the photonics aspect of optimizing the architecture.

Kim, et al. [40] develop a "memory-centric network" of hybrid memory cubes that operate as both a storage and interconnect network for multiple CPUs. They attempt to maximize HMC storage capacity while lowering request latencies in the network through various routing techniques. This work focuses more on the interconnection aspects of the network of HMCs while we focus on the performance evaluation of a single cube and chains of cubes connected to a single host (and not multiple hosts). We also focus more heavily on understanding the internal dynamics of the memory cube as opposed to the traffic patterns between cubes.

## Chapter 4

## Methodology

### 4.1 HMC Simulator

All of the experiments performed are done using a C++ HMC simulator developed by our group. The cycle-based simulator models the entire HMC architecture including the high speed links, the link/vault interconnect, flow control, vault controller logic, and DRAM devices with their full set of timings. The initial version of the simulator was developed during a project that involved HMC modeling for Micron but was later modularized and generalized so that it can model any arbitrary 3D stacked memory device.

Although the internal logic and abstract protocol of the HMC has many practical advantages for the memory system (see 2.2.5), it also complicates academic HMC research. HMC vendors can hide the internals of the device behind the protocol and compete with one another by changing the internals of the device to deliver more performance with less power and cost. This type of competition is very difficult in a conventional DDRx system since all vendors are bound by the timing parameters and behaviors of the DDR specification and consumers make their purchases largely based on cost. However, this means that typically vendors will obscure the internal structure and parameters of the architecture. Parameters such as DRAM timings, clock frequencies, interconnect details, etc., become proprietary details that

| Timing Parameter | $egin{array}{c} 	ext{Value (cycles @} \ t_{CK} = 1.25 	ext{ns}) \end{array}$ | Time (ns) | $egin{array}{c} 	ext{Value (cycles @} \ t_{CK} = 0.8 	ext{ns)} \end{array}$ |

|------------------|------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------|

| $t_{RP}$         | 11 cycles                                                                    | 13.75 ns  | 17 cycles                                                                   |

| $t_{CCD}$        | 4 cycles                                                                     | 5 ns      | 6 cycles                                                                    |

| $t_{RCD}$        | 11 cycles                                                                    | 13.75 ns  | 17 cycles                                                                   |

| $t_{CL}$         | 11 cycles                                                                    | 13.75 ns  | 17 cycles                                                                   |

| $t_{WR}$         | 12 cycles                                                                    | 15 ns     | 19 cycles                                                                   |

| $t_{RAS}$        | 22 cycles                                                                    | 27.5 ns   | 34 cycles                                                                   |

Table 4.1: DRAM timing parameters used in simulations. Based on the parameters published in [40]

are closely guarded by vendors.

### 4.2 HMC Parameters

## 4.2.1 DRAM Timing Parameters

Being a memory device, one of the fundamental parameters in an HMC device is the DRAM timings. Unfortunately, as mentioned in the previous section, the DRAM timing inside of the HMC is proprietary information. The simulations performed here use the DRAM timings published in [40] as they are, to the best of our knowledge, the most comprehensive set of parameters that are currently published. Furthermore, they are more pessimistic with respect to the 45 nm DRAM timings presented in [29] and are similar to the timings mentioned in [41].

For simplicity, however, we assume that the vault clock is a multiple of the link reference clock which is defined as 125 MHz per the HMC specification [22]. To compute the vault clock, we take vault throughput of 10 GB/s [42] and divide it

by the 32 TSV data lanes within each vault [23]. This yields a 2.5 Gb/s data rate, which, if we assume double data rate transmission, yields a 1.25 GHz TSV frequency ( $t_{CK} = 0.8$ ns). This frequency is precisely 10 times the link reference clock of 125 MHz. Table 4.1 shows the timing parameters used by [40], their equivalent time values, and our timing parameters based on a 0.8 ns clock period.

We note, however, that section 5.7.1 will show that small changes in DRAM timing parameters are unlikely to have a significant impact on the results presented here due to the large amount of memory-level parallelism in the HMC device.

#### 4.2.2 Switch Interconnect

The role of the interconnect in the logic layer is to connect links to local vaults and to other links. In the single cube case, the switch interconnect only needs to connect links to vault vaults and vice versa. In the chained case, however, the switch also needs to connect links to other links to pass remote requests to a different cube.

Several presentations refer to the interconnect as a full crossbar [21], whereas the HMC specification refers to a switch structure where each link can service several local vaults with a lower latency than requests to non-local vaults. We will assume the switch interconnect is a crossbar switch due to the lack of details of the implementation of a different switch structure.

Since a flit is the smallest unit of data transmission, we assume that all of the data flows through the links and switches as individual flits until they arrive at the vault controller where they are re-assembled into transactions. Although the flits travel through the system as individual pieces of data, we enforce that flits from two transactions can never interleave when travelling between two endpoints (i.e., all of the flits in a transaction must complete between two points before the flits from another transaction can transmit).

#### 4.2.3 Vault Controller

As transactions arrive at the vault controller from the switch, their flits are re-assembled into transactions and are placed in a command queue. The vault controller uses a First Ready First Come First Serve (FR-FCFS) [43] policy where ready requests can bypass stalled ones. While the controller will reorder requests, it will not reorder dependent requests ahead of one another.

Read responses are held in a "read return queue" as they wait to be transmitted on the switch back to a link. When a vault's read return queue fills up, the controller must stall the execution of all reads to avoid losing data.

We assume the vault controllers will use a closed page policy in which an implicit precharge command immediately follows the DRAM column access. That is, a row is immediately closed after data is written to or read from that row. This is in contrast to another row buffer policy called "open page" which leaves the DRAM row open by keeping its data in the row buffer and allows for subsequent read or write accesses to that row to be serviced from the buffer. For memory access patterns that exhibit high levels of temporal and spatial locality, leaving a DRAM row open can increase performance by amortizing a single row activation over many column

accesses. On the other hand, open page row buffer models also impose a logic cost as the scheduling hardware is typically more complex: queues must be scanned to find transactions that can be scheduled early to an open row to make full use of the open row. Heuristics about when rows are likely to be reused must be carefully designed to avoid needlessly keeping rows open and incurring a power penalty. Furthermore, when an open page policy is used on workloads with little locality, delaying the precharge between accesses to different rows increases the latency of requests.

Server and HPC workloads typically exhibit little or no locality either due to the underlying algorithm (e.g., pointer chasing or sparse floating point computations) or the execution model (e.g., highly threaded server workloads). There is indication that the HMC's DRAM devices have been redesigned to have shorter rows [23] (256 bytes rather than 8-16 KB in a typical DDR3 device). The reduced row length helps to save power by alleviating the so-called "overfetch" problem where many bits are brought into the sense amplifiers but few are used. Shorter rows, however, reduce the probability of a row buffer hit, making open page mode impractical. Moreover, with the large number of banks in each cube, it is more efficient to utilize the high level memory-level parallelism to achieve high performance rather than to rely on locality which may or may not be present in a given memory access stream. For these reasons, we select a closed page row buffer policy for the simulations presented here.

## 4.3 Random Stream Methodology

In order to gain an understanding of the performance characteristics of various design choices, an exploration of the design space is required. Such a step through the design space involves changing many variables simultaneously and thus requires hundreds or potentially thousands of individual simulation runs. Running a full system simulation for each combination of variables is not feasible given that a full system simulation can take anywhere from several hours to several days. Therefore, to gain an initial understanding of how different variables affect performance, we perform random stream simulation for both single and multiple cube configurations.

In addition to having a much lower execution time than full-system simulations, random stream simulations have several useful properties that make them ideal for an initial design space exploration:

• Zero Locality: Random streams exhibit no spatial or temporal locality which represents the worst case performance scenario for modern processors as it renders caches ineffective for hiding memory latency. Furthermore, modern server applications execute many threads which substantially decrease the amount of locality in the memory access stream [44]. Similarly, many high performance computing applications utilize sparse data structures which require dereferencing multiple pointers to reach a particular data item (graphs, sparse matrices, etc.) Such "pointer chasing" algorithms generate a memory access stream that appears to be random. Therefore, a random stream is a good first order approximation for these types of applications as it represents a worst-case

scenario where caches are ineffective and there is maximum load on the main memory system.