**ABSTRACT**

Title of Thesis: MINIATURE THERMOELECTRIC COOLERS FOR ON-

**CHIP HOT SPOTS**

Viatcheslav Litvinovitch, Master of Science, 2009

Thesis Directed By: Professor Avram Bar-Cohen

Department of Mechanical Engineering

Following Moore's Law, semiconductor transistor density has doubled roughly every 18 months to alleviate increasing IC performance demands. Growing microprocessor complexity and performance, coupled with the functional integration of logic and memory components in chip architecture, have led to highly non-uniform on-chip power distribution. The resulting localized high heat flux "hot spots" are becoming a major difficulty due to their propensity for degrading microprocessor performance and for significantly reducing chip reliability.

Most conventional cooling techniques provide uniform cooling to the device and do not focus much attention on the hot spots themselves. Therefore, other innovative and novel thermal management techniques must be explored to aggressively and selectively combat the deleterious effects of on-chip hot spots. This thesis explores two previously proposed thermal management techniques utilizing thermoelectrics to cool on-chip hot spots: the silicon microcooler with an integrated SiGe superlattice layer and the minicontact enhanced conventional thermoelectric cooler (TEC).

## Miniature Thermoelectric Coolers for On-Chip Hot Spots

Viatcheslav Litvinovitch

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science 2009

#### Thesis Committee:

Professor Avram Bar-Cohen, Chair and Advisor Professor Bao Yang, Co-Advisor Professor F. Patrick McCluskey

# ©Copyright by

Viatcheslav Litvinovitch

2009

#### Acknowledgements

The completion of my graduate research and graduate courses could not have been successful without the help and support of others. I would like to thank those who have contributed their time and knowledge to guide me along the way.

First and foremost, I would like to thank my advisor, Dr. Avram Bar-Cohen, who has been instrumental in teaching me about heat transfer, thermoelectrics, and electronic packaging. He gave me an opportunity to pursue graduate studies when I was only an undergraduate junior and I am most grateful. It has truly been a pleasure to work for him and learn from his wealth of knowledge and experience. I would also like to thank my coadvisor Dr. Bao Yang and thesis committee member Dr. F. Patrick McCluskey for always being available when I needed help or when I came to them with a question. I've learned a great deal from our courses together and our numerous discussions.

I am also grateful for the help, encouragement, and comical relief of my lab mates: Juan Cevallos, Emil Rahim, Patrick Luckow, Jessica Sheehan, Chris Bachmann, Dae Whan Kim, Jeff Kahn, Vinh Khuu, Horacio Nochetto, Frank Robinson, Robin Zimmermann, and in particular Peng Wang, who mentored me in the early stages of my research; much of this thesis is based on his work.

Additionally, I would like to thank the Industrial Technology Research Institute in Taiwan for partial sponsorship of my research.

Finally, I'd like to thank parents, Serguei and Lucy, who always supported me and allowed me to find my own path, and my fiancé, Mallory, who always believed in me and provided me with love, happiness, and peace of mind.

## TABLE OF CONTENTS

| Acknowledgements                                                | iii  |

|-----------------------------------------------------------------|------|

| Table of contents                                               | iv   |

| List of tables                                                  | viii |

| List of figures                                                 | ix   |

| 1. Introduction                                                 | 1    |

| 1.1 Description of hot spot problem and motivation for research | 1    |

| 1.2 Overview of Thermal Management Techniques                   | 5    |

| 1.2.1 Passive Cooling                                           | 5    |

| 1.2.2 Active Cooling                                            | 5    |

| 1.2.2.1 Principles of Thermoelectrics                           | 7    |

| 1.2.2.1.1 Thermoelectric Figure of Merit                        | 11   |

| 1.2.2.2 Past Research in TEC Cooling of On-chip Hot Spots       | 14   |

| 1.3 Scope of Work                                               | 15   |

| 2. Superlattice µTEC Hot Spot Cooling                           | 18   |

| 2.1 Introduction                                                | 18   |

| 2.2 TE Microcooler Thermophysics                                | 19   |

| 2.3 Modeling Methodology for On-chip Hot Spot Cooling           | 24   |

| 2.3.1 FEM Model Validation                                      | 28   |

| 2.3.2 Model Simplifications                                     | 32   |

| 2.4 Results and Discussion                                      | 33   |

| 2.4.1 Thermal Characteristics of a TE Microcooler               | 33   |

| 2.4.2 Parametric Analysis                                       | 38   |

| 2.4.2.1 Superlattice Thickness                                         |  |

|------------------------------------------------------------------------|--|

| 2.4.2.2 Si Chip Thickness                                              |  |

| 2.4.2.3 Microcooler Size                                               |  |

| 2.4.2.4 Hot Spot Size and Hot Spot Heat Flux44                         |  |

| 2.5 Conclusion                                                         |  |

| 3. TEC Mini-Contact Cooling of On-chip Hot Spot                        |  |

| 3.1 Introduction                                                       |  |

| 3.2 Mechanism and Simulation of Mini-Contact Enhanced TEC for Hot Spot |  |

| Cooling49                                                              |  |

| 3.2.1 Concept of Mini-Contact Pad49                                    |  |

| 3.2.2 Numerical simulation of Taiwanese Mini-Contact Package50         |  |

| 3.2.2.1 Package Geometry50                                             |  |

| 3.2.2.2 Boundary Conditions57                                          |  |

| 3.2.2.2.1 Contact resistance                                           |  |

| 3.2.2.3 Material Properties                                            |  |

| 3.2.2.4 Element and Mesh Description61                                 |  |

| 3.3 Results                                                            |  |

| 3.3.1 Temperature Field63                                              |  |

| 3.3.2 Influence of Electric Current                                    |  |

| 3.3.3 Mini-Contact Size70                                              |  |

| 3.3.4 Optimized TEC71                                                  |  |

| 3.3.5 Impact of the TIM2 layer on hot spot temperature73               |  |

| 3.3.6 Decreased Lateral Heat Spreader Gap in TETEC Package 76          |  |

| 3.3.7 Additional Simulations for the Taiwanese 250μm and 500μm                     |

|------------------------------------------------------------------------------------|

| TECs77                                                                             |

| 3.3.8 Additional simulations for the TFTEC81                                       |

| 3.4 Conclusion83                                                                   |

| 4. Effect of Thermal Contact Resistance on Optimum Mini-Contact TEC Cooling of On- |

| Chip Hot Spots84                                                                   |

| 4.1 Introduction84                                                                 |

| 4.2 Simulation Study of Mini-Contact Enhanced TEC for Hot Spot Cooling85           |

| 4.2.1 Description of Numerical Model85                                             |

| 4.2.2 Modeling the TEC88                                                           |

| 4.3 Simulation Results and Discussions                                             |

| 4.3.1 Mini-Contact TEC Temperature Profiles91                                      |

| 4.3.2 Effect of Input Power on TEC95                                               |

| 4.3.3 Effect of Thermal Contact Resistance96                                       |

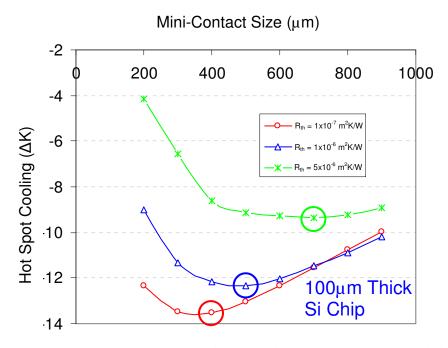

| 4.3.3.1 Combined with Effect of Mini-Contact Size97                                |

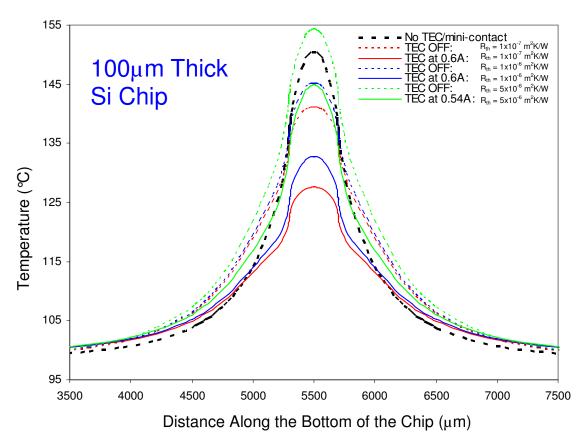

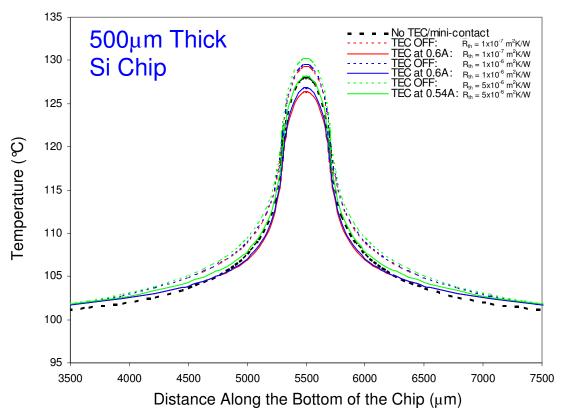

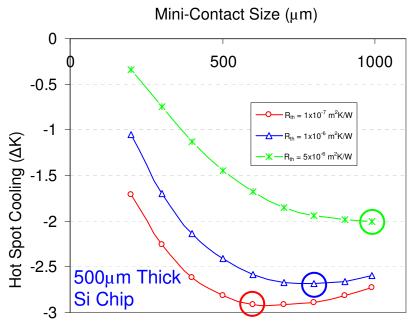

| 4.3.3.2 Combined with Effect of Silicon Chip Thickness98                           |

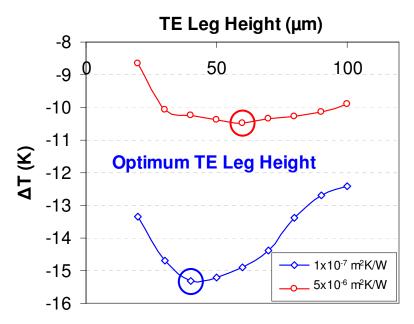

| 4.3.3.3 Combined with Effect of Thermoelectric Leg Height99                        |

| 4.4 Conclusion                                                                     |

| 5. Experimental Testing of Mini-Contact Enhanced TEC                               |

| 5.1 Introduction                                                                   |

| 5.2 Experimental Setup                                                             |

| 5.2.1 Preparing the Si Die                                                         |

| 5.2.2 Machining the Mini-Contact                                                   |

| 5.2.3 Attaching the Mini-contact                            | 106 |

|-------------------------------------------------------------|-----|

| 5.2.4 Attaching the TEC                                     | 107 |

| 5.2.5 Attaching the Cu Spacer, Heat Spreader, and Heat Sink | 107 |

| 5.3 Thermal Test and Experimental Results                   | 108 |

| 5.3.1 Numerical Validation                                  | 112 |

| 5.4 Conclusion                                              | 115 |

| 6. Conclusions and Future Work                              | 117 |

| 6.1 Conclusions                                             | 117 |

| 6.1.1 Conclusions for the Superlattice Microcooler          | 117 |

| 6.1.2 Conclusions for the Mini-Contact Enhanced TEC         | 118 |

| 6.2 Future Work                                             | 119 |

| Doforances                                                  | 121 |

#### LIST OF TABLES

- Table 2.1: Geometry and Material Properties for μTEC-cooled Chip Package

- Table 3.1: FE Package Geometry and Thermal Conductivity for Taiwanese TEC

- Table 3.2: FE Package Geometry and Thermal Conductivity for commercial TFTEC

- Table 4.1: Package dimensions and material properties

- Table 4.2: Hot spot temperature reduction for optimized TE leg height and mini-contact sizes at each thermal contact resistance, with surrounding sensitivity. Si chip thickness =  $100\mu m$

#### LIST OF FIGURES

- Figure 1.1: The 2005 ITRS predictions of feature size, chip size and transistor density for high performance microprocessor chips [1]

- Figure 1.2: 2006 iNEMI road map for chip power in high performance servers [5]

- Figure 1.3: Hot spots resulting from non-uniform power on an Intel Pentium ® III processor (a) and an Intel Itanium ® processor [7]

- Figure 1.4: Schematic illustrating typical die power map (a) and hot spot on the corresponding temperature map (b) [8]

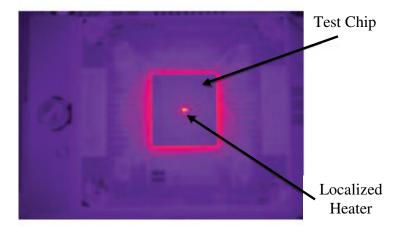

- Figure 1.5: Infrared image of the test chip when only the localized, high heat flux, "hot spot" heater is powered [10]

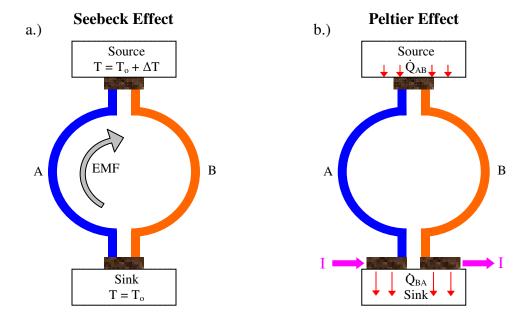

- Figure 1.6: Conceptual schematic of the Seebeck effect (a) and the Peltier effect (b) [12]

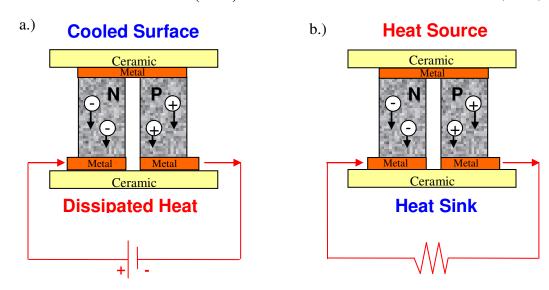

- Figure 1.7: Functional diagram of a thermoelectric cooler (a) and thermoelectric generator (b)

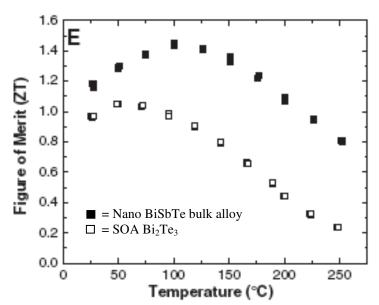

- Figure 1.8: ZT temperature dependence for nanocrystalline BiSbTe alloy and state-of-the-art Bi<sub>2</sub>Te<sub>3</sub> material [15]

- Figure 2.1: Transmission Electron Micrograph of Superlattice Microcooler from Shakouri '06 [21]

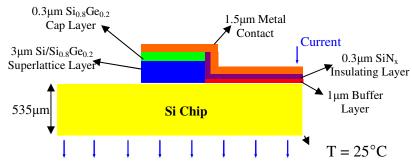

- Figure 2.2: Schematic of the thermoelectric microcooler model

- Figure 2.3: Thermoelectric Microcooler with Integrated SiGe Superlattice Layer

- Figure 2.4: Finite Element Model of Chip Cooled by  $\mu$ TEC (a) Entire chip package FE model, (b) Heat flux distribution on the bottom of the chip surface, (c) Image of the model meshing in ANSYS<sup>TM</sup>, (d) Mesh sensitivity for the silicon microcooler

- Figure 2.5: Zhang *et al* "3D Electrothermal Simulation of Heterostructure Thin Film Micro-coolers" 2003 [36]

- Figure 2.6: Temperature Distribution in Chip with Integrated Superlattice Microcooler [Chip=535 $\mu$ m Silicon; Superlattice = 3 $\mu$ m thick,  $60x60\mu$ m<sup>2</sup>, 0.6A, and  $7.11x10^{-7} \Omega$ –cm<sup>2</sup> contact resistance; ambient temperature = 25°C]

- Figure 2.7: Surface Temperature Reductions with Superlattice Microcoolers

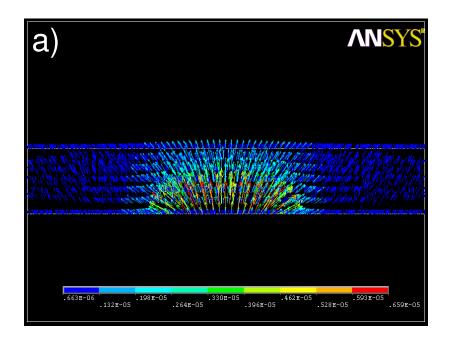

- Figure 2.8: Heat flux distribution in silicon chip with hot spot [q"=680W/cm², L=70μm] (a) no TEC cooling and (b) with TEC cooling from a <u>silicon</u> microcooler operating at 0.6Amps.

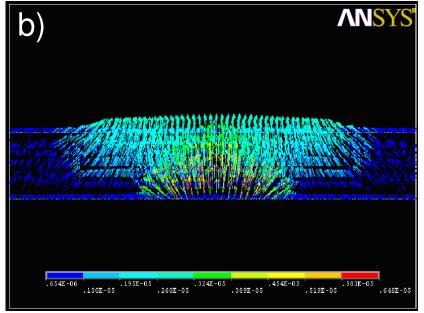

- Figure 2.9: Heat flux distribution in the silicon chip with hot spot [q"=680W/cm<sup>2</sup>, L=70µm] (a) no TEC cooling and (b) with TEC cooling from a <u>superlattice</u> microcooler operating at 0.6Amps.

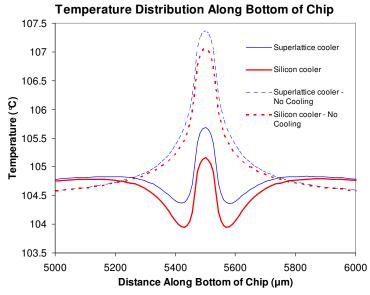

- Figure 2.10: Temperature distribution along the bottom of a  $\mu$ TEC-cooled silicon chip die with hot spot [operating at 0.6Amps and 0Amps, respectively]

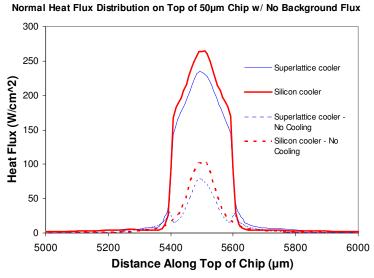

- Figure 2.11: Normal heat flux profile along the top of a  $\mu$ TEC-cooled 50 $\mu$ m thick silicon chip [0.6 Amps and 0 Amps, 200x200 $\mu$ m<sup>2</sup> microcooler, 70x70 $\mu$ m<sup>2</sup> hot spot, 680 W/cm<sup>2</sup> heat flux at hot spot.]

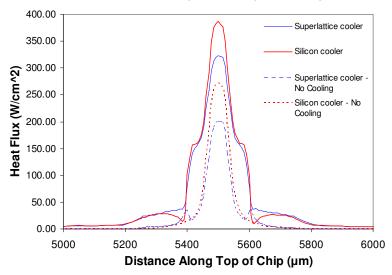

- Figure 2.12: Normal heat flux profile along the top of a  $\mu$ TEC-Cooled 20 $\mu$ m thick silicon chip [0.6 Amps and 0 Amps,  $200x200\mu\text{m}^2$  microcooler,  $70x70\mu\text{m}^2$  hot spot,  $680 \text{ W/cm}^2$  heat flux at hot spot.]

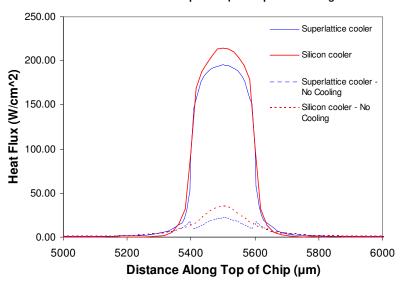

- Figure 2.13: Normal heat flux profile along the top of a  $\mu$ TEC-cooled 100 $\mu$ m thick silicon chip [0.6 Amps and 0 Amps, 200x200 $\mu$ m<sup>2</sup> microcooler, 70x70 $\mu$ m<sup>2</sup> hot spot, 680 W/cm<sup>2</sup> heat flux at hot spot.]

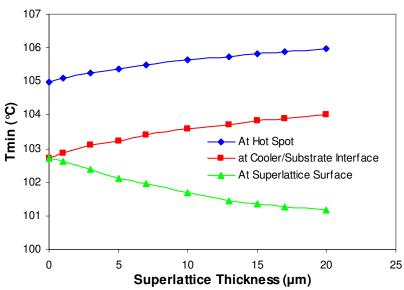

- Figure 2.14: Temperature variation in superlattice cooled silicon chip varying superlattice thickness  $[200x200\mu m^2 \text{ cooler}, 50\mu m \text{ Si chip}, 70x70\mu m^2 \text{ hot spot, and } 680\text{W/cm}^2 \text{ hot spot heat flux}].$

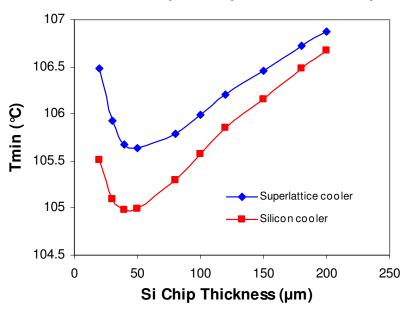

- Figure 2.15: Temperature variation in  $\mu$ TEC cooled silicon chip varying chip thickness [200x200 $\mu$ m<sup>2</sup> cooler, 10 $\mu$ m superlattice, 70x70 $\mu$ m2 hot spot, and 680W/cm<sup>2</sup> hot spot heat flux].

- Figure 2.16: Temperature reduction in  $\mu$ TEC cooled silicon chip varying chip thickness [200x200 $\mu$ m<sup>2</sup> cooler, 10 $\mu$ m superlattice, 70x70 $\mu$ m<sup>2</sup> hot spot, and 680W/cm<sup>2</sup> hot spot heat flux].

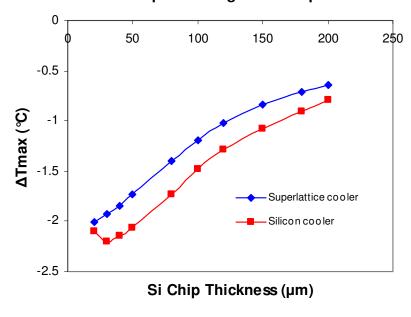

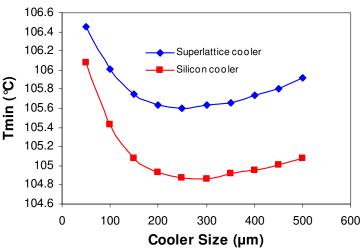

- Figure 2.17: Temperature variation in  $\mu$ TEC cooled silicon chip varying microcooler size [10 $\mu$ m superlattice, 50 $\mu$ m Si chip, 70x70 $\mu$ m<sup>2</sup> hot spot, and 680W/cm<sup>2</sup> hot spot heat flux].

- Figure 2.18: Temperature reduction in  $\mu$ TEC cooled silicon chip varying microcooler size [10 $\mu$ m superlattice, 50 $\mu$ m chip, 70x70 $\mu$ m² hot spot, and 680W/cm² hot spot heat flux].

- Figure 2.19: Temperature variation in  $\mu$ TEC cooled silicon chip varying hot spot size [10 $\mu$ m superlattice, 50 $\mu$ m chip, 200x200 $\mu$ m microcooler, and 680W/cm hot spot heat flux].

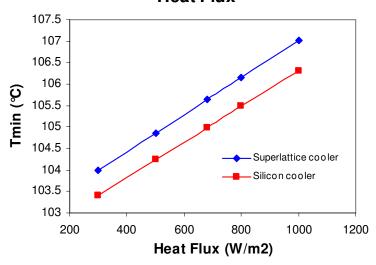

- Figure 2.20: Temperature variation in  $\mu$ TEC cooled silicon chip varying hot spot heat flux [10 $\mu$ m superlattice, 50 $\mu$ m Si chip, 200x200 $\mu$ m<sup>2</sup> microcooler, and 70x70 $\mu$ m<sup>2</sup> hot spot].

- Figure 2.21: Temperature reduction in  $\mu$ TEC cooled silicon chip varying hot spot size [10 $\mu$ m superlattice, 50 $\mu$ m chip, 200x200 $\mu$ m microcooler, and 680W/cm hot spot heat flux].

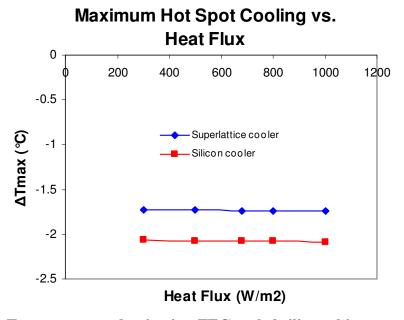

- Figure 2.22: Temperature reduction in  $\mu$ TEC cooled silicon chip varying hot spot heat flux [10 $\mu$ m superlattice, 50 $\mu$ m Si chip, 200x200 $\mu$ m microcooler, and 70x70 $\mu$ m hot spot].

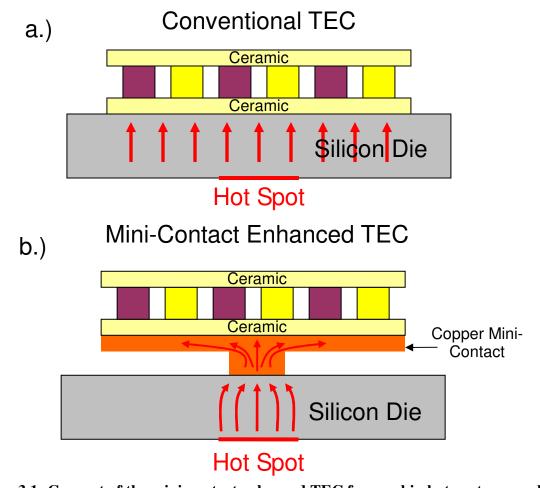

- Figure 3.1: Concept of the mini-contact enhanced TEC for on-chip hot spot removal

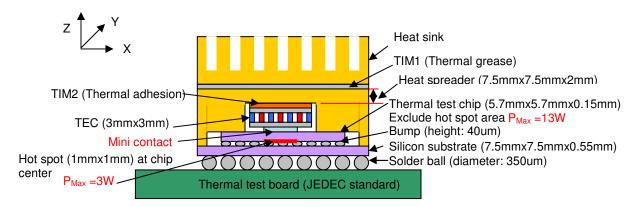

- Figure 3.2: Proposed Taiwanese mini-contact chip package with Taiwanese designed TEC [39]

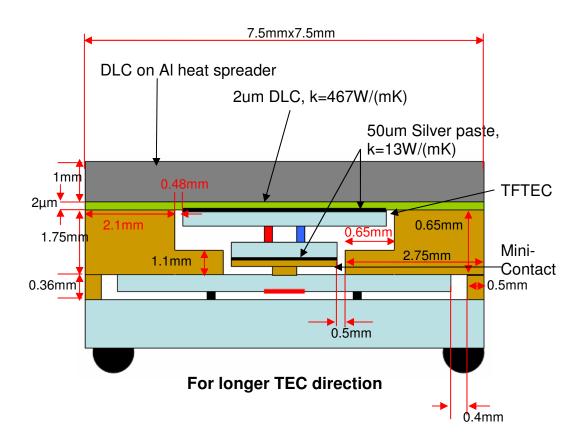

- Figure 3.3: Proposed Taiwanese mini-contact chip package with commercial TFTEC [40]

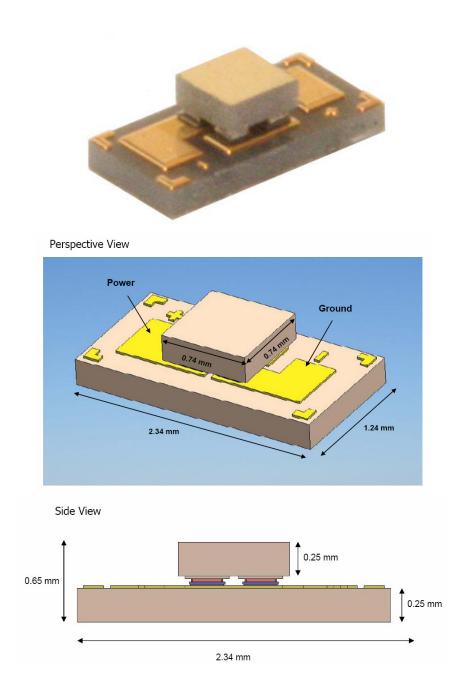

- Figure 3.4: Photograph of the commercial TFTEC (a) [41], perspective (b) and side views of the TFTEC with dimensions (c) [42]

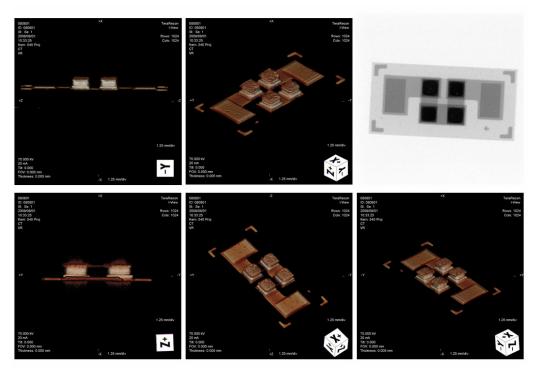

- Figure 3.5: SEM images of the TFTEC [43]

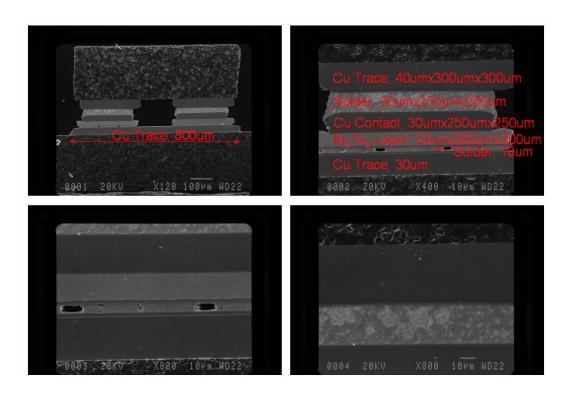

- Figure 3.6: Zoom SEM images of the Cu trace, solder, and Bi<sub>2</sub>Te<sub>3</sub> layers in the TFTEC with dimensions [43]

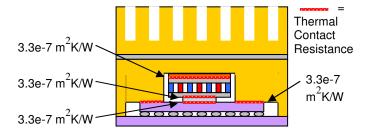

- Figure 3.7: Thermal contact resistance modeled in the Taiwanese chip package

- Figure 3.8: Quarter-symmetry model of TEC

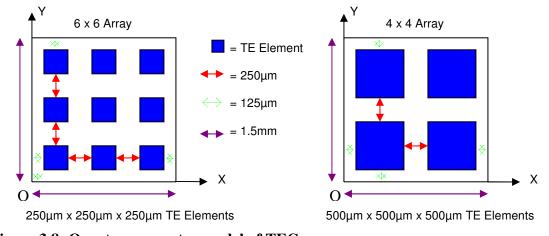

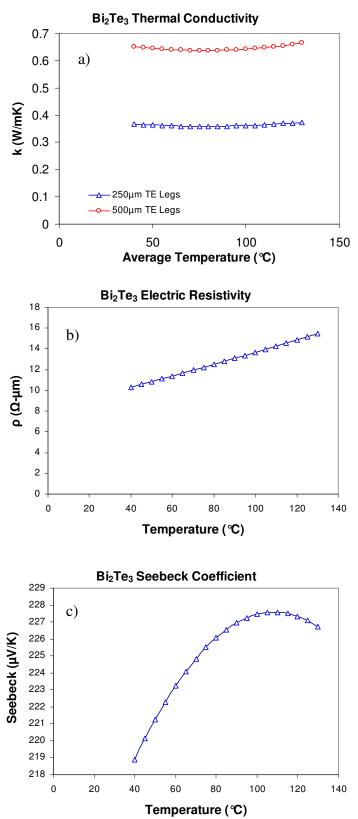

- Figure 3.9: Temperature dependent properties for Bi<sub>2</sub>Te<sub>3</sub>: a) Thermal conductivity, b) Electric Resistivity, c) Seebeck coefficient

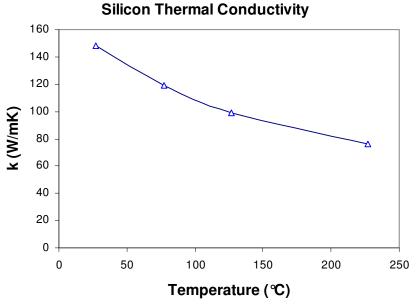

- Figure 3.10: Temperature dependent thermal conductivity for silicon

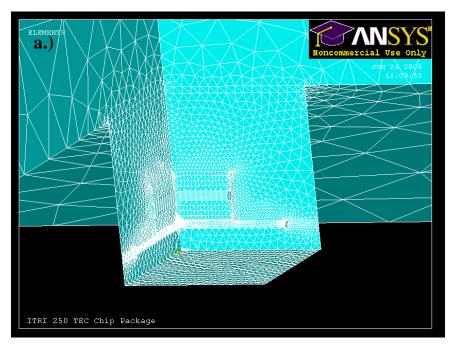

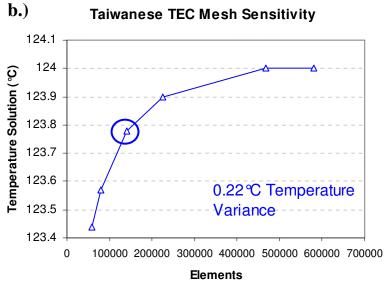

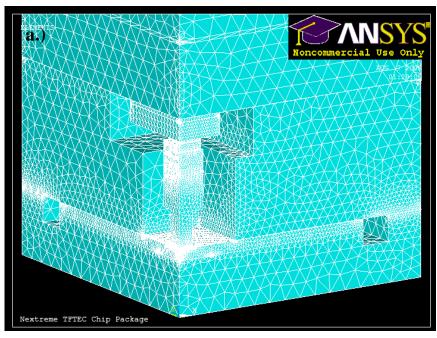

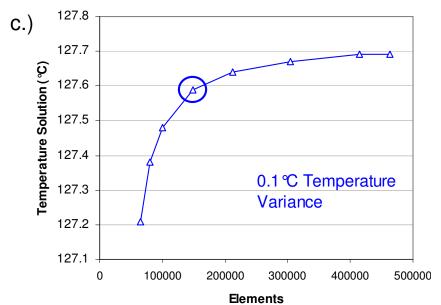

- Figure 3.11: Image of the ANSYS<sup>TM</sup> mesh distribution (a) and mesh sensitivity (b) for the Taiwanese TEC Package

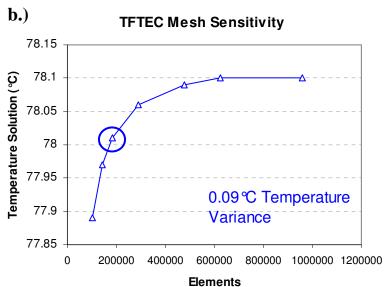

- Figure 3.12: Image of the ANSYS $^{TM}$  mesh distribution (a) and mesh sensitivity (b) for the TFTEC Package

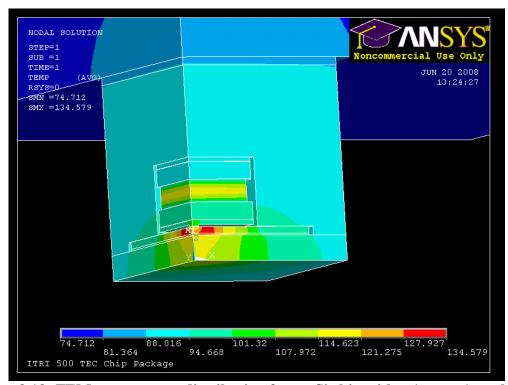

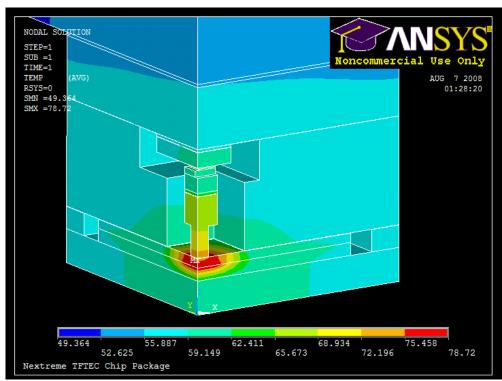

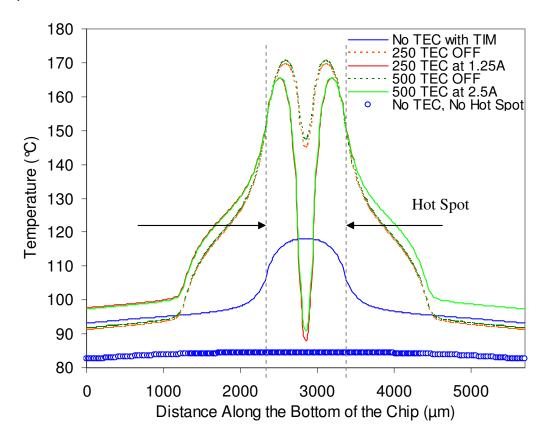

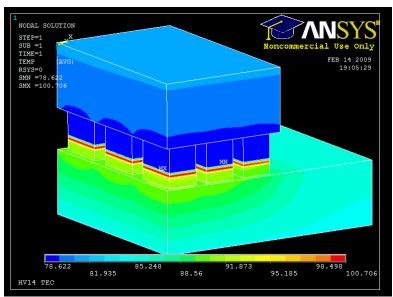

- Figure 3.13: FEM temperature distribution for an Si chip with a 1mm x 1mm hot spot producing a 300W/cm<sup>2</sup> heat flux and background heat flux of 40W/cm<sup>2</sup>. The 500μm Taiwanese TEC is used with the 300μm x 300μm mini-contact

- Figure 3.14: FEM temperature distribution for an Si chip with a 1mm x 1mm hot spot producing a 300W/cm<sup>2</sup> heat flux and background heat flux of 40W/cm<sup>2</sup>. The TFTEC is used with the 400µm x 400µm mini-contact

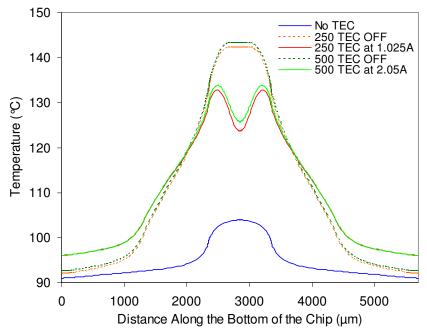

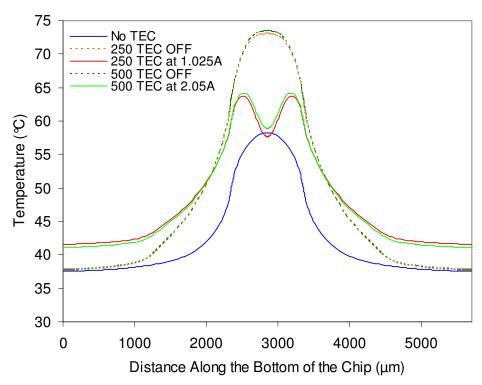

- Figure 3.15: Temperature profile along the bottom of the silicon chip, each respective TEC is operating at its optimum current and the optimum mini-contact size of  $300\mu m$  x  $300\mu m$  is used with the TECs

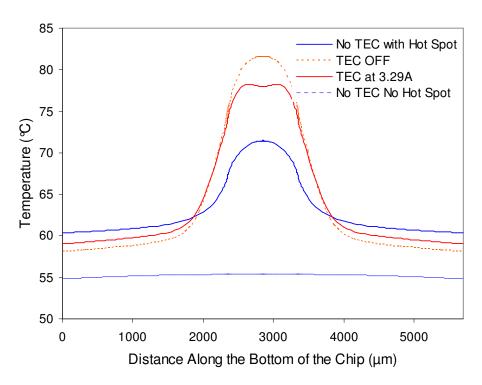

- Figure 3.16: Temperature profile along the bottom of the silicon chip. Commercial TFTEC is operating at its optimum current of 3.29A and the optimum mini-contact size of  $400\mu m \times 400\mu m$  is used

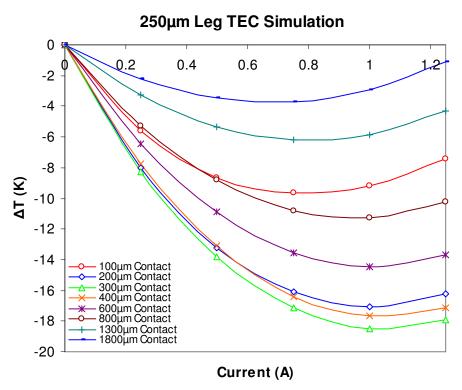

- Figure 3.17: Cooling as a function of input current to the 250µm Taiwanese TEC for various mini-contact sizes

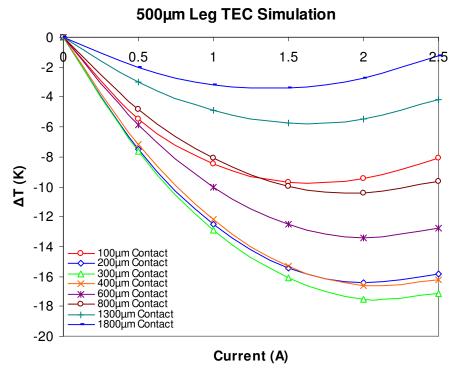

- Figure 3.18: Cooling as a function of input current to the 500µm Taiwanese TEC for various mini-contact sizes

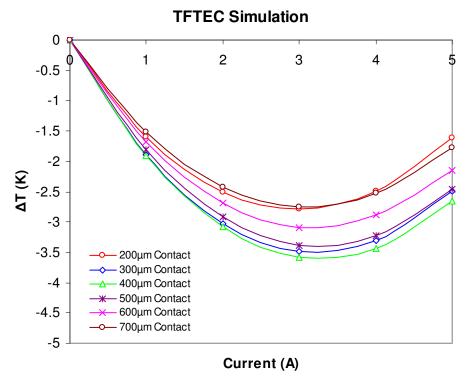

- Figure 3.19: Cooling as a function of input current to the commercial TFTEC for various mini-contact sizes

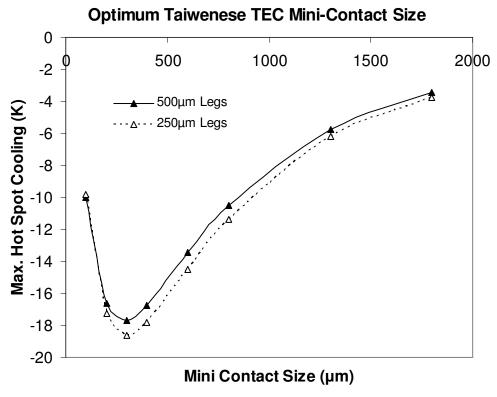

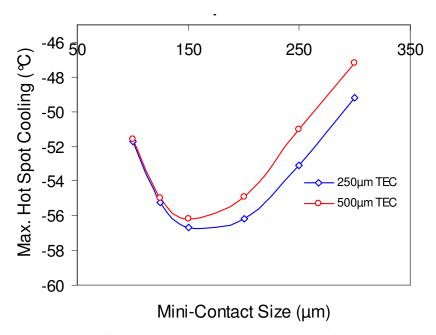

- Figure 3.20: Maximum achievable hot spot cooling as a function of mini-contact size for the Taiwanese TECs

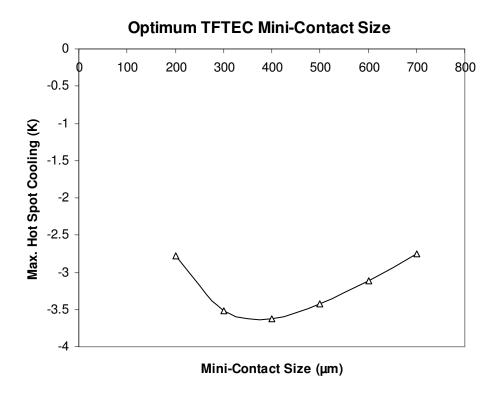

- Figure 3.21: Maximum achievable hot spot cooling as a function of mini-contact size for the TFTEC

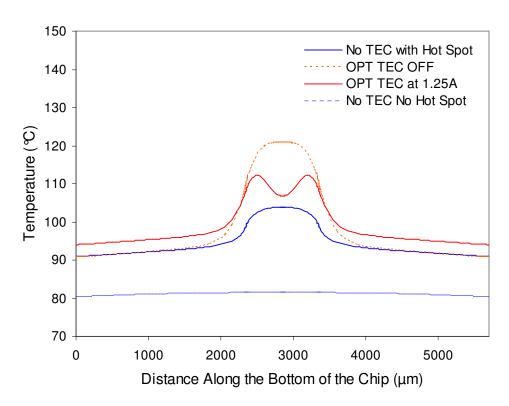

- Figure 3.22: Optimum 40μm TEC leg length with optimum 400μm x 400μm minicontact TE legs have lateral dimensions of 150μm x 150μm with 50μm gaps. 1.25A produces a maximum cooling value of 13.3K

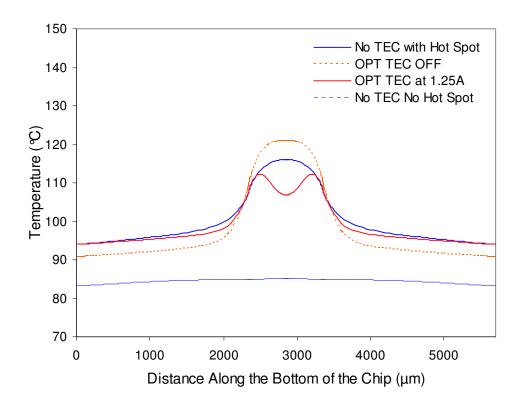

- Figure 3.23: Original Taiwanese TEC temperature profiles with new hot spot temperature profile

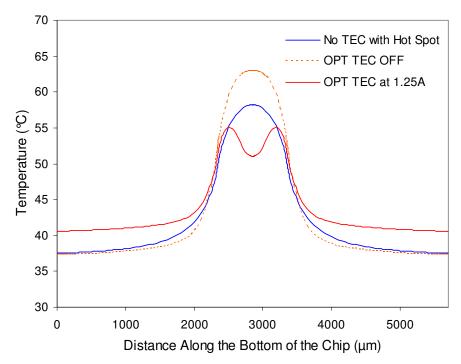

- Figure 3.24: TEC with optimized leg length and mini-contact with new hot spot temperature profile

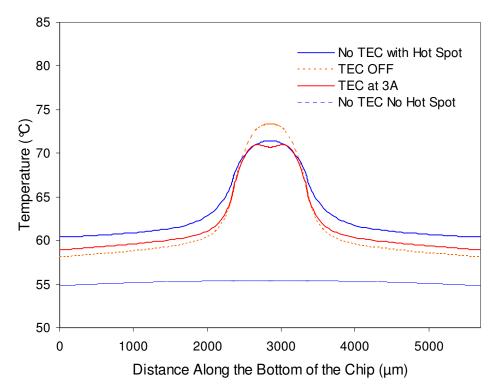

- Figure 3.25: Temperature Profile for TFTEC with a 100µm lateral heat spreader gap. TFTEC is operating at its optimum current of 3A with an optimum mini-contact size of 300µm x 300µm.

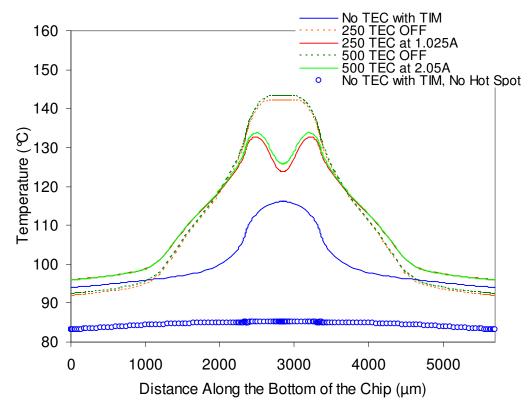

- Figure 3.26: Temperature Profiles for Taiwanese 250µm and 500µm Leg TEC with No Background Heat Flux on Chip. Each respective TEC is operating at its optimum current and the optimum mini-contact size of 300µm x 300µm

- Figure 3.27: Temperature Profiles for the Optimized TEC with No Background Heat Flux on Chip. Optimum 40µm TEC leg length with optimum 400µm x 400µm mini-contact

- Figure 3.28: 25μm Thick Si Chip: Optimum Mini-Contact Size for 250μm and 500μm Taiwanese TECs

- Figure 3.29: Temperature profile along the bottom of a  $25\mu m$  Thick Si Chip for the  $250\mu m$  and  $500\mu m$  Taiwanese TECs operating at optimum current and the optimum mini-contact size of  $150\mu m$  x  $150\mu m$

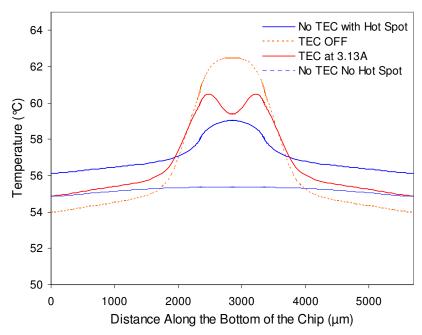

- Figure 3.30: Temperature Profile for TFTEC: Hot Spot has a heat flux of 100W/cm<sup>2</sup>. TFTEC is operating @ optimum current of 3.13A and with 400x400µm<sup>2</sup> mini-contact. Hot spot heat flux has been reduced from 300W/cm<sup>2</sup> to 100W/cm<sup>2</sup>

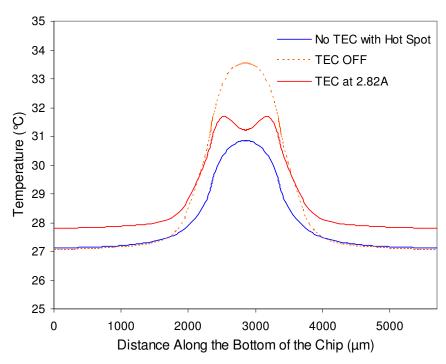

- Figure 3.31: Temperature Profile for TFTEC: No Background Heat Flux and Hot Spot has a heat flux has been reduced from 300W/cm<sup>2</sup> to 100W/cm<sup>2</sup>. TFTEC is operating @ optimum current of 2.82A with 400x400µm<sup>2</sup> mini-contact

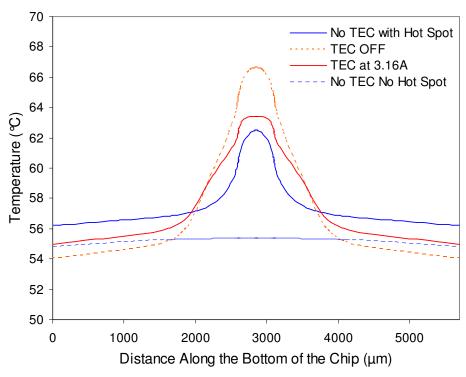

- Figure 3.32: Temperature Profile for TFTEC: Hot Spot is reduced to  $500\mu m \times 500\mu m$ . TFTEC is operating @ optimum current of 3.16A with  $400x400\mu m^2$  mini-contact. Hot spot flux remains  $300W/cm^2$

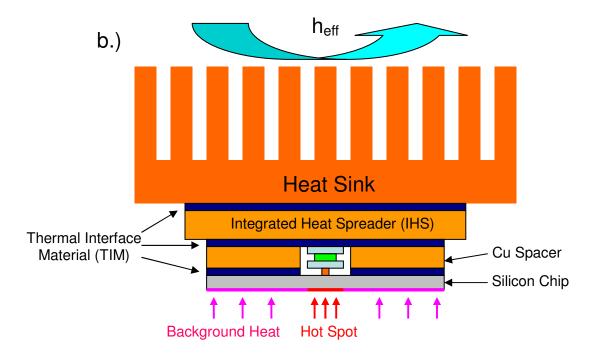

- Figure 4.1: Schematic of a typical package (a) and schematic of package with a minicontact enhanced TEC (b) (not drawn to scale), and ANSYS<sup>TM</sup> model mesh sensitivity (c)

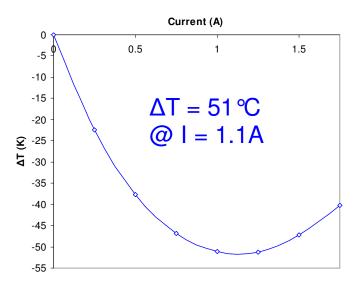

- Figure 4.2: Quarter model image of the TEC used in the numerical simulations operating at 1.1A

- Figure 4.3: Temperature reduction at the cold side of the TEC as a function of input current (only the TEC is modeled)

- Figure 4.4: Temperature distribution on the bottom (active) surface of the chip at various thermal contact resistances; zoomed in on hot spot region. Mini-contact size is optimized (refer to figure 14), TE leg length =  $20\mu m$

- Figure 4.5: Temperature distribution on the bottom (active) surface of the chip at various thermal contact resistances; zoomed in on hot spot region. Mini-contact size is optimized (refer to figure 15), TE leg height =  $20\mu m$

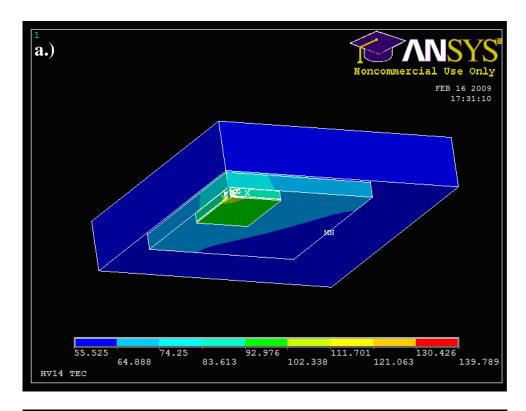

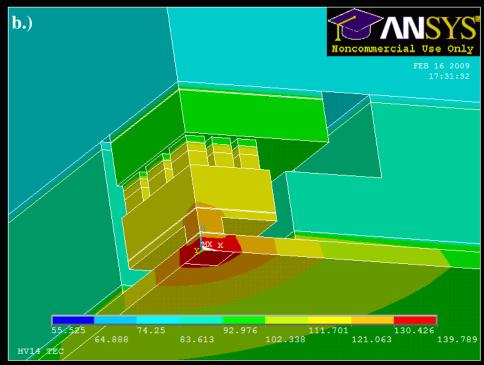

- Figure 4.6: The chip package (a) and zoomed in on mini-contact/TEC (b) for the optimized TE leg height and mini-contact size at  $R_{th} = 1 \times 10^{-7}$  m<sup>2</sup>K/W. (TEC current = 0.38A, TE leg height =  $50 \mu m$ , mini-contact =  $300 \times 300 \mu m^2$ , Si chip thickness =  $100 \mu m$

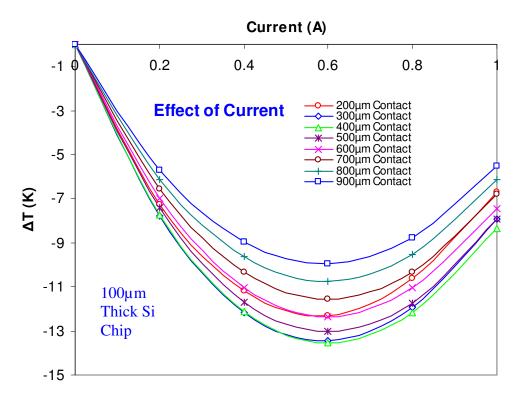

- Figure 4.7: Effect of TEC input current on hot spot temperatures for different minicontact tip sizes. TE leg height =  $20\mu m$ ,  $R_{th} = 1 \times 10^{-7} m^2 K/W$

- Figure 4.8: Hot spot temperature reduction associated with optimum mini-contact sizes at different thermal contact resistances. TE leg height = 20µm

- Figure 4.9: Hot spot temperature reduction associated with optimum mini-contact sizes at different thermal contact resistances. TE leg height = 20µm

- Figure 4.10: Hot spot temperature reduction associated with variations in TE leg height. A 400x400µm² mini-contact is used and two different thermal contact resistances are explored

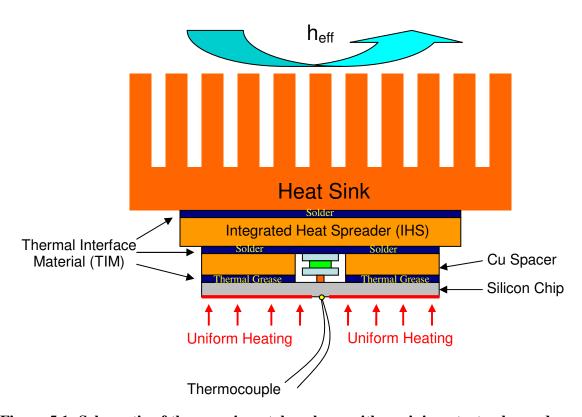

- Figure 5.1: Schematic of the experimental package with a mini-contact enhanced TEC (not drawn to scale)

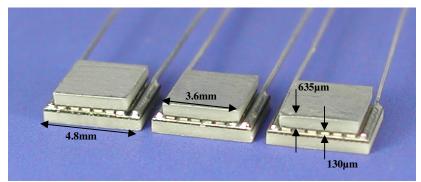

- Figure 5.2: Thermion<sup>TM</sup> TEC's with a 6x6 array of 130μm thick bismuth telluride TE legs [57]

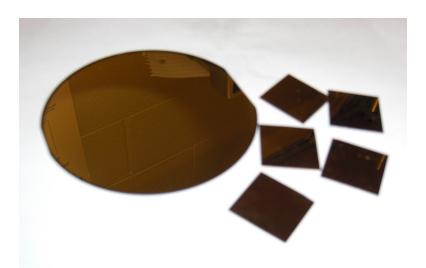

- Figure 5.3: Au coated Si wafer and dies used in the experiment

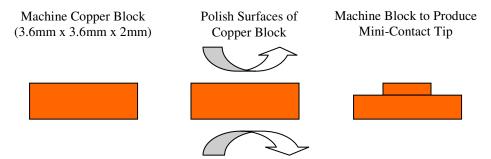

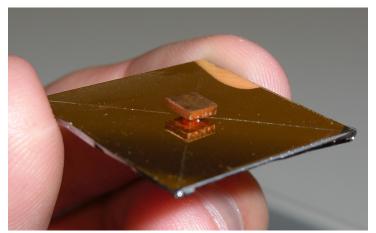

- Figure 5.4: Mini-contact machining process

- Figure 5.5: Mini-contact soldered onto Si die

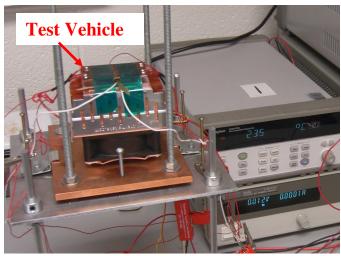

- Figure 5.6: Experimental test package with power supply and temperature measurement equipment

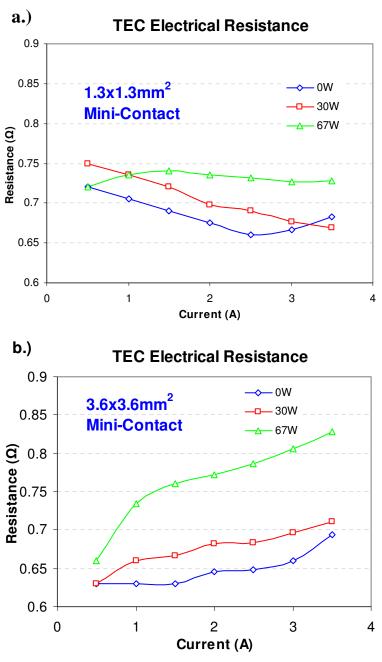

- Figure 5.7: Experimentally observed TEC electrical resistance variations at different input currents and temperatures for the 1.3x1.3mm<sup>2</sup> (a) and 3.6x3.6mm<sup>2</sup> (b) mini-contacts

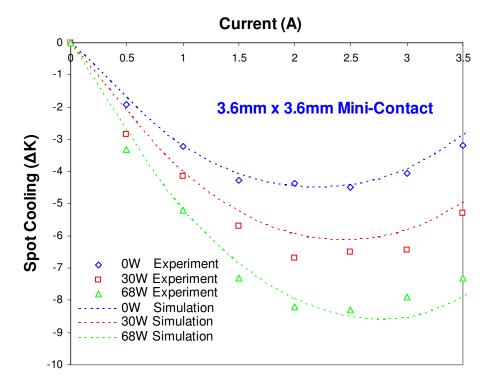

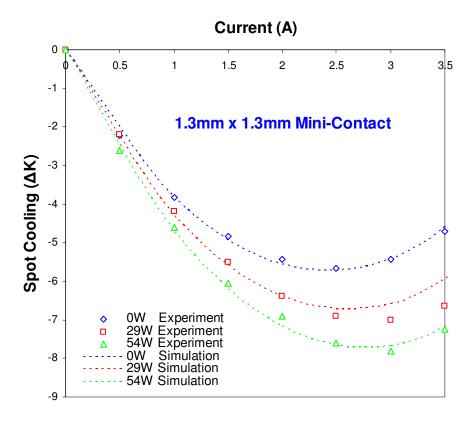

- Figure 5.8: Experimental and numerical spot cooling values, as a function of current, on a 500 $\mu$ m thick Si die with a TEC and 3.6x3.6mm<sup>2</sup> mini-contact. TE leg height = 130 $\mu$ m,  $R_{th} = 9x10^{-6}$  m<sup>2</sup>K/W at the TEC and  $2x10^{-6}$  m<sup>2</sup>K/W at the mini-contact/Si die

- Figure 5.9: Experimental and numerical spot cooling values, as a function of current, on a 500 $\mu$ m thick Si die with a TEC and 1.3x1.3mm<sup>2</sup> mini-contact. TE leg height = 130 $\mu$ m,  $R_{th} = 8.5 \times 10^{-5}$  m<sup>2</sup>K/W at the TEC and 2x10<sup>-6</sup> m<sup>2</sup>K/W at the mini-contact/Si die

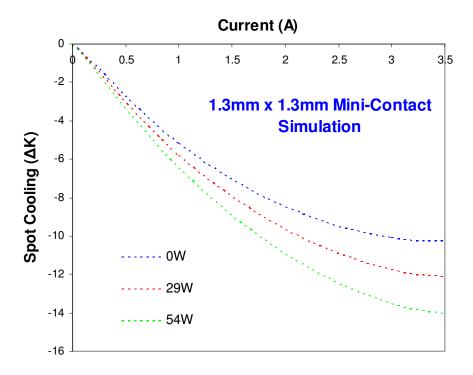

- Figure 5.10: Numerical model of 1.3x1.3mm<sup>2</sup> mini-contact experiment with low thermal contact resistance found in the 3.6x3.6mm<sup>2</sup> experiment ( $R_{th} = 9x10^{-6}$  m<sup>2</sup>K/W)

## Chapter 1

#### 1. Introduction

#### 1.1 Description of hot spot problem and motivation for research

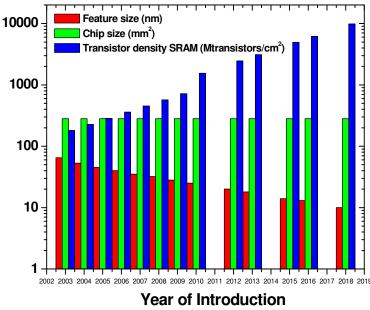

In the 1970's, Moore predicted that semiconductor transistor density would double roughly every 18 months in an effort to alleviate ever increasing IC performance demands. This trend, also known as Moore's Law, has proven itself to be an accurate forecast of future development in the IC packaging industry. The 2005 International Technology Roadmap for Semiconductors (ITRS), shown in figure 1.1, illustrates projected logarithmic increases in on-chip transistor density and logarithmic decreases in feature size over the next ten years, while chip size is expected to remain unchanged [1]. Smaller feature sizes on semiconductors lead to faster and more functional chips, although at the penalty of greater on-chip power dissipation. As a result of ever escalating chip power, elevated chip temperatures are becoming a significant problem that must be addressed.

Figure 1.1: The 2005 ITRS predictions of feature size, chip size and transistor density for high performance microprocessor chips [1]

Thermal management issues in IC packaging will be a key design driver in the next generation of semiconductor microprocessors. New and innovative thermal solutions will have to be developed to overcome the hurdle of rapidly growing on-chip heat generation that limits current device clock speeds and feature sizes. Precise temperature control is necessary in many of today's applications where performance depends on chip temperature uniformity, such as in power electronics and microprocessors. Performance may also be temperature sensitive, such as in IR detectors and semiconductor lasers, where device material properties often change with temperature.

In addition to performance concerns, reliability can also be expected to degrade in overheated devices. Some failure mechanisms, such as electromigration, are temperature dependent and can adversely affect device reliability at elevated temperatures. Also, transistor gate leakage current increases exponentially with temperature [2]. A relation for the mean time to failure (MTF) in semiconductor devices is given by Black's equation [3]:

$$MTF = AJ^2 \exp(\frac{E_A}{k_B T}) \tag{1.1}$$

where A is a constant, J is the current density,  $E_A$  is the active energy where the value for typical silicon failures is approximately 0.68eV,  $k_B$  is Boltzmann's constant and T is the absolute operating temperature. It had been observed that even a 5-10K overall temperature reduction can double the device reliability, in the normal operating temperature range [4].

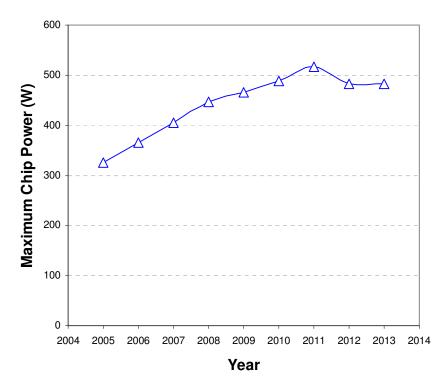

Thermal challenges in microprocessor packaging are likely to intensify as chip power dissipation levels are expected to climb in upcoming years. The 2006 iNEMI roadmap for maximum chip power of high performance servers shows that chip power

levels will soon reach over 500W (figure 1.2) [5]. The thermal barrier doesn't necessarily reside in coping with such high power levels, but in managing the uneven distribution of this power.

Figure 1.2: 2006 iNEMI road map for chip power in high performance servers [5]

Today's microprocessors accommodate many functional blocks that can produce an average heat flux of about  $10 \sim 50 \text{ W/cm}^2$  and a peak flux that can reach six times that of the surrounding areas [6]. Growing microprocessor complexity and performance, coupled with the functional integration of logic and memory components in chip architecture, have led to highly non-uniform on-chip power distribution. The resulting localized high heat flux "hot spots" are becoming a major difficulty due to their propensity for degrading microprocessor performance and for significantly reducing chip reliability.

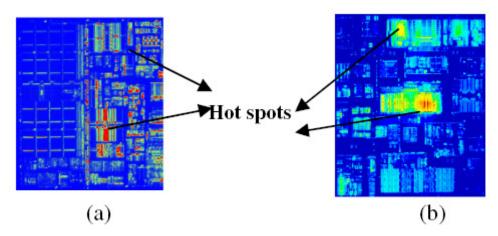

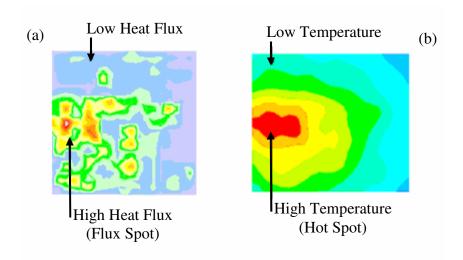

Examples of on-chip hot spots are shown in figures 1.3 and 1.4. Figure 1.3 shows two different Intel chips containing hot spot regions [7] and figure 1.4 shows a typical on-chip heat flux map with accompanying temperature map [8].

Figure 1.3: Hot spots resulting from non-uniform power on an Intel Pentium ® III processor (a) and an Intel Itanium ® processor [7]

Figure 1.4: Schematic illustrating typical die power map (a) and hot spot on the corresponding temperature map (b) [8]

Hot spots often drive the thermal design of the IC package because often they constitute the maximum on-chip junction temperatures (depending on the application,

maximum junction temperatures will be in the range of 90 to 110°C) [9]. Most conventional cooling techniques provide uniform cooling to the device and do not focus much attention on the hot spots themselves. This often results in unnecessarily overcooling the rest of the chip in an effort to bring down hot spot temperatures. Therefore, other innovative and novel thermal management techniques must be explored to aggressively and selectively combat the deleterious effects of on-chip hot spots.

#### 1.2 Overview of Thermal Management Techniques

#### 1.2.1 Passive Cooling

Passive cooling is one of the most commonly used thermal management techniques in today's IC packaging technology. This method relies mainly on heat conduction, spreading, and natural convection. Research in passive cooling focuses on engineering high thermal conductivity materials and low thermal resistance interfaces. Advantages of passive cooling include low complexity, low cost and high reliability, while some disadvantages may include low heat removal, bulkiness, and the inability to cool below ambient temperature. Some examples of passive cooling techniques include heat spreaders, natural convection heat sinks, pool boiling, and reconfiguring the chip architecture to achieve a more uniform heat dissipation and to take maximum advantage of conduction spreading.

#### **1.2.2** Active Cooling

Active cooling is typically more expensive than passive cooling and involves moving parts and/or the input of electrical power. This method actively pumps heat from a heat source to a heat sink. Some common forms of active cooling involve fan cooled

heat sinks, fluid pumped through microchannels, and jet impingement cooling. Thermoelectric coolers, or TECs, are also a form of active cooling and offer a unique and promising solution to the hot spot problem. Some advantages of TECs include their solid state design, the absence of moving parts, high reliability, and their capability to selectively target and cool hot spots.

Recently, Chowdhury et al demonstrated that a high heat flux on-chip hot spot could be cooled by 15°C using an integrated miniature thermoelectric cooler [10]. This advancement in chip scale cooling was achieved by a 3.5mm x 3.5mm thin film TEC (TFTEC) with only a ~100µm total device thickness. The thermoelectric material within the device consisted 5-8µm thick p-type Bi<sub>2</sub>Te<sub>3</sub>/Sb<sub>2</sub>Te<sub>3</sub> of n-type Bi<sub>2</sub>Te<sub>3</sub>/Bi<sub>2</sub>Te<sub>2.83</sub>Se<sub>0.17</sub> superlattices that were grown by metal-organic chemical vapor deposition (MOCVD) on GaAs substrates [10]. Figure 1.5 shows a thermal image of the Si chip with a localized heater that simulates the active hot spot to be cooled by the miniature thermoelectric cooler (heat spreader and TEC are not shown). In this study, the 400μm x 400μm hot spot produced a heat flux of 1250W/cm<sup>2</sup>.

Figure 1.5: Infrared image of the test chip when only the localized, high heat flux, "hot spot" heater is powered [10]

Since miniaturized thermoelectric devices can be focused directly on the hot spots and not overcool the rest of the device, they offer a distinctive and energy efficient way of cooling on-chip semiconductor hot spots. Moreover, this technology has been experimentally demonstrated to work and yield significant hot spot temperature reductions. In order to understand the physics behind thermoelectrics, a brief overview is provided in the next section.

#### 1.2.2.1 Principles of Thermoelectrics

The thermoelectric effect can be described as the conversion of energy between electricity and heat. There are three types of thermoelectric effects that occur: the Seebeck effect, the Peltier effect, and the Thomson effect. These effects are found to be thermodynamically reversible and act in conjunction with irreversible effects such as Joule heating and thermal conduction.

Figure 1.6: Conceptual schematic of the Seebeck effect (a) and the Peltier effect (b) [12]

The Seebeck effect occurs when two dissimilar conductors are joined at two points that are maintained at different temperatures. An electromotive force will develop over the closed loop that can be measured by inserting a voltmeter into the loop; it is also known as the thermocouple voltage [11]. The Seebeck effect for materials A and B, shown in figure 1.6a, is interfacial and arises when charge carriers in a conductor are exposed to a temperature gradient within the conductor. The hotter electrons will diffuse more readily than colder electrons and tend to migrate to the colder area. This produces an electric flow of current that lasts as long as there is a temperature difference along the conductor.

The Peltier effect is the principal effect concerned with thermoelectric refrigeration or heat pumping. This effect is also interfacial and transports heat between two different conductors, from one junction to another, when an electric current passes through the closed loop circuit. In figure 1.6b, heat is absorbed at one junction and carried to the other. The Peltier heat is linear with respect to current, in contrast to the irreversible Joule heat, which is quadratic with respect to current. The rate at which heat is absorbed is proportional to the current and depends on the nature of the two materials comprising the junction. Compared to the Seebeck effect, where heat flow induces an electric current, the Peltier effect is opposite, with an electric current induced a heating or cooling effect.

Also noteworthy is the Thomson effect, which is a bulk effect that transports heat within a current carrying material at one temperature to the same material at a different temperature (i.e. in a material with a temperature gradient). Phonons and electrons act as the two modes of heat transfer and this effect can be thought of as the

evolution/absorption of heat in a conducting material whenever a current traverses that material with a temperature gradient, thereby transporting electrons of one temperature to a zone with electrons at another temperature. Thomson heat, like the Peltier heat, is reversible and is in addition to any irreversible Joule heat [11].

A conventional thermoelectric device is typically comprised of an array of p- and n-type semiconductor materials that are oriented in series electrically but in parallel thermally. A high conductivity metal such as copper is typically used to electrically connect the semiconductor pillars and complete the electric circuit. This circuit is usually sandwiched between two ceramic substrates that are electrically insulated but thermally conductive, such as AlN. Schematics of a thermoelectric cooler and thermoelectric generator are shown in figures 1.7a and 1.7b, respectively. Bismuth telluride (Bi<sub>2</sub>Te<sub>3</sub>) and its alloys are commonly used as the semiconductor materials in many applications because of their high thermoelectric properties, reflected in the commonly-used thermoelectric metric ( $Z = S^2/\rho k$ ) at near room temperature, which is described later. In particular, Bi<sub>2</sub>Te<sub>3</sub> shows the best thermoelectric properties at the desired temperature range for on-chip thermal management [13].

#### **Thermoelectric Cooler (TEC)**

#### Thermoelectric Generator (TEG)

Figure 1.7: Functional diagram of a thermoelectric cooler (a) and thermoelectric generator (b)

Since the goal of this thesis is to utilize thermoelectrics as heat pumps, the Peltier effect will be of most interest. Equation 1.2 shows the defining function that describes the Peltier effect [11]:

$$Q = (S_p - S_n)T_cI - \frac{1}{2}I^2R - K(T_h - T_c)$$

(1.2)

where Q is the net rate of heat transfer in watts,  $S_n$  and  $S_p$  are the Seebeck coefficients for the negative and positive thermoelectric legs, respectively,  $T_c$  and  $T_h$  are the temperatures at the cold and hot sides of the TEC, respectively, I is current, R is the electrical resistance, and K is the thermal conductance. This equation shows the competition between the Seebeck coefficient term, which is responsible for TEC cooling, and the parasitic effects of Joule heating and back heat conduction from the electrical resistance and thermal conductance terms, respectively. The power input in watts required to produce the effect described in (1.2) can be written as [11]:

$$W = I^{2}R + (S_{p} - S_{n})(T_{h} - T_{c})I$$

(1.3)

and the coefficient of performance for a TEC heat pump can be written as:

$$COP = Q/W (1.4)$$

The COP is a common metric used to quantify the effectiveness of a heat engine. It is also important to quantify the amount of heat that a TEC can transfer and the maximum temperature difference across the TEC. Derived from the efficiency equation of a TEC, the equation for maximum heat flux pumping capability can be written as [14]:

$$q_{max} = \frac{1}{L} \left[ \frac{S^2 T_c^2}{2\rho} - k(T_h - T_c) \right]$$

(1.5)

and the maximum temperature reduction across the TEC can be estimated as:

$$\Delta T_{\text{max}} = \frac{S^2 T_c^2}{2k\rho} = \frac{ZT_c^2}{2}$$

(1.6)

where L is the height of the thermoelectric legs,  $\rho$  is the electrical resistivity, and k is the thermal conductivity. Equations 1.5 and 1.6 imply having thin TE legs and maximizing the S<sup>2</sup>T/ $\rho$ k term, which is commonly known as the thermoelectric figure of merit (ZT), reflected in equation 1.6.

#### 1.2.2.1.1 Thermoelectric Figure of Merit

The thermoelectric figure of merit (ZT) is a dimensionless parameter used to assess the usefulness of a semiconductor for use in thermoelectric heat engines. This

parameter is derived from the efficiency equation of the thermoelectric device and combines the coefficients of the electrical and thermal properties of the semiconductor materials. A principal aim of research and development in thermoelectric materials is to fabricate semiconductors having a value as high as possible for the figure of merit over the applicable temperature range of the device [12]. The terms Z and T are shown in equations 1.7 and 1.8 respectively, where T is the mean temperature of the TE leg [11].

$$Z = \left[ \frac{S_p - S_n}{\sqrt{k_p \rho_p} + \sqrt{k_n \rho_n}} \right]^2$$

(1.7)

$$T = \frac{T_c + T_h}{2} \tag{1.8}$$

When the positively and negatively charged thermoelectric semiconductor materials have similar thermal and electrical properties, Z can be written in a more simplified form:

$$Z = \frac{S^2}{\rho k} \tag{1.9}$$

where S,  $\rho$ , and k are the average Seebeck coefficients, electrical resistivities, and thermal conductivities of the p- and n-type elements. In equation 1.9, k is kept low to reduce conduction from the hot side back to the cold side,  $\rho$  is kept low to reduce Joule heating, and S is kept high to get the greatest possible temperature difference per given amount of electrical potential (voltage), or vice versa.

Recent advancements in improving ZT values include the work of Poudel *et al*, who achieved a peak ZT of 1.4 at 100°C from a bismuth antimony telluride (BiSbTe) ptype nanocrystalline bulk alloy [15]. This material is an alloy of Bi<sub>2</sub>Te<sub>3</sub> and is made by hot pressing nanopowders that are ball-milled from crystalline ingots. Figure 1.8 shows ZT values as a function of temperature for the nanocrystalline BiSbTe alloy compared to state-of-the-art based Bi<sub>2</sub>Te<sub>3</sub> material. ZT is about 1.2 at room temperature and peaks at about 1.4 at 100°C, which makes these materials useful for microprocessor cooling applications.

Figure 1.8: ZT temperature dependence for nanocrystalline BiSbTe alloy and state-of-the-art Bi<sub>2</sub>Te<sub>3</sub> material [15]

Since the 1950s, the ZT of Bi<sub>2</sub>Te<sub>3</sub> based alloys near room temperature has remained around 1. The improvement in ZT, in this study, results from low thermal conductivity caused by random nanoscale inclusions in the bulk material; causing increased phonon scattering by grain boundaries and defects. The thermoelectric properties of this material were also found to be isotropic, compared to state-of-the-art

Bi<sub>2</sub>Te<sub>3</sub> based alloys, which have layered structures and, consequently, anisotropic thermoelectric properties [15]. Advancements in the figure of merit ZT have been a major driver in the development of high performance, low cost bulk thermoelectric materials.

#### 1.2.2.2 Past Research in TEC Cooling of On-chip Hot Spots

Proposed uses of miniaturized TECs (μTECs) for on-chip thermal management have included attachment of conventional TECs (using bulk TE materials), as well as the formation of superlattice thin film TE material layers, on the back of the microprocessor chip. Conventional TECs have been attached to the back side of a flip chip and cooled the entire surface area of the chip [16,17] and bulk bismuth telluride pellets have also been directly attached to a silicon chip to form an on-chip TEC without ceramic interfaces [18]. Additionally, thin film Bi<sub>2</sub>Te<sub>3</sub> [19,20] and silicon germanium (SiGe) [21,22] layers have been grown directly on silicon substrates before, but none of these studies have considered the thermal effects of the μTEC on a hot spot.

Previous research efforts by Wang *et al* have investigated various hot spot cooling applications of  $\mu$ TECs on the back side of a microprocessor chip [23-25]. One of the studied approaches, termed the silicon microcooler, consisted of a doped semiconductor chip that contained a hot spot and a very thin deposited SiGe cap layer and peripheral ring electrode layer on the surface of the chip opposite of the hot spot. This approach takes advantage of the high power factor ( $S^2/\rho$ ) of the silicon and essentially utilizes the silicon chip itself as the thermoelectric cooler. Wang *et al* have built a numerical [23] and analytical model [24] of the silicon microcooler problem to explore parametric trends in hot spot temperature reduction associated with varying chip and microcooler geometry, boundary conditions, and Si doping concentration. Another  $\mu$ TEC hot spot cooling

approach researched by Wang, Bar-Cohen, and Yang has been the mini-contact TEC [25]. The mini-contact is a high thermal conductivity pad, usually made of copper, which is attached to a conventional TEC in order to concentrate and optimize the cooling flux of the TEC. The tip of the mini-contact is attached to the back side of the chip and is used to selectively remove hot spot heat.

#### 1.3 Scope of Work

The passive and active thermal management techniques described above have been researched in depth but many of them do not offer a comprehensive solution to the semiconductor hot spot problem. Conventional chip cooling techniques involving heat sinks or heat pipes uniformly cool the entire surface of the chip and do not focus on particular high heat flux regions such as hot spots. The research focus of this thesis expands on the work of Wang, Bar-Cohen, and Yang and examines unexplored applications of the silicon microcooler and mini-contact TEC hot spot cooling approaches. The specific contributions of this thesis are: (1) a numerical model of a modified silicon microcooler, with an integrated SiGe superlattice layer, and parametric comparison to the original silicon microcooler; (2) a parametric investigation into the viability of commercially available TEC technology compatible with the mini-contact hot spot cooling approach; (3) a study of thermal contact resistance impact on mini-contact TEC cooling; (4) a multi-optimization and functional dependence analysis of various parameters in a mini-contact TEC chip package; and (5) new experimental results for a mini-contact enhanced conventional TEC with 130µm thick Bi<sub>2</sub>Te<sub>3</sub> thermoelectric legs. It is to be noted that all of the subsequent chapters are based on published and/or submitted papers on the silicon microcooler [23,24,26,27] and the mini-contact enhanced TEC [25,28,29].

This thesis presents various numerical results for the two outlined hot spot cooling approaches (silicon/superlattice microcooler and mini-contact enhanced TEC) and presents experimental results to validate the numerical model. The thesis is organized as follows:

Chapter 1 discusses present and future thermal challenges in the IC microprocessor industry and outlines the presence of the hot problem. Thermoelectrics are introduced as potential candidates to alleviate on-chip hot spots and a brief overview into the background of thermoelectrics is given. Past research into thermoelectrics along with the objective of this thesis are also presented.

Chapter 2 provides the results of three-dimensional, electro-thermal, finite-element modeling of a superlattice microcooler, focusing on the hot spot temperature and superlattice surface temperature reductions, respectively. Simulated temperature distributions and heat flow patterns in the silicon, associated with variations in microcooler geometry, chip thickness, hot spot size, hot spot heat flux, and superlattice thickness are provided. Comparison is made to hot spot cooling achieved by the Peltier effect in the silicon microprocessor chip itself.

Chapter 3 focuses on the mini-contact TEC cooling approach and outlines the numerical simulation results for three different chip packages proposed by a Taiwanese national laboratory [30], two containing Taiwanese designed TECs, and one containing a commercially available thin film TEC (TFTEC) [31]. A Taiwanese IC package with an actual on-chip hot spot is presented and modeled numerically using ANSYS<sup>TM</sup> FE

software. A description of the model assumptions and parameters is given and the thermal behavior of the Taiwanese and commercial TEC devices, as well as the hot spot, is characterized. Several optimizations were completed to enhance thermal performance and suggestions were made to improve overall cooling for future studies of the minicontact TEC approach.

Chapter 4 studies another variation of the mini-contact TEC hot spot cooling approach. This chapter presents numerical simulations, with a finite-element package-level model, to examine the parasitic effects of the thermal contact resistance, at the interfaces of the mini-contact and TEC, on the cooling efficacy of this thermal solution. Particular attention is devoted to the deleterious effect of contact resistance on the thermoelectric leg height and the mini-contact size required to achieve the greatest hot spot temperature reduction on the chip. Data from experiments with TEC's, having a leg height of 130µm, combined with several sizes of mini-contact pads, are used to validate the modeling approach and the overall conclusions.

Chapter 5 outlines a proof of concept experiment designed to demonstrate the spot cooling capability of a mini-contact enhanced conventional TEC. A brief description of the experimental setup is provided. The experimental results are used to validate the ANSYS<sup>TM</sup> numerical model and provide confidence in further using this numerical model to investigate the effects of on-chip hot spots and thermal contact resistance.

Chapter 6 recapitulates the findings of this research and offers recommendations for future work.

### Chapter 2

### 2. Superlattice µTEC Hot Spot Cooling

#### 2.1 Introduction

Driven by shrinking feature sizes, microprocessor "hot-spots" – with their associated high heat flux and sharp temperature gradients – have emerged as the primary "driver" for on-chip thermal management of today's advanced IC technology. Among the techniques proposed to combat the effects of hot spots, thermoelectric microcoolers ( $\mu$ TECs) provide unique advantages. Their solid state design, the absence of moving parts, and their ability to target micron-sized, high heat flux areas, make such  $\mu$ TECs an ideal micro-cooling solution.

Miniaturized silicon thermoelectric coolers have been shown to provide significant hot spot remediation capability, e.g. removing nearly 80% of the hot spot temperature rise in a 70x70μm hot spot with a heat flux of 680W/cm² on a 50μm thick silicon chip [23]. Silicon-Germanium superlattice structures, formed on the back of a silicon chip, have also been proposed for hot spot remediation [32], but there have been few detailed studies on the cooling capability of such devices.

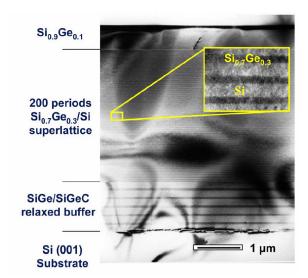

Superlattice structures are typically comprised of tens-to-hundreds of alternating layers of nanometer thick films, together forming a composite thin film structure several microns thick, as exemplified in figure 2.1. The large number of very thin active layers in such superlattices is known to reduce phonon thermal conductivity, through "phonon trapping" at the interfaces between the alternating layers, and to achieve a far more rapid response time than conventional TEC's [21], due to the low mass of the microcooler, as well as to display high heat flux removal capability, due to the reduced joule heating in

the thin superlattice. The present interest in the use of superlattice TEC's has been prompted by these attributes, and most prominently, the relatively high value of the TEC figure-of-merit, ZT ( $S^2T/\rho k$ ) reported in the literature [33].

The objective of this study is to evaluate hot spot cooling performance of a thermoelectric silicon microcooler, comprised of a silicon chip and a SiGe cap layer on top of the chip, compared to a microcooler with an integrated SiGe superlattice layer between the silicon chip and the SiGe cap layer. The study will explore the influence of superlattice thickness, silicon chip thickness, microcooler size, hot spot size, and hot spot heat flux intensity on the hot spot and superlattice temperatures, respectively. This chapter is based on previous publications [23,24,26,27,34].

Figure 2.1: Transmission Electron Micrograph of Superlattice Microcooler from Shakouri '06 [21]

#### 2.2 TE Microcooler Thermophysics

Two thermoelectric microcooler configurations are examined in this study: one containing a superlattice structure and one without. First, a simple silicon microcooler

will be introduced and explained, followed by an integrated superlattice structure for comparison. These two models will be referred to as the silicon TE microcooler and the superlattice TE microcooler, respectively.

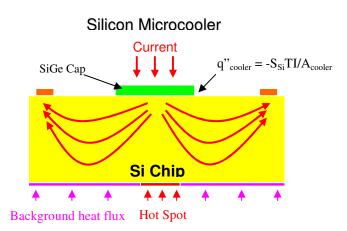

The structure of an on-chip silicon thermoelectric microcooler used for hotspot cooling is illustrated in figure 2.2. It is a single element silicon microcooler that uses the thermoelectric properties of the silicon chip itself. Electric current conducts laterally through the silicon chip and flows out of the ring electrode, which can be located adjacent to or displaced from the microcooler. In the illustrated configuration, the ring electrode is located on the periphery of the chip. The metal lead, which is electrically isolated from the silicon chip with a very thin SiN<sub>x</sub> passivation layer (<0.3µm), is employed to deliver an electric current to the microcooler through the metal contact and silicon cap layer. A thermoelectric cooler uses an electric current to induce the Peltier effect, at the junction of two materials with different Seebeck coefficients, to provide localized cooling, and to transport the absorbed heat to the hot side of the thermoelectric circuit.

Figure 2.2: Schematic of the thermoelectric microcooler model

The figure 2.2 schematic of the silicon µTEC cooler shows that the electric current flowing through the indicated circuit results in Peltier cooling at the junction of the metal contact/silicon cap and again at the silicon cap/silicon chip interface, but causes Peltier heating at the silicon chip/ring electrode interface, where energetic electrons must shed some of their energy in entering the highly-conductive metal. In addition, the resistance to current flow leads to Joule heating in the elements of the thermoelectric circuit, most notably in the silicon chip.

The Peltier cooling rate at the metal contact/silicon cap interface can be expressed:

$$q_{TE,1} = (S_{metal} - S_{cap})T_1I \approx -S_{cap}T_1I$$

(2.1)

where  $S_{metal}$  and  $S_{cap}$  are the Seebeck coefficients of the metal contact and silicon cap layer, respectively, and  $T_1$  is the absolute temperature at the interface between the metal contact and the silicon cap layer. It is to be noted that by comparison to the high Seebeck coefficient of silicon materials under consideration, the Seebeck coefficient of the metal contact,  $S_{metal}$ , is negligibly low [26]. The Peltier cooling rate at the silicon cap/silicon chip interface is given by:

$$q_{TE,2} = (S_{cap} - S_{Si})T_2I$$

(2.2)

where  $S_{Si}$  is the Seebeck coefficient of the silicon chip, which varies with the doping concentration [35], and  $T_2$  is the absolute temperature at the interface between the silicon cap layer and silicon chip. Since the highly-doped silicon cap layer is very thin (<1 $\mu$ m) and the thermal conductivity is large (100~110W/mK at 373K), the temperature

difference between these two interfaces can be neglected, i.e.  $T_1 \approx T_2 = T_c$ . Thus, the overall Peltier cooling rate of the silicon TE microcooler can be expressed as:

$$q_{TE,c} = q_{TE,1} + q_{TE,2} = -S_{cap}T_1I + (S_{cap} - S_{Si})T_2I \approx -S_{Si}T_cI$$

(2.3)

where  $T_c$  is defined as the microcooler temperature. Therefore, in such a silicon thermoelectric microcooler configuration, to a very good first-approximation, the overall intrinsic Peltier cooling rate depends only on the Seebeck coefficient of the silicon chip, the microcooler temperature, and the applied current.

Similarly, the Peltier heating at the silicon chip/ring electrode interface of the present microcooler configuration can be expressed as:

$$q_{TE,h} = S_{Si}T_hI \tag{2.4}$$

where  $T_h$  is the absolute temperature on the ring electrode. However, due to the large surface area covered by the ring electrode/silicon chip interface, Peltier heating at the electrode can be expected to result in a minimal local temperature rise and a negligible effect on the hot spot temperature.

In order to facilitate the numerical modeling and thermal simulation of the IC package without the penalty of very large node counts and long computational runs, the detailed structures of the microcooler, including the silicon cap and the metal contact layer, were combined into a single ANSYS<sup>TM</sup> "surface entity" attached to the top of the silicon chip. This "surface entity" is capable of generating a cooling heat flux equal to the combined Peltier cooling effect at the metal contact/silicon cap interface and at the silicon cap/silicon chip interface, as in equation 2.3. Due in part to the 0.3µm thickness of

the silicon cap layer, volumetric Joule heating in the silicon cap layer was found to typically produce a heating flux two orders of magnitude lower than the cooling flux produced by the microcooler and was therefore neglected. The net Peltier cooling effect can then be expressed as an internal heat flux boundary condition on the surface of the microcooler:

$$q''_{TE.Si. cooler} = -S_{Si}TI/A_{cooler}$$

(2.5)

where  $A_{cooler}$  is the area of the microcooler. This approximation significantly simplifies the numerical computations.

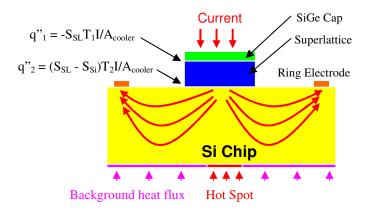

Next, we turn to the superlattice microcooler, with the understanding that at the limit of a zero thickness superlattice, the superlattice  $\mu$ TEC devolves back into the silicon thermoelectric microcooler. Figure 2.3 provides a 3-dimensional representation of a SiGe superlattice, including the distinct thickness of the alternating layers of the Si and Ge that constitute the superlattice. The corresponding boundary conditions for the superlattice microcooler are also shown in figure 2.3.

### Superlattice Microcooler

Figure 2.3: Thermoelectric Microcooler with Integrated SiGe Superlattice Layer

For the superlattice microcooler, equation 2.5 changes to:

$$q''_{TE,SL, cooler} = (S_{SL} - S_{Si})T_2I/A_{cooler}$$

(2.6)

where  $S_{SL}$  is the Seebeck coefficient of the superlattice and  $T_2$  is the absolute temperature at the superlattice/silicon chip interface. This change is made in order to recognize that the effective superlattice Seebeck coefficient falls between the metal lead and the silicon and that, consequently, Peltier cooling occurs on both sides of the superlattice structure. The Peltier cooling at the top of the superlattice is, thus, given by:

$$q''_{TE,SL} = -S_{SL}T_1I/A_{cooler}$$

(2.7)

where  $T_1$  is the temperature at the top of the superlattice. Conceptually, equations 2.6 and 2.7 can be summed to yield the effective cooling rate at the interface between the superlattice  $\mu$ TEC and the silicon chip.

#### 2.3 Modeling Methodology for On-chip Hot Spot Cooling

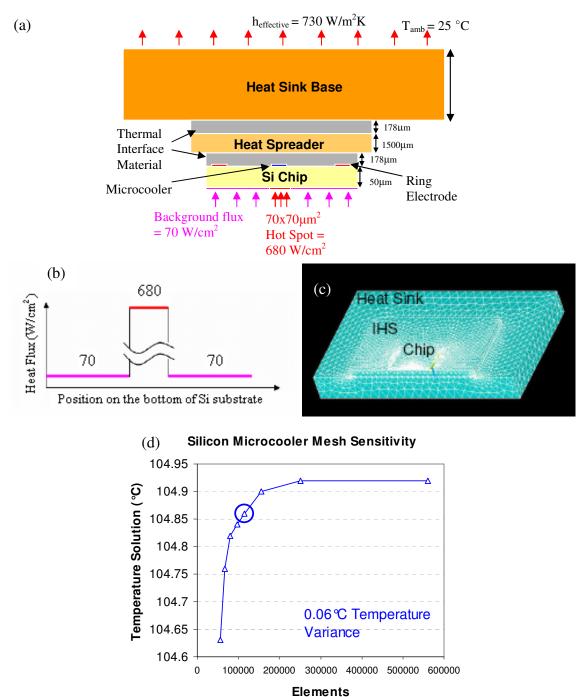

The commercial finite element software, ANSYS<sup>™</sup>, was used in this study to simulate the thermal and thermoelectric behaviors of the silicon and superlattice microcoolers, using a half-symmetry three dimensional (3-D) thermal-electrical model with a total element number of 100,000 - 200,000 for the entire package. Several "help volumes" were created inside the Si chip and around the microcooler to accurately model the high heat flux of the hot spot compared to the much lower surrounding heat flux. The average runtime for a typical simulation was approximately 15 minutes on a Dell Dimension 2400 computer with Intel Pentium 4 processor. Below, figure 2.4a represents the full model including the microcooler centered at the top of the silicon chip, the two

thermal interface layers, the integrated heat spreader, and the heat sink. The lateral dimensions of the chip, heat spreader, and heat sink are  $1.1 \text{cm} \times 1.3 \text{cm}$ ,  $3.1 \text{cm} \times 3.1 \text{cm}$ , and  $5 \text{cm} \times 5 \text{cm}$ , respectively.

Figure 2.4: Finite Element Model of Chip Cooled by  $\mu TEC$  (a) Entire chip package FE model, (b) Heat flux distribution on the bottom of the chip surface, (c) Image of the model meshing in ANSYS<sup>TM</sup>, (d) Mesh sensitivity for the silicon microcooler

ANSYS<sup>TM</sup>' thermal-electrical element - Solid 69 - automatically calculates the bulk Joule heating in each element and hence throughout the modeled space by solving the current continuity and heat conduction equations [26]. This feature allows both thermal and electric fields to be resolved through thermal-electrical coupling. As illustrated in figure 2.4a, a ground voltage of zero is applied as a boundary condition on the surface of the ring electrode. Electric current is then applied as a surface load onto the microcooler surface, for the non-superlattice case, and onto the top of the superlattice structure, for the superlattice case. In this way, Joule heating from the silicon chip could be simulated directly using the thermo-electrical mode of ANSYS<sup>TM</sup>. The elements are densely located for both cases around the microcooler and the hotspot where the largest temperature gradient is expected to occur. Mesh density in the silicon chip around the microcooler is also high in order to accurately calculate the thermal and electrical spreading effects and three dimensional distribution of Joule heating, as indicated in figure 2.4c. For purposes of the thermoelectric modeling study presented herein, the details of the solid-state circuitry in the active regions of the chip, including individual transistors, gates, capacitors, etc., are ignored and the heat generated from these components is represented as a 680W/cm<sup>2</sup> 70µmx70µm<sup>2</sup> hotspot surrounded by a background heat flux of 70W/cm<sup>2</sup> on the bottom surface of the silicon chip, as depicted in figure 2.4b. A ring electrode at a distance of 4mm from the center and a width of 0.3mm is also included. The mesh sensitivity for the silicon microcooler numerical model in figure 2.4d shows a very small temperature difference in a solution with increased element count.

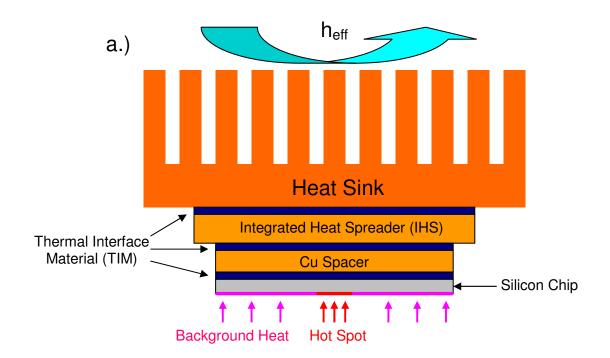

The major heat transfer path in the modeled space is assumed to be from the active region at the bottom of the silicon chip to the top side, then through the heat spreader to the heat sink by conduction, and from the heat sink to the ambient air by forced convection. Two layers of solder-like thermal interface material (TIM) - on either side of the heat spreader - are included in the model. The thermal contact resistances at these two interfaces are included in the effective thermal conductivity value of 30W/mK used for the 178µm TIM's [26]. To simplify the modeling geometry, the details of the heat sink fins are not included in this model and, instead, an equivalent convective heat transfer coefficient of 730 W/m²-K is applied as a boundary condition on the top surface of the heat sink base to achieve a commonly attained heat sink-to-ambient thermal resistance of about 0.55K/W [23]. Also, homogeneous material properties and uniform thicknesses are assumed for the silicon chip, thermal interface materials, heat spreader, and heat sink base. The geometric parameters and material properties for the packaging materials are listed in table 2.1.

Table 2.1: Geometry and Material Properties for µTEC-cooled Chip Package

|                             |                   | Thermal      | Electric    |

|-----------------------------|-------------------|--------------|-------------|

|                             |                   | Conductivity | Resistivity |

|                             | Dimension (L×W×H) | (W/mK)       | (Ωcm)       |

|                             | 11mmx13mmx (20 to |              |             |

| Silicon Chip                | 200µm)            | 110          | 0.00462     |

| TIM (1st layer)             | 11mmx13mmx178µm   | 30           | 100         |

| IHS                         | 31mmx31mmx1.5mm   | 150          | 100         |

| TIM (2 <sup>nd</sup> layer) | 31mmx31mmx178µm   | 30           | 100         |

| Heat sink base              | 50mmx50mmx5mm     | 360          | 100         |

While in this study the thickness of the superlattice ranges from  $1\mu m$  to  $20\mu m$ , its cross sectional area is always the same as the microcooler. Following Zhang et al [36], the superlattice has a thermal conductivity of 6.5 W/mK, an electric resistivity of 0.0016

$\Omega$ cm, and a Seebeck coefficient of 200μV/K. The thermoelectric material properties of the silicon chip, i.e. the Seebeck coefficient and the electrical resistivity, are determined largely by the doping concentration in the silicon. An optimum silicon doping concentration of  $2.5 \times 10^{19}$  cm<sup>-3</sup>, which yields the highest silicon power factor (S²/ $\rho$ =5.79 [27]) at the  $\mu$ TEC operating temperature of approximately 100°C, and assumed negligible electrical contact resistances in the  $\mu$ TECs structure were chosen to produce the most favorable temperature reduction results.

#### **2.3.1 FEM Model Validation**

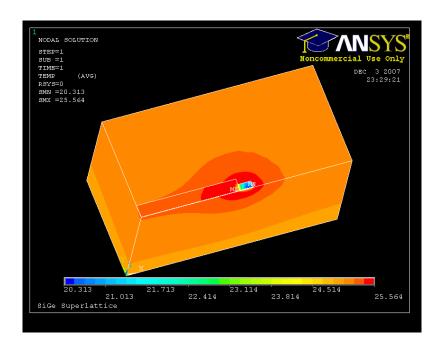

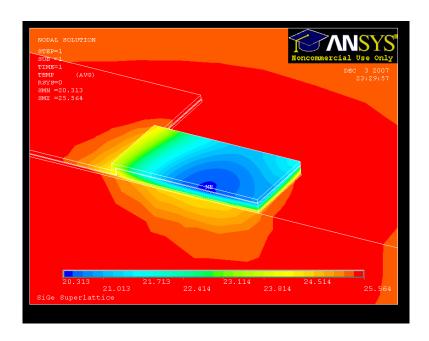

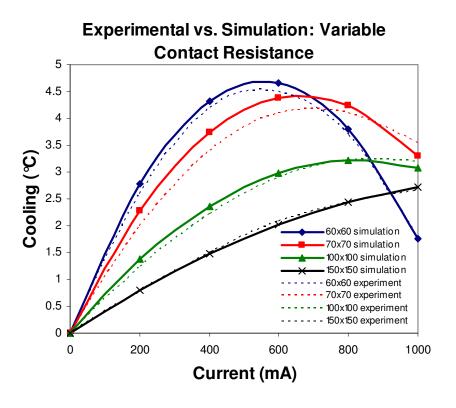

The present analysis of integrated SiGe superlattice microcoolers builds on a fabricated superlattice, with measured material properties as above, which was studied experimentally by Shakouri and co-workers. In this heterostructure thin film microcooler experiment, a 3μm thick superlattice, with contact areas of 60x60μm², 70x70μm², 100x100μm², and 150x150μm², respectively, was used to cool a 535μm thick silicon chip, as shown in the schematic representation in figure 2.5 [36]. The chip was placed on a temperature controlled heat sink at a fixed ambient 25°C. Standard E-type thermocouples were placed on top of the microcooler and at the chip, and an ILX Lightwave LDX3220 current source powered the microcooler through probes [36]. A maximum temperature reduction of 4.5°C was achieved with the 60x60μm² microcooler at the surface of the metal contact. These results are used to validate the Finite Element model and simulation approach developed in this study and to facilitate a detailed exploration of the parametric sensitivities of such μTEC devices.

An FEM ANSYS<sup>™</sup> model, geometrically matched to Zhang et al's [36] laboratory microcooler, was created. The boundary conditions and material properties used in the

simulation were based on information provided in [36]; including a Si chip Seebeck coefficient of  $325\mu V/K$  and a superlattice Seebeck coefficient of  $200\mu V/K$ . Figure 2.6 shows a sample numerical solution of the experimental superlattice microcooler.

Figure 2.5: Zhang *et al* "3D Electrothermal Simulation of Heterostructure Thin Film Micro-coolers" 2003 [36]

Figure 2.6: Temperature Distribution in Chip with Integrated Superlattice Microcooler [Chip=535 $\mu$ m Silicon; Superlattice = 3 $\mu$ m thick, 60x60 $\mu$ m<sup>2</sup>, 0.6A, and 7.11x10<sup>-7</sup>  $\Omega$ -cm<sup>2</sup> contact resistance; ambient temperature = 25°C]

In developing an ANSYS<sup>TM</sup> model for such a superlattice thermoelectric microcooler, attention must be devoted to the thermal contact resistance that occurs between the superlattice and the silicon chip, due to lattice mismatches and the somewhat imperfect adhesion of the two structures. In the absence of a direct empirical measurement of this contact resistance, a comparison between the results of the ANSYS<sup>TM</sup> simulation and the experimental data can be used to determine the value of the electrical contact resistance which provides the best agreement between the two. For best results the contact resistances were found to vary between  $7x10^{-7} \Omega$ –cm<sup>2</sup> and  $20x10^{-7} \Omega$ –cm<sup>2</sup> and to fall in the range of the values suggested by Zhang et al, which was  $6x10^{-7} \Omega$ –cm<sup>2</sup> [36].

Figure 2.7 displays the experimental and simulated temperature reductions achieved by the superlattice microcooler on the surface of the metal contact. The

parabolic variations in surface cooling with current reflect the interplay between the Peltier cooling effect, which increases linearly with the electrical current, and Joule heating, which increases with the square of the current, and yields an optimum current at which the best cooling is achieved. Since the actual temperature depends on the current flux, larger microcoolers require higher optimum currents, as shown. The predicted values in this figure reflect the use of the "best fit" contact resistance determined for each individual cooler size and seen to fall in the anticipated range. The resulting root-mean-square discrepancies between the empirical results and simulated values range between  $0.37^{\circ}\text{C} - 0.20^{\circ}\text{C}$ . The agreement in the functional form of the temperature variation and the actual cooling values between simulation and experimental results creates confidence in the modeling methodology and provides the foundation for more detailed parametric studies of SiGe superlattice microcoolers.

|                        | <b>Contact Resistance</b>                      | $\Delta T_{rms}$ |

|------------------------|------------------------------------------------|------------------|

| 60x60μm <sup>2</sup>   | $7.11 \times 10^{-7} \ \Omega \text{-cm}^2$    | 0.08822          |

| 70x70μm <sup>2</sup>   | $7.89 \times 10^{-7} \ \Omega \text{-cm}^2$    | 0.20122          |

| 100x100μm <sup>2</sup> | $18.13 \times 10^{-7} \Omega$ -cm <sup>2</sup> | 0.12428          |

| 150x150μm <sup>2</sup> | 19.81x10 <sup>-7</sup> Ω-cm <sup>2</sup>       | 0.03737          |

Figure 2.7: Surface Temperature Reductions with Superlattice Microcoolers

### 2.3.2 Model Simplifications

To reduce the complexity of the FE model and reduce the computational time, certain assumptions are made about the structure of the superlattice. Typically the superlattice is comprised of alternating layers of materials, taken in this study to be SiGe and Si, each on the order of 5-10nm thick, layered on top of one another for approximately 100 periods. The result is a superlattice structure with a thickness from 1μm to 20μm. In reality it is difficult to fabricate a 20μm thick superlattice. However, ANSYS<sup>TM</sup> can easily model the theoretical behavior of such a structure. In the model, it is assumed that the superlattice is one homogeneous layer with a set of "effective" material properties that reflect the overall Seebeck coefficient, thermal conductivity, and electric resistivity of the 3D structure. This assumption is made to facilitate the efficient simulation of the surface temperatures and effect of the μTEC on the hot spot temperature but does sacrifice the ability to determine the temperature of the individual layers within the superlattice.

Moreover, in the present study, focused on the comparative effectiveness of hot spot cooling by two configurations of thermoelectric microcoolers (with and without an integrated superlattice), it is assumed that all of the interfaces are perfect and lossless and that there is no electrical contact resistance between the microcooler and the silicon, or

elsewhere in the model. Simulations show that even with the addition of a readily achievable contact resistance of  $2x10^{-6}~\Omega cm$  at the top of a  $200x200\mu m^2$  microcooler with a  $10\mu m$  thick superlattice on a  $50\mu m$  Si chip, the maximum achieved cooling at the hot spot and microcooler interface is only reduced by about 0.1K and the relative temperature reductions for the various configurations remain unaffected.

#### 2.4 Results and Discussion

#### 2.4.1 Thermal Characteristics of a TE Microcooler

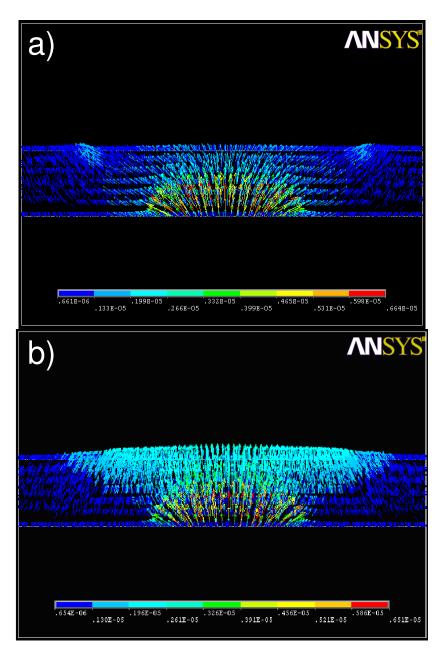

The FEM simulated thermal characteristics of thermoelectric microcoolers are displayed in figures 2.8 and 2.9, showing the heat flow pattern in the through-thickness direction in the vicinity of a 200x200µm² microcooler across from a 70x70µm² hot spot on the bottom of a 50µm thick chip. Figure 2.8a, showing the nearly hemispherical heat flux vector distribution for the uncooled situation is to be contrasted with figure 2.8b which displays the heat flux vectors when Peltier cooling is produced at the silicon chip surface by an electric current of 0.6A. The effectiveness of the silicon microcooler in altering the pure conduction heat flow pattern and attracting heat from the hot spot, as well as the peripheral areas, is clearly visible in figure 2.8b.

While this same general behavior is on display in figures 2.9a and 2.9b for the dormant/activated superlattice  $\mu$ TEC, in the uncooled chip the presence of the low thermal conductivity 10 $\mu$ m thick superlattice layer, with a thermal conductivity of 6.5W/mK, is seen to pose an impediment to heat flow normal to the chip surface, leading to a distinct enhancement of the in-plane heat flow away from the microcooler. Activation of the superlattice with a 0.6A current does draw the heat from the chip towards the superlattice microcooler but at somewhat reduced intensity, due again to the

low thermal conductivity superlattice layer. The resulting temperature distributions for the two activated microcoolers are shown, respectively, in figure 2.10, revealing similar patterns, but somewhat warmer hot spot temperatures for the superlattice configuration. The temperature profiles for the active  $\mu$ TECs follow a characteristic "W" pattern, as previously observed in the literature [28]. This pattern helps mediate the large temperature spike caused by the hot spot and helps achieve temperature uniformity along the bottom (active) surface of the chip.

Figure 2.11 shows the normal heat flux distributions along the top of a 50 µm Si chip, cooled by a silicon microcooler or a superlattice microcooler, both with no background heat flux imposed on the bottom of the chip (only an active 680W/cm<sup>2</sup> hot spot) and with an operating current of 0.6 Amps and 0 Amps, respectively. It is seen that for the uncooled chip, as well as in the presence of an operating microcooler, the superlattice integrated on the back of the chip provides somewhat lower heat removal capability (by approximately 5%), than achievable with the silicon microcooler. When operating at their optimum current, the  $\mu TECs$  dramatically increase the normal heat flux on top of the chip, particularly at the center of the chip where the peak heat flux increases by approximately 150W/cm<sup>2</sup> (for each respective cooler) over the flux when the μTECs are turned off, reaching approximately 250W/cm<sup>2</sup>. For comparison, the normal heat flux distributions along the top of the chip are also shown for a 20µm chip and a 100µm chip in figures 2.12 and 2.13, respectively. For the thinner 20µm chip, the peak normal heat flux at the center of the chip with the silicon microcooler (operating at 0.6A) reaches 400W/cm<sup>2</sup> some 60% of the hot spot heat flux. The peak normal heat flux for the same case with a 100µm chip is increased by approximately 180W/cm<sup>2</sup> to more than 210W/cm<sup>2</sup>, or by a factor of approximately 7, with an activated microcooler.

Figure 2.8: Heat flux distribution in silicon chip with hot spot  $[q"=680W/cm^2, L=70\mu m]$  (a) no TEC cooling and (b) with TEC cooling from a <u>silicon</u> microcooler operating at 0.6Amps.

Figure 2.9: Heat flux distribution in the silicon chip with hot spot [q"=680W/cm², L=70 $\mu$ m] (a) no TEC cooling and (b) with TEC cooling from a superlattice microcooler operating at 0.6Amps.

Figure 2.10: Temperature distribution along the bottom of a  $\mu$ TEC-cooled silicon chip die with hot spot [operating at 0.6Amps and 0Amps, respectively]

Figure 2.11: Normal heat flux profile along the top of a  $\mu$ TEC-cooled 50 $\mu$ m thick silicon chip [0.6 Amps and 0 Amps, 200x200 $\mu$ m<sup>2</sup> microcooler, 70x70 $\mu$ m<sup>2</sup> hot spot, 680 W/cm<sup>2</sup> heat flux at hot spot.]

#### Normal Heat Flux Distribution on Top of 20µm Chip w/ No Background Flux

Figure 2.12: Normal heat flux profile along the top of a  $\mu$ TEC-Cooled 20 $\mu$ m thick silicon chip [0.6 Amps and 0 Amps, 200x200 $\mu$ m<sup>2</sup> microcooler, 70x70 $\mu$ m<sup>2</sup> hot spot, 680 W/cm<sup>2</sup> heat flux at hot spot.]

Figure 2.13: Normal heat flux profile along the top of a  $\mu$ TEC-cooled 100 $\mu$ m thick silicon chip [0.6 Amps and 0 Amps, 200x200 $\mu$ m<sup>2</sup> microcooler, 70x70 $\mu$ m<sup>2</sup> hot spot, 680 W/cm<sup>2</sup> heat flux at hot spot.]

#### 2.4.2 Parametric Analysis

To gain a better understanding of the detailed behavior of a superlattice equipped microcooler, it is helpful to observe the effect of distinct variations in the geometric parameters and boundary condition, relative to a baseline design. The previously described baseline design involves a  $10\mu m$  thick superlattice, operating at 0.6 Amps, a  $50\mu m$  thick Si chip, a  $200x200\mu m^2$  microcooler, a  $70x70\mu m^2$  hot spot region, and a  $680W/cm^2$  hot spot heat flux, along with a  $70W/cm^2$  background heat flux on the bottom of the chip.

### 2.4.2.1 Superlattice Thickness

Figure 2.14 shows several key temperatures in the integrated superlattice microcooler chip, including the minimum hot spot temperature, the minimum superlattice temperature, and the temperature of the interface between the chip and the microcooler, respectively, as a function of the superlattice thickness in the range of 0μm to 20μm. It is important to note that the temperatures shown are achieved at different currents, each μTEC configuration requiring an optimum current to achieve its best performance, with current typically ranging from 0 to 1Amp. It should be noted that the zero-thickness superlattice microcooler – by definition – becomes the silicon μTEC.

As is clearly visible in figure 2.14, the lowest hot spot temperatures are achieved with vanishingly thin superlattice thicknesses, i.e. with the silicon thermoelectric microcooler. It is evident that as the superlattice thickness increases, the minimum hot spot and chip/microcooler interface temperatures rise almost linearly, by approximately 1K over the indicated thickness range, leading to progressively poorer cooling at the semiconductor hot spot. Alternatively, the surface temperature on the top of the superlattice – the furthest removed from the hot spot and separated from this heat source by the relatively low thermal conductivity "phonon trapping," alternating layers of SiGe – is seen to decrease by some 1.5K as the superlattice thickness increases to 20µm. Thus,

use of a thicker superlattice does significantly lower the temperature at the top of the superlattice surface, but not at the base surface where contact is made with the chip and, hence, not at the semiconductor hot spot.

# Minimum Temperature vs. Superlattice Thickness

Figure 2.14: Temperature variation in superlattice cooled silicon chip – varying superlattice thickness  $[200x200\mu m^2 \text{ cooler}, 50\mu m \text{ Si chip}, 70x70\mu m^2 \text{ hot spot, and } 680\text{W/cm}^2 \text{ hot spot heat flux}].$

#### 2.4.2.2 Si Chip Thickness

Variation in the hot spot temperature with chip thickness from 0 to 200µm, for the baseline 10µm superlattice configuration, is shown in figure 2.15. The thickness of the silicon (or chip) is seen to have a profound effect on the temperature of the hot spot, decreasing with chip thickness until a minimum temperature is reached and then rising as the chip thickness approaches zero. The minimum hotspot temperature, with both the silicon microcooler and the superlattice microcooler, respectively, is seen to occur at nearly the same chip thickness of 40-50µm. This provides an "optimal" ratio of