**ABSTRACT**

Title of Document: PARALLEL COMPUTATION OF

NONRIGID IMAGE REGISTRATION

Frances Kimpik Leung, Master of Science,

2010

Directed By: Professor Raj Shekhar,

Dept of Diagnostic Radiology (University of

Maryland, Baltimore) and Dept of Electrical

and Computer Engineering

Automatic intensity-based nonrigid image registration brings significant impact in

medical applications such as multimodality fusion of images, serial comparison

for monitoring disease progression or regression, and minimally invasive image-

guided interventions. However, due to memory and compute intensive nature of

the operations, intensity-based image registration has remained too slow to be

practical for clinical adoption, with its use limited primarily to as a pre-operative

too. Efficient registration methods can lead to new possibilities for development

of improved and interactive intraoperative tools and capabilities.

In this thesis, we propose an efficient parallel implementation for intensity-based

three-dimensional nonrigid image registration on a commodity graphics

processing unit. Optimization techniques are developed to accelerate the compute-

intensive mutual information computation. The study is performed on the

hierarchical volume subdivision-based algorithm, which is inherently faster than

other nonrigid registration algorithms and structurally well-suited for data-parallel

computation platforms. The proposed implementation achieves more than 50-fold runtime improvement over a standard implementation on a CPU. The execution time of nonrigid image registration is reduced from hours to minutes while retaining the same level of registration accuracy.

#### PARALLEL COMPUTATION OF NON-RIGID IMAGE REGISTRATION

By

Frances Kimpik Leung

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science 2010

Advisory Committee: Professor Raj Shekhar, Chair Professor Shuvra Bhattacharyya Professor Uzi Vishkin © Copyright by Frances K Leung 2010

## Acknowledgements

I would like to express my sincere utmost gratitude to Dr. Raj Shekhar for his guidance throughout this thesis. Without his supervision and direction, this thesis would not have been possible. I would also like to thank my thesis committee members, Dr. Shuvra Bhattacharryya and Dr. Uzi Vishkin, for their cooperation and support amidst their busy schedules.

I am also thankful to my colleagues at the Imaging Technologies Laboratory, in particular, Dr. William Plishker and Dr. Reza Rad. They have been providing valuable help and inputs at various times during my research. Many insightful discussions and feedback have sharpened this work on to completion.

Finally, I would like to thank my grandparents and parents for their support and encouragement. They have always been patient to me and challenged me in achieving higher goals in my career. I am also grateful to my siblings, Helen, Kimmy, Cece, and Kim, for their words of encouragement. I would like to especially mention my long time friends Jessica and Chanson for always been there with me. Many people have been part of my graduate education and I take this opportunity to thank them all.

# **Table of Contents**

| Acknowledgements                                              | ii    |

|---------------------------------------------------------------|-------|

| Table of Contents                                             | iii   |

| List of Tables                                                | iv    |

| List of Figures                                               |       |

| Chapter 1: Introduction and Motivation                        | 1     |

| Introduction                                                  |       |

| Contribution of this Thesis                                   | 3     |

| Outline of Thesis                                             | 4     |

| Chapter 2: Background on Image Registration                   | 5     |

| Image Registration                                            | 6     |

| Intensity-based Image Registration                            | 9     |

| Nonrigid Registration                                         | 12    |

| Mutual Information                                            | 15    |

| Hierarchical Volume Subdivision-based Nonrigid Registration   | 22    |

| Graphic Processing Unit                                       | 25    |

| Related Works                                                 | 35    |

| Chapter 3: MI-based Rigid Image Registration on GPU           | 41    |

| Introduction                                                  | 41    |

| Implementation                                                | 47    |

| Result and Discussion                                         |       |

| Chapter 4: Parallelization of Hierarchical Volume Subdivision | based |

| Registration                                                  | 62    |

| Introduction                                                  | 62    |

| Implementation                                                | 63    |

| Result and Discussion                                         | 66    |

| Chapter 5: Optimized GPU/MI-based Nonrigid Image              | 68    |

| Introduction                                                  | 68    |

| Implementation                                                | 68    |

| Result and Discussion                                         | 72    |

| Chapter 6: Conclusions                                        | 75    |

| Bibliography                                                  | 78    |

# **List of Tables**

| Table 2.1:  | GeForce GTX285 and GTX480 Hardware Specification 35                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2:  | Summary of Recently Reported GPU/MI-based Image Registration Rigid and Nonrigid Image Registration                           |

| Table 2.3:  | Hardware Specification                                                                                                       |

| Table 3.1:  | Thread Block Size vs Registration Runtime                                                                                    |

| Table 3.2:  | Thread Block Dimension vs Registration Runtime 50                                                                            |

| Table 3.3:  | Execution with and without 'sort and count' and average normalized result                                                    |

| Table 3.4:  | Sort and count experiment with different group size, and average normalized result                                           |

| Table 3.5:  | Registration Runtime with NN and PV interpolation, and average normalized result                                             |

| Table 3.6:  | Comparison of Registration Runtime with 'Sort and Count' and Register-level Sort Technique, and average normalized result 56 |

| Table 3.7:  | Number of Partial histograms vs. Runtime of Rigid Registration with NN-interpolation, and average normalized result 57       |

| Table 3.8:  | Number of Partial histograms vs. Runtime of Rigid Registration with PV-interpolation, and average normalized result 59       |

| Table 3.9:  | Rigid Registration Timing Result with CPU, FPGA, and GPU, and average normalized result                                      |

| Table 3.10: | Rigid Registration Accuracy Result with CPU, FPGA, and GPU                                                                   |

| Table 4.1:  | Nonrigid Registration Runtime with CPU and GPU 65                                                                            |

| Table 4.2: | GPU-based Nonrigid Registration Execution Time Speedup Compared to CPU Implementation                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| Table 4.3: | Nonrigid Registration Accuracy Result with CPU and GPU 66                                                                 |

| Table 5.1: | Subvolume Group Size vs Registration Runtime71                                                                            |

| Table 5.2: | Number of Partial Histograms vs Registration Runtime                                                                      |

| Table 5.3: | Optimal Nonrigid Image Registration Timing Result, and average normalized result                                          |

| Table 5.4: | Optimal Rigid and Nonrigid Image Registration Accuracy Result                                                             |

| Table 6.1: | Nonrigid Registration Timing Result of Case 1 with CPU, 3-FPGA, and GPU Implementations, and average normalized result 76 |

| Table 6.2: | Nonrigid Registration Accuracy Result with CPU, 3-FPGA, and GPU Implementations                                           |

# **List of Figures**

| Figure 2.1:  | Image Registration Flow Diagram                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------|

| Figure 2.2:  | Transformation of Reference Image Voxels to Floating Image 11                                                 |

| Figure 2.3:  | Joint Histogram of an MR image with itself with different degree of image alignment                           |

| Figure 2.4:  | Different Interpolation Schemes (NN, TRI, PV)                                                                 |

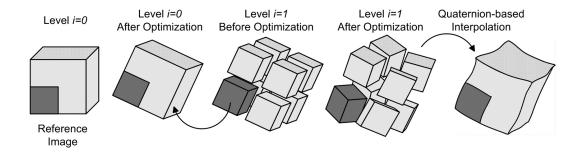

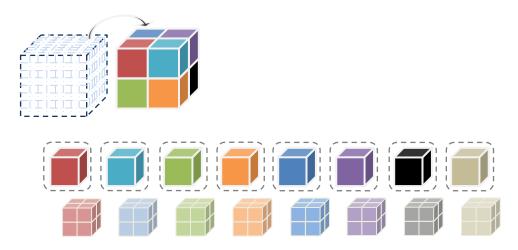

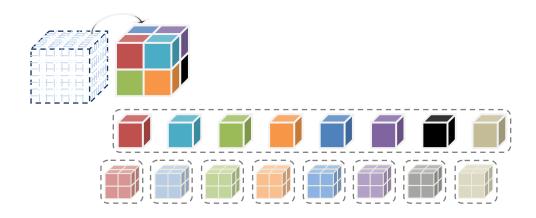

| Figure 2.5:  | Hierarchical volume subdivion based nonrigid registration 23                                                  |

| Figure 2.6   | The GPU Devotes More Transistors to Data Processing                                                           |

| Figure 2.7:  | Thread Hierarchy                                                                                              |

| Figure 2.8:  | CUDA Hardware Model                                                                                           |

| Figure 2.9:  | CUDA Programming Model                                                                                        |

| Figure 2.10: | CUDA Software and Hardware Architecture Relationship 31                                                       |

| Figure 2.11: | Fermi Streaming Multiprocessor                                                                                |

| Figure 3.1:  | Block distribution scheme for CPU cluster implementation with distributed partial mutual histograms           |

| Figure 3.2:  | Block assignment scheme for GPU implementation with distributed partial mutual histograms in shared memory 44 |

| Figure 3.3:  | Block assignment scheme for GPU implementation with partial mutual histograms in global memory                |

| Figure 3.4:  | Voxel-to-Thread based thread block assignment scheme 48                                                       |

| Figure 3.5:  | Voxel-to-Thread based blocks assignment scheme                                                                |

| Figure 3.6:  | Thread blocks Update Mutual Histogram in Global Memory 50                                                     |

| Figure 3.7:  | Thread blocks Update Mutual Histogram in Global Memory with Block-based Sort and Court                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------|

| Figure 3.8:  | Thread blocks Update Mutual Histogram in Global Memory with Sort Group                                                     |

| Figure 3.9:  | Sort and count experiment with different group size 54                                                                     |

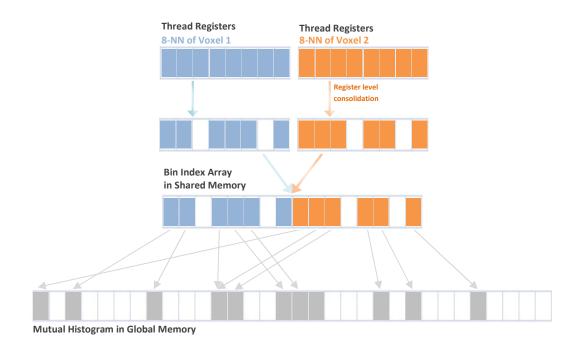

| Figure 3.10: | Update PV-Rigid Registration Mutual Histogram entries in Global Memory with Data Consolidation                             |

| Figure 3.11: | Update PV-Rigid Registration Mutual Histogram entries in Global Memory with Register-level Data Consolidation              |

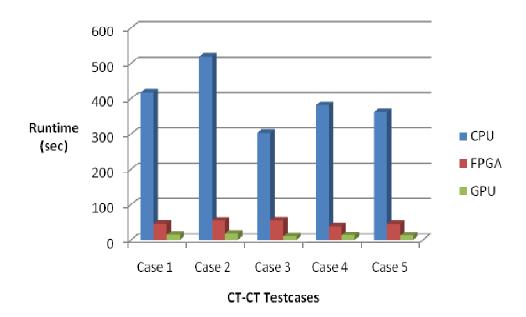

| Figure 3.12: | Rigid Registration Timing Result with CPU, FPGA, and GPU                                                                   |

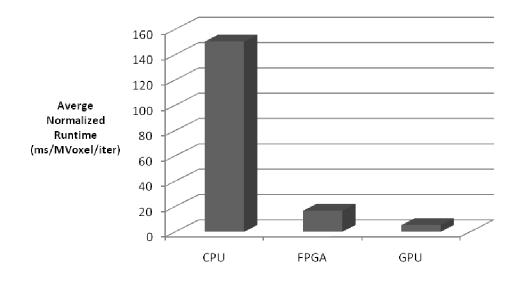

| Figure 3.13: | Average Normalized Rigid Registration Timing Result 60                                                                     |

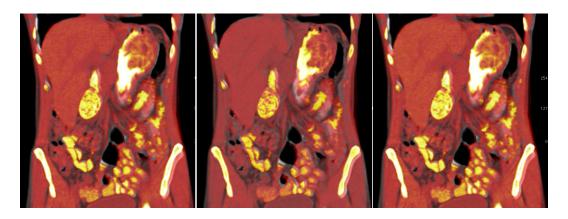

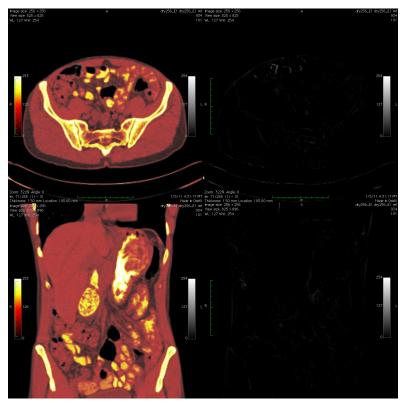

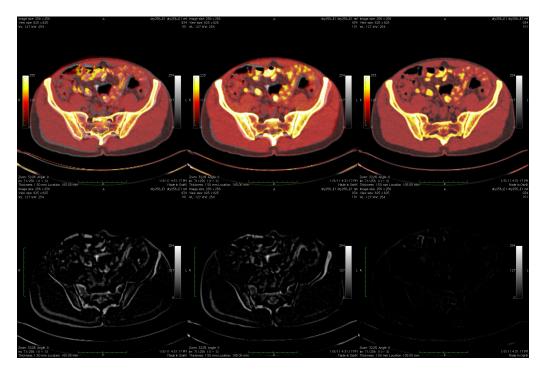

| Figure 3.14: | Case 1 Rigid Registration Result with Three Platforms: CPU, FPGA, and GPU                                                  |

| Figure 4.1:  | Hierarchical Volume Subdivision-based Nonrigid Registration 63                                                             |

| Figure 4.2:  | Pseudo code of Nonrigid Image Registration                                                                                 |

| Figure 5.1:  | Hierarchical Volume Subdivision-based Nonrigid Registration with the Subvolume Groups of 8                                 |

| Figure 5.2:  | Pseudo code of GPU-based Nonrigid Registration with the Concept of Subvolume Groups                                        |

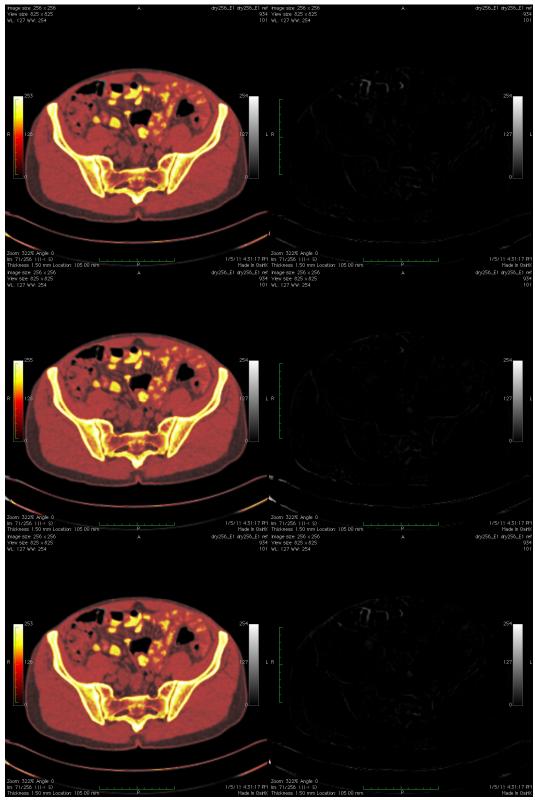

| Figure 5.3:  | Optimal Nonrigid Image Registration Result of Case 1 Fusion Image, and Different Image                                     |

| Figure 5.4:  | GPU-based Nonrigid Image Registration Result of Case 1 with No-Registration, Rigid Registration, and Nonrigid Registration |

| Figure 6.1 | Nonrigid Registration Result with CPU, 3-FPGA, and GPU |   |

|------------|--------------------------------------------------------|---|

|            | Implementations                                        | 7 |

## **Chapter 1: Introduction**

#### 1.1. Introduction and Motivation

Image registration, the process of spatially aligning two images, is an essential need in a number of medical procedures. Medical image registration has historically been used for multimodality fusion of images providing complementary information; comparison of images from different time points for qualifying disease progression or regression; and recently emerging to applications in fusion of pre- and intraoperative images in minimally invasive image-guided interventions (IGIs). These applications have the potential to improve the quality of patient care by improving the efficiency and effectiveness of the associated medical procedures.

The success of these novel medical capabilities is critically dependent on accurate and precise target identification and localization. Previous research has recognized intensity-based registration by maximizing mutual information (MI) between two images as the most accurate, robust, versatile and fully automatic approach to image registration. Meyer et al. [1] demonstrated the accuracy and clinical versatility of MI for automatic multimodality thoracic and abdominal image registration. Rueckert et al. [2] developed an MI-based nonrigid registration algorithm for deformation correction in three-dimensional (3D) magnetic resonance (MR) breast images. Hill et al. [3] applied nonrigid registration to pre- and post-resection interventional MR brain images to quantify intraoperative brain deformation.

Whereas these proven advantages have led to intensity-based registration becoming the approach of choice, the lengthy execution of MI computation continues to discourage clinical adoption. Fast automatic image registration will open new possibilities for development of interactive intraoperative tools.

#### **1.2.** Contribution of this Thesis

The goal of this thesis work is to present a multiprocessor implementation for nonrigid image registration applications by utilizing parallelism in MI computation. The hierarchical volume subdivision-based algorithm reported by Walimbe and Shekhar [4] is the focus in this work. The parallelizable nature of this registration algorithm would be exploited.

In this thesis, a complete implementation of the graphics processing unit (GPU)-based nonrigid image registration algorithm is presented. The implementation is scalable for the ever evolving generations of GPU or other massively parallel architectures in the future. A warp-aware sort and merge technique is presented to target the dominated runtime bottleneck in compiling the mutual histograms for MI computation.

The final implementation is validated with five sets of 256 x 256 x 256 computed tomography (CT)-CT test cases. A GPU with the latest NVIDIA hardware and software architecture is used to benchmark the resulting performance and accuracy. The overall performance of rigid and nonrigid registrations implementations is compared with a CPU and an FPGA-based implementation.

#### 1.3. Outline of this Thesis

The thesis is organized as follows: Chapter 2 provides the background on image registration and the associated techniques used within the registration framework. The concept of intensity-based image registration, specifically MI-based algorithm, are discussed. The latest GPU architecture and recently reported GPU-based image registration results follow next. In Chapter 3, a GPU-based rigid registration implementation is presented. Numbers of critical design considerations will be discussed in the content of rigid registration and further expanded while discussing nonrigid registration. In Chapter 4, a GPU-based nonrigid registration implementation is presented for the hierarchical volume subdivision-based image registration algorithm. Chapter 5 describes an optimized multiprocessor implementation in detail. Finally, in Chapter 6, conclusions and future work are presented.

## **Chapter 2: Background and Related Work**

Three-dimensional (3D) image registration is fundamental to various medical procedures, including image-based longitudinal comparison, multimodality image fusion, and population based atlas creation. It is a prerequisite when *before* and *after* images are to be compared (subtracted) in longitudinal comparison studies for quantifying disease progression or regression, often in response to a treatment. It is also a necessary first step in multimodality image fusion before images from one or more modalities with complementary information can be meaningfully overlaid. In these intra-patient instances, images are misregistered (misaligned) because they are usually acquired at two different times separated by hours to months with the patient in different body orientations. In the inter-patient instance of population-based atlas creation, images are misaligned also because they come from different individuals with different body types and thus necessitate image registration.

One of the growing applications of image registration that requires real-time performance is image-guided interventions (IGIs). The success of IGIs is critically dependent on accurate and precise target identification. Diagnostic-quality pre-treatment images are often used for treatment and navigation planning, while intra-treatment images available to provide accurate spatial information to navigate interventional devices are generally lower-resolution and less information-rich. Rapidly merging these two types of images with complementary strengths (clear target definition and up-to-date patient anatomy) can help clearly

visualize targets during an IGI, provide real-time quantitative feedback on organ motion and deformation, and permit real-time treatment monitoring. Achieving high-speed image registration is a fundamental need in not only interventional applications but virtually all applications.

Decades of research has led to significant success in developing accurate, reliable and fully automated image registration algorithms and techniques. The most recognized technique among these is intensity-based registration by maximizing MI (also referred to as MI-based image registration) between the two images to be registered [5-12]. However, due to the large size of 3D images and the computation intensive nature of this search-based technique, intensity-based image registration has remained too slow to be practical for clinical adoption. The slow execution has also prevented large-scale validation studies and clinical trials evaluating the quality and benefits of image registration.

#### Image Registration

Image registration is the iterative process of spatially aligning two or more images taken at different times, from different modality, or from different viewing angles. Maintz and Viergever [13] and Hill etal. [14] have presented a detailed summary of the medical image registration domain. Generally medical image registration can be classified into two main categories; extrinsic registration and intrinsic registration. Extrinsic methods based on other foreign objects that are not natively

a part of the imaged space; whereas intrinsic registration is based purely on the image information from the patients.

Extrinsic methods rely on artificial objects which may be attached to the patient or placed within the field of view of the image. These objects are specially designed to be well visible and accurately detectable in all pertinent modalities. The registration of the acquired images involves simply determining the corresponding translation between the external objects, which can be computed explicitly without the need for complex optimization algorithm. Therefore, this type of registration is comparatively easy, fast, and possible to be automated. However, extrinsic methods generally require advanced planning; provisions must be made at the time of preprocedural imaging. The marker objects are often invasive to the patients, while non-invasive marker options are generally less accurate. As extrinsic methods do not include patient-related image information, the nature of the registration transformation is mostly restricted to rigid transformation model only.

Intrinsic methods, on the contrary, rely on patient-generated image content only. Registration may be based on a limited set of identified salient points (landmarks), the alignment of segmented binary anatomical structures (segmentation based), or directly based on the image intensity values (voxel property based).

Landmark-based registration uses predefined salient points (landmarks) from the different images and determines the spatial transformation of the images with these paired points. Landmarks can be anatomical; accurately locatable points of the visible anatomy, which are usually identified interactively by the users. Landmark-based methods are often used to find rigid or affine transformations. Given a large enough set of points, they can also be used for more complex nonrigid transformation. The optimization procedure of landmark-based registration is relatively fast as the set of identified points is sparse compared with the original image content. However, this approach cannot be fully automated as user interaction is usually required for the identification of the landmarks.

Segmentation-based image registration methods aligns images based on the same anatomical structures (mostly surfaces and curves) extracted from the images to be registered. The alignment between the structures can be either rigid model based or deformable model based. The rigid model based approaches are the most popular methods in clinical use due to the success of the 'head-hat' method introduced for multimodal images. The nonrigid model based approaches elastically deforms the extracted structure from an image to fit the second image. Segmentation-based techniques are computationally efficient and they support multi-modal registration. However, the accuracy of registration highly depends on the segmentation accuracy. These methods cannot be fully automated as the segmentation step is often performed semi-automatically.

Voxel property-based methods operate directly on the image grey value without prior data reduction by the user or segmentation. The image grey value content is either reduced to a representative set of scalars and orientations, or the full image content is used. Theoretically, voxel property-based methods using the full image content are the most flexible methods which become the most interesting methods of current research. Voxel property based methods can be fully automatic, they also support multi-modal registration and are proven to be accurate. However, these methods are still limited from 3D clinical applications by the considerable computational costs. This thesis work will address this aspect through the use of the latest graphic processor units.

#### Intensity-Based Image Registration

Intensity based image registration is an automatic approach to spatially align two images based on their voxel grey levels. This method consists of numbers of optimization iterations with the aim to find the transformation parameters  $T_{opt}$  which optimally aligns the reference image (RI), with the floating image (FI) by maximizing the similarity measure. The following equation summaries this process, where S is the similarity function to be maximized, T is the transformation operator applied to the reference image coordinates.

$$T_{opt} = argmax S(RI(x,y,z), FI(T(x,y,z)))$$

Eq. 2.1

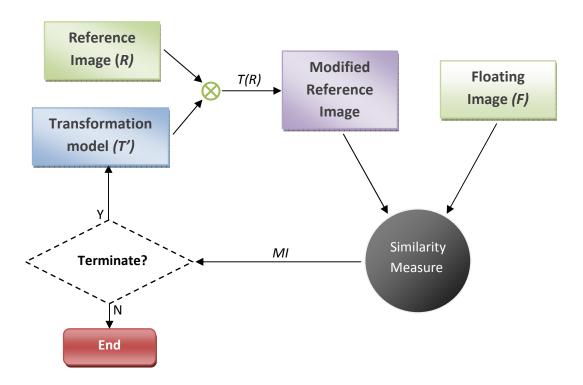

Registration starts with an initial transformation T, which can be rigid model or nonrigid model, and maps the reference image voxels into the floating image space. The similarity measure S quantitatively determines the degree of misalignment between the images based on the voxel intensities (without considering any abstracted representation of the images). The optimization algorithm then updates the parameters of the transformation T based on the similarity measure result. This iterative process allows the optimization algorithm to search for the best transformation parameters that achieve the most optimal align between the two images. The major components of the image registration operation are depicted in Figure 2.1. Each component will be discussed in detail in the following sections.

Figure 2.1: Image Registration Flow Diagram

#### Transformation Model

$$T: (x,y,z) \to (x',y',z')$$

Eq. 2.2

Transformation model describes the spatial relationship between the reference and the floating images. These models are categorized according to their degrees of freedom. Rigid transformation includes only translations and rotations. Affine transformation advances rigid models by also including scaling and shearing. Perspective transformation is similar to affine transformation; however, the parallelism of lines need not be preserved [15].

Figure 2.2: Transformation of Reference Image Voxels to Floating Image

#### Rigid Models

Translations and rotations suffice to register images of rigid objects, for example, bone or brain. For 3D image registration, rigid models can be described using a single constant 4x4 transformation matrix ( $Eq\ 2.3,\ 2.4$ ). Where t is an arbitrary translation vector and r is a 3x3 rotation matrix.

$$y = T_{rigid} x Eq. 2.3$$

$$\begin{bmatrix} y_1 \\ y_2 \\ y_3 \\ 1 \end{bmatrix} = \begin{bmatrix} r_{xx} & r_{xy} & r_{xz} & t_x \\ r_{yx} & r_{yy} & r_{yz} & t_y \\ r_{zx} & r_{zy} & r_{zz} & t_z \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ 1 \end{bmatrix}$$

Eq. 2.4

As rigid registration has reported numbers of successes [12], the limited degrees of freedom is not sufficient for applications where nonrigid transformations are required, such as modeling soft tissue movement and deformation.

#### Nonrigid (Deformable) Models

While rigid registration limiting the deformation to rotations and translations, nonrigid transformation models offers higher degrees of freedom to represent the misalignment between images. This provides the mean to model local deformations of the images which results high accuracy in registration result. One of the applications is intrasubject registration, when nonrigid transformations are required to accommodate any tissue deformation due to interventions or changes over time.

One of the well recognized nonrigid transformation models is Free Form Deformation (FFD) [2, 16]. FFD deforms an object by manipulating an underlying mesh of control points. The resulting deformation controls the shape of the 3D object and produces a smooth and continuous transformation. The set of control points controls the degree of nonrigid deformation which can be advanced by the resolution of the mesh of control points. A large spacing of control points

allows modeling of global nonrigid deformations, while a small spacing of control points allows modeling of highly local nonrigid deformations. However, this modeling approach suffers from high computational complexity. The resolution of control point mesh not only controls the finest of the local deformation field, but also defines the number of degrees of freedom, consequently, the computational complexity. For the case of 5x5x5 mesh of control points, the FFD model yields 375 degrees of freedom.

Another class of nonrigid registration algorithms is based on the concept of hierarchical image subdivision. These algorithms divide the image into numbers of sub-images (subvolumes) and perform local rigid (linear) transformation on individual subvolumes. Interpolation technique is applied to the result of individual transformed subvolumes to obtain the final smooth deformation field. Finer the resolution of the subvolumes, finer the local deformable registration can be achieved. These algorithms are computationally efficient and inherently suited well in the parallel computing framework as each subvolume can be processed independently from other subvolumes of the same hierarchical level. In this thesis, we have considered one of the hierarchical volume subdivision deformable registration algorithms proposed by Walimbe and Shekhar [4]. The details of this algorithm will be discussed in the later session.

#### Similarity Measure

Automatic registration requires a metric for measuring the degrees of similarity between the images to be registered at each iteration of the optimization process. The metric is used to guide the optimization engine to approach the optimal alignment. Ideally, the similarity measure attains its maximum (or minimum) when the images are perfectly aligned and deviates as the images are less overlaid. Similarity measure for intensity-based registration is computed directly from the voxel intensity values of the images rather than from geometrical structures. Some of the commonly used metrics are sum of squared difference (SSD), normalized cross correlation (NCC), correlation ratio (CR), and mutual information (MI) [17, 18]. One of the decision factors on selecting the proper similarity measure is the use of image modality; whether the images are taken with the same or different type of imaging modalities.

For intramodality images, registration is to compare the images of a subject taken at different time with the same modality. If there is no change in the subject, or the images are properly aligned, the difference image, subtraction of the reference image and the transformed image, will result no structural difference except for noise. The amount of residue in the difference image corresponds to the amount of registration error. The iterative optimization process will calculate the optimal transformation T to minimize the residue in the difference image. The computation of similarity measure techniques for intramodality images is more straightforward and highly parallelizable.

For intermodality registration, there is no simple relationship between the intensities of the two images to be registered. The registration error cannot be quantified simply by deriving a difference image. Mutual information (MI) based approach introduced by Collignon et al. and Wells, et al. provides a sufficient similarity metric applicable for both intramodality and intermodality registration.

#### Mutual Information

Mutual information (MI) is a basic concept from information theory based on the concept of entropy. MI measures the statistical dependency between two random variables or the amount of information that one variable contains about the other. In the case of intensity-based image registration, the MI of the intensity of the voxel pairs is maximal when the two images are properly aligned.

Entropy is a measure of information of message developed from communication theory. This concept can be interpreted as a measure of the amount of information an event gives, the uncertainty about the outcome of an event, and the dispersion of the probabilities. Shannon introduced an entropy measure in 1948 [19], which weights the information per outcome by the probability of that outcome. Given events  $e_1$ , ...,  $e_m$  occurring with probabilities  $p_1$ , ...,  $p_m$ , the Shannon entropy is defined as

$$H = -\sum p(x) \cdot \ln(p(x))$$

Eq. 2.5

When the concept of entropy applied to images, the distribution of the grey values of the image is concerned. The probability distribution of the grey values is the number of occurring of each grey value in the image divided by the total number of occurrences. An image with small variance in grey values has a low entropy value; it contains very little information. Whereas an image contains a lot of information, with even distribution of different grey values, the entropy value will be high. Entropy also describes the dispersion of a probability distribution. The entropy value is low when the distribution has a few dominant peaks and it is maximal when all outcomes have an equal chance of occurring.

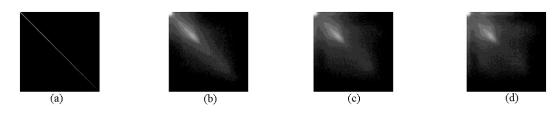

Image registration adopts this concept as similar measure criterion by measuring the information of the joint probability distribution of the images to be registered. Woods et al. [20-21] first introduced the idea of using the grey values ratio for similarity measure back in the early 1990s. Hill et al. [22] later adapted Woods' measure and proposed the technique of constructing a feature space which is a two-dimensional plot showing the combination of grey values in each of the two images for all corresponding points. As the alignment of the two images changes, the feature space (joint histogram) also changes. When the images are optimally registered, the joint histogram will show certain clusters of grey values. As the degree of misregistration increases, the joint histogram shows increasing dispersion. Figure 2.3 shows an example of a joint histogram of an MR image registered with itself. When the images are perfectly registered, the distribution of the joint histogram forms on the diagonal as the images are identical (Figure 2.3a).

When one of the images rotates, the resulting histogram starts to disperse (Figure 2.3b). As the degree of rotation increases, the amount of dispersion of the joint distribution increases (Figure 2.3c-d).

Figure 2.3: Joint Histogram of an MR image with itself with different degree of image alignment. [12]

Collignon etal. [23] and Studholme et al. [24] suggested using entropy in image registration by measuring the dispersion of the joint probability distribution. When the joint distribution has a few dominant peaks (better registered), the entropy value is low. As the images deviate away from the proper alignment, the entropy of the joint distribution increases. The Shannon entropy definition is derived as Eq. 2.6 for a joint distribution. Proper registration of images is achieved by obtaining the transformation which minimizes their joint entropy.

$$H = -\sum \sum p_{RI,FI}(x,y) \cdot \ln(p_{RI,FI}(x,y)).$$

Eq. 2.6

Shortly after the knowledge of using joint entropy in image registration was proposed, Collignon et al. [25,26] and Viola and Wells [27-29] introduced the use of mutual information for image registration.

The definition of MI is frequently presented in the following forms, where H(.) denotes as entropy (Shannon's entropy).

$$MI(RI,FI) = H(RI) - H(RI|FI),$$

Eq. 2.7

$$MI(RI,FI) = H(FI) - H(FI|RI),$$

Eq. 2.8

$$MI(RI,FI) = H(RI) + H(FI) - H(RI,FI),$$

Eq. 2.9

where the individual and mutual entropies are calculated as:

$$H(RI) = -\sum p_{RI}(x) \cdot \ln(p_{RI}(x)), \qquad Eq. 2.10$$

$$H(FI) = -\sum p_{FI}(x) \cdot \ln(p_{FI}(x)),$$

Eq. 2.11

$$H(RI, FI) = -\sum \sum p_{RI, FI}(x, y) \cdot \ln(p_{RI, FI}(x, y)).$$

Eq. 2.12

In this thesis, the third definition of MI (Eq. 2.9) is chosen as this definition is most closely related to joint entropy and most applicable for image registration application. This form of representation consists of the term H(RI,FI), which means that maximizing mutual information is related to minimizing joint entropy. As recalled in our earlier discussion, the joint histogram of two images' grey values disperses when they are misaligned which result increases of entropy and decreases of MI.

To further improve the stability of the measure criterion, Studholme et al. [30] proposed a normalized measure of mutual information. The size of overlapping part of the images influences the mutual information measures in two ways. As the area of overlap decreases and the number of samples decreases, the statistical power of the probability distribution estimation is reduced. Also, Studholme et al. [9, 30] have shown that the mutual information measure might increase with

increasing misregistration. This occurs when the relative areas of object and background even out and the sum of the marginal entropies increases, faster than the joint entropy. Normalized mutual information (NMI) has addressed these issues as it is less sensitive to change in overlap.

$$NMI(RI, FI) = \frac{H(RI) + H(FI)}{H(RI, FI)}$$

Eq. 2.13

Mutual information similarity measure enables full automatic registration on a large variety of applications as prior segmentation (manual marker identification) is not required. It advances other similarity measure particularly in intermodality registration, as no assumption is made regarding the nature of relation between the image intensities in both modalities. Holden et al. [31] have demonstrated that mutual information-based techniques are, in general, superior to other techniques for deformable image registration. A comprehensive survey of MI-based registration was presented by Pluim et al. [12].

#### Interpolation

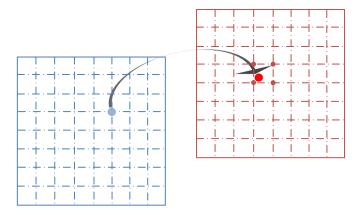

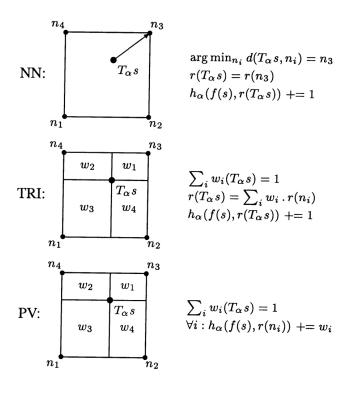

The joint image intensity histogram of the image volume is constructed by binning the image intensity pairs (RI(x,y,z), FI(T(x,y,z))) for all overlapping voxels. In general, T(x,y,z) will not coincide with a grid point (integer coordinate), interpolation techniques would be needed to obtain the corresponding image intensity value. Nearest neighbor (NN), trilinear (TRI), and partial volume (PV)

interpolation schemes have been traditionally used for this purpose. Figure 2.4 shows the differences of these three schemes.

Figure 2.4: Different Interpolation Schemes (NN, TRI, PV) [8]

Nearest neighbor interpolation is the most straightforward approach, but it is insufficient to guarantee subvoxel accuracy. Trilinear interpolation may introduce new intensity values which are originally not present in the floating image. This effect would lead to unpredictable changes in the marginal distribution of the floating image. Partial Volume interpolation, proposed by Collignon [17], was specifically designed for creating joint histograms. Instead of computing a weighted intensity value and updating a single histogram entry, it uses the same weights of trilinear interpolation for fractional updates of the histogram entries corresponding to the neighbors of a transformed point. The contribution of the

image intensity R(x,y,z) to the joint histogram is distributed over the intensity values of all eight nearest neighbors (for 3D case) of T(x,y,z) on the grid of the floating image. PV interpolation creates smoother changes of the joint histogram for varying transformations and hence a smoother registration function. This scheme has been reported to produce the least interpolation error for MI-based registration [8, 32].

Consequently, PV interpolation scheme increases the number of memory accesses of the MH accumulation operation by approximately eight times, and floating point implementation is required to represent the fractional updates of the histogram entries. These differences of the interpolation schemes have direct impact on the performance, therefore, special techniques would be considered to ease the burden in memory bandwidth and compute resources.

#### Optimization Algorithm

Optimization algorithms are used to navigate the search space of transformation parameters. They identify the optimal combination of transformation parameters that best aligns a pair of images. In the case of multimodality intensity-based image registration, the voxel similarity function of the mutual information is the objective function to be optimized. The algorithm chosen in our implementation is the downhill simplex method.

The downhill simplex method is a multidimensional nonlinear optimization technique first introduced by Nelder and Mead [33]. This method uses the concept of a simplex, which is a special polytope of *N*+1 vertices in an *N*-dimensional space. The simplex method places an initial simplex in the solution space and takes a series of steps to move the vertices towards the local optimum. Shekhar et al. [34, 35] and Walimbe et al. [4, 36] have reported successful use of this optimization technique for voxel similarity–based image registration.

#### Hierarchical Volume Subdivision Based Algorithm

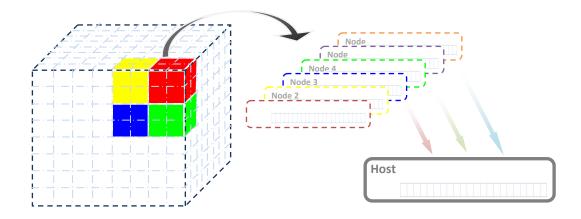

Hierarchical volume subdivision based nonrigid image registration algorithms are inherently faster compared to most of the intensity based nonrigid registration algorithms. The framework of these algorithms is well adaptable to the architecture of parallel computing, which significantly advances the performance in computation. This class of nonrigid registration algorithms involves modeling the elastic transformation between images as an interpolation of multiple local rigid-body registrations [37]. One or both of the images to be registered are divided into subimages (subvolumes) which will be registered independently. The final non-linear transformation field is generated from the independent registration solutions from the subimages using various interpolation techniques.

Most of the earlier proposed volume subdivision based algorithms allows only translation-based model for the subvolumes due to the complexity in direct interpolation of 3D rotation. With only three degrees of freedom locally, very

small subvolumes are needed in order to recover extremely complex misalignment. However, similarity measures like MI lack the statistical power for robust registration as the subvolume size decreases. Walimbe and Shekhar [4] suggested to enhance this model by using the six-parameter rigid body transformation model throughout for registration of individual subvolumes and incorporating a quaternion-based scheme for direct interpolation of the resulting rigid body transformations for generation of the deformation field.

In the case of 3D image registration between two images, the references image (RI) and the floating image (FI), this hierarchical subdivision based algorithm first recovers the global mismatch between the two images, followed by a series of refinement of the local matching. The reference image is divided by performing hierarchical octree-based subdivision. The subvolumes at each hierarchical level are registered to the undivided floating image. Localized misalignments are captured by using the six-parameter translation and rotation transformation models at the global (traditional rigid registration) as well as the local levels. The concept of the hierarchical registration scheme is presented in Figure 2.5.

Figure 2.5: Hierarchical volume subdivion based nonrigid registration

Volume subdivision and subvolume registration steps continue until the voxel count of an individual subvolume reaches the predefined limit. The final deformation field obtained by quaternion-based interpolation of the individual subvolume transformations at the final hierarchical level is used to deform the floating image to match the reference image.

#### Technique in Calculating MI for Subvolumes

As the voxel count of an individual subvolume decreases, the accumulated mutual histogram for similarity measure becomes sparse, thus resulting unreliable mutual information for robust registration. A concept of MH<sub>rest</sub> (MH-rest) is introduced to resolve this issue by taking information from all image voxels into the local registration problem of a given subvolume. The mutual histogram is compiled not only with the voxels of the given subvolume, but with the sum of two mutual histograms; MH<sub>subvlume</sub> and MH<sub>rest</sub>. MH<sub>subvlume</sub> is compiled with the voxels of the subvolume being registered, and MH<sub>rest</sub> is calculated with all the remaining voxels of the image based on the transformations obtained from the preceding hierarchical level. For a given subvolume registration, MH<sub>subvlume</sub> will be evolved as a function of the subvolume transformation model while MH<sub>rest</sub> remains constant during the iterative optimization process as it is independent from the current hierarchical level. The resulting MI from the combined MH is computed over the entire image with local variations corresponding to the subvolume under optimization. This approach increases the statistical power of the calculated MI and provides additional guidance to the registration process. Eq. 2.14 summarizes this process. The contribution of current subvolume p at level i to the MH is computed based on the candidate transformation  $T_p^i$ . The contribution from the rest of the subvolumes to the MH remains constant during the optimization process.

$$MH^{i}_{Total_{p}} = MH^{i}_{Subvolume_{p}} + MH^{i}_{Rest_{p}}$$

Eq. 2.14

$$MH^{i}_{Subvolume_{p}} = Accumulate(T_{p}^{i})$$

Eq. 2.15

$$MH^{i}_{\operatorname{Re} st_{p}} = Accumulate\left(T_{-p}^{i-1}\right)$$

Eq. 2.16

#### *Graphic Processing Unit (GPU)*

A graphics processing unit (GPU) is best known for its compute-intensive and high parallel computation capability for computer graphics applications. Fueled by the desire for real time, high-definition 3D graphics, GPUs have evolved into a multithreaded, multicore highly parallel, processor with tremendous computational power and very high memory bandwidth [38]. With the latest improvement in floating-point performance and increases in programmability flexibility, GPUs have also become the processor of choice for accelerating many non-graphics data parallel applications; especially favorable for numerically intensive scientific applications. Nieuwpoort and Romein introduce GPUs to radio astronomy signals correlation applications [39]. Levine et al [40] expand the GPU compute capacity to modular dynamic simulation acceleration applications and attain twenty times performance improvement compared to the use of single CPU. In this thesis, we focus on the GPUs developed by NVDIA and build our knowledge of CPU-based image registration algorithm on the latest NVDIA GPU architecture.

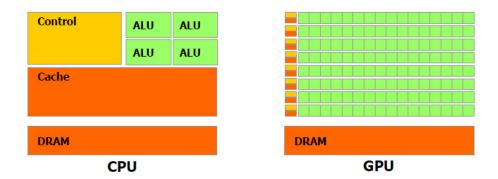

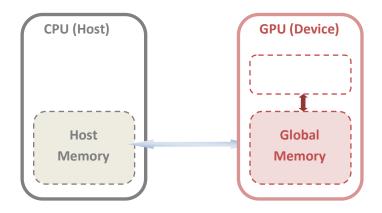

GPU outperforms CPU in compute capability by devoting more transistors to its arithmetic logic units (ALUs) for data processing at the expense of reduced data caching and flow control (Figure 2.6). This makes the GPU architecture especially well suited for addressing problems that can be expressed as data-parallel programming model. The high arithmetic intensity in data-parallel computations can effectively hide the memory access latency even though the capacity of data caching is comparatively less sufficient in GPU architecture.

Figure 2.6: The GPU Devotes More Transistors to Data Processing [38]

#### CUDA Overview

Compute Unified Device Architecture (CUDA) is a general-purpose parallel computing hardware and software architecture developed by NVIDIA. This architecture introduces a new parallel programming model and instruction set architecture, which leverages the parallel compute engine to solve many complex computation problems in a more efficient way on a GPU than on a CPU. CUDA

programming model introduces abstractions, such as a hierarchy of thread groups, shared memories, and barrier synchronization, to cover fine-grained parallelism (thread parallelism) to coarse-grained parallelism (task parallelism). These abstractions guide programmers to partition their problems into coarse subproblems. Each sub-problem can be solved in parallel by groups of threads (thread blocks). Each block of threads can be scheduled on any of the available processor cores with no specific constraint on execution sequence. Multiple subproblems can be computed in series or in parallel depending on the version of the GPU architecture. A CUDA program therefore can be seemingly executed on any number of processor cores. This allows applications to transparently scale their parallelism to leverage the increasing number of processor cores.

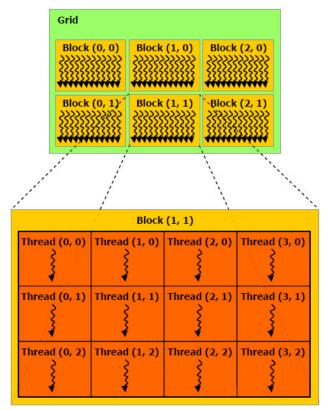

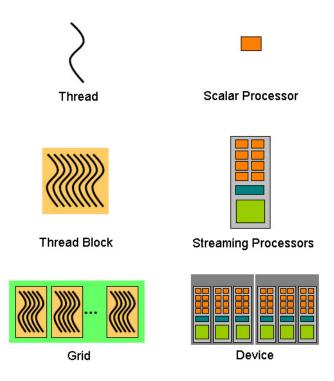

CUDA abstracts the parallel programs to be run on the GPU as kernels. A kernel executes in parallel across a set of parallel threads which are organized in a grid of user-defined 1D/2D array of thread blocks. A thread block consists of a set of concurrently executing threads which can cooperate among themselves through per-block shared memory space and barrier synchronization. A grid of thread blocks shares results in the global memory space. Figure 2.7 shows the structure of the thread hierarchy.

Figure 2.7: Thread Hierarchy [38]

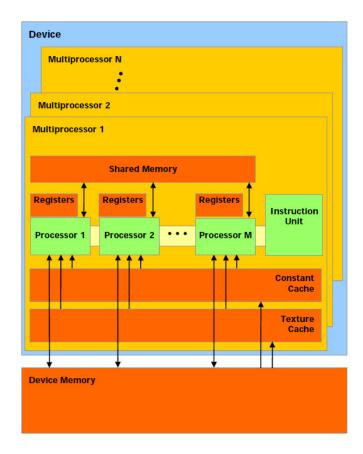

The CUDA hardware architecture is built around a scalable array of multithreaded Streaming Multiprocessors (SMs). Each SM consists of 8 to 32 Scalar Processors (SPs), 2 to 4 special function units (SPU) for transcendental instructions, an instruction unit and on-chip shared memory. Each CUDA processor has a fully pipelined integer arithmetic logic unit (ALU) and floating point unit (FPU). The total number of scalar processors and on-chip shared memory varies among generations of GPU architectures. Figure 2.8 illustrates the hardware model of the multiprocessor.

Figure 2.8: CUDA Hardware Model [38]

# Programming Model

A typical CUDA implementation consists of the following steps (Figure 2.9). First, memory is allocated on the GPU (device). The CPU (host) then transfers the data from the host to the device and initialized the device memory if required. Next, the host determines the execution configure, i.e. the number of thread blocks and block size, and invokes the kernels. The device executes the kernels and stores the result in the device memory. When the computation is completed, the resulting data is transferred from the device to the host.

Figure 2.9: CUDA Programming Model

When a CUDA program on the host CPU invokes one or more kernel grids, the thread blocks of the kernel grids are distributed to the available streaming multiprocessors with sufficient memory resources. The threads of a thread block execute concurrently on scalar processors of a single steaming multiprocessor, and multiple thread blocks can execute on one multiprocessor if resource is available. Figure 2.10 shows the relationship between threads and processors in the CUDA architecture.

A multiprocessor is designed to execute hundreds of threads concurrently. To manage such a large number of threads running several different programs, the multiprocessor employs a new architecture called SIMT (Single-Instruction, Multiple-Thread) architecture. The multiprocessor maps each thread to one scalar processor, and each thread executes independently with its own instruction address and register state. SIMT enables programmers to write thread-level

parallel code for independent, scalar threads, as well as data-parallel code for coordinated threads.

Figure 2.10: CUDA Software and Hardware Architecture Relationship

The multiprocessor manages, schedules, and executes threads in groups of 32 parallel threads called warps. A half-warp refers either to the first or the second half of a warp. When one or more thread blocks are assigned to a multiprocessor, the processor partitions the threads into warps, which will be scheduled by the warp scheduler for execution. A warp executes one common instruction at a time; therefore it reaches the most efficient performance when all 32 threads of a warp follow the same execution path and access memory in nearby addresses. When some of the threads of a warp diverge at a conditional branch, the warp serially

executes the different branch paths, then converges back to the same execution path when all the paths complete.

The number of blocks and warps that can reside and be processed together on the multiprocessor depends on the number of registers and shared memory available on the multiprocessor and the amount of registers and shared memory used by the kernel. The multiprocessor also has a limit on the number of resident blocks and the number of resident warps. These limitations and the amount of memory resources vary among generations of CUDA architecture. In this thesis, our discussion will focus on the latest CUDA compute architecture code named  $Fermi^{TM}$ .

#### Fermi Architecture

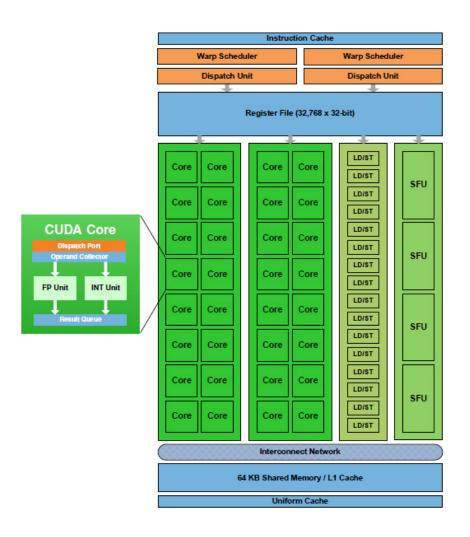

The Fermi architecture is NVIDIA's latest generation of CUDA architecture. Building upon the knowledge from the prior generations of processors, the new architecture has taken new approaches in design and achieved significant improvement in compute power through architectural innovations. With the increases in programmability and compute efficiency, the Fermi architecture is known to be the world's first computational GPU [41].

To target the performance in programmability and compute efficiency, Fermi architecture introduces the third generation streaming multiprocessor. The Fermi based GPUs consist of up to 16 Streaming Multiprocessors (SMs). Each SM consists of 32 Scalar Processors (SPs); four fold increases compared to the prior generation, and 4 special function units (SFU). This features a total of 512 SPs per GPU (Figure 2.11). To achieve near peak hardware performance, two warp schedulers and two instruction dispatch units are introduced to allow two warps to

Figure 2.11: Fermi Streaming Multiprocessor [41]

be issued and executed concurrently. Double precision floating point arithmetic performances have also advanced up to 16 double precision multiply-add operations per SM, per clock, translated to 8x performance over the previous generation. 64KB of RAM with configurable partitioning of shared memory and L1 cache further extends the data sharing capacity among threads of the same thread block to greatly reduce off-chip traffic.

Memory subsystem of the Fermi architecture also demonstrates major improvements on memory hierarchy, called Parallel DataCache hierarchy, and atomic memory operation performance. The Parallel DataCache hierarchy, which consists of per-SM configurable L1 caches and unified L2 cache, provides a single unified memory request path for loads and stores and greatly improves performance over direct access to DRAM. Atomic memory operations allows concurrent threads to correctly perform read-modify-write operations on shared data structure which is one of the important elements in parallel programming. In the new architecture, more atomic units are available in hardware. Along with the addition of the L2 cache, atomic operations performance is up to 20x faster compared to the prior generation architecture.

In this thesis, our implementation and analysis result is based on the NVIDIA GeForce GTX 480 device. Table 2.1 highlights the hardware specification of this device along with the previous generation of GTX 285.

|                                 | GeForce GTX 285 | GeForce GTX 480                                         |

|---------------------------------|-----------------|---------------------------------------------------------|

| Transistor count                | 1.4B            | 3.0B                                                    |

| Process node                    | 55 nm @ TSMC    | 40 nm @ TSMC                                            |

| Core clock                      | 648 MHz         | 700 MHz                                                 |

| Memory clock                    | 1300 MHz        | 924 MHz                                                 |

| Memory transfer rate            | 2600 MT/s       | 3696 MT/s                                               |

| Memory bus width                | 512 bits        | 384 bits                                                |

| Memory bandwidth                | 166.4 GB/s      | 177.4 GB/s                                              |

| CUDA processors                 | 240             | 480                                                     |

| SM count                        | 30              | 15                                                      |

| Special Function Units (per SM) | 2               | 4                                                       |

| Shared Memory (per SM)          | 16 KB           | Configurable 48 KB or<br>16 KB<br>Configurable 16 KB or |

| L1 Cache (per SM)               | None            | 48 KB                                                   |

| L2 Cache                        | None            | 768 KB                                                  |

| Global Memory                   | 1024 MB         | 1536 MB                                                 |

| Peak single-precision FLOPS     | 0.708 Tflops    | 1.35 Tflops                                             |

| Peak double-precision FLOPS     | 88.5 Gflops     | 168 Gflops                                              |

Table 2.1: GeForce GTX285 and GTX480 Hardware Specification

# Related Work

The increasing programmability and compute efficiency of the GPU architecture has attracted many researchers in adapting this computing model to registration algorithms. Earlier work in this area was restricted in mapping the programs (non-graphic applications) to graphics processing pipeline in terms of vertex and fragment shaders. This approach suffers from substantial programming overhead and results in modest performance improvements over CPU-based implementations.

Latest software platforms for GPU programming, NVIDIA's CUDA and AMD/ATI's Brook+, have drastically changed the programming paradigm to resolve this limitation by increasing the programmability. The programming environment is C/C++-like and it is easy to be upgraded for future generations of hardware. These programming model and architectural changes enable GPUs to general-purpose programming for various non-graphic applications. As NVIDIA's CUDA has been exclusively adopted by the research community, the papers referenced in this thesis are all developed based on CUDA.

GPUs are equipped for speeding up geometric transformations part of the image registration process, so the computation efficiency of similarity measures becomes a critical knob of the overall performance. For single-modality similarity measure implementation, the algorithm falls naturally onto the parallel architectures and the entire registration process can be efficiently parallelized. The input data can be processed independently, ideal for the SIMT architecture, with only a final reduction step to generate the result. Plishker et al. [42] have reported a CUDA implementation of SSD based rigid and nonrigid registration. Muyan-Ozcelik et al. [43] have reported a CUDA implementation of Demons deformable registration algorithm.

Compared to single modality image registration, similarity measures for multimodality image registration require statistical measure like mutual information (MI) is not a trivial translation on GPUs. Efficient mutual histogram compilation scheme on GPUs previously proposed have involved special handling on data distribution, data alignment, subsampling, memory/cache hierarchy, etc.. However, performance improvement usually comes in the cost of reduced accuracy by using smaller sample size (image voxels subsampling) or fewer histogram bins (less precise image intensity). Lin and Medioni [44] presented an implementation of Viola's [18] MI approximation method based on stochastic sampling of image intensities and Parzen windowing. Shams et al. proposed an approximate histogram computation method to speed up MI computation [45]. Without tolerating the lost in registration accuracy, Sham et al [46] later presented the 'sort and count' method for histogram computation on the entire data set. This method sorts blocks of data with a parallel sort algorithm before writing to the memory to ease the need for synchronization or atomic operations.

A comprehensive survey of MI-based registration on GPU was presented by Shams et al. [37]. Table 2.2 highlights the recently reported results of rigid and nonrigid MI-based image registration implementations. As the GPU architecture has been rapidly evolving in the past few years, inter-architecture performance comparison of reported results becomes challenging. Research groups generally benchmark their implementations with the latest available GPU architecture compared with the CPU implementation, but rarely compared across GPU platforms. Hardware, software, and compiler improvement in different versions of the GPU architectures would significantly alter the performance results. Besides,

most groups report their speedups for the entire registration algorithm and for specific data sets. Comparison of different results is further complicated as other techniques might have been implemented for further speed up; for example multi-resolution scheme, specific convergence criteria for optimization algorithm, etc.. To better present the performance results, normalized results are given in terms of average execution time in milliseconds per mega-voxel per iteration of the optimization algorithm (ms/MVoxel/itr).

| Group      | Hardware                       | Pref. | Techniques                     |

|------------|--------------------------------|-------|--------------------------------|

| SHAMS [45] | GTX 8800<br>(16 MP/ 128 CORES) | 6.17  | MI ESTIMATED BY BIN SAMPLING   |

| LIN [44]   | GTX 8800<br>(16 MP/ 128 CORES) | _     | MI ESTIMATED BY SAMPLING       |

|            | GTX 280                        |       | MI COMPUTED USING BITONIC SORT |

| SHAMS [46] | (30 MP/ 240 CORES)             | 4.06  | AND COUNT                      |

|            |                                | (a)   |                                |

| Group       | Hardward          | Pref | Technique                        |

|-------------|-------------------|------|----------------------------------|

|             |                   |      | COMBINED MI AND KULLBACK-LEIBLER |

| VETTER [48] | GTX 7800          | 2860 | MEASURE                          |

|             | GTX 8800 ULTRA    |      | COMBINED MI AND KULLBACK-LEIBLER |

| FAN[49]     | (16 MP/128 CORES) | 324  | MEASURE                          |

|             | •                 | (b)  | •                                |

Table 2.2: Summary of Recently Reported GPU/MI-based Image Registration (a) Rigid (b) Nonrigid Image Registration [47]

For rigid image registration, the *sort and count* technique proposed by Sham et al has presented the most significant performance improvement. While it performs well on registrations with nearest-neighbor interpolation (each input data point results in one output data), the performance gains degrades for registrations with

partial volume interpolation (each input data point results in eight output data) which is a crucial component for MI-based nonrigid registration. The execution time of the *sort and count* operation on the larger output data set dominates the overall registration runtime. For nonrigid registration, the solutions proposed by Vetter et al [48] and Fan et al [49] reported noticeable speedup over the CPU implements, however, the performances is still far from acceptable for real-time applications.

In addition, the latest GPU architecture, for example NIVIDA *Fermi*, continues to report improvements in both hardware and software critical for general purpose computing. The new memory hierarchy in particular allows efficient data caching which shows significant performance improvement in atomic update operations. These technological improvements do not only scaling the throughput of the existing implementations; they also give researchers the flexibility in exploring innovative approaches for better designs and implementations of parallel image registration algorithms.

#### **Validation**

The GPU-based implementation presented in this thesis will be compared with a CPU and a FPGA implementation in terms of execution time and registration accuracy. Table 2.3 shows the hardware used for validation. To better present the speedup without the dependence on the size of images involved and the number

of optimization iterations, the execution time is normalized and averaged in milliseconds for a single iteration for processing 1,000,000 voxel pairs (ms/MVoxel/itr).

GPU GTX480, 1GB Memory, 15 SMs, 480 SPs, 48KB

CPU (host) Intel Xeon 2.33GHz, 4GB RAM

FPGA Altera Stratix II FPGA 200MHz, 1GB RAM

Table 2.3: Hardware Specification

Five artificially deformed CT-CT image pairs are used as test cases. The known deformation fields of these testsets are used as reference. The RMS of the resulting deformation fields from different implementations will be computed against the reference data.

# **Chapter 3: MI-based Image Registration on GPU**

This chapter presents a GPU-based implementation for mutual information based rigid image registration. First, we discuss previously reported works and their limitations. Next, we present various considerations of our implementation to show how our implementation maps rigid registration algorithm in general to the GPU architecture. This implementation approach not only can fully exercise the GPU compute capacity, but also retain the scalability. Finally, we compare the performance of this implementation with earlier reported result.

#### Motivation

The maximization of mutual information is the core computation in both rigid and nonrigid intensity-based image registration. The most common approach to computing MI is mutual histogram-based approach. The mutual histogram accumulation process requires intensive computation power and excessive memory accesses. Various multiprocessor solutions (multicore processor, CPU cluster and GPU) have been proposed over the years to accelerate the parallelizable computation; however, these solutions have not fully addressed the limitations on memory access and thus provide moderate acceleration at best.

Mutual information measures the similarity in a pair of images by first constructing the mutual (joint) histogram and then determining the joint and individual probability distribution functions (pdfs) and entropies. In the maximization process, the result forms the input to the optimization engine that

computes the next set of candidate registration parameters. The process repeats until the maximum of mutual information is reached.

In every iteration of the optimization algorithm, every voxel in the reference image is mapped to one voxel or a group of voxels, depending on the interpolation scheme, in the floating image. Based on the intensity of voxels, one or several bins of the mutual histogram are updated. For an image of size n, the computation time is on the order of O(n), which is also the order of the number of memory accesses.

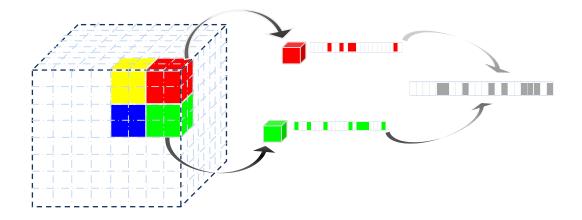

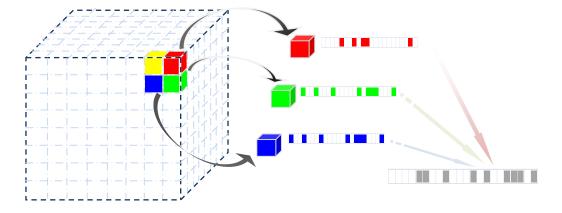

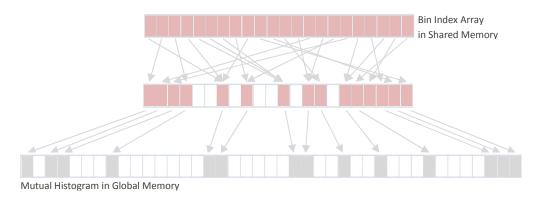

Previous multiprocessor solutions, CPU cluster in particular, accelerate this process by dividing the images into a number of subimages (subvolumes) and distributing the data across the cluster (Figure 3.1). Each processor is responsible for processing one part of the image while managing its own partial mutual histogram. These individual partial mutual histograms are sent back to the host machine at the end of the process and combined into a single mutual histogram. The speedup of this approach is generally limited by the number of processors in the cluster as the number of parallelizable subimages is constrained by the number of processors and each processor processes the subvolumes voxels in series. As the number of subvolumes goes up, the number of partial mutual histograms, which needed to be consolidated at the end of the process, also goes up.

Figure 3.1: Block distribution scheme for CPU cluster implementation with distributed partial mutual histograms

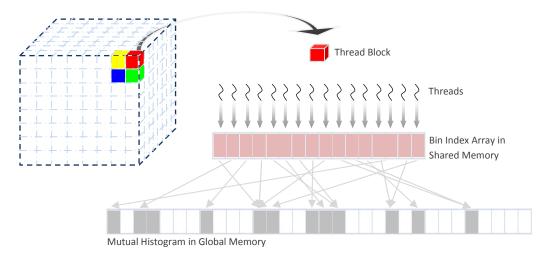

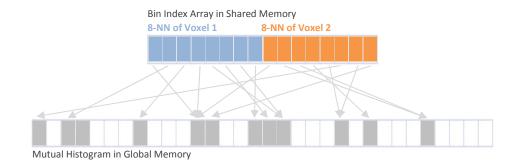

With the parallel nature of the voxel coordinate transformation computation, GPU, which offers massive parallel compute power, appears to be a suitable platform for the MI problem. Ideally, with the GPU architecture, thread blocks can be visualized as CPUs in the cluster. The image is again divided into a number of subvolumes and each thread block is assigned a specific subvolume (Figure 3.2). Voxels in each subvolume are processed in parallel by the threads of the assigned thread block. Depending on the number of threads available in each block, each thread processes one or more voxels until all voxel in the subvolume are covered. Results are updated onto the partial mutual histogram residing at each block (shared memory). The partial mutual histograms will eventually be combined into a single mutual histogram in the main memory (global memory).

Figure 3.2: Block assignment scheme for GPU implementation with distributed partial mutual histograms in shared memory

Although the number of threads available is virtually unlimited, the amount of shared memory available for each thread block is constrained by the current technology. Medical images are either natively 8-bit or converted down to 8 bits for intensity-based image registration. This translates to a mutual histogram size of 256 x 256 bins, which far exceeds the available shared memory size offered by the current GPU architecture for accumulating partial mutual histogram in a thread block, regardless of the data type.

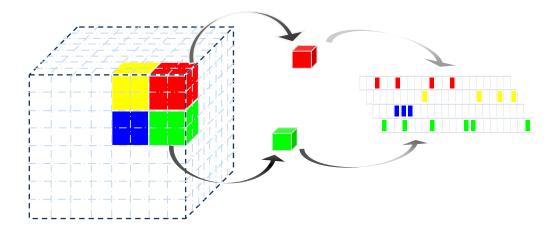

An obvious alternative is to store the partial histograms directly in the global memory instead of the shared memory (Figure 3.3). The drawback is the global memory access latency penalty ranges from 200 to 300 cycles. Besides, every block has a dedicated partial mutual histogram in the global memory; the number of blocks is now limited by the global memory size which hinders the scalability of this approach.

Figure 3.3: Block assignment scheme for GPU implementation with partial mutual histograms in global memory

Depending on the GPU architecture, atomic update can be a feasible solution for easing the constraint caused by the global memory size. Instead of assigning a dedicated partial mutual histogram for each thread block, all thread blocks would update a single histogram in the global memory. Atomic update operations generally exhibit longer latency. The latest GPU architecture has attempted to resolve this performance bottleneck by introducing true cache hierarchy. Significant speedup in atomic update operations is reported compared to the previous generation of the architecture. With proper interleaving of compute and memory access operations, the memory access latency can be hidden from the overall execution time.

Some applications have sacrificed registration accuracy for performance by either decreasing the number of bins of the mutual histograms to fit a smaller version of the partial mutual histograms in the shared memory, or decreasing the number of samples (image voxels) in order to decrease the number of mutual histogram

accesses to the global memory. These alternatives might seem applicable for some applications, but are not practical for MI-based nonrigid image registration and are not considered in this work as a high degree of accuracy is crucial for eventual clinical use.

Philip [50] proposed a bit-slicing solution, which subdivides the images by voxel intensity, and consequently subdivides the mutual histogram. With this approach, each thread block is assigned to reference image voxels of the same intensities; therefore, only one "slice" of the mutual histogram (256 bins in the case of 8-bit intensity images) is needed to be maintained in the shared memory. The bit-slicing solution addresses the limitation in shared memory and the time overhead in the mutual histogram combination step; however, it requires fast preprocessing and load balancing support. When the intensity distribution is unbalanced, multiple blocks would be required to process voxels of a single intensity and mutual histogram combination step still cannot be avoided.

These proposed solutions addressed some of the issues in the lengthy MI computation process but have not yet fully exploited the compute capability of the GPU, which is architecturally different from the traditional CPU or CPU-cluster architecture, and integrated that into their algorithms. The constraints in the number and the size of the thread blocks drafted in these solutions limited the scalability of these algorithms. As a result, only moderate acceleration was achieved with the growing trend of multicore architectures.

### GPU Implementation of Rigid Registration

We have first explored the fundamental design considerations based on the basic rigid image registration problem. In rigid registration, the entire 3D image is transformed with the same transformation matrix and the computation of each element is totally independent from other elements. If unlimited number of threads and compute capacity are available, all voxels could potentially be processed concurrently. This observation leads to the following proposed solution.

## Voxel-to-Thread Approach

To better utilize the GPU capacity for computation acceleration problem, maximization of parallelism and minimization of memory access are the two fundamental goals we want to achieve. One of the crucial decisions in achieving these goals is to determine the proper image subdivision and thread block allocation schemes to better balance the throughput and memory usage.

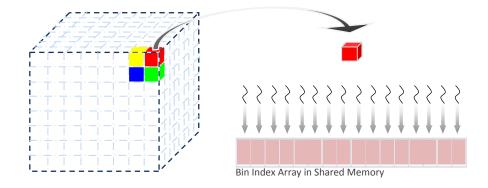

As discussed previously, designers typically approach this problem taking the global memory limitation of fitting the mutual histograms as priority. As a result, only small number of blocks is initialized with the maximum number of threads allowable to iterate through the assigned portion of the subdivided image. We approach this problem from the opposite direction by taking the benefit of the enhanced atomic update operations in the latest architecture. Instead of limiting

Figure 3.4: Voxel-to-Thread based thread block assignment scheme

ourselves by the memory usage of storing the mutual histograms, we maximize the parallelism of the algorithm by launching as many threads as the number of voxels in the image. Each thread is dedicated to process only one voxel in the reference image. Instead of maintaining a partial mutual histogram of any form in each block and having each thread to immediately update the result onto its local histogram, each thread will simply write the resulting bin index to an array (Figure 3.4). Therefore, the size of the thread blocks is solely determined by the number of registers and shared memory used by each thread for reading the image voxel intensities and storing the resulting bin indices. The size of the thread

Figure 3.5: Voxel-to-Thread based blocks assignment scheme

blocks is equivalent to the size of the subimage blocks in this approach (Figure 3.5). Therefore, the larger the thread block size, the fewer is the total number of thread blocks.

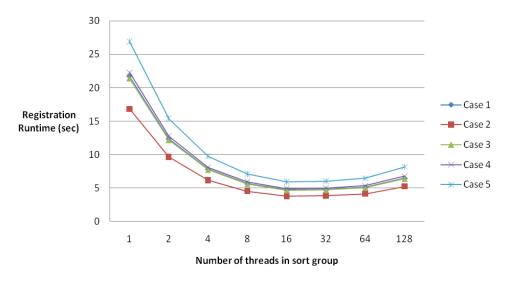

Although it seems reasonable to define the thread block size simply based on the maximum technology limits (1024 threads for Fermi) and memory usage, the balance between the number of threads per block and the overall number of blocks should be considered. Larger block size might not result in optimal performance. We have examined the effect in performance with various block sizes ranging from 32 threads (one warp) to 1024 threads. For rigid registration with nearest-neighbor interpolation, specifying 128-threads per block results in optimal performance (Table 3.1). Thread block dimensions also slightly alter the overall performance. As GPU memory access is warp-based, better block dimension definition could lower the number of memory accesses. Table 3.2 shows four different block dimension definitions and the associated registration runtime. Blocks of 8 x 4 x 4 show slight performance gain in runtime.

| Number of |        |        | (sec)  |        |        |

|-----------|--------|--------|--------|--------|--------|

| Threads   | Case 1 | Case 2 | Case 3 | Case 4 | Case 5 |

| 32        | 6.66   | 5.36   | 6.56   | 6.94   | 8.37   |

| 64        | 4.97   | 3.99   | 4.90   | 5.17   | 6.22   |

| 128       | 4.83   | 3.86   | 4.75   | 5.02   | 6.01   |

| 256       | 4.93   | 3.95   | 4.86   | 5.13   | 6.15   |

| 512       | 5.06   | 4.05   | 4.98   | 5.26   | 6.32   |

| 1024      | 5.39   | 4.33   | 5.33   | 5.62   | 6.75   |

Table 3.1: Thread Block Size vs Registration Runtime (sec)

|    |   |   |        |        | (sec)  |        |        |

|----|---|---|--------|--------|--------|--------|--------|

| X  | Υ | Z | Case 1 | Case 2 | Case 3 | Case 4 | Case 5 |

| 8  | 4 | 4 | 4.76   | 3.81   | 4.67   | 4.95   | 5.94   |

| 16 | 4 | 2 | 4.86   | 3.87   | 4.79   | 5.05   | 6.05   |

| 16 | 8 | 1 | 4.82   | 3.84   | 4.75   | 5.01   | 6      |

| 32 | 4 | 1 | 4.92   | 3.93   | 4.84   | 5.11   | 6.09   |

Table 3.2: Thread Block Dimension vs Registration Runtime (sec)

# Warp Level Global Memory Access Reduction